Renesas Electronics 8V19N882 RF Clock Generator & Jitter Attenuator

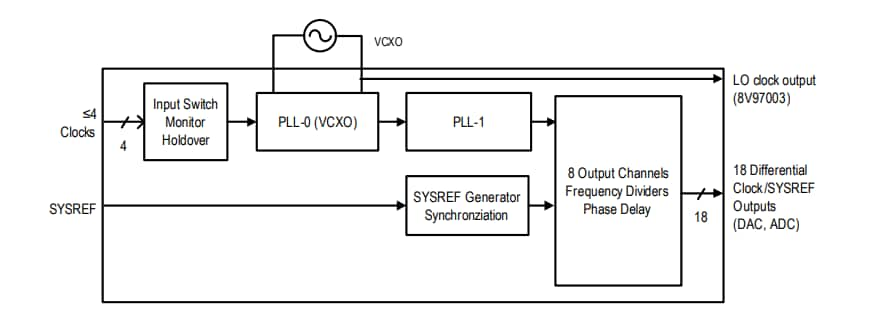

Renesas Electronics 8V19N882 RF Sampling Clock Generator and Jitter Attenuator is a high-performance clock solution for conditioning and frequency/phase management of wireless base station radio equipment boards. The 8V19N882 is optimized to deliver excellent phase noise performance as required in 4G, 5G, and including mmWave radio implementations.The Renesas 8V19N882 RF Sampling Clock Generator and Jitter Attenuator support JESD204B (subclass 0 and 1) and JESD204C. A two-stage PLL architecture provides both jitter attenuation and frequency multiplication. The first stage PLL is the jitter attenuator and uses an external VCXO for the best possible phase noise characteristics. In the second stage, PLL locks on the first PLL output signal and synthesizes the target frequency. The second stage PLL, can use the internal or an external high-frequency VCO.

The 8V19N882 is configured through a 3/4-wire SPI interface, and reports lock and signal loss status in internal registers and via the GPIO[1:0] outputs. Internal status bit changes are reported via a GPIO output.

Features

- High-performance clock RF sampling clock generator and clock jitter attenuator with support for JESD204B/C

- -144.7dBc/Hz (800kHz offset; 491.52MHz) Low phase noise

- Integrated phase noise of 74fs RMS (12kHz to 20MHz, 491.52MHz)

- Dual-PLL architecture with internal and optional external VCO

- Eight output channels with a total of 16 outputs

- Configurable integer clock frequency dividers

- Up to 3932.16MHz (Internal VCO) and 6GHz (optional external VCO) clock output frequencies

- Differential, low noise I/O

- Deterministic phase delay and integrated phase delay circuits

- Redundant input clock architecture with two inputs and monitors, holdover and input switching

- SPI 3/4 wire configuration interface

- 1.8V, 2.5V and 3.3V Supply voltage

- 76-VFQFN (9mm × 9mm) Package

- -40°C to +105°C Board temperature range

Applications

- Wireless infrastructure applications: 4G, 5G, and mmWave

- Data acquisition: jitter-sensitive ADC and DAC circuits

- Radar, imaging, instrumentation, and medical

Simplified Block Diagram

Block Diagram (fVCO = 3932.16MHz)

.png)