**ZL70550 Programmer User's Guide

for

ZL70550 Ultra-Low-Power Sub-GHz RF Transceiver**

© 2016 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### About Microsemi

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 4,800 employees globally. Learn more at [www.microsemi.com](http://www.microsemi.com).

# Contents

|                                                 |    |

|-------------------------------------------------|----|

| <b>1 Revision History</b>                       | 1  |

| 1.1 Initial Release History                     | 1  |

| <b>2 Overview</b>                               | 2  |

| 2.1 Introduction                                | 2  |

| 2.2 Product Description                         | 2  |

| <b>3 Architecture</b>                           | 3  |

| 3.1 Block Diagram                               | 3  |

| 3.2 System Clock                                | 3  |

| <b>4 Communication Protocol</b>                 | 4  |

| 4.1 Packet Definition                           | 4  |

| 4.1.1 Packet Modes Overview                     | 4  |

| 4.1.2 Frame Control                             | 7  |

| 4.1.3 Frame Processing                          | 8  |

| 4.1.4 Packet Exchange Timing                    | 12 |

| 4.1.5 Packet Operations                         | 14 |

| 4.1.6 Adaptive Packet Reception                 | 17 |

| 4.1.7 Packet Reception                          | 19 |

| 4.2 Channel Monitoring                          | 19 |

| 4.2.1 CSMA Threshold                            | 20 |

| 4.2.2 RSSI Measurement                          | 20 |

| 4.3 State Machine Diagrams                      | 20 |

| 4.3.1 Single Packet Operation                   | 21 |

| 4.3.2 Transaction Sequence Operation            | 22 |

| <b>5 Application Interface</b>                  | 25 |

| 5.1 Introduction                                | 25 |

| 5.1.1 Support for Peripheral Access and Control | 25 |

| 5.2 Serial Peripheral Interface                 | 25 |

| 5.2.1 SPI Principles                            | 25 |

| 5.2.2 SPI Command Set                           | 25 |

| 5.2.3 SPI Command Encoding                      | 26 |

| 5.2.4 SPI Status                                | 27 |

| 5.3 SPI Commands                                | 27 |

| 5.3.1 Short-Address Read and Write              | 27 |

| 5.3.2 Long-Address Read and Write               | 28 |

| 5.3.3 Packet Write                              | 28 |

| 5.3.4 Packet Read                               | 29 |

| 5.3.5 Other SPI Commands                        | 29 |

| 5.4 Registers, Interrupts, and Memory Map       | 30 |

| 5.4.1 Registers                                 | 30 |

| 5.4.2 Basic Memory Map                          | 30 |

| 5.4.3 Interrupts                                | 30 |

| 5.4.4 Interrupt Controller                      | 31 |

| 5.5 GPIO Pins                                   | 32 |

| <b>6 Setup and Initialization</b>               | 35 |

| 6.1 Power Management                            | 35 |

| 6.1.1 Power Domains                             | 35 |

| 6.1.2 Power Modes                               | 35 |

|          |                                                                        |           |

|----------|------------------------------------------------------------------------|-----------|

| 6.2      | Power Up .....                                                         | 35        |

| 6.2.1    | Initial Reset .....                                                    | 35        |

| 6.2.2    | Wake-Up Operation .....                                                | 35        |

| 6.2.3    | Monitoring Wake-Up .....                                               | 35        |

| 6.3      | Sleep Operation .....                                                  | 36        |

| 6.3.1    | Manual Sleep Operation .....                                           | 36        |

| 6.3.2    | Automatic Sleep Operation .....                                        | 36        |

| 6.4      | Synthesizer Controller and Channel Selection .....                     | 36        |

| 6.4.1    | A and M Requirements .....                                             | 36        |

| 6.4.2    | A and M Value Calculation .....                                        | 36        |

| 6.4.3    | Channel Frequency Calculation .....                                    | 37        |

| 6.4.4    | A and M Programming Example .....                                      | 37        |

| 6.5      | Recommended Initialization Settings .....                              | 37        |

| 6.5.1    | Z-Star Operation .....                                                 | 38        |

| 6.5.2    | For Raw Bit Mode .....                                                 | 38        |

| <b>7</b> | <b>Calibrations .....</b>                                              | <b>40</b> |

| 7.1      | Overview/Summary .....                                                 | 40        |

| 7.2      | Sequence .....                                                         | 41        |

| 7.3      | Setup, Initiation, and Control of Calibrations .....                   | 42        |

| 7.4      | Required Time for Calibrations .....                                   | 43        |

| 7.5      | Procedures .....                                                       | 43        |

| 7.5.1    | Current Reference Trimming .....                                       | 43        |

| 7.5.2    | XO Tuning .....                                                        | 43        |

| 7.5.3    | RCO Tuning .....                                                       | 45        |

| 7.5.4    | VCO Frequency and Amplitude Trimming .....                             | 45        |

| 7.5.5    | Blocker Peak Detector Offset Trimming .....                            | 48        |

| 7.5.6    | Antenna Tuning .....                                                   | 48        |

| 7.5.7    | LNA Load Tuning .....                                                  | 49        |

| 7.5.8    | RX Filter (FM detector, IF filter, and Gaussian filter) Trimming ..... | 50        |

| 7.5.9    | FSK Deviation Trimming .....                                           | 50        |

| 7.5.10   | Output Power Trimming .....                                            | 50        |

| 7.5.11   | LNA Gain .....                                                         | 51        |

| <b>8</b> | <b>Registers .....</b>                                                 | <b>52</b> |

| 8.1      | Using the Memory Map .....                                             | 52        |

| 8.2      | Address Space .....                                                    | 53        |

| 8.3      | SPI Local Registers .....                                              | 61        |

| 8.3.1    | Chip ID .....                                                          | 61        |

| 8.3.2    | Chip Revision .....                                                    | 61        |

| 8.3.3    | 2V Reset Generator .....                                               | 61        |

| 8.3.4    | Chip Reset .....                                                       | 62        |

| 8.3.5    | Power Down Request .....                                               | 62        |

| 8.3.6    | SPIR Local Status .....                                                | 62        |

| 8.3.7    | SPI Control Register .....                                             | 63        |

| 8.4      | System Bus Control and Status Registers .....                          | 63        |

| 8.4.1    | Frame Sync Control 1 .....                                             | 63        |

| 8.4.2    | Received PHY Header Status .....                                       | 64        |

| 8.4.3    | RX Payload Length .....                                                | 64        |

| 8.4.4    | MAC SPI Status .....                                                   | 65        |

| 8.4.5    | RX Frame Length .....                                                  | 65        |

| 8.4.6    | Fields Received in Z-Star MAC Header .....                             | 65        |

| 8.4.7    | MAC RX Frame Status .....                                              | 67        |

| 8.4.8    | MAC Sequencer Status .....                                             | 68        |

| 8.4.9    | Manual Global Enables .....                                            | 69        |

| 8.4.10   | Manual Miscellaneous .....                                             | 69        |

|        |                                                                                                       |    |

|--------|-------------------------------------------------------------------------------------------------------|----|

| 8.4.11 | Clock Enable Tests .....                                                                              | 70 |

| 8.4.12 | ADC Mode Conversion .....                                                                             | 70 |

| 8.4.13 | Maximum Result in ADC Modes and When Using RSSI in CSMA-CA Modes .....                                | 71 |

| 8.4.14 | Average Result in ADC Modes and When Using RSSI in CSMA-CA Modes .....                                | 71 |

| 8.4.15 | Trimmed RSSI Average at Completion of DC Restore Process in RSSI Detect Modes with CSMA Not Active 71 |    |

| 8.4.16 | IRQ Status .....                                                                                      | 72 |

| 8.4.17 | Trim Command .....                                                                                    | 74 |

| 8.4.18 | LNA Trim Peak ADC Value .....                                                                         | 74 |

| 8.4.19 | Antenna Trim Peak ADC Value .....                                                                     | 74 |

| 8.5    | Always-On System Bus Control and Status Registers .....                                               | 75 |

| 8.5.1  | VCO Frequency Tune Value for RX Mode .....                                                            | 75 |

| 8.5.2  | VCO Frequency Tune Value for TX mode (with modulation off) with Power Amplifier Off (only bias on) 75 |    |

| 8.5.3  | VCO Frequency Tune Value for TX mode (with modulation off) with Power Amplifier On .....              | 76 |

| 8.5.4  | VCO Frequency Tune Value at Output of Multiplexer .....                                               | 76 |

| 8.5.5  | VCO Frequency Band Trim Value .....                                                                   | 77 |

| 8.5.6  | Modulator DAC Trim Value .....                                                                        | 77 |

| 8.5.7  | Frequency Deviation Trim Target .....                                                                 | 77 |

| 8.5.8  | RC Oscillator Frequency Trim Value .....                                                              | 77 |

| 8.5.9  | LNA Frequency Trim .....                                                                              | 78 |

| 8.5.10 | Manual LNA Trim Value .....                                                                           | 78 |

| 8.5.11 | IREF Resistor Trim Value .....                                                                        | 78 |

| 8.5.12 | Crystal Oscillator Trim Value .....                                                                   | 79 |

| 8.5.13 | Gaussian Filter Trim Value .....                                                                      | 79 |

| 8.5.14 | VCO Amplitude Trim Value .....                                                                        | 79 |

| 8.5.15 | Antenna Trim Value .....                                                                              | 79 |

| 8.5.16 | RX Peak Detector Trim Value .....                                                                     | 80 |

| 8.5.17 | Initial DC Correct/AFC Value .....                                                                    | 80 |

| 8.5.18 | IRQ Enables .....                                                                                     | 80 |

| 8.5.19 | Pad Enable .....                                                                                      | 81 |

| 8.5.20 | TX Control .....                                                                                      | 82 |

| 8.5.21 | TX Frame-Packet Buffer Length .....                                                                   | 84 |

| 8.5.22 | TX Frame Control for Z-Star Packet Mode .....                                                         | 85 |

| 8.5.23 | TX Frame Sequence Number for Z-Star Packet Mode .....                                                 | 85 |

| 8.5.24 | RX Control for Z-Star Packet Mode .....                                                               | 86 |

| 8.5.25 | Address Mask .....                                                                                    | 88 |

| 8.5.26 | RX Buffer Length .....                                                                                | 88 |

| 8.5.27 | RX Buffer Write Threshold .....                                                                       | 89 |

| 8.5.28 | Network ID .....                                                                                      | 89 |

| 8.5.29 | Device Short ID: Address of This Device .....                                                         | 89 |

| 8.5.30 | Short ID: Address of Other Device .....                                                               | 89 |

| 8.5.31 | Long ID of This Device .....                                                                          | 90 |

| 8.5.32 | Long ID of Other Device .....                                                                         | 90 |

| 8.5.33 | MAC Controls .....                                                                                    | 90 |

| 8.5.34 | CRC Polynomial .....                                                                                  | 91 |

| 8.5.35 | SPI Control .....                                                                                     | 91 |

| 8.5.36 | CSMA Control .....                                                                                    | 92 |

| 8.5.37 | CSMA 100- $\mu$ s Counts Per Interval .....                                                           | 92 |

| 8.5.38 | CSMA Maximum Random Number of Intervals in Back-Off .....                                             | 92 |

| 8.5.39 | CSMA Retry Minimum Back-Off in Intervals .....                                                        | 93 |

| 8.5.40 | Synchronization Threshold Minimum Number of Bits That Need to Match the 40-Bit Sync Word 93           |    |

| 8.5.41 | Delay Time Count for ptx_tx_trig .....                                                                | 93 |

| 8.5.42 | Selection for GP Input/Output .....                                                                   | 94 |

| 8.5.43 | Frame Sync Pattern .....                                                                              | 94 |

| 8.5.44 | PLL Start-Up Delay (100- $\mu$ s count) .....                                                         | 95 |

| 8.5.45 | RX Time Limit for Acknowledgment Timeout (100- $\mu$ s count) .....                                   | 95 |

|           |                                                                                                |            |

|-----------|------------------------------------------------------------------------------------------------|------------|

| 8.5.46    | RX Time Limit for Packet Timeout (100- $\mu$ s count) . . . . .                                | 95         |

| 8.5.47    | RX Frame Sequence Number . . . . .                                                             | 96         |

| 8.5.48    | TX Non-Acknowledgment Packet Transmitted Count . . . . .                                       | 96         |

| 8.5.49    | TX Packet Retry Accumulated Count (after ACK failure) . . . . .                                | 96         |

| 8.5.50    | TX Packet Drop Accumulated Count (after ACK failure) . . . . .                                 | 96         |

| 8.5.51    | RX Non-Acknowledgment Packet Received Count . . . . .                                          | 97         |

| 8.5.52    | RX Packet Received Count for All Types . . . . .                                               | 97         |

| 8.5.53    | RX Non-Acknowledgment Packet Drop Accumulated Count . . . . .                                  | 97         |

| 8.5.54    | RX Packet Sync Error Accumulated Count . . . . .                                               | 97         |

| 8.5.55    | RX Packet All Error Accumulated Count for All Errors . . . . .                                 | 98         |

| 8.5.56    | CSMA Retry Count . . . . .                                                                     | 98         |

| 8.5.57    | CSMA Fail Count . . . . .                                                                      | 98         |

| 8.5.58    | PHY RX Mode Select . . . . .                                                                   | 98         |

| 8.5.59    | Frame Sync Control 2 . . . . .                                                                 | 99         |

| 8.5.60    | PHY TX Raw Mode Control . . . . .                                                              | 99         |

| 8.5.61    | Data Rate Control . . . . .                                                                    | 99         |

| 8.5.62    | M Divide Counter Value . . . . .                                                               | 100        |

| 8.5.63    | A Divide Counter Value . . . . .                                                               | 100        |

| 8.5.64    | ADC Modes Multiplexer Input Selection . . . . .                                                | 101        |

| 8.5.65    | Number of Conversions Used for Averaging in ADC Modes and When Using RSSI in CSMA-CA Modes 102 |            |

| 8.5.66    | ADC CSMA Threshold . . . . .                                                                   | 103        |

| 8.5.67    | LNA Gain . . . . .                                                                             | 103        |

| 8.5.68    | PA Power Level . . . . .                                                                       | 103        |

| 8.5.69    | PA Buffer Bias Control . . . . .                                                               | 104        |

| 8.5.70    | VCO Control . . . . .                                                                          | 104        |

| <b>9</b>  | <b>Errata . . . . .</b>                                                                        | <b>105</b> |

| 9.1       | Full VCO Trim Failure . . . . .                                                                | 105        |

| 9.1.1     | Description . . . . .                                                                          | 105        |

| 9.1.2     | Solution or Workaround . . . . .                                                               | 105        |

| <b>10</b> | <b>References . . . . .</b>                                                                    | <b>106</b> |

| <b>11</b> | <b>Glossary . . . . .</b>                                                                      | <b>107</b> |

# Figures

|           |                                                                      |    |

|-----------|----------------------------------------------------------------------|----|

| Figure 1  | ZL70550 Block Diagram                                                | 3  |

| Figure 2  | Packet Format, Z-Star Packet Mode                                    | 5  |

| Figure 3  | Packet Format, User Packet Mode                                      | 6  |

| Figure 4  | Packet Format, Raw Packet Mode                                       | 7  |

| Figure 5  | Basic Transaction                                                    | 8  |

| Figure 6  | Basic Transaction with Retry                                         | 9  |

| Figure 7  | Hub to Node Frame Transaction                                        | 9  |

| Figure 8  | Data Request Transaction                                             | 10 |

| Figure 9  | Packet Processing in User Packet Mode and Raw Packet Mode            | 12 |

| Figure 10 | Default TX Start-Up Timing                                           | 12 |

| Figure 11 | Default RX Start-Up Timing                                           | 13 |

| Figure 12 | Optimized Turnaround in Preamble Detect Mode                         | 14 |

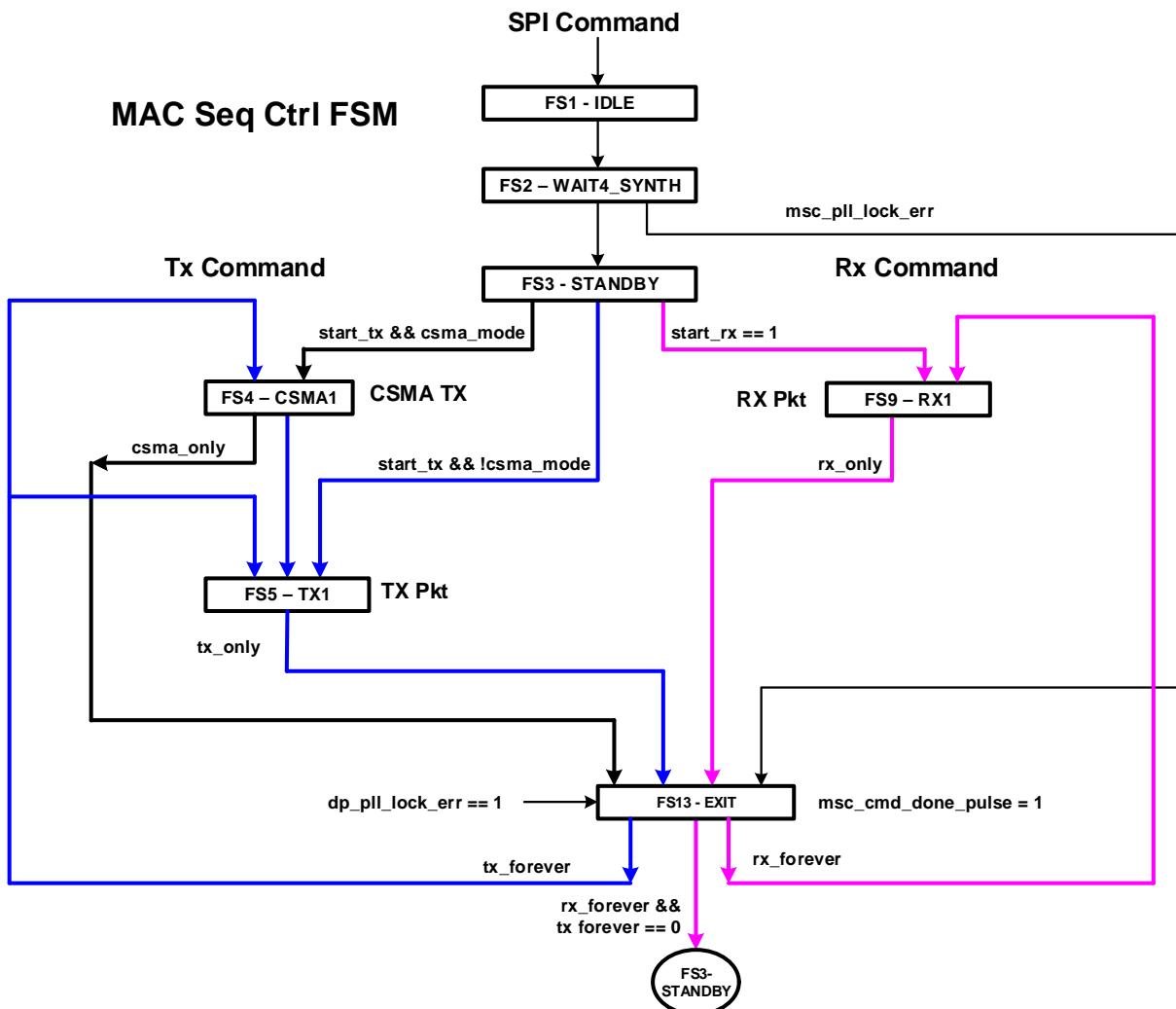

| Figure 13 | Simplified Single Packet Mode State Machine                          | 21 |

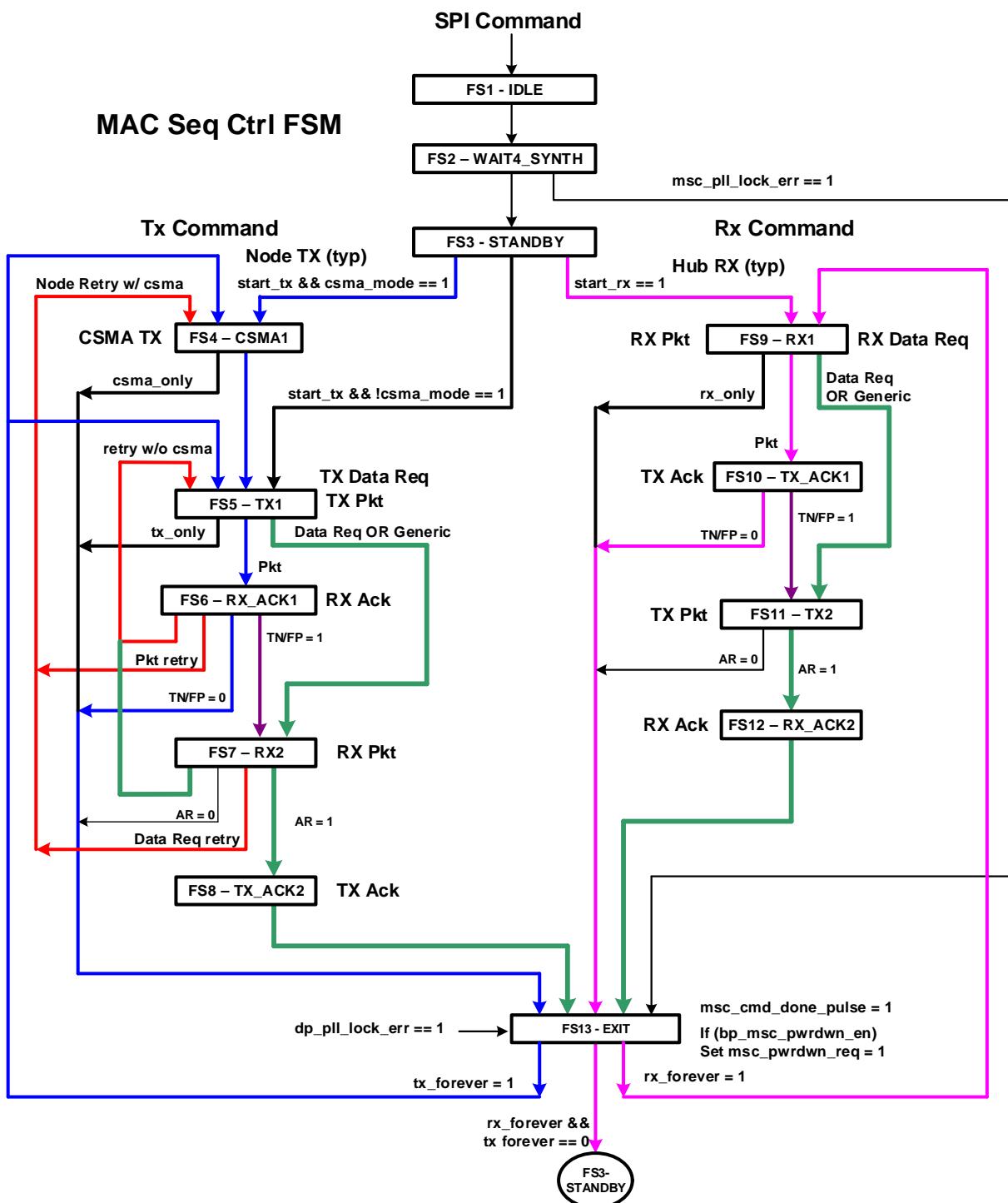

| Figure 14 | Simplified MAC Sequencer State Machine                               | 23 |

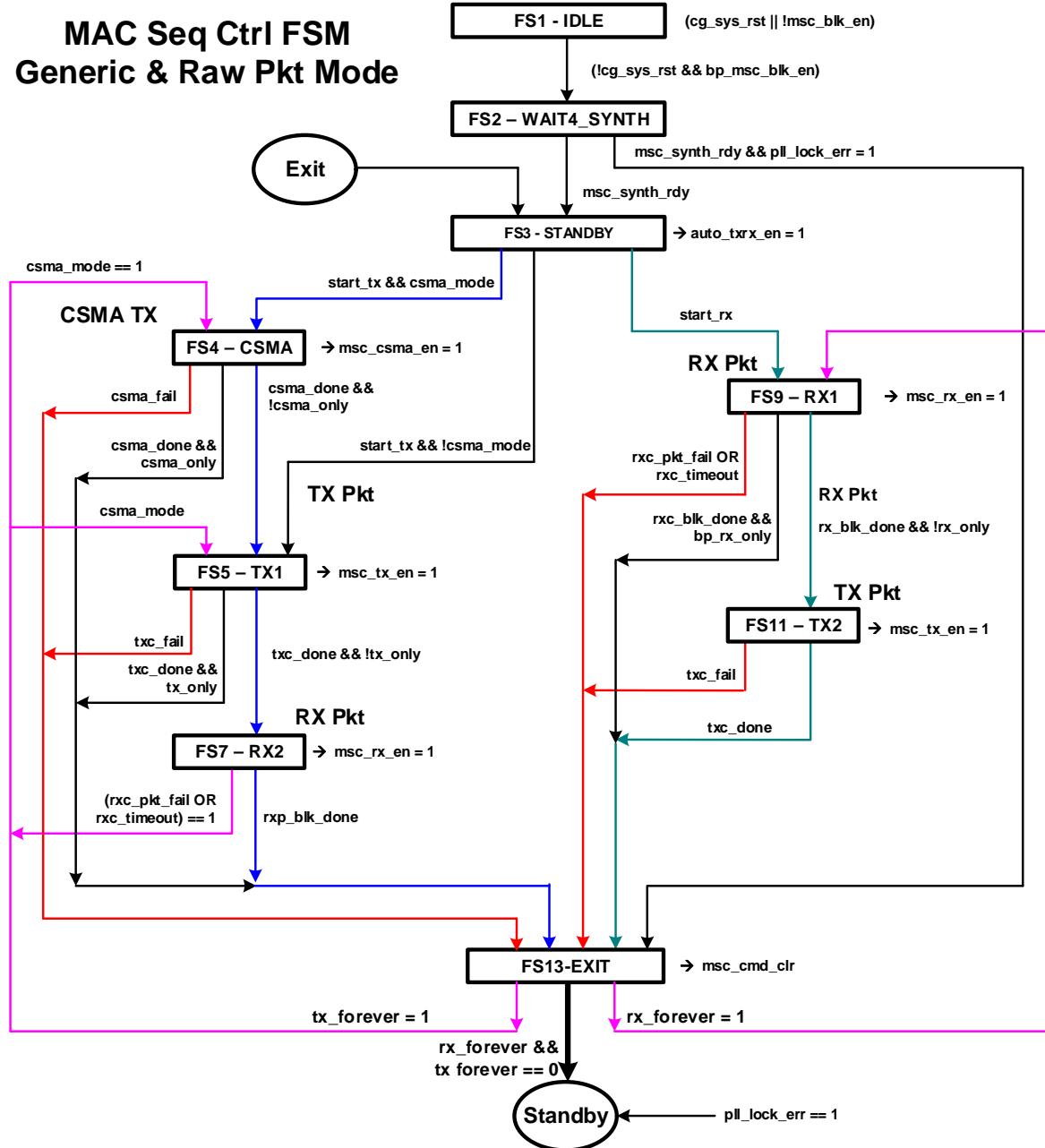

| Figure 15 | State Machine for User Packet Mode and Raw Packet Mode               | 24 |

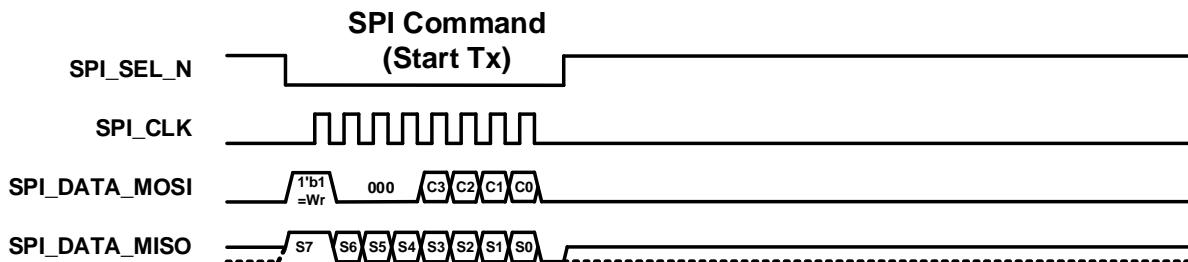

| Figure 16 | SPI Command Encoding                                                 | 26 |

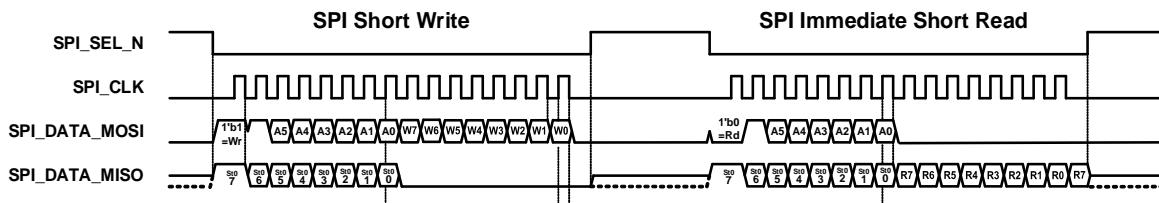

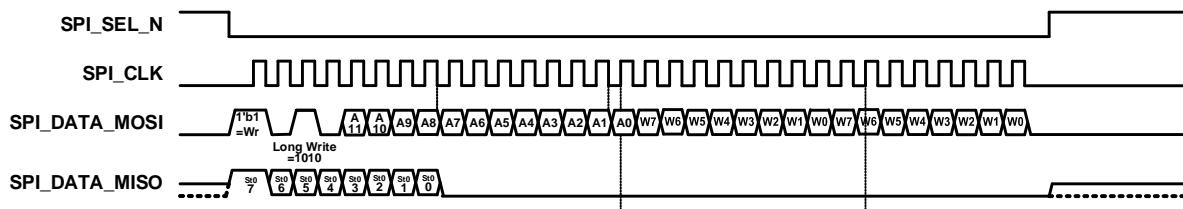

| Figure 17 | Short-Address Read-Write Timing                                      | 28 |

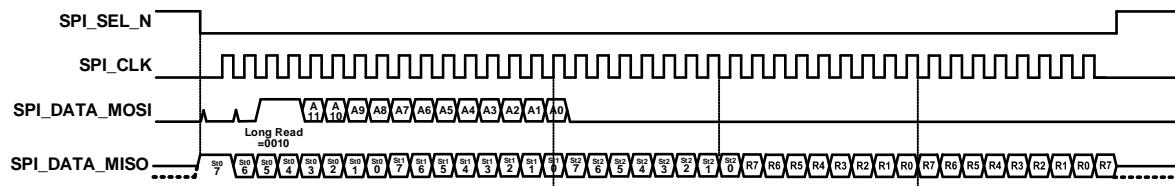

| Figure 18 | Long-Address Read Timing                                             | 28 |

| Figure 19 | Long-Address Write Timing                                            | 28 |

| Figure 20 | Command Timing                                                       | 29 |

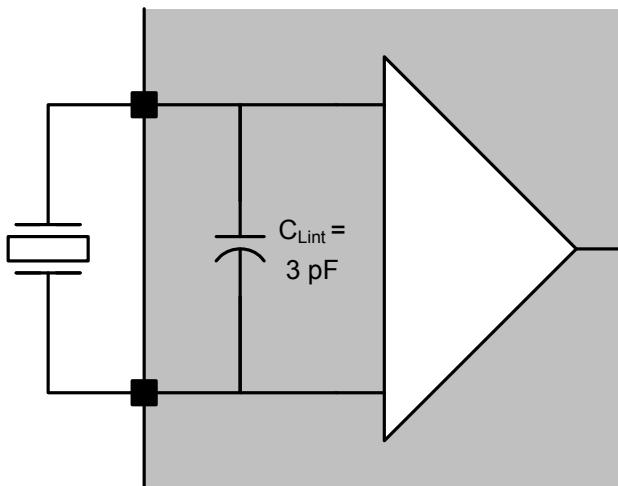

| Figure 21 | Crystal Oscillator with Optional Additional External Load Capacitors | 44 |

# Tables

|          |                                                    |    |

|----------|----------------------------------------------------|----|

| Table 1  | Default Frequencies                                | 3  |

| Table 2  | Packet Modes of Operation                          | 4  |

| Table 3  | Auto Header Generation and Checking                | 11 |

| Table 4  | Settings for TX Frame Sync Polarity and FEC Enable | 18 |

| Table 5  | TX Preamble Pattern                                | 18 |

| Table 6  | Enable for TX FEC Encoding                         | 19 |

| Table 7  | Receiver Hamming Decoder Enable                    | 19 |

| Table 8  | Procedure for Manual RSSI Measurement              | 20 |

| Table 9  | SPI Command Set                                    | 26 |

| Table 10 | SPI Status Returned on MISO                        | 27 |

| Table 11 | Basic Memory Map                                   | 30 |

| Table 12 | ZL70550 Interrupt Register Bit Definitions         | 31 |

| Table 13 | GPIO Output Signal Selection                       | 32 |

| Table 14 | Power Modes and Operational Conditions             | 35 |

| Table 15 | General Parameters                                 | 38 |

| Table 16 | Receive Parameters                                 | 38 |

| Table 17 | TX Raw Bit Mode Controls                           | 38 |

| Table 18 | RX Raw Bit Mode Controls                           | 39 |

| Table 19 | Recommended System Calibration Order               | 41 |

| Table 20 | Procedure for Tune and Trim Setup                  | 42 |

| Table 21 | Trim Commands                                      | 42 |

| Table 22 | Required Time for Calibrations                     | 43 |

| Table 23 | Procedure for Current Reference Trim               | 43 |

| Table 24 | Procedure for Crystal Oscillator Tune              | 44 |

| Table 25 | Procedure for RC Oscillator Trim                   | 45 |

| Table 26 | Typical Frequency Range Selection                  | 46 |

| Table 27 | Procedure for VCO Amplitude Trim                   | 46 |

| Table 28 | Procedure VCO Full Frequency Trim                  | 47 |

| Table 29 | Procedure Blocker Peak Detector Offset Trim        | 48 |

| Table 30 | Procedure for Antenna Tuning                       | 48 |

| Table 31 | Procedure for LNA Load Tune                        | 49 |

| Table 32 | Procedure for RX Filter Tune                       | 50 |

| Table 33 | Procedure for FSK Deviation Trim                   | 50 |

| Table 34 | Procedure for Transmitter Output Power Trim        | 51 |

| Table 35 | Memory Map                                         | 53 |

| Table 36 | SPIR_CHIP_ID                                       | 61 |

| Table 37 | SPIR_REVISION                                      | 61 |

| Table 38 | SPIR_2V_RESET                                      | 61 |

| Table 39 | SPIR_SYS_RESET                                     | 62 |

| Table 40 | SPIR_PWRDWN_REQ                                    | 62 |

| Table 41 | SPIR_LOCAL_STAT                                    | 62 |

| Table 42 | SPIR_CTRL                                          | 63 |

| Table 43 | DP_CTRL0                                           | 63 |

| Table 44 | RPHR_STAT                                          | 64 |

| Table 45 | RXC_PLD_LEN                                        | 64 |

| Table 46 | MSC_SPI_STAT                                       | 65 |

| Table 47 | RXC_FRM_LEN                                        | 65 |

| Table 48 | RXC_FRM_CTRL0                                      | 65 |

| Table 49 | RXC_SOURCE_SID                                     | 66 |

| Table 50 | RXC_NETWORK_ID                                     | 66 |

| Table 51 | RXC_DEST_SID                                       | 66 |

| Table 52 | RXC_FRM_CTRL1                                      | 66 |

| Table 53 | RXC_DEST_LID                                       | 67 |

| Table 54 | RXC_SOURCE_LID                                     | 67 |

| Table 55 | RXC_FRM_STAT0                                      | 67 |

|           |                             |    |

|-----------|-----------------------------|----|

| Table 56  | RXC_FRM_STAT1 .....         | 68 |

| Table 57  | MSC_FRM_STAT0 .....         | 68 |

| Table 58  | MSC_FRM_STAT1 .....         | 69 |

| Table 59  | MAN_GLOBAL_EN .....         | 69 |

| Table 60  | MAN_TEST .....              | 69 |

| Table 61  | CLK_TEST .....              | 70 |

| Table 62  | ADC_CONV_START .....        | 70 |

| Table 63  | ADC_MAX .....               | 71 |

| Table 64  | ADC_AVG .....               | 71 |

| Table 65  | ADC_AVG_TRMD_PKT_RSSI ..... | 71 |

| Table 66  | IRQ0 .....                  | 72 |

| Table 67  | IRQ1 .....                  | 72 |

| Table 68  | IRQ2 .....                  | 73 |

| Table 69  | TRIM_CMD .....              | 74 |

| Table 70  | LNA_PEAK_ADC .....          | 74 |

| Table 71  | ANT_PEAK_ADC .....          | 74 |

| Table 72  | VCO_FRQ_RX_TRIM .....       | 75 |

| Table 73  | VCO_FRQ_TXPAOFF_TRIM .....  | 75 |

| Table 74  | VCO_FRQ_TXPAON_TRIM .....   | 76 |

| Table 75  | VCO_FRQ_TRIM .....          | 76 |

| Table 76  | VCO_FRQ_BAND_TRIM .....     | 77 |

| Table 77  | MOD_DAC_TRIM .....          | 77 |

| Table 78  | FSK_DEV_TRIM_TARGET .....   | 77 |

| Table 79  | RCOSC_FREQ_TRIM .....       | 77 |

| Table 80  | LNA_FRQ_TRIM .....          | 78 |

| Table 81  | LNA_BIAS_TRIM .....         | 78 |

| Table 82  | IREF_TRIM .....             | 78 |

| Table 83  | XO_TRIM .....               | 79 |

| Table 84  | GAÜS_TRIM .....             | 79 |

| Table 85  | VCO_AMP_TRIM .....          | 79 |

| Table 86  | ANT_TRIM .....              | 79 |

| Table 87  | RX_PKDET_TRIM .....         | 80 |

| Table 88  | DC_CNTR_TRIM .....          | 80 |

| Table 89  | IRQ_EN0 .....               | 80 |

| Table 90  | IRQ_EN1 .....               | 80 |

| Table 91  | IRQ_EN2 .....               | 81 |

| Table 92  | PAD_EN0 .....               | 81 |

| Table 93  | TX_CTRL0 .....              | 82 |

| Table 94  | TX_CTRL1 .....              | 82 |

| Table 95  | TX_CTRL2 .....              | 83 |

| Table 96  | TX_BUF_LEN .....            | 84 |

| Table 97  | TX_FRM_CTRL .....           | 85 |

| Table 98  | TX_FRM_SEQ_NO .....         | 85 |

| Table 99  | RX_CTRL0 .....              | 86 |

| Table 100 | RX_CTRL1 .....              | 86 |

| Table 101 | RX_CTRL2 .....              | 87 |

| Table 102 | ADDR_MASK .....             | 88 |

| Table 103 | RX_FRM_LEN .....            | 88 |

| Table 104 | RX_HDR_THRESH .....         | 89 |

| Table 105 | NETWORK_ID .....            | 89 |

| Table 106 | DEVICE_SID .....            | 89 |

| Table 107 | OTHER_SID .....             | 89 |

| Table 108 | DEVICE_LID .....            | 90 |

| Table 109 | OTHER_LID .....             | 90 |

| Table 110 | MAC_CTRL .....              | 90 |

| Table 111 | CRC_POLY .....              | 91 |

| Table 112 | SPI_CTRL .....              | 91 |

| Table 113 | CSMA_CTRL .....             | 92 |

| Table 114 | CSMA_TIME .....             | 92 |

|           |                              |     |

|-----------|------------------------------|-----|

| Table 115 | CSMA_MAX RAND_BACKOFF .....  | 92  |

| Table 116 | CSMA_RETRY_MIN_BACKOFF ..... | 93  |

| Table 117 | SYNC_THRESH .....            | 93  |

| Table 118 | TX_TRIG_CNT .....            | 93  |

| Table 119 | GPIO_0_SEL .....             | 94  |

| Table 120 | GPIO_1_SEL .....             | 94  |

| Table 121 | GPIO_2_SEL .....             | 94  |

| Table 122 | GPIO_3_SEL .....             | 94  |

| Table 123 | SYNC_PTRN .....              | 94  |

| Table 124 | PLL_START_DLY .....          | 95  |

| Table 125 | ACK_TIME_LIMIT .....         | 95  |

| Table 126 | PKT_TIME_LIMIT .....         | 95  |

| Table 127 | RX_FRM_SEQ_NO .....          | 96  |

| Table 128 | TX_PKT_CNT .....             | 96  |

| Table 129 | TX_PKT_RETRY_CNT .....       | 96  |

| Table 130 | TX_PKT_DROP_CNT .....        | 96  |

| Table 131 | RX_PKT_CNT .....             | 97  |

| Table 132 | RX_ALL_PKT_CNT .....         | 97  |

| Table 133 | RX_PKT_DROP_CNT .....        | 97  |

| Table 134 | RX_SYNC_ERR_CNT .....        | 97  |

| Table 135 | RX_ALL_ERR_CNT .....         | 98  |

| Table 136 | CSMA_RETRY_CNT .....         | 98  |

| Table 137 | CSMA_FAIL_CNT .....          | 98  |

| Table 138 | PHY_RX_MODE_SEL .....        | 98  |

| Table 139 | DPORT_CTRL .....             | 99  |

| Table 140 | PHY_TX_RAW_MODE_CTRL .....   | 99  |

| Table 141 | RATE_CTRL .....              | 99  |

| Table 142 | SYNTH_M_DIV .....            | 100 |

| Table 143 | SYNTH_A_DIV .....            | 100 |

| Table 144 | ADC_MUX_IN_SEL .....         | 101 |

| Table 145 | ADC_POW_N_CONV .....         | 102 |

| Table 146 | ADC_CSMA_THRESH .....        | 103 |

| Table 147 | LNA_GAIN .....               | 103 |

| Table 148 | PA_PWR_LEVEL .....           | 103 |

| Table 149 | VCO_BUF_BIAS .....           | 104 |

| Table 150 | VCO_CTRL .....               | 104 |

# 1 Revision History

---

The revision history describes the changes that were implemented in the ZL70550 Programmer User's Guide (153552). The changes are listed by revision, starting with the most current publication.

## 1.1 Initial Release History

Revision 1, dated July 2016, was the first publication of this document.

## 2 Overview

---

### 2.1 Introduction

The ZL70550 Programmer User's Guide contains a comprehensive list of typical and required programming procedures for the various modes of operation and required calibrations of the ZL70550 Ultra-Low-Power Sub-GHz RF Transceiver. Complementing these procedures is a complete memory map defining all of the application registers, with detailed descriptions of their bit definitions including reset values and register access types.

For programming examples, example source code written in C is available to all users who complete a Source Code License Agreement (SCLA) with Microsemi. This source code provides examples of many of the procedures in this user's guide and therefore significantly reduces the development time for users. This source code runs on the ZL70550 Application Development Kit (ADK) boards, which is also available and recommended for users. The ZL70550 ADK provides users with a platform to observe the behavior of the procedures in a lab environment. The ZL70550 ADK also provides an example circuit, allowing users to evaluate the RF performance of the device.

### 2.2 Product Description

Microsemi's ZL70550 RF transceiver is a low-power sub-GHz ISM-band radio designed for wireless-sensor applications that use either continuous monitoring or low-duty-cycle monitoring. The ZL70550 device operates in unlicensed frequency bands between 779 MHz and 965 MHz and offers a maximum data rate of 200 kbit/s to support voice communication. For data communication, the ZL70550 supports extremely low power consumption in packet-based networks. The device includes the RF transceiver as well as a Media Access Controller (MAC) that performs most link support functions.

The ZL70550 system uses the same device at both ends of the communication link.

All control and packet transfers occur across the SPI interface. Setup and control information is accessed with SPI interface operations to either volatile or always-on memory-mapped registers. Packet data is also transferred with block read/write operations.

After the device is set up and necessary information is written to the registers, packet operations can be performed. Packets are written to the transmit buffer across the SPI interface, with or without packet headers. If written without headers, then the headers are automatically added to the packets, depending on the packet format. Likewise, packets can be read from the receive buffer, with or without packet headers. The packet headers are decoded by the device as necessary per the packet format.

Operations can be performed as single-packet operations or, alternatively, the device can perform intelligent packet sequence transactions. With packet transactions, automatic packet acknowledgments are transmitted and received, and if the acknowledgment is not received, automatic retransmissions are attempted.

Completion of packet operations is signaled by various interrupts, depending on the operation being performed, at which point the host processor is notified of the result of the operation.

The device is intended to operate primarily in CSMA mode, but can also support TDMA operation. In CSMA mode, the node initiates all packet transfers starting with a CSMA-CA operation to detect whether the channel is clear. It then transmits that packet and typically waits for an acknowledgment packet. If the acknowledgment fails, then the node may attempt a retransmission after a random back-off period and another CSMA-CA operation to detect whether the channel is clear.

The hub typically waits in receive mode for a packet. Once a packet is received, it transmits a response. In Z-Star packet mode, the hub may also immediately send another nonacknowledgment packet following the acknowledgment packet by signaling in the acknowledgment packet that it will be doing so.

Typically in CSMA operation, the hub does not initiate packet transfers and must wait for the node to send a packet. For nodes that do not periodically transmit data, they must periodically send data-request packets to see if the hub has a packet for them.

## 3 Architecture

## 3.1 Block Diagram

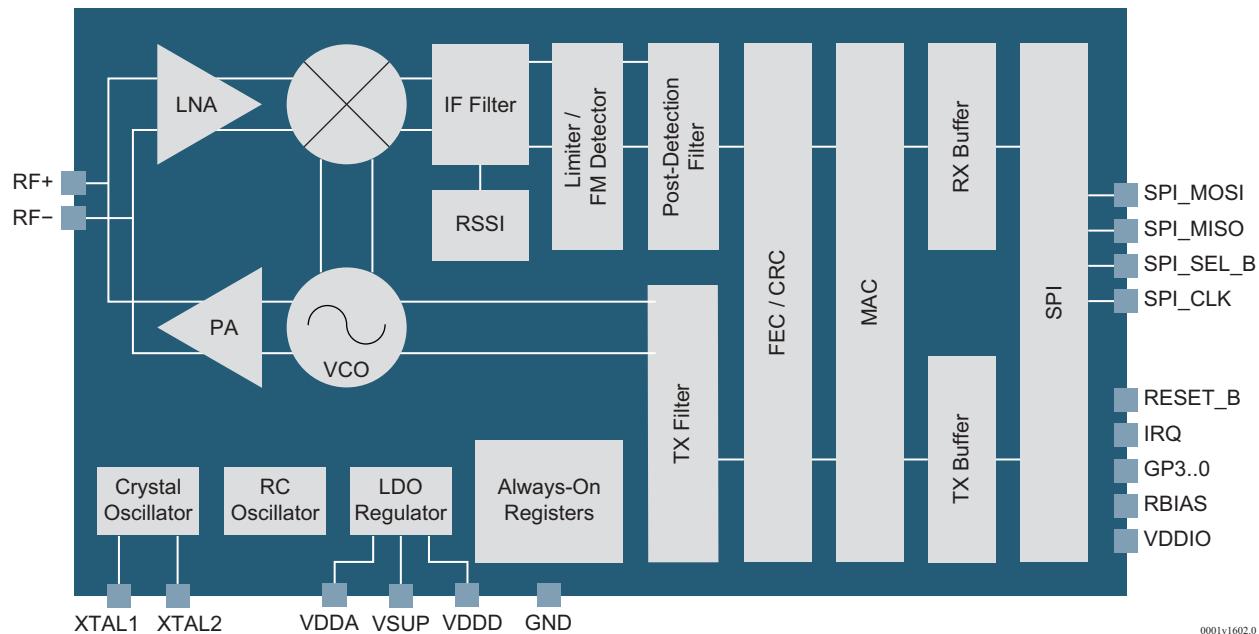

The ZL70550 block diagram is shown in [Figure 1](#), page 3. All control and data is transferred across the SPI slave interface. The 2,048-byte internal address space includes status and control registers plus a 1,024-byte packet buffer.

**Figure 1 • ZL70550 Block Diagram**

## 3.2 System Clock

The system clock is derived from the crystal oscillator (XTAL) clock, running at 24 MHz and giving the frequencies shown in [Table 1](#), page 3.

**Table 1 • Default Frequencies**

|                           |                                       |

|---------------------------|---------------------------------------|

| Crystal                   | 24.0 MHz                              |

| Internal system clock     | 1.20 MHz                              |

| PLL clock channel spacing | 300 kHz                               |

| IF frequency              | 600 kHz                               |

| Supported bit rates       | 200 kbit/s, 100 kbit/s, and 50 kbit/s |

# 4 Communication Protocol

## 4.1 Packet Definition

The packet format provides a high effective data rate with excellent error detection and error correction capability. As shown in [Table 2](#), page 4, depending on the packet mode selected by the user, the format of a complete packet may contain:

- Packet preamble

- Frame sync

- PHY header (Z-Star packet mode and user packet mode only)

- MAC header (Z-Star packet mode only)

- User data blocks

- Frame Check Sequence (FCS) or CRC

This packet format is used in both directions, from hub to node and from node to hub. For maximum data throughput, the packet preamble and header are both as small as possible, while allowing up to 511 bytes of user data within a packet.

Sections [4.1.1.1 Z-Star Packet Mode](#), page 5, through [4.1.1.3 Raw Packet Mode Format](#), page 6, show the structure of the complete packet: the preamble, the header, a typical data block, and CRC. The time sequence runs from left to right, so the preamble is first and CRC is last.

### 4.1.1 Packet Modes Overview

All packet transfers occur to and from the internal packet buffer across the system bus between the SPI interface and the MAC. Typically, 512 bytes are allocated to the transmit buffer, and 512 bytes to the receive buffer. Packet sizes are typically limited to 511 bytes.

The packet mode is selected using *tx\_mode* in the **TX\_CTRL0** register for TX and using *rx\_mode* in the **RX\_CTRL0** register for RX. The various packet modes provide different features, as shown in [Table 2](#), page 4.

**Table 2 • Packet Modes of Operation**

| Mode               | Description                                                         | Frame Sync | FEC | PHY Header | Auto-Length | MAC Header | CRC |

|--------------------|---------------------------------------------------------------------|------------|-----|------------|-------------|------------|-----|

| Raw bit mode       | Optional serial clock and data (TX/RX buffer or <b>GP3..0</b> pins) | No         | No  | No         | No          | No         | No  |

| Raw packet mode    | Compatible with ZL70251 MAC with optional FEC and CRC               | Yes        | Opt | No         | No          | No         | Opt |

| User packet mode   | User-defined packet (no MAC header)                                 | Yes        | Opt | Yes        | Yes         | No         | Opt |

| Z-Star packet mode | Fully functional MAC based on Microsemi's Z-Star protocol           | Yes        | Opt | Yes        | Yes         | Yes        | Yes |

There are restrictions on CRC availability in raw packet mode, since there is no length information in the packet. Either fixed length packets must be used, or length information must be extracted dynamically during packet reception to set the length.

#### 4.1.1.1 Z-Star Packet Mode

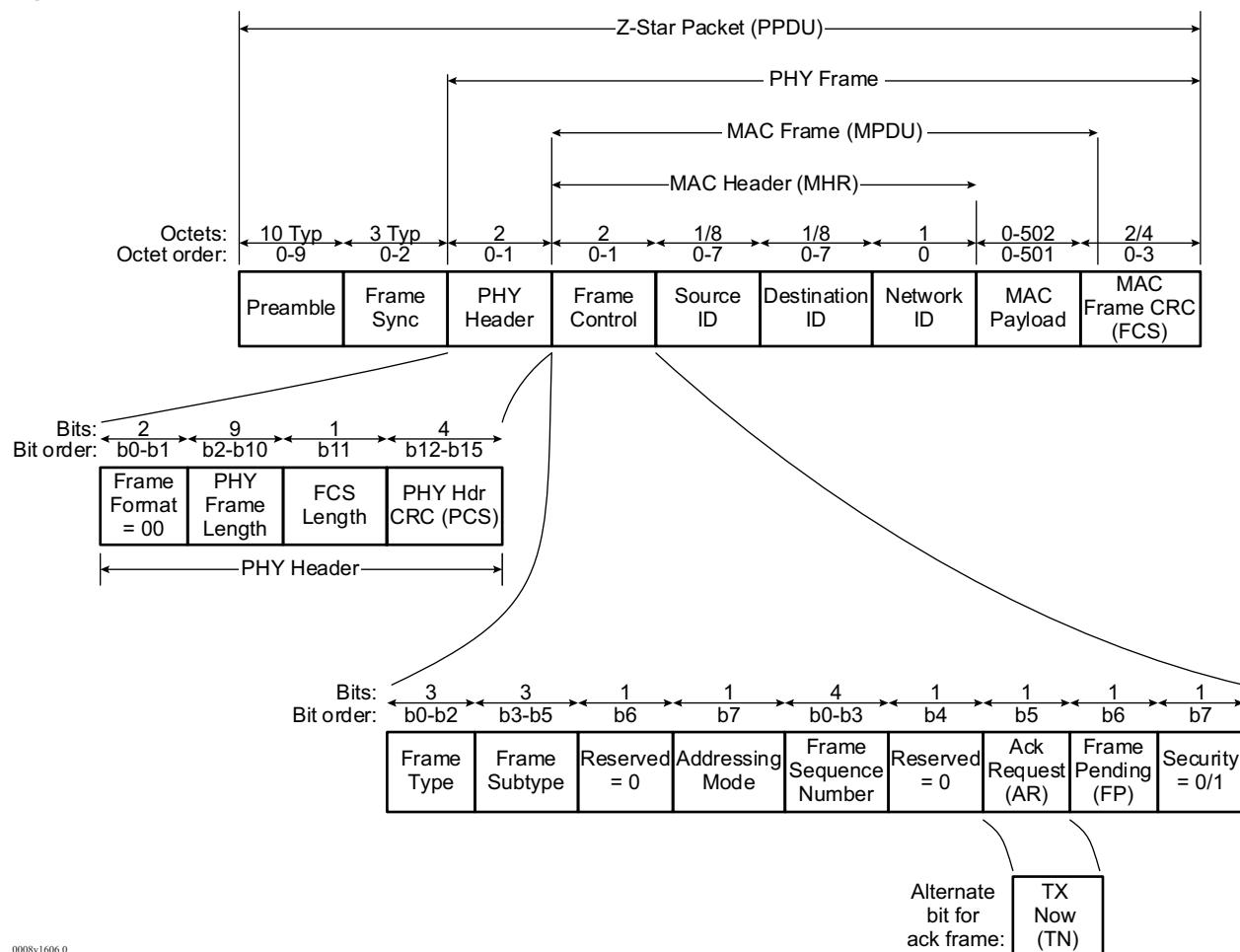

The function of the transmitter is to build the packet PHY frame, as shown in [Figure 2](#), page 5. The recommended preamble length is 10 bytes, and the frame synchronization pattern is programmable from 2 to 5 bytes. The Z-Star packet is composed of six distinct sections for the Z-Star frame:

- Preamble

- Frame synchronization pattern

- PHY header

- MAC header

- Payload

- Frame Check Sequence (FCS) or CRC

The generated PHY frame is optionally hamming encoded and serialized in the MAC for final packet generation and transmission.

**Figure 2 • Packet Format, Z-Star Packet Mode**

#### 4.1.1.2 User Packet Mode

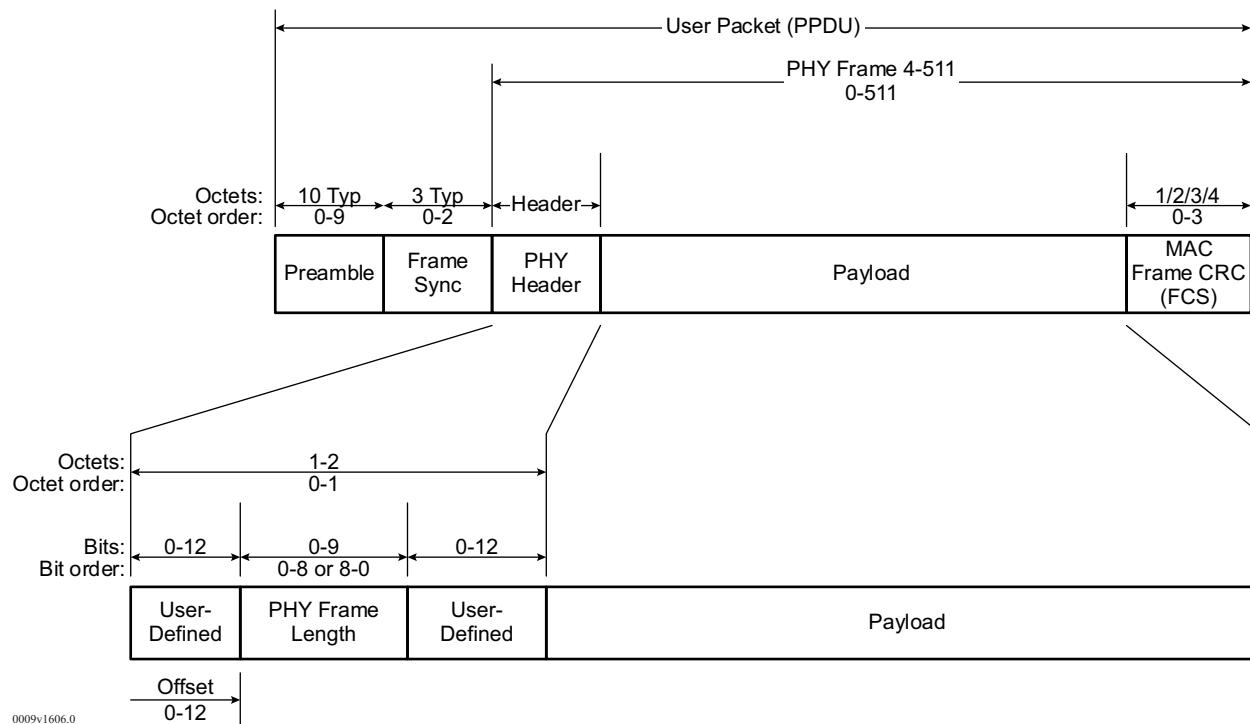

In the user packet mode, the frame is composed of the PHY header, payload, and FCS as shown in [Figure 3](#), page 6. There is no MAC header. The FCS is variable, set by `rx_fcs_len` for receive and `tx_fcs_len` for transmit. If the setting is zero, then there is no FCS. The correct FCS polynomial must be set in `crc_poly`. Both values must be the same for both devices in any one direction, but can be different for the different directions.

The recommended preamble length is 10 bytes, and the frame synchronization pattern is programmable from 2 to 5 bytes.

For transmit, the length is generated automatically by the SPI packet write command if *tx\_auto\_hdr* is set to 1; in user packet mode, this limits the PHY header to one byte and therefore limits frame length to 255 bytes. Alternatively, if *tx\_auto\_hdr* is set to 0, a two-byte PHY header is an option and the length is determined by *tx\_buf\_len*, so the maximum packet size is 511 bytes. In the latter case, the user must write the entire packet, including the frame length in the PHY header, to the transmit buffer.

The frame length may be placed anywhere in the first two bytes, but the receiver must preprogrammed for the location of the frame length field.

**Figure 3 • Packet Format, User Packet Mode**

#### 4.1.1.3 Raw Packet Mode Format

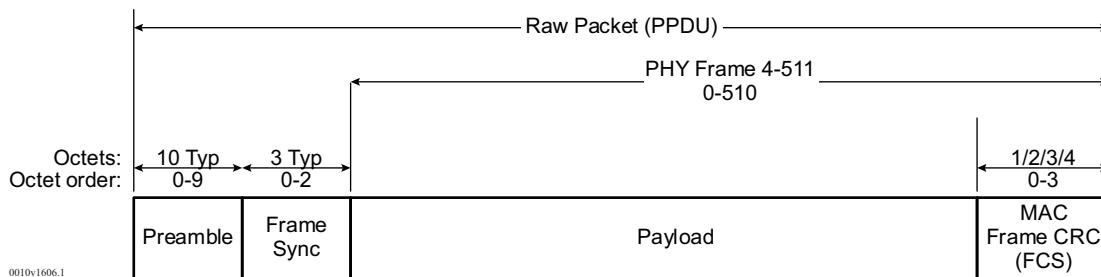

The raw packet mode is similar to the user packet mode, except that there is no PHY header and no frame length in the packet. In raw packet mode, packets are transmitted without a header.

The packet format is shown in [Figure 4](#), page 7. The preamble and frame sync are transmitted, so that received data is byte-aligned before being written to the RX buffer. The operation in raw packet mode is limited to that shown in the state machine operation shown in [Figure 15](#), page 24. Raw packet mode can be used if the packet format does not support the PHY header requirements that exist in user packet mode for the packet length field. In this case, the TX and RX packet length are controlled by *tx\_buf\_len* and *rx\_frm\_len* respectively.

The recommended preamble length is 10 bytes, and the frame synchronization pattern is programmable from 2 to 5 bytes. FEC encoding/decoding is optional. Preamble and frame synchronization length, and FEC selection operate the same as for other modes.

The RX frame length *rx\_frm\_len* may be updated during packet reception, providing this occurs before the end of the packet. The packet may optionally be terminated by a SPI abort command. In all cases, ***rxc\_pkt\_buf\_len[8:0]*** indicates the number of bytes written to the RX buffer (which is either the entire PHY frame length or the payload length; see [Table 10](#), page 27).

The FCS is variable, set by `tx_fcs_len` and `rx_fcs_len`. If the setting is zero, then there is no FCS. The correct FCS polynomial must be set in `crc_poly`. Both values must be the same for both devices in any one direction, but can be different for the different directions.

The CRC is optional and requires using one of two methods for RX packet length.

- A fixed packet length is used, in which case the CRC is always known.

- The host CPU dynamically derives the length from the contents of the beginning of the packet, and writes that value to `rx_frm_len` prior to the end of packet being received. Otherwise, the FCS cannot be calculated correctly.

To facilitate the latter case, a programmable interrupt, `rx_hdr_rdy_irq`, is available to interrupt the host CPU after a predetermined number of packet bytes have been written to the RX buffer. The RX buffer fullness threshold `rx_hdr_thresh` controls the number of bytes written to the RX buffer, at which point `rx_hdr_rdy_irq` is asserted.

**Figure 4 • Packet Format, Raw Packet Mode**

## 4.1.2 Frame Control

### 4.1.2.1 Frame Control for Raw Bit Mode Operation

In raw bit mode, raw bits are transmitted from the transmitter without preamble, frame sync pattern, header, or CRC. If these properties are needed, then they must be encoded in the bit stream.

In raw bit TX mode, the transmitter sends a user defined bit stream. The source of the data can be either the TX buffer or the **GP1** pin. It is recommended that the preamble be included in the data stream, unless manual DC receiver settings can be used.

On the receiver side, the bit stream is input without frame synchronization or byte alignment. The received data is placed in the receive buffer, and can also be output to a general-purpose I/O pin along with an output clock.

In raw bit mode, the receiver does not require a frame sync to receive the RX data. As soon as the receiver is enabled, data is streamed into the RX buffer. All data is streamed to the receive buffer, with no byte alignment and no dewhitening. Optionally, the data could be qualified by preamble detection.

Raw bit mode has two basic applications. First, it can be used for raw bit error testing using the GPIO TX and RX I/O modes. Second, it can be used for applications where the packet framing is not desired, or for data rates not supported by the ZL70550. There are limitations to this second case.

This mode allows for user defined bit rates, particularly if **GP1** is used for input data, because the user can change the bit value at his chosen rate. On the receiver side, the raw RX data bits are available either in the RX buffer or at a general-purpose I/O pin.

To use raw bit mode, refer to the setup and initialization information provided in Section [6.5.2 For Raw Bit Mode](#), page 38.

### 4.1.2.2 Frame Control for Packet Mode Operation

Packet mode is used in Z-Star packet mode, user packet mode, and raw packet mode.

In packet mode, preamble and frame sync is added during transmissions, and expects both preamble and frame sync during receive. For optimum performance of the receiver, the DC level of the receiver must be set, and the preamble is used to automatically set the DC level. The frame sync is needed to

perform byte alignment and synchronize the whitener in the PHY. It is also used in the MAC to locate the beginning of the PHY frame, which is required for FEC decoding, and header decoding, and CRC checking.

## 4.1.3 Frame Processing

### 4.1.3.1 Frame Processing in Z-Star Packet Mode

In Z-Star packet mode, frame processing is performed per [Figure 14](#), page 23. This state machine diagram shows the sequence of packet transfers that can be performed automatically by the device, and follows the transaction sequences defined by the Z-Star protocol.

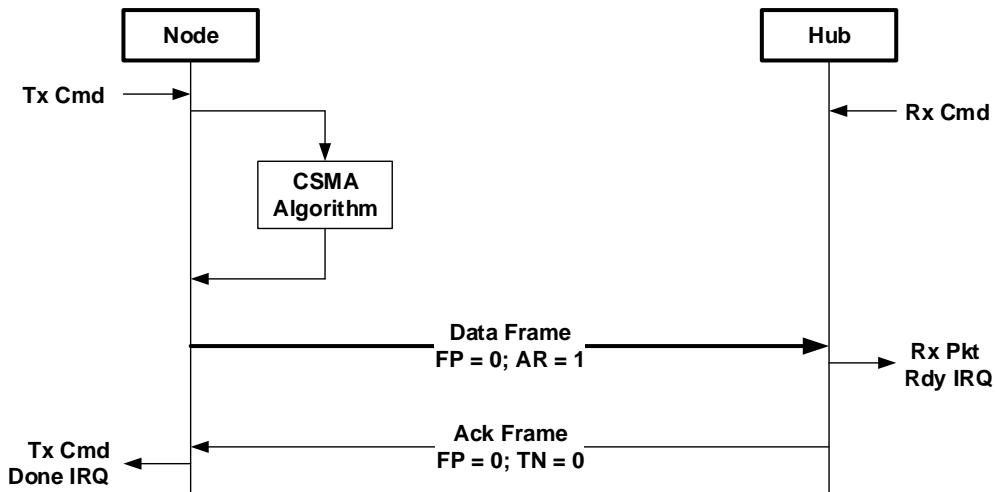

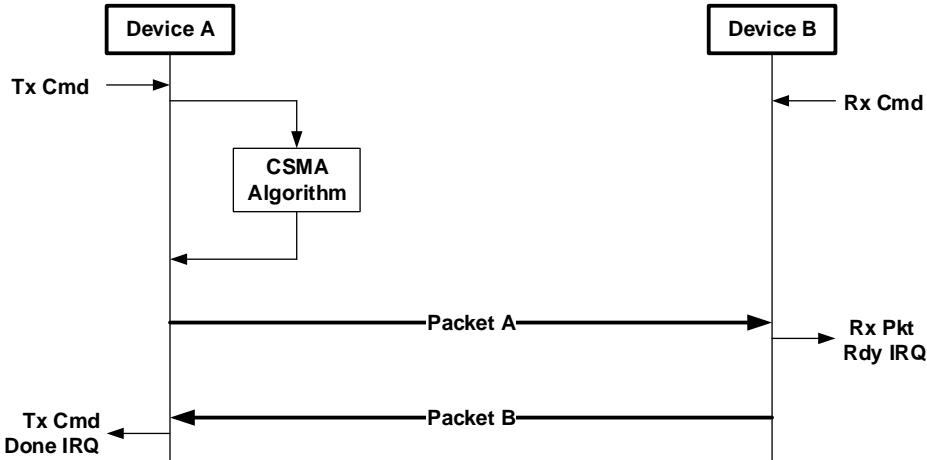

**Figure 5 • Basic Transaction**

[Figure 5](#), page 8, shows the basic packet transaction. Typically the node starts in CSMA1 to listen for a clear channel before proceeding to TX1 to transmit a packet or send a data request. After sending a non-data-request packet, it turns around to RX to receive the acknowledgment packet. The node is interrupted with a *cmd\_done\_irq* when the packet operation is complete.

The hub remains in blind reception receive mode, waiting for a packet from any node in its network. When a packet is received, as indicated by the *rx\_pkt\_rdy\_irq* and the AR bit is set, then the hub sends an acknowledgment packet back to the node. The FP and TN bits are set to 0 in the acknowledgment packet to indicate to the node that the hub has no packets for the node. This completes the packet transaction.

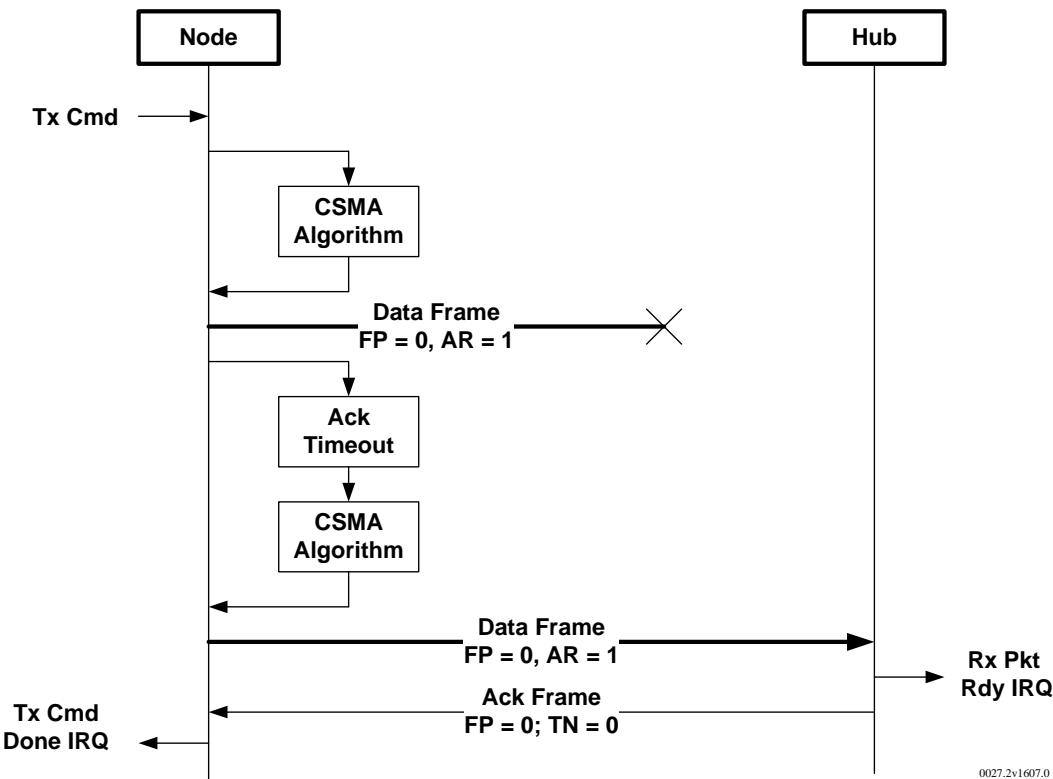

If the packet is not received by the hub, or if the acknowledgment packet is sent and not received by the node, then the node retransmits the same packet, as shown in [Figure 6](#), page 9. This start with a random back-off prior at the beginning of the CSMA operation, followed by the retransmission of the packet.

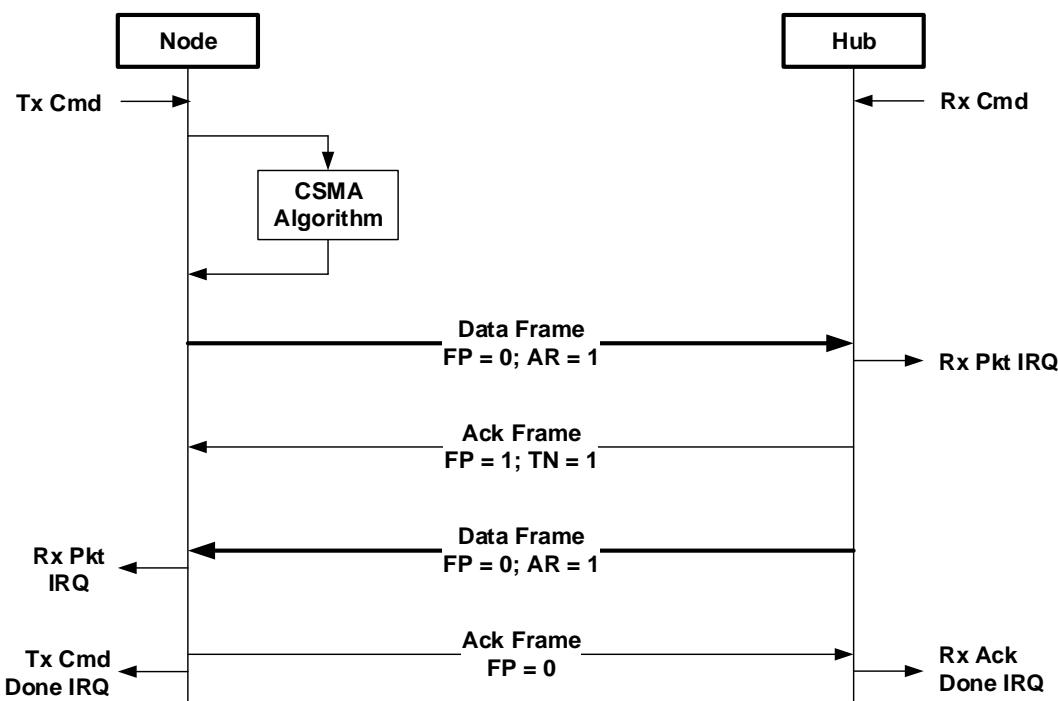

If the hub needs to transmit a packet to the node, it must wait for that node to initiate either a packet transmission, or a data-request packet transmission. The data packet transmission is shown in [Figure 7](#), page 9. When the hub receives a packet, it must check its transmit queue for that node to see if it has a pending packet for that node. If it does, the hub sets FP and TN to 1 in the acknowledge packet, signifying to the node that it will immediately receive another packet.

When this packet is received, the node is notified with the *rx\_pkt\_rdy\_irq*, and if the AR bit is set in the packet header, the node sends the acknowledgment packet back to the hub.

When the hub receives the acknowledgment as signaled by *rx\_ack\_done\_irq*, it can mark that packet as sent and remove it from its transmit queue for that node.

**Figure 6 • Basic Transaction with Retry**

**Figure 7 • Hub to Node Frame Transaction**

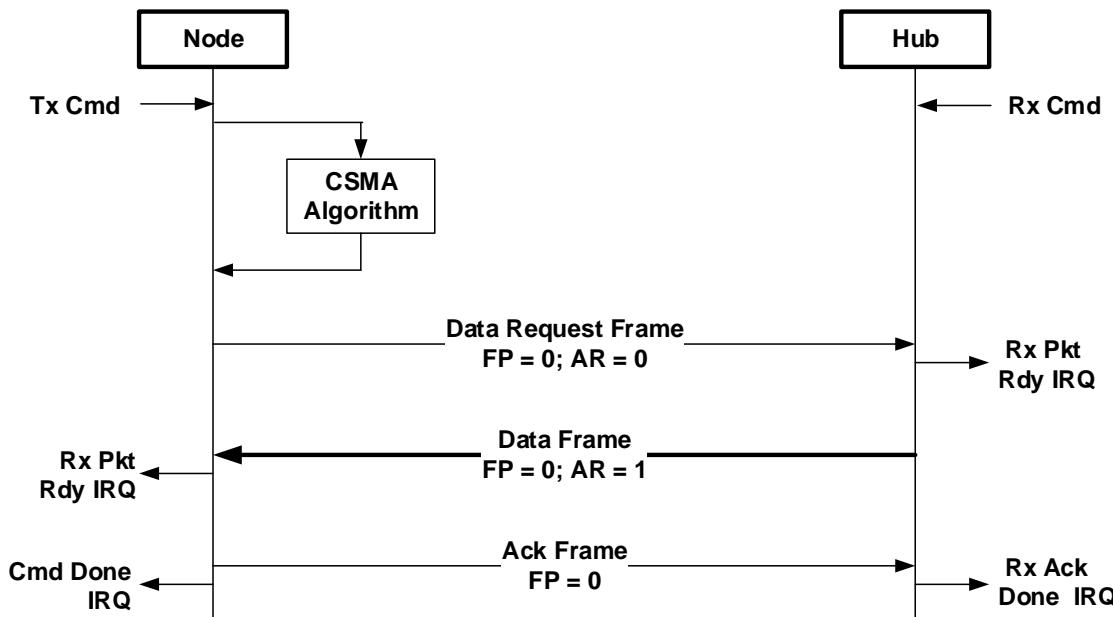

The node should periodically communicate with the hub, so that the hub and node remain connected and so the hub can send packets to the node. If the node does not have periodic data for the hub, then it should periodically send a data-request packet to the hub, as shown in [Figure 8](#), page 10.

The node first checks for a clear channel with CSMA, and then sends a data-request packet. The data-request packet contains the next expected frame sequence number for that node.

When the hub receives the data request, it must check its transmit queue to see if it has a packet for that node. If so, it immediately sends the packet with the expected frame sequence number, typically with the AR bit set to request an acknowledgment packet.

When the node receives the packet, it is interrupted with *rx\_pkt\_rdy\_irq*, and the acknowledgment packet is automatically transmitted back to the hub. When the hub receives the acknowledgment, it clears the packet from its transmit queue for that node.

If the hub does not have a packet for that node, or if the hub has already transmitted the requested sequence number, then it sends a null packet with AR equal to 0. This terminates the transaction on both sides.

**Figure 8 • Data Request Transaction**

#### 4.1.3.1.1 Z-Star FCS Calculation

In Z-Star packet mode, the polynomial is controlled dynamically, depending of the FCS length. The transmitter transmits an FEC length as defined in *tx\_fcs\_len*. If set to 3'b010, then the 16-bit polynomial is used for calculating the FCS. On the receiver, if FCS length is set to 0 in the PHY header, the 16-bit FCS is calculated over the entire MAC frame, not including the PHY header. The 16-bit FCS polynomial is shown in [EQ 4-1](#). The polynomial is entered LSB first, also known as reverse bit order. For 16-bit FCS, the polynomial is 0x00008408.

$$FCS = x^{16} + x^{12} + x^5 + 1 \quad EQ\ 4-1$$

If *tx\_fcs\_len* is set to 3'b100, then the transmitter uses to 32-bit polynomial to generate the 32-bit FCS. On the receiver, if FCS length in the PHY header is set to 1, the 32-bit FCS is calculated over the entire MAC frame, not including the PHY header, and uses the 32-bit FCS polynomial shown in [EQ 4-2](#). For the 32-bit FCS, the polynomial is 0xEDB88320.

$$FCS = x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1 \quad EQ\ 4-2$$

#### 4.1.3.1.2 Z-Star Header Generation

The MAC header may be automatically generated from the always-on registers, or loaded into the transmit buffer, depending on the setting of *tx\_auto\_hdr*. It is set to 1 for auto-header generation. In auto-header generation, the MAC header is generated from the contents of the always-on registers, from the previous received packet, or from default values per packet type. For acknowledgment, data request, and null packets, *tx\_auto\_hdr* is ignored and the headers are automatically generated, where the frame type and frame subtype fields, and other fields, are over-ridden relative to the values in the always-on registers.

[Table 3](#), page 11, shows the typical header field sources for auto-header generation in transmit (where the column headings correspond to the state machine diagram shown in [Figure 14](#), page 23). RX packet means that fields are derived from the current/last RX packet received. Payloads with payload lengths are only used in TX1 and TX2, where the command is not TX data request and when *tx\_null\_frm* is 0.

The contents of the packet may always be completely specified, over-riding the contents of [Table 3](#), page 11, by two methods. One method is to use a SPI TX command (not TX data request) with *tx\_auto\_hdr* equal to 1 and *tx\_null\_frm* equal to 0, and have all settings in the always-on registers. The other method is to use a SPI transmit command with *tx\_auto\_hdr* equal to 0 and *tx\_null\_frm* equal to 0, and place the header in the transmit buffer.

**Table 3 • Auto Header Generation and Checking**

|                     | TX1 Data Pkt        | TX1 Null Pkt        | TX1 Data Request    | TX_ACK2             | TX_ACK1             | TX2                 |

|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| Source address      | Always-on registers |

| Destination address | Always-on registers | Always-on registers | Always-on registers | RX packet           | RX packet           | RX packet           |

| Network address     | Always-on registers | Always-on registers | Always-on registers | RX packet           | RX packet           | RX packet           |

| Address mode        | Always-on registers | Always-on registers | Always-on registers | RX packet           | RX packet           | RX packet           |

| FSN                 | Always-on registers | 0                   | 1 + last RX FSN     | RX packet           | RX packet           | Always-on registers |

| FP                  | Always-on registers | 0                   | 0                   | 0                   | Always-on registers | Always-on registers |

| AR/TN               | Always-on registers | 0                   | 0                   | 0                   | Always-on registers | Always-on registers |

| FCS length          | Always-on registers | 2                   | 2                   | 2                   | 2                   | Always-on registers |

| Frame type          | Always-on registers | Data                | Data request        | Ack                 | Ack                 | Always-on registers |

| Payload length      | Always-on registers | 0                   | 0                   | 0                   | 0                   | Always-on registers |

#### 4.1.3.2 Frame Processing in User Packet Mode

The user packet mode, processing is shown in [Figure 15](#), page 24. As in Z-Star, the network is configured for CSMA operation with the node, Device A, initiating all packet transactions. When Device B receives a packet and is interrupted with *rx\_pkt\_rdy\_irq*, it immediately turns around and starts transmitting the response packet. The host CPU must have the packet loaded into the transmit buffer by the time the frame synchronization pattern is transmitted. After the packet is transmitted from Device B, Device B goes back to receive mode, waiting for another packet.

When Device A receives a good packet, the transaction sequence is complete, and *cmd\_done\_irq* is asserted. This transaction sequence is shown in [Figure 9](#), page 12. If the packet reception fails, then Device A performs a random back-off at the beginning of the CSMA and automatically retransmits the same packet up to the retry count. If no response packet is received, and all retries are exhausted, then the process exits with a *cmd\_done\_irq* interrupt and the *cmd\_fail\_irq* status.

**Figure 9 • Packet Processing in User Packet Mode and Raw Packet Mode**

## 4.1.4 Packet Exchange Timing

There are several registers that control the timing in the ZL70550. This timing relates to the sequence of internal operations required to transmit or receive packets. Microsemi recommends using either the default values or the values listed in [Section 8.2 Address Space](#), page 53, which were tested and chosen for optimal system performance.

### 4.1.4.1 TX Timing Delays (Default Register Settings)

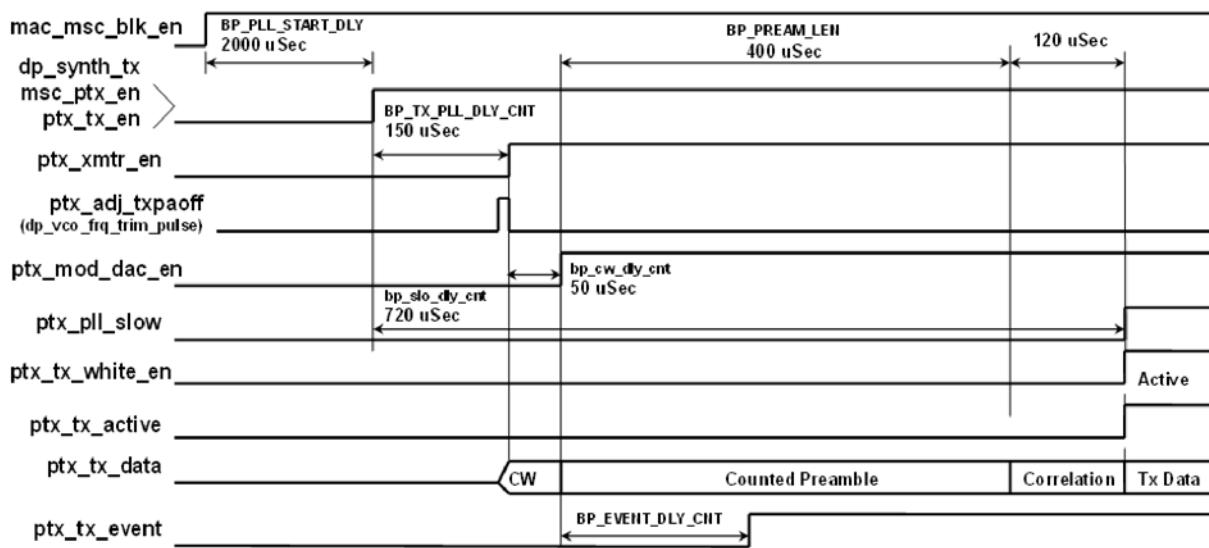

[Figure 10](#), page 12, shows the default TX start-up timing, using the default register settings. The *pll\_start\_dly* controls the setting time of the PLL start-up from when it is enabled. This typically occurs when *msc\_blk\_en* is high after wake-up. The CSMA, transmit, and receive operations cannot start until this delay is complete. It only occurs once during the start-up of the device after power-on. For other TX/RX start-up conditions, it is bypassed.

**Figure 10 • Default TX Start-Up Timing**

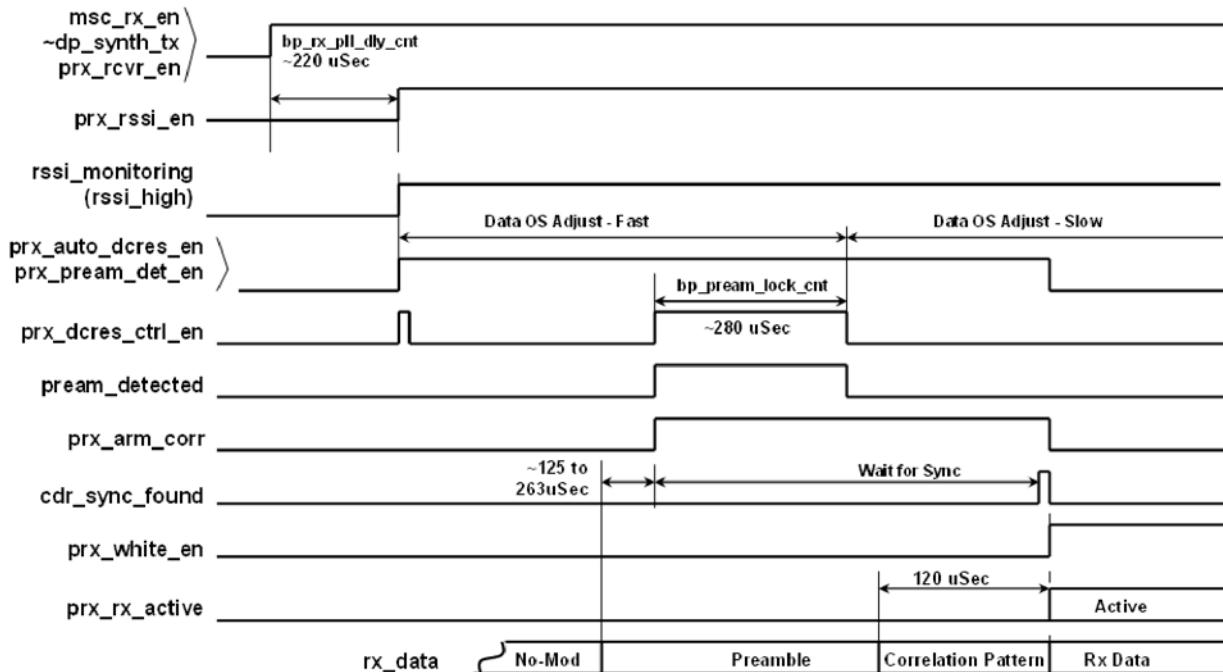

#### 4.1.4.2 RX Timing Delays (Default Register Settings)

Figure 11, page 13, shows the timing for the typical RX startup using the default settings. The timing assumes that the PLL start-up delay is already complete, and that a transmit operation has recently completed. The **RX\_PLL\_DLY\_CNT** is the settling time allowed for changing from the channel center frequency to the IF RX frequency. This delay is bypassed on device startup and if more than 300 $\mu$ s has elapsed since the last TX. However, it is always present on the TX to RX turnaround.

Depending on the mode, there is a delay from when the RSSI-ADC block is turned on and when the RSSI is level is detected high. Because **ADC\_RSSI\_THRESH** is greater than zero (see recommended initialization value in Table 35, page 53), then the RSSI must be above the threshold before the receive process continues. If **ADC\_RSSI\_THRESH** is zero (not recommended), then the receive process commences immediately by either enabling the DC restore block, or enabling the preamble detector block, depending on the setting of *pream\_det\_mode*.

In preamble detect mode (default mode), the preamble detector detects the arrival of the preamble. At that time, it turns on the DC restore block. Once the frame synchronization pattern is detected, the receiver informs the MAC that the packet data is now valid.

**Figure 11 • Default RX Start-Up Timing**

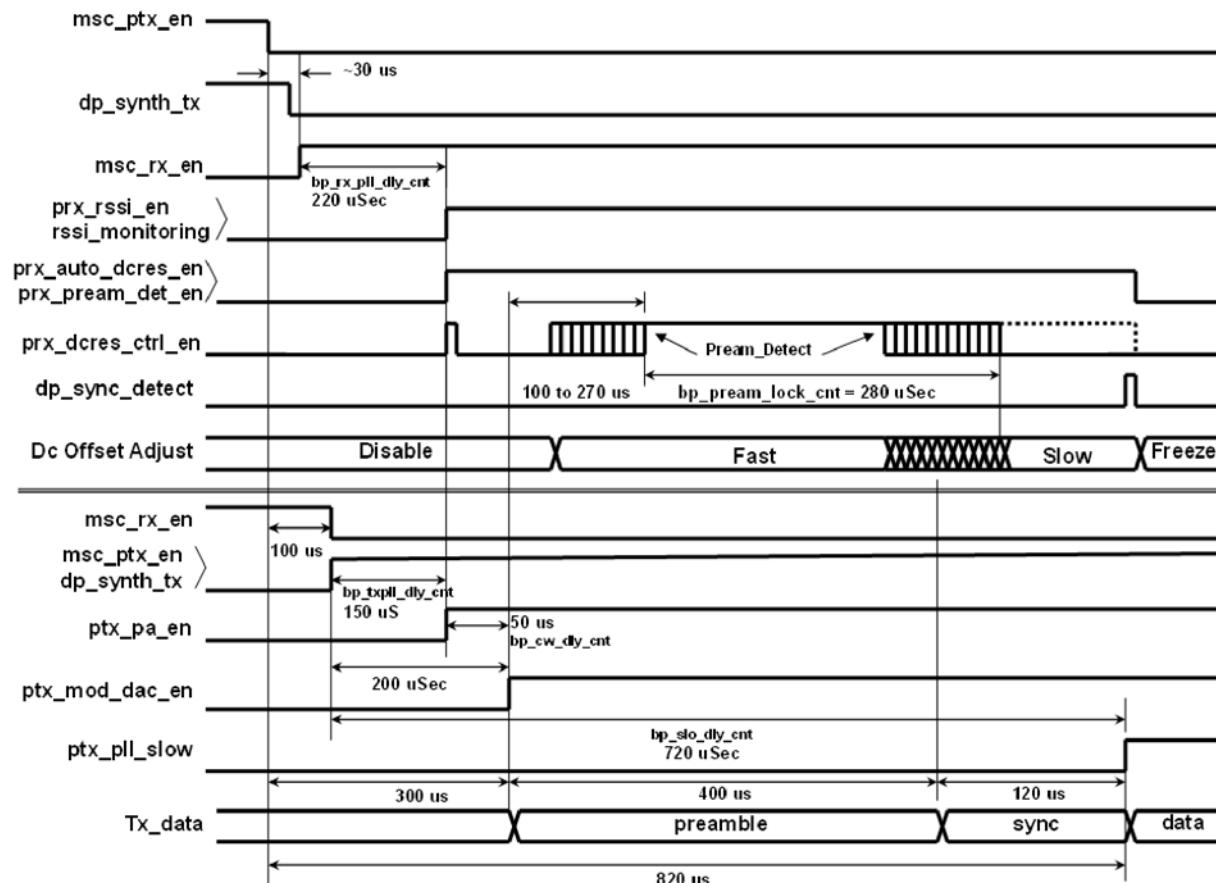

#### 4.1.4.3 Optimized TX to RX Turnaround Timing with Preamble Detection

Figure 12, page 14, shows the TX to RX turnaround timing using preamble detect mode. The top section shows the device going from TX to RX, and the bottom portion shows the device going from RX to TX.

**Figure 12 • Optimized Turnaround in Preamble Detect Mode**

## 4.1.5 Packet Operations

### 4.1.5.1 Z-Star Node Operation, Transmit Transaction Sequence Mode

The node is typically set up to perform a single packet transmit transaction, starting with a CSMA operation. All the node MPU needs to do is write the payload into the node's transmit buffer using a SPI packet write command, and then wait for the *cmd\_done\_irq* interrupt. While waiting, the MPU can be put in the sleep state.

When the interrupt is received, the node MPU needs to check for any errors. If a PLL lock error is present, then a VCO trim is required. Note that *cmd\_done\_irq* may not be the first interrupt to be asserted on a packet transaction when other interrupts are enabled. In particular, *rx\_pkt\_rdy\_irq* and *rx\_frm\_pend\_irq* can occur, if enabled, after the packet is transmitted and before the *cmd\_done\_irq* in both TX Packet and TX Data Request operations. In this case, the user needs to understand the associated timing and decide whether *rx\_pkt\_rdy\_irq* and *rx\_frm\_pend\_irq* should be enabled as interrupts or just used as status. In general, *cmd\_done\_irq* is the last interrupt to be asserted in a packet transaction, and the other interrupt/status can wait for *cmd\_done\_irq*.

If the *rx\_pkt\_rdy\_irq* status/interrupt is received, then there is a packet in the RX buffer from the hub that needs to be read using a packet read operation. The length of the packet is in the SPI status when the interrupt is read.

If *cmd\_fail\_irq* and *rx\_frm\_pend\_irq* status are both set, then the hub attempted to send the node a packet, and the packet was not received. In this case, the node MPU should send a SPI data request command to give the hub another opportunity to send the packet.

If *cmd\_fail\_irq* and *msc\_rx\_ack\_fail* status are both set, then the node did not receive an acknowledgment for the transmitted packet from the hub after the programmed number of retries or because CSMA failed.

- The first option is to re-try the packet transmission.

- Next is to use a mode that gives more sensitivity with lower data rate and/or enabling FEC. In this case, it is necessary to have both devices setup in adaptive mode, with the hub in Follow receiver mode.

- If there is no response from the hub, then search for the hub on another channel using a SPI data request command.

#### 4.1.5.1.1 Transmit Transaction Sequence

A packet transmission sequence is initiated as follows, after initialization and register setup as defined in [Section 6 Setup and Initialization](#), page 35, for the node. It is assumed that the node has been put in a sleep state, where the main section of the chip is powered down. See [Table 14](#), page 35.

1. Perform dummy read by performing a SPI read of address 0x000 (if the device is in sleep mode). This takes the device out of the SLEEP state and puts it in STANDBY.

- Put MPU into sleep mode and wait for SPI ready interrupt on **IRQ** pin

2. Write payload to TX buffer using a SPI packet write command:

- Put MPU into sleep mode and wait for interrupt on **IRQ** pin

- After the interrupt, read registers **IRQ0**, **IRQ1**, and **IRQ2** in a single three-byte SPI read operation

3. If *cmd\_done\_irq* is received and *rx\_frm\_pend\_irq* status is 1:

- Write SPI data request command

- Put MPU into sleep mode and wait for interrupt on **IRQ** pin

- After the interrupt, read registers **IRQ0**, **IRQ1**, and **IRQ2** in a single three-byte SPI read operation

- If *cmd\_done\_irq* is received and *rx\_pkt\_rdy\_irq* status is 1, then go to Step 6

- Else If *cmd\_done\_irq* is received and *msc\_rx\_null\_data\_frm*, then the command is complete; put the device into the SLEEP state via the SPI interface by writing 0xDE to **SPIR\_PWRDWN\_REQ**

- Else If *cmd\_done\_irq* is received and *cmd\_fail\_irq* status is 1, go to Step 5

**Note:** If *rx\_frm\_pend\_irq\_en* is equal to 1, then this interrupt is asserted, and may occur prior to *cmd\_done\_irq*. Typically it is preferred to set *rx\_frm\_pend\_irq\_en* equal to 0 and to use *rx\_frm\_pend\_irq* as status only.

4. Else If *cmd\_done\_irq* is received and *cmd\_fail\_irq* status is 0:

- Mark TX packet as transmitted and remove it from TX queue.

- Command is complete; put the device into the SLEEP state via the SPI interface by writing 0xDE to **SPIR\_PWRDWN\_REQ**

5. Else If *cmd\_done\_irq* is received and *cmd\_fail\_irq* status is 1:

- Read MAC and receiver status and process error accordingly.

- Command is complete; put the device into the SLEEP state via the SPI interface by writing 0xDE to **SPIR\_PWRDWN\_REQ**

6. Else If *cmd\_done\_irq* is received and *rx\_pkt\_rdy\_irq* status is 1:

- Save **rx\_pkt\_buf\_len[8:0]** from previous SPI interrupt status read (see [Table 10](#), page 27)

- Read packet using SPI packet read command

- Perform any processing required by the received packet

- Mark TX packet as transmitted and remove it from TX queue

- Command is complete; put the device into the SLEEP state via the SPI interface by writing 0xDE to **SPIR\_PWRDWN\_REQ**

7. Else wait for MPU timeout. In this case, the TX packet was successful and acknowledged, and the hub successfully transmitted a packet back to the node.

**Note:** If *rx\_pkt\_rdy\_irq\_en* is equal to 1, then this interrupt is asserted, and may occur prior to *cmd\_done\_irq*. Typically it is preferred to set *rx\_pkt\_rdy\_irq\_en* equal to 0 and to use *rx\_pkt\_rdy\_irq* as status only.

#### 4.1.5.1.2 Transmit Data Request Transaction Sequence

1. Perform dummy read by performing a SPI read of address 0x000 (if the device is in sleep mode)

- Put MPU into sleep mode and wait for SPI ready interrupt on **IRQ** pin

2. After the interrupt, write SPI data request command.

- Put MPU into sleep mode and wait for interrupt on **IRQ** pin

- After the interrupt, read registers **IRQ0**, **IRQ1**, and **IRQ2** in a single three-byte SPI read operation

3. If *cmd\_done\_irq* is received and *rx\_pkt\_rdy\_irq* status is 1, then:

- Save *rx\_pkt\_buf\_len[8:0]* from previous SPI interrupt status read (see [Table 10](#), page 27).

- Read packet using SPI packet read command

- Perform any processing required by the received packet

- Command is complete; put the device into the SLEEP state via the SPI interface by writing 0xDE to **SPIR\_PWRDWN\_REQ**

4. Else If *cmd\_done\_irq* is received and *msc\_rx\_null\_data\_frm* status is 1:

- Command is complete; put the device into the SLEEP state via the SPI interface by writing 0xDE to **SPIR\_PWRDWN\_REQ**

5. Else If *cmd\_done\_irq* is received and *cmd\_fail\_irq* status is 1:

- Read status and process error accordingly.

- Command is complete; put the device into the SLEEP state via the SPI interface by writing 0xDE to **SPIR\_PWRDWN\_REQ**

6. Else wait for MPU timeout.

#### 4.1.5.2 Z-Star Hub Operation, Receive Transaction Sequence Mode

The hub is typically set up to perform continuous receive operations. It only needs one SPI receive command to start it receiving packets. It waits for an *rx\_pkt\_rdy\_irq* interrupt, and then reads the packet with a SPI packet read command. The acknowledgment packet is automatically sent to the node when a good packet is received.

When the hub receives a packet from the node, it should check its transmit queue for any pending packets to be sent to that node. If it has a packet for the node, and the packet received from the node was a non-data-request packet, then the hub MPU must set the *tx\_pkt\_frm\_pend* and *tx\_tn* bits to 1 for transmission in the acknowledgment packet, and then immediately write the packet into the transmit buffer with a packet write command.

This is a time critical operation. Both *tx\_pkt\_frm\_pend* and *tx\_tn* must be set before the acknowledgment packet header is transmitted, and the packet must be written to the TX buffer before the packet header for transmitted packet is written on this back-to-back TX-TX operation.

If a data request packet is received, then the hub only needs to write the packet to the TX buffer. No acknowledgment packet is sent. Once again, the packet must be in the buffer prior to the header being transmitted. This is because the length is contained in the header. If there is not enough time to write the entire packet, then the length must be written first to *tx\_buf\_len* and the SPI interface needs to be set to non-auto-length mode by setting *tx\_auto\_len\_en* equal to 0.

When a packet is sent to the node, the hub should monitor for the *rx\_ack\_done\_irq* interrupt and check *msc\_rx\_ack\_fail* status to determine if the packet transmission was completed correctly.

#### 4.1.5.2.1 Receive Transaction Sequence

A packet reception sequence is processed as follows when the packet is a data packet or data request packet. After initialization and register setup as defined in [Section 6 Setup and Initialization](#), page 35, for the hub:

1. Set *rx\_forever* equal to 1 on the hub

2. Write SPI receive command to begin receive process

3. Wait for interrupt on the **IRQ** pin

4. When the **IRQ** pin goes high, read registers **IRQ0**, **IRQ1**, and **IRQ2** in a single three-byte SPI read operation. Save **rx\_pkt\_buf\_len** from the SPI status (see [Table 10](#), page 27).

5. If **rx\_pkt\_rdy\_irq** is received and **msc\_rx\_data\_frm** equals 1:

- Read packet using SPI packet read command

- Perform any processing required by the received packet

- In MPU, check TX queue for a packet for that node.

- If there is a packet in queue for that node, go to Step 8

- Else (that is, if there is no packet for that node), done. Wait for another RX packet; go to Step 3

6. Else If **rx\_pkt\_rdy\_irq** is received and **msc\_rx\_data\_req\_frm** equals 1:

- Check the source ID from the SPI status received during the IRQ status read

- In MPU, check TX queue for a packet for that node

- If there is a packet for that node, go to Step 9

- Else If there is no packet for that node:

- Set **tx\_null\_frm** equal to 1

- Set **tx\_ack\_frm\_pend** equal 0 and **tx tn** equal to 0

- Wait for interrupt on **IRQ** pin

- If **cmd\_done\_irq** is received and **tx\_pkt\_done\_irq** status equals 1:

- Set **tx\_null\_frm** equal to 0

- Else, process error

- Done; wait for another RX packet. go to Step 3

7. Else, process error

8. Set up for immediate packet TX to node after TX of acknowledgment packet:

- Set **tx\_ack\_frm\_pend** equal to 1 and **tx tn** equal to 1

- TX acknowledgment packet is automatically transmitted

9. Transmit packet to node

- Write the packet to TX buffer using SPI packet write command

- Wait for interrupt on **IRQ**

- After the interrupt, read registers **IRQ0**, **IRQ1**, and **IRQ2** in a single three-byte SPI read operation

10. If **cmd\_done\_irq** is received and **rx\_ack\_done\_irq** status is 1:

- In MPU remove packet from TX queue.

- Done; wait for another RX packet; go to Step 3

11. Else, TX packet failed

- Mark TX attempt on TX queue; wait for another TX opportunity to same node

- Done; wait for another RX packet; go to Step 3

12. Exit and wait for another packet; go to Step 3

**Note:** This process assumes that the device is a hub, and **rx\_forever** is set to 1. With this setting, the hub returns to waiting in receive for another packet after each transaction is completed, regardless of whether or not the transaction passed or failed.

## 4.1.6 Adaptive Packet Reception

### 4.1.6.1 Auto Detection of Bit Rate

Auto bit rate detection (where **adapt\_rate\_en** is equal to 1) uses the receiver preamble detector to determine the bit rate. Three preamble detectors operate in parallel, each being set to one of the three rates. Refer to [Table 5](#), page 18. The first to detect preamble determines the rate. Once the rate is selected, the rate controls the prefilter bandwidth, the AFC/DC restore time and bandwidth, and the clock and data recovery rates.

Once the preamble is detected, the corresponding rate is latched as *prx\_rx\_rate*. When *adapt\_rate\_en* is set to 0, *rx\_rate* controls the receiver behavior. When *adapt\_rate\_en* is set to 1, the RX rate is controlled by *prx\_rx\_rate* instead of *rx\_rate* in the PHY RX controller.

#### 4.1.6.2 Auto FEC Detection

When *adapt\_fec\_en* is set to 1, the receiver frame synchronization correlator searches for both inverted and noninverted frame sync patterns. If a normal frame synchronization pattern is found, then the FEC decoder in the receiver are by-passed. If an inverted frame synchronization pattern is found, then the receiver FEC decoder is enabled and used for error correction of the RX data.

The MAC enables FEC on the MAC receiver if an inverted sync was received. If *adapt\_fec\_en* is set to 0, it uses *hmd\_dec\_en* to enable FEC on the MAC receiver.

If *tx\_follow\_rx\_fec* is set to 1, the transmitter responds to a received packet with the same FEC mode (on/off) that it received. The bit *cdr\_inverted\_sync* indicates that the previous frame sync was inverted. When *tx\_follow\_rx\_fec* is set to 1, the transmitter uses the *cdr\_inverted\_sync* bit to determine whether FEC should be enabled and whether the frame synchronization pattern should be inverted.

The polarity of the transmitter frame synchronization pattern and the FEC enable state is shown in [Table 4](#), page 18.

**Table 4 • Settings for TX Frame Sync Polarity and FEC Enable**

|                                |     |     |     |     |     |     |

|--------------------------------|-----|-----|-----|-----|-----|-----|

| <i>adapt_fec_en</i>            | 0   | 0   | 1   | 1   | 1   | 1   |

| <i>tx_follow_rx_fec</i>        | X   | X   | 0   | 0   | 1   | 1   |

| <i>hme_enc_en</i>              | 1   | 0   | 1   | 0   | X   | X   |

| <i>cdr_inverted_sync</i>       | X   | X   | X   | X   | 1   | 0   |

| Frame synchronization polarity | Pos | Pos | Pos | Neg | Pos | Neg |

| FEC enable                     | 1   | 0   | 1   | 0   | 1   | 0   |

#### 4.1.6.3 Transmitted Preamble

The preamble bit pattern is always 00110011, which is expressed in bit periods and not symbols because the transmitter deals only with bits. (For example, the preamble symbol pattern for a bit rate of 100 kbit/s is 00110011 in bits, but it is 0000111100001111 in symbols.)

**Table 5 • TX Preamble Pattern**

| <i>tx_rate</i> | Preamble Pattern In Bits | Bit Rate   |

|----------------|--------------------------|------------|

| 00             | 00110011                 | 200 kbit/s |

| 01             | 00110011                 | 100 kbit/s |

| 10             | 00110011                 | 50 kbit/s  |

#### 4.1.6.4 Transmitted FEC and Frame Sync Pattern

The TX hamming enable is sourced from *hme\_enc\_en* when *tx\_follow\_rx\_fec* is 0, or from the receiver *cdr\_inverted\_sync* if *tx\_follow\_rx\_fec* is 1 to automatically transmit in the same FEC mode as the packet received. In the latter case, enabling FEC causes the frame synchronization pattern to be transmitted inverted. See [Table 6](#), page 19.

**Table 6 • Enable for TX FEC Encoding**

| <i>tx_follow_rx_fec</i> | <i>hme_enc_en</i> | <i>cdr_inverted_sync</i> | <b>FEC Encoding</b> |

|-------------------------|-------------------|--------------------------|---------------------|

| 0                       | 0                 | X                        | OFF                 |

| 0                       | 1                 | X                        | ON                  |

| 1                       | X                 | 0                        | OFF                 |

| 1                       | X                 | 1                        | ON                  |

If *adapt\_rate\_en* is set to 1, then the transmitted frame sync pattern is inverted if FEC is enabled and noninverted if FEC is disabled. If *adapt\_rate\_en* is set to 0, then the transmitted frame sync pattern is never inverted.

#### 4.1.6.5 Receiver FEC Decoding