# Agilex™ 3 FPGAs and SoCs Device Overview

[Online Version](#)

[Send Feedback](#)

817231

2025.04.22

## Contents

---

|                                                                                      |           |

|--------------------------------------------------------------------------------------|-----------|

| <b>1. Overview of the Agilex™ 3 FPGAs and SoCs.....</b>                              | <b>4</b>  |

| 1.1. Key Features and Innovations in Agilex 3 FPGAs and SoCs.....                    | 5         |

| 1.2. Agilex 3 FPGAs and SoCs Block Diagram.....                                      | 6         |

| 1.3. Agilex 3 FPGAs and SoCs Summary of Features.....                                | 7         |

| 1.4. Additional Features for Agilex 3 SoCs.....                                      | 9         |

| <b>2. Agilex 3 FPGAs and SoCs Family Plan.....</b>                                   | <b>11</b> |

| 2.1. Agilex 3 FPGAs and SoCs C-Series.....                                           | 11        |

| 2.2. Agilex 3 FPGAs and SoCs C-Series Package Options.....                           | 13        |

| 2.3. Part Number Decoder.....                                                        | 14        |

| <b>3. Second Generation Hyperflex Core Architecture.....</b>                         | <b>15</b> |

| <b>4. Adaptive Logic Module in Agilex 3 FPGAs and SoCs.....</b>                      | <b>17</b> |

| <b>5. Internal Embedded Memory in Agilex 3 FPGAs and SoCs.....</b>                   | <b>19</b> |

| <b>6. Variable-Precision DSP in Agilex 3 FPGAs and SoCs.....</b>                     | <b>20</b> |

| <b>7. Core Clock Network in Agilex 3 FPGAs and SoCs.....</b>                         | <b>22</b> |

| <b>8. I/O PLLs in Agilex 3 FPGAs and SoCs.....</b>                                   | <b>23</b> |

| <b>9. General Purpose I/Os in Agilex 3 FPGAs and SoCs.....</b>                       | <b>24</b> |

| <b>10. External Memory Interface in Agilex 3 FPGAs and SoCs.....</b>                 | <b>25</b> |

| 10.1. External Memory Interface Performance.....                                     | 26        |

| 10.2. Features of the Hard Memory Controller.....                                    | 26        |

| <b>11. Hard Processor System in Agilex 3 SoCs.....</b>                               | <b>28</b> |

| <b>12. Transceivers in Agilex 3 FPGAs and SoCs.....</b>                              | <b>32</b> |

| 12.1. PMA Features in Agilex 3 FPGA GTS Transceivers.....                            | 33        |

| 12.2. PCS Features in Agilex 3 FPGA GTS Transceivers.....                            | 33        |

| 12.3. GTS Transceiver PLL in Agilex 3 FPGAs and SoCs.....                            | 34        |

| <b>13. MIPI Protocols Support in Agilex 3 FPGAs and SoCs.....</b>                    | <b>35</b> |

| <b>14. Variable Pitch BGA (VPBGA) Package Design of Agilex 3 FPGAs and SoCs.....</b> | <b>37</b> |

| <b>15. Configuration via Protocol Using PCIe for Agilex 3 FPGAs and SoCs.....</b>    | <b>39</b> |

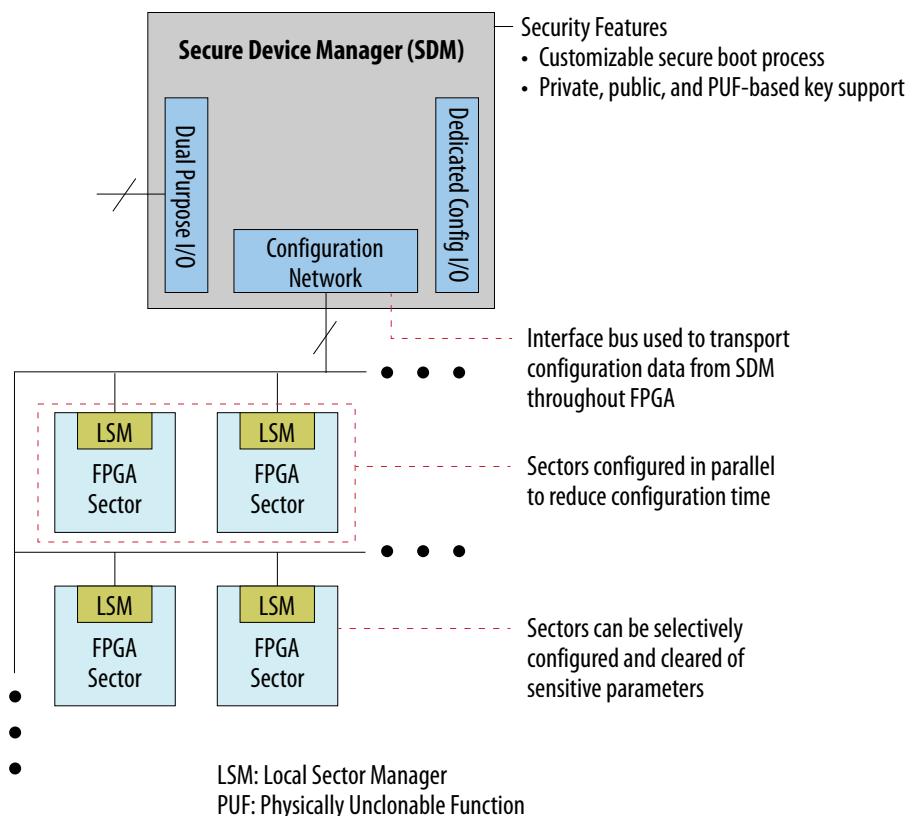

| <b>16. Device Configuration and the SDM in Agilex 3 FPGAs and SoCs.....</b>          | <b>40</b> |

| <b>17. Partial and Dynamic Configuration of Agilex 3 FPGAs and SoCs.....</b>         | <b>42</b> |

| <b>18. Device Security for Agilex 3 FPGAs and SoCs.....</b>                          | <b>43</b> |

| <b>19. SEU Error Detection and Correction in Agilex 3 FPGAs and SoCs .....</b>       | <b>44</b> |

| <b>20. Power Management for Agilex 3 FPGAs and SoCs.....</b>                         | <b>45</b> |

| <b>21. Software and Tools for Agilex 3 FPGAs and SoCs.....</b>                       | <b>46</b> |

**22. Revision History for the Agilex 3 FPGAs and SoCs Device Overview.....47**

## 1. Overview of the Agilex™ 3 FPGAs and SoCs

The Agilex™ 3 FPGA product family extends the innovations of the Agilex FPGA portfolio to low power and cost optimized FPGA applications. The Agilex 3 FPGAs and SoCs serve a broad range of applications that require higher performance, lower power consumption, smaller form factor, and lower logic densities.

- Enhanced DSP with AI Tensor block—delivers high-efficiency artificial intelligence (AI) and digital signal processing (DSP)

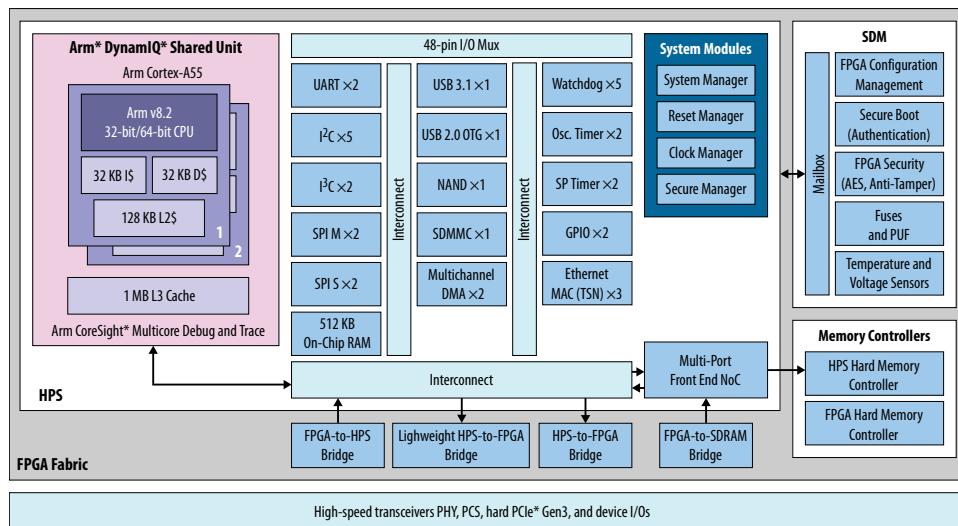

- Dual-core Arm\* Cortex\*-A55 processors enables you to optimize the performance and power efficiency of processing workloads

- Monolithic die architecture—provides higher system integration and lower power with smaller form factor packages

- Advanced connectivity features:

- High-speed GTS transceivers up to 12.5 Gbps

- PCI Express\* (PCIe\*) 3.0 ×4 support

- DDR external memory interface up to 2,133 Mbps LPDDR4

- General purpose I/Os supporting voltages from 1.0 V to 3.3 V

The Agilex 3 FPGA product family delivers on average 1.9x higher fabric performance and up to 38% lower total power consumption compared to previous generation Altera FPGAs. To achieve this improvement, the product family leverages these key innovations and techniques:

- Advanced Intel® 7 technology

- Second generation Hyperflex® FPGA architecture

- High level of system integration

- Fixed low core voltage device

- Power islands, power gating, and other power reduction techniques

The Agilex 3 FPGA product family brings high performance capabilities and features to the cost optimized FPGA application space. The applications span across many segments including video and broadcast equipments, industrial, test and measurement, medical electronics, data centers, and defense.

**Note:** The information contained in this document is preliminary and subject to change.

### Related Information

#### [Agilex 3 FPGA and SoC FPGA on the Intel website](#)

Provides the latest information about Agilex 3 devices.

© Altera Corporation. Altera, the Altera logo, the 'a' logo, and other Altera marks are trademarks of Altera Corporation. Altera and Intel warrant performance of its FPGA and semiconductor products to current specifications in accordance with Altera's or Intel's standard warranty as applicable, but reserves the right to make changes to any products and services at any time without notice. Altera and Intel assume no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera or Intel. Altera and Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

\*Other names and brands may be claimed as the property of others.

## 1.1. Key Features and Innovations in Agilex 3 FPGAs and SoCs

The Agilex 3 FPGAs and SoCs tier consists of C-Series FPGAs.

**Table 1. Agilex 3 FPGAs and SoCs C-Series**

| Feature and Innovation    | C-Series                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Process technology        | Intel 7                                                                                                                                                                                                                                                                                                                                                                                                                |

| Architecture              | Monolithic die                                                                                                                                                                                                                                                                                                                                                                                                         |

| Packaging                 | <ul style="list-style-type: none"> <li>Variable pitch BGA (VPBGA) package<sup>(1)</sup> for smaller form factor and to help reduce the number of PCB layers</li> <li>Rectangular package and standard pattern ball array with smaller ball pitch of 0.5 mm for smaller form factor</li> </ul>                                                                                                                          |

| Core fabric               | Second generation Hyperflex core fabric                                                                                                                                                                                                                                                                                                                                                                                |

| Logic elements            | 25 thousand to 135 thousand                                                                                                                                                                                                                                                                                                                                                                                            |

| On-chip RAM               | <ul style="list-style-type: none"> <li>MLAB and M20K</li> <li>8.3 Mb</li> </ul>                                                                                                                                                                                                                                                                                                                                        |

| Variable precision DSP    | Digital signal processing (DSP) support with up to 180 GFLOPS                                                                                                                                                                                                                                                                                                                                                          |

| AI Tensor Block           | Yes                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Clocking and PLL          | <ul style="list-style-type: none"> <li>Programmable clock tree synthesis for flexible, low power, and low skew clocking</li> <li>I/O PLL supports integer mode with precise frequency synthesis for general purpose I/O, external memory interfaces, LVDS, and fabric usage</li> <li>Transmit PLL (TX PLL) supports fractional synthesis and ultra-low jitter with LC tank-based PLL for transceiver usage.</li> </ul> |

| General Purpose I/Os      | <ul style="list-style-type: none"> <li>1.0 V to 1.3 V high-speed I/O (HSIO)</li> <li>1.8 V to 3.3 V high-voltage I/O (HVIO)</li> </ul>                                                                                                                                                                                                                                                                                 |

| MIPI® D-PHY® v2.5         | Up to 2.5 Gbps <sup>(2)</sup> per lane                                                                                                                                                                                                                                                                                                                                                                                 |

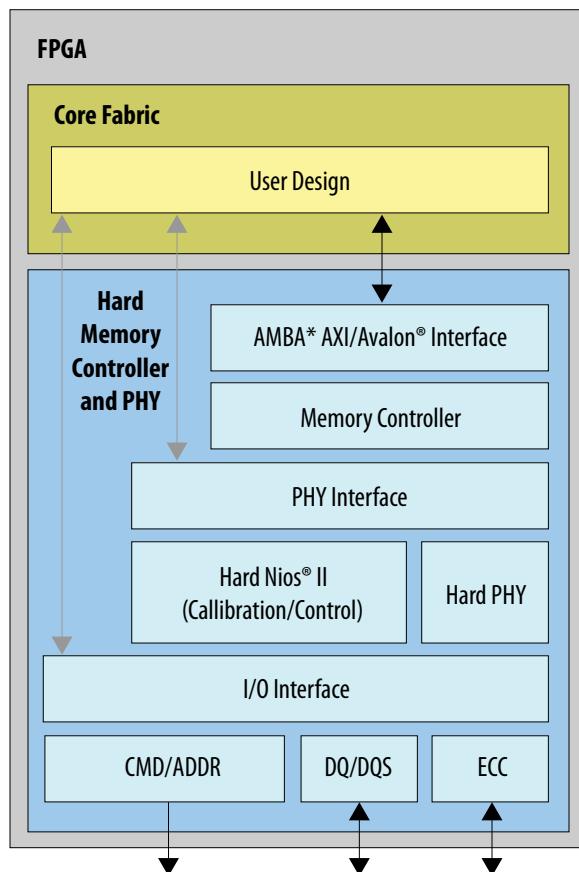

| External memory interface | Fourth generation scalable integrated hard memory controllers and PHY <ul style="list-style-type: none"> <li>2,133 Mbps LPDDR4</li> </ul>                                                                                                                                                                                                                                                                              |

| Cryptographic Services    | SDM supports Advanced Encryption Standard (AES)                                                                                                                                                                                                                                                                                                                                                                        |

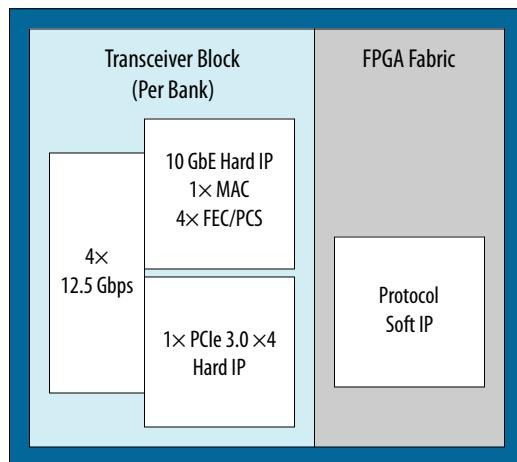

| Transceiver hard IPs      | <ul style="list-style-type: none"> <li>Multiple Gigabit Ethernet (GbE) network interface connectivity in one device</li> <li>PCS and PCIe hard IPs free up valuable core logic resources, save power, and increase your productivity</li> <li>Hardened 10 GbE MAC, PCS, and FEC with IEEE 1588 support</li> <li>Up to 12.5 Gbps NRZ</li> <li>Up to PCIe 3.0 ×4</li> </ul>                                              |

| SDM                       | <p>Dedicated secure device manager (SDM) that:</p> <ul style="list-style-type: none"> <li>Manages FPGA configuration process and all security features</li> <li>Performs authenticated FPGA configuration and HPS boot</li> <li>Supports FPGA bitstream encryption, secure key provisioning, and physically unclonable function (PUF) key storage</li> </ul>                                                           |

*continued...*

<sup>(1)</sup> The Variable Pitch BGA (VPBGA) packaging is compatible with Type III PCBs that use the design rules equivalent to 0.8 mm ball pitch and standard plated through hole (PTH) vias. The VPBGA ball pitch is variable and it helps to ease signal routing. For more information, contact your local sales representative.

<sup>(2)</sup> Up to 2.5 Gbps for standard reference, short reference, and long reference channels.

| Feature and Innovation | C-Series                                                                                                                                                                                                                                                                                                         |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | <ul style="list-style-type: none"> <li>Manages runtime sensors and supports active tamper detection and responses</li> <li>Supports platform attestation using the security protocol and data model (SPDM) protocol</li> <li>Provides user mode access to hardened cryptographic engines as a service</li> </ul> |

| HPS (SoCs only)        | Hard processor system (HPS) with embedded multicore Arm processors—Dual-core 64-bit Arm Cortex-A55 up to 800 MHz                                                                                                                                                                                                 |

| Power Saving           | Comprehensive set of advanced power saving features that deliver up to 38% lower power compared to previous generation FPGAs                                                                                                                                                                                     |

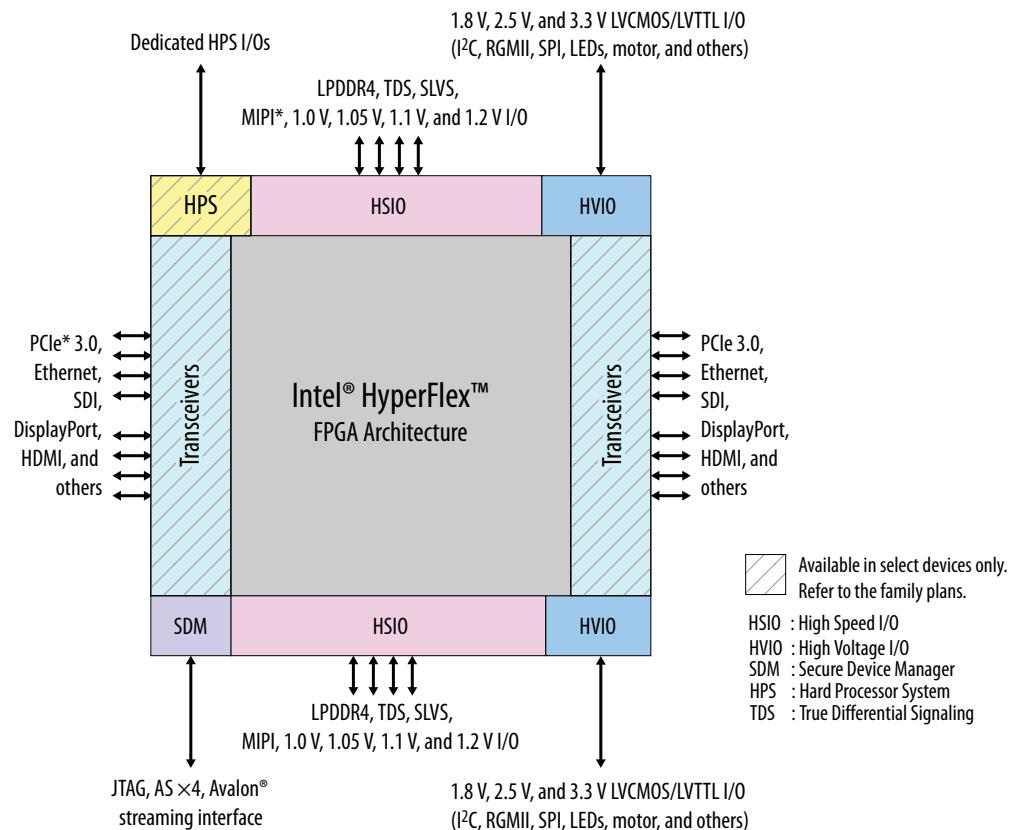

## 1.2. Agilex 3 FPGAs and SoCs Block Diagram

Figure 1. Agilex 3 FPGAs and SoCs C-Series Block Diagram

### Related Information

Agilex 3 FPGAs and SoCs Family Plan on page 11

## 1.3. Agilex 3 FPGAs and SoCs Summary of Features

**Table 2. Feature Summary**

| Feature                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Packaging                     | <ul style="list-style-type: none"> <li>Multiple devices with identical package footprints allows seamless migration across different device densities</li> <li>Variable Pitch BGA (VPBGA) package<sup>(3)</sup> for smaller package form factor and to help reduce the number of PCB layers</li> <li>0.5 mm ball pitch package option for small form-factor with more I/O counts</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| High performance core fabric  | <ul style="list-style-type: none"> <li>Second Generation Hyperflex core architecture with Hyper-Registers throughout the interconnect routing and at the inputs of all functional blocks</li> <li>Enhanced adaptive logic module (ALM)</li> <li>Improved multi-track routing architecture reduces congestion and improves compile times</li> <li>Hierarchical core clocking architecture with programmable clock tree synthesis</li> <li>Fine-grained partial reconfiguration</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Internal memory blocks        | <ul style="list-style-type: none"> <li>Multi-level on-chip memory hierarchy</li> <li>M20K—20 kilobits with hard error correction code (ECC) support</li> <li>MLAB—640-bit distributed LUTRAM</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Variable precision DSP blocks | <ul style="list-style-type: none"> <li>Variable precision DSP blocks with hard IEEE 754-compliant floating-point units, including support for: <ul style="list-style-type: none"> <li>Single-precision FP32 (32-bit arithmetic)</li> <li>Half-precision FP16 (16-bit arithmetic) and FP19 (19-bit arithmetic) floating point modes</li> <li>Tensor floating point FP19 floating point modes</li> <li>BFLOAT16 floating-point format</li> </ul> </li> <li>High-performance AI Tensor blocks: <ul style="list-style-type: none"> <li>Enables high-performance compute density of FPGA fabric Tera Operations Per Second (TOPS)</li> <li>Up to 2.54 INT8 TOPS for AI workloads</li> <li>Hardware programmable for AI with customized workloads</li> <li>Supports push-button flow from industry standard frameworks, such as TensorFlow*, to FPGA bitstream</li> </ul> </li> <li>Every DSP block supports INT16 complex multiplication mode</li> <li>Supports signal processing with precision ranging from 9×9 up to 54×54</li> <li>Native 27×27, 18×19, and 9×9 multiplication modes</li> <li>64-bit accumulator and cascade for systolic 200 GbE finite impulse responses (FIRs)</li> <li>Internal coefficient memory banks</li> <li>Pre-adder/subtractor improves efficiency</li> <li>2× additional pipeline register increases performance and reduces power consumption</li> </ul> |

*continued...*

<sup>(3)</sup> The Variable Pitch BGA (VPBGA) packaging is compatible with Type III PCBs that use the design rules equivalent to 0.8 mm ball pitch and standard plated through hole (PTH) vias. The VPBGA ball pitch is variable and it helps to ease signal routing. For more information, contact your local sales representative.

| Feature                   |                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core clock networks       |                                     | <ul style="list-style-type: none"> <li>Programmable clock tree synthesis—backwards compatible with global, regional and peripheral clock networks</li> <li>Synthesize clocks where needed only—minimizes dynamic power</li> <li>625 MHz LVDS interface clocking—supports 1,250 Mbps LVDS interface through the 1.3 V TDS standard compatible with LVDS, RSDS, mini-LVDS, and LVPECL standards</li> <li>1,067 MHz external memory interface clocking, supports 2,133 Mbps LPDDR4 interface</li> </ul>                                                                                                |

| General purpose I/Os      | General                             | <ul style="list-style-type: none"> <li>1.25 Gbps 1.3 V TDS standard compatible with LVDS, RSDS, mini-LVDS, and LVPECL standards</li> <li>1.0 V, 1.05 V, 1.1 V, and 1.2 V single-ended LVCMS interfacing</li> <li>1.8 V, 2.5 V, and 3.3 V single-ended LVCMS/LVTTL I/O</li> <li>On-chip termination (OCT)</li> <li>Over 300 total GPIOs available</li> </ul>                                                                                                                                                                                                                                         |

|                           | External memory interface (Hard IP) | 1,067 MHz (2,133 Mbps) LPDDR4 external memory interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                           | MIPI                                | MIPI D-PHY v2.5 at up to 2.5 Gbps <sup>(4)</sup> per lane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Phase locked loops (PLL)  | I/O PLL                             | <ul style="list-style-type: none"> <li>Integer PLLs adjacent to general purpose I/Os</li> <li>Precision frequency synthesis</li> <li>Clock delay compensation</li> <li>Zero-delay buffering</li> <li>Support external memory and LVDS-compatible interface</li> </ul>                                                                                                                                                                                                                                                                                                                               |

|                           | Transmit PLLs (TX PLLs)             | <ul style="list-style-type: none"> <li>Precise fractional synthesis</li> <li>Ultra low jitter with LC tank-based PLL</li> <li>Supports transceiver interfaces</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                           | System PLL                          | <ul style="list-style-type: none"> <li>One System PLL per GTS transceiver bank</li> <li>Integer mode</li> <li>Precision frequency synthesis</li> <li>Supports transceiver-to-fabric interface</li> <li>You can repurpose the System PLL for core usage if it is not used by the GTS transceiver</li> </ul>                                                                                                                                                                                                                                                                                          |

| Memory controller support |                                     | <p>Multiple hard IP instantiations in each device</p> <ul style="list-style-type: none"> <li>LPDDR4 hard memory controller</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Transceivers              | PCIe                                | PCIe rates up to PCIe 3.0, 8 Gbps NRZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                           | Networking                          | <ul style="list-style-type: none"> <li>Insertion loss compliant to 802.3bj and CEI 25G-LR standards</li> <li>Oversampling capability for data rates below 1 Gbps</li> <li>SFP+ optical module support</li> <li>Adaptive linear and decision feedback equalization</li> <li>Transmit pre-emphasis and de-emphasis</li> <li>Dynamic reconfiguration of individual GTS transceiver channels</li> <li>On-chip instrumentation (Quartus® Prime Eye Viewer with non-destructive eye height and destructive eye width margining)</li> <li>Continuous operating range of 1 Gbps to 12.5 Gbps NRZ</li> </ul> |

continued...

<sup>(4)</sup> Up to 2.5 Gbps for standard reference, short reference, and long reference channels.

| Feature             |                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transceiver hard IP | PCIe            | <ul style="list-style-type: none"> <li>One hard IP instantiations in each device</li> <li>Single-root I/O virtualization (SR-IOV)</li> <li>Precise time management</li> <li>Up to PCIe 3.0 ×4 EP and RP</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                     | Other protocols | <ul style="list-style-type: none"> <li>CR/KR (AN/LT)</li> <li>1588 PTP</li> <li>MAC, PCS, and FEC bypass options</li> <li>Ethernet IP configuration: 4 × 10 GbE MAC, PCS, and FEC</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Configuration       |                 | <ul style="list-style-type: none"> <li>Dedicated SDM</li> <li>Software-programmable device configuration</li> <li>Serial flash interface</li> <li>Configuration from parallel flash through external host</li> <li>Fine-grained partial reconfiguration of core fabric—add or remove system logic while the device is operating</li> <li>Dynamic reconfiguration of GTS transceivers and PLLs</li> <li>Comprehensive set of security features including AES-256, SHA-256/384, and ECDSA-256/384 accelerators</li> <li>PUF service</li> <li>Platform attestation</li> <li>Anti-tamper features</li> <li>Configuration via protocol (CvP) using PCIe 1.0, 2.0, or 3.0</li> </ul> |

| Functional safety   |                 | <ul style="list-style-type: none"> <li>Functional Safety Data Package (FSDP)</li> <li>Improved FPGA diagnostic measures enable use of Agilex 3 FPGAs in safety-critical applications</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Software and tools  |                 | <ul style="list-style-type: none"> <li>Quartus Prime Pro Edition design suite with new compiler and Hyper-Aware design flow</li> <li>New compile innovations in each Intel oneAPI release</li> <li>Transceiver toolkit</li> <li>Platform Designer IP integration tool</li> <li>Altera DSP Builder for Intel FPGAs advanced blockset</li> <li>Arm Development Studio for Intel SoC FPGA (Arm DS for Intel SoC FPGA)</li> </ul>                                                                                                                                                                                                                                                  |

## 1.4. Additional Features for Agilex 3 SoCs

In addition to the common features of the Agilex 3 FPGAs and SoCs, the Agilex 3 SoCs provide additional features.

**Table 3. Features Specific to Agilex 3 SoCs**

| SoC Subsystem | Feature                  | Description                                                                                                                                                                                                                                                                                      |

|---------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HPS           | Multiprocessor unit core | <ul style="list-style-type: none"> <li>Dual-core Arm Cortex-A55 MPCore processors, with Arm CoreSight* debug and trace technology</li> <li>Scalar floating-point unit supporting single and double precision</li> <li>Arm Neon* technology media processing engine for each processor</li> </ul> |

|               | System controllers       | <ul style="list-style-type: none"> <li>System memory management unit (SMMU)</li> <li>Cache coherency unit (CCU)</li> </ul>                                                                                                                                                                       |

*continued...*

| SoC Subsystem             | Feature                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | Cache                                        | <ul style="list-style-type: none"> <li>Arm Cortex-A55:           <ul style="list-style-type: none"> <li>Level 1 cache per core:               <ul style="list-style-type: none"> <li>32 KB L1 instruction cache with parity</li> <li>32 KB L1 data cache with ECC</li> </ul> </li> <li>Level 2 cache per core: Unified 128 KB L2 data and instructions cache with ECC</li> <li>Level 3 cache: 1 megabytes (MB) L3 cache</li> </ul> </li> </ul> |

|                           | On-chip memory                               | 512 KB on-chip RAM                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                           | Direct memory access (DMA)                   | Eight-channel DMA controller                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                           | Ethernet MAC (TSN)                           | Three 10 Mbps/100 Mbps/1 Gbps Ethernet MACs with integrated DMA and Time-Sensitive Networking (TSN) support                                                                                                                                                                                                                                                                                                                                    |

|                           | USB                                          | <ul style="list-style-type: none"> <li>One USB 2.0 On-The-Go (OTG) with integrated DMA</li> <li>One USB 3.1 Gen 1</li> </ul>                                                                                                                                                                                                                                                                                                                   |

|                           | UART                                         | Two UART 16550-compatible controllers                                                                                                                                                                                                                                                                                                                                                                                                          |

|                           | Serial peripheral interface (SPI) controller | Four SPI (two masters and two slaves)                                                                                                                                                                                                                                                                                                                                                                                                          |

|                           | I <sup>2</sup> C                             | Five I <sup>2</sup> C controllers                                                                                                                                                                                                                                                                                                                                                                                                              |

|                           | I <sup>3</sup> C                             | Two I <sup>3</sup> C controllers                                                                                                                                                                                                                                                                                                                                                                                                               |

|                           | SD/SDIO/eMMC controller                      | <ul style="list-style-type: none"> <li>SD/eMMC devices up to version 5.1</li> <li>SD devices up to version 6.1</li> <li>SDIO devices up to version 4.1</li> </ul>                                                                                                                                                                                                                                                                              |

|                           | NAND flash controller                        | <ul style="list-style-type: none"> <li>One ONFI 1.x and 2.x</li> <li>8 bit and 16 bit support</li> <li>Compatible with Toggle 1.x and 2.x specifications</li> </ul>                                                                                                                                                                                                                                                                            |

|                           | GPIO                                         | Maximum of 48 software-programmable GPIOs                                                                                                                                                                                                                                                                                                                                                                                                      |

|                           | Timers                                       | <ul style="list-style-type: none"> <li>Four general-purpose timers</li> <li>Five watchdog timers</li> </ul>                                                                                                                                                                                                                                                                                                                                    |

| SDM                       |                                              | <ul style="list-style-type: none"> <li>Secure boot</li> <li>AES encryption</li> <li>Secure Hash Algorithms (SHA) and Elliptic Curve Digital Signature Algorithm (ECDSA) authentications</li> </ul>                                                                                                                                                                                                                                             |

| External memory interface |                                              | Hard memory controllers—LPDDR4                                                                                                                                                                                                                                                                                                                                                                                                                 |

## 2. Agilex 3 FPGAs and SoCs Family Plan

The Agilex 3 FPGAs and SoCs are available as C-Series FPGAs with different features to fit your application requirements.

*Note:*

- The tables in the following sections are preliminary and subject to change.

- The resource counts vary by package options.

- The performance specifications vary by speed grades.

- The HPS and GTS transceivers are available only for specific ordering part numbers.

### Related Information

[Agilex 3 FPGAs and SoCs Family Plan](#) on page 11

### 2.1. Agilex 3 FPGAs and SoCs C-Series

**Table 4. C-Series FPGA Family Plan—Core Features**

The values in this table are maximum resources or performance.

| Device | Logic Element | Adaptive Logic Module | M20K  |           | MLAB  |           | DSP               |                                  |

|--------|---------------|-----------------------|-------|-----------|-------|-----------|-------------------|----------------------------------|

|        |               |                       | Count | Size (Mb) | Count | Size (Mb) | 18x19 Multipliers | Peak INT8 (TOPS <sup>(5)</sup> ) |

| A3C025 | 25,075        | 8,500                 | 65    | 1.27      | 450   | 0.27      | 68                | 0.47                             |

| A3C050 | 47,200        | 16,000                | 123   | 2.40      | 800   | 0.49      | 130               | 0.90                             |

| A3C065 | 65,490        | 22,200                | 169   | 3.30      | 1,050 | 0.64      | 179               | 1.21                             |

| A3C100 | 100,300       | 34,000                | 262   | 5.12      | 2,000 | 1.22      | 276               | 1.90                             |

| A3C135 | 135,110       | 45,800                | 353   | 6.89      | 2,300 | 1.40      | 368               | 2.54                             |

<sup>(5)</sup> Tera Operations Per Second

© Altera Corporation. Altera, the Altera logo, the 'a' logo, and other Altera marks are trademarks of Altera Corporation. Altera and Intel warrant performance of its FPGA and semiconductor products to current specifications in accordance with Altera's or Intel's standard warranty as applicable, but reserves the right to make changes to any products and services at any time without notice. Altera and Intel assume no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera or Intel. Altera and Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

\*Other names and brands may be claimed as the property of others.

**Table 5. C-Series FPGA Family Plan—I/Os and Interfaces**

The values in this table are maximum resources or performance.

| Device | HVIo<br>(1.8 V–3.3 V) | HSIO<br>(1.0 V–1.3 V) | PLL Count  |                                              | 1.3 V LVDS<br>Pairs<br>at 1.25 Gbps | LPDDR4<br>Interface<br>(×32) | MIPI<br>D-PHY<br>Interface |

|--------|-----------------------|-----------------------|------------|----------------------------------------------|-------------------------------------|------------------------------|----------------------------|

|        |                       |                       | I/O<br>PLL | Fabric-<br>Feeding I/O<br>PLL <sup>(6)</sup> |                                     |                              |                            |

| A3C025 | 160                   | 96                    | 2          | 5                                            | 48                                  | 0                            | 0                          |

| A3C050 | 160                   | 96                    | 2          | 5                                            | 48                                  | 1                            | 7                          |

| A3C065 | 160                   | 96                    | 2          | 5                                            | 48                                  | 1                            | 7                          |

| A3C100 | 200                   | 192                   | 4          | 8                                            | 96                                  | 2                            | 14                         |

| A3C135 | 200                   | 192                   | 4          | 8                                            | 96                                  | 2                            | 14                         |

**Table 6. C-Series FPGA Family Plan—Transceivers and HPS**

The values in this table are maximum resources or performance.

| Device | PCIe 3.0 ×4 | HPS                                      |                                                                                                                                                                         |

|--------|-------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |             | Processor                                | Cache Size                                                                                                                                                              |

| A3C025 | —           | —                                        | —                                                                                                                                                                       |

| A3C050 | —           | —                                        | —                                                                                                                                                                       |

| A3C065 | —           | —                                        | —                                                                                                                                                                       |

| A3C100 | 1           | • Dual core Arm Cortex-A55 up to 800 MHz | <ul style="list-style-type: none"> <li>1 MB L3</li> <li>Cortex-A55:           <ul style="list-style-type: none"> <li>32 KB L1</li> <li>128 KB L2</li> </ul> </li> </ul> |

| A3C135 | 1           |                                          |                                                                                                                                                                         |

<sup>(6)</sup> The fabric-feeding I/O PLL counts include the System PLL in the GTS transceiver banks. You can use the System PLL for core fabric usage if you do not use it for the transceiver.

## 2.2. Agilex 3 FPGAs and SoCs C-Series Package Options

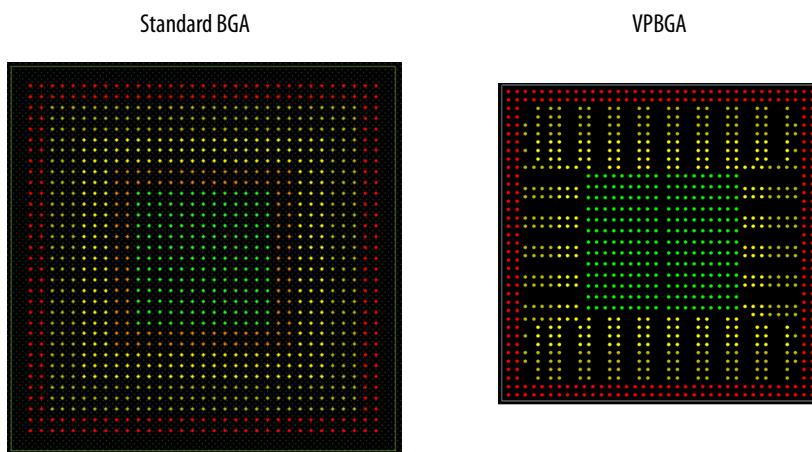

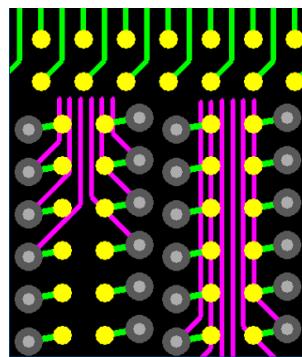

**Figure 2. Package Options, Migrations, and I/O Pins—C-Series**

In this figure, the arrows indicate the package migration paths. The shades represent the devices included in each path.

| Series   | Device  | Package                                                                        |                                       |                                                                                                               |                                        |                                        |

|----------|---------|--------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------|

|          |         | Ball Pitch: 0.5 mm<br>Grid Array Pattern: Standard<br>MBGA: Micro Fineline BGA |                                       | Ball Pitch: Variable <sup>(1)(2)</sup><br>Grid Array Pattern: Variable Pitch BGA<br>VPBGA: Variable Pitch BGA |                                        |                                        |

|          |         | M12A<br>484-pin MBGA<br>12 mm × 12 mm                                          | M16A<br>896-pin MBGA<br>16 mm × 16 mm | B18A<br>474-pin VPBGA<br>18 mm × 18 mm                                                                        | B18B<br>538-pin VPBGA<br>23 mm × 23 mm | B23C<br>931-pin VPBGA<br>23 mm × 23 mm |

| C-Series | A3C 025 | ↑ 160 / 72 (36) / 0 / 0                                                        |                                       | ↑ 160 / 48 (24) / 0 / 0                                                                                       | ↑ 160 / 96 (48) / 0 / 0                |                                        |

|          | A3C 050 | 160 / 72 (36) / 0 / 0                                                          |                                       | 160 / 48 (24) / 0 / 0                                                                                         | 160 / 96 (48) / 0 / 0                  |                                        |

|          | A3C 065 | ↓ 160 / 72 (36) / 0 / 0                                                        |                                       | 160 / 48 (24) / 0 / 0                                                                                         | ↓ 160 / 96 (48) / 0 / 0                |                                        |

|          | A3C 100 |                                                                                | ↑ 40 / 192 (96) / 48 / 4              | 160 / 48 (24) / 0 / 0                                                                                         |                                        | ↑ 200 / 144 (72) / 48 / 4              |

|          | A3C 135 |                                                                                | ↓ 40 / 192 (96) / 48 / 4              | 160 / 48 (24) / 0 / 0                                                                                         |                                        | ↓ 200 / 144 (72) / 48 / 4              |

Notes:

(1) The Variable Pitch BGA (VPBGA) packaging is compatible with Type III PCBs that use the design rules equivalent to 0.8 mm ball pitch and standard plated through hole (PTH) vias.

(2) The VPBGA ball pitch is variable and it helps to ease signal routing. For more information, contact your local sales representative.

For more information about the device migration path, refer to the *Device Migration Guidelines: Agilex 3 FPGAs and SoCs C-Series*.

### Related Information

[Device Migration Guidelines: Agilex 3 FPGAs and SoCs C-Series](#)

Provides more information about the device migration path.

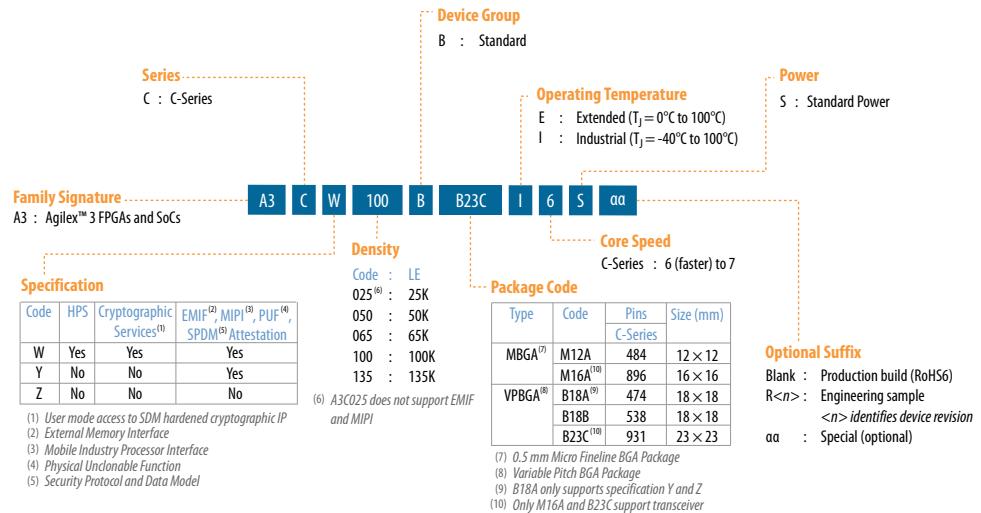

## 2.3. Part Number Decoder

**Figure 3. Agilex 3 FPGAs and SoCs Ordering Part Number**

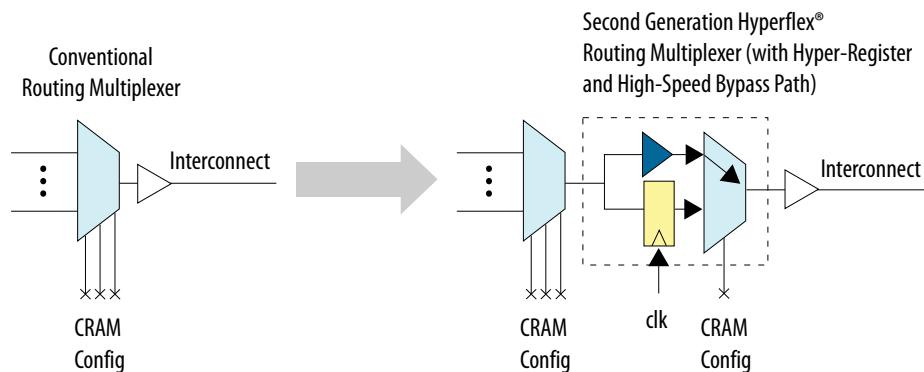

### 3. Second Generation Hyperflex Core Architecture

The Agilex 3 FPGAs and SoCs are based on a core fabric featuring the second generation Hyperflex core architecture.

**Table 7. Advantages of the Hyperflex Core Architecture**

This table lists some of the advantages of the Hyperflex core architecture.

| Advantage                       | Description                                                                                                                                                                    |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Higher throughput               | Delivers, on average, 1.9x higher core clock frequency performance in designs from previous generation FPGAs to obtain throughput breakthroughs.                               |

| Improved power efficiency       | Uses reduced IP size to consolidate designs that previously spanned multiple devices into a single device.                                                                     |

| Greater design functionality    | Uses faster clock frequency to reduce bus widths and reduce IP size. The reduced bus widths and IP size free up additional FPGA resources to add greater functionality.        |

| Increased designer productivity | Boosts performance with less routing congestion and fewer design iterations using the Hyper-Aware design tools, obtaining greater timing margin for more rapid timing closure. |

Additional to traditional ALM user registers, the Hyperflex core architecture adds bypassable registers called Hyper-Registers:

- Distributed throughout the FPGA fabric.

- Available on every interconnect routing segment and at the inputs of all functional blocks.

**Figure 4. Bypassable Hyper-Register**

In the second generation Hyperflex core architecture, Altera optimized the number of registers to improve timing closure time and fabric area utilization.

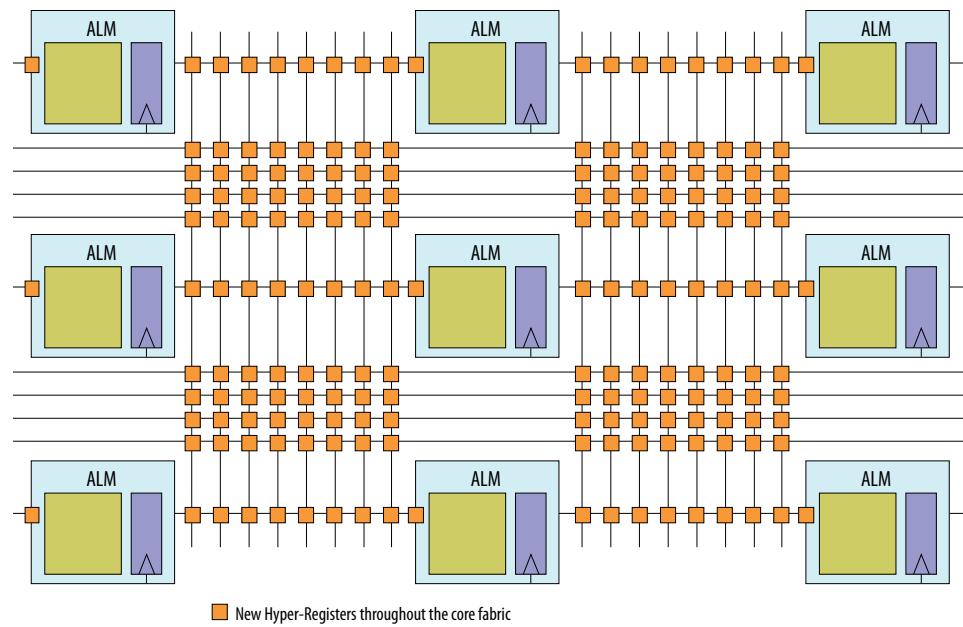

Figure 5. Hyperflex Core Architecture

The Hyper-Registers enable you to achieve core performance increases using key design techniques. If you implement these design techniques, the Hyper-Aware design tools automatically utilizes the Hyper-Registers to achieve maximum core clock frequency:

- Fine grain Hyper-Retiming to eliminate critical paths

- Zero-latency Hyper-Pipelining to eliminate routing delays

- Flexible Hyper-Optimization for best-in-class performance

## 4. Adaptive Logic Module in Agilex 3 FPGAs and SoCs

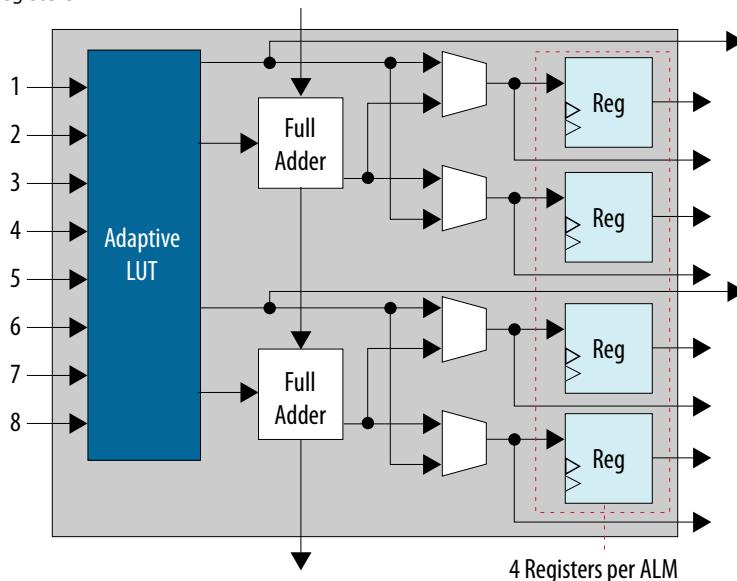

The Agilex 3 FPGAs and SoCs use an enhanced adaptive logic module (ALM) as shown in the *ALM Block Diagram* figure and its key features and capabilities are listed in the *Key Features and Capabilities of the ALM* table.

**Figure 6. ALM Block Diagram**

This figure shows the ALM with 8-input fracturable look-up table (LUT), two dedicated embedded adders, and four dedicated registers.

**Table 8. Key Features and Capabilities of the ALM**

| Key Feature               | Capability                                                                                                                                                                                      |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High register count       | Together with the second generation Hyperflex architecture, the four registers per 8-input fracturable LUT enables maximized core performance at very high core logic utilization.              |

| ALM operating modes       | Optimize core logic utilization by implementing an extended 7-input logic function, a single 6-input logic function, or two smaller independent functions (for example, two 4-input functions). |

| Two clock sources         | Two clock sources per ALM generate two normal clocks and two delayed clocks to drive the ALM registers, resulting in more clock domains and time-borrowing capability.                          |

| Additional LUT outputs    | Additional fast 6-LUT and 5-LUT outputs for combinatorial functions improve critical path for logic cascade.                                                                                    |

| Improved register packing | The improved register packing, including 5-input LUT with two packed register paths, results in more efficient usage of the fabric area and improved critical path.                             |

| Latch mode support        | The ALM supports latch mode in the address latch enable.                                                                                                                                        |

© Altera Corporation. Altera, the Altera logo, the 'a' logo, and other Altera marks are trademarks of Altera Corporation. Altera and Intel warrant performance of its FPGA and semiconductor products to current specifications in accordance with Altera's or Intel's standard warranty as applicable, but reserves the right to make changes to any products and services at any time without notice. Altera and Intel assume no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera or Intel. Altera and Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

\*Other names and brands may be claimed as the property of others.

The Quartus Prime software capitalizes on the ALM logic structure to deliver the highest performance, optimal logic utilization, and lowest compile times. The Quartus Prime software simplifies design reuse as the software automatically maps legacy designs into the ALM architecture of the Agilex 3 FPGAs and SoCs.

## 5. Internal Embedded Memory in Agilex 3 FPGAs and SoCs

The embedded memory blocks in Agilex 3 FPGAs and SoCs are similar to the embedded memory of previous generation Altera FPGAs.

**Table 9. Embedded Memory Block Types and Features for Agilex 3 FPGAs and SoCs**

| Feature        | MLAB                                                                                                                          | M20K                                                                                                                                                                                                                                              |

|----------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Usage          | For wide and shallow memory configurations                                                                                    | For supporting larger memory configurations                                                                                                                                                                                                       |

| Block size     | 640 bits                                                                                                                      | 20 kilobits                                                                                                                                                                                                                                       |

| Configurations | <ul style="list-style-type: none"> <li>• <math>64 \times 10</math> (emulated)</li> <li>• <math>32 \times 20</math></li> </ul> | <ul style="list-style-type: none"> <li>• <math>2,048 \times 10</math> (or <math>\times 8</math>)</li> <li>• <math>1,024 \times 20</math> (or <math>\times 16</math>)</li> <li>• <math>512 \times 40</math> (or <math>\times 32</math>)</li> </ul> |

| Hard ECC       | —                                                                                                                             | Yes                                                                                                                                                                                                                                               |

| Modes          | Single-port RAM, dual-port RAM, FIFO, ROM, and shift register                                                                 |                                                                                                                                                                                                                                                   |

## 6. Variable-Precision DSP in Agilex 3 FPGAs and SoCs

The Agilex 3 FPGAs and SoCs are the cost-optimized FPGAs with an AI tensor block, making it the ideal choice for edge AI applications.

For INT8 operations in a single DSP block, the Agilex 3 FPGAs and SoCs C-Series improve peak theoretical TOPS up to 3.6 times than Cyclone® V FPGAs.

Through a large increase in arithmetic density<sup>(7)</sup>, the Agilex 3 FPGAs and SoCs fit more multipliers and accumulators in the same footprint of a standard DSP block.

The FPGA AI Suite (FPGA AI) supports the new AI features. The FPGA AI Suite enables push-button flow from industry standard frameworks—such as Caffe, PyTorch\*, and TensorFlow—to FPGA bitstream.

Additionally, the Agilex 3 FPGAs and SoCs also carry over the variable-precision DSP architecture from previous Altera FPGAs with hard fixed point and IEEE 754-compliant floating point capabilities.

In fixed point mode, you can configure the DSP blocks to support signal processing with precisions from  $9\times 9$  up to  $54\times 54$ :

- Increased  $9\times 9$  multipliers count, with three  $9\times 9$  multipliers for every  $18\times 19$  multiplier

- A pipeline register increases the maximum DSP block operating frequency and reduces the power consumption

- Dynamically switch multiplier inputs through `scanin` and `chainout` signals

- Compile each DSP block independently as six  $9\times 9$ , dual  $18\times 19$ , or single  $27\times 27$  multiply-accumulate.

The variable-precision DSP supports floating point addition, multiplication, multiply-add, and multiply-accumulate:

- Single-precision 32-bit arithmetic FP32 floating point mode

- Half-precision 16-bit arithmetic FP16 and FP19 floating point modes, and BFLOAT16 floating point format

With a dedicated 64-bit cascade bus, you can cascade multiple variable-precision DSP blocks to efficiently implement even higher-precision DSP functions.

---

<sup>(7)</sup> Arithmetic density is a measure of how many dot products can fit into a 1 mm<sup>2</sup> of silicon on any given process node.

© Altera Corporation. Altera, the Altera logo, the 'a' logo, and other Altera marks are trademarks of Altera Corporation. Altera and Intel warrant performance of its FPGA and semiconductor products to current specifications in accordance with Altera's or Intel's standard warranty as applicable, but reserves the right to make changes to any products and services at any time without notice. Altera and Intel assume no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera or Intel. Altera and Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

\*Other names and brands may be claimed as the property of others.

**Table 10. Variable-Precision DSP Block Configurations in Agilex 3 FPGAs and SoCs C-Series**

This table lists the way Agilex 3 FPGAs and SoCs C-Series accommodate the different precisions within a DSP block or by utilizing multiple DSP blocks.

| Multiplier                      | DSP Block Resource Usage                                                                                              | Expected Application                                  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| 9×9 bits                        | One-sixth of a variable-precision DSP block<br>(One DSP block can support six 9×9)                                    | Low-precision fixed point                             |

| 18×19 bits                      | Half of a variable-precision DSP block                                                                                | Medium-precision fixed point                          |

| 27×27 bits                      | One variable-precision DSP block                                                                                      | High-precision fixed point                            |

| 19×36 bits                      | One variable-precision DSP block with external adder                                                                  | Fixed point fast Fourier transform (FFT)              |

| 36×36 bits                      | Two variable-precision DSP blocks with external adder                                                                 | Very high-precision fixed point                       |

| 54×54 bits                      | Four variable-precision DSP blocks with external adder                                                                | Double-precision fixed point                          |

| Half-precision floating point   | One variable-precision DSP block<br>(Contains adder for two FP16, FP19, or BFLOAT16 multipliers with one accumulator) | Half-precision floating point                         |

| Single-precision floating point | One variable-precision DSP block<br>(Contains one FP32 multipliers with one accumulator)                              | Single-precision floating point                       |

| AI tensor block                 | Two sums of ten INT8×INT8 multipliers tensor fixed-point and floating-point computation                               | Tensor dot products of 10-element vectors computation |

| Complex multiplication mode     | One variable-precision DSP block<br>(16×16 ± 16×16)                                                                   | INT16 complex multiplication                          |

## 7. Core Clock Network in Agilex 3 FPGAs and SoCs

Agilex 3 FPGAs and SoCs use programmable clock tree synthesis for its core clocking function.

Programmable clock tree synthesis uses dedicated clock tree routing and switching circuits. These dedicated circuits enable the Quartus Prime software to create the exact clock trees that your design requires.

Advantages of using programmable clock tree synthesis:

- Minimizes clock tree insertion delay

- Reduces dynamic power dissipation in the clock tree

- Allows greater flexibility of clocking in the core

- Maintains backwards compatibility with legacy global and regional clocking schemes

Features of the core clock network of Agilex 3 FPGAs and SoCs:

- Supports the second-generation Hyperflex core architecture

- Supports the hard memory controllers<sup>(8)</sup> for:

- LPDDR4—up to 2,133 Mbps

- Supported by dedicated clock input pins and integer I/O PLLs

### Related Information

- [Key Features and Innovations in Agilex 3 FPGAs and SoCs](#) on page 5

- [Agilex 3 FPGAs and SoCs Summary of Features](#) on page 7

---

<sup>(8)</sup> Each Agilex 3 FPGA series has different hard memory controller support. For more information, refer to the related information.

© Altera Corporation. Altera, the Altera logo, the 'a' logo, and other Altera marks are trademarks of Altera Corporation. Altera and Intel warrant performance of its FPGA and semiconductor products to current specifications in accordance with Altera's or Intel's standard warranty as applicable, but reserves the right to make changes to any products and services at any time without notice. Altera and Intel assume no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera or Intel. Altera and Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

\*Other names and brands may be claimed as the property of others.

## 8. I/O PLLs in Agilex 3 FPGAs and SoCs

The I/O banks of the Agilex 3 FPGAs and SoCs contain I/O PLLs for use in I/O interfacing or fabric clocking.

**Table 11. I/O PLLs in Different I/O Bank Types**

| I/O Bank Type    | Bank I/O PLL | Fabric-Feeding I/O PLL |

|------------------|--------------|------------------------|

| HSIO (96 I/Os)   | 2            | 1                      |

| HVIO (2x20 I/Os) | —            | 1                      |

You can use the I/O PLLs for general purpose applications in the core fabric, such as clock network delay compensation and zero-delay clock buffering.

The I/O PLLs are situated adjacent to the hard memory controllers and LVDS serializer/deserializer (SERDES) blocks in the I/O bank. This placement creates a tight coupling of the PLLs with the I/Os that need them. The architecture simplifies designing external memory and high-speed LVDS interfaces, and eases timing closure.

## 9. General Purpose I/Os in Agilex 3 FPGAs and SoCs

The Agilex 3 FPGAs and SoCs are equipped with two types of general purpose I/Os—the high-speed I/Os (HSIO) and the high-voltage I/Os (HVIO). Both HSIO and HVIO enable important support for edge applications in Agilex 3 FPGAs and SoCs.

**Table 12. I/O Standards Support and Performance**

| I/O Type | I/Os Per Bank     | I/O Standard     | Specification                                                                                                                        | Notes                                                                                                                             |

|----------|-------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

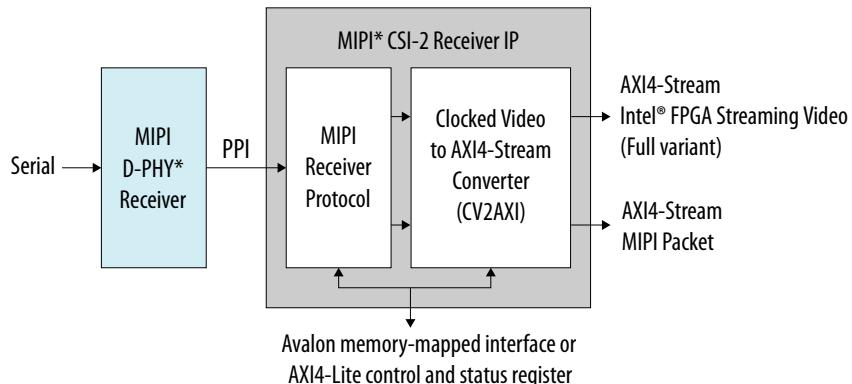

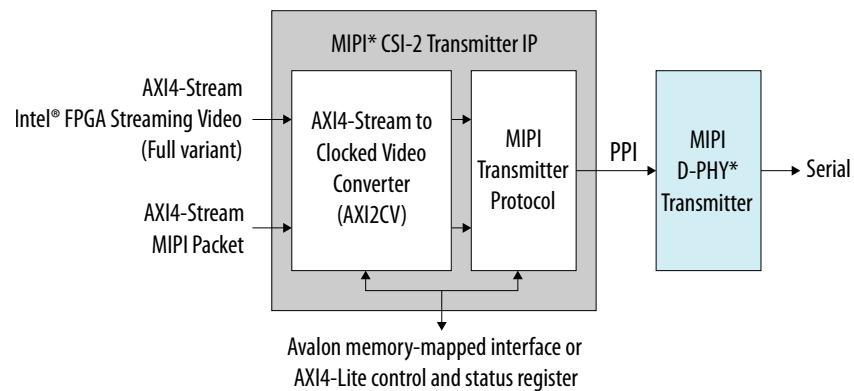

| HSIO     | 96 <sup>(9)</sup> | LVCMOS           | 1.0 V, 1.05 V, 1.1 V, and 1.2 V single-ended                                                                                         | —                                                                                                                                 |