## ISL94216EVKIT1Z

### Evaluation Kit and GUI

#### Purpose

This user manual is intended to demonstrate basic operations of the GUI and ISL94216 Evaluation Kit. Use this document in the sequence it was written, each section assumes the previous section was completed. See the [ISL94216](#) datasheet for detailed information.

#### Software

The ISL94216 GUI is built on top of Excel using Visual Basic for Applications (VBA 1.00). It is designed to allow you to perform detailed evaluation of the ISL94216 and also includes a simplified demonstration GUI.

#### Hardware

The ISL94216EVKIT1Z evaluation kit consists of the following components:

- ISL94216EV1Z - ISL94216 evaluation board

- ISO-DONGLE-EV1Z - ISL94216 communications dongle with USB cable

- BMS-PS-CELL16Z - A 16-cell resistor ladder board

The following equipment is also needed to complete an evaluation of the device:

- Power supply (or battery pack)

- Current meter

- Voltmeter

- Oscilloscope

#### Related Literature

For a full list of related documents, visit our website:

- [ISL94216](#) device page

#### Ordering Information

| Part Number     | Description                                                                         |

|-----------------|-------------------------------------------------------------------------------------|

| ISL94216EVKIT1Z | ISL94216E evaluation kit includes ISL94216EV1Z, ISO-DONGLE-EV1Z, and BMS-PS-CELL16Z |

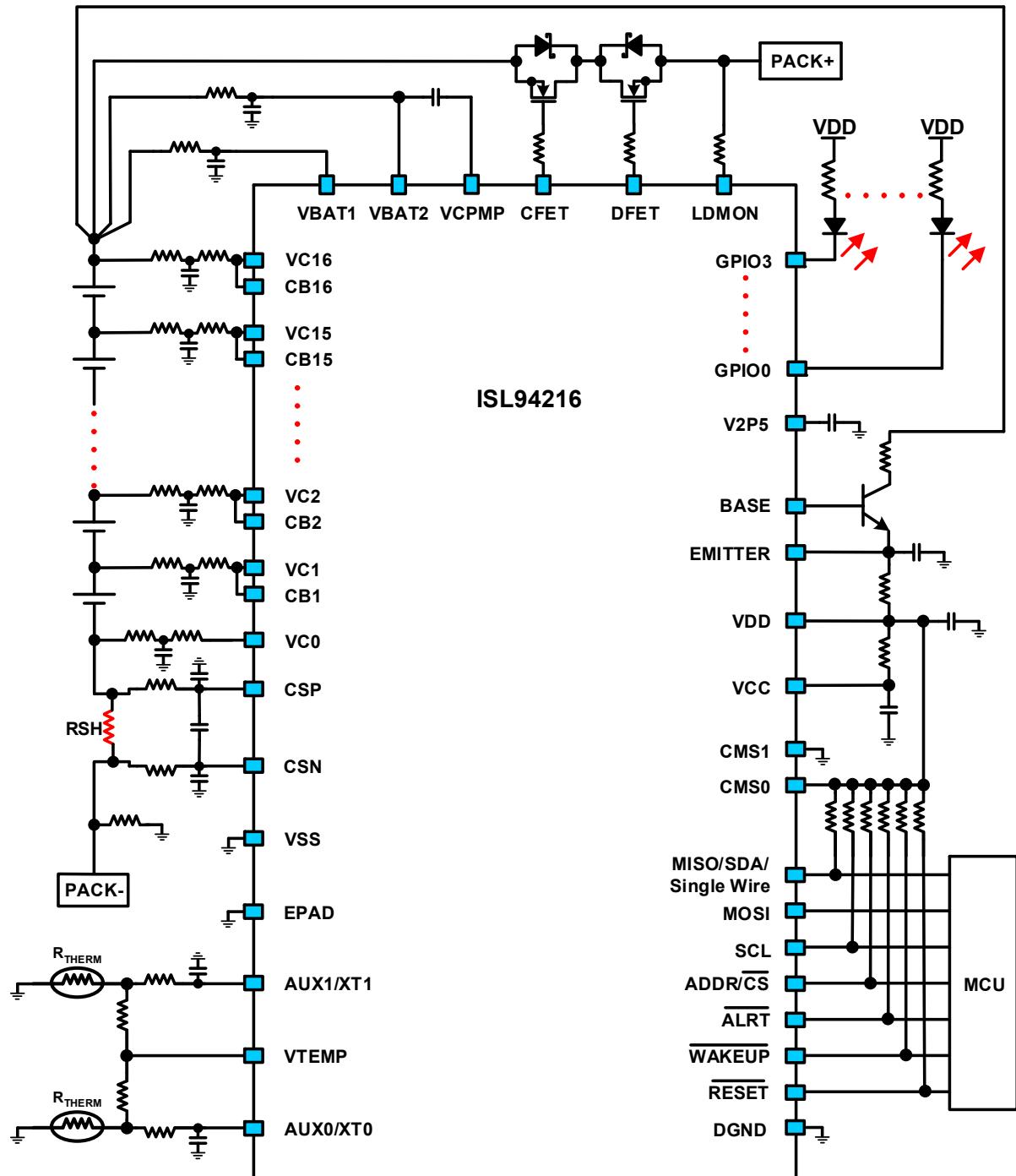

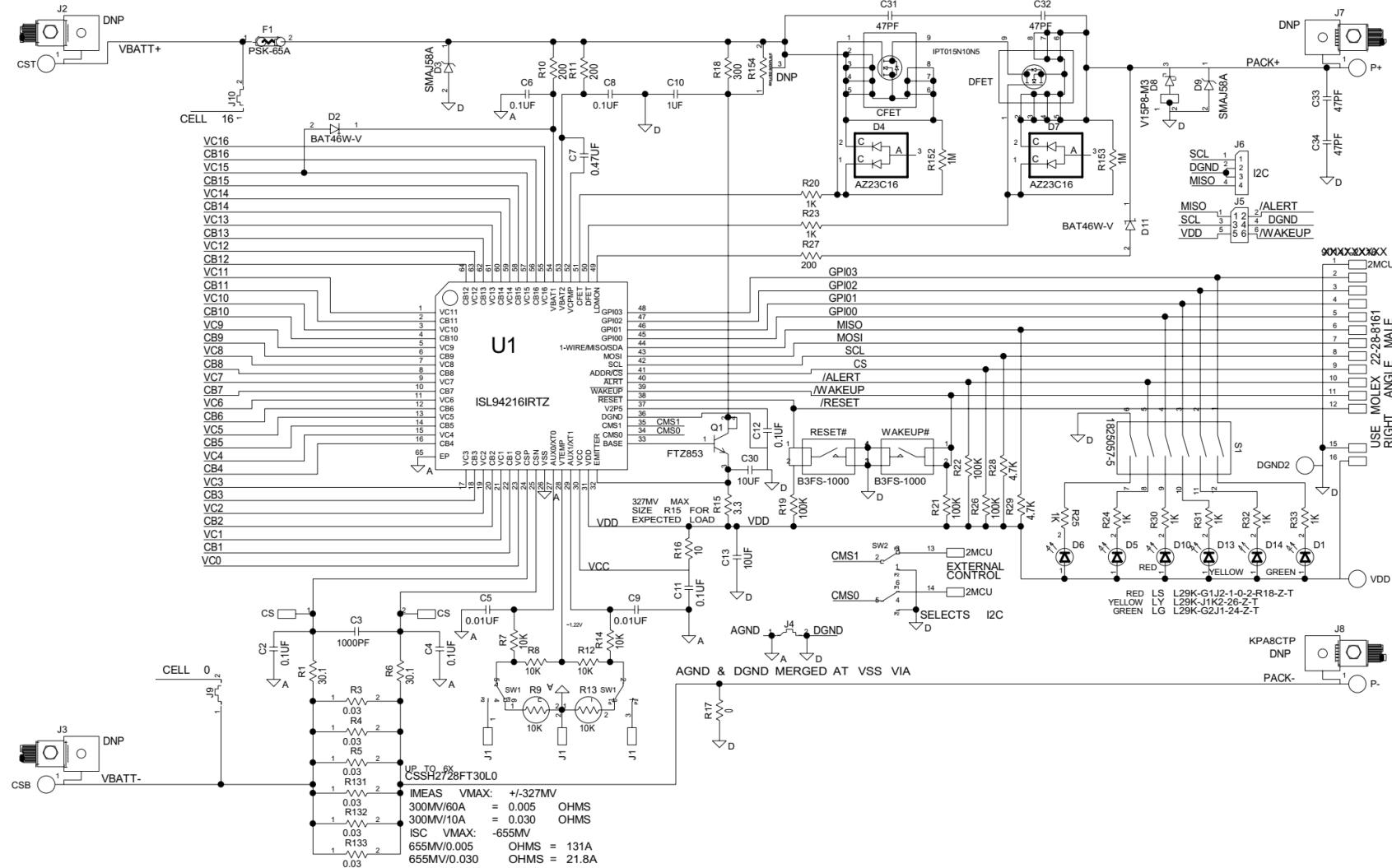

Figure 1. ISL94216 Typical Application

## Contents

|                                    |           |

|------------------------------------|-----------|

| <b>1. Functional Description</b>   | <b>5</b>  |

| 1.1 Evaluation Board               | 5         |

| 1.2 Evaluation Board LEDs          | 6         |

| 1.3 Communications Dongle          | 7         |

| 1.4 Resistor Ladder                | 7         |

| 1.5 Power Supply                   | 8         |

| 1.6 Current Meter                  | 8         |

| 1.7 Voltmeter                      | 8         |

| 1.8 Oscilloscope                   | 8         |

| 1.9 BMS Assembly                   | 9         |

| 1.10 High Current Loads            | 9         |

| <b>2. ISL94216 GUI Start</b>       | <b>10</b> |

| 2.1 Power Supply                   | 10        |

| 2.2 Connect                        | 10        |

| 2.3 Initialization                 | 11        |

| <b>3. SCAN Mode</b>                | <b>13</b> |

| 3.1 Busy Bit                       | 13        |

| 3.2 Single System Scans            | 14        |

| 3.3 Continuous System Scans        | 15        |

| 3.4 Low Power Timer                | 16        |

| <b>4. IDLE Mode</b>                | <b>18</b> |

| 4.1 VCell Trigger                  | 18        |

| 4.2 IPack Trigger                  | 20        |

| 4.3 VREG Trigger                   | 23        |

| 4.4 VBAT/ITEMP Triggers            | 25        |

| 4.5 COMM Timeout                   | 27        |

| <b>5. LOW POWER Mode</b>           | <b>29</b> |

| 5.1 Strong/Weak Regulator          | 29        |

| <b>6. SHIP Mode</b>                | <b>30</b> |

| 6.1 Strong/Weak Regulator          | 30        |

| 6.2 Wakeup                         | 30        |

| <b>7. Demonstration GUI</b>        | <b>32</b> |

| 7.1 Launching the Demo GUI         | 32        |

| 7.2 Initializing the Demo GUI      | 32        |

| 7.3 Demo Single Scan               | 32        |

| 7.4 Demo Continuous Scan           | 33        |

| 7.5 Demo Graphing                  | 33        |

| 7.6 Demo Threshold Modification    | 34        |

| 7.7 Demo Fault Indicators/Clearing | 35        |

| 7.8 Exiting the Demo GUI           | 35        |

|                            |    |

|----------------------------|----|

| 8. Appendix A .....        | 36 |

| 9. Schematic .....         | 47 |

| 10. Revision History ..... | 49 |

## 1. Functional Description

### 1.1 Evaluation Board

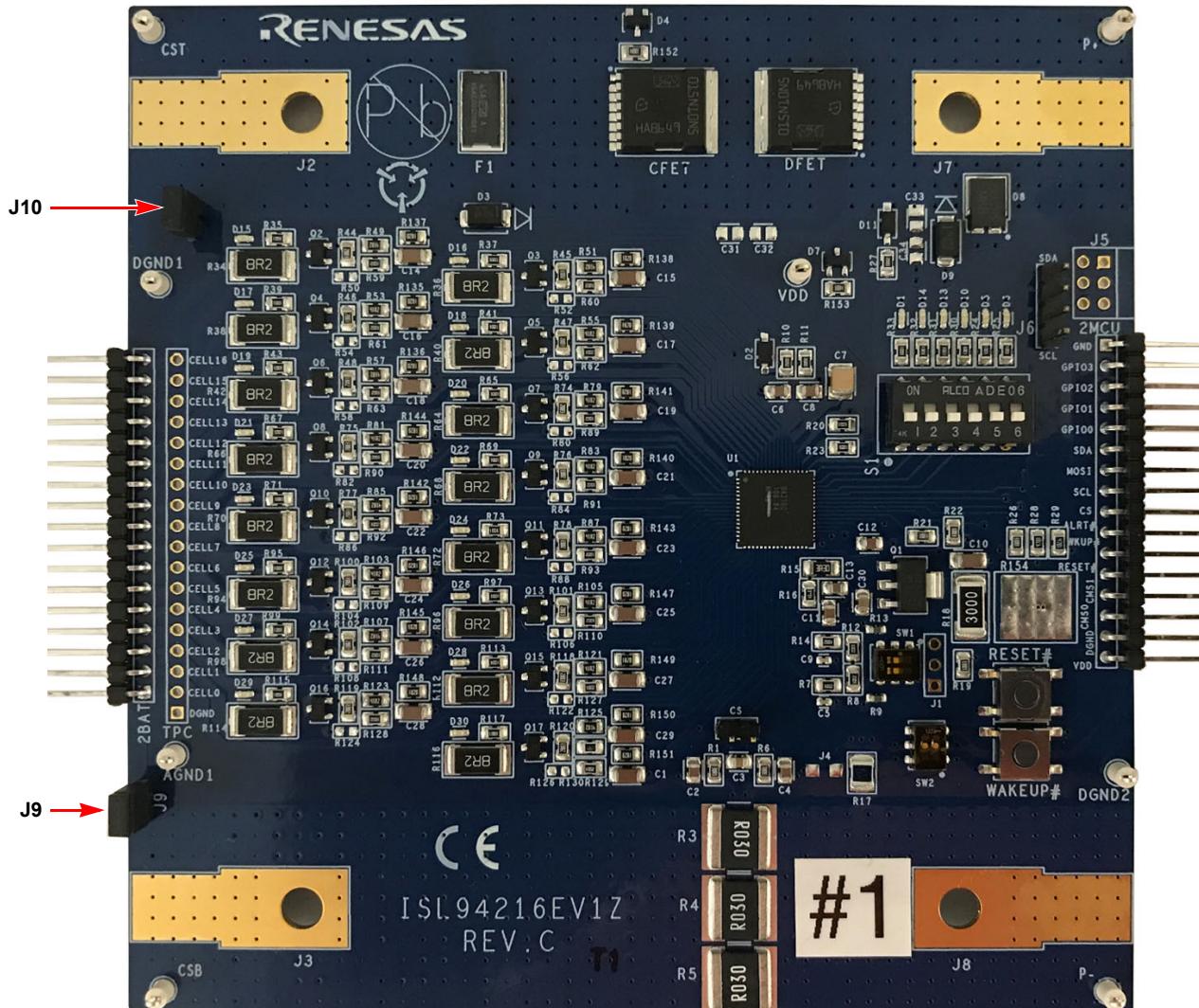

Figure 2. ISL94216EV1Z Evaluation Board

The ISL94216 evaluation board (Figure 2) as shipped from stock is set up for 16 cells with external cell balancing components selected to provide ~500mA of cell balancing current.

Supply current can be monitored by connecting the current meter across J9 or J10. These jumpers MUST be in place if a current meter is not. Exceptions are listed in ["High Current Loads" on page 9](#).

The board can be configured for fewer cells by installing jumpers on connector TPC, or across parts of J3 on the resistor ladder board (see ["Resistor Ladder" on page 7](#)).

A complete schematic for the evaluation board is available here: ["Schematic" on page 47](#).

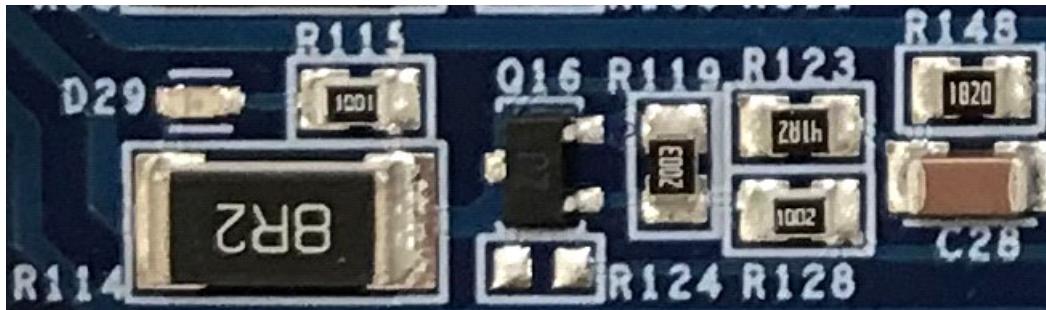

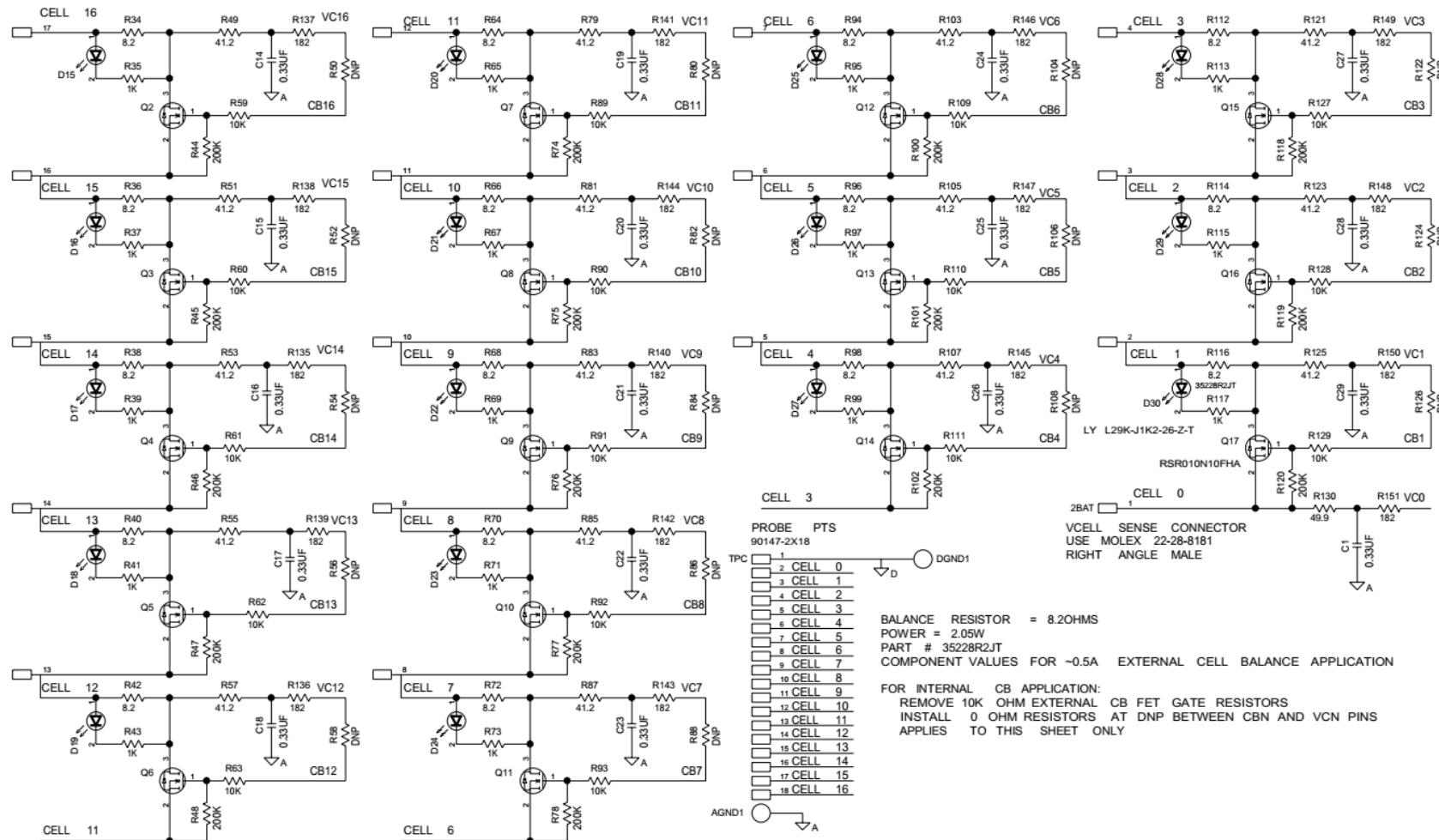

Figure 3. VC1 External Cell Balancing Circuitry

The cell balancing current can be adjusted by changing resistors R34, R36, R38, R40, R42, R64, R66, R68, R70, R72, R94, R96, R98, R112, R114, and R116. VC1 external cell balancing circuitry is shown in [Figure 3](#) with R114 in the lower left.

## 1.2 Evaluation Board LEDs

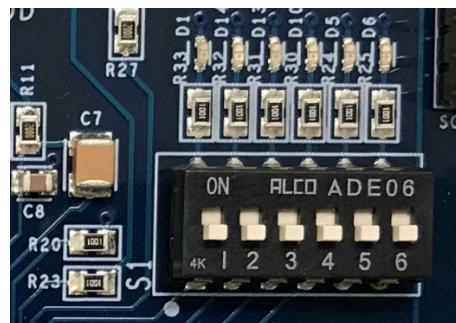

Figure 4. LEDs

The evaluation board has six LEDs, four on the GPIO pins, one for  $\overline{\text{ALRT}}$  and one for VDD. S1 positions 1-4 are in line with the GPIO pins, position 5 is  $\overline{\text{ALRT}}$  and position 6 is VDD. In the OFF position, as shown in [Figure 4](#), the LEDs and their pull-up resistors to VDD are disconnected from the ISL94216 pins. The OFF position allows the ISL94216 supply current to be measured without the external LED current for demonstration and/or verification of datasheet limits.

Slide S1 positions 5 ( $\overline{\text{ALRT}}$  LED D5) and 6 (VDD LED D6) up to the **ON** setting. D6 should light up when the ISL94216 is powered.

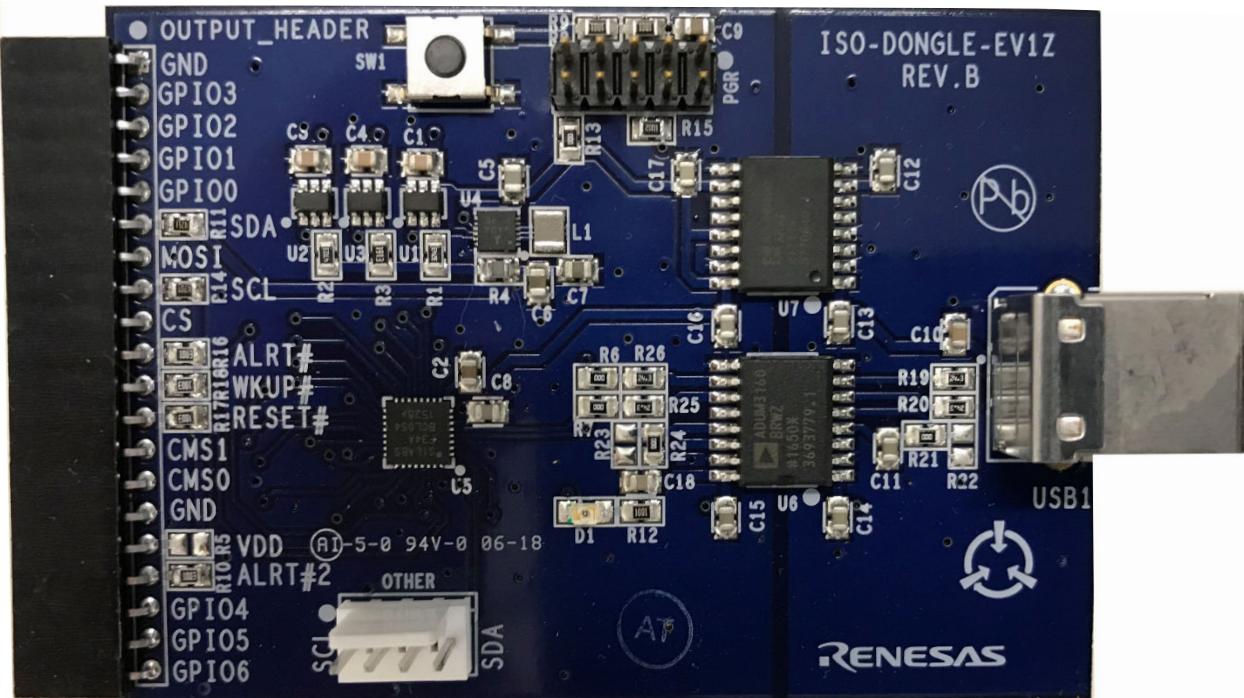

### 1.3 Communications Dongle

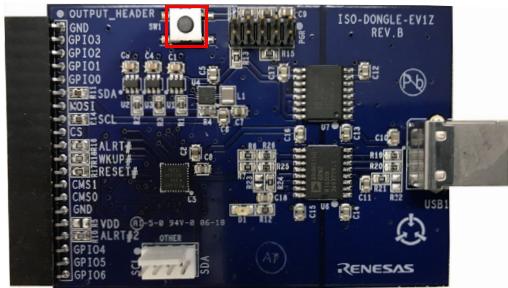

Figure 5. ISO-DONGLE-EV1Z Communications Dongle

The communications dongle, shown in [Figure 5](#), is a board designed to isolate the ISL94216 evaluation board assembly ground from the PC and workbench grounds. Most Battery Management Systems (BMS) operate isolated from earth ground. **IMPORTANT:** When an oscilloscope probe ground is connected to the assembly it can provide a path to earth ground, which in severe cases can reset the ISL94216. Any earth ground connection should be made before the board is powered to avoid an unintended reset.

The dongle enables SPI, I<sup>2</sup>C, and Single Wire communications with the ISL94216. Connect the dongle to the PC using the provided USB cable.

Using the GUI the dongle can be configured to drive or read the ISL94216 GPIO pins.

Under some circumstances the dongle draws current from the ISL94216 evaluation board, it might be necessary to disconnect the dongle from the evaluation board if attempting to measure the current drawn by the ISL94216.

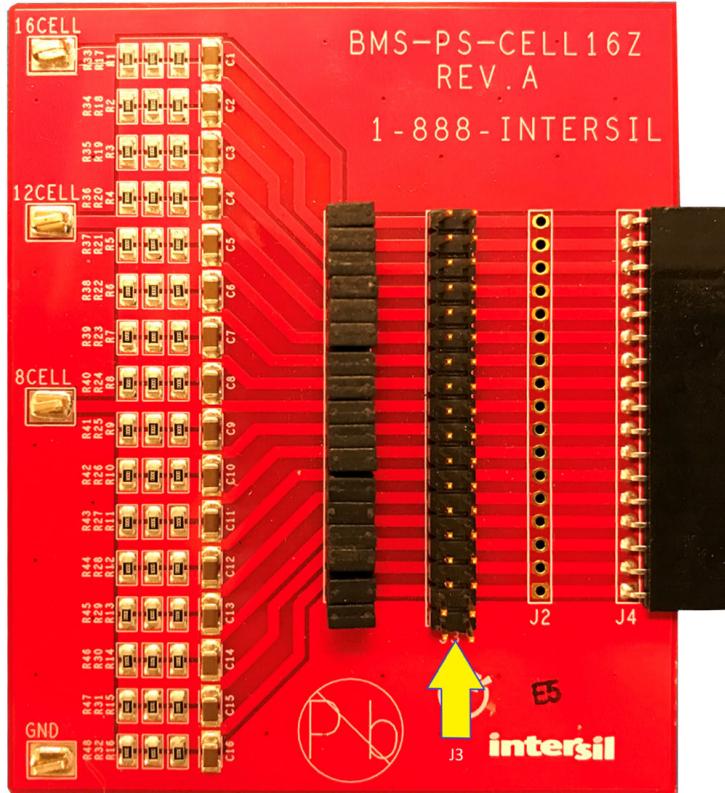

### 1.4 Resistor Ladder

A resistor ladder board is used to mimic a cell stack (limited) if a battery pack is not available. AC or heavy load currents and cell balancing cause voltage fluctuations when using a resistor ladder that would not occur with batteries.

Connector J3, yellow arrow in [Figure 6](#), can be used to short out center cells for the evaluation of systems with fewer than 16 cells. See the Reduced Cell Count section of the ISL94216 datasheet for details.

Each “CELL” of the resistor ladder consists of three 300Ω resistors in parallel resulting in 100Ω per cell. At a typical operating voltage of 48V with 16 100Ω cells in series ~30mA is consumed.

Figure 6. Resistor Ladder Board

## 1.5 Power Supply

If a battery pack is not available, the combination of a power supply and a resistor ladder is used. The power supply must be selected so that it can supply the ladder, ISL94216 evaluation board, and load currents at the required voltage without current limiting.

With the power supply output disabled, connect the negative terminal to the GND clip and the positive terminal to the 16CELL clip on the resistor ladder board.

Set the power supply output voltage to 48V, but keep the output disabled. If using a reduced number of cells, set to the appropriate voltage. Do not exceed 55V VBAT or 4.8V per cell, whichever is lower.

## 1.6 Current Meter

The current meter is used to measure the current consumed by the ISL94216 Evaluation Board and/or load. If a multimeter is used, make certain it is connected and set to measure current. The current meter should be connected in place of **either** jumper J9 or J10 on the evaluation board. The text in the following sections assumes this meter is installed at J10. The jumpers must be installed except in special cases, such as the insertion of the current meter or as described in ["High Current Loads" on page 9](#). The meter should be connected before the power supply output is enabled, or a battery pack is connected to the evaluation board.

## 1.7 Voltmeter

The voltmeter is used to measure various voltages of interest on the ISL94216 BMS assembly. The recommended startup connection is Pack+ (J7) vs Pack- (J8).

## 1.8 Oscilloscope

For capture of communications, analog and digital signals associated with the ISL94216 as needed.

## 1.9 BMS Assembly

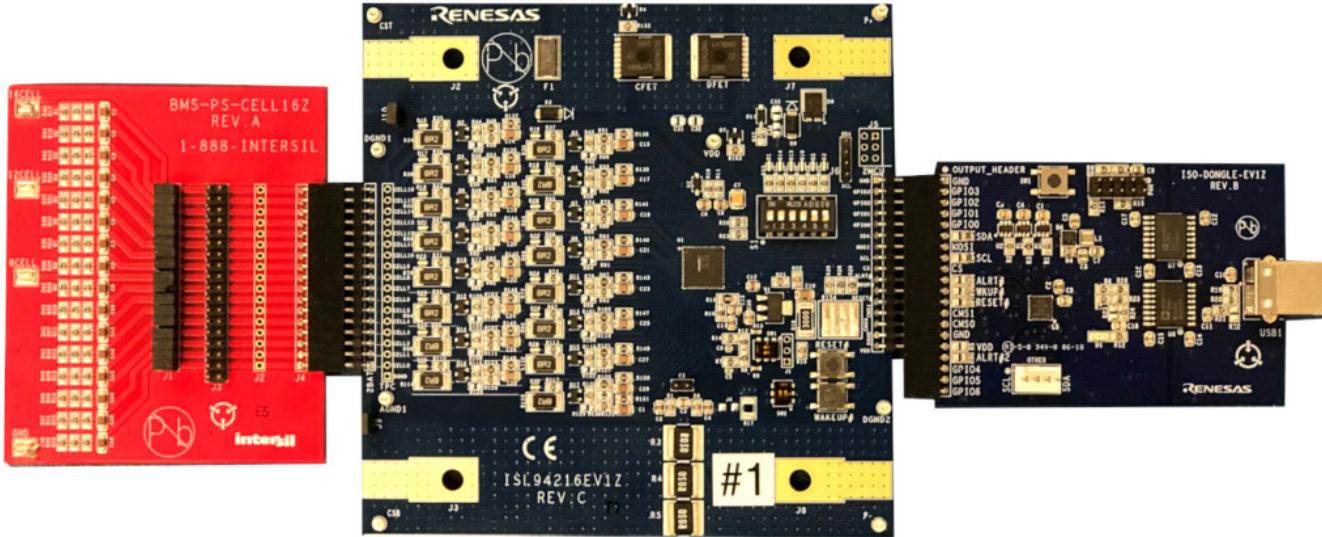

The three boards described previously are connected together as shown in [Figure 7](#).

**Figure 7. BMS Assembly**

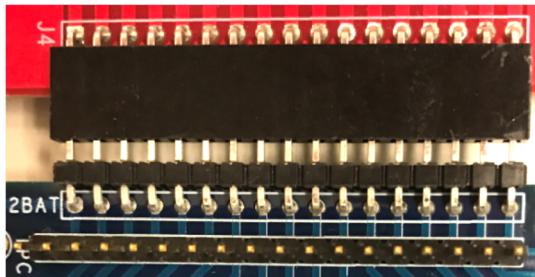

The resistor ladder and ISL94216 evaluation boards connectors line up Pin 1 to Pin 1 with a total of 17 pins. Pin 1 of both connectors is at the bottom of the mated pair shown in [Figure 7](#) and [Figure 8](#).

**Figure 8. Cell Connection**

**Figure 9. Dongle Connection**

The dongle and ISL94216 evaluation board connectors line up Pin 1 to Pin 1, though the dongle has four extra pins. These extra pins are for use with other evaluation boards.

Take note of the orientation of the two connectors ([Figures 8, 9](#)) and in the BMS assembly image ([Figure 7](#)). When you have verified all of the connections, proceed to the next section.

## 1.10 High Current Loads

The evaluation board as configured in [Figure 7](#) is only capable of sourcing low load currents without inducing measurement errors. Jumper J9 connects the low-side current sense resistor to the bottom of the resistor ladder through the VC0 sense line. Jumper J10 connects the high-side load/charge path to the top of the resistor ladder through the VC16 sense line. This configuration routes load current through the voltage sense lines which can induce offset errors in the cell measurements. A setup using a resistor ladder is not appropriate for charging tests.

For high currents a properly sized connection must be made between J3 and the negative terminal of the supply (or battery pack), then J9 should be removed. Another wire from J2 to the positive terminal of the supply is also necessary, then J10 should be removed. This separates the voltage sense lines from the load/charge current path to reduce errors to a minimum and is the recommended configuration for all applications.

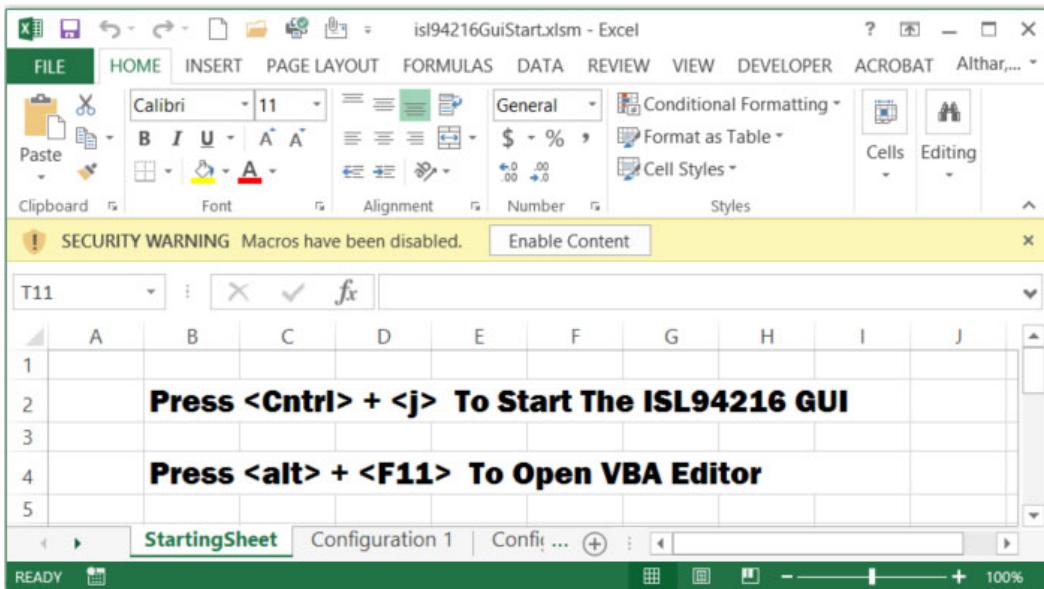

## 2. ISL94216 GUI Start

Open the workbook to get started, there is no installation required. Macros are automatically disabled on some PCs; if the message **SECURITY WARNING Macros have been disabled** is visible beneath the menu bar, select **Enable Content**. This is shown in the [Figure 10](#).

Press the **<Ctrl> + <J>** keys simultaneously to start the GUI.

Figure 10. GUI Start

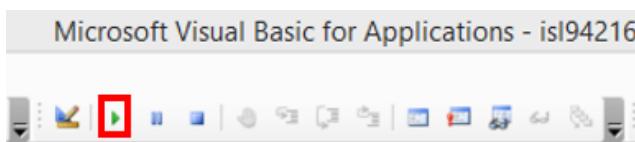

When attempting to launch the GUI from the workbook using the **<Ctrl> + <J>** shortcut, occasionally Excel stops responding and/or crashes. If this occurs, re-open the workbook and press **<Alt> + <F11>** to open the VBA editor. From here either press the green play button, outlined in red in [Figure 11](#), or press **<F5>** to launch the GUI.

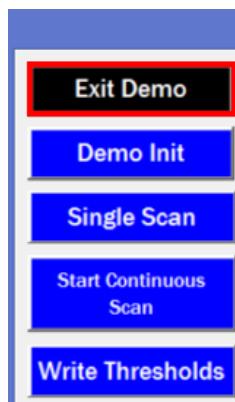

Launching from the VBA editor can open the Demo GUI. Select the **Exit Demo** shown in [Figure 12](#) button to close this and open the Evaluation GUI. The use of the Demo GUI is covered later in this document.

Figure 11. VBA Editor

Figure 12. Exit Demo

### 2.1 Power Supply

Enable the power supply connected to the resistor ladder board (or connect the battery pack). With VBAT set to 48V, the power supply should source ~32mA.

Typical power supplies only source current, this prevents demonstration of charging features using this type of supply. A battery pack or four-quadrant source/sink type of supply is required to demonstrate charging. Only a battery pack is suitable for cell balancing examples.

### 2.2 Connect

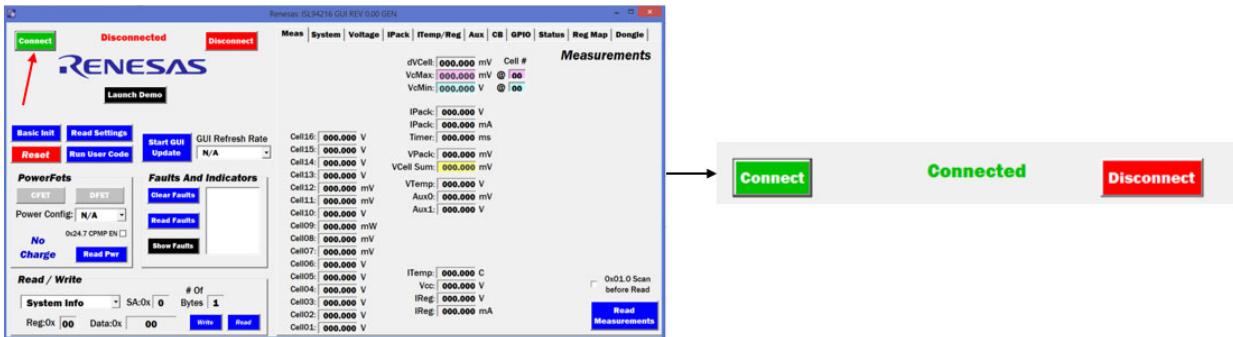

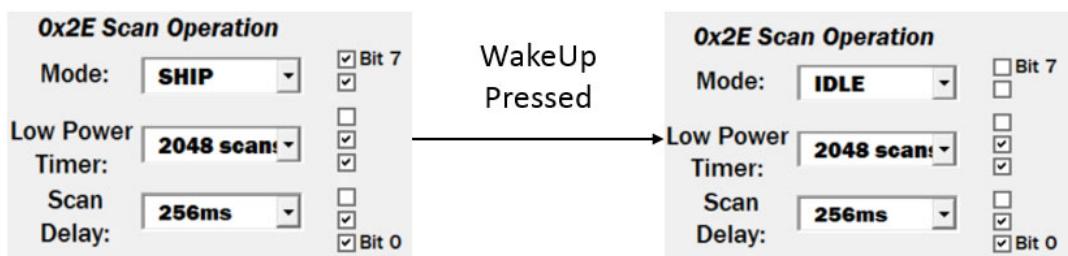

The GUI must detect the dongle is present to operate, this is referred to as the **Connect** step. Insert the USB cable between the dongle and PC, then connect the dongle to the evaluation board. Press the green **Connect** button to start the detection process as shown in [Figure 13](#).

Figure 13. Connect

The device must be powered for this step to complete successfully. If the device is not powered up, an error message is displayed informing you that there was a communication error. When this error occurs you should either unplug then re-plug in the communications dongle, or press the reset button on the dongle (highlighted in [Figure 14](#)).

You must have read/write access permission for the USB port, this might require intervention by your IT resource(s) if **Connect** continuously fails.

Figure 14. Reset Button

## 2.3 Initialization

On startup, the GUI displays that the ISL94216 settings are empty. The ISL94216 has started up in its default configuration (see [ISL94216](#) datasheet). The displays must be synchronized with the ISL94216 by reading the present values from the device into the displays. After this, a basic Initialization is also recommended.

### 2.3.1 Read Settings

Click on the **Read Settings** button on the left side of the GUI to sync the information displayed in the GUI to the settings in the ISL94216. This button operates in all but SHIP Mode.

### 2.3.2 Basic Init

Click on the **Basic Init** button on the top center of the GUI to set the ISL94216 into an operational mode chosen for evaluation purposes. This button automatically synchronizes displays to the settings in the ISL94216 after they are initialized. Basic Init operates regardless of mode as it begins with a hard RESET.

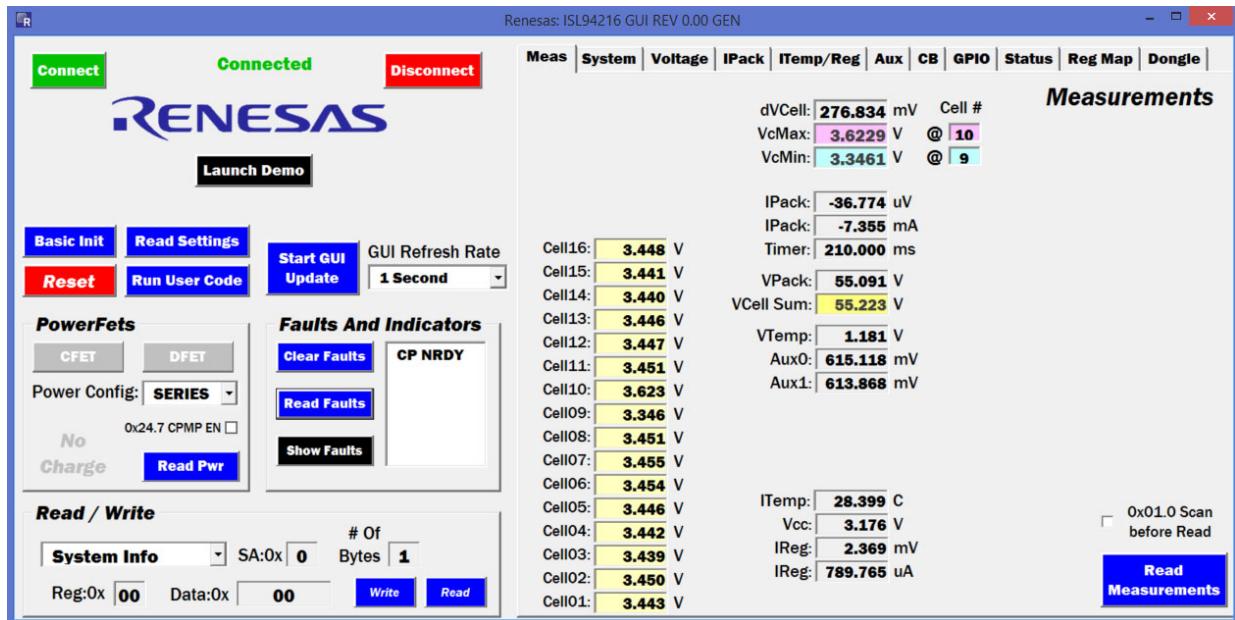

Following execution of Basic Init, the main display is shown in [Figure 15](#):

Figure 15. Main Display Following Execution of Basic Init

Screen captures of Basic Init settings displayed in the tab panels can be found in ["Appendix A" on page 36](#).

### 3. SCAN Mode

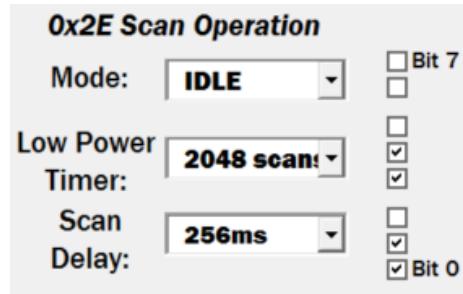

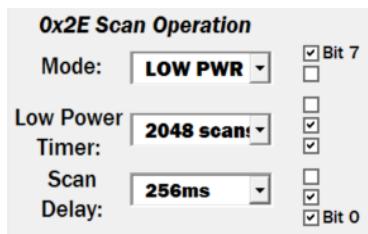

For normal operation during charging or discharging of the Battery Pack, the ISL94216 should be in SCAN Mode. The system Mode is controlled by the Scan Operation register, shown in [Table 1](#) and [Table 2](#). The POR/RESET defaults are highlighted in yellow.

**Table 1. 0x2E Scan Operation**

| Bits     | D[7:6]      | D[5:3]          | D[2:0]     |

|----------|-------------|-----------------|------------|

| Bit Name | System Mode | Low Power Timer | Scan Delay |

| Default  | 00          | 01 1            | 011        |

The System Mode bits are used to manually put the ISL94216 into a specific mode.

**Table 2. SM Mode**

| D[7:6] | SM Mode        |

|--------|----------------|

| 00     | IDLE mode      |

| 01     | SCAN mode      |

| 10     | LOW POWER mode |

| 11     | SHIP mode      |

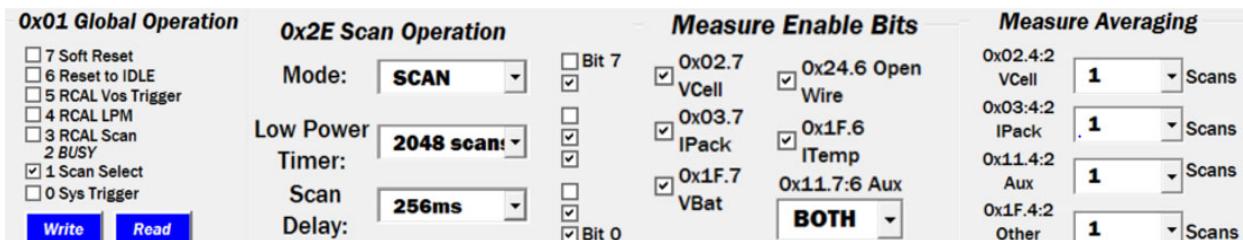

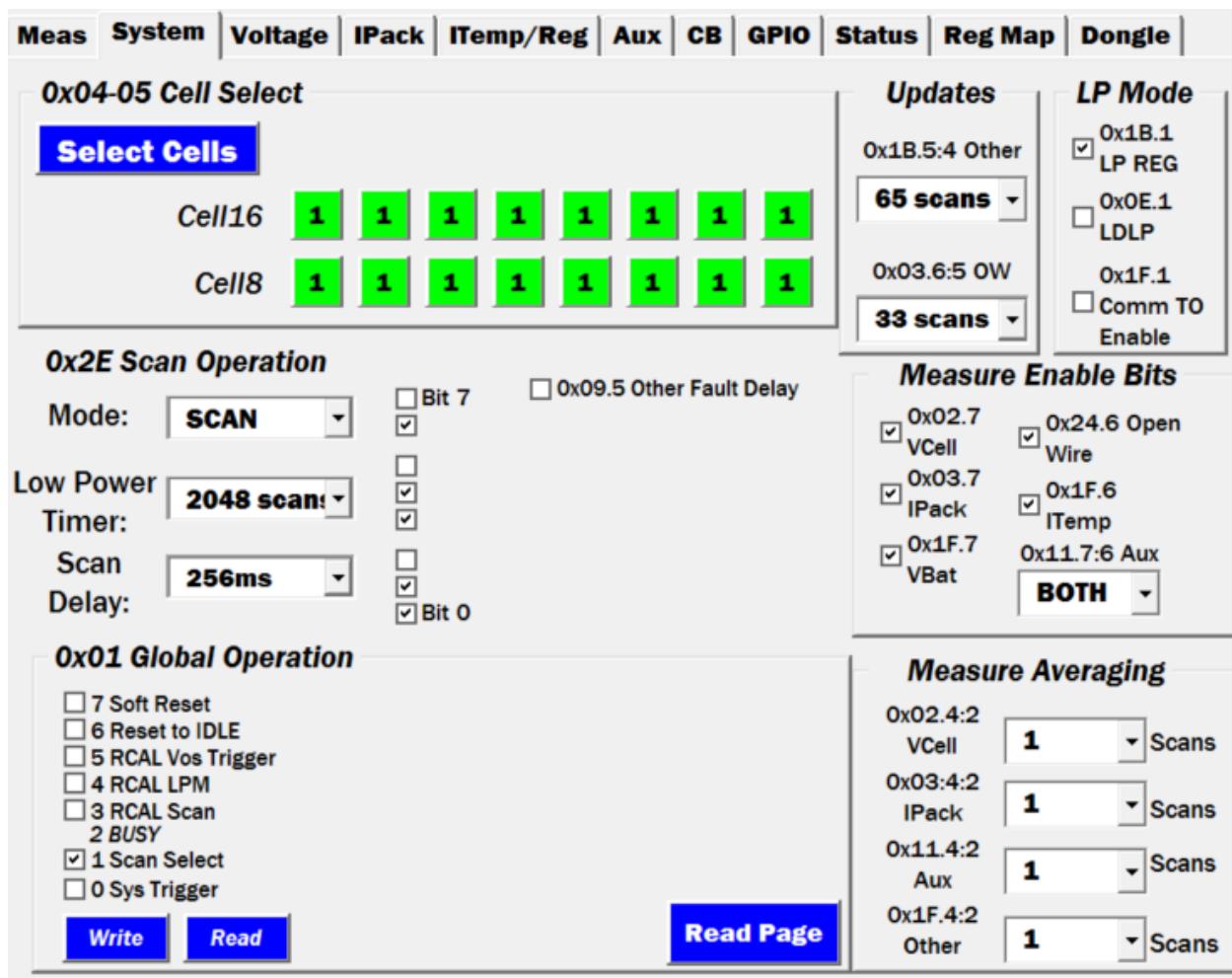

A variety of important controls are changed from the default setting during Basic Init, some are set as shown in [Figure 16](#). These settings can be found on the **System** tab. Review the datasheet descriptions for each of these registers to familiarize yourself with the control functions before proceeding.

**Figure 16. Basic Init**

Bit 1 of the Global Operations register is set to 1 for Single Scan. With this setting, a System Trigger initiates a single measurement scan of all enabled measurements. If Bit 1 is set to 0 when a System Trigger is executed, the device runs Continuous Scans.

All of the Measure Enable Bits are set to enable measurement of all inputs during a system scan. The Measure Averaging setting for the measurements is set to 1.

The System Mode (Bits 7:6 of the Scan Operation register) are set to SCAN Mode. The Scan Delay bits are set to 256ms. Scan Delay only operates when running Continuous Scans. Low Power Timer, the number of scans without a charge or discharge current detection required for the device to transition to low power mode is also shown.

#### 3.1 Busy Bit

The ISL94216 has a read-only bit used to indicate when the device is busy making measurements, bit 2 of the Global Operations register. The bit is 1 when the device is busy measuring and 0 when idle. The bit value status is inverted and output on the ALRT pin if Mask Register 0x65 Bit 0 is set to 0 (done by Basic Init). ALRT is low when the device is busy and transitions high when measurements complete. This bit combined with ALRT is useful for applications and bench debug.

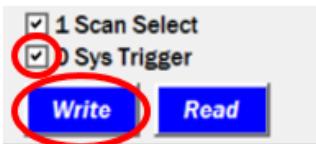

## 3.2 Single System Scans

Select the check box for Bit 0 of the Global Operations register, then click on the **Write** button (Figure 17) to trigger a single system scan while watching ALRT LED D5. With Bits 0 and 1 selected, we are writing 0x03 to this register.

Figure 17. Single Scan

Figure 18. Read

Figure 19. Scan

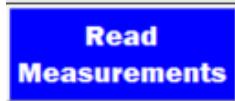

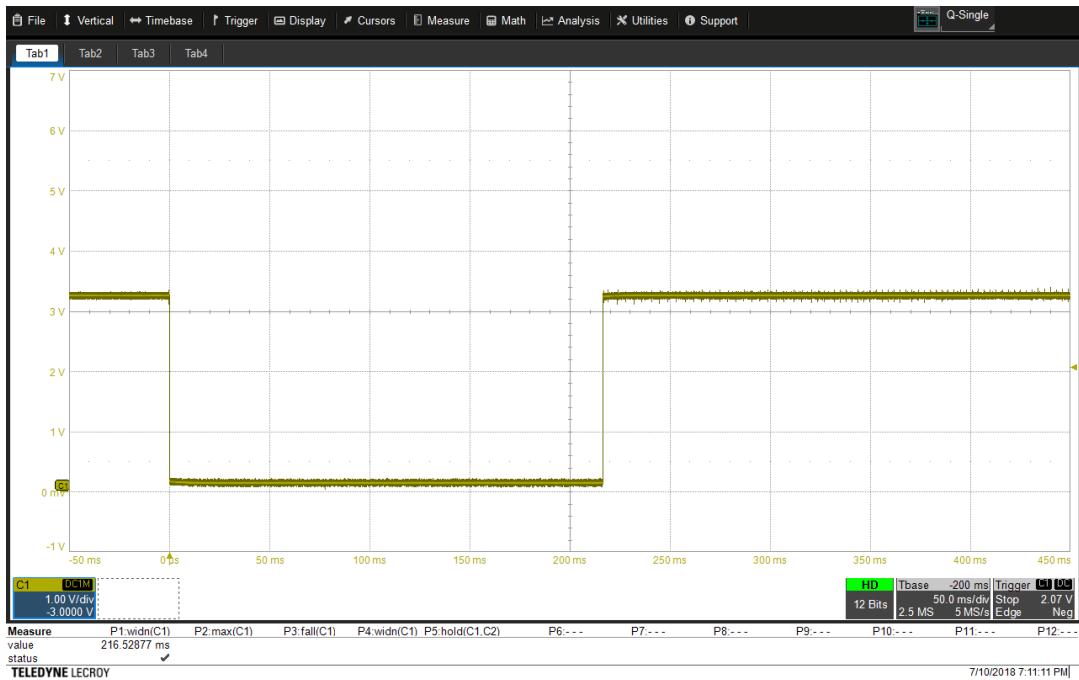

The LED should flash on for approximately 220ms given the Basic Init settings. The single system scan runs all tests on each trigger. Switch to the **Measurement Tab**. Switching tabs automatically performs reads relevant to tab being switched to, so the measurements should automatically update on switching. Additionally, the **Read Measurements** button (Figure 18) can be clicked to confirm that the values were properly read by the GUI.

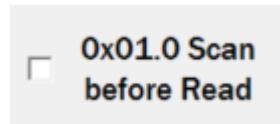

Check the **Scan before Read** box (Figure 19) then click the **Read Measurements** button. This triggers a system scan then displays the results of the measurements. As long as the device is in SCAN Mode and **Scan before Read** is checked, clicking the **Read Measurements** button operates in this manner. The **Scan before Read** box signals the GUI software to send a System Trigger and waits for the measurements to complete, then reads back the results. If the **Scan before Read** box is not checked, the button only executes a read.

### 3.2.1 Measure Enable Bits

As previously shown, the ISL94216 has several measure enable bits that allow you to control what is executed during a system scan. If the enable bits are set to 1, the related measurements are executed during a single system scan. Cell Voltage, IPack, Pack Voltage and Internal Temperature measurements along with Open-Wire detection can all be enabled or disabled. Additionally, there are four options for ETAUX: None, Only Aux0, Only Aux 1, or both. The **Basic Init** function enables all measurements and both thermistors.

If available, connect an oscilloscope probe to the ALRT pin and the ground to one of the DGND pins. Set up the scope to view a signal of 0V to 3.3V and a time span of 400ms to 500ms with a negative edge trigger. If a scope is not available, the ALRT LED is the indicator to be observed.

**Note:** The connection of the oscilloscope ground to the board ground can reset the ISL94216 if the board was floating relative to earth ground prior to this connection. If this happens, execute **Basic Init** to put the ISL94216 back to the required mode and settings. The dongle isolates the evaluation board ground from the PC ground. If the negative terminal of the power supply is not isolated from ground then the evaluation board is not either.

Check the **Scan before Read** box then click the **Read Measurement** button (Figure 15) to trigger a single system scan and display the results of the measurements. The scope capture should look similar to the image in Figure 20.

Figure 20. Oscilloscope Measurement Results

Experiment by disabling all but one Measurement Enable bit to see the busy times for each section.

Also, look at the effect on the measurement time of the averaging settings. The capture in [Figure 20](#) was obtained with all measurements enabled and all averaging set to minimum.

### 3.3 Continuous System Scans

In the Global Operations register, clear all checked bits then click on the **Write** button to write 0x00. Select the **Read** button to read back and confirm the setting. The device is now set for continuous system scans, though we have not triggered it to start.

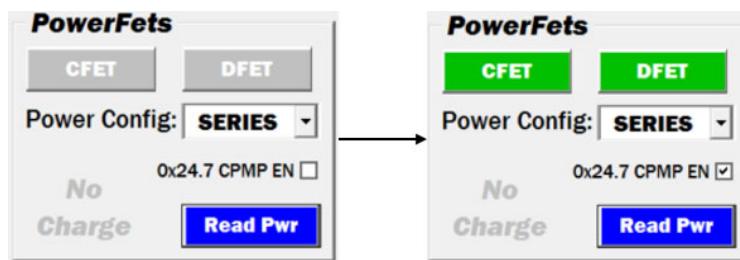

Before beginning continuous scans we will enable the power FETs. Though not required in order to perform continuous system scans, it is necessary to demonstrate the automatic FET response of various faults in the coming sections. To enable the power FETs, locate the **PowerFets** box on the left side of the GUI, check the **0x24.7 CPMP EN** box, which enables the charge pump. Click the **CFET** and **DFET** buttons; they should turn green. Click the **Read Pwr** button and confirm that the CPMP EN box is checked and the **CFET** and **DFET** buttons are green as seen in [Figure 21](#).

Figure 21. Power FETs

Next, check the **Status** tab to see that the status Bit 0x64.5 CP NRDY is now clear.

Select the check box for Bit 0 of the Global Operations register then click on the **Write** button below it to trigger a continuous system scan while watching ALRT LED D5. The LED is flashing because a continuous system scan is now running. With the settings given previously, the LED flashes about every 512ms, and most flashes are for ~35ms. The first and every thirty-third flash is ~220ms. See the Update Other Sweeps section in the datasheet. To

stop the scan, clear all bits of register 0x01 and set (check) Bit 0x01.1 Sys Select, then click on the **Write** button below it. Writing a value of 0x02 to register 0x01 stops the continuous scan.

Any changes to settings that are used as controls or thresholds during system scan (single or continuous) must be made when the system scan is STOPPED.

Experiment with the **Measure Averaging** settings on the **System** tab and note the change in the duration the busy bit sets the **ALRT** output low. Use an oscilloscope to measure the pulse width if one is available.

Be sure to stop the scan by setting Bit 0x01.1 Sys Select before making changes and restarting the scan.

**Table 3. Scan Delay**

| Delay: D[2:0] |   |   | Delay (ms) |

|---------------|---|---|------------|

| 0             | 0 | 0 | 0          |

| 0             | 0 | 1 | 64         |

| 0             | 1 | 0 | 128        |

| 0             | 1 | 1 | 256        |

| 1             | 0 | 0 | 512        |

| 1             | 0 | 1 | 1024       |

| 1             | 1 | 0 | 2048       |

| 1             | 1 | 1 | 4096       |

The Scan Delay bits of the Scan Operation register control the delay time between finishing a System Scan measurement/test sequence in continuous scan mode and starting a new one. The various settings are shown in [Table 3](#). Experiment with the **SCAN DELAY** bit settings in the Scan Operation register and note the change in the delay between **ALRT** output low periods. Remember, the scan must be stopped to make changes to settings used during scan.

Stop the continuous system scan by setting Bit 0x01.1 Sys Select before proceeding to the next step.

### 3.4 Low Power Timer

The Low Power Timer bits select the number of consecutive System Scans with a current reading below the charge and discharge thresholds required before the ISL94216 transitions from SCAN Mode to LOW POWER Mode. [Table 4](#) shows the various Low Power Timer settings.

**Table 4. Low Power Timer**

| Delay: D[5:3] |   |   | Number of Scans |

|---------------|---|---|-----------------|

| 0             | 0 | 0 | OFF             |

| 0             | 0 | 1 | 512             |

| 0             | 1 | 0 | 1024            |

| 0             | 1 | 1 | 2048            |

| 1             | 0 | 0 | 4096            |

| 1             | 0 | 1 | 8192            |

| 1             | 1 | 0 | 16384           |

| 1             | 1 | 1 | 32768           |

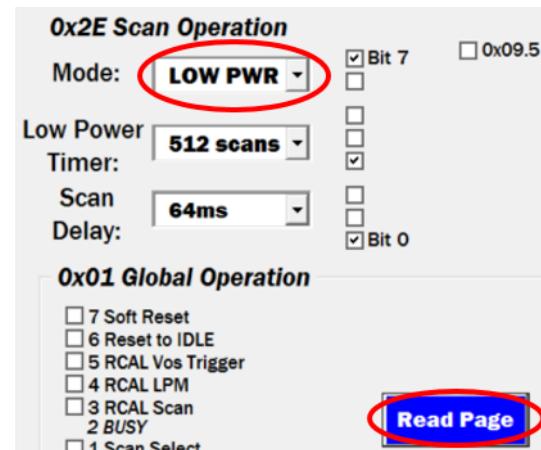

In the **0x2E Scan Operation** area on the **System Tab**, set the mode to SCAN, set the Low Power Timer to 512 scans, and the scan delay to 64ms. With these settings, each scan takes ~100ms. If the IPack voltage is between approximately  $\pm 200\mu\text{V}$  for 512 consecutive scans, the device transitions from SCAN to LOW POWER Mode.

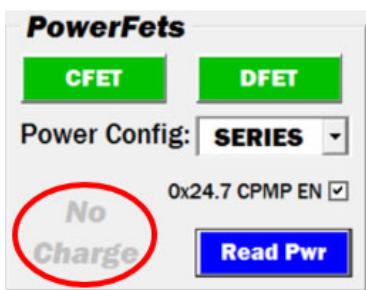

Execute a few single system scans, if the IPack voltage is not within the  $\pm 200\mu\text{V}$  range and/or the indicator in the **PowerFets** block is not **No Charge** as seen in [Figure 22](#), then short out the IPack current sense resistor with a

jumper across the 2-pin CS connector. This should only be done if no significant load is present. It might be necessary to set all S1 switches to OFF.

Set the Global Operations register to 0x01 to trigger a continuous system scan and watch the ALRT LED. After less than 60 seconds, the frequency of the LED flashing significantly decreases to ~2s as the device has transitioned from SCAN to LOW POWER Mode.

Click the **Read Page** button on the system tab and confirm the mode has switched to LOW PWR as shown in [Figure 23](#)

Figure 22. Power FETs

Figure 23. Scan Operation

## 4. IDLE Mode

IDLE Mode is the default mode following POR, RESET, or Reset-to-IDLE. An important difference between IDLE and SCAN Modes is neither continuous nor single system scans can be executed in IDLE Mode. Current direction bits CHRG1 and DCHRG1 do not operate in IDLE Mode, current direction dependent faults will set without regard to the current direction but the MCU is required to enable/disable CFET and DFET in IDLE Mode.

Put the ISL94216 in IDLE Mode. On the **Meas** tab with the **0x01.0 Scan before Read** box checked, click the read measurements button. Note the displays are not updated. Uncheck the **Scan before Read** box then use System Trigger Bit 0x01.0 to execute a system trigger followed by **Read Measurements**. Again the displays are not updated and the ALRT LED does not flash. Leave the **Scan before Read** box unchecked in IDLE Mode.

With the device in IDLE Mode, the individual trigger bits, as opposed to the System Trigger, must be used. The individual trigger bits operate in both SCAN and IDLE Modes.

### 4.1 VCell Trigger

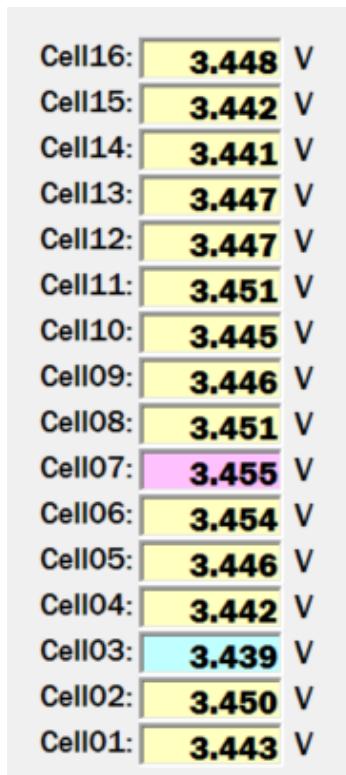

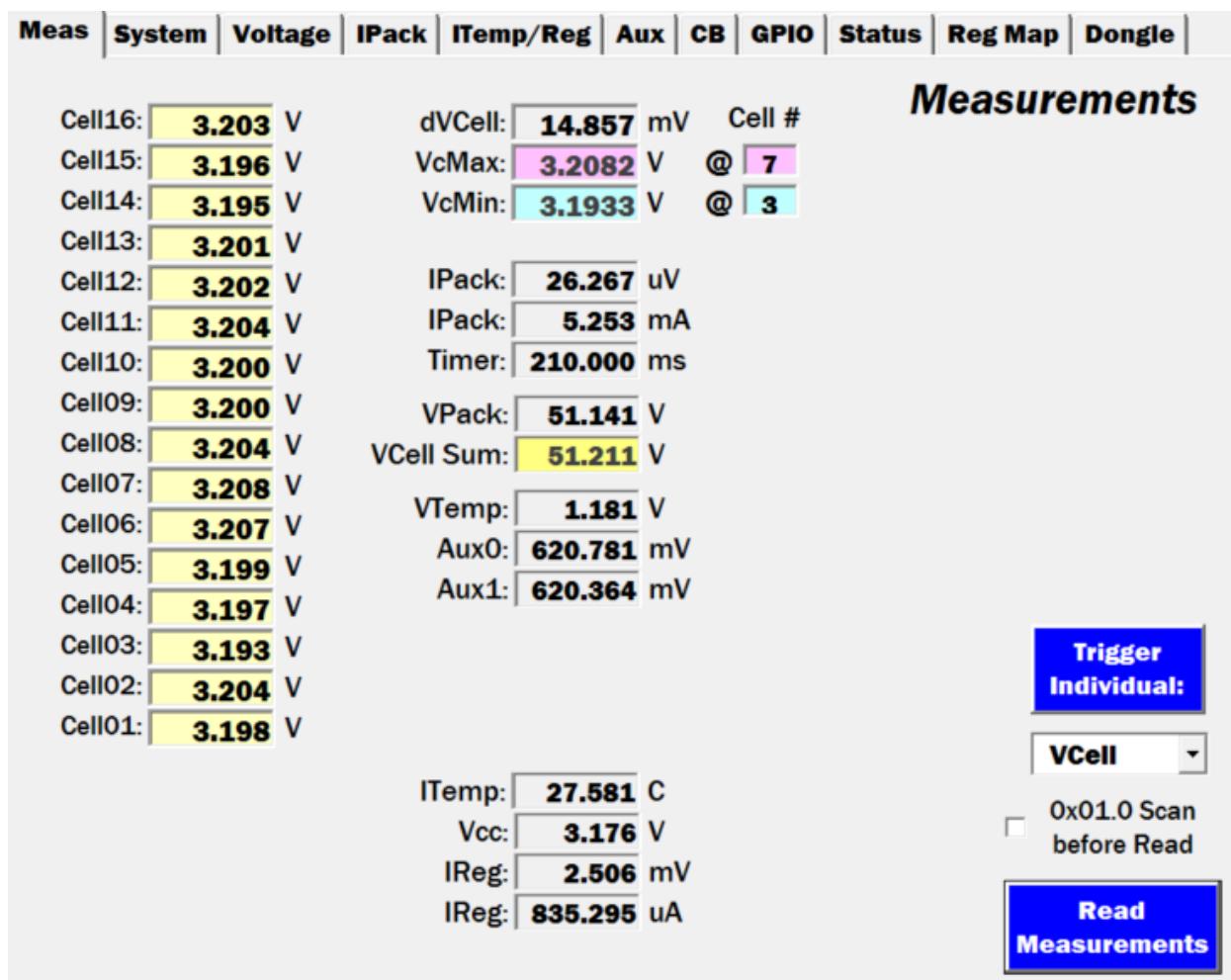

On the **Meas** tab, select **VCell** from the drop-down menu and press the **Trigger Individual** button. This writes a 1 to VCell Operation Bit 0x02.0, which triggers a VCell measurement. The ALRT LED flashes during the measurement. Click **Read Measurements** and note that only the cell voltages, shown in [Figure 24](#), update. On the **System** tab, increase the Measurement Averaging count for VCell to 128. Trigger another VCell Measurement and note that the LED on time has increased, indicating a longer measurement period.

Figure 24. VCell Measure

#### 4.1.1 Cell Select

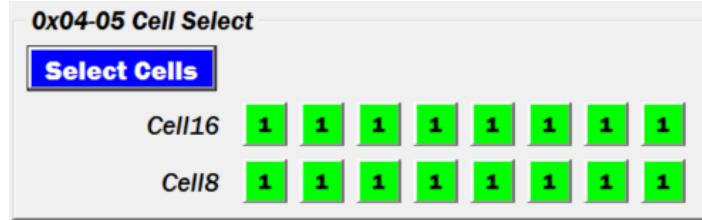

Cell Select register settings (Figure 25) are found on the **System** tab of the GUI.

Figure 25. Cell Select

The Cell Select register sets which and how many cells the ISL94216 manages. If the box (and associated bit) corresponding to a particular cell is 0 and grayed out, that cell is not measured or compared to thresholds.

Clicking on any of the cell boxes toggles between a green box with a 1, and a gray box with a 0. Clicking **Select Cells** writes the displayed selections to registers 0x04 and 0x05. Cells represented by a green box are enabled while cells represented by a gray box are disabled. Toggle the boxes for Cells 8 and 9 to gray, then click the **Select Cells** button.

Trigger a cell voltage measurement. The **ALRT** LED flashes during the measurement. Click **Read Voltages** and note that all of the cell voltages update except Cells 8 and 9.

Enable Cells 8 and 9 before proceeding to the next section.

#### 4.1.2 VCell Fault Detection

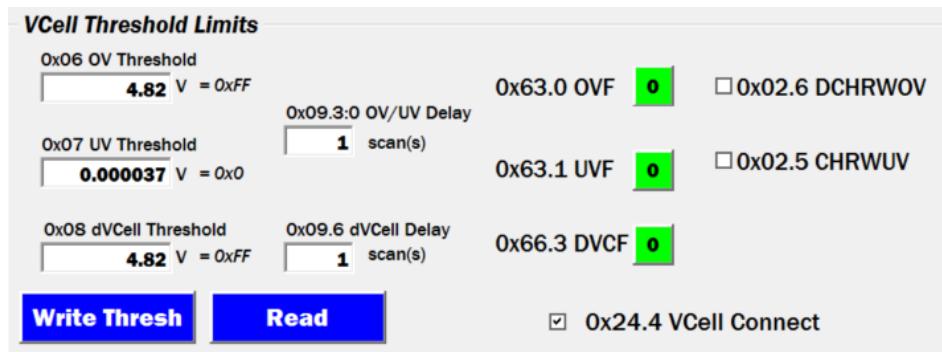

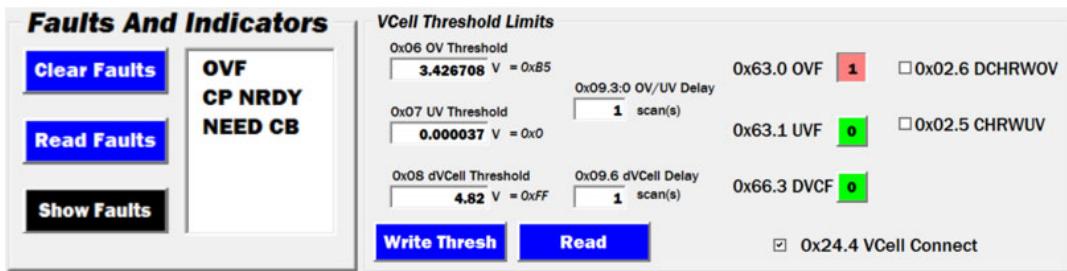

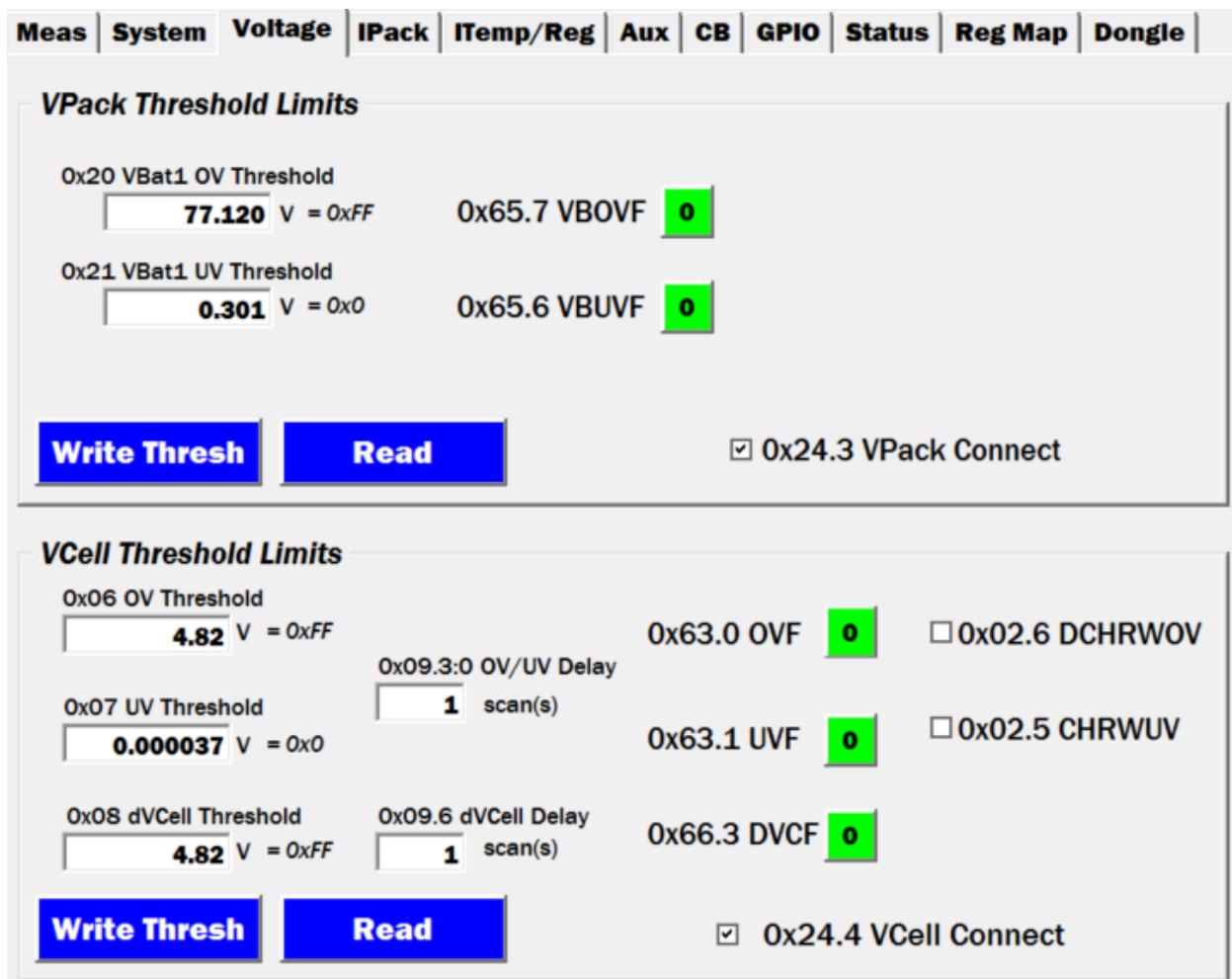

VCell Fault detection threshold register settings (Figure 26) are found on the Voltage tab of the GUI. Figure 26

Figure 26. VCell Thresholds

During cell voltage measurement each enabled cell voltage is compared to both overvoltage (0x06) and undervoltage (0x07) threshold registers. The lowest cell voltage is subtracted from the highest cell voltage and this difference is compared to the VCell Delta Voltage (0x08) threshold. A threshold violation sets the fault bit associated with that threshold.

Enter a voltage in the box labeled 0x06 VCell OV that is less than at least one of the cell voltages, then click on **Write Thresh** and **Read** buttons. The GUI sets the threshold to the closest possible voltage setting without exceeding the entered value. Trigger a cell voltage measurement then **Read Measurements**. Notice the fault is indicated in both the **Faults and Indicators** box and on the VCell Portion of the Voltage tab as shown in Figure 27.

Figure 27. OV Fault

If in SCAN Mode, the Power FETs have been disabled but they remain on if in IDLE Mode. Check the Pack+ voltage on the evaluation board with the multimeter to verify. Press the **Read Pwr** button in the **PowerFets** block.

Figure 28. FET Status (Disabled)

Figure 29. Faults and Status

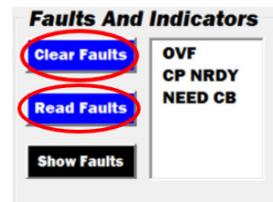

Click on the **Clear Faults** then the **Read Faults** button and note the faults are now cleared. Whenever a **Clear Faults** is performed it should be followed by a **Read Faults** to verify the desired fault has been cleared. This is equivalent to writing a 1 to the VCell Operations register Bit 0x02.1, this bit is adjacent to the VCell Trigger bit.

Re-enable the Power FETs by clicking on the gray **CFET** and **DFET** buttons, they should turn green. Verify with the multimeter. Note the FETs are enabled while there is a cell overvoltage condition. The fault check is a digital compare accomplished during the cell voltage measurement. Trigger another VCell measurement and verify the fault is detected and if the FETs have shut off.

Click on the **Clear Faults** button and note the faults are now cleared. Re-enable the Power FETs by clicking on the red **CFET** and **DFET** buttons, they should return to green. Set the VCell OV Threshold register to 4820mV. Trigger another VCell measurement and verify no fault is detected and the FETs stay on.

Experiment with threshold registers 0x07 UV Threshold and 0x08 Delta VCell Threshold using the previous sequence in both IDLE and SCAN Modes to verify the function of each.

Before proceeding to the next section, click on the **Clear Fault** button and re-enable the Power FETs by clicking on the red **CFET** and **DFET** buttons. Set the VCell OV, UV, and Delta V Threshold registers to default. Trigger another VCell measurement and verify no fault is detected and the FETs stay on.

## 4.2 IPack Trigger

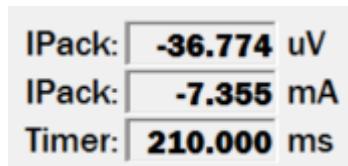

Figure 30. IPack Measure

Trigger a pack current measurement by selecting IPack from the drop-down menu on the **Meas** tab, then pressing **Trigger Individual**. The **ALRT** LED flashes during the measurement. Click **Read Measurements** and note only the IPack current measurements (Figure 30) update. Change the Measure Averaging for IPack on the **System** tab, trigger another measurement and note the LED on time has increased indicating a longer measurement period.

## 4.2.1 IPack Fault Detection

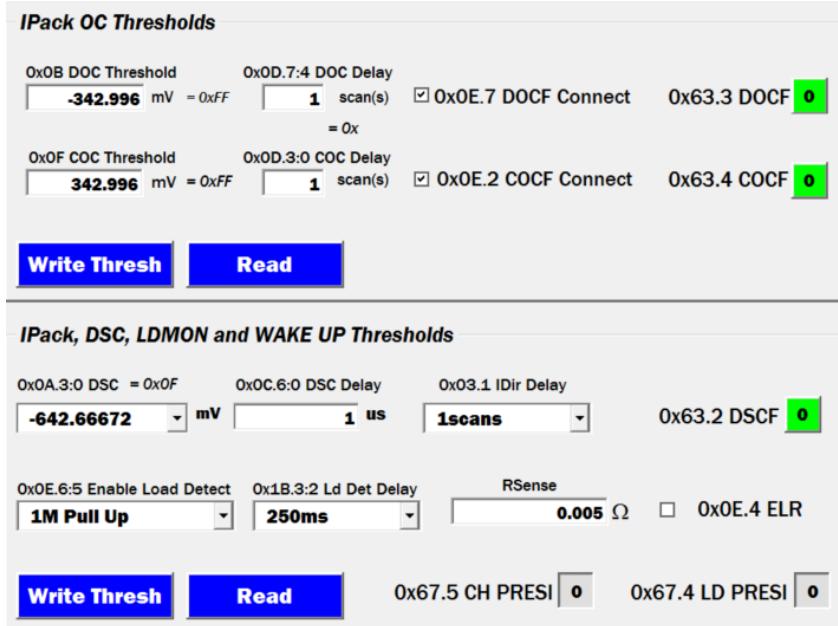

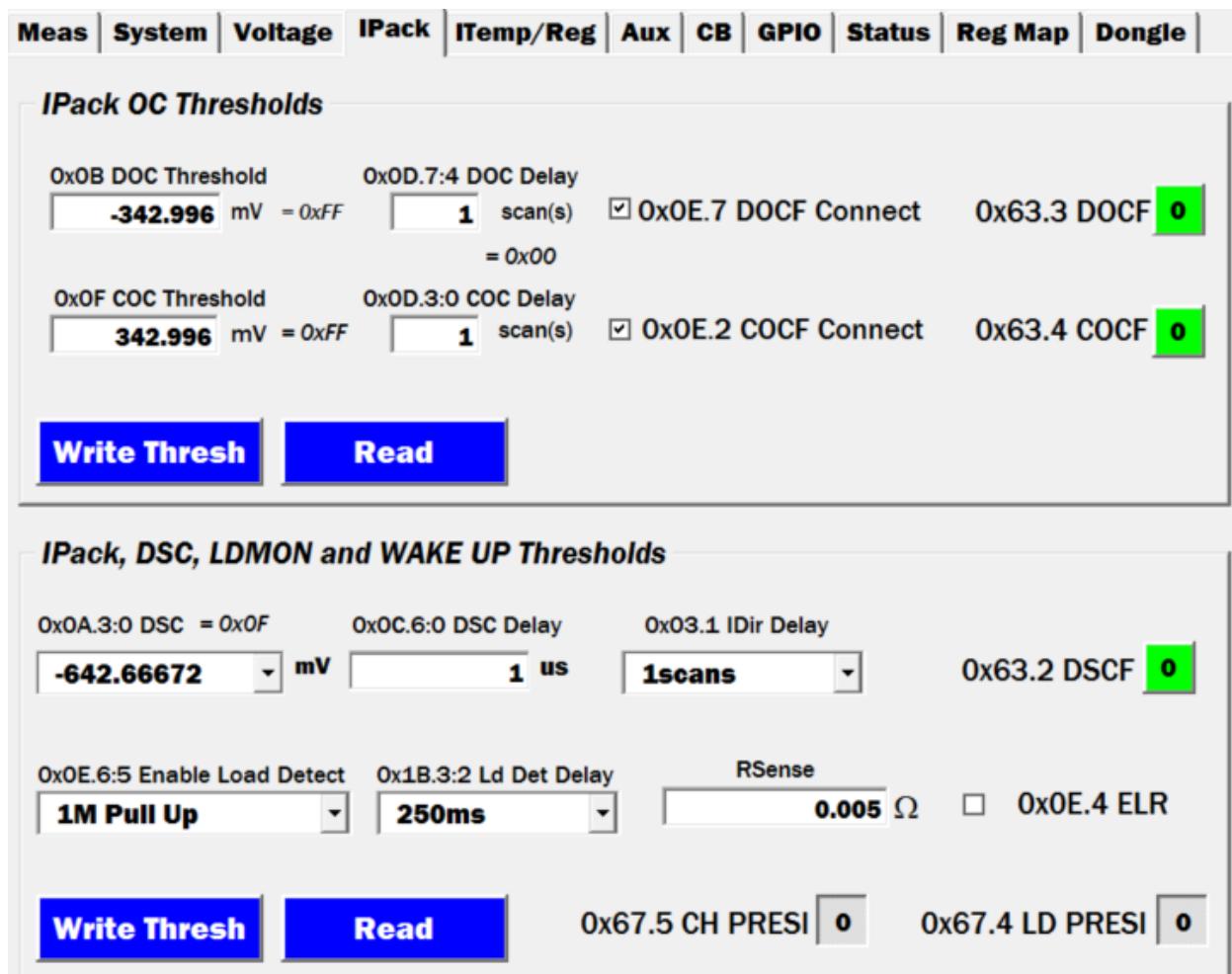

IPack Fault detection threshold register settings (Figure 31) are found on IPack tab of the GUI.

Figure 31. IPack Thresholds

If using a battery pack, most cells are capable of providing the necessary current for the following examples. When a power supply and resistor ladder are used instead of a battery pack, it is necessary to either apply a voltage across the stock current-sense resistor to mimic an overcurrent condition or replace the current-sense resistors with a higher value component so the voltage threshold can be reached with a lower current.

**Note:** The **RSense** setting in the GUI must match the value of the current sense resistance on the evaluation board for the IPack current displayed on the **Meas** tab to be correct. Enter the new value in the box provided and hit the **Write Thresh** button to update. The default value of  $0.005\Omega$  matches the evaluation boards as shipped.

### 4.2.1.1 IPack Voltage Source

For setups using a power supply and resistor ladder, a second power supply connected across IPack can be used to trigger an overcurrent fault. A floating power supply, with the ground pin unconnected, is required for this function. Set the voltage to 0.0V, connect the positive terminal to J3 and the negative terminal to J8 to simulate a charge current.

### 4.2.1.2 COC Fault

Set the Charge Overcurrent Threshold register 0x0F to a voltage achievable with your setup while the IPack voltage is below this threshold. Trigger an IPack measurement then Read the results into the GUI display. No fault should be set. If the IPack voltage is  $>200\mu V$  and the device is in SCAN Mode, the CHRG1 bit (0x67.6) should set indicating the device has detected a charge current. This can be monitored in the Power FETs Block as shown in Figure 32. Step up the IPack current/voltage followed by a **Trigger** and **Read** until the threshold is violated and the COCF Fault bit (0x63.4) sets. The COCF indicator will become red as seen in Figure 33.

Figure 32. PowerFets Block

Figure 33. COCF

This fault is only detected during an IPack measurement, and when detected it shuts off the power FETs if the device is in SCAN Mode and Bit **0xE.2 COCF Connect** is set as in [Figure 33](#).

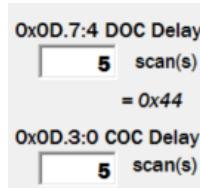

Execute Clear Fault and enable CFET and DFET using the methods previously described. Enter 5 in the two DOC and COC boxes ([Figure 34](#)) and then press Write Thresh to write the setting to their shared register (0x0D).

**Figure 34. DOC and COC Delay**

Put the device in SCAN Mode, trigger a continuous system scan then count the times the **ALRT** LED flashes. With this setting, five consecutive measurements above the threshold are required to trigger a fault, shut off the power FETs, and stop a system scan. These and the other fault counters only operate in continuous scan mode. In all other modes, only a single measurement above the threshold is required to trigger a fault. Automatic shut off of the power FETs only occurs in SCAN Mode as previously described.

Put the device in IDLE Mode, execute Clear Fault and enable CFET and DFET. Set the COC threshold register back to its maximum value.

Remove the charge current, or set the external IPack voltage source to 0.0V then disconnect it (setup dependent).

#### 4.2.1.3 DOC Fault

Set register 0x0B Discharge Overcurrent threshold to a voltage achievable with your setup while the IPack voltage is below this threshold (less negative). Trigger an IPack measurement then Read the results into the GUI display. No fault should be set. If the IPack voltage is  $< -200\mu\text{V}$  and the device is in SCAN Mode, the DCHRI bit (0x67.7) should set indicating the device has detected discharge current. This can be seen in the Power FETs block in [Figure 35](#).

**Figure 35. Power FETs Block**

If your setup uses the IPack voltage source for charge/discharge current, connect the voltage source positive terminal to J8 and the negative terminal to J3. This is reversed from the COC arrangement.

Step up the magnitude of the IPack discharge current/voltage followed by a Trigger and Read until the threshold is violated and the DOCF Fault bit (0x63.3) sets as shown in [Figure 36](#).

**Figure 36. DOCF**

Like COCF, this fault is only detected during an IPack measurement, and when detected in SCAN Mode it shuts off the power FETs given the DOCF Connect Bit 0x0E.7 is set.

Execute Clear Fault and enable CFET and DFET. If previously cleared, enter 5 in the two DOC and COC boxes ([Figure 37](#)) and write them to their shared register (0x0D).

Figure 37. OC Delay

Put the device in SCAN Mode, trigger a continuous system scan then count the times the ALRT LED flashes. With this setting five consecutive measurements above the threshold are required to trigger a fault, shut off the power FETs and stop system scan. These and the other fault counters only operate in continuous scan mode. In all other modes, only a single measurement beyond the threshold is required to trigger a fault. Automatic shut off of the power FETs only occurs in SCAN Mode as previously described.

Put the device in IDLE Mode, execute Clear Fault and enable CFET and DFET. Set the DOC threshold register back to its maximum negative value.

Remove the discharge current, or set the external IPack voltage source to 0.0V then disconnect it (setup dependent).

### 4.3 VREG Trigger

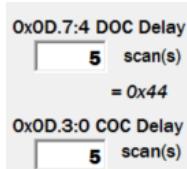

Select the **Meas** tab. Select VReg from the drop-down list then press the **Trigger Individual** button to trigger a regulator voltage measurement. Click **Read Measurements** and note that only the VCC and IREG voltage displays update (Figure 38). Because these voltages are very stable relative to the LSB size, multiple trigger/read cycles can be necessary to see a change in the display.

Figure 38. Reg Measure

The IReg Sense R resistor value is set in the ITemp/Reg tab and is used to calculate the IReg current value displayed on the **Meas** tab. This resistor is 3.3Ω on stock RevC EVKITS. Check R15 on the evaluation board to be certain, it is nearest to the lower right corner of the ISL94216.

#### 4.3.1 VCC Min Threshold

The VCC Minimum Threshold register on the ITemp/Reg tab sets the minimum VCC/VDD operating voltage. If VCC drops below this threshold, the fault Bit 0x63.7 VCCF sets (viewable on the Status Tab).

Figure 39. VCC Min

0x1C VCC Min Threshold

0.01255; V = 0x0

Figure 40. VCC Min and VCCF

0x1C VCC Min Threshold

4.00414; V = 0x9F

0x63.7 VCCF 1

Set the 0x1C VCC Min Threshold to a value greater than the last reading for VCC as shown in Figure 38 and Figure 39. Trigger a VReg measurement using the VReg Trigger then read the voltages and status bits. The VCCF bit should set as seen in Figure 40.

**Note:** After the voltage is measured it is compared to the VCC Min Threshold and the VCCF bit sets, CFET and DFET are turned off. If this occurs during a continuous system scan in SCAN Mode then scan is stopped.

Set the 0x1C VCC Min Threshold to its minimum, execute Clear Fault and enable CFET and DFET.

### 4.3.2 IReg OC1 Threshold

The Regulator Overcurrent 1 threshold register on the ITemp/Reg tab sets the maximum regulator current threshold when the device is in either SCAN or IDLE Mode. The threshold setting is compared to the voltage across the IREG sense resistor R15. If the current through the sense resistor causes the voltage to violate this threshold, fault Bit 0x67.2 IREG1 sets.

Set the 0x1D IRegOC1 Threshold ([Figure 41](#)) to a value less than the last reading for IREG (as shown in [Figure 38](#) on the previous page). On the **Meas** tab, select VReg from the drop-down list and then press Trigger Individual to trigger a VReg measurement. Press **Read Measurements** to read back the result.

Figure 41. IRegOC1 Threshold

Figure 42. IREG1F

After the voltage is measured, it is compared to the VReg Min Threshold and the IREG1 fault bit sets ([Figure 42](#)), CFET and DFET are turned off. If this occurs during a continuous system scan in SCAN Mode, the scans also stop.

Setting LED switches S1 to ON and setting the GPIO pins low (see [Figure 80](#)) increases the regulator current.

Set the 0x1D IRegOC1 Threshold to its maximum, execute Clear Fault and enable CFET and DFET.

### 4.3.3 IReg OC2 Threshold

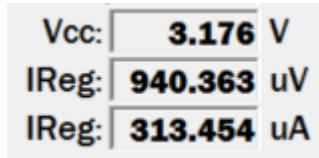

The Regulator Overcurrent 2 threshold register on the ITemp/Reg tab ([Figure 43](#)) sets the maximum regulator current threshold when the device is in LOW POWER Mode. The threshold setting is compared to the voltage across the IReg sense resistor. If the current through the sense resistor causes the voltage to violate this threshold, fault Bit 0x67.1 IReg2 sets.

Figure 43. IReg OC2

Set the 0x1E IRegOC2 Threshold to a value less than the last reading for IReg as previously shown. Trigger a VReg measurement using the VReg Trigger then read the voltages and status bits. Because this threshold is only active in LOW POWER Mode and the device is in IDLE Mode, the voltage updates but no fault is detected. At this point make sure the measured voltage is greater than the set threshold voltage.

Put the device in LOW POWER Mode by selecting **LOW PWR** from the Mode drop-down menu on the **System** tab and watch the ALRT LED. Press the **Read Faults** button on the first flash. If the threshold is violated, the IREG2 bit sets as shown in [Figure 44](#) within ~256ms.

**Note:** Bit 0x65.5 CP NRDY also sets. This occurs if the charge pump was enabled prior to the transition to LOW POWER Mode and was not triggered by the IREG2 fault.

Figure 44. IREG2 Fault

Put the device in **IDLE Mode** by selecting **IDLE** from the Mode drop-down menu on the **System** tab then press **Read Page** on the system tab to confirm the mode was switched successfully. The Bit 0x65.5 CP NRDY clears automatically, CFET and DFET turn back on but IREG2 remains set.

Set the 0x1E IREGOC2 Threshold to its maximum and execute Clear Faults.

#### 4.4 VBAT/ITEMP Triggers

On the **Meas** tab select **VBat** from the drop-down list to trigger an individual measurement. Click **Read Measurements** and note that only the VPack display updates. On the **System** tab increase the Measure Averaging Value for **Other**. Perform another individual VBat measurement and note the increase in the amount of time the ALRT LED is on. On the **Meas** tab select **ITemp** from the drop-down list and then press the **Trigger Individual** button. Perform a read measurement and note that only the ITemp value updates.

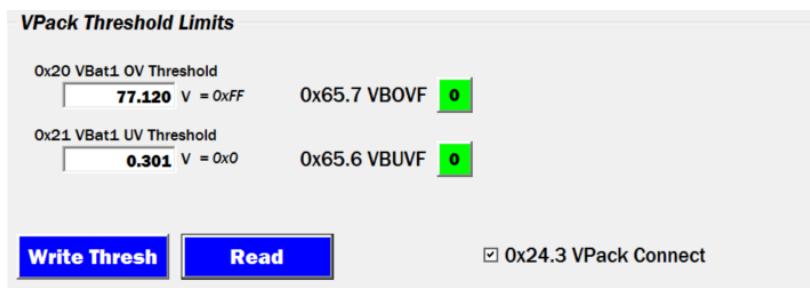

##### 4.4.1 VBAT1 OV Threshold

The Vbat1 Overvoltage Threshold register sets the maximum voltage for the VBAT1 pin voltage, exceeding this voltage during charging in SCAN Mode sets the Bit 0x65.7 VBOVF and shuts off the power FETs.

Trigger an Individual VBat measurement and read back the results.

On the **Voltage** tab, in the VPack Threshold Limits section shown in [Figure 45](#), set register 0x20 BAT1 OV to a voltage less than the measured result.

Figure 45. VBat1 OV

Trigger another VBAT voltage measurement and read back the results, VBOVF is now set as seen in [Figure 46](#).

Figure 46. VBOVF

If the device is charging (CHRG1 is set), CFET and DFET shuts off. If running in continuous scan, the scan stops. If discharging or neither, the FETs stay on. Verify this by experiment.

Set the 0x20 OVBAT1 to its maximum, execute Clear Fault, enable CFET and DFET and put the device back into IDLE Mode.

##### 4.4.2 VBAT1 UV Threshold

The Vbat1 Undervoltage Threshold register sets the minimum voltage for the VBAT1 pin voltage, dropping below this voltage during discharge in SCAN Mode sets the Bit 0x65.6 VBUVF and shuts off the power FETs.

On the **Meas** tab, select **VBat** from the drop-down list and then press **Trigger Individual**. Read Measurements and notice the VPack result updates.

On the **Voltage** tab, adjust the value of **0x21 VBat1 UV Threshold** to a voltage greater than the measured result. Then press **Write Thresh** to write the setting to the device, followed by a **Read** to confirm the setting was set properly.

Figure 47. VBUVF

Trigger another VBAT voltage measurement and read back the results, VBUVF is now set as shown in [Figure 47](#). All Fault and status bits are also viewable on the Status tab.

If the device is discharging (DCHRG1 is set), CFET and DFET shut off. If running in continuous scan, the scan stops. If charging or neither, the FETs stay on. Verify this by experiment.

Set the 0x21 UVBAT1 to its minimum, execute Clear Fault, enable CFET and DFET and put the device back into IDLE Mode.

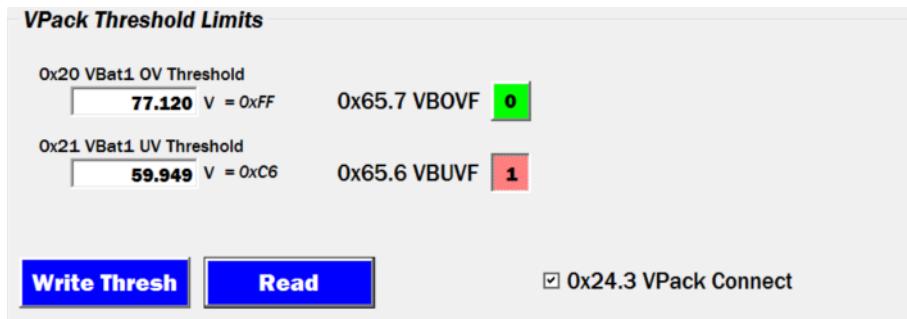

#### 4.4.3 Internal Temperature

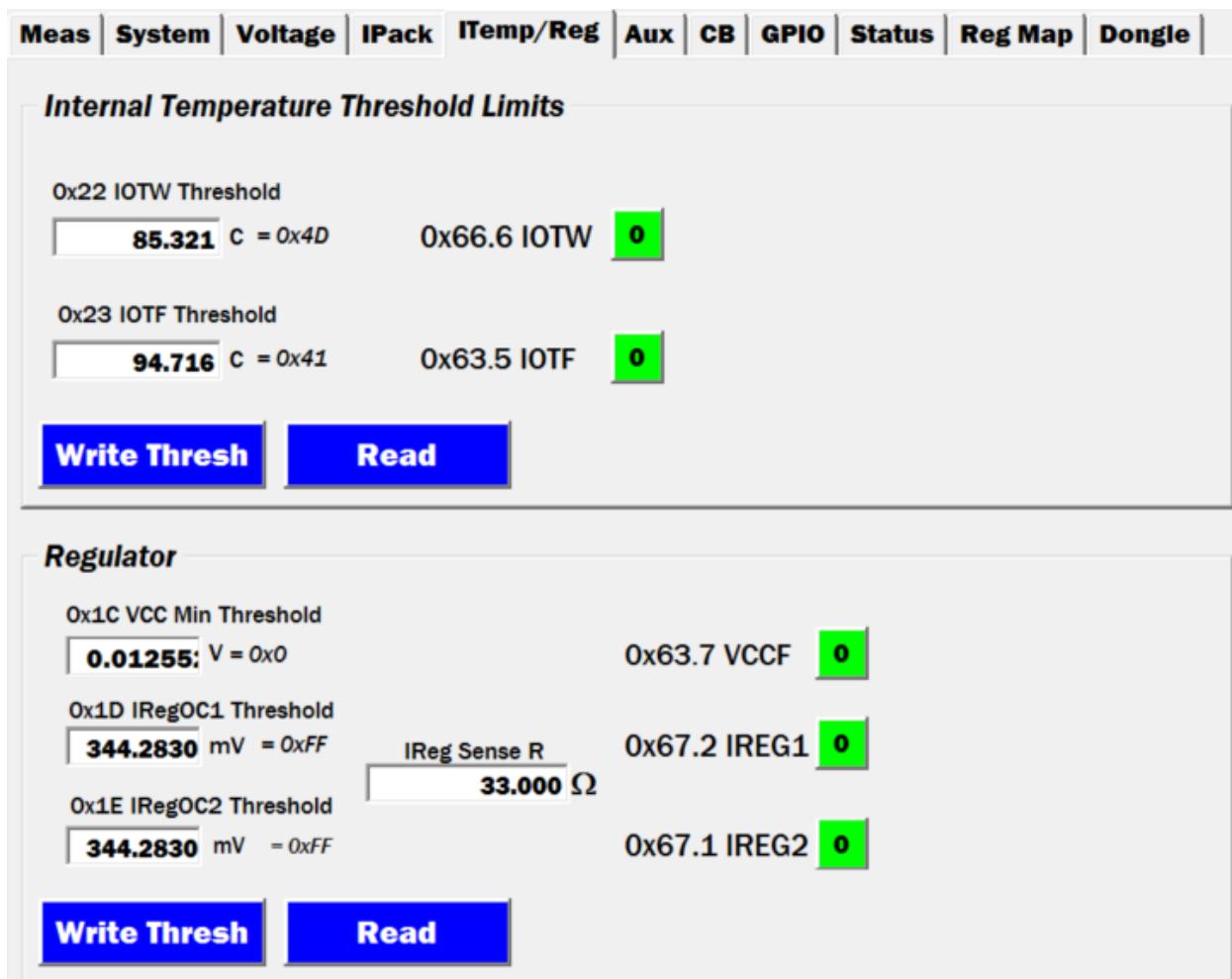

The ISL94216 has an internal temperature sensor with two programmable over-temperature thresholds, a warning and a fault. The trigger for internal temperature sensor measurement and the result display was covered previously. The thresholds are on the **ITemp/Reg** tab shown in [Figure 48](#).

Figure 48. IOTW and IOTF

##### 4.4.3.1 IOTW Threshold

On the **Meas** tab, select **ITemp** from the drop-down menu then press **Trigger Individual**. Select **Read Measurements** and note the **ITemp** value. On the **ITemp/Reg** tab set **0x22 IOTW Threshold** to about 10 degrees less than the previously returned **ITemp** value. Perform **Write Thresh** followed by a **Read** to confirm the setting.

Trigger another internal temperature measurement, then **Read Measurements** and note the **IOTW** bit is set as seen in [Figure 49](#).

Figure 49. IOTW

This is intended as a warning bit, it does not shut off the power FETs or stop continuous system scans.

#### 4.4.3.2 IOTF Threshold

On the **ITemp/Reg** tab, set **0x23 IOTF Threshold** to about 5° less than the **ITemp** display value then perform a **Write Thresh** followed by a **Read** to set and confirm the threshold.

Trigger another internal temperature measurement, then Read Voltages and note the IOTF bit is set as seen in [Figure 50](#).

Figure 50. IOTF

This is the internal temperature fault bit, if set it shuts off the power FETs and stops continuous system scans. Verify these fault bits are also set on the **Status** tab.

Set register 0x22 IOTW Threshold to about 85° and register 0x23 IOTF Threshold to about 95°. Trigger another internal temperature measurement, then Read Voltages and note the IOTW and IOTF bits remain set. While the IOTF bit is set the power FETs cannot be turned on and scan does not start. Use the Clear Fault function, then trigger another measurement. Both IOTW and IOTF are now clear and the FETs can be turned on, if the FETs are off turn them back on to verify.

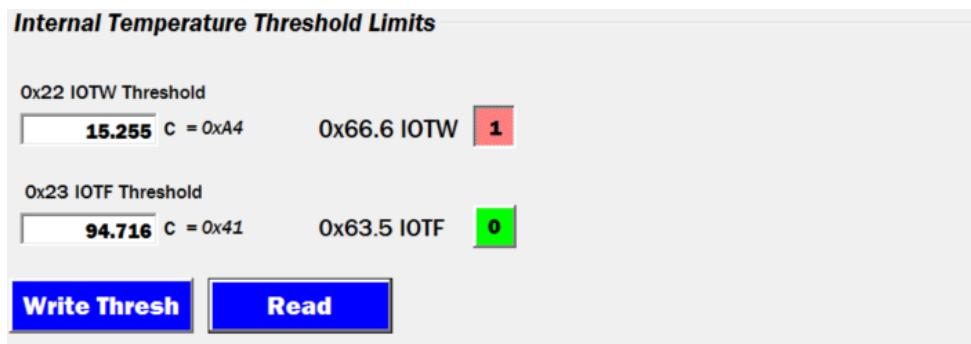

## 4.5 COMM Timeout

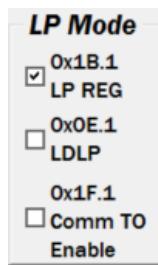

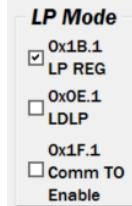

The VBAT Control register includes a communications timeout bit at 0x1F.1. On the System tab in the top Right corner check **0x1F.1 Comm TO Enable** to enable the ISL94216 to react to an unexpected loss of communications with the MCU. This check box is highlighted in [Figure 51](#).

Put the device in **IDLE Mode** by selecting **IDLE** from the drop-down **Mode** menu on the **System** tab as shown in [Figure 52](#).

Figure 51. Comm TO

Figure 52. IDLE Mode

After approximately 4s without communications the device transitions from IDLE to LOW POWER Mode. After this happens, the ALRT LED flashes approximately every 2s. Verify the Mode change by reading register 0x2E.

Put the device in IDLE Mode by selecting it from the drop-down menu, then uncheck the **Comm TO Enable** box to disable the Timeout function.

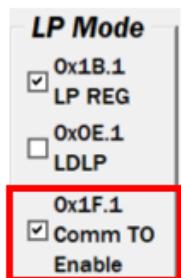

## 5. LOW POWER Mode

Put the device in LOW POWER Mode by selecting **LOW PWR** from the Mode drop-down menu on the **System** tab as shown in [Figure 53](#).

Figure 53. LP Mode

As stated previously, while in this mode the **ALRT** LED flashes every ~2s while the ISL94216 powers up necessary circuitry to make measurements, then powers down again.

Click on the **Read Voltages** button a few times and note the results. Measurement results are not stored in the data registers in LOW POWER Mode, but they are compared to Fault thresholds (see datasheet). On exit from LP Mode the last results obtained are stored in the data registers if transitioning to SCAN or IDLE.

### 5.1 Strong/Weak Regulator

Figure 54. LP Reg

On the **System** tab, confirm that **0x1B.1 LP REG** is checked as shown in [Figure 54](#). The bit should already be set as part of the Basic Init operation. Connect a voltmeter to either of the ISL94216 power pins, VDD or VCC. The voltage reads ~3.3V throughout the ~2s measurement cycle.

Now uncheck 0x1B.1 to and monitor the voltage with an oscilloscope. The voltage reads ~3.3V during the short measurement period, then drops to ~2.3V during the idle time between measurements.

The Strong regulator operates at ~3.3V with the external transistor in the feedback loop.

The Weak regulator operates at ~2.3V and it excludes the external transistor. The Weak regulator is only intended to drive the ISL94216 with enough voltage/current to maintain the register settings and communications. The Weak regulator is not able to drive external circuitry.

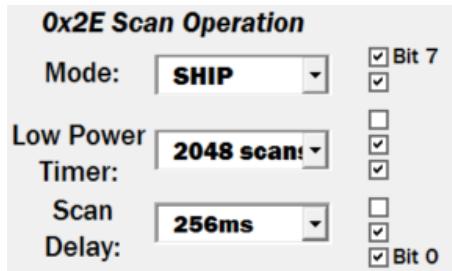

## 6. SHIP Mode

Put the device in SHIP Mode by selecting **SHIP** from the Mode drop-down menu on the System tab as shown in [Figure 55](#).

Figure 55. SHIP Mode

Click on the **Read Voltages** button and note the results. While in SHIP Mode the IC does nothing but wait for a WAKEUP or a RESET assertion or a change mode command. All reads or writes that do not access the Scan Operation register return a NACK. The GUI interprets this as junk data when updating the display.

### 6.1 Strong/Weak Regulator

Figure 56. LP Reg

Put the device in **IDLE Mode** by selecting **IDLE** from the Mode drop-down menu on the **System** tab as shown in [Figure 55](#). Confirm the box **0x1B.1 LP REG** is checked. Connect a voltmeter to either of the ISL94216 power pins, VDD or VCC, to monitor the supply voltage. Set all LED switches to OFF to remove this component of the supply current.

Put the device in SHIP Mode by selecting **SHIP** from the Mode drop-down menu. The supply voltage reads ~3.3V since the strong regulator remains on in **SHIP Mode** if the **LP REG** Bit 0x1B.1 is set to 1.

Note the supply current. Disconnect the dongle from the evaluation board, do not execute any GUI functions with the dongle disconnected. Note the supply current again. Reconnect the dongle. This example demonstrates the dongle draws current from the ISL94216 evaluation board, which is not part of the normal evaluation board current.

Put the device in **IDLE Mode** by setting Scan Operation Bits 0x2E.7:6 to 00 on the **System** tab. Uncheck the **0x1B.1 LP REG** box on the **System** tab.

Put the device in SHIP Mode by selecting from the Mode drop-down menu. The supply voltage reads ~2.4V because the weak regulator is on in SHIP Mode if the **LOW PWR REG SEL** Bit 0x1B.1 is set to 0.

Note the supply current. Disconnect the dongle from the evaluation board, do not execute any GUI functions with the dongle disconnected. Note the supply current again. Reconnect the dongle.

### 6.2 Wakeup

Continuing from the previous section, the ISL94216 should be in SHIP Mode with the weak regulator active. Press the **Read Page** button on the **System** tab to read the settings, including the Scan Operation Register.

Press the **WAKEUP#** button (NOT RESET#) on the evaluation board and then perform another **Read Page** on the system tab. Note the mode has returned to IDLE as seen in [Figure 57](#).

Figure 57. Wake Up

## 7. Demonstration GUI

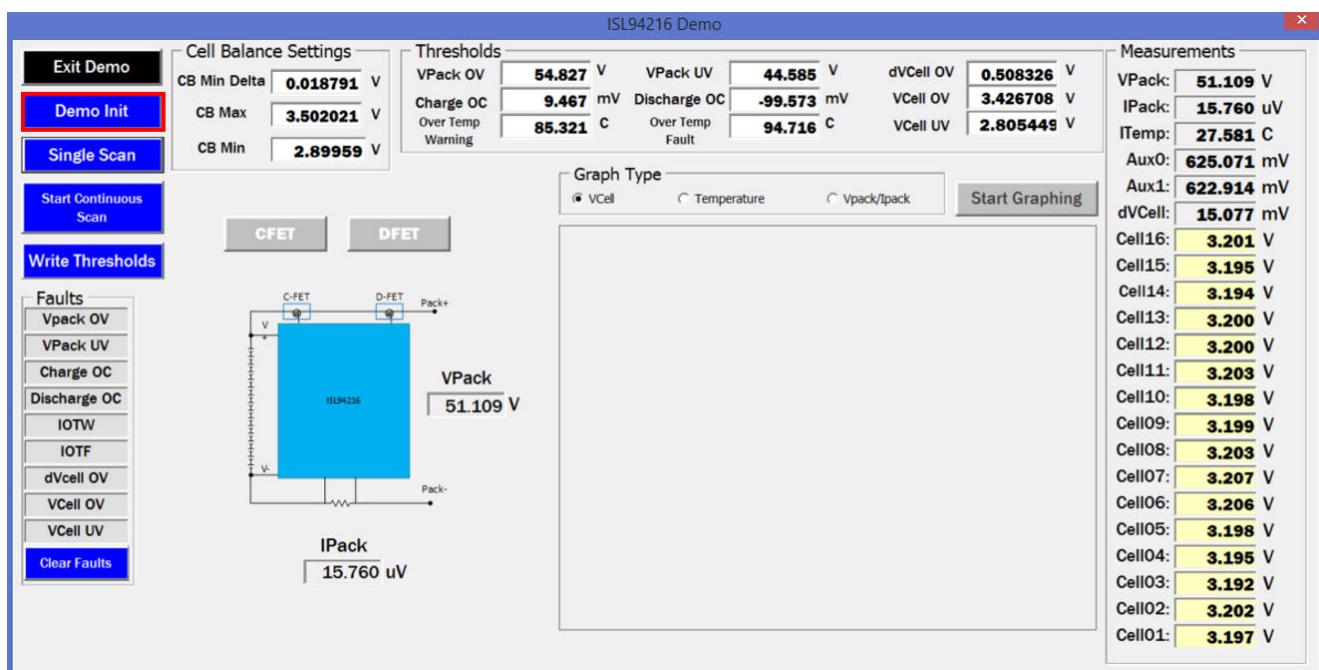

Built into the full Evaluation GUI, there is also a demonstration GUI designed to highlight some of the key features and behaviors of the ISL94216.

### 7.1 Launching the Demo GUI

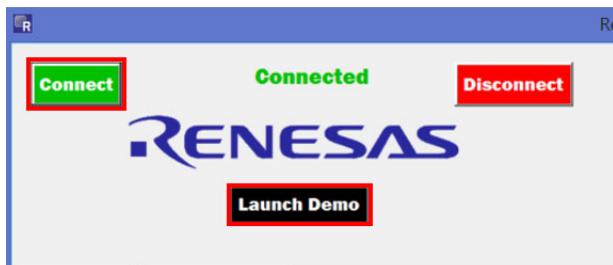

To launch the demo GUI, first press the green **Connect** button. If the device is not connected, the demo GUI does not launch and you are prompted with an error message. After connecting, press the **Launch Demo** button to bring up the demo GUI. This sequence is highlighted in [Figure 58](#).

Figure 58. Connect

### 7.2 Initializing the Demo GUI

After launching the demo GUI, press the **Demo Init** button on the left side of the GUI as highlighted in [Figure 59](#). This configures the ISL94216 with settings appropriate for demonstration, and reads these settings into the GUI.

Figure 59. Demo GUI

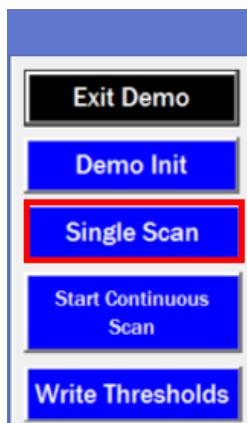

### 7.3 Demo Single Scan

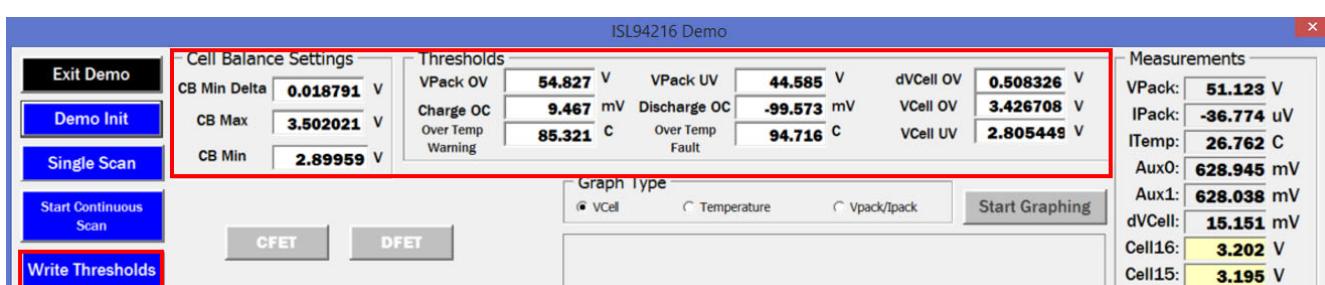

The **Single Scan** button, highlighted in [Figure 60](#), performs a single system scan and reads back all relevant information into the demo GUI. This includes not only the measurements, but the faults/status bits, thresholds, and any other information displayed in the demo GUI.

Figure 60. Single Scan

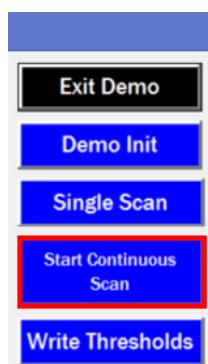

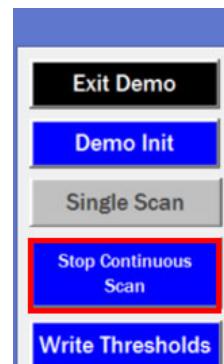

## 7.4 Demo Continuous Scan

The demo GUI also offers the ability to start and monitor a continuous scan in the ISL94216. To do this, press the **Start Continuous Scan** button, shown in [Figure 61](#).

When the continuous scan has begun, the GUI updates approximately every two seconds with information from the previous scan. To prevent the system trigger bit from getting stuck, the Single Scan function is disabled while a continuous scan is running. To stop the continuous scan, press the **Stop Continuous Scan** button shown in [Figure 62](#).

Figure 61. Start Continuous Scan

Figure 62. Stop Continuous Scan

## 7.5 Demo Graphing

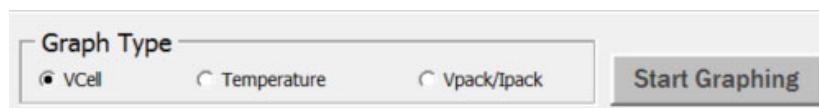

The demonstration GUI enables graphing of measurements of interest versus time.

**Note:** The graphing function generates an image in the directory in which the workbook is stored to work properly.

To use the graphing function a continuous scan must be in progress, otherwise the **Start Graphing** button is grayed out and locked as seen in [Figure 63](#).

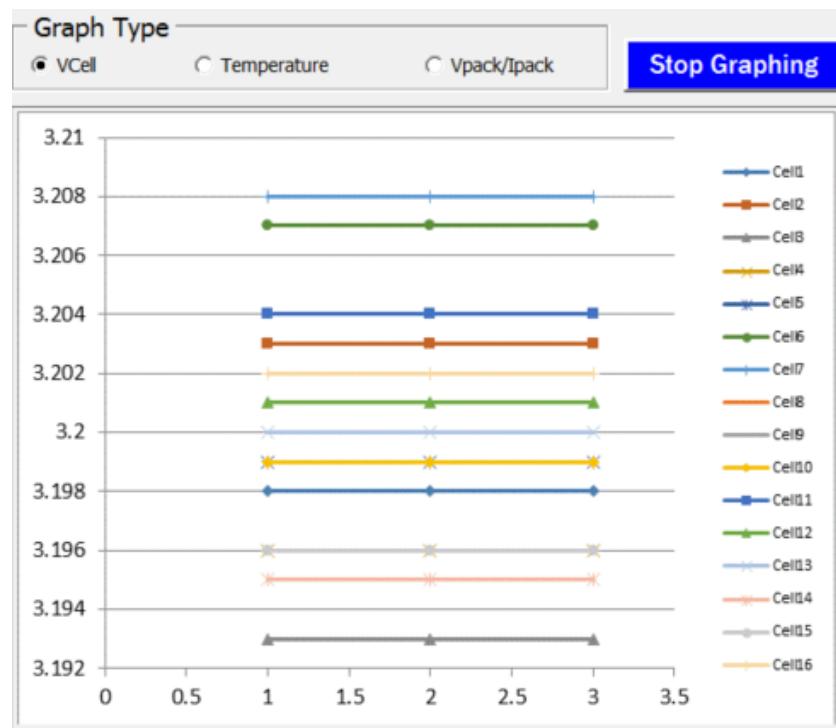

Figure 63. Graph Type

The Graph displays information based on which option is selected in the **Graph Type** section. The VCell option displays the voltage of each cell, the temperature option shows both internal and auxiliary temperatures, and the VPack/IPack option shows the VPack and IPack values. When graphing has started you can freely switch between the three Graph Types without erasing the data for any of them. An example of a VCell graph is shown in [Figure 64](#).

Figure 64. VCell Graph

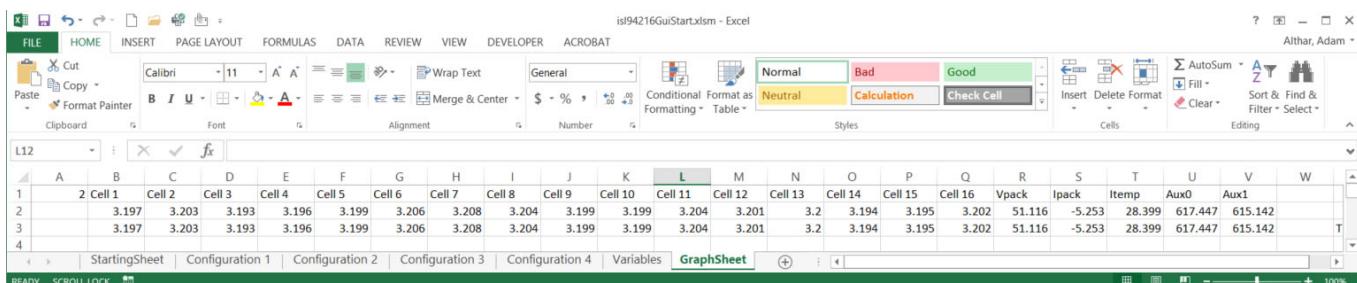

If you wish to look more closely at the data that is used to make the graphs, it can be seen on the **Graph Sheet** tab (Figure 65) of the GUI workbook. This data gets erased every time **Start Graphing** is pressed.

Figure 65. Graph Sheet

## 7.6 Demo Threshold Modification

**Demo Init** sets some of the key thresholds in the ISL94216 to values more useful than that of the default values, but these values might need to be modified further. To modify any of the available settings, simply change the value in the boxes highlighted in Figure 66, then press the **Write Thresholds** button. A single scan can be used to confirm the settings were written correctly.

Figure 66. Demo Thresholds

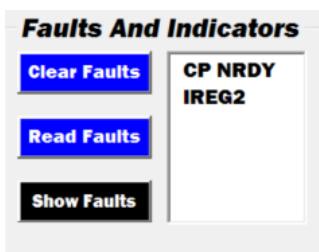

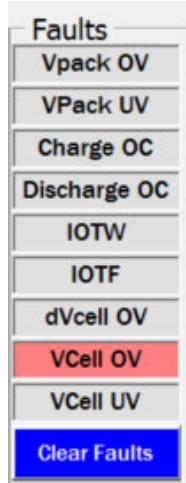

## 7.7 Demo Fault Indicators/Clearing

The bottom left side of the screen provides fault indicators. If any of the faults listed are detected during a system scan, the corresponding fault box turns red. This can be seen in [Figure 67](#) for VCell OV. Pressing **clear faults** writes these bits to 0. However, keep in mind some faults cannot be written low while the fault condition persists.

Figure 67. Demo Faults

## 7.8 Exiting the Demo GUI

To return to the evaluation GUI from the demonstration GUI simply press the **Exit Demo** button in the top left corner of the display. This button is highlighted in [Figure 68](#).

Figure 68. Exit Demo

## 8. Appendix A

The values displayed in the following images are the device settings following Basic Init.

- The **Reg Map** tab ([Figure 69](#)) displays the values of all of the user registers in hex

- The **Read All Reg** button reads the registers from the device and updates the GUI with these values.

- The **Write All Reg** button writes the GUI displayed values to the device registers.

- The **Read Sheet** button updates the register map with the data stored in the configuration sheet corresponding to whichever option is selected in the **Sheet Select** box. This only updates the values displayed in the **Register Map** tab of the GUI, it does not change the values in the device.

- The **Write To Sheet** button modifies the configuration sheet corresponding to the **Sheet Select** option with values from the GUI **Register Map**. Examine the Configuration sheets carefully, as not every register is contained within them.

| Meas                | System     | Voltage    | IPack      | ITemp/Reg  | Aux        | CB | GPIO | Status | Reg Map | Dongle |

|---------------------|------------|------------|------------|------------|------------|----|------|--------|---------|--------|

| <b>Register Map</b> |            |            |            |            |            |    |      |        |         |        |

| 0x00: 0xF0          | 0x15: 0xFF | 0x2A: 0x00 | 0x3F: 0x43 | 0x54: 0x00 | 0x69: 0x00 |    |      |        |         |        |

| 0x01: 0x02          | 0x16: 0x00 | 0x2B: 0xFF | 0x40: 0xB7 | 0x55: 0x00 | 0x83: 0xFF |    |      |        |         |        |

| 0x02: 0x80          | 0x17: 0xFF | 0x2C: 0x00 | 0x41: 0x05 | 0x56: 0x00 | 0x84: 0xFF |    |      |        |         |        |

| 0x03: 0x80          | 0x18: 0x00 | 0x2D: 0xFF | 0x42: 0xB7 | 0x57: 0x0E | 0x85: 0xFE |    |      |        |         |        |

| 0x04: 0xFF          | 0x19: 0xFF | 0x2E: 0x5B | 0x43: 0x06 | 0x58: 0x63 | 0x86: 0xFF |    |      |        |         |        |

| 0x05: 0xFF          | 0x1A: 0x00 | 0x2F: 0x00 | 0x44: 0xB7 | 0x59: 0x8F | 0x87: 0xFF |    |      |        |         |        |

| 0x06: 0xFF          | 0x1B: 0x32 | 0x30: 0xB6 | 0x45: 0x49 | 0x5A: 0x63 | 0x88: 0xFF |    |      |        |         |        |

| 0x07: 0x00          | 0x1C: 0x00 | 0x31: 0xE7 | 0x46: 0xB7 | 0x5B: 0x6F | 0x89: 0xFF |    |      |        |         |        |

| 0x08: 0xFF          | 0x1D: 0xFF | 0x32: 0xB7 | 0x47: 0x1F | 0x5C: 0xB6 |            |    |      |        |         |        |

| 0x09: 0x00          | 0x1E: 0xFF | 0x33: 0x42 | 0x48: 0xB7 | 0x5D: 0xF8 |            |    |      |        |         |        |

| 0x0A: 0x0F          | 0x1F: 0xC0 | 0x34: 0xB6 | 0x49: 0x11 | 0x5E: 0x95 |            |    |      |        |         |        |

| 0x0B: 0xFF          | 0x20: 0xFF | 0x35: 0xA7 | 0x4A: 0xB6 | 0x5F: 0x78 |            |    |      |        |         |        |

| 0x0C: 0x00          | 0x21: 0x00 | 0x36: 0xB6 | 0x4B: 0xC1 | 0x60: 0x7E |            |    |      |        |         |        |

| 0x0D: 0x00          | 0x22: 0x4D | 0x37: 0xD6 | 0x4C: 0xB6 | 0x61: 0x0D |            |    |      |        |         |        |

| 0x0E: 0xB4          | 0x23: 0x41 | 0x38: 0xB7 | 0x4D: 0xD1 | 0x62: 0xE8 |            |    |      |        |         |        |

| 0x0F: 0xFF          | 0x24: 0x5C | 0x39: 0x00 | 0x4E: 0xB7 | 0x63: 0x00 |            |    |      |        |         |        |

| 0x10: 0x00          | 0x25: 0x01 | 0x3A: 0xB7 | 0x4F: 0x2F | 0x64: 0x00 |            |    |      |        |         |        |

| 0x11: 0xC0          | 0x26: 0x00 | 0x3B: 0x6F | 0x50: 0x00 | 0x65: 0x20 |            |    |      |        |         |        |

| 0x12: 0x1F          | 0x27: 0x00 | 0x3C: 0xB7 | 0x51: 0xD8 | 0x66: 0x01 |            |    |      |        |         |        |

| 0x13: 0xFF          | 0x28: 0x00 | 0x3D: 0x7F | 0x52: 0xFF | 0x67: 0x00 |            |    |      |        |         |        |

| 0x14: 0x00          | 0x29: 0x00 | 0x3E: 0xB7 | 0x53: 0xFC | 0x68: 0x00 |            |    |      |        |         |        |

Figure 69. Reg Map Tab

The Configuration sheets ([Figure 70](#)) can be found in the excel workbook that contains the GUI. These sheets allow you to save and access multiple complete device configurations and switch between them quickly.

| StartingSheet | Configuration 1        | Configuration 2 | Configuration 3 | Configuration 4 | Variables | GraphSheet |

|---------------|------------------------|-----------------|-----------------|-----------------|-----------|------------|

|               | <b>Configuration 1</b> |                 |                 |                 |           |            |

Figure 70. Configuration Tabs

Figure 71. MEAS Tab

The **Meas** tab (Figure 71) allows you to see the ISL94216 measurement results obtained during a system or an individual triggered scan.

The IPack current is calculated by dividing the IPack voltage by the RSense resistor value stored on the **IPack** tab.

The IReg current is calculated by dividing the IReg voltage by the IReg Sense R resistor value on the **ITemp/Reg** tab.

Figure 72. System Tab

The **System** tab (Figure 72) contains various settings related to overall system behavior. These include which cells are enabled, the Scan and Global operations registers, which measurements are enabled during a scan, Low Power Mode Options, Measure Averaging Options, and how frequently certain values are updated during a continuous scan.

Figure 73. Voltage Tab

The **Voltage** tab (Figure 73) allows you to view and change various thresholds and settings related to both Pack and Cell voltage settings. For VPack, you can set the Pack Overvoltage and Undervoltage fault thresholds, and VPack Connect allows you to control if these faults disable the power FETs. For VCell, you can set the Cell Overvoltage and Undervoltage thresholds, and the maximum cell differential voltage. Also, you can control how many consecutive scans a Cell OV/UV or Cell Delta Voltage fault must be detected before the fault bit is set. When VCell Connect is enabled, it allows detections of OFV, UVF, and DVCF to turn off the Power FETs. DCHRWOV allows discharging while a cell overvoltage condition is present and CHRWUV allows charging while a cell undervoltage condition is present.

Figure 74. IPack Tab

The **IPack** tab (Figure 74) contains various IPack control options. The **IPack OC Thresholds** section allows you to view and adjust settings related to charge overcurrent and discharge overcurrent conditions. The **IPack, DSC, LDMON and WAKE UP Thresholds** allow you to adjust other pack current and load detection related settings.

Importantly, this is where you can set the RSense value that the GUI uses to calculate the current displayed on the **Meas** tab. Press **Write Thresh** to move the new values into the device after changing them on the GUI.

Figure 75. ITEMP/Reg Tab

The **ITemp/Reg** tab (Figure 75) allows you to view and modify settings related to the internal temperature fault thresholds and regulator thresholds.

The IReg Sense R resistor value is set in this tab, which is used to calculate the IReg current value displayed on the **Meas** tab. Press **Write Thresh** to store the value after changing it. This resistor is  $3.3\Omega$  on stock RevC EVKIts. Check R15 on the evaluation board to be certain, it is nearest to the lower right corner of the ISL94216.

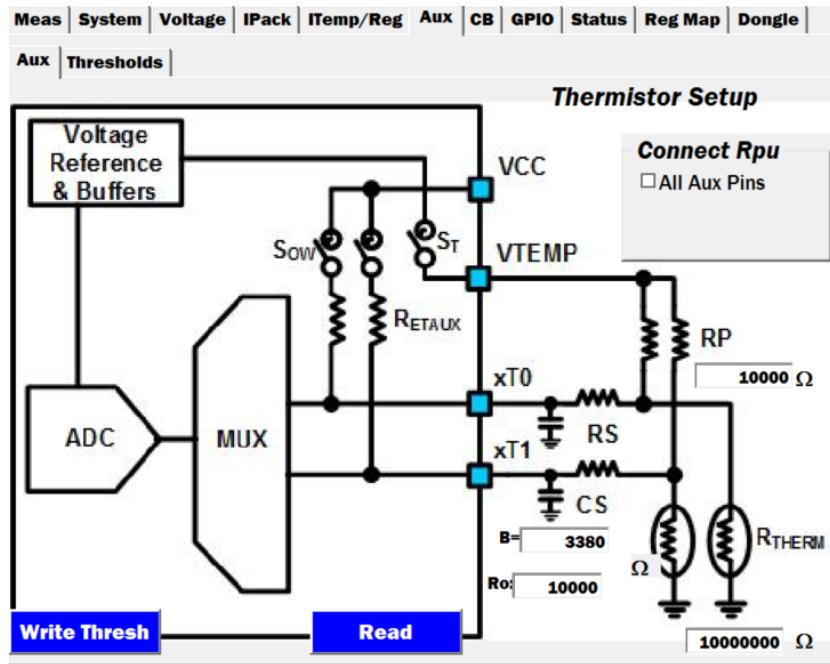

Figure 76. AUX/AUX tab

The **Aux** tab is composed of two sub-tabs related to the external thermistors.

The **Aux** sub-tab (Figure 76) allows you to view and modify various component values related to the thermistors.

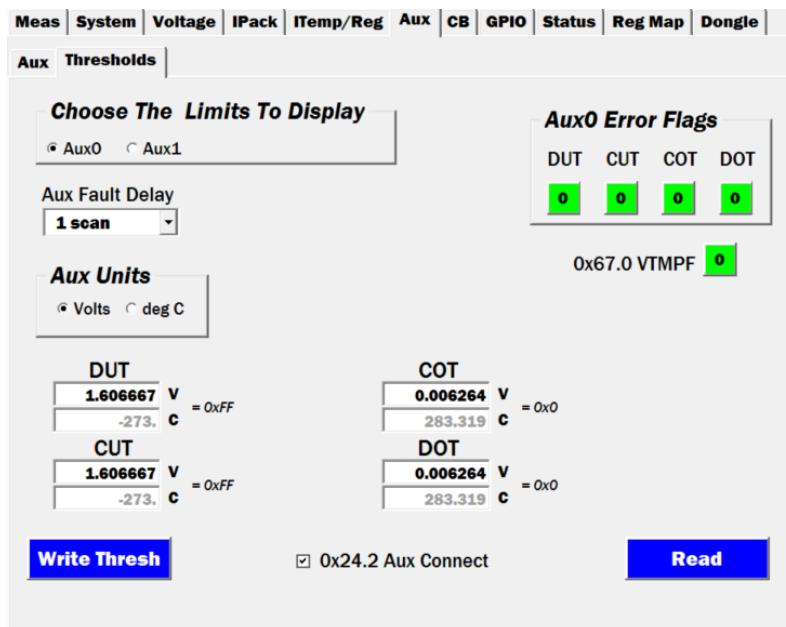

Figure 77. AUX Thresholds Tab

The **Thresholds** sub-tab (Figure 77) allows you to view and modify various auxiliary related fault settings. Aux Connect controls if an Aux related fault disables the power FETs.

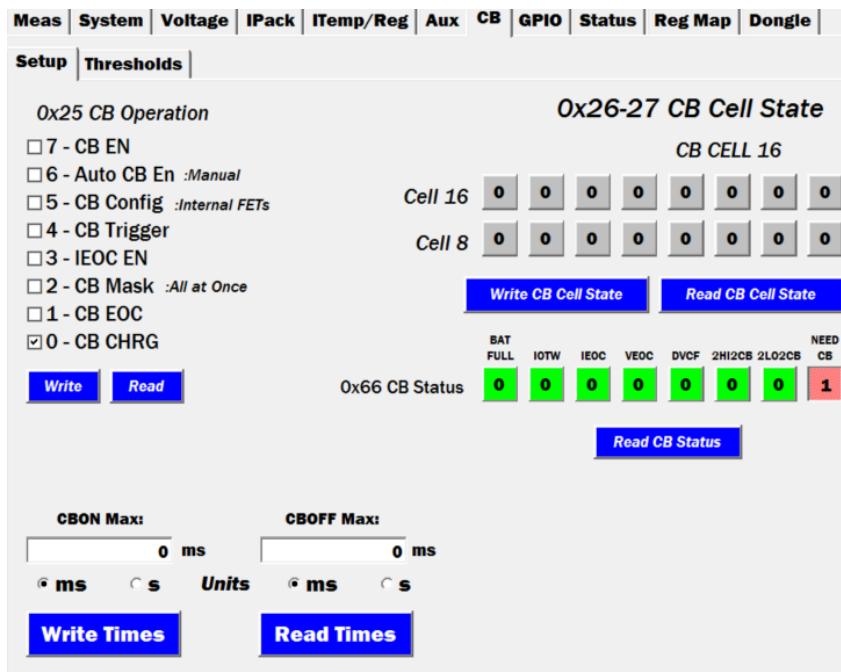

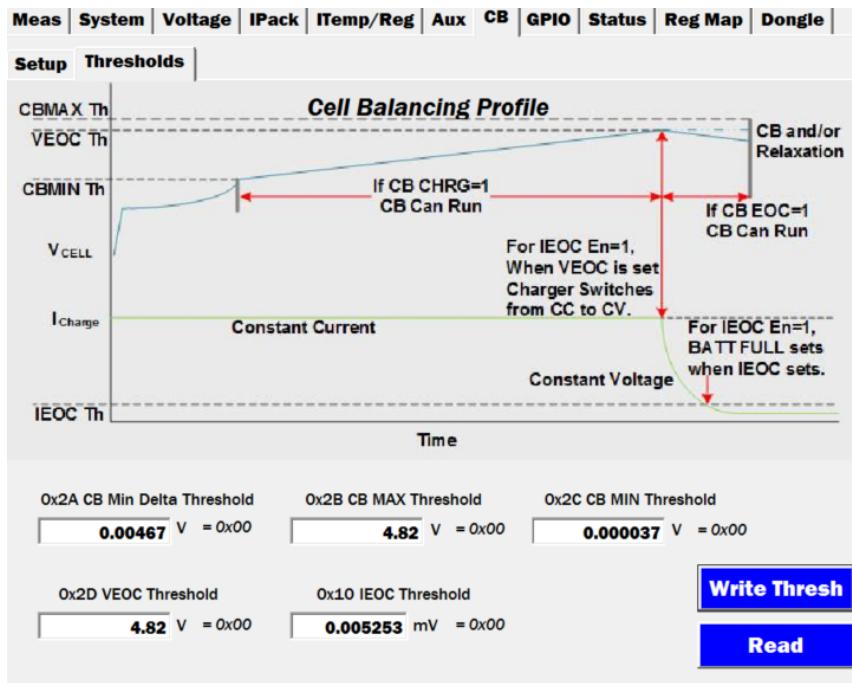

Figure 78. CB Setup Tab

The **CB** tab is composed of two Cell Balancing related sub-tabs.

The **Setup** sub-tab (Figure 78) allows you to view and adjust various cell balancing related settings. Importantly, this is where the CB Operation register is controlled from. To understand how this register controls Cell Balancing consult the datasheet.

Figure 79. CB Thresholds Tab

The **Thresholds** sub-tab (Figure 79) allows you to view and adjust various cell balancing and charging related thresholds. There is also a charging profile that provides insight into what each of these thresholds represents.

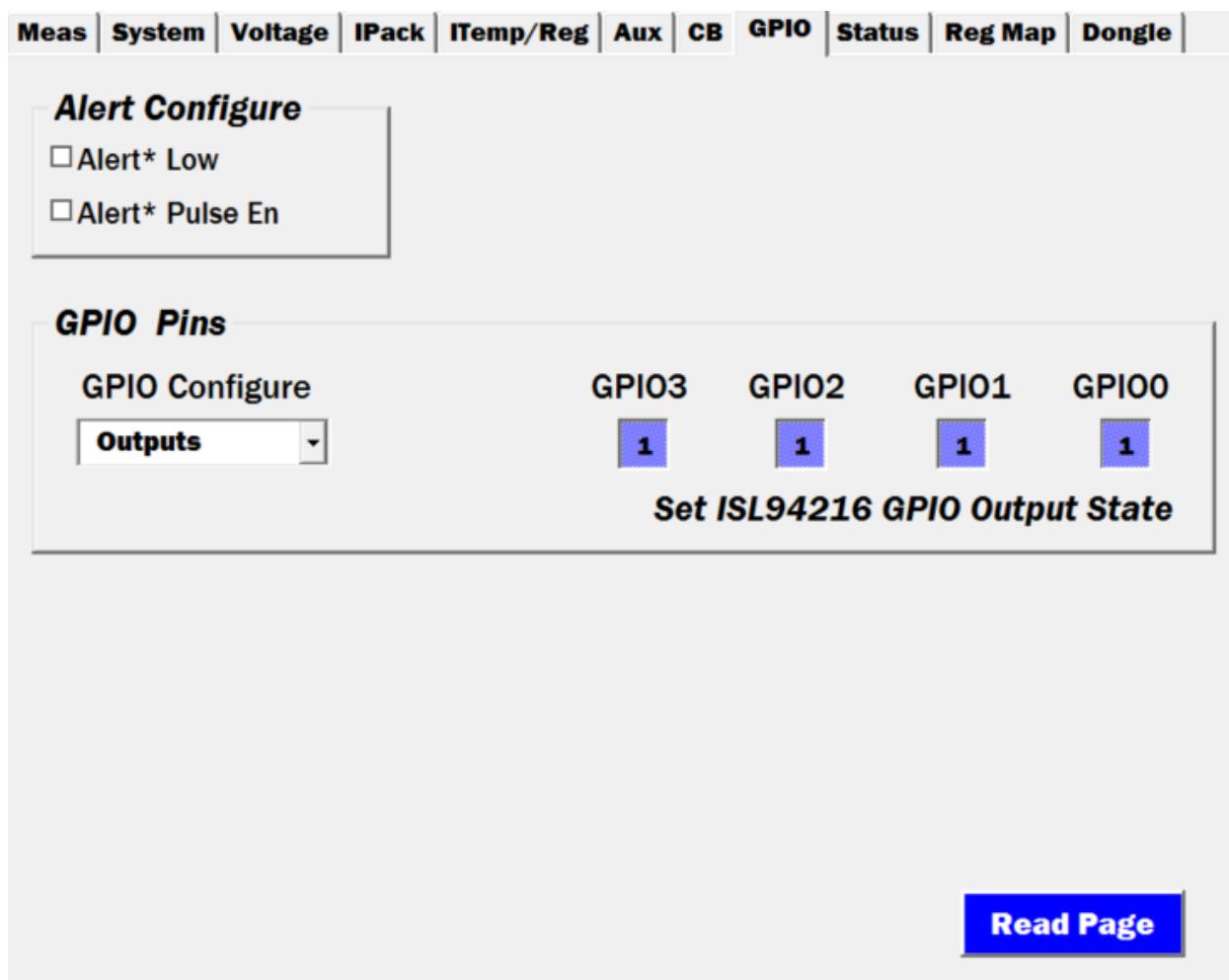

Figure 80. GPIO Tab

The **GPIO** tab (Figure 80) allows you to either view or control the status of the ISL94216 GPIO pins, depending on the configuration. The tab also allows you to select from the various GPIO configurations for the device. See the datasheet for the various GPIO configurations and operation.

| Faults/Status Bits   Mask Bits |             |       |       |       |                 |        |        |       |   |   |   |   |   |   |   |

|--------------------------------|-------------|-------|-------|-------|-----------------|--------|--------|-------|---|---|---|---|---|---|---|

| Bit 7                          |             |       |       |       |                 |        |        | Bit 0 |   |   |   |   |   |   |   |

| 0x63 Priority Faults           | VCCF        | OWF   | IOTF  | COCF  | DOCF            | DSCF   | UVF    | OVF   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0x64 ETAUX Faults              | COT1        | CUT1  | DOT1  | DUT1  | COTO            | CUTO   | DOTO   | DUTO  | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0x65 Other Faults              | VBOVF       | VBUVF | CPMP  | OW    | OW              | OW     | OW     | RSV   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0x66 CB Status                 | BAT<br>FULL | IOTW  | IEOC  | VEOC  | DVCF            | 2HI2CB | 2LO2CB | CB    | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0x67 Status                    | DCHRG1      | CHRGI | PRES1 | PRES1 | OTHER<br>FAULTS | IREG11 | IREG21 | VTMPF | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0x68 Open-Wire Status          | OW16        | OW15  | OW14  | OW13  | OW12            | OW11   | OW10   | OW9   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0x69 Open-Wire Status          | OW8         | OW7   | OW6   | OW5   | OW4             | OW3    | OW2    | OW1   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Read Status                    |             |       |       |       |                 |        |        |       |   |   |   |   |   |   |   |

Figure 81. Faults/Status Bits Tab

The **Status** tab is comprised of two sub-tabs.

The **Faults/Status Bits** sub-tab (Figure 81) displays the status of the various faults and status bits contained in the ISL94216.

| Faults/Status Bits   Mask Bits |             |       |       |       |                 |        |        |       |   |   |   |   |   |   |   |

|--------------------------------|-------------|-------|-------|-------|-----------------|--------|--------|-------|---|---|---|---|---|---|---|

| Bit 7                          |             |       |       |       |                 |        |        | Bit 0 |   |   |   |   |   |   |   |

| 0x83 Priority Faults Mask      | VCCF        | OWF   | IOTF  | COCF  | DOCF            | DSCF   | UVF    | OVF   | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0x84 ETAUX Faults Mask         | COT1        | CUT1  | DOT1  | DUT1  | COTO            | CUTO   | DOTO   | DUTO  | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0x85 Other Faults Mask         | VBOVF       | VBUVF | CPMP  | OW    | OW              | OW     | OW     | BUSY  | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0x86 CB Status Mask            | BAT<br>FULL | IOTW  | IEOC  | VEOC  | DVCF            | 2HI2CB | 2LO2CB | CB    | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0x87 Status Mask               | DCHRG1      | CHRGI | PRES1 | PRES1 | OTHER<br>FAULTS | IREG11 | IREG21 | VTMPF | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0x88 Open-Wire Mask            | OW16        | OW15  | OW14  | OW13  | OW12            | OW11   | OW10   | OW9   | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0x89 Open-Wire Mask            | OW8         | OW7   | OW6   | OW5   | OW4             | OW3    | OW2    | OW1   | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| Write Mask                     |             |       |       |       |                 |        |        |       |   |   |   |   |   |   |   |

| Read Mask                      |             |       |       |       |                 |        |        |       |   |   |   |   |   |   |   |

Figure 82. Faults/Status Mask Bits Tab

The **Mask Bits** sub-tab (Figure 82) allows you to view and modify the various mask bits in the device. Writing any of these bits to 0 allows the corresponding fault/status to propagate to the ALRT pin.

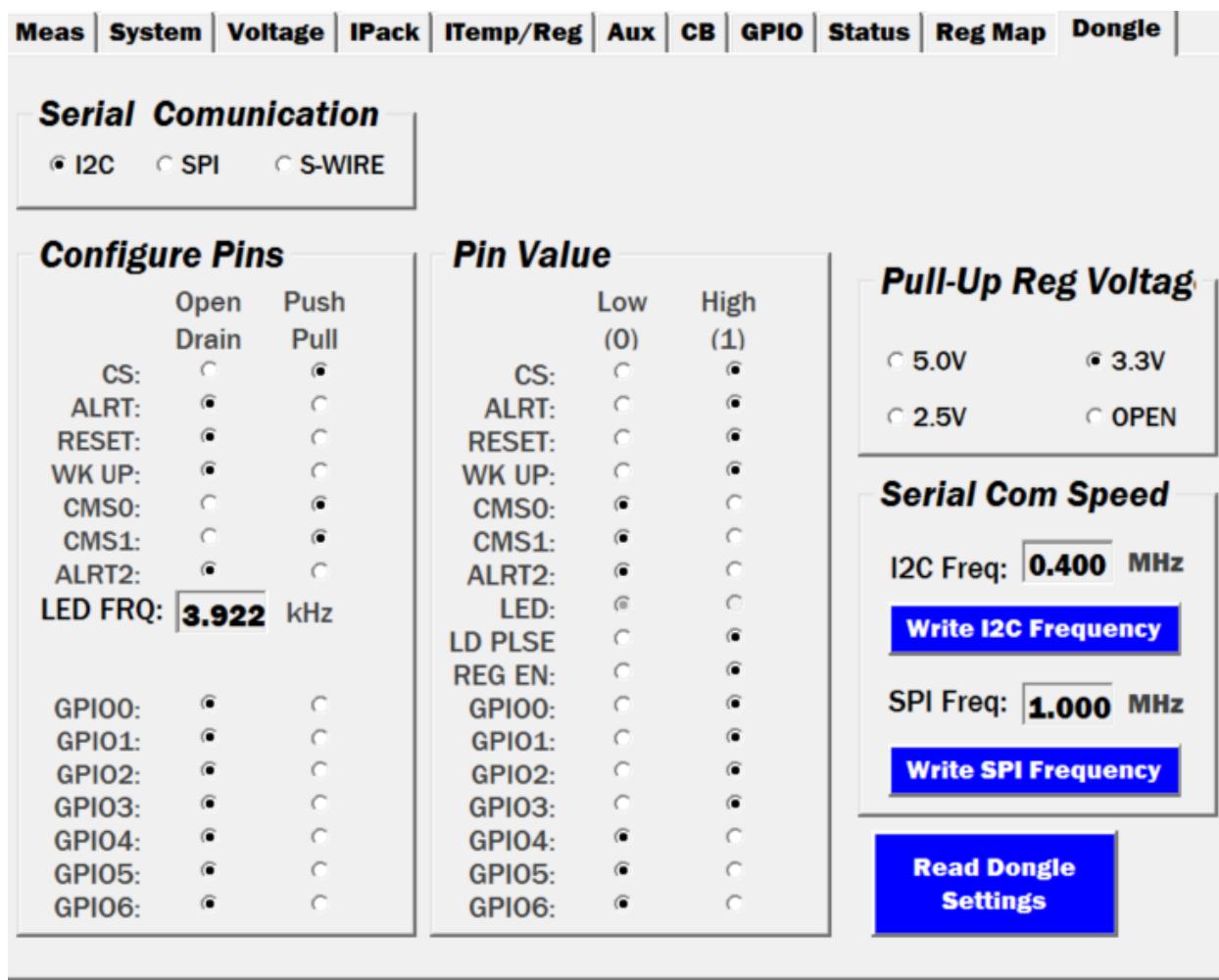

Figure 83. Dongle Tab

The **Dongle** tab (Figure 83) allows you to view and modify the settings of the ISO-DONGLE-EV1Z communications dongle.

## 9. Schematic

Figure 85. Evaluation Board Schematic Sheet 2

## 10. Revision History

| Rev. | Date     | Description     |

|------|----------|-----------------|

| 1.00 | Jun.3.20 | Initial release |

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

[www.renesas.com/contact/](http://www.renesas.com/contact/)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.