# FPGA AI Suite

## IP Reference Manual

Updated for FPGA AI Suite: **2024.3**

## Contents

---

|                                                                                     |           |

|-------------------------------------------------------------------------------------|-----------|

| <b>1. FPGA AI Suite IP Reference Manual.....</b>                                    | <b>4</b>  |

| <b>2. About the FPGA AI Suite IP.....</b>                                           | <b>5</b>  |

| 2.1. Supported Models.....                                                          | 7         |

| 2.1.1. MobileNet V2 differences between Caffe and TensorFlow models.....            | 7         |

| 2.2. Model Performance.....                                                         | 7         |

| 2.2.1. Throughput on the MobileNetV1 model (and other very fast models).....        | 12        |

| 2.3. Software Emulation of the FPGA AI Suite IP.....                                | 12        |

| 2.4. FPGA AI Suite Layer / Primitive Ranges.....                                    | 13        |

| 2.5. FPGA AI Suite IP Block Configuration.....                                      | 14        |

| 2.5.1. Architecture Description File Format for Instance Parameterization.....      | 16        |

| 2.5.2. Architecture Description File Parameters.....                                | 17        |

| 2.6. IP Block Interfaces.....                                                       | 31        |

| 2.6.1. Clock and Reset.....                                                         | 32        |

| 2.6.2. AXI Interfaces.....                                                          | 32        |

| 2.6.3. AXI Interface Clock and Reset.....                                           | 32        |

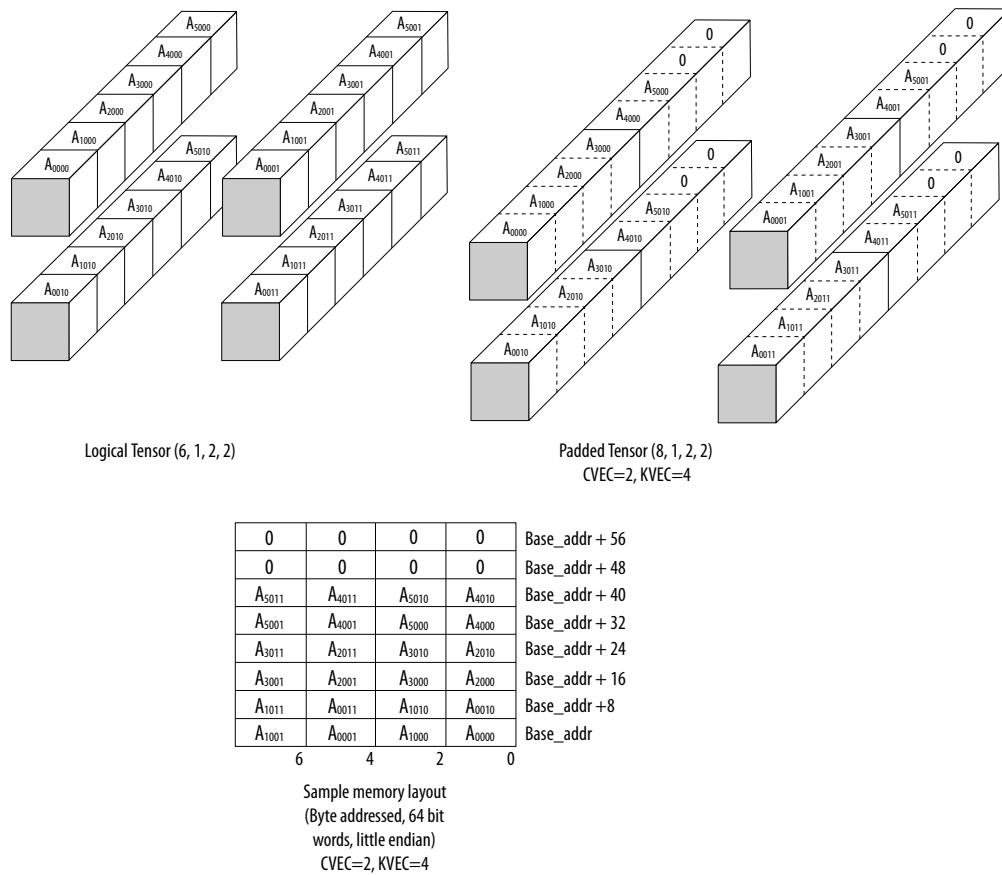

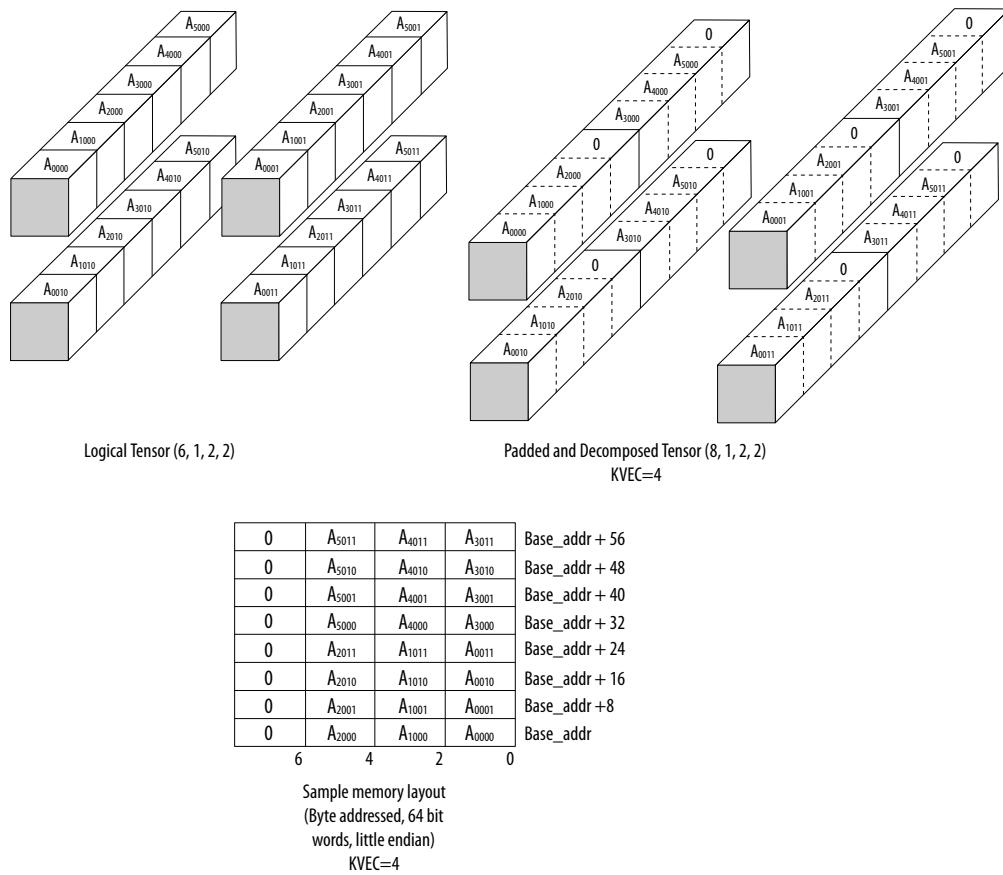

| 2.6.4. Input Feature Tensor In-Memory Format.....                                   | 33        |

| 2.6.5. Output Tensor In-Memory Format.....                                          | 37        |

| 2.7. Feature Input and Output Streaming .....                                       | 40        |

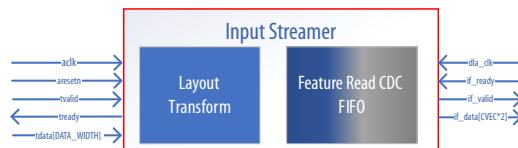

| 2.7.1. Input Streaming.....                                                         | 40        |

| 2.7.2. Output Streaming.....                                                        | 42        |

| 2.8. DDR-Free Operation.....                                                        | 43        |

| <b>3. FPGA AI Suite IP Generation Utility.....</b>                                  | <b>45</b> |

| 3.1. IP Generation Utility Execution Flows.....                                     | 45        |

| 3.2. IP Generation Utility Inputs.....                                              | 47        |

| 3.3. IP Generation Utility Outputs.....                                             | 47        |

| 3.4. IP Generation Utility Command Line Options.....                                | 47        |

| 3.4.1. The --flow create_ip Flow.....                                               | 49        |

| 3.4.2. The --flow add_arch Flow.....                                                | 50        |

| 3.4.3. The --flow list Flow.....                                                    | 51        |

| 3.4.4. The --flow remove_arch Flow.....                                             | 51        |

| <b>4. FPGA AI Suite Ahead-of-Time Splitter Utility.....</b>                         | <b>52</b> |

| 4.1. Files Generated by the FPGA AI Suite Ahead-of-Time (AOT) Splitter Utility..... | 52        |

| 4.2. Building the FPGA AI Suite Ahead-of-Time (AOT) Splitter Utility.....           | 53        |

| 4.3. Running the FPGA AI Suite Ahead-of-Time (AOT) Splitter Utility.....            | 53        |

| 4.4. FPGA AI Suite Ahead-of-Time (AOT) Splitter Utility Example Application.....    | 55        |

| <b>5. CSR Map and Descriptor Queue.....</b>                                         | <b>56</b> |

| 5.1. Discovery ROM.....                                                             | 56        |

| 5.2. Interrupt Control.....                                                         | 57        |

| 5.3. DMA Descriptor Queue.....                                                      | 57        |

| 5.4. DMA Control Registers.....                                                     | 58        |

| 5.5. Performance Registers.....                                                     | 59        |

| 5.6. Debug Network Registers.....                                                   | 59        |

| 5.7. DMA License Register.....                                                      | 60        |

| 5.8. DMA Transaction Counters.....                                                  | 60        |

|                                                                            |           |

|----------------------------------------------------------------------------|-----------|

| <b>A. FPGA AI Suite IP Reference Manual Archives.....</b>                  | <b>61</b> |

| <b>B. FPGA AI Suite IP Reference Manual Document Revision History.....</b> | <b>62</b> |

## 1. FPGA AI Suite IP Reference Manual

The *FPGA AI Suite IP Reference Manual* provides an overview of the FPGA AI Suite IP and the parameters that you can set to customize the IP. This document also covers the FPGA AI Suite IP generation utility.

### About the FPGA AI Suite Documentation Library

Documentation for the FPGA AI Suite is split across a few publications. Use the following table to find the publication that contains the FPGA AI Suite information that you are looking for:

**Table 1. FPGA AI Suite Documentation Library**

| Title and Description                                                                                                                                                                                                                                                                                           |                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| <i>Release Notes</i><br>Provides late-breaking information about the FPGA AI Suite including new features, important bug fixes, and known issues.                                                                                                                                                               | <a href="#">Link</a> |

| <i>Getting Started Guide</i><br>Get up and running with the FPGA AI Suite by learning how to initialize your compiler environment and reviewing the various design examples and tutorials provided with the FPGA AI Suite                                                                                       | <a href="#">Link</a> |

| <i>IP Reference Manual</i><br>Provides an overview of the FPGA AI Suite IP and the parameters you can set to customize it. This document also covers the FPGA AI Suite IP generation utility.                                                                                                                   | <a href="#">Link</a> |

| <i>Compiler Reference Manual</i><br>Describes the use modes of the graph compiler ( <code>dla_compiler</code> ). It also provides details about the compiler command options and the format of compilation inputs and outputs.                                                                                  | <a href="#">Link</a> |

| <i>PCIe-based Design Example User Guide</i><br>Describes the design and implementation for accelerating AI inference using the FPGA AI Suite, Intel® Distribution of OpenVINO™ toolkit, and a Terasic® DE10-Agilex Development Board.                                                                           | <a href="#">Link</a> |

| <i>SoC-based Design Example User Guide</i><br>Describes the design and implementation for accelerating AI inference using the FPGA AI Suite, Intel Distribution of OpenVINO toolkit, and an Arria® 10 SX SoC FPGA Development Kit (DK-SOC-10AS066S) or Agilex™ 7 FPGA I-Series Transceiver-SoC Development Kit. | <a href="#">Link</a> |

### Intel Distribution of OpenVINO toolkit Requirement

To use the FPGA AI Suite, you must be familiar with the Intel Distribution of OpenVINO toolkit.

FPGA AI Suite Version 2024.3 requires the Intel Distribution of OpenVINO toolkit Version 2023.3 LTS. For OpenVINO documentation, refer to <https://docs.openvino.ai/2023.3/documentation.html>.

© Altera Corporation. Altera, the Altera logo, the 'a' logo, and other Altera marks are trademarks of Altera Corporation. Altera and Intel warrant performance of its FPGA and semiconductor products to current specifications in accordance with Altera's or Intel's standard warranty as applicable, but reserves the right to make changes to any products and services at any time without notice. Altera and Intel assume no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera or Intel. Altera and Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

\*Other names and brands may be claimed as the property of others.

## 2. About the FPGA AI Suite IP

The FPGA AI Suite IP is an RTL-instantiable configurable IP with AXI interfaces that you can instantiate into a generic embedded FPGA system.

The IP is configured through parameters defined in an Architecture Description File. The Architecture Description File, along with the OpenVINO intermediate representation of your trained model, is compiled by the FPGA AI Suite compiler into configuration instructions for the IP.

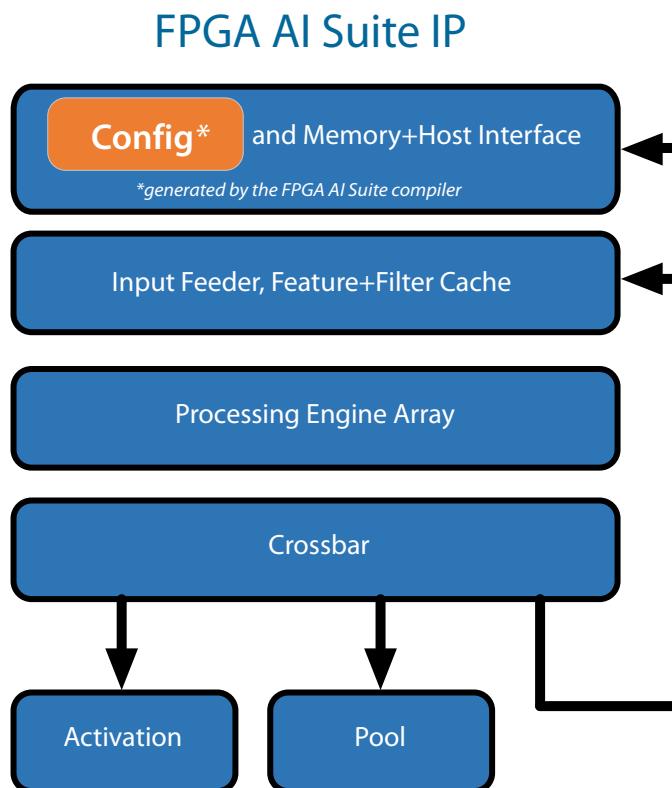

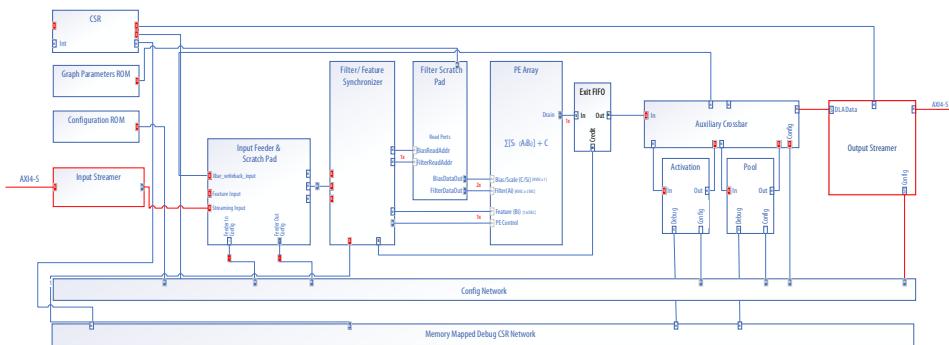

The following diagram shows a high-level architecture of the FPGA AI Suite IP.

**Figure 1. High-Level Architecture of the FPGA AI Suite IP**

The primary parameters defined in an Architecture Description File cover the following properties:

- PE array vectorization

- Scratch pad sizing

- External memory bus bandwidth

- Types/vectorization of auxiliary layer blocks

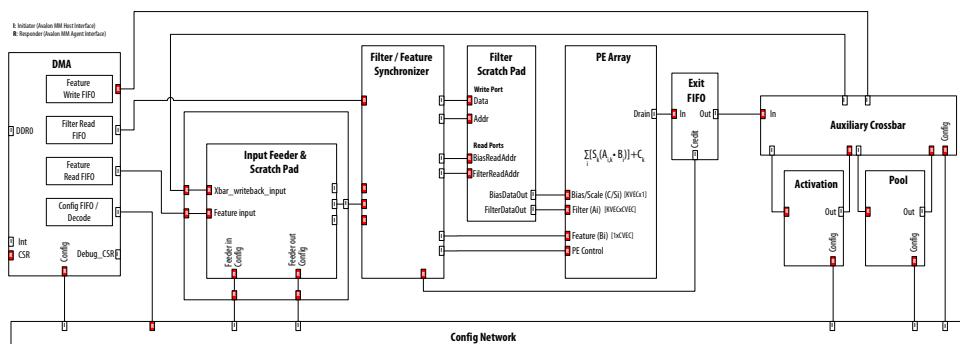

The following diagram is an architecture diagram for a specific instantiation of the FPGA AI Suite IP. The blocks connected to the crossbar in this diagram are examples. The selection of blocks connected to the crossbar are determined by compile time parameters.

**Figure 2. Architecture of an Example Instantiation of the FPGA AI Suite IP**

Two teams are typically involved in the implementation of an AI feature:

- A machine learning (ML) team responsible for developing and delivering an AI model.

- An FPGA team responsible for integrating the FPGA AI Suite IP and runtime together into a system.

Defining the IP architecture straddles the boundary between these two teams. The ML team must develop an AI model that meets the target performance in some parameterization of the configurable IP. The FPGA team must ensure it fits onto the FPGA and closes timing.

Although responsibility for defining the parameterization of the configurable architecture can lie with either team (but is a joint responsibility), it might be easiest for the ML team to define the architecture.

The team responsible for defining the IP parameterization can use the FPGA AI Suite compiler (`dla_compiler` command) area and performance estimator tools to guide their decisions. The *FPGA AI Suite Compiler Reference Manual* describes how to use the `dla_compiler` tool.

In addition to the FPGA team and the ML team, another team is likely responsible for the software integration on the host processor. Depending on the system details, this software is likely responsible for interfacing with OpenVINO and communicating (via the BSP) with the FPGA AI Suite IP. This software will likely be based on the runtime system that is included with the PCIe Example Design or possibly based on an SOC Example Design.

## 2.1. Supported Models

The FPGA AI Suite supports the following pretrained models from OpenVINO Model Zoo:

**Table 2. OpenVINO Model Zoo 2023.3 LTS**

| Model Zoo 2023.3 LTS path            | Model                         | Framework  |

|--------------------------------------|-------------------------------|------------|

| public/mobilenet-v1-1.0-224          | MobileNet V1                  | Caffe      |

| public/mobilenet-v2                  | MobileNet V2                  | Caffe      |

| public/mobilenet-v2-1.4-224          | MobileNet V2                  | TensorFlow |

| public/mobilenet-v3-large-1.0-224-tf | MobileNet V3                  | TensorFlow |

| public/resnet-50-tf                  | ResNet-50                     | TensorFlow |

| intel/unet-camvid-onnx-0001          | UNet                          | PyTorch    |

| public/yolo-v3-tf                    | YOLO v3                       | TensorFlow |

| public/yolo-v3-tiny-tf               | TinyYOLO v3                   | TensorFlow |

|                                      | Yolo v8 (all heads)           | PyTorch    |

| public/squeezezenet1.1               | SqueezeNet v1.1               | Caffe      |

| public/i3d_rgb_tf                    | Inflated 3D (I3D)             | TensorFlow |

|                                      | Multilayer Perceptrons (MLPs) |            |

After installation, the location `$COREDLA_ROOT/example_graphs/MLP/` contains an example MLP graph.

In addition, the FPGA AI Suite supports certain signed INT8 symmetric quantized models that use neural network compression framework (NNCF) flows.

Customized models that are similar to the supported models or are derived from the above models are not supported, although in some cases they might work without modification.

The supplied example architectures (or *IP Configurations*) support all of the above models, except for the Small and Small\_Softmax architectures that support only ResNet-50, MobileNet V1, and MobileNet V2.

### 2.1.1. MobileNet V2 differences between Caffe and TensorFlow models

There are two inverted bottlenecks (group of expand, depthwise, projection) in which TensorFlow has already gone down to 14x14 while Caffe is still at 28x28. This is the only place where the structure of the graph differs. TensorFlow also uses ReLU6, implemented with a clamp in the FPGA AI Suite IP, while Caffe uses ReLU.

## 2.2. Model Performance

The performance estimator tool (described in the [FPGA AI Suite Compiler Reference Manual](#)) assumes the following  $f_{MAX}$  values for FPGA devices:

- Arria 10: 265 MHz

- Agilex 7: 400 MHz

These assumptions are reasonable and conservative for the standard speed bin. As shown by the results in this section, the achieved  $f_{MAX}$  of the example design typically exceeds these assumptions.

The performance results for the designs that follow were achieved using the `dla_build_example_design.py` script that is included with the FPGA AI Suite. The script uses a standard (-2) speed bin with a single seed and uses high-effort compiler settings.

The runtime hosts used for determining the performance results are as follows:

- **Agilex 7 runtime host:** SUSE Linux Enterprise Server 15 host on an Intel Xeon® processor E5-1650 @ 3.5 GHz.

This design uses a dedicated DDR interface for the IP. The batch size is 1. Performance varies based on the clock speed, the DDR latency and bandwidth.

The `dla_build_example_design.py` script includes the following two `.qsf` lines to enable non-default Quartus® Prime options during design compilation:

```

set_global_assignment -name ALLOW_SHIFT_REGISTER_MERGING_ACROSS_HIERARCHIES

ALWAYS

set_global_assignment -name DISABLE_REGISTER_MERGING_ACROSS_HIERARCHIES OFF

```

The architectures in the tables that follow are in the `$COREDLA_ROOT/example_architectures/` directory. Review the `README` file in that directory for information about each architecture.

The **IP Throughput** column in the tables that follow shows the performance for the portion of the graph that runs on the FPGA device. In many cases, the entire graph runs on the FPGA device. The IP Throughput is representative of performance if the IP is used in a hostless configuration.

The **IP+host Throughput** column in the tables that follow shows the performance including the host. The IP+host performance may be lower than IP-only performance if the host is unable to stream data to the FPGA device quickly enough, or if the host is limited by some of the processing associated with the graph (for example, the host performs NMS for the YOLOv3 graph). Achievable IP+host performance depends on the speed and loading of the host and the FPGA AI Suite IP.

### Details - FPGA AI Suite 2024.3

| Architecture                  | $f_{MAX}$ | ALMs    | DSPs | M20Ks | Registers |

|-------------------------------|-----------|---------|------|-------|-----------|

| <b>AGX7_FP16_Generic</b>      | 600 MHz   | 33.6 k  | 186  | 511   | 95 k      |

| <b>AGX7_FP16_Performance</b>  | 605 MHz   | 103.9 k | 1162 | 1533  | 324 k     |

| <b>AGX7_Small_NoSoftmax</b>   | 610 MHz   | 17.2 k  | 80   | 296   | 49 k      |

| <b>AGX7_Small_Softmax</b>     | 616 MHz   | 18.6 k  | 90   | 304   | 57 k      |

| <b>AGX7_Generic</b>           | 600 MHz   | 38.9 k  | 202  | 778   | 113 k     |

| <b>AGX7_Performance</b>       | 585 MHz   | 70.5 k  | 650  | 1278  | 207 k     |

| <b>AGX7_Performance_Giant</b> | 535 MHz   | 127.8 k | 1546 | 2371  | 359 k     |

**public/mobilenet-v1-1.0-224**

| Architecture                  | ALMs    | DSPs | DDR(*) [MB/s] | IP Throughput [fps] | IP+host Throughput [fps] | Top-1 [%] | Top-5 [%] |

|-------------------------------|---------|------|---------------|---------------------|--------------------------|-----------|-----------|

| <b>AGX7_FP16_Generic</b>      | 33.6 k  | 186  | 2261          | 171                 | 171                      | 71.2      | 89.5      |

| <b>AGX7_FP16_Performance</b>  | 103.9 k | 1162 | 9117          | 572                 | 567                      | 71.2      | 89.5      |

| <b>AGX7_Small_NoSoftmax</b>   | 17.2 k  | 80   | 2770          | 167                 | 167                      | 70.9      | 89.6      |

| <b>AGX7_Small_Softmax</b>     | 18.6 k  | 90   | 2796          | 169                 | 168                      | 70.9      | 89.5      |

| <b>AGX7_Generic</b>           | 38.9 k  | 202  | 3306          | 255                 | 251                      | 70.9      | 89.5      |

| <b>AGX7_Performance</b>       | 70.5 k  | 650  | 8893          | 566                 | 399                      | 70.9      | 89.5      |

| <b>AGX7_Performance_Giant</b> | 127.8 k | 1546 | 8987          | 1483                | 764                      | 71.0      | 89.6      |

**public/mobilenet-v2**

| Architecture                  | ALMs    | DSPs | DDR(*) [MB/s] | IP Throughput [fps] | IP+host Throughput [fps] | Top-1 [%] | Top-5 [%] |

|-------------------------------|---------|------|---------------|---------------------|--------------------------|-----------|-----------|

| <b>AGX7_FP16_Generic</b>      | 33.6 k  | 186  | 3653          | 148                 | 147                      | 71.8      | 89.6      |

| <b>AGX7_FP16_Performance</b>  | 103.9 k | 1162 | 6948          | 372                 | 367                      | 71.8      | 89.6      |

| <b>AGX7_Small_NoSoftmax</b>   | 17.2 k  | 80   | 4609          | 141                 | 138                      | 71.6      | 89.6      |

| <b>AGX7_Small_Softmax</b>     | 18.6 k  | 90   | 4645          | 142                 | 139                      | 71.8      | 89.4      |

| <b>AGX7_Generic</b>           | 38.9 k  | 202  | 2720          | 203                 | 198                      | 71.8      | 89.4      |

| <b>AGX7_Performance</b>       | 70.5 k  | 650  | 7166          | 343                 | 276                      | 71.7      | 89.4      |

| <b>AGX7_Performance_Giant</b> | 127.8 k | 1546 | 6370          | 1081                | 726                      | 71.8      | 89.4      |

**public/mobilenet-v2-1.4-224**

| Architecture                  | ALMs    | DSPs | DDR(*) [MB/s] | IP Throughput [fps] | IP+host Throughput [fps] | Top-1 [%] | Top-5 [%] |

|-------------------------------|---------|------|---------------|---------------------|--------------------------|-----------|-----------|

| <b>AGX7_FP16_Generic</b>      | 33.6 k  | 186  | 4085          | 122                 | 121                      | 74.8      | 91.9      |

| <b>AGX7_FP16_Performance</b>  | 103.9 k | 1162 | 8717          | 290                 | 288                      | 74.8      | 91.9      |

| <b>AGX7_Generic</b>           | 38.9 k  | 202  | 4184          | 151                 | 145                      | 74.7      | 91.8      |

| <b>AGX7_Performance</b>       | 70.5 k  | 650  | 8716          | 290                 | 226                      | 74.7      | 91.8      |

| <b>AGX7_Performance_Giant</b> | 127.8 k | 1546 | 7539          | 847                 | 618                      | 74.7      | 91.7      |

(\*) **DDR** is estimated minimum average read + write (that is, read + write require at least this much bandwidth on average). Peak bandwidth is higher.

## public/mobilenet-v3-large-1.0-224-tf

| Architecture                  | ALMs    | DSPs | DDR(*) [MB/s] | IP Throughput [fps] | IP+host Throughput [fps] | Top-1 [%] | Top-5 [%] |

|-------------------------------|---------|------|---------------|---------------------|--------------------------|-----------|-----------|

| <b>AGX7_FP16_Generic</b>      | 33.6 k  | 186  | 3774          | 169                 | 165                      | 75.8      | 92.1      |

| <b>AGX7_FP16_Performance</b>  | 103.9 k | 1162 | 11260         | 240                 | 234                      | 75.8      | 92.1      |

| <b>AGX7_Generic</b>           | 38.9 k  | 202  | 4530          | 181                 | 174                      | 72.3      | 90.7      |

| <b>AGX7_Performance</b>       | 70.5 k  | 650  | 11293         | 246                 | 201                      | 72.1      | 90.5      |

| <b>AGX7_Performance_Giant</b> | 127.8 k | 1546 | 8492          | 355                 | 304                      | 72.6      | 90.6      |

## public/resnet-50-tf

| Architecture                  | ALMs    | DSPs | DDR(*) [MB/s] | IP Throughput [fps] | IP+host Throughput [fps] | Top-1 [%] | Top-5 [%] |

|-------------------------------|---------|------|---------------|---------------------|--------------------------|-----------|-----------|

| <b>AGX7_FP16_Generic</b>      | 33.6 k  | 186  | 3005          | 32                  | 32                       | 76.8      | 92.9      |

| <b>AGX7_FP16_Performance</b>  | 103.9 k | 1162 | 11715         | 166                 | 164                      | 76.8      | 92.9      |

| <b>AGX7_Small_NoSoftmax</b>   | 17.2 k  | 80   | 5935          | 28                  | 28                       | 77.0      | 92.9      |

| <b>AGX7_Small_Softmax</b>     | 18.6 k  | 90   | 5989          | 28                  | 28                       | 77.1      | 92.9      |

| <b>AGX7_Generic</b>           | 38.9 k  | 202  | 4206          | 60                  | 60                       | 77.1      | 92.9      |

| <b>AGX7_Performance</b>       | 70.5 k  | 650  | 11540         | 163                 | 143                      | 76.9      | 92.9      |

| <b>AGX7_Performance_Giant</b> | 127.8 k | 1546 | 8067          | 237                 | 229                      | 76.9      | 92.8      |

## Resnet50 v1 (Caffe)

| Architecture                  | ALMs    | DSPs | DDR(*) [MB/s] | IP Throughput [fps] | IP+host Throughput [fps] | Top-1 [%] | Top-5 [%] |

|-------------------------------|---------|------|---------------|---------------------|--------------------------|-----------|-----------|

| <b>AGX7_FP16_Generic</b>      | 33.6 k  | 186  | 2822          | 38                  | 38                       | 74.4      | 91.4      |

| <b>AGX7_FP16_Performance</b>  | 103.9 k | 1162 | 12139         | 195                 | 195                      | 74.4      | 91.4      |

| <b>AGX7_Small_NoSoftmax</b>   | 17.2 k  | 80   | 4161          | 37                  | 37                       | 74.1      | 91.4      |

| <b>AGX7_Small_Softmax</b>     | 18.6 k  | 90   | 4203          | 37                  | 37                       | 74.2      | 91.3      |

| <b>AGX7_Generic</b>           | 38.9 k  | 202  | 4489          | 73                  | 73                       | 74.2      | 91.3      |

| <b>AGX7_Performance</b>       | 70.5 k  | 650  | 12119         | 195                 | 162                      | 74.0      | 91.4      |

| <b>AGX7_Performance_Giant</b> | 127.8 k | 1546 | 8379          | 270                 | 247                      | 74.1      | 91.4      |

## intel/unet-camvid-onnx-0001

| Architecture                 | ALMs    | DSPs | DDR(*) [MB/s] | IP Throughput [fps] |

|------------------------------|---------|------|---------------|---------------------|

| <b>AGX7_FP16_Generic</b>     | 33.6 k  | 186  | 825           | 1.09                |

| <b>AGX7_FP16_Performance</b> | 103.9 k | 1162 | 4552          | 7.57                |

| <b>AGX7_Small_NoSoftmax</b>  | 17.2 k  | 80   | 1140          | 1.10                |

| <i>continued...</i>          |         |      |               |                     |

| Architecture                  | ALMs    | DSPs | DDR(*) [MB/s] | IP Throughput [fps] |

|-------------------------------|---------|------|---------------|---------------------|

| <b>AGX7_Small_Softmax</b>     | 18.6 k  | 90   | 1153          | 1.11                |

| <b>AGX7_Generic</b>           | 38.9 k  | 202  | 1319          | 2.14                |

| <b>AGX7_Performance</b>       | 70.5 k  | 650  | 4331          | 7.36                |

| <b>AGX7_Performance_Giant</b> | 127.8 k | 1546 | 5426          | 11.71               |

#### public/yolo-v3-tf

| Architecture                  | ALMs    | DSPs | DDR(*) [MB/s] | IP Throughput [fps] | IP+host Throughput [fps] | Detection mAP @0.5 | Detection mAP @0.5:0.95 |

|-------------------------------|---------|------|---------------|---------------------|--------------------------|--------------------|-------------------------|

| <b>AGX7_FP16_Generic</b>      | 33.6 k  | 186  | 1428          | 4.2                 | 4                        | 62.27              | 31.58                   |

| <b>AGX7_FP16_Performance</b>  | 103.9 k | 1162 | 6347          | 27.9                | 28                       | 62.25              | 31.58                   |

| <b>AGX7_Generic</b>           | 38.9 k  | 202  | 1901          | 8.2                 | 8                        | 62.28              | 31.49                   |

| <b>AGX7_Performance</b>       | 70.5 k  | 650  | 6170          | 27.0                | 11                       | 62.22              | 31.47                   |

| <b>AGX7_Performance_Giant</b> | 127.8 k | 1546 | 6634          | 40.5                | 30                       | 62.25              | 31.46                   |

#### public/yolo-v3-tiny-tf

| Architecture                  | ALMs    | DSPs | DDR(*) [MB/s] | IP Throughput [fps] | IP+host Throughput [fps] | Detection mAP @0.5 | Detection mAP @0.5:0.95 |

|-------------------------------|---------|------|---------------|---------------------|--------------------------|--------------------|-------------------------|

| <b>AGX7_FP16_Generic</b>      | 33.6 k  | 186  | 1200          | 41                  | 36                       | 35.79              | 14.77                   |

| <b>AGX7_FP16_Performance</b>  | 103.9 k | 1162 | 4680          | 116                 | 113                      | 35.81              | 14.78                   |

| <b>AGX7_Generic</b>           | 38.9 k  | 202  | 2433          | 82                  | 66                       | 35.76              | 14.74                   |

| <b>AGX7_Performance</b>       | 70.5 k  | 650  | 4647          | 115                 | 40                       | 35.73              | 14.72                   |

| <b>AGX7_Performance_Giant</b> | 127.8 k | 1546 | 5028          | 109                 | 64                       | 35.81              | 14.75                   |

#### public/yolo-v8-nano detection

| Architecture                 | ALMs    | DSPs | DDR(*) [MB/s] | IP Throughput [fps] | IP+host Throughput [fps] | Detection mAP @0.5 | Detection mAP @0.5:0.95 |

|------------------------------|---------|------|---------------|---------------------|--------------------------|--------------------|-------------------------|

| <b>AGX7_FP16_Performance</b> | 103.9 k | 1162 | 6728          | 94                  | 91                       | 51.15              | 36.52                   |

| <b>AGX7_Generic</b>          | 38.9 k  | 202  | 2427          | 50                  | 39                       | 51.14              | 36.50                   |

| <b>AGX7_Performance</b>      | 70.5 k  | 650  | 6720          | 95                  | 32                       | 51.10              | 36.48                   |

#### public/yolo-v8-nano classification

| Architecture                 | ALMs    | DSPs | DDR(*) [MB/s] | Throughput [fps] | Top-1 [%] | Top-5 [%] |

|------------------------------|---------|------|---------------|------------------|-----------|-----------|

| <b>AGX7_FP16_Performance</b> | 103.9 k | 1162 | 10345         | 1384             | 67.92     | 87.72     |

| <b>AGX7_Generic</b>          | 38.9 k  | 202  | 5489          | 943              | 67.96     | 87.86     |

| <b>AGX7_Performance</b>      | 70.5 k  | 650  | 10178         | 1358             | 67.72     | 87.72     |

### public/squeezezenet1.1

| Architecture                  | ALMs    | DSPs | DDR(*) [MB/s] | IP Throughput [fps] | IP+host Throughput [fps] | Top-1 [%] | Top-5 [%] |

|-------------------------------|---------|------|---------------|---------------------|--------------------------|-----------|-----------|

| <b>AGX7_FP16_Generic</b>      | 33.6 k  | 186  | 631           | 218                 | 219                      | 58.5      | 81.1      |

| <b>AGX7_FP16_Performance</b>  | 103.9 k | 1162 | 4679          | 940                 | 886                      | 58.5      | 81.1      |

| <b>AGX7_Small_NoSoftmax</b>   | 17.2 k  | 80   | 923           | 220                 | 219                      | 58.5      | 81.0      |

| <b>AGX7_Small_Softmax</b>     | 18.6 k  | 90   | 933           | 222                 | 222                      | 58.5      | 81.0      |

| <b>AGX7_Generic</b>           | 38.9 k  | 202  | 1722          | 535                 | 536                      | 58.5      | 81.0      |

| <b>AGX7_Performance</b>       | 70.5 k  | 650  | 4654          | 932                 | 419                      | 58.4      | 81.0      |

| <b>AGX7_Performance_Giant</b> | 127.8 k | 1546 | 3631          | 951                 | 735                      | 58.3      | 81.1      |

### public/i3d\_rgb\_tf

| Architecture                  | ALMs    | DSPs | DDR(*) [MB/s] | Throughput [fps] | Top-1 [%] | Top-5 [%] |

|-------------------------------|---------|------|---------------|------------------|-----------|-----------|

| <b>AGX7_FP16_Generic</b>      | 33.6 k  | 186  | 442           | 0.61             | 65.79     | 82.89     |

| <b>AGX7_FP16_Performance</b>  | 103.9 k | 1162 | 2562          | 4.14             | 65.79     | 82.89     |

| <b>AGX7_Small_NoSoftmax</b>   | 17.2 k  | 80   | 492           | 0.58             | 65.35     | 82.89     |

| <b>AGX7_Small_Softmax</b>     | 18.6 k  | 90   | 496           | 0.59             | 65.57     | 82.89     |

| <b>AGX7_Generic</b>           | 38.9 k  | 202  | 742           | 1.36             | 65.57     | 83.11     |

| <b>AGX7_Performance</b>       | 70.5 k  | 650  | 2486          | 4.01             | 65.13     | 83.11     |

| <b>AGX7_Performance_Giant</b> | 127.8 k | 1546 | 2839          | 4.64             | 65.79     | 82.89     |

## 2.2.1. Throughput on the MobileNetV1 model (and other very fast models)

Due to the high system throughput, the MobileNetV1 performance with large IP instances is strongly dependent on the host.

## 2.3. Software Emulation of the FPGA AI Suite IP

The FPGA AI Suite includes a compiled software model of the FPGA AI Suite IP that is bit-accurate<sup>(\*)</sup>. The emulation of the FPGA AI Suite IP is accessible through the OpenVINO plugin interface. This emulation models the numeric details of the IP, including the behavior of the block floating point numerics (when used).

The OpenVINO emulation plugin is enabled in the \$COREDLA\_ROOT/bin/plugins\_emulation.xml plugins file. Because it uses the OpenVINO plugin architecture, it works with both the OpenVINO Python API and the C++ API. For an example that shows how to use emulation as the inference engine for the runtime dla\_benchmark utility, refer to “[Performing Inference Without an FPGA Board](#)” in the [FPGA AI Suite Getting Started Guide](#).

(\*) Minor rounding differences between software emulation and hardware will typically result in differences of less than two units of least precision (ulps).

Because the emulation executes on the CPU and does not benefit from the FPGA acceleration, the emulation is much slower than inference on the FPGA. Typical inference times for a single image with ResNet50 are on the order of minutes of time. The inference speed varies dramatically depending on the architecture configuration and the graph.

## 2.4. FPGA AI Suite Layer / Primitive Ranges

The following table lists the hyperparameter ranges supported by key primitive layers:

| Layer / Primitive              | Hyperparameter                                             | Supported Range                                                                                                |

|--------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Fully connected                | None                                                       | n/a                                                                                                            |

| 2D Conv                        | Filter Size                                                | Width = [1..28]<br>Height = [1..28]<br>Height does not have to equal width.<br>Default value for each is 14.   |

|                                | Stride                                                     | Maximum stride is 15                                                                                           |

|                                | Pad                                                        | Maximum pad is $(2^{16}) - 1$                                                                                  |

| 3D Conv                        | Filter Size                                                | Width = [1..28]<br>Height = [1..28]<br>Depth = [1..14]<br>Filter volume should fit into the filter cache size. |

|                                | Stride                                                     | Maximum stride is 15.                                                                                          |

|                                | Pad                                                        | Maximum pad is $(2^{16}) - 1$                                                                                  |

| Depthwise                      | Filter Size                                                | Same as 2D Conv filter size<br>Depth = 1                                                                       |

|                                | Stride                                                     | Same as 2D Conv stride<br>Depth = 1                                                                            |

|                                | Pad                                                        | Same as 2D conv padding<br>Depth = 1                                                                           |

| Scale-Shift                    | Scale factor                                               | FP16 float range                                                                                               |

|                                | Bias term                                                  | FP16 float range                                                                                               |

| Deconv / Transpose Convolution | Filter Size                                                | Any – Same as convolution, and height/width can be different<br>Depth = 1                                      |

|                                | Stride                                                     | 1, 2, 4, 8 (stride width == stride height)<br>Depth = 1                                                        |

|                                | Pad                                                        | Restricted to filter_[height, width] - 1<br>Depth = 1                                                          |

| ReLU                           | n/a                                                        | n/a                                                                                                            |

| pReLU                          | Scaling parameter (a) (1 per filter / conv output channel) | float range<br>Depth = 1                                                                                       |

| Leaky ReLU                     | Scaling parameter (a) (1 per tensor)                       | float range                                                                                                    |

| Clamp                          | Limit parameters (a, b) (1 per tensor)                     | float range                                                                                                    |

*continued...*

| Layer / Primitive                                                                            | Hyperparameter                         | Supported Range                                                                                  |

|----------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------|

| Round_Clamp                                                                                  | Limit parameters (a, b) (1 per tensor) | float range                                                                                      |

| H-sigmoid                                                                                    | n/a                                    | n/a                                                                                              |

| H-swish                                                                                      | n/a                                    | n/a                                                                                              |

| Sigmoid                                                                                      | n/a                                    | FP16 float range                                                                                 |

| Swish                                                                                        | n/a                                    | FP16 float range                                                                                 |

| Tanh                                                                                         | n/a                                    | FP16 float range                                                                                 |

| Max Pool                                                                                     | Window Size                            | up to 13x13x13                                                                                   |

|                                                                                              | Pad                                    | 1, 2                                                                                             |

|                                                                                              | Stride                                 | 1, 2, 3, 4                                                                                       |

| Average Pool                                                                                 | Window Size                            | Up to 27x27 (one less than the maximum 2D convolution size)<br>Width == Height<br>Depth = 1 or 2 |

|                                                                                              | Pad                                    | 1, 2                                                                                             |

|                                                                                              | Stride                                 | 1, 2, 3, 4                                                                                       |

| Softmax                                                                                      | Maximum Number of Channels             | 4096                                                                                             |

| Elementwise Multiplication of feature * filter and feature * feature tensors. <sup>(1)</sup> | n/a                                    | Tensor sizes are expanded if necessary to support the multiplication.<br>Depth = 1               |

| ChannelToSpace<br>DepthToSpace<br>PixelShuffle                                               | block_mode                             | blocks_first or blocks_last                                                                      |

|                                                                                              | block_size                             | 2, 4, 8                                                                                          |

## 2.5. FPGA AI Suite IP Block Configuration

The FPGA AI Suite IP block has many important parameters that describe arithmetic precision, feature set, size of various modules (such as the PE Array), and details regarding the internal buses and the external AXI interface.

Configurable parameters are specified in the Architecture Description (.arch) file, as described in [Architecture Description File Format for Instance Parameterization](#) on page 16 and [Architecture Description File Parameters](#) on page 17.

The table below shows the major parameters, some of which are not configurable, that describe the IP block.

| Common Parameter Name | Description                                                                                                                                                     | Valid Range    |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| c_vector<br>(CVEC)    | Size of the dot product performed by each PE in the PE Array.<br>Typically optimized when generating an optimized architecture with the FPGA AI Suite compiler. | [4,8,16,32,64] |

| k_vector              | Number of PEs in the PE Array                                                                                                                                   | [4-128]        |

**continued...**

<sup>(1)</sup> This is an element-wise multiplication, not a matrix multiply operation.

| Common Parameter Name                                                | Description                                                                                                                                                                                                                                                                                                  | Valid Range                                                                                                                                                        |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (PE KVEC)                                                            |                                                                                                                                                                                                                                                                                                              | Must be a multiple of c_vector                                                                                                                                     |

| num_lanes                                                            | Number of execution lane. Each lane contains a set of auxiliary modules (aux_modules) and a number (equal to k_vector) of PEs                                                                                                                                                                                | [1,2,4]                                                                                                                                                            |

| N/A                                                                  | Number of auxiliary modules connecting to the crossbar (XBAR)                                                                                                                                                                                                                                                | [1-4]                                                                                                                                                              |

| pool k_vector<br>(Pool KVEC)                                         | Width of the pool interface.<br>Typically optimized when generating an optimized architecture with the FPGA AI Suite compiler.                                                                                                                                                                               | [1,2,4,8,16,32,64]                                                                                                                                                 |

| pool max_window_height<br>pool max_window_width                      | Size of the pooling window                                                                                                                                                                                                                                                                                   | [3x3, 7x7,13x13]                                                                                                                                                   |

| depthwise k_vector<br>(Depthwise KVEC)                               | Number of output channels processed in parallel.<br>Typically optimized when generating an optimized architecture with the FPGA AI Suite compiler.                                                                                                                                                           | [16, 32, 64]<br>Must be equal to k_vector                                                                                                                          |

| depthwise max_window_height<br>depthwise max_window_width            | Size of the depthwise filter                                                                                                                                                                                                                                                                                 | [3x3, 5x5, 7x7]                                                                                                                                                    |

| depthwise max_dilation_vertical<br>depthwise max_dilation_horizontal | Maximum supported value for the depthwise dilation                                                                                                                                                                                                                                                           | [1-6]                                                                                                                                                              |

| activation k_vector<br>(Activation KVEC)                             | Width of the activation interface.<br>Typically optimized when generating an optimized architecture with the FPGA AI Suite compiler.                                                                                                                                                                         | [2,4,8,16,32,64]                                                                                                                                                   |

| enable_clamp                                                         | Enables clamp activation function                                                                                                                                                                                                                                                                            | [true, false]                                                                                                                                                      |

| enable_relu                                                          | Enables ReLU activation function                                                                                                                                                                                                                                                                             | [true, false]                                                                                                                                                      |

| enable_leaky_relu                                                    | Enables Leaky ReLU activation function                                                                                                                                                                                                                                                                       | [true, false]                                                                                                                                                      |

| enable_prelu                                                         | Enables PReLU activation function                                                                                                                                                                                                                                                                            | [true, false]                                                                                                                                                      |

| enable_round_clamp                                                   | Enables round clamp activation function                                                                                                                                                                                                                                                                      | [true, false]                                                                                                                                                      |

| enable_sigmoid                                                       | Enables Sigmoid and Swish activation functions                                                                                                                                                                                                                                                               | [true, false]                                                                                                                                                      |

| enable_tanh                                                          | Enables Tanh activation function                                                                                                                                                                                                                                                                             | [true, false]                                                                                                                                                      |

| enable_parameter_rom                                                 | Enables storing graph parameters in on-chip memory, which requires input and output streaming to be enabled and configured.<br>For details about DDR-free operation, refer to <a href="#">"Generating Artifacts for DDR-Free Operation"</a> in the <a href="#">FPGA AI Suite Compiler Reference Manual</a> . | [true, false]                                                                                                                                                      |

| arch_precision<br>(PE precision)                                     | Precision of features and weights in the PE Array.<br>For details about how this parameter affects DSP utilization, refer to the <a href="#">"Parameter: arch_precision" section of Parameter Group: Global Parameters</a> on page 17.                                                                       | "FP11" (INT7-BFP / 1s.6m.5e)<br>"FP12AGX" (INT8-BFP / 8m.5e, two's complement)<br>"FP13AGX" (INT9-BFP / 9m.5e, two's complement)<br>"FP16" (INT12-BFP / 1s.11m.5e) |

| PE bias add precision                                                | Precision of accumulator bias value in the PE Array.                                                                                                                                                                                                                                                         | fp16                                                                                                                                                               |

| PE accumulator precision                                             | Precision of the accumulators in the PE Array.                                                                                                                                                                                                                                                               | fp32                                                                                                                                                               |

| PE drain precision                                                   | Precision of values drained from the PE Accumulators to the XBAR and AUX Modules.                                                                                                                                                                                                                            | fp16                                                                                                                                                               |

| <i>continued...</i>                                                  |                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                    |

| Common Parameter Name   | Description                                                                                                                                | Valid Range                                                                                                                                                                                                       |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PE interleave factor    | Multi-threading factor for the features x filters in the PE array accumulators.                                                            | <b>Agilex 5 devices:</b> 12x1<br><b>Agilex 7 devices:</b> 2x3, 3x2, 5x1, 1x5<br><b>Arria 10 devices:</b> 2x2, 4x1, 1x4<br><b>Stratix® 10 devices:</b> 2x3, 3x2, 5x1, 1x5<br>1x1 supported for graphs with no bias |

| PE scale precision      | Precision of scale multiplier in the PE array                                                                                              | fp16                                                                                                                                                                                                              |

| Aux module precision    | Precision of the Aux Modules                                                                                                               | fp16                                                                                                                                                                                                              |

| Memory port width       | Width of memory port                                                                                                                       | [64, 128, 256, 512]                                                                                                                                                                                               |

| enable_debug            | Toggle the FPGA AI Suite debug network that includes interface profiling counters that can be queried with the CSR.<br>Enabled by default. | [true, false]                                                                                                                                                                                                     |

| enable_layout_transform | Enables the dedicated input tensor layout transform module.                                                                                | [true, false]                                                                                                                                                                                                     |

The major constraints include:

- PE KVEC must be a multiple of CVEC

- PE KVEC must be divisible by XBAR and AUX KVECs

- PE drain width must be equal to XBAR KVEC

Graph limitations include:

- Convolution filter size:  $1 \times 1 \rightarrow 28 \times 28$ , including asymmetric

- Convolution filter stride: 1 .. 15

- No limitation on convolution padding

- The limits of the depthwise layers are the same as normal convolution. Depthwise convolution is handled with software emulation using regular convolution passes.

The maximum supported DDR size is 4GB.

### 2.5.1. Architecture Description File Format for Instance Parameterization

The FPGA AI Suite IP has a highly configurable architecture. Configuring the design allows for different trade-offs between inference performance (throughput and latency) and utilization of FPGA resources (area). Configurations are specified through Architecture Description Files. The IP instances corresponding to these configurations can be compiled as part of an FPGA design into an FPGA bitstream.

The architecture determines how much FPGA area is consumed by the FPGA AI Suite IP and strongly affects the achieved inference fps and ease of timing closure.

Achieving the best performance of a given graph for a given FPGA area (or the smallest FPGA area for a given performance target) requires optimizing the architecture. The architecture optimization function of the FPGA AI Suite compiler is designed to produce good architectures for a given graph or set of graphs. For more details about the architecture optimization function of the compiler, refer to the [FPGA AI Suite Compiler Reference Manual](#).

The FPGA AI Suite Architecture Description Files use the protobuf format and have a .arch file extension. While these files are human readable and editable, manually optimizing an architecture requires a deep knowledge of the FPGA AI Suite IP design and is not recommended.

You adjust some of the architecture parameters by hand, because the Architecture Optimizer does not modify them. For example, the optimizer does not modify the numerical precision (for example, fp16 or fp11) in the architecture file. Similarly, the optimizer does not modify details related to the AXI interfaces on the IP. In some case, you can improve performance of the resulting optimized architecture by the choice of these values.

When possible, modifying the graph or batch size might also result in performance improvements. For example, a graph that requires FP16 precision might have sufficient accuracy at FP11 or FP12 if a few extra layers are added. Reducing the internal precision enables a large memory and area reduction. Very small and fast graphs might achieve a higher performance on hardware by using a batch size that is greater than one.

The example\_architectures/ directory includes an example that shows how to enable the hardware-accelerated softmax function.

The comment character in the .arch format is #.

## 2.5.2. Architecture Description File Parameters

### 2.5.2.1. Parameter Group: Global Parameters

#### Parameter: family

This parameter specifies the target FPGA device family for the architecture.

Legal

Values

**Table 3. Valid Values for family Global Parameter**

| Value | Description                 |

|-------|-----------------------------|

| A10   | Target Arria 10 devices.    |

| AGX5  | Target Agilex 5 devices.    |

| AGX7  | Target Agilex 7 devices.    |

| C10   | Target Cyclone® 10 devices. |

| S10   | Target Stratix 10 devices.  |

#### Parameter: k\_vector

This parameter, also called KVEC, describes the number of filters that the PE Array is able to process simultaneously.

Typically the architecture optimizer is used to set this parameter.

Legal

values:

[4-128]

- The `k_vector` value must be a multiple of the `c_vector` value.

- The `k_vector` value must be divisible by the `xbar_k_vector` and auxiliary `k_vector` values.

- When you use the depthwise module, the `k_vector` value must equal the `c_vector` value.

#### Parameter: `c_vector`

This parameter, also called CVEC, describes the size of the dot product within each PE in the PE Array.

Typically the architecture optimizer is used to set this parameter.

*Legal values:* [4,8,16,32,64]

- When you use the depthwise module, the `c_vector` value must equal the `k_vector` value.

#### Parameter: `num_lanes`

This parameter describes how many output-height slices the architecture can compute in parallel.

Using the `num_lanes` architecture parameter has the following effects:

- Setting the `num_lanes` parameter scales the PE array in the FPGA AI Suite IP by the given number and provides additional parallelism at the cost of more DSPs and area.

- The total stream buffer size scales with the `num_lanes` parameter. Because the feature surface of a graph is divided across multiple lanes, adjust the `stream_buffer_depth` parameter listed in the `.arch` file by the inverse of the `num_lanes` parameter value. For example, a 4-lane architecture with 10k stream buffer depth indicates a 40k total stream buffer size.

When the value of the `num_lanes` parameter of architecture is greater than 1, the architecture is subject to the following limitations:

- All `c_vector` and `k_vector` values in the architecture must be the same

- The softmax auxiliary module is not supported.

*Legal values:* [1,2,4]

#### Parameter: `arch_precision`

This parameter sets the precision (in bits) of the internal numeric representation used by FPGA AI Suite IP. Lower values increase fps and reduce area, but at the cost of inference accuracy.

Each internal precision option corresponds to a different number of sign and mantissa bits, and uses either two's complement or sign+magnitude. For details, refer to the table in [FPGA AI Suite IP Block Configuration](#) on page 14.

The FP16 precision significantly increases the size of the resulting IP, but can improve accuracy (particularly in models that have not been retrained for low precision).

All numeric options use block floating point format. In block floating point format, each block of size CVEC shares a common exponent. Both CVEC (c\_vector) and arch\_precision affect the accuracy of the inference. However, the impact of c\_vector is generally small, while the impact of the arch\_precision setting is relatively large.

The block floating point format used by the FPGA AI Suite IP is directly compatible with graphs that use INT8 symmetric quantization. INT8 symmetric quantization requires that all operations going from floating point to integer, and vice versa, require only scaling (multiplication or division). When given a graph with INT8 weights, the FPGA AI Suite compiler sets the exponent of the block floating point weights so the original INT8 weights can be used directly as the mantissa. This setting limits the use of INT8 weights to architectures where the mantissa is 8-bits or larger.

The use of INT8 graphs does not significantly affect either the inference speed or the FPGA resource consumption. All inference, regardless of whether block floating point is used, is performed with the same hardware.

In addition to selecting a compatible numeric precision, set the pe\_array/enable\_scale parameter to true in order to support graphs with INT8 quantization.

The example architectures that are included with the FPGA AI Suite are already set to the recommended arch\_precision parameter values for their supported FPGA family. In some cases, it is useful to select a different arch\_precision value. FP11 is the lowest precision option, but requires the least number of RAM blocks, and slightly reduces the amount of external memory traffic. The FP12AGX significantly reduces the number of DSPs required to implement the PE array, but logic utilization may increase.

Agilex 5 devices implement enhanced DSPs with AI tensor blocks. To take advantage of AI tensor blocks, set the arch\_precision value to FP12AGX or FP11 and use interleave values of 12x1.

For more details about the block floating point format, refer to the [Low-Precision Networks for Efficient Inference on FPGAs](#) white paper.

Legal values:

| FPGA Device Family | Supported arch_precision Values                                                                                      |

|--------------------|----------------------------------------------------------------------------------------------------------------------|

| Agilex 5           | <ul style="list-style-type: none"> <li>FP11</li> <li>FP12AGX</li> <li>FP13AGX</li> <li>FP16 (less common)</li> </ul> |

| Agilex 7           | <ul style="list-style-type: none"> <li>FP11</li> <li>FP13AGX</li> <li>FP16 (less common)</li> </ul>                  |

*continued...*

| FPGA Device Family | Supported arch_precision Values                                                    |

|--------------------|------------------------------------------------------------------------------------|

| Arria 10           | <ul style="list-style-type: none"> <li>FP11</li> <li>FP16 (less common)</li> </ul> |

| Cyclone 10 GX      | <ul style="list-style-type: none"> <li>FP11</li> <li>FP16 (less common)</li> </ul> |

| Stratix 10         | <ul style="list-style-type: none"> <li>FP11</li> <li>FP16 (less common)</li> </ul> |

**Table 4. Multiplication Operations per DSP**

| Precision | FPGA Device Family                      |          |                   |

|-----------|-----------------------------------------|----------|-------------------|

|           | Arria 10<br>Cyclone 10 GX<br>Stratix 10 | Agilex 7 | Agilex 5          |

| FP11      | 4                                       | 4        | 20 <sup>(*)</sup> |

| FP12AGX   | –                                       | –        | 20 <sup>(*)</sup> |

| FP13AGX   | –                                       | 4        | 4 <sup>(**)</sup> |

| FP16      | 2                                       | 2        | 2                 |

INT8 symmetric quantization is enabled by FP12AGX and higher precision options.

The total number of multipliers required by the PE Array will be equal to CVEC \* KVEC \* num\_lanes. Due to quantization, this calculation underpredicts the number of DSPs required when using Agilex 5 DSP tensor mode. In addition, the PE Array requires KVEC \* num\_lanes DSPs to build the FP32 accumulators.

**Parameter: stream\_buffer\_depth**

This parameter controls the depth of the stream buffer. The stream buffer is used as the on-chip cache for feature (image) data. Larger values increase area (logic and block RAM) but also increase performance.

Typically the architecture optimizer is used to set this parameter.

*Legal values:* [2048-262144]

**Parameter: enable\_eltwise\_mult**

This parameter enables the Elementwise multiplication layer. This layer is required for MobileNetV3.

(\*) Assumes a 12x1 interleave.

(\*\*) The Agilex 5 DSP block supports six multipliers per block, but currently FPGA AI Suite uses only four of them.

**Parameters: filter\_size\_width\_max, filter\_size\_height\_max**

These parameters determine the maximum size of a convolution filter, which also relates the maximum window size for Average Pool.

The maximum window size for Average Pool is no larger than the value determined by the following formula:  $\min(\text{filter\_size\_width\_max}, \text{file\_size\_height\_max}) - 1$ . In addition, the Average Pool window size may be limited by the filter\_scratchpad and filter\_depth parameters.

*Legal values:* [14,28]

**Parameters: output\_image\_height\_max, output\_image\_width\_max, output\_channels\_max**

These parameters control the maximum size of the output tensor.

The default maximum size is 128x128, with up to 8192 channels

**Parameter: enable\_debug**

This parameter toggles the FPGA AI Suite debug network to allow forwarding of read requests from the CSR to one of many externally-attached debug-capable modules.

Generally not required for production architectures.

*Legal values:* [true, false]

**Parameter: enable\_layout\_transform**

The parameter enables the dedicated input tensor transform module in the FPGA AI Suite IP. When enabled, the dedicated layout transform hardware transforms the input tensor format and folds the inputs into channels.

You can use the layout transform in streaming and non-streaming configurations of the FPGA AI Suite IP. The transform is particularly useful for doing fast and deterministic tensor preprocessing in hostless applications, or applications where the hard-processor is slow or highly loaded.

However, the layout transform comes with an FPGA area cost that scales mainly with the input data bus width, maximum tensor/stride dimensions, and CVEC. In particular, instances where the value of `max_stride_width`  $\times$  `max_stride_height`  $\times$  `max_channels` is greater than the CVEC value consume significant memory resources due to the buffer space required for the overflowing CVEC.

In graphs where the first convolution stride dimensions are unity, no folding can be done, and the layout transform cannot optimize the layout of the input tensor. In such a case, try doing a lighter-weight transformation operation outside of the FPGA AI Suite IP.

When this parameter is enabled, configure the transform with the parameters as described in [Parameter Group: layout\\_transform\\_params](#) on page 31. For information about the layout transformation operation and hardware, refer to [Input Layout Transform Hardware](#) on page 36.

The hardware layout transform is not supported in SoC designs in streaming-to-memory (S2M) mode. the S2M design uses a lightweight, external transform module.

### 2.5.2.2. Parameter Group: activation

This parameter group configures the activation module. These activation functions are common in deep learning, and it is beyond the scope of this document to describe them.

Different activation functions can be enabled or disabled to suit the graph to be run. Disabling unnecessary activations functions can reduce area.

#### Parameter: activation/enable\_relu

This parameter enables or disables the Rectified Linear Unit (ReLU) activation function.

*Legal values:* [true, false]

#### Parameter: activation/enable\_leaky\_relu

This parameter enables or disables the Leaky ReLU activation function. This activation function is a superset of the ReLU activation function.

*Legal values:* [true, false]

#### Parameter: activation/enable\_prelu

This parameter enables or disables the Parametric ReLU activation function. This activation function is a superset of the Leaky ReLU activation function.

*Legal values:* [true, false]

#### Parameter: activation/enable\_clamp

This parameter enables or disables the clamp function. Enabling the clamp function also enables a ReLU6 activation function.

*Legal values:* [true, false]

#### Parameter: activation/enable\_round\_clamp

This parameter enables or disables the round\_clamp function. Enabling the round\_clamp function also enables ReLU.

If both enable\_clamp and enable\_round\_clamp are set, enable\_round\_clamp takes priority over enable\_clamp when implementing ReLU.

*Legal values:* [true, false]

#### Parameter: activation/enable\_sigmoid

This parameter enables or disables the Sigmoid and Swish activation functions.

As a side-effect, enabling these activation functions also enables the Tanh and Reciprocal activation function. This side-effect might change in a future release, so the best practice is to enable activation function explicitly instead of depending on the side-effect.

*Legal values:* [true, false]

#### **Parameter activation/enable\_tanh**

This parameter enables or disables the Tanh activation function.

As a side-effect, enabling this activation functions also enables the Sigmoid, Swish, and Reciprocal activation functions. This side-effect might change in a future release, so the best practice is to enable activation functions explicitly instead of depending on the side-effect.

*Legal value:* [true, false]

### **2.5.2.3. Parameter Group: pe\_array**

This parameter group configures the PE Array. The PE Array is used to calculate dot products.

#### **Parameter: pe\_array/dsp\_limit**

Use this parameter to force the PE array to implement multipliers in ALM logic on the FPGA.

The number of multipliers that the PE requires is determined by the `k_vector` and `c_vector` global parameters. Given the value of the `arch_precision` global parameter and the target architecture (for example, Arria 10 or Agilex 7), the number of multipliers determines the number of DSPs that the PE Array tries to use. If this number exceeds the value set in the `dsp_limit` parameter, then some multipliers are implemented in ALM logic to ensure that the PE Array DSP usage does not exceed the limit set by the `dsp_limit` parameter.

If this option is omitted, then all multipliers are implemented in the FPGA AI Suite IP as DSPs.

Typically, this parameter is set by the architecture optimizer.

#### **Parameters: pe\_array/num\_interleaved\_features, pe\_array/num\_interleaved\_filters**

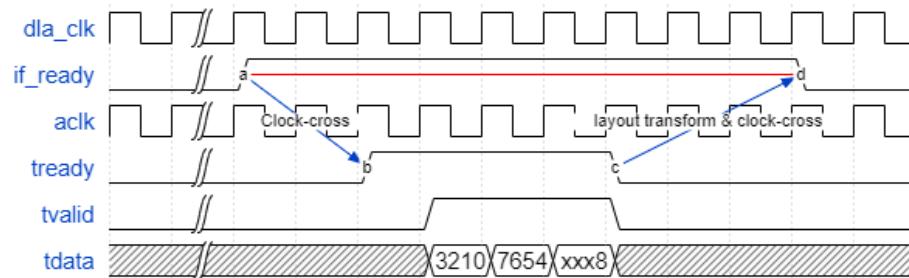

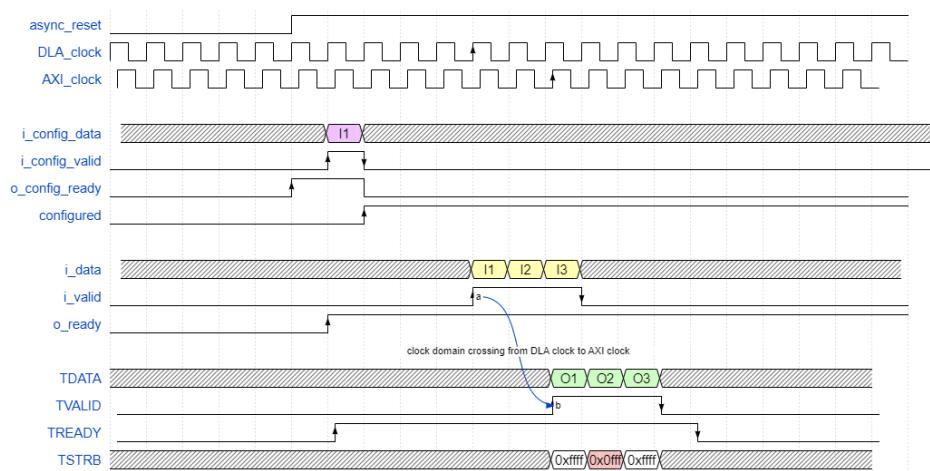

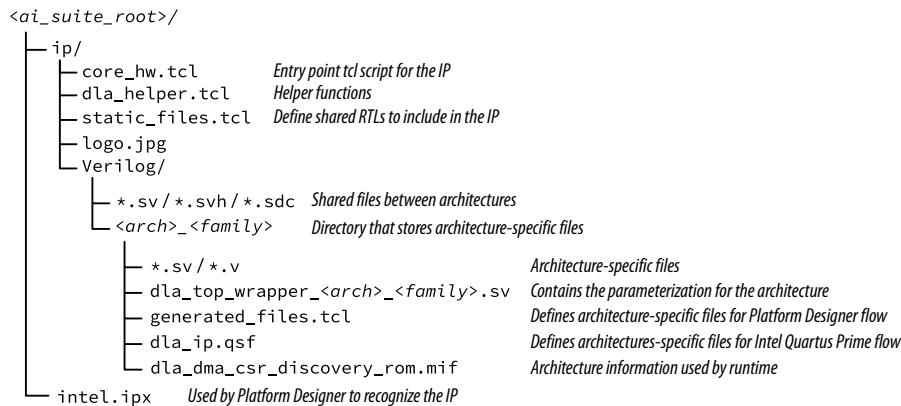

To support layers with bias values, the PE array uses a threaded accumulator that is time-multiplexed to handle multiple accumulations. Each accumulation corresponds to an output filter and feature.