# dsPIC33 DSC Product Selection Guide

## Quick Reference Guide

1: dsPIC33 DSCs offer SAR ADC and high-speed ADC    2: dsPIC33 DSCs offer general-purpose DAC and audio DAC    3: Hardware Safety Features: L1: Includes WDT, oscillator fail-safe, illegal opcode detect, TRAP, reset trace, register lock, frequency check, CodeGuard™ security, PWM lock\*    L2: Includes features of L1 + CRC    L3: Includes features of L2 + Flash ECC and/or DMT    L4: Includes features of L3 + RAM MBIST    L5: Includes L4 + ECC RAM + IOIM    \*PWM lock available in devices with MC PWM/SMPS PWM peripheral (5V) dsPIC33 DSCs with 5V operating Voltage    Note: Similar family of devices with fewer variations are grouped with the same color coding

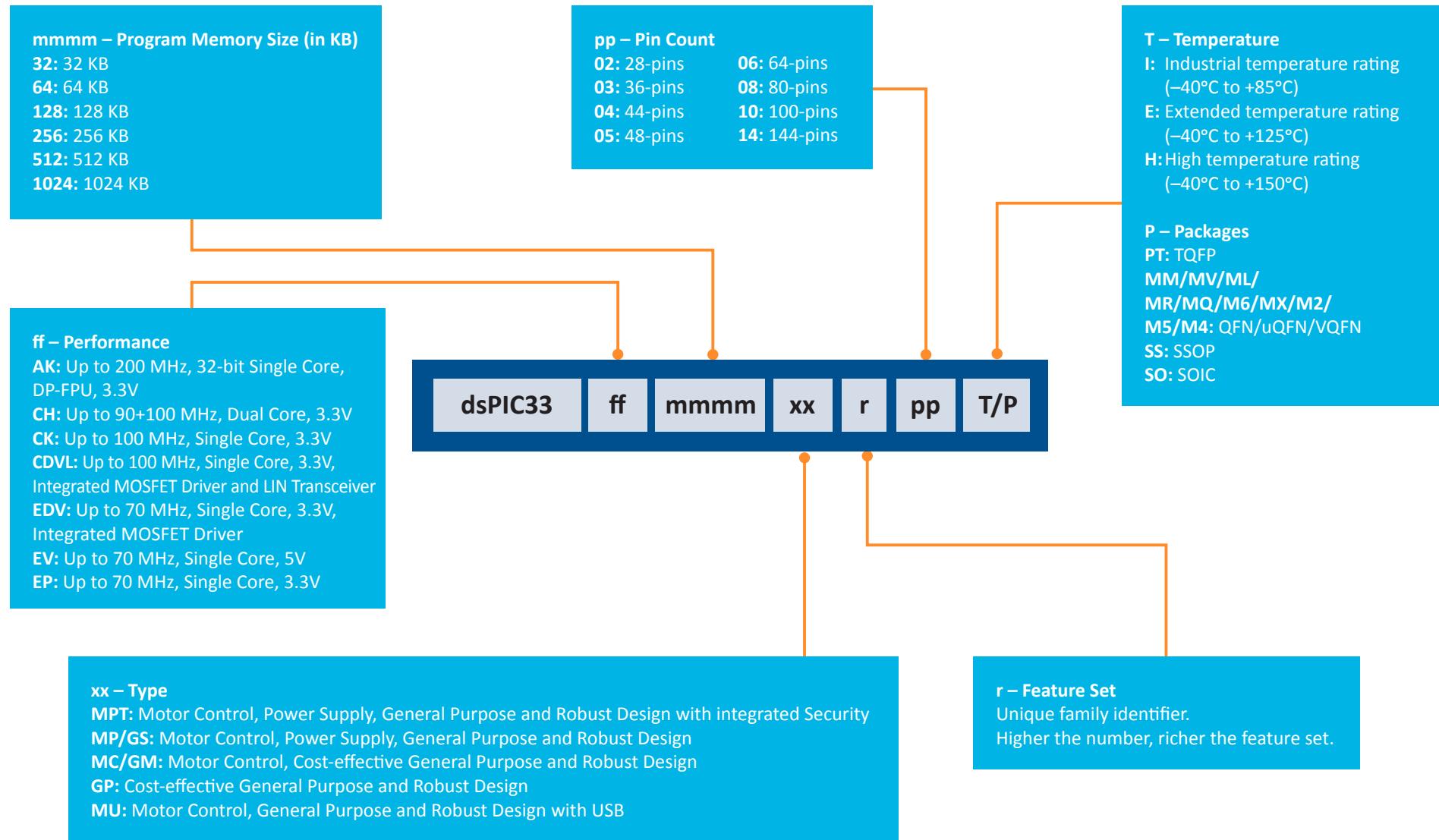

# dsPIC33 DSC Part Number Decoder

| INTEGRATED ANALOG: Sensor Interfacing and Signal Conditioning                 |                                                                                                                                                                               |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>ADC: Analog-to-Digital Converter</b>                                       | General-purpose ADC with up to 10-/12-bit resolution                                                                                                                          |

| <b>HS ADC: High-Speed Analog-to-Digital Converter</b>                         | High-speed SAR ADC with 12-bit resolution and sampling speed of 10 Msps                                                                                                       |

| <b>DAC: Digital-to-Analog Converter</b>                                       | General-purpose DAC with resolution up to 16-bit resolution                                                                                                                   |

| <b><math>\Delta\Sigma</math> DAC: Delta-Sigma Digital-to-Analog Converter</b> | Second-order digital bipolar, two output channel Delta-Sigma DAC with stereo operation support                                                                                |

| <b>HS Comp: High-Speed Comparator</b>                                         | General-purpose rail-to-rail comparator with <1 ns response time                                                                                                              |

| <b>OPA/PGA: Operational Amplifier and Programmable Gain Amplifiers</b>        | General-purpose op amp and PGAs for internal and external signal source conditioning                                                                                          |

| WAVEFORM CONTROL: PWM Drive and Waveform Generation                           |                                                                                                                                                                               |

| <b>SCCP: Single Capture/Compare/PWM</b>                                       | Multi-purpose 16-/32-bit input capture, output compare and PWM                                                                                                                |

| <b>MCCP: Multiple Capture/Compare/PWM</b>                                     | Multi-purpose 16-/32-bit input capture, output compare and PWM with up to six outputs and an extended range of output control features                                        |

| <b>PWM: Pulse Width Modulation</b>                                            | 16-bit PWM with up to nine independent time bases                                                                                                                             |

| <b>MC PWM: Motor Control Pulse Width Modulation</b>                           | Motor control 16-bit PWM with multiple synchronized pulse-width modulation, up to six outputs with four duty cycle generators and resolution up to 1 ns                       |

| <b>SMPS PWM: Power Supply Pulse Width Modulation</b>                          | Power supply 16-bit PWM with multiple synchronized pulse-width modulation, up to eight outputs with four independent time bases and resolution up to 1 ns                     |

| <b>IC: Input Capture</b>                                                      | Input capture with an independent timer base to capture an external event                                                                                                     |

| <b>OC: Output Compare</b>                                                     | Output compare with an independent time base to compare value with compare registers and generate a single output pulse, or a train of output pulses on a compare match event |

| TIMERS AND INTERFACES                                                         |                                                                                                                                                                               |

| <b>Host BiSS Interface</b>                                                    | Host bidirectional Serial Synchronous (BiSS) is a digital interface for actuators used in position control                                                                    |

| <b>16-/32-bit Timer</b>                                                       | General-purpose 16-/32-bit timer/counter with compare capability                                                                                                              |

| <b>QEI: Quadrature Encoder Interface</b>                                      | Quadrature encoder interface to increment encoders for obtaining mechanical position data                                                                                     |

| SAFETY AND MONITORING: Hardware Monitoring and Fault Detection                |                                                                                                                                                                               |

| <b>Error Correction Code</b>                                                  | ECC detects the presence of single and double bit errors, and corrects single bit error automatically                                                                         |

| <b>RAM MBIST: Memory Built-In Self-Test</b>                                   | RAM MBIST tests for functional correctness of all memory locations                                                                                                            |

| <b>WDT: Watch Dog Timer</b>                                                   | System supervisory circuit that generates a reset when software timing anomalies are detected within a configurable critical window                                           |

| <b>DMT: Dead Man Timer</b>                                                    | System supervisory circuit that generates a reset when instruction sequence anomalies are detected within a configurable critical window                                      |

| <b>CRC: Cyclical Redundancy Check with Memory Scan</b>                        | Automatically calculates CRC checksum of Program/DataEE memory for NVM integrity and a general-purpose 16-bit CRC for use with memory and communications data                 |

| <b>IO Integrity Monitors (IOIM)</b>                                           | The module validates the IO functionality in safety-critical applications by checking an output signal against a reference                                                    |

| <b>Hardware Safety Features</b>                                               | Hardware Safety features include Flash error correction, RAM MBIST, backup system oscillator, WDT, DMT, CRC scan, etc.                                                        |

| <b>Functional Safety - ISO 26262/IEC 61508</b>                                | Functional Ready Devices are ideal for automotive and industrial safety applications requiring ISO 26262 (ASIL B/C) and IEC 61508 (SIL 2/3) safety compliance.                |

| <b>IEC 60730 Class B Safety</b>                                               | IEC 60730 Functional Safety Ready Devices offers Class B safety diagnostic libraries for designing household applications                                                     |

| COMMUNICATIONS: General, Industrial, Lighting and Automotive |                                                                                                                                                                             |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>USB OTG: Universal Serial Bus</b>                         | USB 2.0 full-speed (host and device), low-speed (host) and On-The-Go (OTG) support                                                                                          |

| <b>CAN/CAN FD: Controller Area Network</b>                   | Industrial- and automotive-centric communication bus                                                                                                                        |

| <b>UART: Universal Asynchronous Receiver Transceiver</b>     | General-purpose full-duplex, 8-bit or 9-bit data serial communications with optional ISO 7816 Smart Card support                                                            |

| <b>LIN: Local Interconnect Network</b>                       | 1. Industrial- and automotive-centric communication bus<br>2. Support for LIN when using the EUSART                                                                         |

| <b>I<sup>2</sup>C: Inter-Integrated Circuit</b>              | General purpose 2-wire inter IC serial interface for communicating with other peripherals or microcontroller devices                                                        |

| <b>SPI: Serial Peripheral Interface</b>                      | General-purpose 4-wire synchronous serial interface for communicating with other peripherals or microcontroller devices                                                     |

| <b>I<sup>2</sup>S: Data Converter Interface</b>              | 3-wire synchronous half duplex serial interface to handle the stereo data                                                                                                   |

| <b>SENT: Single-Edge Nibble Transmission</b>                 | SENT is an unidirectional, single-wire serial communications protocol designed for point-to-point transmission of signal values                                             |

| USER INTERFACE: CAPACITIVE TOUCH SENSING                     |                                                                                                                                                                             |

| <b>Capacitive Touch Sensing</b>                              | Capacitive sensing for touch buttons, sliders and system measurement and deduction (e.g. water level, intrusion detection, etc)                                             |

| EMBEDDED SECURITY                                            |                                                                                                                                                                             |

| <b>Security Access Control</b>                               | Helps in realizing secure boot, secure firmware update, secure debug access control, code protection and device locking                                                     |

| <b>CodeGuard Security - Secure Boot</b>                      | Allows devices to configure the boot segment as a read-only section of memory to protect the bootloader from modification via remote digital attacks.                       |

| <b>Flash OTP by ICSP™ Write Inhibit</b>                      | Flash OTP by ICSP™ Write Inhibit enables Flash to be configured as One-Time Programmable (OTP) memory with the ability to write and read protect the Flash memory           |

| <b>Integrated Secure Subsystem (HSM)</b>                     | Supports implementing secure boot, Message Authentication, trusted firmware updates, mutual node authentication and multiple key management protocols                       |

| SYSTEM FLEXIBILITY: System Peripherals and Interconnects     |                                                                                                                                                                             |

| <b>Dual Partition Flash</b>                                  | Dual partition Flash operation, allowing the support of robust bootloader systems and fail-safe storage of application code, with options designed to enhance code security |

| <b>CLC: Configurable Logic Cell</b>                          | Integrated combinational and sequential logic with custom interconnection and re-routing of digital peripherals                                                             |

| <b>PPS: Peripheral Pin Select</b>                            | I/O pin remapping of digital peripherals for greater design flexibility and improved EMI board layout                                                                       |

| <b>PTG: Peripheral Trigger Generator</b>                     | User-programmable sequencer, capable of generating complex trigger signal sequences to coordinate the operation of other peripherals                                        |

| <b>DMA: Direct Memory Access</b>                             | Direct memory access for transfer of data between the CPU and its peripherals without CPU assistance                                                                        |

| <b>DOZE, IDLE, SLEEP and PMD</b>                             | Low-power saving modes                                                                                                                                                      |

Learn more about dsPIC33 DSCs at

[www.microchip.com/dsPIC](http://www.microchip.com/dsPIC)