## 1. General description

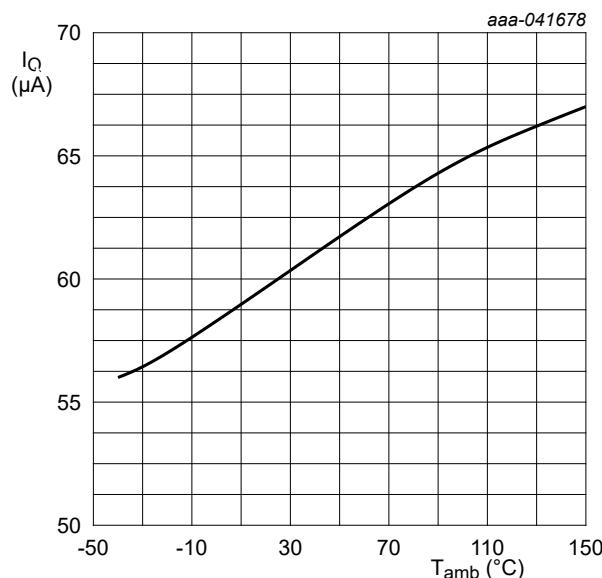

The NEX40400 is a high efficiency step-down converter with low operating quiescent current of typically 60  $\mu$ A. It provides up to 600 mA output with current mode control for fast loop response.

The wide 4.5 V to 40 V input range is suitable for variety of the power step-down applications in industrial and automotive environments. 0.3  $\mu$ A ultra-low shutdown supply current allows use in battery-powered applications.

High power conversion efficiency across a wide load range is achieved by folding down the switching frequency at light load condition reducing the switching losses.

Frequency foldback helps to prevent inductor current runaway during start-up and to allow operation in both high conversion ratio and low drop-out cases. Thermal shutdown provides reliable and robust operation.

The NEX40400 comes in a cost-effective 6 leads SOT8061-1 (TSOT23-6) plastic, surface-mounted package with 2.9 mm x 1.6 mm body dimensions.

## 2. Features and benefits

- 4.5 V to 40 V wide input voltage range

- 600 mA continuous output current

- 60  $\mu$ A standby, 0.3  $\mu$ A shutdown current

- 1% output voltage accuracy

- 1.05 MHz and 2.1 MHz fixed switching frequency

- Pulse Frequency Modulation (PFM) option for light load efficiency

- Frequency foldback for high conversion ratio and low drop-out applications

- Force PWM (FPWM) option for small output ripple

- Spread spectrum for better EMI

- Start-up with pre-biased output

- Precision enable

- Internal compensation

- Short circuit protection with Hiccup mode

- SOT8061-1 (TSOT23-6) 6 leads, plastic surface-mounted package

## 3. Target applications

- Industrial distributed power systems

- Grid infrastructure: Smart E-meter

- Battery powered home appliances

- White goods

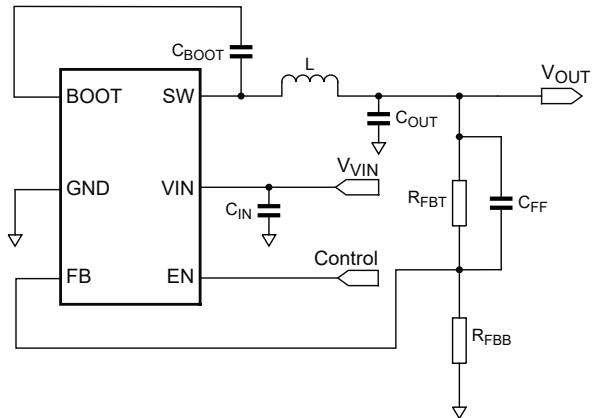

aaa-041703

Fig. 1. Typical application circuit

$V_{OUT} = 5$  V,  $f_{SW} = 1.05$  MHz

|                            |                            |

|----------------------------|----------------------------|

| (1) PFM, $V_{VIN} = 8$ V   | (5) PFM, $V_{VIN} = 24$ V  |

| (2) PFM, $V_{VIN} = 12$ V  | (6) FPM, $V_{VIN} = 40$ V  |

| (3) FPWM, $V_{VIN} = 8$ V  | (7) FPWM, $V_{VIN} = 24$ V |

| (4) FPWM, $V_{VIN} = 12$ V | (8) FPWM, $V_{VIN} = 40$ V |

Fig. 2. Efficiency versus load current

## 4. Ordering information

**Table 1. Ordering information**

| Type number                 | Package           |          |                                                         |                           |

|-----------------------------|-------------------|----------|---------------------------------------------------------|---------------------------|

|                             | Temperature range | Name     | Description                                             | Version                   |

| <a href="#">NEX40400ADA</a> | -40 °C to +150 °C | TSOT23-6 | Plastic, surface-mounted package (TSOT23-6);<br>6 leads | <a href="#">SOT8061-1</a> |

| <a href="#">NEX40400BDA</a> |                   |          |                                                         |                           |

| <a href="#">NEX40400CDA</a> |                   |          |                                                         |                           |

| <a href="#">NEX40400DDA</a> |                   |          |                                                         |                           |

| <a href="#">NEX40400EDA</a> |                   |          |                                                         |                           |

| <a href="#">NEX40400FDA</a> |                   |          |                                                         |                           |

## 5. Marking

**Table 2. Marking**

| Type number  | Marking code |

|--------------|--------------|

| NEX40400ADAZ | N4A          |

| NEX40400BDAZ | N4B          |

| NEX40400CDAZ | N4C          |

| NEX40400DDAZ | N4D          |

| NEX40400EDAZ | N4E          |

| NEX40400FDAZ | N4F          |

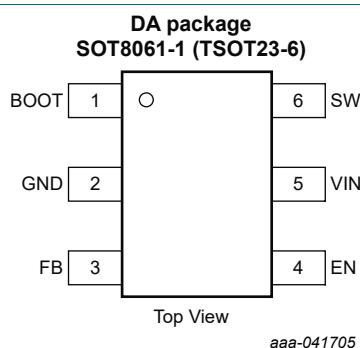

## 6. Pinout

### 6.1. Pinout

Fig. 3. Pin configuration SOT8061-1 (TSOT23-6)

### 6.2. Pin description

Table 3. Pin description

| Pin    |      | I/O | Description                                                                                                                                                                                             |

|--------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Name |     |                                                                                                                                                                                                         |

| 1      | BOOT | PWR | Bootstrap capacitor connection for high-side FET drive. Connect 100 nF or larger capacitor between the BOOT pin and SW pin.                                                                             |

| 2      | GND  | PWR | Power ground pin, internally connected to the source of low-side FET. Connect to system ground. Path to the input decoupling capacitor must be short.                                                   |

| 3      | FB   | IN  | Inverting input of the error amplifier. Connect FB pin to the middle of a resistor divider of the converter output to set the target output voltage.                                                    |

| 4      | EN   | IN  | Precision enable input of the converter. High level enables converter. Can be tied to VIN. Adjustable UVLO can be achieved by connecting EN to the middle of a resistor divider between VIN and ground. |

| 5      | VIN  | PWR | Power supply input for internal bias LDO and high-side FET. Place 2.2 $\mu$ F or larger decoupling capacitor between VIN and ground close to this pin.                                                  |

| 6      | SW   | OUT | The switch pin is connected to the internal power MOSFET switches. Connect SW pin to the inductor of the output LC filter.                                                                              |

## 7. Device Comparison

Table 4. Device Comparison

| Type number  | Operation Mode | Spread Spectrum | Switching Frequency |

|--------------|----------------|-----------------|---------------------|

| NEX40400ADAZ | PFM            | Off             | 2.1 MHz             |

| NEX40400BDAZ | FPWM           | Off             | 2.1 MHz             |

| NEX40400CDAZ | FPWM           | On              | 2.1 MHz             |

| NEX40400DDAZ | PFM            | Off             | 1.05 MHz            |

| NEX40400EDAZ | FPWM           | Off             | 1.05 MHz            |

| NEX40400FDAZ | FPWM           | On              | 1.05 MHz            |

## 8. Limiting values

**Table 5. Limiting values**

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

| Symbol        | Parameter            | Conditions            | Min  | Max             | Unit |

|---------------|----------------------|-----------------------|------|-----------------|------|

| $V_{VIN}$     | supply voltage       |                       | -0.3 | +42             | V    |

| $V_{SW}$      | switch node voltage  | DC                    | -0.3 | $V_{VIN} + 0.3$ | V    |

|               |                      | AC, less than 20 ns   | -3.5 | $V_{VIN} + 0.3$ | V    |

| $V_{EN}$      | EN pin voltage       |                       | -0.3 | $V_{VIN} + 0.3$ | V    |

| $V_{FB}$      | FB pin voltage       |                       | -0.3 | +6              | V    |

| $V_{BOOT-SW}$ | BOOT pin voltage     | Referenced to SW node | -0.3 | +6              | V    |

| $T_j$         | junction temperature |                       | -40  | +150            | °C   |

| $T_{stg}$     | storage temperature  |                       | -65  | +150            | °C   |

## 9. Recommended operating conditions

**Table 6. Recommended operating conditions**

| Symbol    | Parameter            | Min | Nom | Max       | Unit |

|-----------|----------------------|-----|-----|-----------|------|

| $V_{CCA}$ | supply voltage       | 4.5 |     | 40        | V    |

| $I_{OUT}$ | output current       | 0   |     | 0.6       | A    |

| $V_{EN}$  | enable input         | 0   |     | $V_{VIN}$ | V    |

| $V_{FB}$  | feedback input       |     | 0.8 |           | V    |

| $T_j$     | junction temperature | -40 |     | 150       | °C   |

## 10. ESD ratings

**Table 7. ESD ratings**

| Symbol    | Parameter                       | Conditions                           | Value  | Unit |

|-----------|---------------------------------|--------------------------------------|--------|------|

| $V_{ESD}$ | electrostatic discharge voltage | HBM: ANSI/ESDA/JEDEC JS-001 class 2  | ± 2000 | V    |

|           |                                 | CDM: ANSI/ESDA/JEDEC JS-002 class C3 | ± 500  | V    |

## 11. Thermal characteristics

**Table 8. Thermal characteristics**

| Symbol        | Parameter                                                 | Condition                        | SOT402-1 | Unit |

|---------------|-----------------------------------------------------------|----------------------------------|----------|------|

| $R_{th(j-a)}$ | thermal resistance from junction to ambient               | in free air;<br>JEDEC test board | 90       | °C/W |

| $R_{th(j-c)}$ | thermal resistance from junction to case (top) of package | in free air;<br>JEDEC test board | 32       | °C/W |

## 12. Characteristics

### 12.1. Electrical characteristics

Table 9. Electrical characteristics

$V_{VIN} = 4.5 \text{ V to } 40 \text{ V}$ , typical values are at  $T_j = 25^\circ\text{C}$  (unless otherwise noted)

| Symbol                            | Parameter                                     | Test Conditions                                                                        | $T_j = -40^\circ\text{C to } 150^\circ\text{C}$ |      |      | Unit             |

|-----------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------|------|------|------------------|

|                                   |                                               |                                                                                        | Min                                             | Typ  | Max  |                  |

| <b>Supply (VIN pin)</b>           |                                               |                                                                                        |                                                 |      |      |                  |

| $I_Q$                             | operating quiescent current (non-switching)   | PFM variants, $V_{VIN} = 12 \text{ V}$ , $V_{EN} = V_{VIN}$ , $V_{FB} = 0.9 \text{ V}$ | -                                               | 60   | 100  | $\mu\text{A}$    |

| $I_{SD}$                          | shutdown current                              | $V_{VIN} = 12 \text{ V}$ , $EN = \text{GND}$                                           | -                                               | 0.3  | 1.5  | $\mu\text{A}$    |

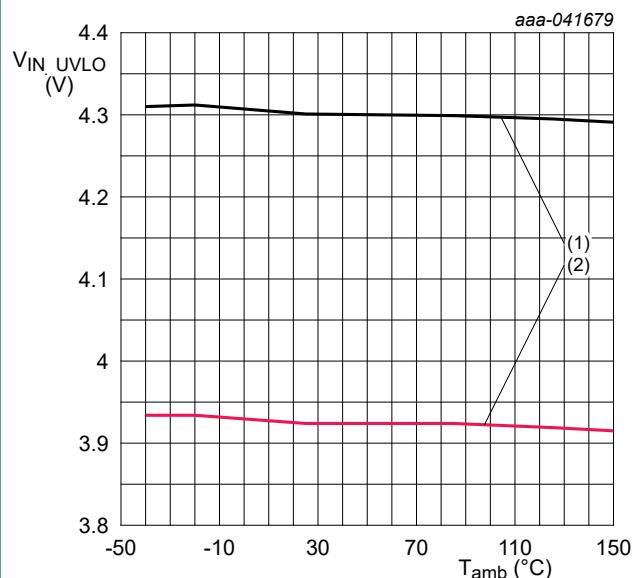

| $V_{IN\_UVLO+}$                   | undervoltage lockout threshold                | rising $V_{VIN}$                                                                       | -                                               | 4.3  | 4.4  | V                |

| $V_{IN\_UVLO-}$                   |                                               | falling $V_{VIN}$                                                                      | 3.8                                             | 3.9  | -    | V                |

| <b>Enable (EN pin)</b>            |                                               |                                                                                        |                                                 |      |      |                  |

| $V_{EN\_H}$                       | enable rising threshold                       |                                                                                        | -                                               | 1.23 | 1.30 | V                |

| $V_{EN\_L}$                       | enable falling threshold                      |                                                                                        | 1.0                                             | 1.1  | -    | V                |

| $V_{EN\_HYS}$                     | enable hysteresis voltage                     |                                                                                        | -                                               | 0.13 | -    | V                |

| $I_{EN}$                          | leakage current at EN                         | $V_{VIN} = 12 \text{ V}$ , $V_{EN} = 3.3 \text{ V}$                                    | -                                               | 10   | 100  | nA               |

| <b>Power switches</b>             |                                               |                                                                                        |                                                 |      |      |                  |

| $R_{ON\_HS}$                      | high side MOSFET on-resistance                | $V_{VIN} = 12 \text{ V}$ , $V_{BOOT} - V_{SW} = 5 \text{ V}$ , $I = 200 \text{ mA}$    | -                                               | 440  | 800  | $\text{m}\Omega$ |

| $R_{ON\_LS}$                      | low side MOSFET on-resistance                 | $V_{VIN} = 12 \text{ V}$ , $I = 200 \text{ mA}$                                        | -                                               | 240  | 450  | $\text{m}\Omega$ |

| $t_{ON\_MIN}$                     | minimum ON time                               |                                                                                        | -                                               | 45   | -    | ns               |

| $t_{OFF\_MIN}$                    | minimum OFF time                              | 1.05 MHz FPWM variant                                                                  | -                                               | 100  | -    | ns               |

| $t_{ON\_MAX}$                     | maximum ON time                               |                                                                                        | -                                               | 10   | -    | $\mu\text{s}$    |

| $I_{HS\_LIMIT}$                   | peak inductor current limit                   |                                                                                        | 0.8                                             | 1.0  | 1.4  | A                |

| $I_{LS\_LIMIT}$                   | valley inductor current limit                 |                                                                                        | 0.5                                             | 0.65 | 0.8  | A                |

| $I_{LS\_ZC}$                      | zero cross threshold                          | PFM variants                                                                           | -                                               | 30   | -    | $\text{mA}$      |

| <b>Voltage reference (FB pin)</b> |                                               |                                                                                        |                                                 |      |      |                  |

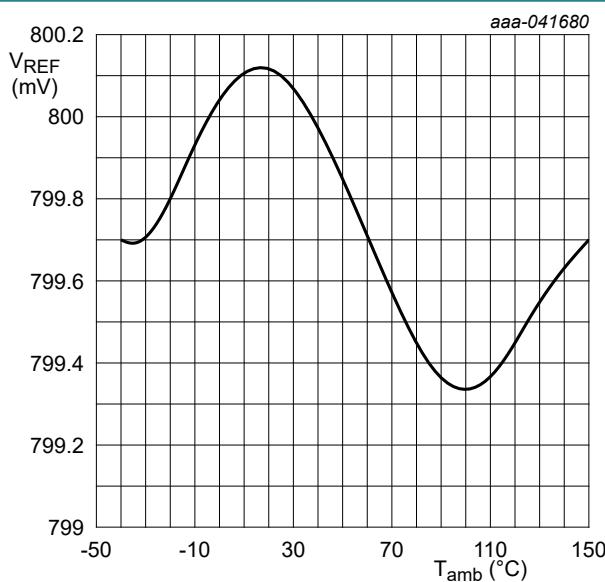

| $V_{REF}$                         | reference voltage                             | $T_j = 25^\circ\text{C}$                                                               | 792                                             | 800  | 808  | $\text{mV}$      |

|                                   |                                               | $T_j = -40^\circ\text{C to } 150^\circ\text{C}$                                        | 788                                             | 800  | 812  | $\text{mV}$      |

| $I_{FB}$                          | leakage current at FB pin                     | $V_{FB} = 0.85 \text{ V}$                                                              | -                                               | 5    | 50   | nA               |

| <b>Oscillator</b>                 |                                               |                                                                                        |                                                 |      |      |                  |

| $f_{SW}$                          | oscillator frequency                          | 1.05 MHz variants                                                                      | 0.94                                            | 1.05 | 1.16 | MHz              |

|                                   |                                               | 2.1 MHz variants                                                                       | 1.88                                            | 2.1  | 2.32 | MHz              |

| $f_{SW\_SS}$                      | spread spectrum switching frequency variation |                                                                                        | -                                               | +/-5 | -    | %                |

| <b>Hiccup and soft start</b>      |                                               |                                                                                        |                                                 |      |      |                  |

| $t_{HIC\_WAIT}$                   | waiting time before hiccup shutdown           | $V_{FB} \leq 0.4 \times V_{REF}$                                                       | -                                               | 256  | -    | clock cycles     |

| $t_{HICCUP}$                      | hiccup shutdown time before restart           | PFM variants                                                                           | -                                               | 120  | -    | ms               |

| Symbol                        | Parameter                  | Test Conditions                                                                                                 | $T_j = -40^{\circ}\text{C}$ to $150^{\circ}\text{C}$ |     |     | Unit               |

|-------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----|-----|--------------------|

|                               |                            |                                                                                                                 | Min                                                  | Typ | Max |                    |

| $t_{\text{ss}}$               | internal soft-start time   | the time for internal reference to ramp up from 10% to 90% of $V_{\text{REF}}$ , $V_{\text{VIN}} = 12\text{ V}$ | -                                                    | 1.8 | -   | ms                 |

| <b>Overvoltage protection</b> |                            |                                                                                                                 |                                                      |     |     |                    |

| $V_{\text{FB\_OVP+}}$         | overvoltage threshold      | $V_{\text{FB}}$ is rising, % of $V_{\text{REF}}$                                                                | -                                                    | 109 | -   | %                  |

| $V_{\text{FB\_OVP-}}$         |                            | $V_{\text{FB}}$ is falling, % of $V_{\text{REF}}$                                                               | -                                                    | 104 | -   | %                  |

| <b>Thermal shutdown</b>       |                            |                                                                                                                 |                                                      |     |     |                    |

| $T_{\text{SHDN}}$             | thermal shutdown threshold | rising junction temperature                                                                                     | -                                                    | 170 | -   | $^{\circ}\text{C}$ |

| $T_{\text{HYS}}$              | hysteresis                 |                                                                                                                 | -                                                    | 15  | -   | $^{\circ}\text{C}$ |

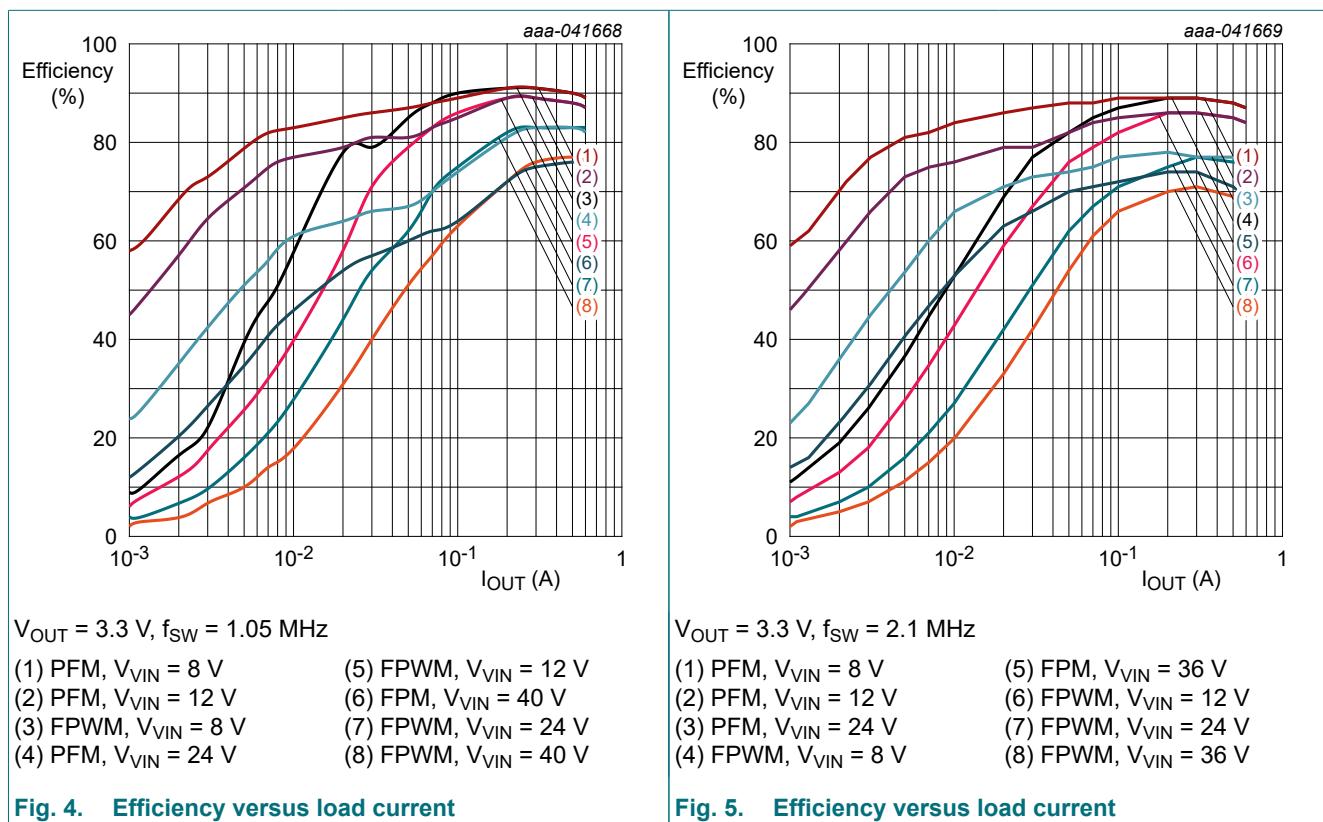

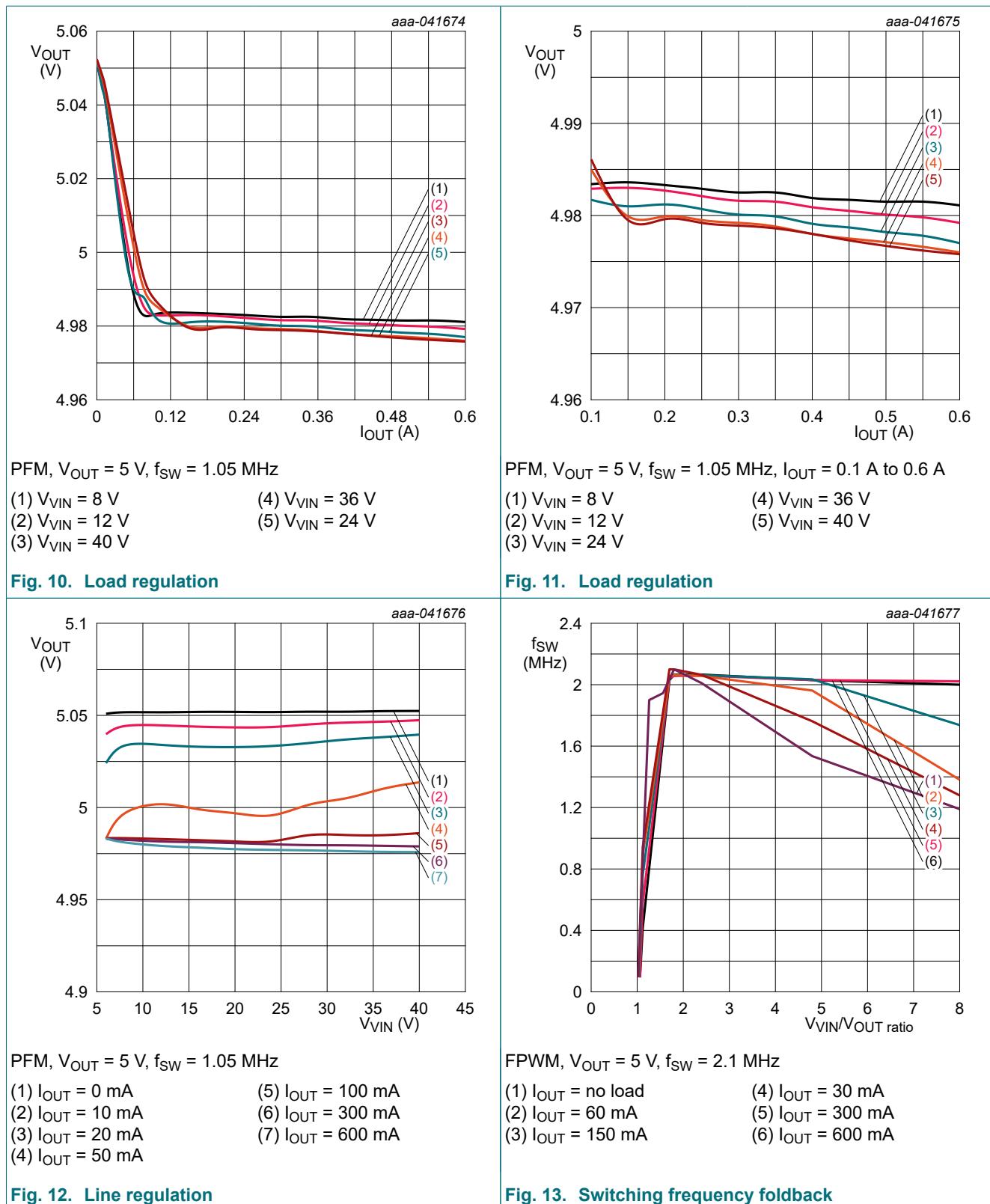

## 12.2. Typical characteristics

At recommended operating conditions; voltages are referenced to GND (ground = 0 V); typical values are at  $25^{\circ}\text{C}$  (unless otherwise noted).

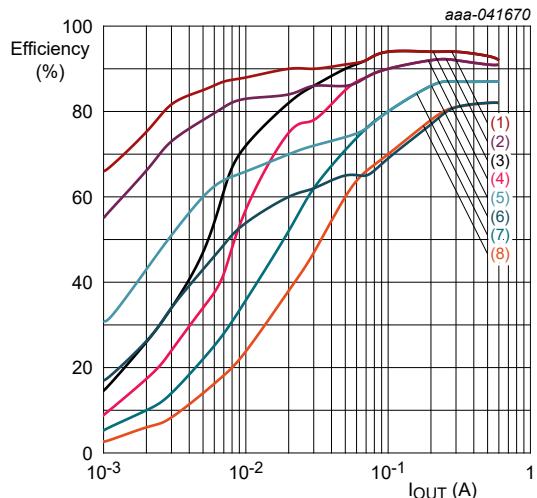

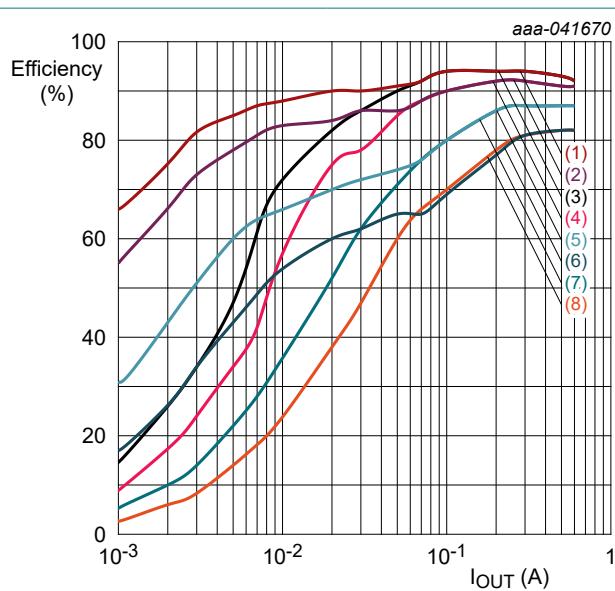

$V_{OUT} = 5$  V,  $f_{SW} = 1.05$  MHz

- (1) PFM,  $V_{VIN} = 8$  V

- (2) PFM,  $V_{VIN} = 12$  V

- (3) FPWM,  $V_{VIN} = 8$  V

- (4) FPWM,  $V_{VIN} = 12$  V

- (5) PFM,  $V_{VIN} = 24$  V

- (6) FPM,  $V_{VIN} = 40$  V

- (7) FPWM,  $V_{VIN} = 24$  V

- (8) FPWM,  $V_{VIN} = 40$  V

Fig. 6. Efficiency versus load current

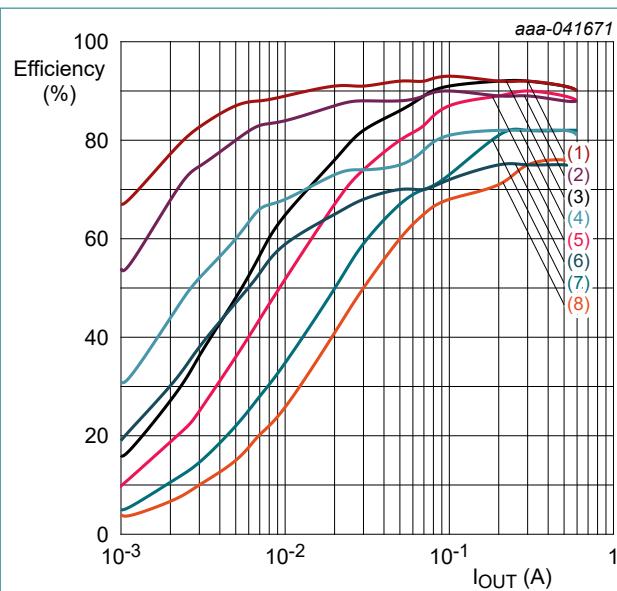

$V_{OUT} = 5$  V,  $f_{SW} = 2.1$  MHz

- (1) PFM,  $V_{VIN} = 8$  V

- (2) PFM,  $V_{VIN} = 12$  V

- (3) FPWM,  $V_{VIN} = 8$  V

- (4) PFM,  $V_{VIN} = 24$  V

- (5) FPWM,  $V_{VIN} = 12$  V

- (6) PFM,  $V_{VIN} = 36$  V

- (7) FPWM,  $V_{VIN} = 24$  V

- (8) FPWM,  $V_{VIN} = 36$  V

Fig. 7. Efficiency versus load current

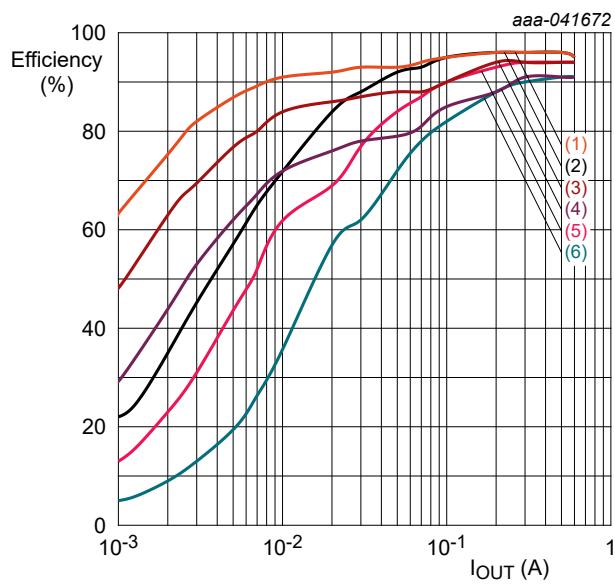

$V_{OUT} = 12$  V,  $f_{SW} = 1.05$  MHz

- (1) PFM,  $V_{VIN} = 15$  V

- (2) FPWM,  $V_{VIN} = 15$  V

- (3) PFM,  $V_{VIN} = 24$  V

- (4) PFM,  $V_{VIN} = 40$  V

- (5) FPWM,  $V_{VIN} = 24$  V

- (6) FPWM,  $V_{VIN} = 40$  V

Fig. 8. Efficiency versus load current

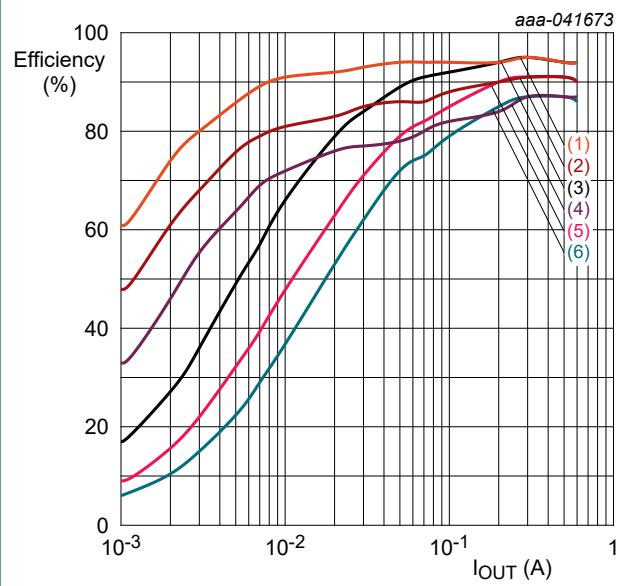

$V_{OUT} = 12$  V,  $f_{SW} = 2.1$  MHz

- (1) PFM,  $V_{VIN} = 15$  V

- (2) PFM,  $V_{VIN} = 24$  V

- (3) FPWM,  $V_{VIN} = 15$  V

- (4) PFM,  $V_{VIN} = 36$  V

- (5) FPWM,  $V_{VIN} = 24$  V

- (6) FPWM,  $V_{VIN} = 36$  V

Fig. 9. Efficiency versus load current

Fig. 14. Quiescent current versus ambient temperature

(1)  $V_{\text{IN\_UVLO+}}$  (rising  $V_{\text{VIN}}$ )

(2)  $V_{\text{IN\_UVLO-}}$  (falling  $V_{\text{VIN}}$ )Fig. 15.  $V_{\text{IN\_UVLO}}$  versus ambient temperature

Fig. 16. Reference voltage versus ambient temperature

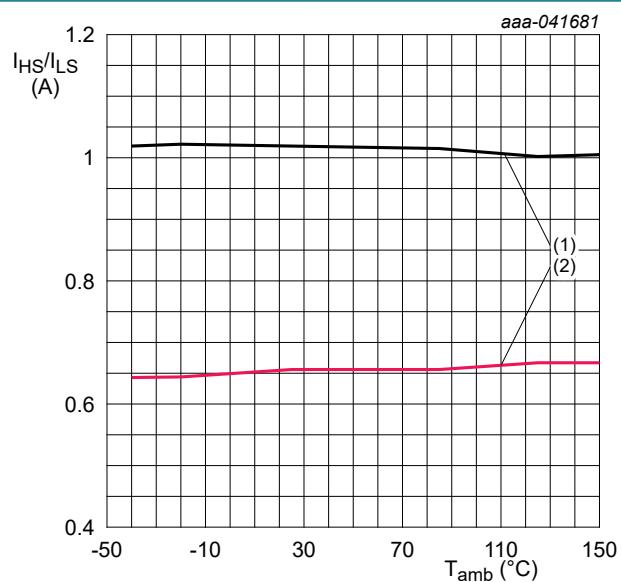

(1)  $I_{\text{HS\_LIMIT}}$

(2)  $I_{\text{LS\_LIMIT}}$

Fig. 17. HS and LS limits versus ambient temperature

## 13. Functional description

### 13.1. Overview

The NEX40400 is a fixed-frequency, synchronous step-down converter with low quiescent current consumption. It operates from 4.5 V to 40 V supply voltage, and capable of delivering up to 600 mA DC load current in a small solution size. There are six variants available that are suitable to various applications; refer to [Section 7](#) for detailed information.

The NEX40400 employs fixed-frequency peak-current mode control. The device enters PFM (Pulse Frequency Modulation) mode at light load to achieve high efficiency with PFM version. The FPWM (Forced Pulse Width Modulation) version is provided to achieve low output voltage ripple. The device is internally compensated, which reduces design time, and requires few external components. Frequency foldback helps prevent inductor current runaway during start-up and output short circuit fault condition. It also helps achieving high conversion ratio and low drop-out. Frequency spread spectrum function is implemented to improve EMI performance of converters.

Additional features such as precision enable and internal soft start provide a flexible and easy to use solution for a wide range of applications. Protection features include thermal shutdown,  $V_{VIN}$  under-voltage lockout, output over-voltage protection, cycle-by-cycle current limit, and hiccup mode for short-circuit protection.

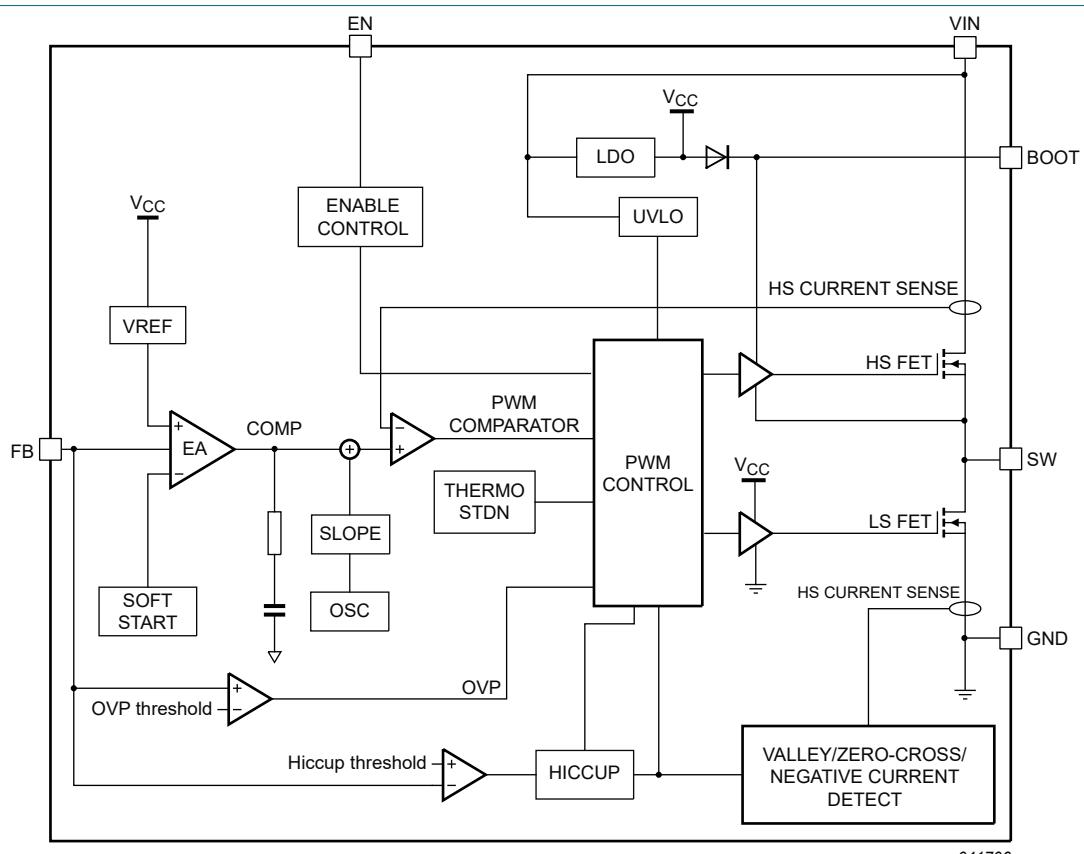

### 13.2. Functional Block Diagram

Fig. 18. Functional block diagram

### 13.3. Features

#### 13.3.1. Pulse-Width Modulation (PWM) Operation

At mid-to-high output currents, the NEX40400 operates in a fixed-frequency, peak-current control mode to regulate the output voltage. A pulse-width modulation (PWM) cycle initiated by the internal clock turns on the high-side MOSFET (HS-FET). The HS-FET remains on until its current reaches the value set by the COMP voltage – the output of the Error Amplifier (AE). After the HS-FET is off, the low-side MOSFET (LS-FET) turns on, and the inductor current flows through the LS-FET. To avoid a shoot-through, a dead time prevents the HS-FET and LS-FET from turning on at the same time. LS-FET turns off at the end of the switching cycle, and then a new PWM cycle begins with the next clock. Under light load conditions, depending on the variant, the NEX40400 operates in different mode.

#### 13.3.2. Pulse Frequency Modulation (PFM) Operation

For Pulse Frequency Modulation (PFM) version, when the load current is lower than half of the peak-to-peak inductor current in CCM, the NEX40400 operates in Discontinuous Conduction Mode (DCM). In DCM operation, the LS switch is turned off when the inductor current drops to  $I_{LS\_ZC}$  threshold (30 mA typical) to reduce conduction loss and improve efficiency.

At lower load, PFM mode is activated to maintain high efficiency operation the minimum peak inductor current  $I_{PEAK\_MIN}$  (150 mA typical) is reached, the switching frequency decreases to maintain regulation. In PFM mode, switching frequency is decreased by the control loop to maintain output voltage regulation when load current reduces. Switching loss is further reduced in PFM operation due to less frequent switching.

#### 13.3.3. Forced PWM Operation

For FPWM variant, the NEX40400 operates in Continuous Conduction Mode (CCM) in the whole load range. This operation is maintained even at no-load condition, by allowing the negative inductor current as low as minus 0.5 A to slightly discharge the output and keep it in regulation. In FPWM mode, the light load efficiency will be lower than in PFM mode.

#### 13.3.4. Adjustable output voltage

The output voltage is set by a resistor divider from the output voltage to the FB pin. 1% tolerance resistors are recommended. Select the bottom-side resistor  $R_{FBB}$  for the desired divider current and use below equation to calculate top-side resistor  $R_{FBT}$ .  $R_{FBB}$  in the range from 10 kΩ to 100 kΩ is recommended for most applications.

$$R_{FBT} = \frac{V_{OUT} - V_{REF}}{V_{REF}} \times R_{FBB}$$

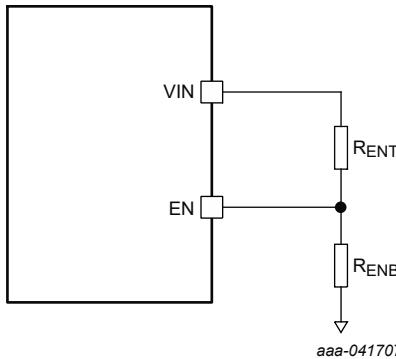

#### 13.3.5. $V_{IN\_UVLO}$ and enable control (EN)

The NEX40400 implements internal undervoltage-lockout (UVLO) circuitry on the VIN pin. The converter shuts down when the VIN pin voltage falls below the internal threshold  $V_{IN\_UVLO}$ . The internal VIN UVLO threshold has a hysteresis of 400 mV.

The NEX40400 has a dedicated enable control pin (EN) to control ON or OFF operation of device. A voltage less than 1 V disables the converter, while a voltage higher than 1.30 V enables the regulator. The EN pin may not be left open or floating; if not used, to be connected to VIN.

If an application requires a higher UVLO threshold on the VIN pin, then the EN pin can be configured as shown on [Fig. 19](#) to program the required  $V_{IN\_UVLO}$  threshold.

Fig. 19. External UVLO by enable divider

### 13.3.6. Frequency foldback

The NEX40400 has a minimum on-time and off-time limitation for HS-FET, which is  $t_{ON\_MIN}$  and  $t_{OFF\_MIN}$  respectively. Given a fixed switching frequency and target output voltage,  $t_{ON\_MIN}$  and  $t_{OFF\_MIN}$  determine the allowed maximum and minimum input voltage to keep the output voltage in regulation. This relationship is described in equations below.

$$V_{IN\_MAX} = \frac{V_{OUT}}{f_{SW} \times t_{ON\_MIN}}$$

$$V_{IN\_MIN} = \frac{V_{OUT}}{1 - f_{SW} \times t_{OFF\_MIN}}$$

To extend the input voltage range for the regulated output voltage, a frequency foldback scheme is implemented in NEX40400.

The on-time decreases while VIN voltage increases. Once the on-time decreases to  $t_{ON\_MIN}$ , the switching frequency starts to decrease while VIN continues to go up, thus the actual duty cycle is lower, and higher input voltage is allowed for a regulated output voltage. This feature is important to prevent inductor current and output voltage runaway during start-up or output short circuit fault condition.

On the other hand, as VIN voltage decreases, duty cycle increases, and the off-time decreases. Once the off-time decreases to  $t_{OFF\_MIN}$  and VIN continue to decrease, the inductor flux balance can't be maintained in a normal cycle. The current in the HS-FET can't reach the COMP-set current value within one nominal PWM cycle, the HS-FET remains on until its current hit the COMP-set current value, then HS-FET will turn off for  $t_{OFF\_MIN}$  (100 ns typical) before next turn-on. In this condition, the switching frequency is lower than nominal frequency, and the maximum duty cycle is extended, the output voltage can be kept in regulation with a lower input voltage. To effectively refresh the bootstrap capacitor, the maximum on-time of HS-FET is limited at 10  $\mu$ s, corresponding to a minimum 100 kHz switching frequency.

### 13.3.7. Over current and Hiccup protections

The NEX40400 has cycle-by-cycle current limit on both the peak and valley of the inductor current. High-side MOSFET over-current protection is implemented by the Peak Current Mode control. The HS switch current is sensed when the HS-FET is turned on after a set blanking time. The HS-FET will be turned off once its current intersects the current command from COMP minus slope compensation every switching cycle. In an over current or short circuit fault condition, COMP voltage is pushed to and clamped at  $V_{COMP\_MAX}$ , correspondingly the peak current of HS-FET is limited by the maximum peak current threshold  $I_{HS\_LIMIT}$ .

Sometimes the inductor current may run away due to the  $t_{ON\_MIN}$  limitation of HS-FET. For example, during start-up period, or during output short-to-ground fault condition, the output voltage is too low, may not have enough time to reset the inductor flux properly, inductor current may be higher and higher by cycles, which is called current run away. To address this problem, the current going through LS-FET is also sensed and monitored in the NEX40400. When the LS-FET turns on, the inductor current begins to ramp down. The LS switch will not be turned off at the end of a switching cycle if its current is above the LS current limit set by COMP voltage. The LS switch is kept on so that inductor current keeps ramping down, until the inductor current ramps below the LS current limit. Then the LS switch will be turned off and the HS switch will be turned on to start a new cycle. In this way, the valley of inductor current is controlled by COMP voltage. In short circuit fault condition, as COMP voltage is clamped at  $V_{COMP\_MAX}$ , the corresponding LS current limit is clamped at its maximum value  $I_{LS\_LIMIT}$ .

If the feedback voltage is lower than 40% of the VREF and the current of the LS switch triggers  $I_{LS\_LIMIT}$  for 256 consecutive cycles, hiccup current protection mode is activated. In hiccup mode, the regulator shuts down and keeps off for a period of hiccup,  $t_{HICCU}$  (120 ms typical for PFM variants; 15 ms for FPWM), before the NEX40400 tries to start again. If overcurrent or short-circuit fault condition still exist, hiccup repeats until the fault condition is removed. Hiccup mode reduces power dissipation under severe over-current conditions, prevents over-heating and potential damage to the device.

For FPWM variants, the inductor current is allowed to go negative. If the negative inductor reaches minus 0.5 A the LS switch is turned off immediately. This protects the LS switch from excessive negative current.

### 13.3.8. Internal soft start

A reference-type soft start prevents the converter output voltage from overshooting during start-up. When the chip starts up, the internal circuitry generates a soft-start voltage ( $V_{SS}$ ) that ramps up from 0 V during the soft start time. When  $V_{SS}$  is lower than  $V_{REF}$ ,  $V_{SS}$  overrides  $V_{REF}$  as the error amplifier reference. The typical soft start time ( $t_{SS}$ ) is 1.8 ms.

There is over-current protection blanking time  $t_{OCP\_BLK}$  (20 ms typical) at the beginning of power-up to prevent start-up failure for some application with high output voltage and large output capacitance. In those application, due to current limit, the time to charge up output cap will be much longer than 1.8 ms.

### 13.3.9. Safe start-up into pre-biased output

The NEX40400 has been designed to prevent the LS FET from discharging a pre-biased output. During monotonic pre-biased start-up, both high-side and low-side MOSFETs are not allowed to be turned on until the internal soft-start voltage is higher than FB pin voltage, except of the need to re-fresh the boot capacitor.

### 13.3.10. Spread spectrum

The NEX40400 implements frequency spread spectrum to improve EMI performance in FPWM version. The jittering span is  $\pm 5\%$  of the switching frequency with pseudo-random swing frequency.

### 13.3.11. Bootstrap voltage

The NEX40400 provides an integrated bootstrap voltage regulator. A small capacitor between the BOOT and SW pins provides the gate drive voltage for the high-side MOSFET. The bootstrap capacitor is refreshed when the high-side MOSFET is off and the low-side switch conducts. The recommended value of the bootstrap capacitor is 0.1  $\mu$ F. A ceramic capacitor with an X7R or X5R grade dielectric and a voltage rating of 16 V or higher is recommended for stable performance over temperature and voltage.

### 13.3.12. Output Overvoltage Protection (OVP)

The NEX40400 incorporates an overvoltage transient protection (OVP) circuit to minimize output voltage overshoot when recovering from output fault conditions or strong unload transients. The OVP circuit includes an overvoltage comparator to compare the FB pin voltage and internal thresholds. When the FB pin voltage goes above  $109\% \times V_{REF}$ , the high-side MOSFET will be forced off. When the FB pin voltage falls below  $104\% \times V_{REF}$ , the high-side MOSFET will be enabled again.

### 13.3.13. Thermal shutdown

The junction temperature ( $T_j$ ) of the device is monitored by an internal temperature sensor. Once the  $T_j$  exceeds the thermal shutdown threshold  $T_{SHDN}$  of 170 °C, the device enters thermal shutdown. Both the high side and low side power FETs are turned off. When  $T_j$  falls below 155 °C, the device re-initiates the power up sequence controlled by the internal soft-start circuitry.

## 14. Application information

The following session discusses the external components to complete the power supply design for several input and output voltage options by using the typical applications as a reference.

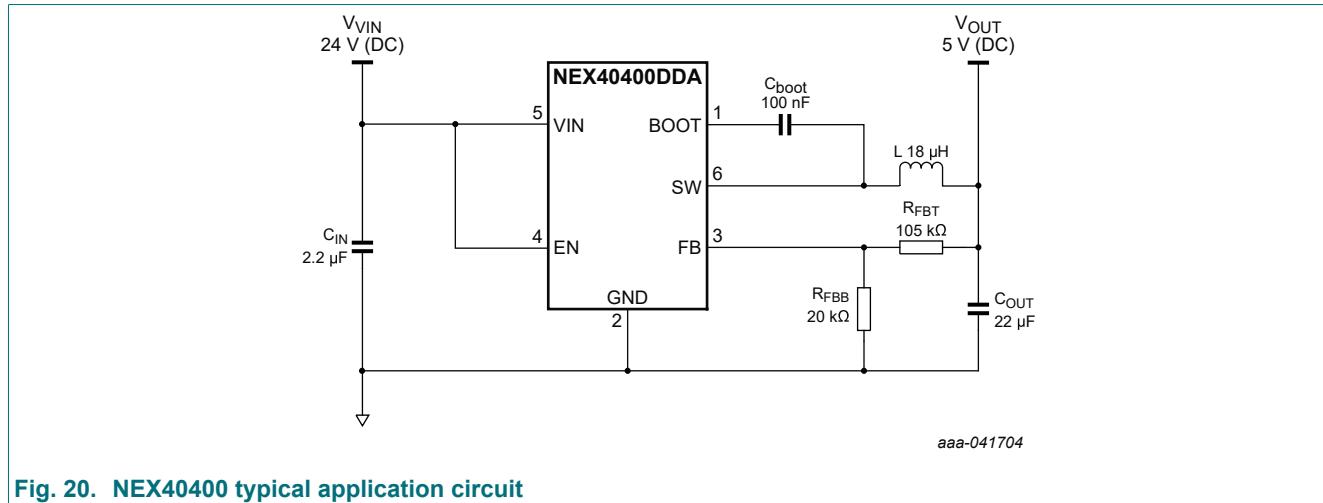

### 14.1. Typical application

Fig. 20. NEX40400 typical application circuit

### 14.2. Design requirements

Table 10. Typical recommended values of inductor, output capacitor, and the feedback resistive divider

| $f_{SW}$ (MHz) | $V_{OUT}$ (V) | $L$ (μH) | $C_{out}(\mu F)$ / (V) | $R_{FBB}$ (kΩ) | $R_{FBT}$ (kΩ) |

|----------------|---------------|----------|------------------------|----------------|----------------|

| 1.05           | 3.3           | 12       | 22 μF / 10 V           | 20             | 61.9           |

|                | 5.0           | 18       | 22 μF / 10 V           | 20             | 105            |

|                | 12            | 33       | 10 μF / 25 V           | 20             | 280            |

| 2.1            | 3.3           | 6.2      | 10 μF / 10 V           | 20             | 61.9           |

|                | 5.0           | 10       | 10 μF / 10 V           | 20             | 105            |

|                | 12            | 18       | 10 μF / 25 V           | 20             | 280            |

### 14.3. Inductor selection

The inductor value affects the peak-to-peak ripple current, the PWM to PFM transition point, the output voltage ripple and the efficiency. To optimize the efficiency and solution size, allow the peak-to-peak ripple current in the inductor to be around 30% of the maximum load current is suggested. The inductance value can be calculated with below equation:

$$L = \frac{V_{OUT}}{f_{SW} \times \Delta I_L} \times \left( 1 - \frac{V_{OUT}}{V_{VIN}} \right)$$

Where  $V_{OUT}$  is the output voltage,  $V_{VIN}$  is the input voltage,  $f_{SW}$  is the switching frequency, and  $\Delta I_L$  is the peak-to-peak inductor ripple current.

Once the inductance is chosen, the peak-to-peak inductor ripple current can be calculated. The maximum peak inductor current can be calculated with below equation:

$$I_{LP} = I_{LOAD} + \frac{\Delta I_L}{2}$$

Where  $I_{LOAD}$  is the maximum load current.

Choose an inductor that will not saturate under the maximum inductor peak current calculated above.

A more conservative way is to select the inductor saturation current according to the high side MOSFET switch current limit, because during a heavy load transient the inductor current may rise above the calculated maximum peak inductor current value.

#### 14.4. Input capacitor selection

The input capacitor can be electrolytic, tantalum, or ceramic. When using electrolytic or tantalum capacitors, add a small, high-quality, ceramic capacitor (e.g.: 0.1  $\mu$ F) as close to the IC as possible. When using ceramic capacitors, ensure that they have enough capacitance to provide a sufficient charge to prevent excessive voltage ripple at the input.

The input voltage ripple caused by the capacitance can be estimated with equation:

$$\Delta V_{VIN} = \frac{I_{LOAD} \times V_{OUT}}{f_{SW} \times C_{IN} \times V_{VIN}} \times \left( 1 - \frac{V_{OUT}}{V_{VIN}} \right)$$

Where  $I_{LOAD}$  is the maximum load current, and  $C_{IN}$  is the input capacitance.

#### 14.5. Output capacitor selection

Output capacitor is required to maintain the DC output voltage. Ceramic, tantalum, or low ESR electrolytic capacitors are recommended. Low ESR capacitors are recommended to keep the output voltage ripple low. The output voltage ripple can be estimated with Equation:

$$\Delta V_{OUT} = \frac{V_{OUT}}{f_{SW} \times L} \times \left( 1 - \frac{V_{OUT}}{V_{VIN}} \right) \times \left( R_{ESR} + \frac{1}{8 \times f_{SW} \times C_{OUT}} \right)$$

Where  $L$  is the inductor value,  $R_{ESR}$  is the equivalent series resistance (ESR) value of the output capacitor, and  $C_{OUT}$  is output capacitance.

In the case of ceramic capacitors, the impedance at the switching frequency is dominated by the capacitance. The output voltage ripple is caused mainly by the capacitance. For simplification, the output voltage ripple can be estimated with Equation:

$$\Delta V_{OUT} = \frac{V_{OUT}}{8 \times f_{SW}^2 \times L \times C_{OUT}} \times \left( 1 - \frac{V_{OUT}}{V_{VIN}} \right)$$

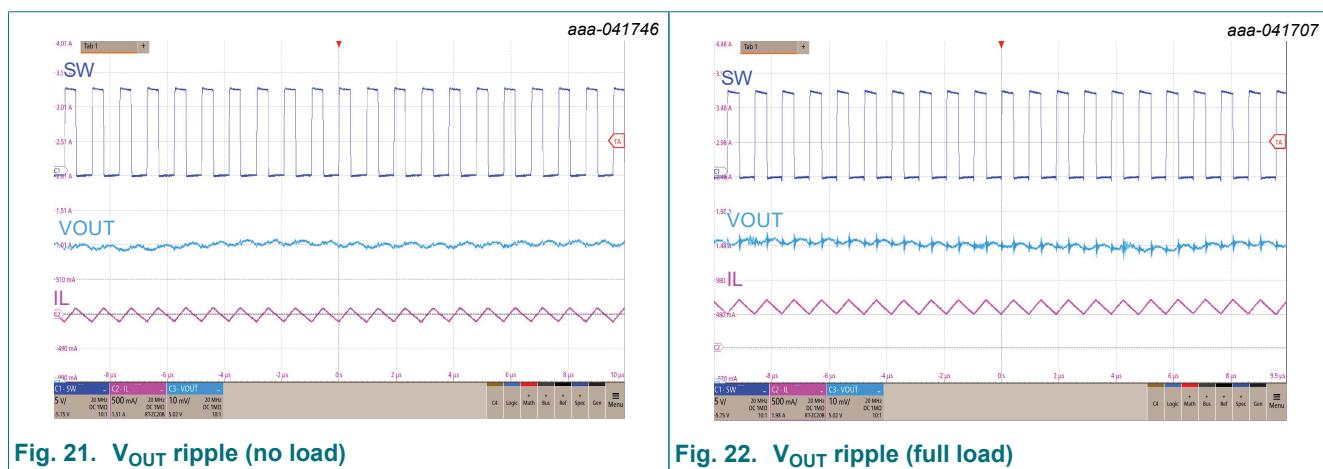

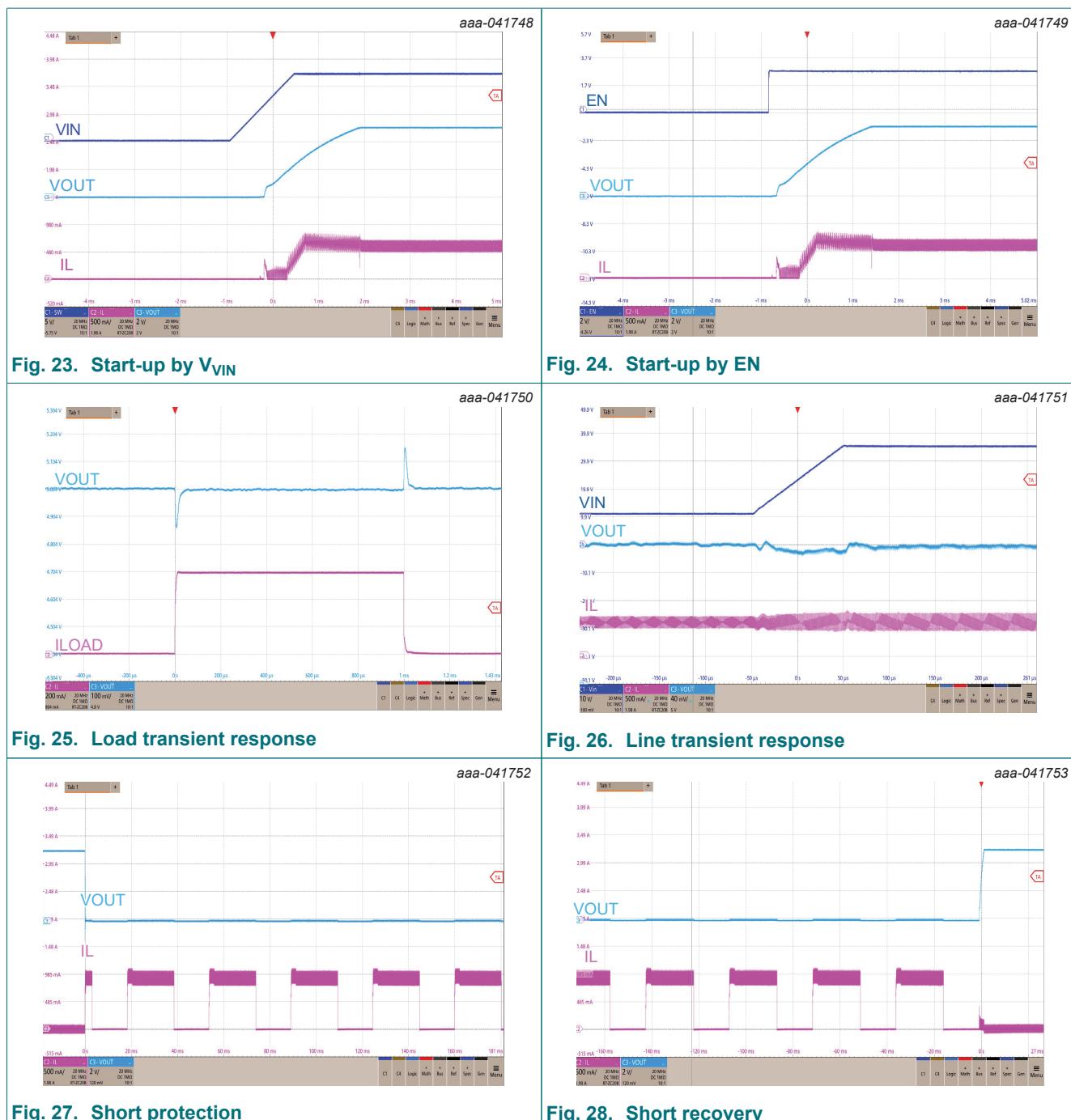

#### 14.6. Typical operation

Fig. 21. V<sub>OUT</sub> ripple (no load)

Fig. 22. V<sub>OUT</sub> ripple (full load)

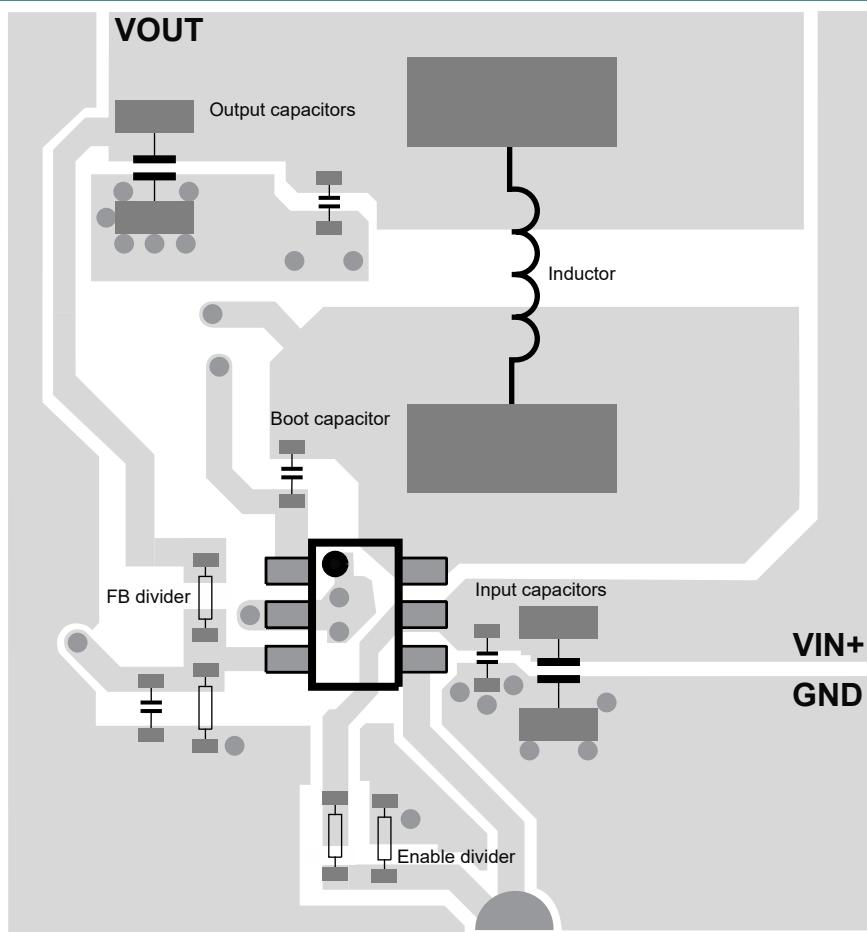

## 14.7. PCB layout

Fig. 29. Example of NEX40400 PCB Layout

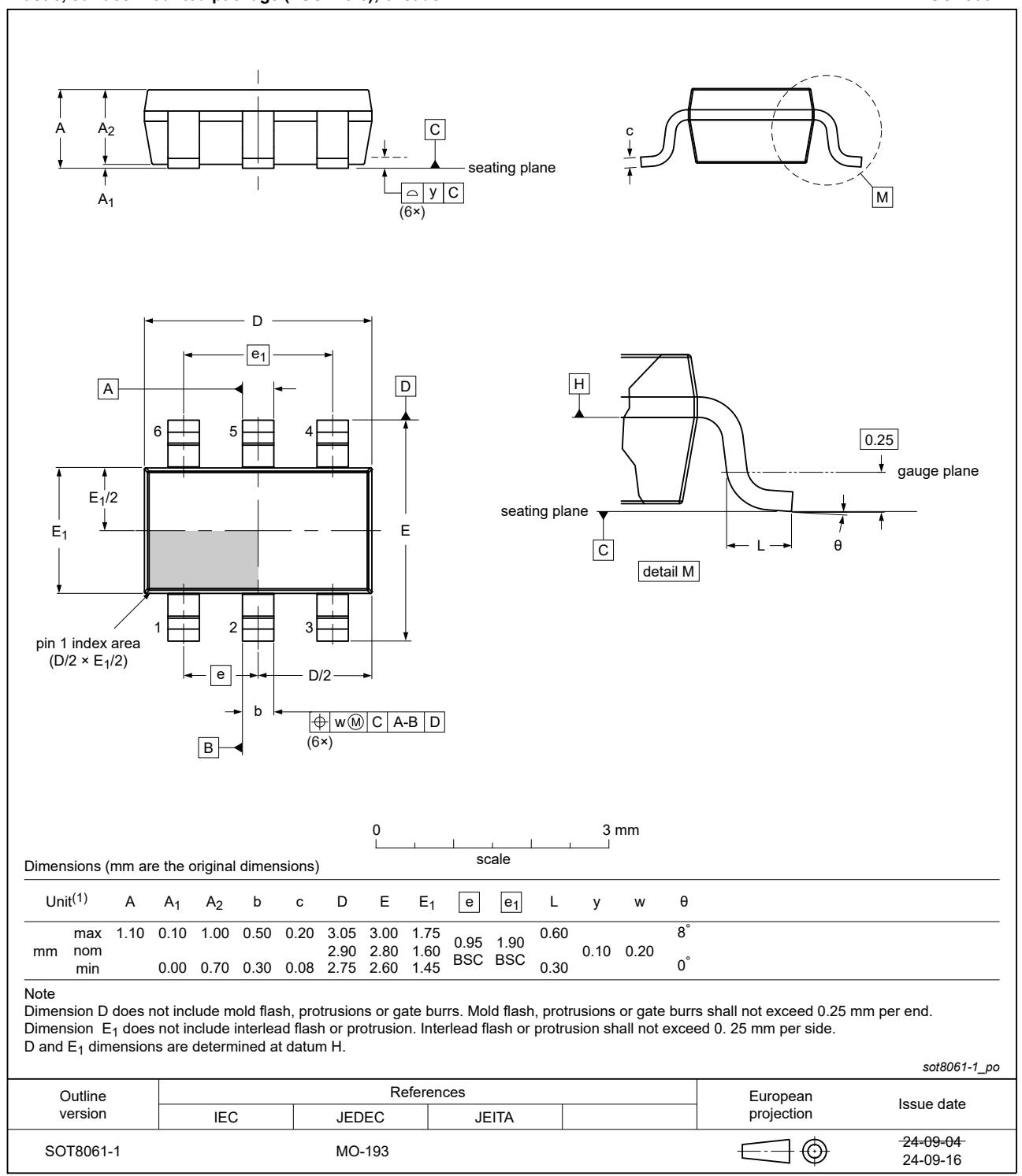

## 15. Package information

Plastic, surface-mounted package (TSOT23-6); 6 leads

SOT8061-1

Fig. 30. Package outline SOT8061-1 (TSOT23-6)

## 16. Revision history

Table 11. Revision history

| Document ID  | Release date | Data sheet status  | Change notice | Supersedes |

|--------------|--------------|--------------------|---------------|------------|

| NEX40400 v.1 | 20241206     | Product data sheet | -             | -          |

## 17. Legal information

### Data sheet status

| Document status [1][2]         | Product status [3] | Definition                                                                            |

|--------------------------------|--------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development        | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification      | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production         | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the internet at <https://www.nexperia.com>.

### Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

**Short data sheet** — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local Nexperia sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between Nexperia and its customer, unless Nexperia and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the Nexperia product is deemed to offer functions and qualities beyond those described in the Product data sheet.

### Disclaimers

**Limited warranty and liability** — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.

In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.

**Right to make changes** — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal

injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Nexperia product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). Nexperia does not accept any liability in this respect.

**Limiting values** — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

**Terms and conditions of commercial sale** — Nexperia products are sold subject to the general terms and conditions of commercial sale, as published at <http://www.nexperia.com/profile/terms>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Nexperia hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of Nexperia products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Non-automotive qualified products** — Unless this data sheet expressly states that this specific Nexperia product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. Nexperia accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without Nexperia's warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond Nexperia's specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies Nexperia for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond Nexperia's standard warranty and Nexperia's product specifications.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

### Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

## Contents

|                                                         |           |

|---------------------------------------------------------|-----------|

| <b>1. General description.....</b>                      | <b>1</b>  |

| <b>2. Features and benefits.....</b>                    | <b>1</b>  |

| <b>3. Target applications.....</b>                      | <b>1</b>  |

| <b>4. Ordering information.....</b>                     | <b>2</b>  |

| <b>5. Marking.....</b>                                  | <b>2</b>  |

| <b>6. Pinout.....</b>                                   | <b>3</b>  |

| 6.1. Pinout.....                                        | 3         |

| 6.2. Pin description.....                               | 3         |

| <b>7. Device Comparison.....</b>                        | <b>3</b>  |

| <b>8. Limiting values.....</b>                          | <b>4</b>  |

| <b>9. Recommended operating conditions.....</b>         | <b>4</b>  |

| <b>10. ESD ratings.....</b>                             | <b>4</b>  |

| <b>11. Thermal characteristics.....</b>                 | <b>4</b>  |

| <b>12. Characteristics.....</b>                         | <b>5</b>  |

| 12.1. Electrical characteristics.....                   | 5         |

| 12.2. Typical characteristics.....                      | 6         |

| <b>13. Functional description.....</b>                  | <b>10</b> |

| 13.1. Overview.....                                     | 10        |

| 13.2. Functional Block Diagram.....                     | 10        |

| 13.3. Features.....                                     | 11        |

| 13.3.1. Pulse-Width Modulation (PWM) Operation.....     | 11        |

| 13.3.2. Pulse Frequency Modulation (PFM) Operation..... | 11        |

| 13.3.3. Forced PWM Operation.....                       | 11        |

| 13.3.4. Adjustable output voltage.....                  | 11        |

| 13.3.5. $V_{IN\_UVLO}$ and enable control (EN).....     | 11        |

| 13.3.6. Frequency foldback.....                         | 12        |

| 13.3.7. Over current and Hiccup protections.....        | 12        |

| 13.3.8. Internal soft start.....                        | 13        |

| 13.3.9. Safe start-up into pre-biased output.....       | 13        |

| 13.3.10. Spread spectrum.....                           | 13        |

| 13.3.11. Bootstrap voltage.....                         | 13        |

| 13.3.12. Output Overvoltage Protection (OVP).....       | 13        |

| 13.3.13. Thermal shutdown.....                          | 13        |

| <b>14. Application information.....</b>                 | <b>14</b> |

| 14.1. Typical application.....                          | 14        |

| 14.2. Design requirements.....                          | 14        |

| 14.3. Inductor selection.....                           | 14        |

| 14.4. Input capacitor selection.....                    | 15        |

| 14.5. Output capacitor selection.....                   | 15        |

| 14.6. Typical operation.....                            | 15        |

| 14.7. PCB layout.....                                   | 17        |

| <b>15. Package information.....</b>                     | <b>18</b> |

| <b>16. Revision history.....</b>                        | <b>19</b> |

| <b>17. Legal information.....</b>                       | <b>20</b> |

© Nexperia B.V. 2024. All rights reserved

For more information, please visit: <http://www.nexperia.com>

For sales office addresses, please send an email to: [salesaddresses@nexperia.com](mailto:salesaddresses@nexperia.com)

Date of release: 6 December 2024