Simultaneously Sampling 4- and 7-Channel  $\Sigma\Delta$  ADC with SPI

## FEATURES

- ▶ 4- or 7-channel high performance, simultaneous sampling  $\Sigma\Delta$  ADCs

- ▶ SNR up to 105dB

- ▶ Programmable sample rate of up to 64kSPS

- ▶ Wide input-voltage range:  $\pm 1.2V_{PK}$ , 848mV<sub>RMS</sub> full-scale

- ▶ High impedance, differential inputs

- ▶ Internal voltage reference temperature coefficient: 5ppm/°C typical

- ▶ Integrated digital integrator and high-pass filter for use with Rogowski coils

- ▶ Fast start-up with first samples in 0.5ms after valid supply

- ▶ Tamper detect mode, low power for battery back-up

- ▶ 4-wire SPI with bidirectional CRC and daisy-chain functionality

- ▶ Simple synchronization of multiple ADC devices

- ▶ Gain, phase, and offset compensation for each channel

- ▶ Unique SPI readable part ID registers

- ▶ Only 18mW power consumption with 7-channel ADC

- ▶ Wide temperature range: -40°C to +125°C

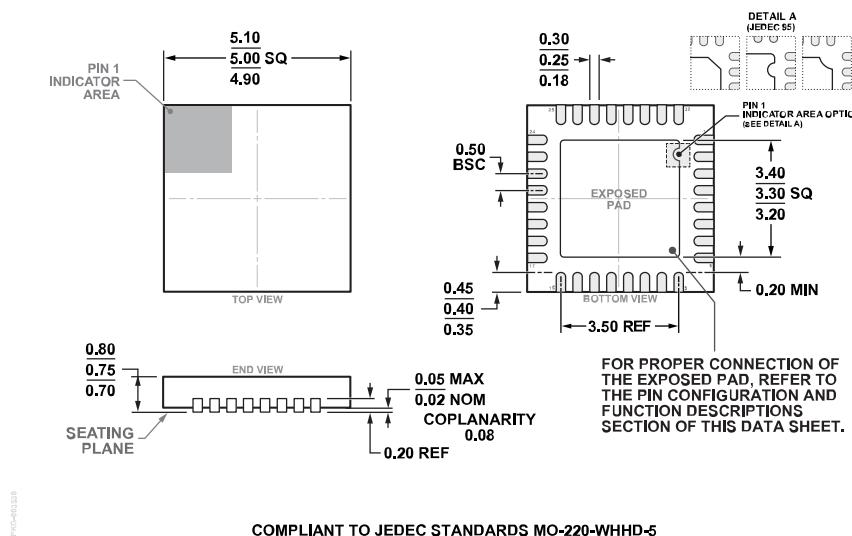

- ▶ Compact 32-lead, 5mm x 5mm LFCSP

## APPLICATIONS

- ▶ Polyphase energy meters

- ▶ Split-phase energy meters

- ▶ Branch circuit monitoring

- ▶ Power distribution units

- ▶ Power quality monitoring

- ▶ Circuit breakers

- ▶ Protection relays

- ▶ Electric vehicle supply equipment

## GENERAL DESCRIPTION

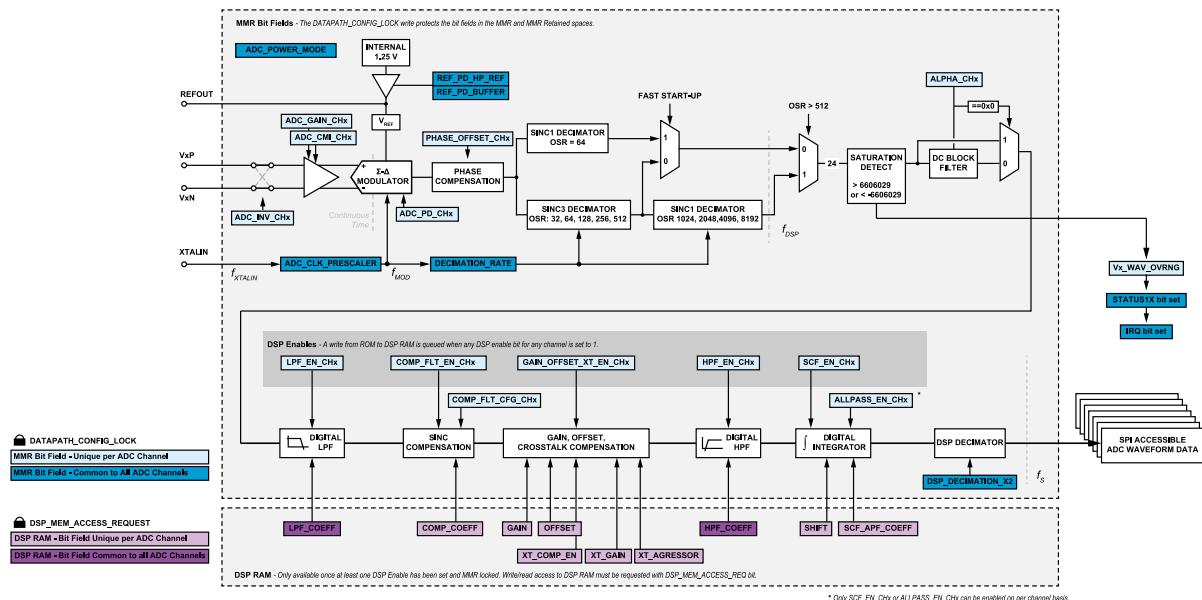

The ADEMA124/ADEMA127 are 4- and 7-channel simultaneously sampling 24-bit sigma delta analog-to-digital converters (ADC), ideal for use in polyphase or split-phase energy metering applications. The ADEMA124/ADEMA127 are compatible with voltage dividers, shunts, and isolated current sensors such as current transformers and Rogowski coils.

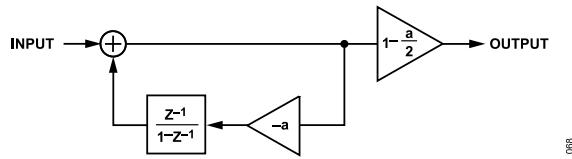

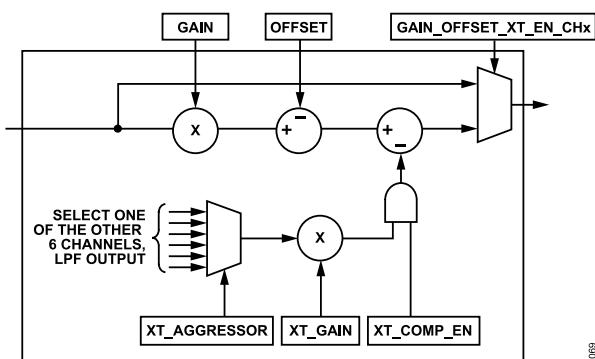

The ADEMA124/ADEMA127 include independent hardware and DSP filters enabling gain, phase and offset compensation on each ADC channel. The ADEMA124/ADEMA127 also have bespoke compensation and DSP features, which include an integrator and second-order high-pass filter to allow streamlined Rogowski sensor implementations. DSP filter coefficients for typical use cases are automatically loaded and are accessible for customization of filter characteristics.

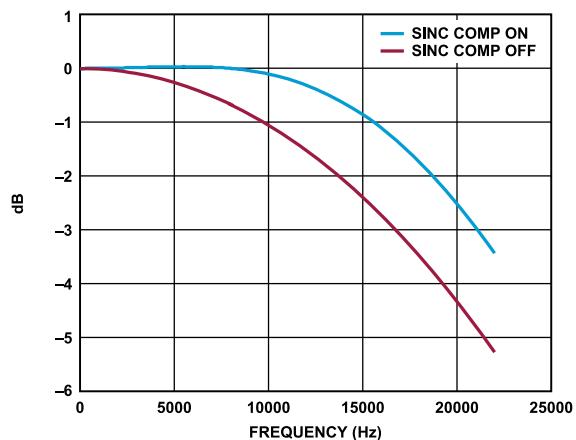

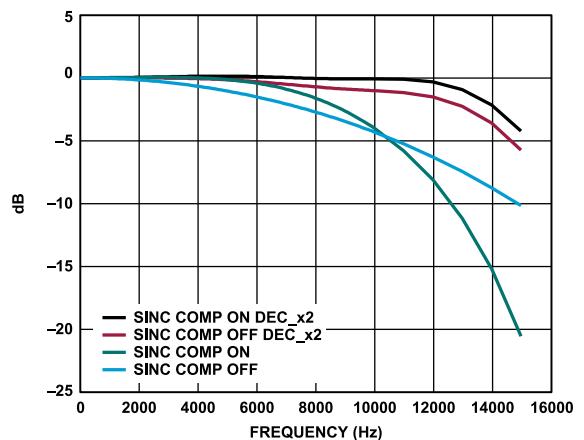

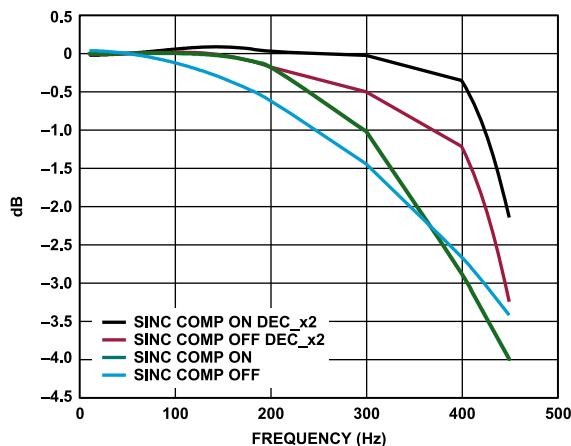

The sinc compensation, LPF, and DSP decimate-by-2 feature extend the usable analog bandwidth by up to 70% for a given output sample rate. The high bandwidth makes ADEMA124/ADEMA127 suitable for IEC 61000-4-30 Power Quality Class A and Class S meters. The ADEMA124/ADEMA127 can be used in systems compliant to active energy standards IEC 62053-21, IEC 62053-22, OIML R46, and ANSI C12.1, and reactive energy standards IEC 62053-23, IEC 62053-24, and EN 50470-3. The ADEMA124/ADEMA127 can be used in circuit breakers and protection relays, particularly with a Rogowski sensor due to a 0.5ms fast start-up time.

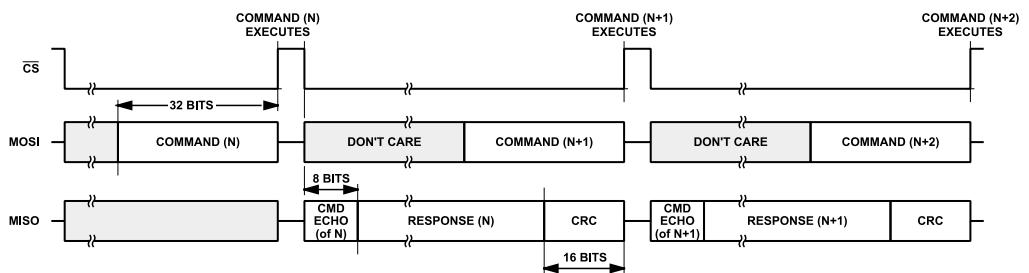

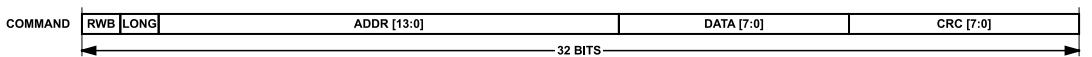

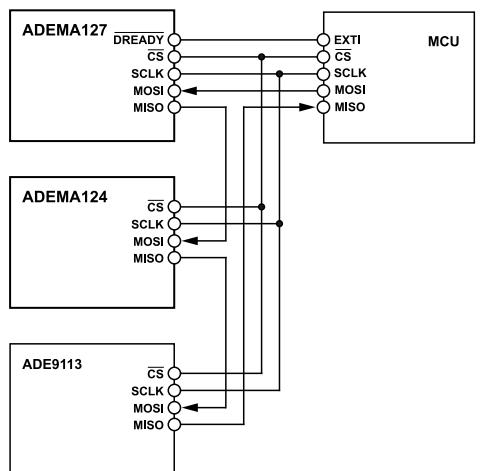

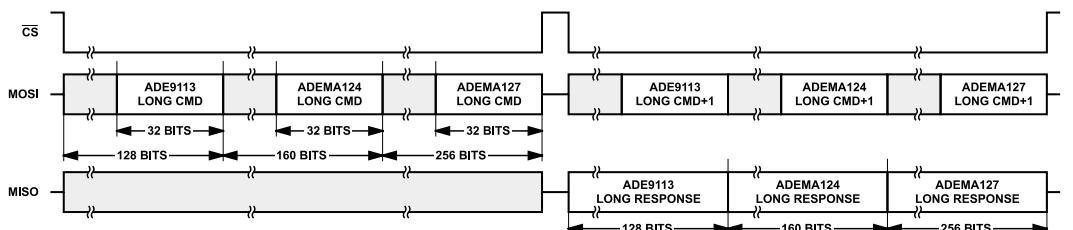

The ADEMA124/ADEMA127 have a flexible SPI interface for configuration and data retrieval. The daisy-chain SPI interface allows multiple compatible ADCs to be serviced simultaneously by a single SPI port, which saves many pins on the host microcontroller. Additionally, the SPI port is daisy-chain compatible with the 2- and 3-channel isolated ADC, [ADE9112/ADE9113](#). To maintain integrity of ADC waveform data, independent cyclic redundancy checks (CRC) are available to detect errors in inbound and outbound SPI packets, and incidental changes of configuration registers.

**Table 1. Product Comparison**

| Model    | 24-Bit ADC Channels |

|----------|---------------------|

| ADEMA124 | 4                   |

| ADEMA127 | 7                   |

## TABLE OF CONTENTS

|                                                   |    |                                          |    |

|---------------------------------------------------|----|------------------------------------------|----|

| Features.....                                     | 1  | SPI Compatible Communication.....        | 25 |

| Applications.....                                 | 1  | Datapath Configuration.....              | 33 |

| General Description.....                          | 1  | Configuration Procedure.....             | 39 |

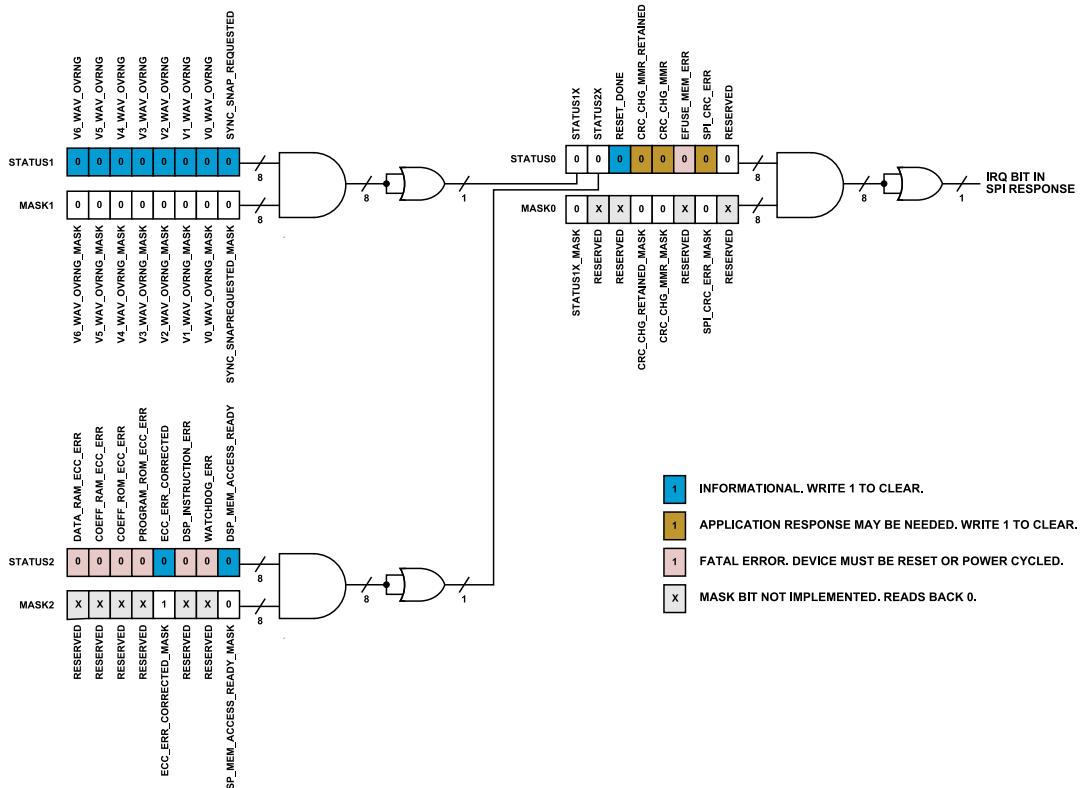

| Functional Block Diagrams.....                    | 3  | Status Registers and IRQ.....            | 40 |

| Specifications.....                               | 4  | CRC Protection.....                      | 41 |

| Bandwidth and Pass-Band Flatness.....             | 7  | Sensor to ADC Interface.....             | 43 |

| Timing Characteristics.....                       | 8  | Crystal Oscillator/External Clock.....   | 44 |

| Absolute Maximum Ratings.....                     | 9  | Synchronization of Multiple Devices..... | 45 |

| Thermal Resistance.....                           | 9  | Power Consumption.....                   | 46 |

| ESD Caution.....                                  | 9  | Polyphase Energy Meters.....             | 47 |

| Pin Configurations and Function Descriptions..... | 10 | Split Phase Energy Meters.....           | 49 |

| Typical Performance Characteristics.....          | 12 | Hardware Identifiers.....                | 50 |

| Test Circuit.....                                 | 18 | SPI Accessible Addresses.....            | 51 |

| Terminology.....                                  | 19 | Register Summary.....                    | 52 |

| Theory of Operation.....                          | 20 | Register Details.....                    | 55 |

| Gain and Offset Correction.....                   | 20 | DSP RAM Summary.....                     | 70 |

| Quick Start Guide.....                            | 20 | DSP RAM Details.....                     | 73 |

| Applications Information.....                     | 21 | Outline Dimensions.....                  | 78 |

| Start-Up Sequence and Timing.....                 | 21 | Ordering Guide.....                      | 78 |

| Modes of Operation.....                           | 22 | Evaluation Boards.....                   | 78 |

## REVISION HISTORY

## 11/2025—Rev. 0 to Rev. A

|                                                                                                                                                         |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Changes to General Description Section.....                                                                                                             | 1  |

| Changes to ADC Gain Drift over Temperature Parameter; ADC Transfer Function Parameter; and Signal-to-Noise Ratio (SNR), 2x Gain Parameter, Table 2..... | 4  |

| Changes to Table 3.....                                                                                                                                 | 7  |

| Changes to Figure 14 Caption and Figure 15 Caption.....                                                                                                 | 13 |

| Changes to Figure 27 Caption.....                                                                                                                       | 15 |

| Added Figure 28 and Figure 29; Renumbered Sequentially.....                                                                                             | 15 |

| Changes to Figure 31 Caption and Figure 36 Caption.....                                                                                                 | 16 |

| Change to Figure 37 Caption.....                                                                                                                        | 17 |

| Change to Figure 38.....                                                                                                                                | 18 |

| Changes to Software Reset Section.....                                                                                                                  | 24 |

| Changes to Hardware Reset Section.....                                                                                                                  | 24 |

| Changes to ADC Transfer Function Section.....                                                                                                           | 35 |

| Changes to Digital Low-Pass Filter (LPF) Section.....                                                                                                   | 38 |

| Changes to Sinc Compensation Filter Section.....                                                                                                        | 38 |

| Changes to Digital High-Pass Filter (HPF) Section.....                                                                                                  | 38 |

| Changes to Digital Integrator and All Pass Filter Section.....                                                                                          | 39 |

| Changes to Anti-Aliasing Filters Section and Figure 63.....                                                                                             | 43 |

| Changes to Figure 66.....                                                                                                                               | 44 |

| Change to Table 28.....                                                                                                                                 | 52 |

| Changes to Table 30.....                                                                                                                                | 58 |

## 7/2025—Revision 0: Initial Version

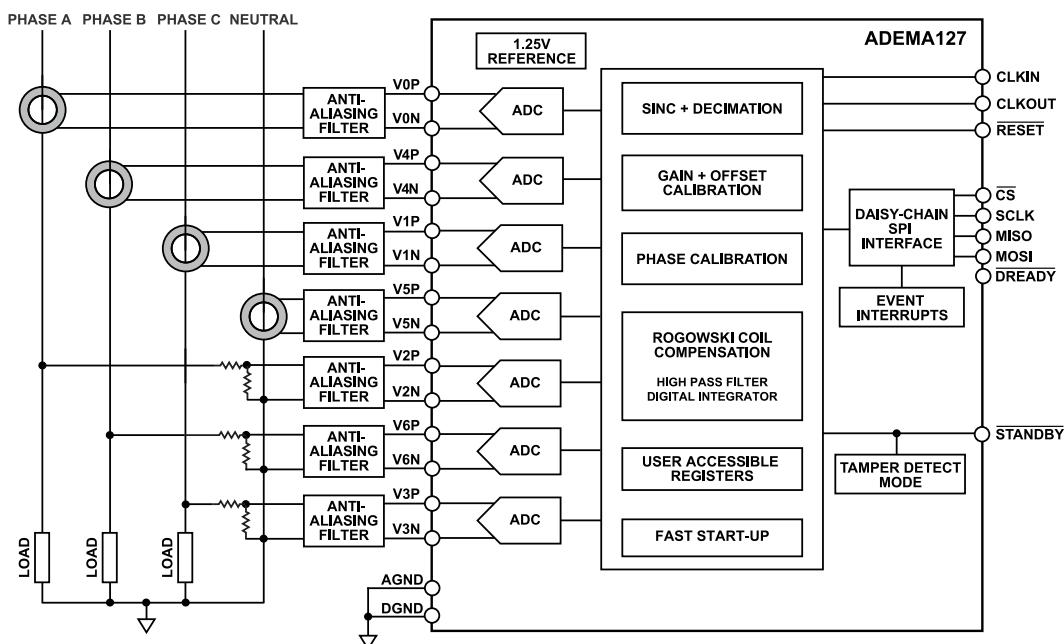

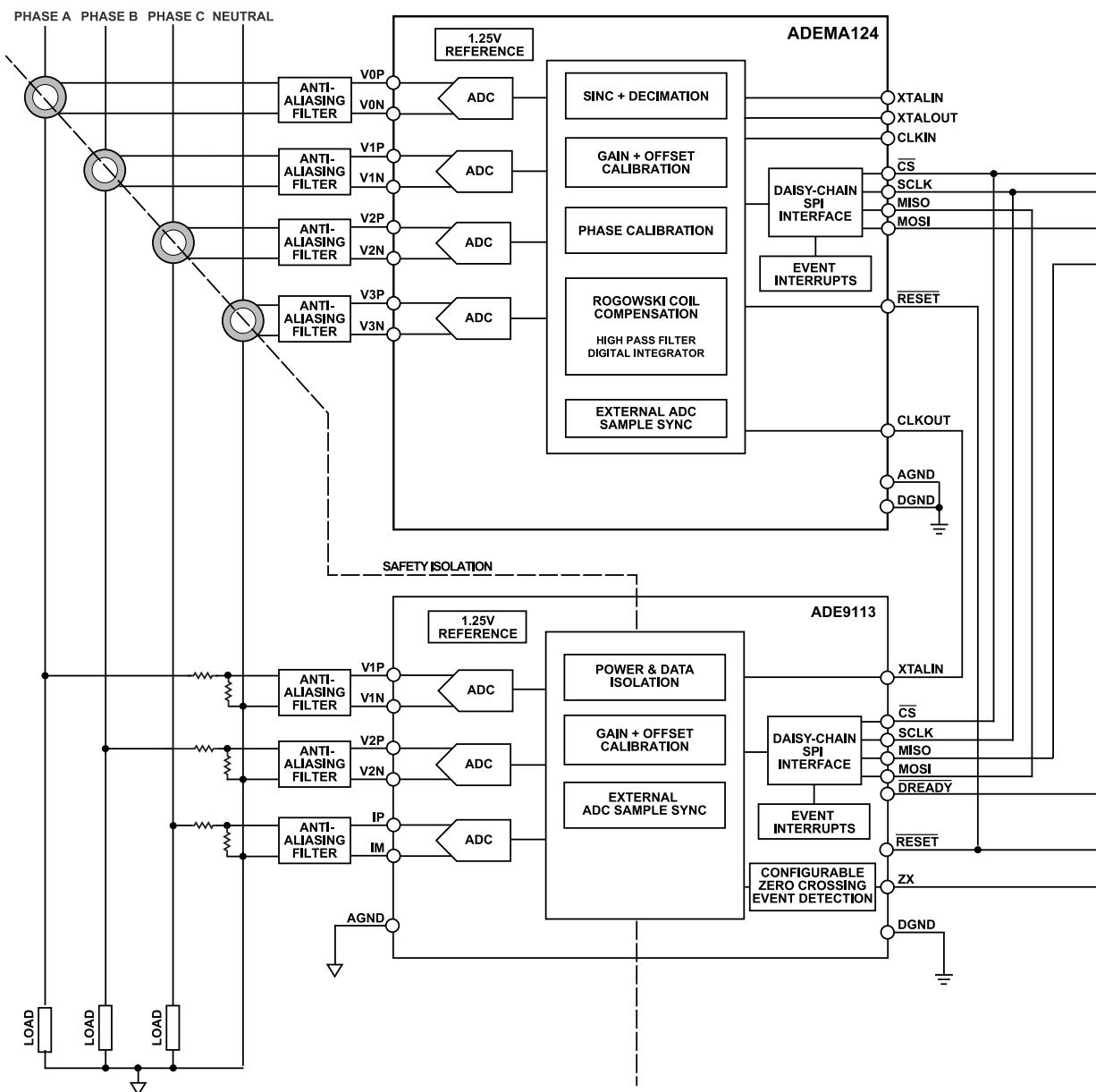

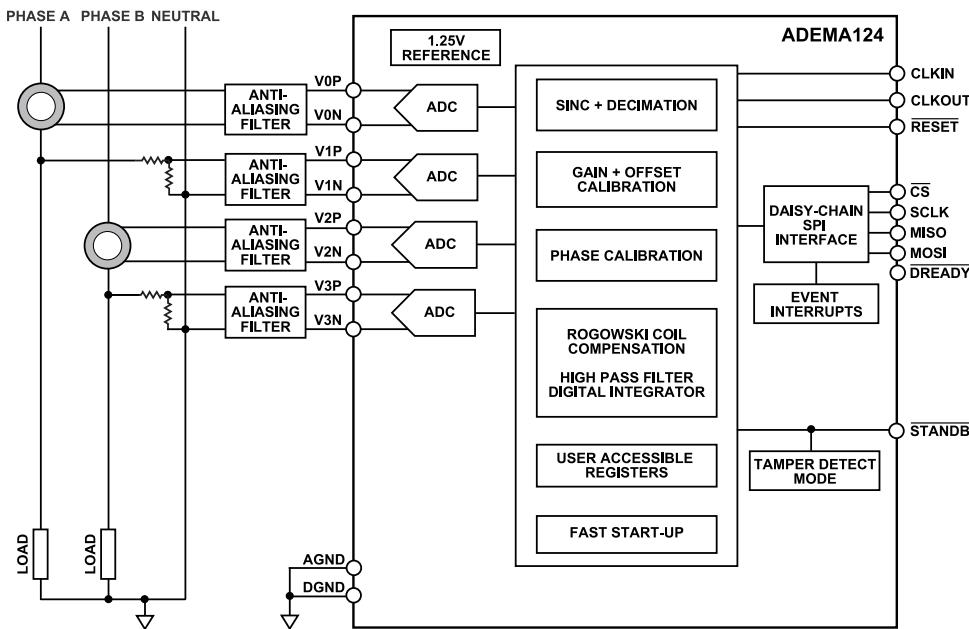

## FUNCTIONAL BLOCK DIAGRAMS

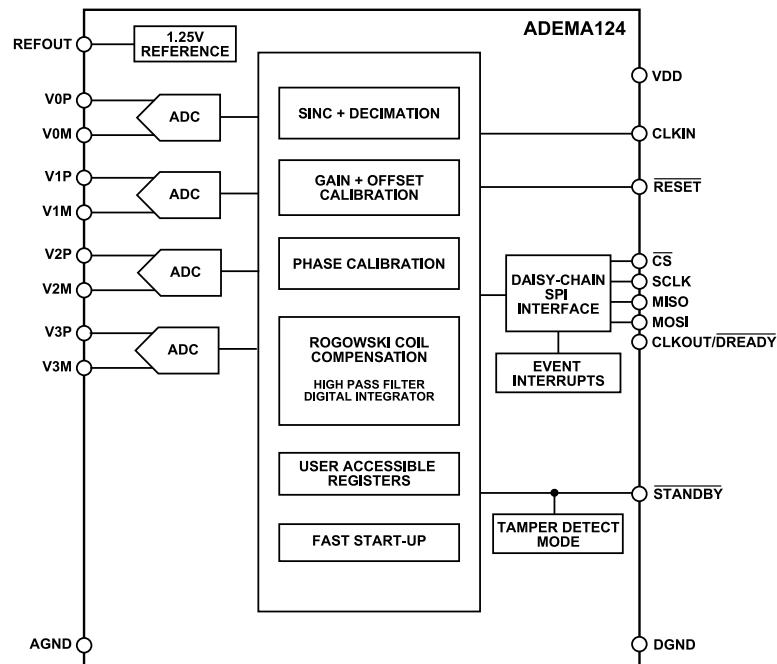

Figure 1. ADEMA124 Functional Block Diagram

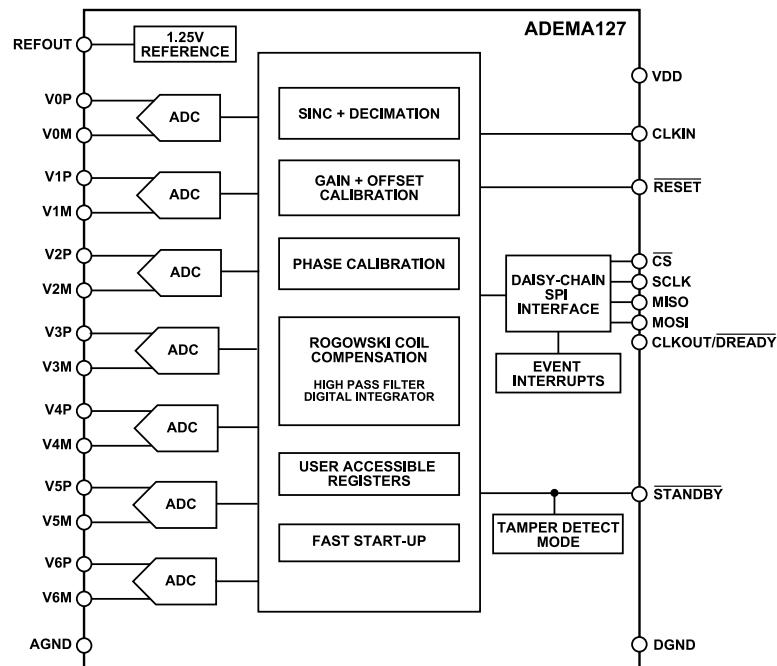

Figure 2. ADEMA127 Functional Block Diagram

## SPECIFICATIONS

$V_{DD} = 3.3V \pm 10\%$ ,  $GND = 0V$ , on-chip reference,  $f_{XTALIN} = 16.384MHz$ ,  $T_{MIN}$  to  $T_{MAX} = -40^\circ C$  to  $+125^\circ C$ ,  $T_A = 25^\circ C$  (typical). Output rate 4kHz. Values are based off full performance mode,  $ADC\_POWER\_MODE = 11$ , unless otherwise specified.

Table 2. Electrical Characteristics

| Parameter                               | Min  | Typ   | Max  | Unit   | Test Conditions/Comments                                                                         |

|-----------------------------------------|------|-------|------|--------|--------------------------------------------------------------------------------------------------|

| POWER SUPPLY                            |      |       |      |        |                                                                                                  |

| Start-Up Inrush <sup>1</sup>            |      | 55    |      | mA     | Includes required decoupling capacitors                                                          |

| ADEMA124                                |      |       |      |        |                                                                                                  |

| High Resolution                         |      | 9.9   | 11.2 | mA     | All DSP filters enabled, $f_{XTALIN} = 16.384MHz$ , $f_{MOD} = 2.048MHz$ , $f_s = 64kSPS$        |

| Default Configuration                   |      | 4.2   | 4.9  | mA     | No DSP filters enabled, $f_{XTALIN} = 16.384MHz$ , $f_{MOD} = 2.048MHz$ , $f_s = 32kSPS$         |

| Low Power                               |      | 1.8   | 2.3  | mA     | $f_{XTALIN} = 2.048MHz$ , $f_{MOD} = 256kHz$ , DSP off, $f_s = 1kSPS$ , $ADC\_POWER\_MODE = 0x0$ |

| Standby/Reset Mode                      |      | 4     |      | μW     |                                                                                                  |

| Tamper Detect Mode                      |      | 11.25 |      | mW     | 2 ADC channels active                                                                            |

| ADEMA127                                |      |       |      |        |                                                                                                  |

| High Resolution                         |      | 11.5  | 13.1 | mA     | All DSP filters enabled, $f_{XTALIN} = 16.384MHz$ , $f_{MOD} = 2.048MHz$ , $f_s = 64kSPS$        |

| Default Configuration                   |      | 5.4   | 6.3  | mA     | DSP off, $f_{XTALIN} = 16.384MHz$ , $f_{MOD} = 2.048MHz$ , $f_s = 32kSPS$                        |

| Low Power                               |      | 2.2   | 2.8  | mA     | $f_{XTALIN} = 2.048MHz$ , $f_{MOD} = 256kHz$ , DSP off, $f_s = 1kSPS$ , $ADC\_POWER\_MODE = 0x0$ |

| Standby/Reset Mode                      |      | 4     |      | μW     |                                                                                                  |

| Tamper Detect Mode                      |      | 12.5  |      | mW     | 4 ADC channels active                                                                            |

| INTERNAL VOLTAGE REFERENCE <sup>2</sup> |      |       |      |        |                                                                                                  |

| Voltage Reference                       |      | 1.25  |      | V      | $V_{REF}$                                                                                        |

| Temperature Coefficient                 |      | 5     | 15   | ppm/°C |                                                                                                  |

| EXTERNAL VOLTAGE REFERENCE              |      |       |      |        |                                                                                                  |

| Input Voltage (REFOUT)                  |      | 1.25  |      | V      | $V_{REF}$                                                                                        |

| Input Impedance (REFOUT)                |      | 20    |      | kΩ     |                                                                                                  |

| TEMPERATURE RANGE                       |      |       |      |        |                                                                                                  |

| Operating Range                         | -40  |       | +125 | °C     |                                                                                                  |

| ANALOG INPUTS                           |      |       |      |        |                                                                                                  |

| Differential Voltage Range              |      |       |      |        |                                                                                                  |

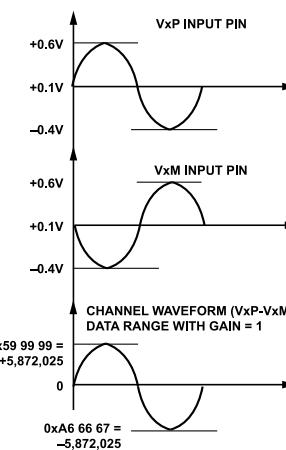

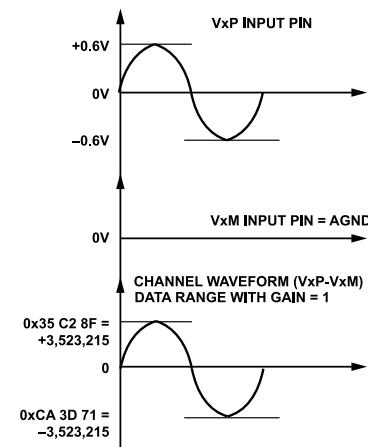

| 1x Gain                                 | -1.2 |       | +1.2 | V      | $V_{xP} - V_{xN}$                                                                                |

| 2x Gain                                 | -0.6 |       | +0.6 | V      | $ADC\_GAIN\_CHx = 0$                                                                             |

| Common-Mode Range                       |      |       |      |        |                                                                                                  |

| $ADC\_CMI\_CHx = 0$                     | -0.1 |       | +0.1 | V      | $ADC\_GAIN\_CHx = 1$                                                                             |

| $ADC\_CMI\_CHx = 1$                     | 0.9  |       | 1.2  | V      | $(V_{xP} + V_{xN})/2$                                                                            |

| Single-Ended Voltage Range              |      |       |      |        |                                                                                                  |

| 1x Gain                                 | -0.6 |       | +0.6 | V      | Input from CT or voltage divider                                                                 |

| 2x Gain                                 | -0.3 |       | +0.3 | V      | Input from preamplifier with DC offset                                                           |

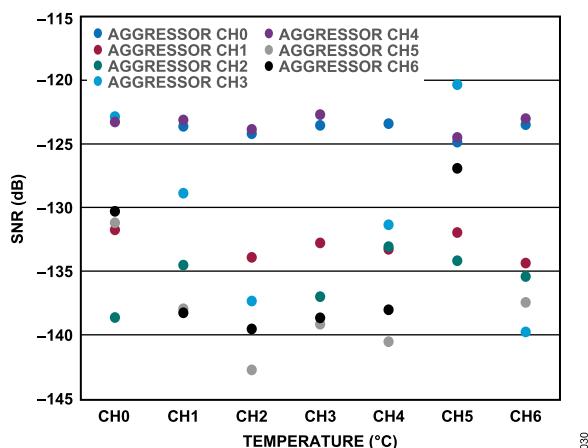

| Crosstalk                               |      |       |      |        |                                                                                                  |

| 1x Gain                                 |      | -120  |      | dB     | Pseudodifferential connection, voltage on the pin with respect to AGND (AGND = DGND)             |

| 2x Gain                                 |      | -120  |      | dB     | Full-scale without clipping, $ADC\_CMI\_CHx = 0$ , $ADC\_GAIN\_CHx = 0$                          |

|                                         |      |       |      |        | Full-scale without clipping, $ADC\_CMI\_CHx = 0$ , $ADC\_GAIN\_CHx = 1$                          |

|                                         |      |       |      |        | Aggressor channels at full-scale                                                                 |

## SPECIFICATIONS

Table 2. Electrical Characteristics (Continued)

| Parameter                                                                  | Min  | Typ       | Max  | Unit    | Test Conditions/Comments                                                                                        |

|----------------------------------------------------------------------------|------|-----------|------|---------|-----------------------------------------------------------------------------------------------------------------|

| Differential Input Impedance                                               |      |           |      |         |                                                                                                                 |

| 1x Gain                                                                    |      | 150       |      | kΩ      |                                                                                                                 |

| 2x Gain                                                                    |      | 75        |      | kΩ      |                                                                                                                 |

| ADC Offset Error                                                           |      |           |      |         |                                                                                                                 |

| 1x Gain                                                                    | -150 | ±20       | 150  | µV      |                                                                                                                 |

| 2x Gain                                                                    | -150 | ±45       | 150  | µV      |                                                                                                                 |

| ADC Offset Drift over Temperature                                          |      |           | 150  | nV/°C   |                                                                                                                 |

| ADC Gain Error                                                             | -2.0 | ±0.1      | +2.0 | %       | Not including anti-aliasing filter                                                                              |

| ADC Gain Drift over Temperature                                            |      | 5         |      | ppm/°C  | Without internal voltage reference                                                                              |

|                                                                            |      | 2         | 10   | ppm/°C  | With internal voltage reference                                                                                 |

| ADC Transfer Function                                                      |      |           |      |         | 1.25V internal reference. Without gain error correction. See the <a href="#">ADC Transfer Function</a> section. |

| 1x Gain                                                                    |      | 4,772,275 |      | codes/V |                                                                                                                 |

| 2x Gain                                                                    |      | 9,543,472 |      | codes/V |                                                                                                                 |

| Tamper Detect Mode                                                         |      |           |      |         |                                                                                                                 |

| Total Unadjusted Error (TUE)                                               | -2   |           | +2   | %FSR    |                                                                                                                 |

| POWER-SUPPLY REJECTION RATIO (PSRR)/<br>COMMON-MODE REJECTION RATIO (CMRR) |      |           |      |         |                                                                                                                 |

| PSRR                                                                       |      | 120       |      | dB      | 120mV <sub>RMS</sub> 50Hz contaminated VDD                                                                      |

| CMRR                                                                       |      |           |      |         |                                                                                                                 |

| 1x Gain                                                                    |      | 110       |      | dB      | ADC_CMI_CHx = 0                                                                                                 |

| 1x Gain                                                                    |      | 95        |      | dB      | ADC_CMI_CHx = 1                                                                                                 |

| 2x Gain                                                                    |      | 110       |      | dB      | ADC_CMI_CHx = 0                                                                                                 |

| ADC PERFORMANCE                                                            |      |           |      |         | $f_{MOD} = 2.048\text{MHz}$                                                                                     |

| 32kSPS                                                                     |      |           |      |         |                                                                                                                 |

| Signal-to-Noise Ratio (SNR)                                                |      |           |      |         |                                                                                                                 |

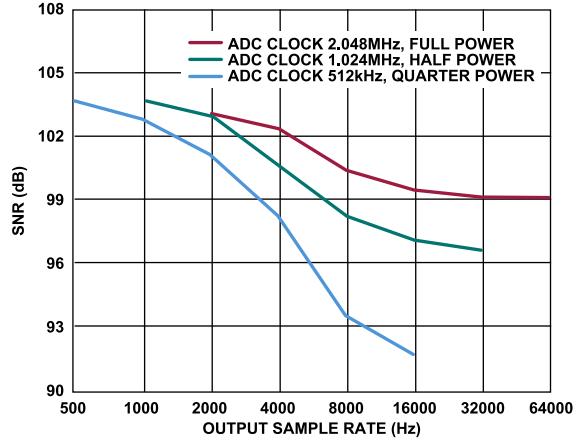

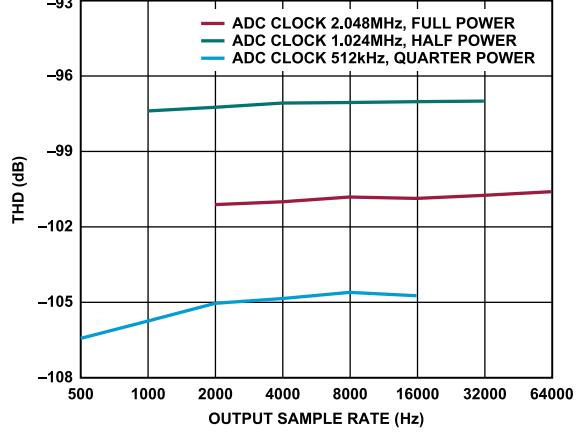

| 1x Gain                                                                    |      | 97        |      | dBFS    | <a href="#">Figure 25</a> , <a href="#">Figure 27</a>                                                           |

| 2x Gain                                                                    |      | 97        |      | dBFS    | <a href="#">Figure 28</a>                                                                                       |

| Signal-to-Noise and Distortion Ratio (SINAD)                               |      |           |      |         |                                                                                                                 |

| 1x Gain                                                                    |      | 95        |      | dBFS    |                                                                                                                 |

| 2x Gain                                                                    |      | 87        |      | dBFS    |                                                                                                                 |

| Total Harmonic Distortion (THD)                                            |      |           |      |         |                                                                                                                 |

| 1x Gain                                                                    |      | -98       |      | dBFS    | <a href="#">Figure 26</a> , <a href="#">Figure 30</a>                                                           |

| 2x Gain                                                                    |      | -88       |      | dBFS    |                                                                                                                 |

| Spurious-Free Dynamic Range (SFDR)                                         |      |           |      |         |                                                                                                                 |

| 1x Gain                                                                    |      | 100       |      | dBFS    |                                                                                                                 |

| 2x Gain                                                                    |      | 89        |      | dBFS    |                                                                                                                 |

| 4kSPS                                                                      |      |           |      |         |                                                                                                                 |

| SNR                                                                        |      |           |      |         |                                                                                                                 |

| 1x Gain                                                                    |      | 102       |      | dBFS    |                                                                                                                 |

| 2x Gain                                                                    |      | 101       |      | dBFS    |                                                                                                                 |

| SINAD                                                                      |      |           |      |         |                                                                                                                 |

| 1x Gain                                                                    |      | 98        |      | dBFS    |                                                                                                                 |

| 2x Gain                                                                    |      | 90        |      | dBFS    |                                                                                                                 |

| THD                                                                        |      |           |      |         |                                                                                                                 |

| 1x Gain                                                                    |      | -101      |      | dBFS    |                                                                                                                 |

| 2x Gain                                                                    |      | -90       |      | dBFS    |                                                                                                                 |

| SFDR                                                                       |      |           |      |         |                                                                                                                 |

## SPECIFICATIONS

Table 2. Electrical Characteristics (Continued)

| Parameter                                             | Min    | Typ    | Max    | Unit | Test Conditions/Comments                              |

|-------------------------------------------------------|--------|--------|--------|------|-------------------------------------------------------|

| 1x Gain                                               |        | 104    |        | dBFS |                                                       |

| 2x Gain                                               |        | 92     |        | dBFS |                                                       |

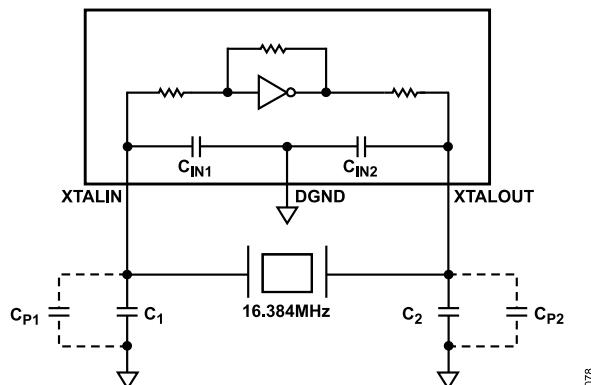

| CRYSTAL OSCILLATOR                                    |        |        |        |      |                                                       |

| Nominal Crystal Frequency                             | 12.288 |        | 16.384 | MHz  |                                                       |

| Internal Capacitance on CLKIN, CLKOUT                 |        | 3.5    |        | pF   |                                                       |

| Internal Feedback Resistance between CLKIN and CLKOUT |        | 2.5    |        | MΩ   |                                                       |

| Transconductance ( $g_m$ )                            | 6      | 8      |        | mA/V |                                                       |

| EXTERNAL CLOCK INPUT                                  |        |        |        |      |                                                       |

| Input Clock Frequency                                 | 0.3    | 16.384 | 16.547 | MHz  |                                                       |

| XTALIN Duty Cycle                                     | 45     |        | 55     | %    |                                                       |

| With XTALOUT Routed to Other Devices                  | 47.5   |        | 52.5   | %    |                                                       |

| XTALIN Pulse Width                                    | 28     |        |        | ns   |                                                       |

| CLOCK OUTPUT                                          |        |        |        |      |                                                       |

| XTALIN to CLKOUT Propagation Delay                    |        | 6      |        | ns   |                                                       |

| OUTPUT SAMPLE RATE                                    |        |        |        |      |                                                       |

| ΣΔ Modulator Frequency ( $f_{MOD}$ )                  |        |        | 2.048  | MHz  |                                                       |

| DSP Frequency ( $f_{DSP}$ )                           |        |        | 64     | kSPS |                                                       |

| LOGIC INPUTS - XTALIN Pin                             |        |        |        |      |                                                       |

| Input High Voltage, $V_{INH}$                         | 1.2    |        |        | V    |                                                       |

| Input Low Voltage, $V_{INL}$                          |        |        | 0.5    | V    |                                                       |

| LOGIC INPUTS - MOSI, SCLK, CS, STDBY, and RESET Pins  |        |        |        |      |                                                       |

| Input High Voltage, $V_{INH}$                         | 2.0    |        |        | V    |                                                       |

| Input Low Voltage, $V_{INL}$                          |        |        | 0.8    | V    |                                                       |

| Input Current, $I_{IN}$ (MOSI, SCLK, CS)              |        |        | 8      | μA   |                                                       |

| Input Current, $I_{IN}$ (STDBY, and RESET)            |        |        | 200    | nA   | Integrated pull-up                                    |

| LOGIC OUTPUTS - CLKOUT/DREADY, and MISO Pins          |        |        |        |      |                                                       |

| Output High Voltage, $V_{OH}$                         | 2.4    |        |        |      | Source current ( $I_{SOURCE}$ ) = 3.5mA               |

| Output Low Voltage, $V_{OL}$                          |        |        | 0.4    |      | Sink current ( $I_{SINK}$ ) = 3.5mA                   |

| LOW DROPOUT REGULATORS (LDOs)                         |        |        |        |      |                                                       |

| ALDOOUT                                               |        | 1.9    |        | V    |                                                       |

| VLDOOUT                                               |        | 1.9    |        | V    |                                                       |

| UNDERVOLTAGE LOCKOUT <sup>1</sup>                     |        |        |        |      | UVLO                                                  |

| Positive VDD Threshold                                |        |        | 2.8    | V    | Rising supply voltage enable threshold, $V_{UVLO+}$   |

| Negative VDD Threshold                                | 2.2    |        |        | V    | Falling supply voltage lockout threshold, $V_{UVLO-}$ |

| VDD Hysteresis                                        |        |        | 14     | mV   | UVLO hysteresis, $V_{UVLO\_HYS}$                      |

<sup>1</sup> Guaranteed by design. Not subject to production test.<sup>2</sup> The reference temperature coefficient is trimmed in production test to optimize channel gain.

## SPECIFICATIONS

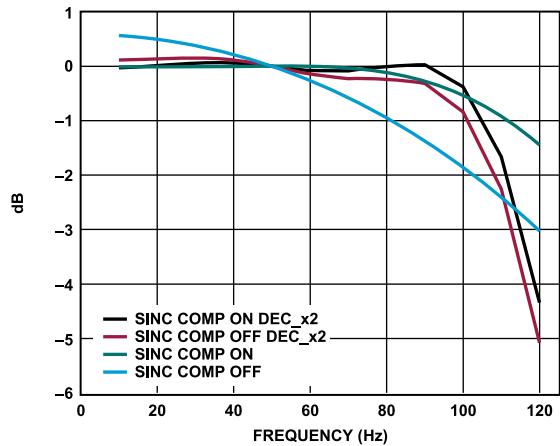

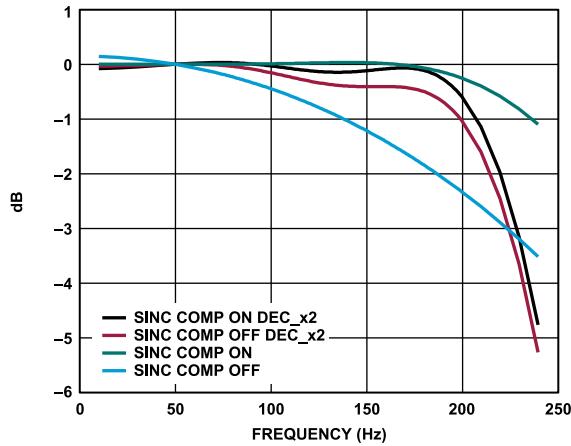

## BANDWIDTH AND PASS-BAND FLATNESS

All specifications typical figures for  $f_{XTALIN} = 16.384\text{MHz}$  and default DSP filter coefficients.

Table 3. Bandwidth and Pass-Band Flatness Characteristics

| Parameter                   | Sinc Decimation Only | Sinc Compensation | Sinc Compensation and LPF | Sinc Compensation, LPF, and DSP Decimate-by-2 | Unit | Comment                |

|-----------------------------|----------------------|-------------------|---------------------------|-----------------------------------------------|------|------------------------|

| Output Bandwidth (-3dB)     |                      |                   |                           |                                               |      |                        |

| 64kSPS                      | 17,000               | 21,000            | 14,500                    | N/A <sup>1</sup>                              | Hz   | ADC Output Bandwidth   |

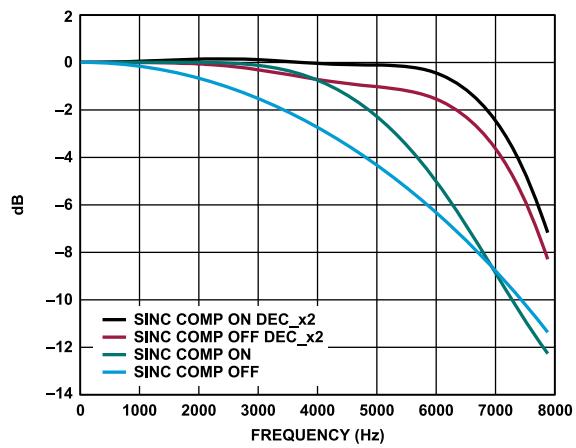

| 32kSPS                      | 8,400                | 9,300             | 7,150                     | 14,500                                        | Hz   | Figure 7               |

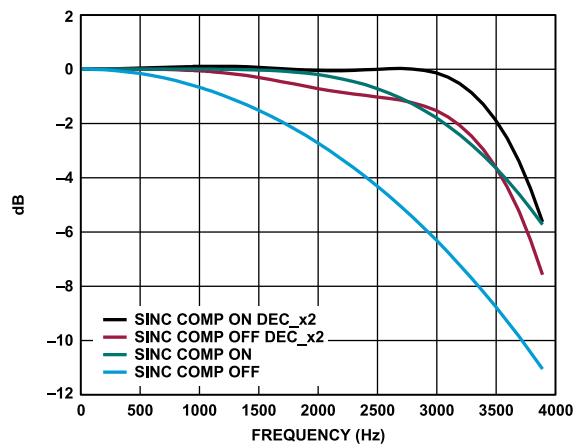

| 16kSPS                      | 4,200                | 5,300             | 3,650                     | 7,200                                         | Hz   | Figure 8               |

| 8kSPS                       | 2,100                | 3,400             | 1,850                     | 3,650                                         | Hz   | Figure 11              |

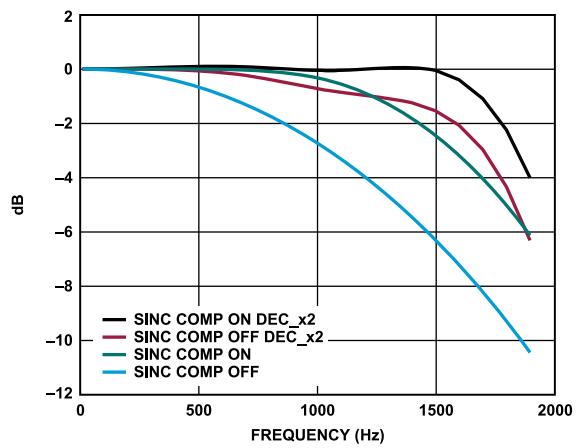

| 4kSPS                       | 1,050                | 1,600             | 920                       | 1,850                                         | Hz   | Figure 9               |

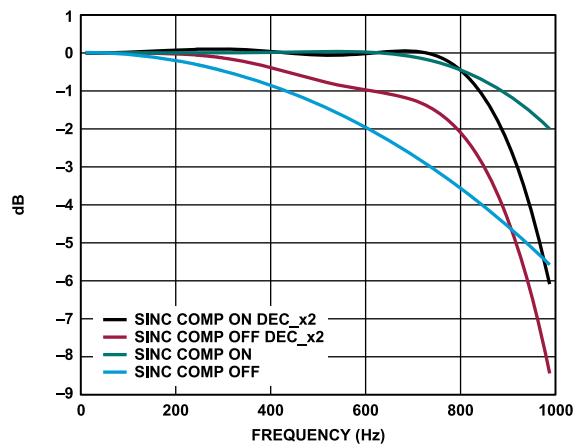

| 2kSPS                       | 740                  | > $f_s/2$         | 465                       | 920                                           | Hz   | Figure 12              |

| 1kSPS                       | 420                  | 410               | 250                       | 465                                           | Hz   | Figure 13              |

| 500SPS                      | 225                  | > $f_s/2$         | 125                       | 230                                           | Hz   | Figure 15              |

| 250SPS                      | 120                  | > $f_s/2$         | 58                        | 115                                           | Hz   | Figure 14              |

| Pass-Band Flatness (-0.1dB) |                      |                   |                           |                                               |      |                        |

| 64kSPS                      | 3,100                | 10,000            | 11,000                    | N/A <sup>1</sup>                              | Hz   | ADC Pass-Band Flatness |

| 32kSPS                      | 1,600                | 4,800             | 4,600                     | 11,000                                        | Hz   | Figure 7               |

| 16kSPS                      | 800                  | 2,900             | 2,950                     | 4,600                                         | Hz   | Figure 10              |

| 8kSPS                       | 400                  | 1,800             | 1,700                     | 3,300                                         | Hz   | Figure 8               |

| 4kSPS                       | 200                  | 850               | 850                       | 1,650                                         | Hz   | Figure 11              |

| 2kSPS                       | 150                  | 700               | 385                       | 760                                           | Hz   | Figure 9               |

| 1kSPS                       | 94                   | 180               | 180                       | 420                                           | Hz   | Figure 12              |

| 500SPS                      | 70                   | 185               | 104                       | 115                                           | Hz   | Figure 13              |

| 250SPS                      | 55                   | 80                | 31 <sup>2</sup>           | 95                                            | Hz   | Figure 15              |

<sup>1</sup> N/A means not applicable. This is not a valid configuration.

<sup>2</sup> Referenced to 10Hz.

## SPECIFICATIONS

## TIMING CHARACTERISTICS

$V_{DD} = 3.3V \pm 10\%$ ,  $AGND = 0V$ ,  $DGND = 0V$ , on-chip reference,  $f_{XTALIN} = 16.384MHz$ , and  $T_{MIN}$  to  $T_{MAX} = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.

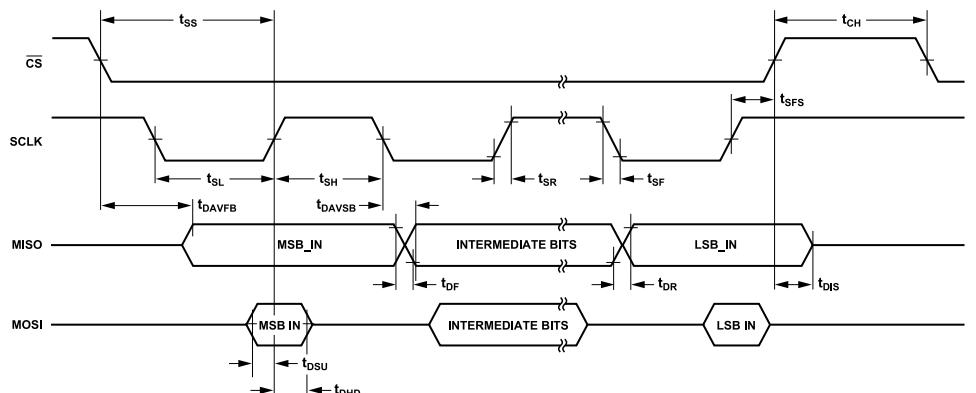

Table 4. SPI Interface Timing Parameters

| Parameter <sup>1</sup>                                          | Symbol      | Min | Max    | Unit |

|-----------------------------------------------------------------|-------------|-----|--------|------|

| CS to SCLK Positive Edge                                        | $t_{SS}$    | 10  |        | ns   |

| SCLK Frequency <sup>2</sup>                                     | $f_{SCLK}$  | 250 | 22,000 | kHz  |

| SCLK Duty Cycle                                                 |             | 40  | 60     | %    |

| SCLK Low Pulse Width                                            | $t_{SL}$    | 20  |        | ns   |

| SCLK High Pulse Width                                           | $t_{SH}$    | 20  |        | ns   |

| Data Output Valid After $\overline{CS}$ Edge                    | $t_{DAVFB}$ |     | 20     | ns   |

| Subsequent Data Output Valid after SCLK Edge                    | $t_{DAVSB}$ |     | 20     | ns   |

| Data Input Setup Time before SCLK Edge                          | $t_{DSU}$   | 10  |        | ns   |

| Data Input Hold Time after SCLK Edge                            | $t_{DHD}$   | 10  |        | ns   |

| Data Output Fall Time                                           | $t_{DF}$    |     | 10     | ns   |

| Data Output Rise Time                                           | $t_{DR}$    |     | 10     | ns   |

| SCLK Rise Time                                                  | $t_{SR}$    |     | 5      | ns   |

| SCLK Fall Time                                                  | $t_{SF}$    |     | 5      | ns   |

| MISO Disable after $\overline{CS}$ Rising Edge                  | $t_{DIS}$   |     | 20     | ns   |

| $\overline{CS}$ High after SCLK Edge                            | $t_{SFS}$   |     | 10     | ns   |

| $\overline{CS}$ High Time between SPI Transactions <sup>3</sup> | $t_{CH}$    | 400 |        | ns   |

<sup>1</sup> Specifications guaranteed by design and characterization and not subject to production test.

<sup>2</sup>  $f_{SCLK}$  must be  $<1.4 \times f_{XTALIN}$ .

<sup>3</sup> For  $f_{XTALIN} < 16.384MHz$ ,  $t_{CH}$  must be  $>6/f_{XTALIN}$ . For more details, see the SPI Compatible Communication section.

Figure 3. SPI Timing, SPI mode 3 (CPOL = 1 and CPHA = 1)

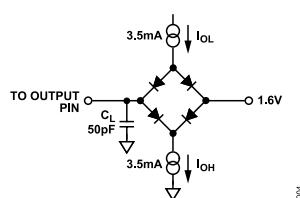

Figure 4. Load Circuit for Timing Specifications

## ABSOLUTE MAXIMUM RATINGS

Table 5. ADEMA124/ADEMA127 Absolute Maximum Ratings

| Parameter                                                                             | Rating                   |

|---------------------------------------------------------------------------------------|--------------------------|

| $V_{DD}$ to DGND                                                                      | -0.3V to +3.7V           |

| Analog Input Voltage                                                                  |                          |

| $V_{0P}$ and $V_{0M}$ to DGND                                                         | -1.7V to +2V             |

| $V_{1P}$ and $V_{1M}$ to DGND                                                         | -1.7V to +2V             |

| $V_{2P}$ and $V_{2M}$ to DGND                                                         | -1.7V to +2V             |

| $V_{3P}$ and $V_{3M}$ to DGND                                                         | -1.7V to +2V             |

| $V_{4P}$ and $V_{4M}$ to DGND                                                         | -1.7V to +2V             |

| $V_{5P}$ and $V_{5M}$ to DGND                                                         | -1.7V to +2V             |

| $V_{6P}$ and $V_{6M}$ to DGND                                                         | -1.7V to +2V             |

| Digital Input Voltage                                                                 |                          |

| MOSI, SCLK, $\overline{CS}$ , XTALIN, $\overline{STDBY}$ , $\overline{RESET}$ to DGND | -0.3V to $V_{DD}$ + 0.3V |

| Digital Output Voltage                                                                |                          |

| CLKOUT/ $\overline{DREADY}$ , MISO, XTALOUT to DGND                                   | -0.3V to $V_{DD}$ + 0.3V |

| Reference Voltage                                                                     |                          |

| REFOUT to DGND                                                                        | -0.3V to +2.2V           |

| Temperature                                                                           |                          |

| Operating                                                                             | -40°C to +125°C          |

| Storage Range                                                                         | -65°C to +150°C          |

| Lead (Soldering, 10sec) <sup>1</sup>                                                  | 260°C                    |

| Moisture Sensitivity Level                                                            | MSL 3                    |

<sup>1</sup> Analog Devices recommends that reflow profiles used in soldering RoHS compliant devices conform to J-STD-020D.1 from JEDEC. For the latest revision of this standard, refer to the JEDEC.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural junction-to-ambient thermal resistance measured in a one cubic foot sealed enclosure and  $\theta_{JC}$  is the junction-to-case thermal resistance.

Table 6. Thermal Resistance

| Package Type <sup>1</sup> | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|---------------------------|---------------|---------------|------|

| CP-32-20                  | 31.73         | 25.60         | °C/W |

<sup>1</sup> Test condition 1: Thermal impedance simulated values are based upon use of 2S2P JEDEC PCB.

## ESD CAUTION

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

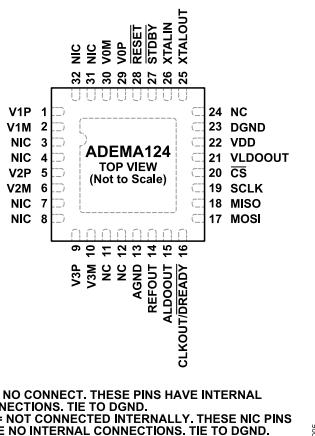

Figure 5. ADEMA124 Pin Configuration

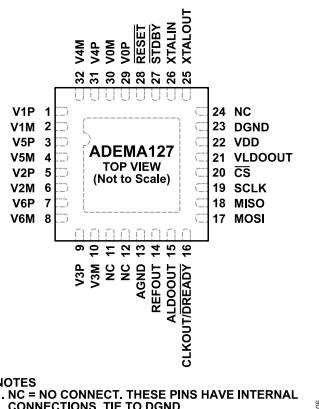

Figure 6. ADEMA127 Pin Configuration

Table 7. Pin Function Descriptions

| Pin Number         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADEMA124           | ADEMA127 | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1, 2               | 1, 2     | V1P, V1M | Analog Inputs for ADC Channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3, 4, 7, 8, 31, 32 |          | NIC      | Not Connected Internally. These NIC pins have no internal connections. Connect to DGND.                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | 3, 4     | V5P, V5M | Analog Inputs for ADC Channel 5.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5, 6               | 5, 6     | V2P, V2M | Analog Inputs for ADC Channel 2.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                    | 7, 8     | V6P, V6M | Analog Inputs for ADC Channel 6.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9, 10              | 9, 10    | V3P, V3M | Analog Inputs for ADC Channel 3.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 11, 12             | 11, 12   | NC       | No Connect. These pins have internal connections. Connect to DGND.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 13                 | 13       | AGND     | Analog Ground Reference. Connect to DGND.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 14                 | 14       | REFOUT   | This pin provides access to the on-chip voltage reference. The on-chip reference has a nominal value of 1.25V. Decouple the REFOUT pin to DGND with a 0.1 $\mu$ F capacitor and 2.2 $\mu$ F capacitor. Place capacitors as close as possible.<br>To use the internal voltage reference with external circuits, a buffer is required.<br>An external voltage reference may be connected to this pin. For more details, see the <a href="#">Voltage Reference</a> section. |

| 15                 | 15       | ALDOOUT  | 1.9V Output of Analog Low Dropout (LDO) Regulator.<br>Decouple this pin with a 0.22 $\mu$ F capacitor to DGND. Do not connect the external load circuitry to the ALDOOUT pin.                                                                                                                                                                                                                                                                                            |

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Table 7. Pin Function Descriptions (Continued)

| Pin Number |          |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|----------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADEMA124   | ADEMA127 | Name          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

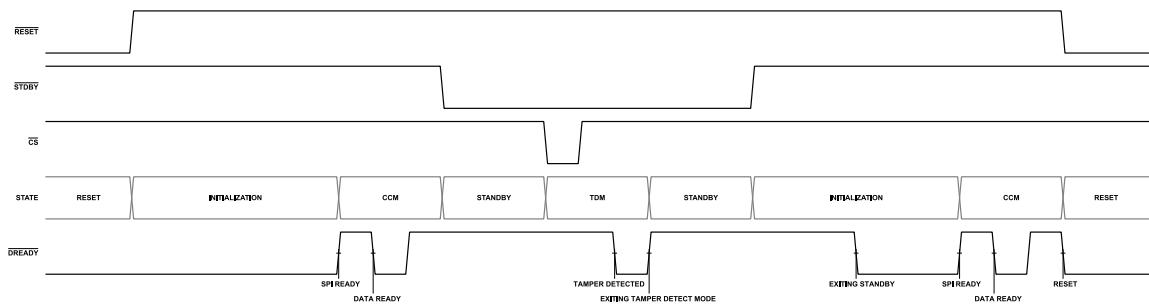

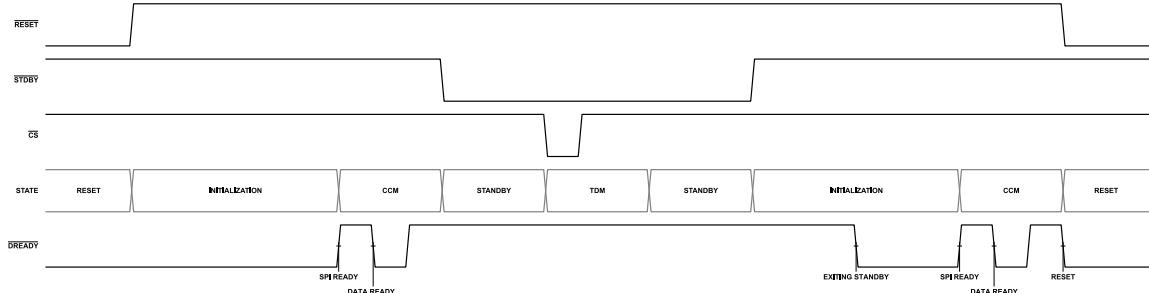

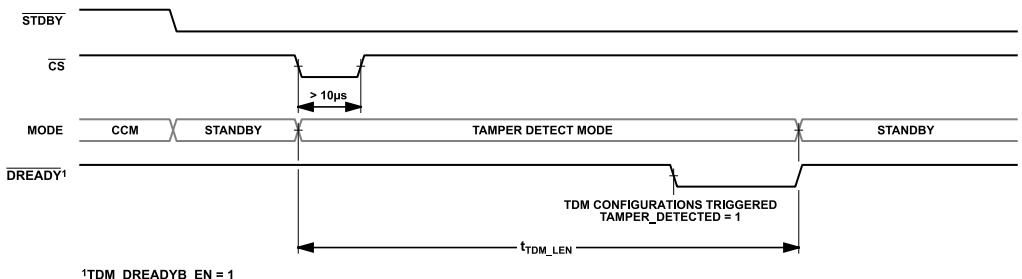

| 16         | 16       | CLKOUT/DREADY | <p>Data Ready, Active Low (DREADY). The DREADY pin generates an active-low signal to indicate the availability of new ADC samples and is synchronous to the ADC output frequency. Use this signal to synchronize the reading of ADC outputs.</p> <p>DREADY is the default functionality of the pin. The first rising edge after reset indicates that SPI port is ready for commands. A falling edge indicates ADC sample availability in CCM. See <a href="#">Figure 40</a>.</p> <p>DREADY may be set as an interrupt pin when ADEMA124/ADEMA127 operates in TDM. For more details, see the <a href="#">Tamper Detect Mode</a> section.</p> <p>Clock Output (CLKOUT). Pin function set by CLKOUT_EN bit. When CLKOUT functionality is selected, the ADEMA124/ADEMA127 generates a digital signal synchronous to the controller clock at the XTALIN pin. Use CLKOUT to provide a clock to other devices.</p> |

| 17         | 17       | MOSI          | Data Input for SPI Port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 18         | 18       | MISO          | Data Output for SPI Port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 19         | 19       | SCLK          | Serial Clock Input for SPI Port. All serial data transfers are synchronized to this clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 20         | 20       | CS            | Chip Select for SPI Port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 21         | 21       | VLDOOUT       | <p>1.9V Output of Digital Low Dropout (LDO) Regulator.</p> <p>Decouple this pin with a 0.22<math>\mu</math>F capacitor to DGND. Do not connect the external load circuitry to the VLDOOUT pin.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 22         | 22       | VDD           | Supply Voltage, 3.3V +/- 10%. Decouple this pin with a 0.1 $\mu$ F and 2.2 $\mu$ F capacitor to DGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 23         | 23       | DGND          | Digital Ground Reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 24         | 24       | NC            | No Connect. This pin has an internal connection. Connect to DGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 25         | 25       | XTALOUT       | Crystal Output. Choose a crystal based on the transconductance ( $g_m$ ) shown in <a href="#">Table 2</a> . Connect a crystal across XTALIN and XTALOUT to provide a clock source for the ADEMA124/ADEMA127. The XTALOUT pin must float when unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 26         | 26       | XTALIN        | <p>Controller Clock Input.</p> <p>An external clock can be provided at this logic input, such as the CLKOUT signal provided by another device.</p> <p>Alternatively, a crystal can be connected across XTALIN and XTALOUT.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 27         | 27       | STDBY         | Active Low Standby Input. This pin requires an external pull-up and should be tied to VDD if unused. For more details, see the <a href="#">Standby Mode</a> section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 28         | 28       | RESET         | Active Low Reset Input. This pin requires an external pull-up and must be connected to VDD if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 29, 30     | 29, 30   | V0P, V0M      | Analog Inputs for ADC Channel 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            | 31, 32   | V4P, V4M      | Analog Inputs for ADC Channel 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |          | EPAD          | Exposed Pad. The exposed pad must be connected to DGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## TYPICAL PERFORMANCE CHARACTERISTICS

007

010

008

011

009

012

## TYPICAL PERFORMANCE CHARACTERISTICS

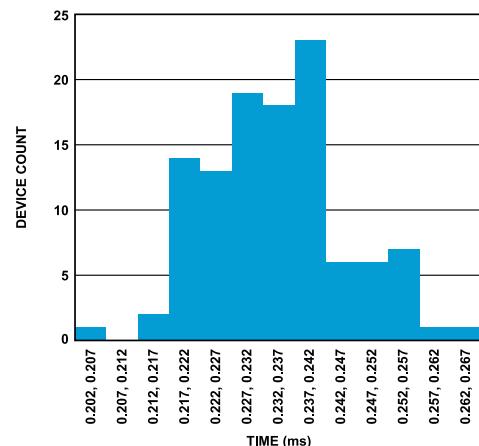

Figure 13. Bandwidth at 1kSPS

013

Figure 14. Bandwidth at 250SPS

014

Figure 15. Bandwidth at 500SPS

015

Figure 16. Fast Start-up Time Histogram

016

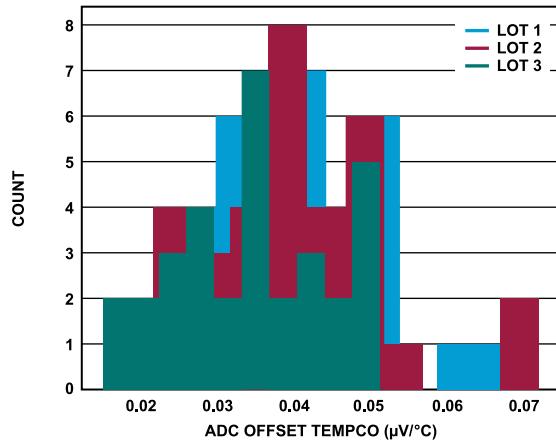

Figure 17. Input Offset Voltage vs. Temperature Histogram

017

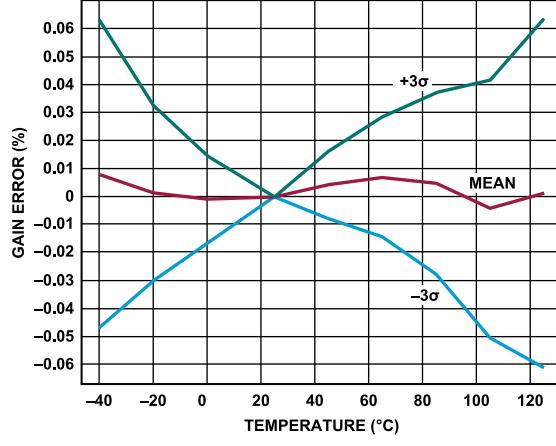

Figure 18. Gain Error vs. Temperature

018

## TYPICAL PERFORMANCE CHARACTERISTICS

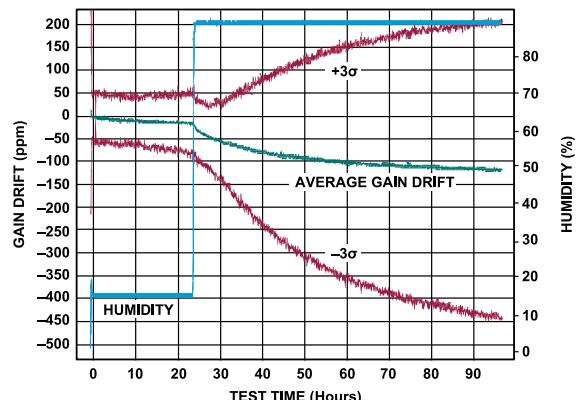

Figure 19. Gain Drift vs. Humidity, Mean and  $\pm 3\sigma$

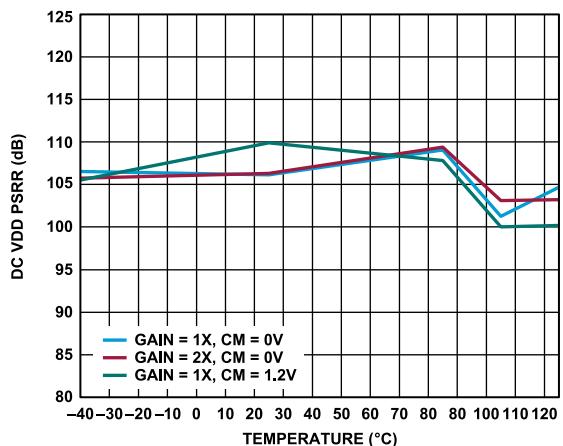

Figure 22. DC VDD PSRR vs. Temperature, Full Power Mode

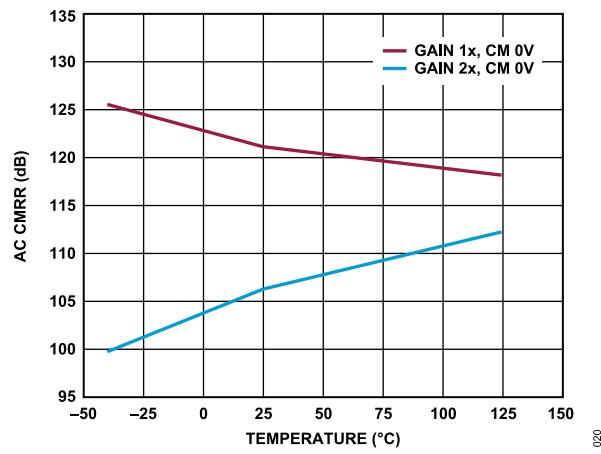

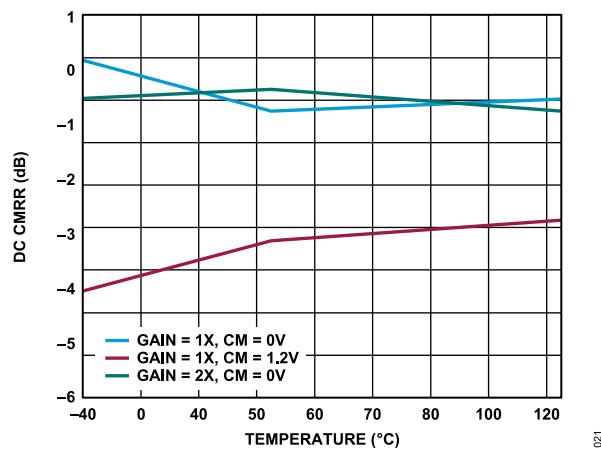

Figure 20. AC CMRR vs. VDD 50Hz,  $V_{DD} = 3.3V$ , Full Power Mode

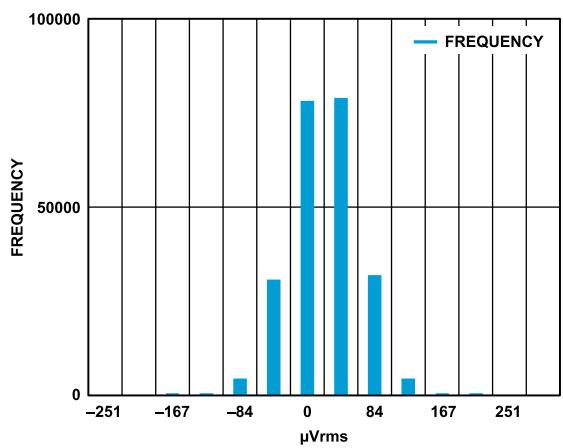

Figure 23. Single Device Noise Histogram at 32kSPS, Inputs Shorted, Gain = 1

Figure 21. DC CMRR vs. Temperature, Full Power Mode

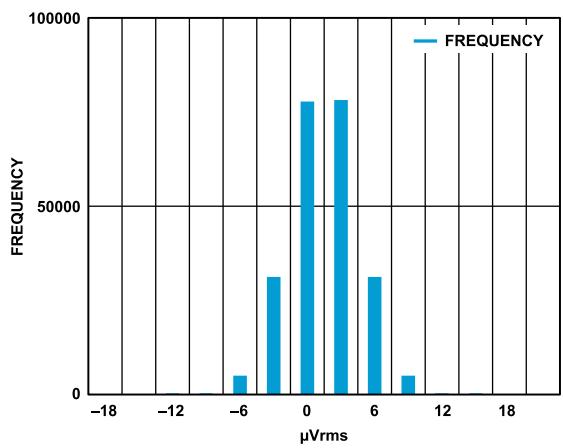

Figure 24. Single Device Noise Histogram at 4kSPS, ADC Inputs Shorted, Gain = 1

## TYPICAL PERFORMANCE CHARACTERISTICS

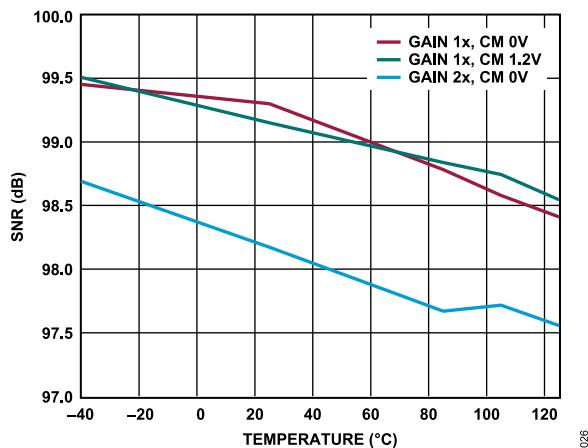

Figure 25. SNR vs. Temperature 32kSPS

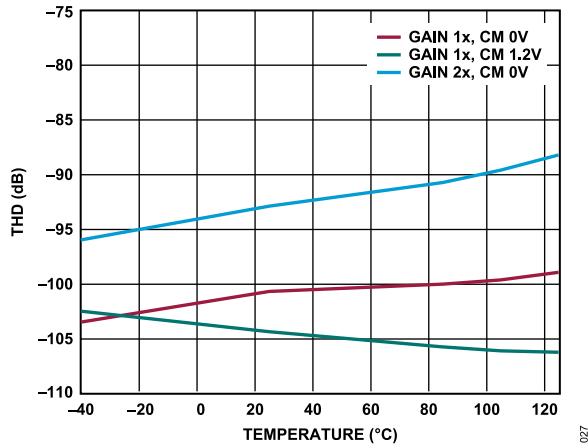

Figure 26. THD vs. Temperature 32kSPS

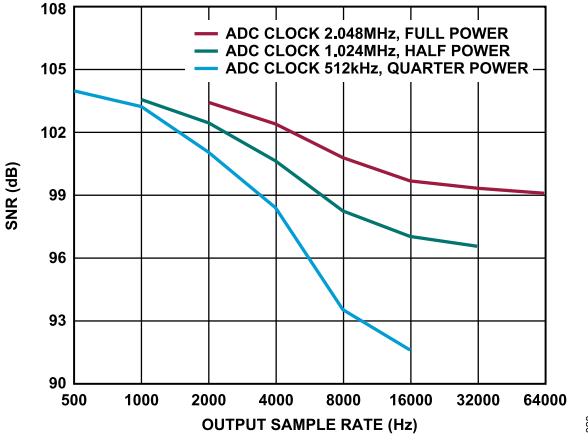

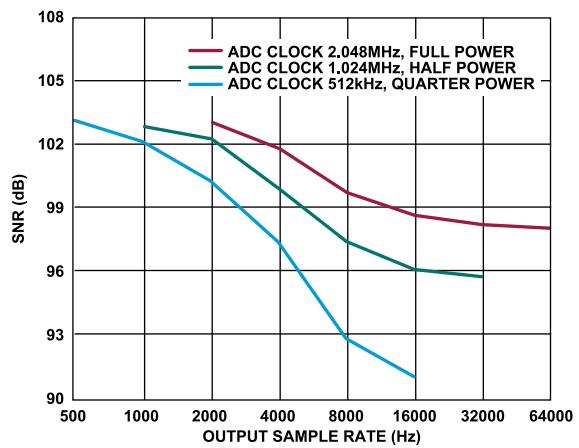

Figure 27. SNR vs. OSR, Gain = 1, Common-Mode = 0V

Figure 28. SNR vs OSR, Gain = 2, Common-Mode = 0V

Figure 29. SNR vs. OSR, Gain = 1, Common-Mode = 1.2V

Figure 30. THD vs. OSR Gain = 1

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 31. Crosstalk vs. Channel, Gain = 1, Common-Mode = 0V

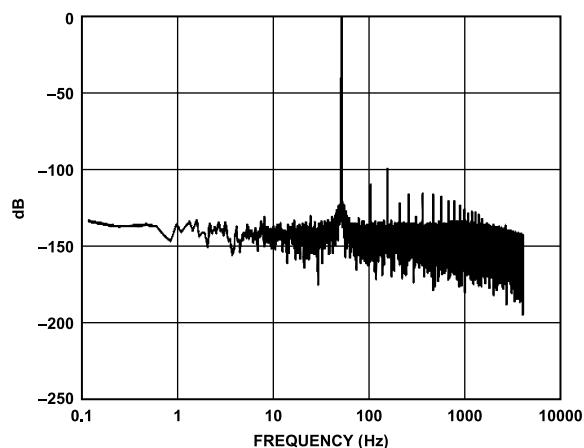

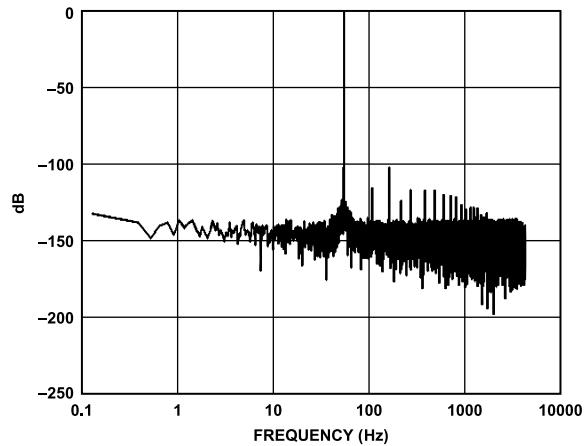

Figure 34. 50Hz Input, FFT, 8kSPS Sinc3 Only

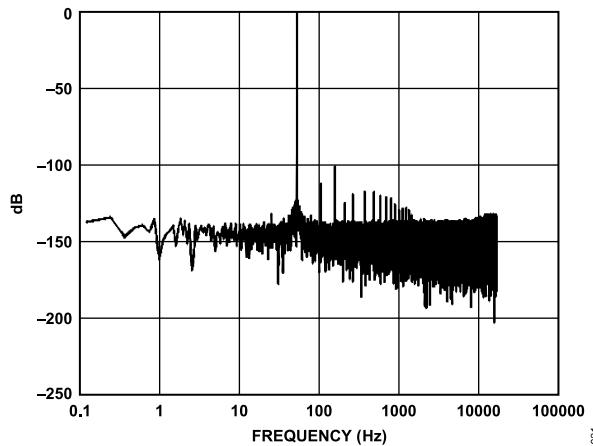

Figure 32. 50Hz Input, Fast Fourier Transform (FFT), 32kSPS Sinc3 Only

Figure 35. 50Hz Input, FFT, 8kSPS with DSP Sinc Compensation, Digital LPF and Decimate by 2 Enabled

Figure 33. 50Hz Input, FFT, 32kSPS with DSP Sinc Compensation, Digital LPF and Decimate by 2 Enabled

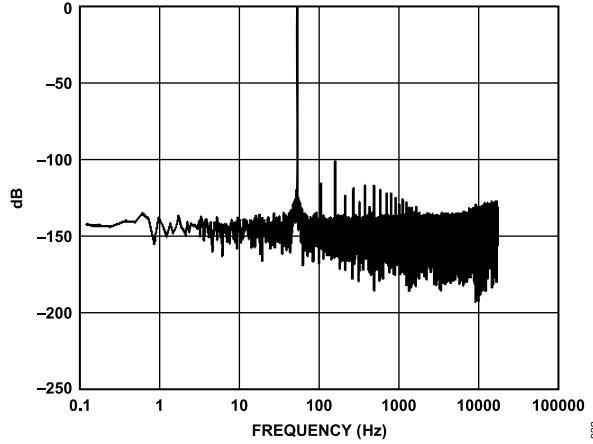

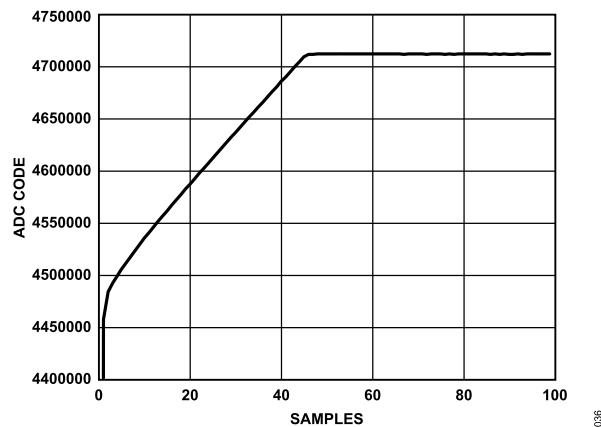

Figure 36. Sample Count Convergence to Specified Gain Error, Reset to CCM,  $f_{XTALIN} = 16.384\text{MHz}$ , Gain=1, 1VDC input

## TYPICAL PERFORMANCE CHARACTERISTICS

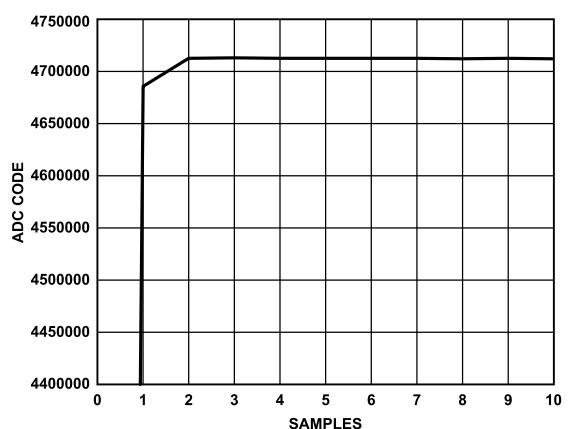

Figure 37. Sample Count Convergence to Specified Gain Error, TDM to CCM,

$f_{XTALIN} = 16.384\text{MHz}$ , Gain=1, 1VDC input

## TEST CIRCUIT

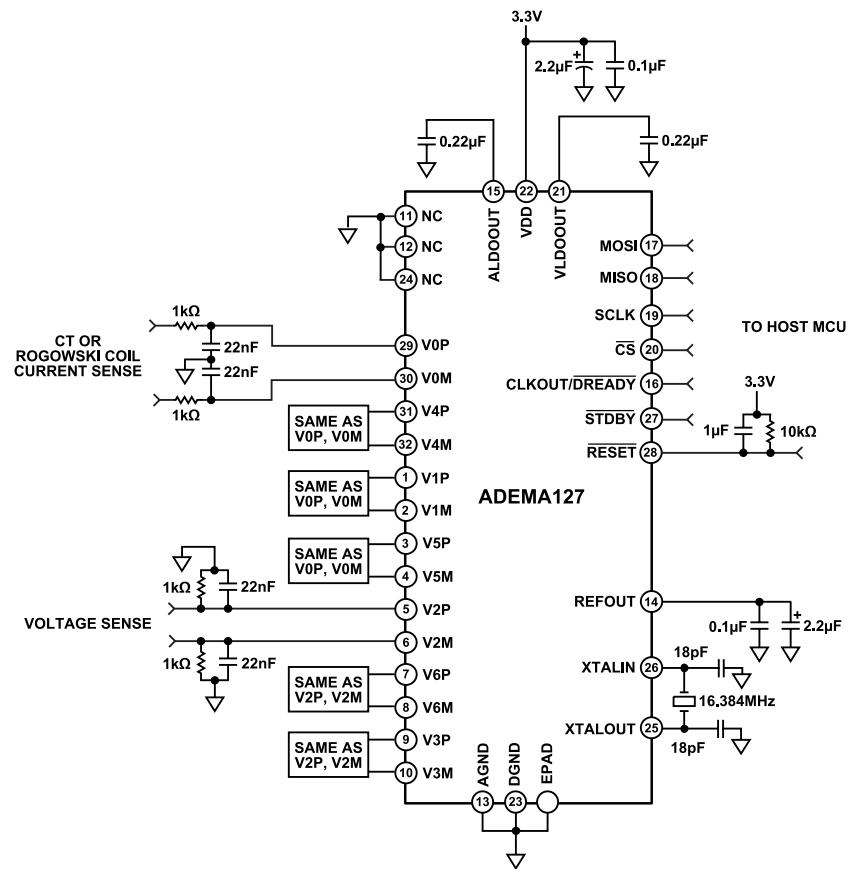

041

Figure 38. ADEMA127 Test Circuit, 3PH Voltage and Current

## TERMINOLOGY

### Crosstalk

Crosstalk is measured by grounding 1-channel and applying a full-scale 50Hz or 60Hz signal on all the other channels. The crosstalk is equal to the ratio between the grounded ADC output value and its ADC full-scale output value. The ADC outputs are acquired for 100sec. Crosstalk is expressed in decibels.

### Differential Input Impedance (DC)

The differential input impedance represents the impedance between the pair VxP and VxM. It varies with the ADC\_GAIN\_CHx gain selection, as shown in Differential Input Impedance specification in [Table 2](#).

### ADC Offset Error

ADC offset error is the difference between the average measured ADC output code with both inputs connected to AGND and the ideal ADC output code of zero. ADC offset is expressed in  $\mu$ V.

### ADC Offset Drift Over Temperature

The ADC offset drift is the change in offset over temperature. It is measured at  $-40^{\circ}\text{C}$ ,  $+25^{\circ}\text{C}$ , and  $+125^{\circ}\text{C}$ . Calculate the offset drift over temperature as follows:

$$\text{Drift} = \max\left(\left|\frac{\text{Offset}(-40^{\circ}\text{C}) - \text{Offset}(+25^{\circ}\text{C})}{(-40^{\circ}\text{C} - +25^{\circ}\text{C})}\right|, \left|\frac{\text{Offset}(+125^{\circ}\text{C}) - \text{Offset}(+25^{\circ}\text{C})}{(+125^{\circ}\text{C} - +25^{\circ}\text{C})}\right|\right) \quad (1)$$

Offset drift is expressed in  $\text{nV}/^{\circ}\text{C}$ .

### ADC Gain Error

The gain error in the ADCs represents the difference between the measured ADC output code (minus the offset) and the ideal output code when an external voltage reference of 1.25V is used. The difference is expressed as a percentage of the ideal code. It represents the overall gain error of 1-channel.

### ADC Gain Drift Over Temperature

This temperature coefficient includes the temperature variation of the ADC gain while using an external voltage reference of 1.25V. It represents the overall temperature coefficient of one current or voltage channel. With an external voltage reference of 1.25V in use, the ADC gain is measured at  $-40^{\circ}\text{C}$ ,  $+25^{\circ}\text{C}$ , and  $+125^{\circ}\text{C}$ . Then the temperature coefficient is computed as follows:

$$\text{Drift} = \max\left(\left|\frac{\text{Gain}(-40^{\circ}\text{C}) - \text{Gain}(+25^{\circ}\text{C})}{\text{Gain}(+25^{\circ}\text{C}) \times (-40^{\circ}\text{C} - +25^{\circ}\text{C})}\right|, \left|\frac{\text{Gain}(+125^{\circ}\text{C}) - \text{Gain}(+25^{\circ}\text{C})}{\text{Gain}(+25^{\circ}\text{C}) \times (+125^{\circ}\text{C} - +25^{\circ}\text{C})}\right|\right) \quad (2)$$

Gain drift is measured in  $\text{ppm}/^{\circ}\text{C}$ .

### AC Power-Supply Rejection Ratio (PSRR)

AC PSRR quantifies the measurement error as a percentage of reading when the DC power supply is nominal ( $V_{\text{NOM}}$ ) and modulated with AC, and the inputs are grounded. For the AC PSRR measurement, 20sec samples are captured with nominal supplies (3.3V, which is  $V_1$ ) and a second set ( $V_2$ ) is captured with an additional AC signal (120mV<sub>rms</sub> at 50Hz) introduced onto the supplies. Then, the PSRR is expressed as  $\text{PSRR} = 20\log_{10}(V_2/V_1)$ .

### Signal-to-Noise Ratio (SNR)

SNR is calculated by inputting a 50Hz signal, and samples are acquired for 8sec. The amplitudes for each frequency up to the bandwidth given in [Table 1](#) as the ADC output bandwidth ( $-3\text{dB}$ ) are calculated. To determine the SNR, the signal at 50Hz is compared to the sum of the power from all the other frequencies, removing power from its harmonics. The value for SNR is expressed in decibels.

### Signal-to-Noise and Distortion Ratio (SINAD)

SINAD is calculated by inputting a 50Hz signal, and samples are acquired for 8sec. To determine the SINAD, the signal at 50Hz is compared to the sum of the power from all the other frequencies. The value for SINAD is expressed in decibels.

### Total Harmonic Distortion (THD)

THD is calculated by inputting a 50Hz signal, and samples are acquired for over 8sec. To determine the THD, the amplitudes of the 50Hz harmonics up to the bandwidth are root sum squared. The value for THD is expressed in decibels.

### Spurious-Free Dynamic Range (SFDR)

SFDR is calculated by inputting a 50Hz signal, and samples are acquired for over 8sec. To determine the SFDR, the amplitude of the largest signal that is not a harmonic of 50Hz is recorded. The value for SFDR is expressed in decibels.

### ADC Pass-Band Flatness

The bandwidth to which the ADC output is within 0.1dB of a 50Hz reference signal input.

### ADC Output Bandwidth

The ADC output bandwidth is the bandwidth within  $-3\text{dB}$ , resulting from the digital filtering in the sinc3 and enabled DSP features.

## THEORY OF OPERATION

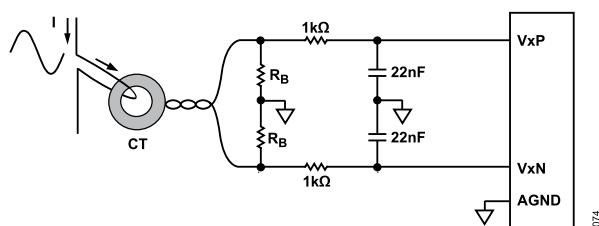

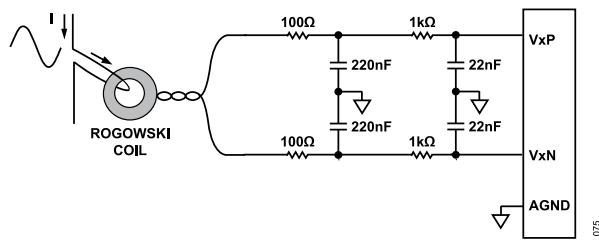

Accurate measurement, real-time monitoring, and comprehensive management of energy flow is required across the electrical power distribution networks. The ADEMA124 and ADEMA127 are 4- and 7-channel simultaneously sampling ADCs designed with features specifically for energy metering. All ADC channels have fully-differential inputs, identical dynamic range, programmable gain, and an independent 24-bit sigma delta ADC. Each ADC channel of the ADEMA124/ADEMA127 can directly support shunts, current transformers (CTs), and with the on-board digital integrators and HPFs, Rogowski sensors.

The ADEMA124/ADEMA127 ADCs are flexible and scalable components in energy metrology systems. The daisy-chain communication interface simplifies system architecture and allows a microcontroller to service a series of ADEMA124/ADEMA127 as though they are a single device. Synchronization of the multiple ADCs is simplified to a SPI write to the `SYNC_SNAP` register of each ADC followed by a simultaneous assertion of the `CS` pins. The integrated gain, phase, and offset compensation along with other DSP features reduce processing resources of the host microcontroller and make processed ADC waveform samples immediately available to the system.

The DSP decimate-by-2 enables higher bandwidth for reliable measurement of harmonics and, thus, superior power quality analysis for renewable energy resources, more efficient power delivery across the grid, and improved longevity of devices.

## GAIN AND OFFSET CORRECTION

Gain and offset correction is commonly required in metrology systems. The ADEMA124/ADEMA127 provide gain and offset calibration bit fields for each ADC channel, which reduces the required processing burden of the host microcontroller.

## QUICK START GUIDE

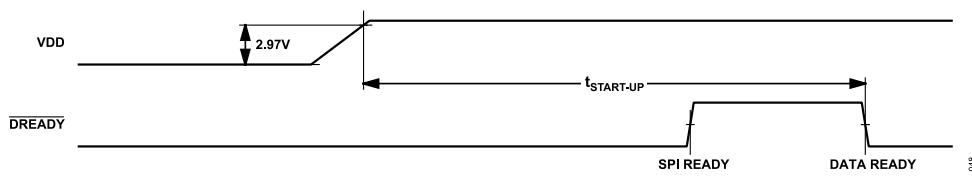

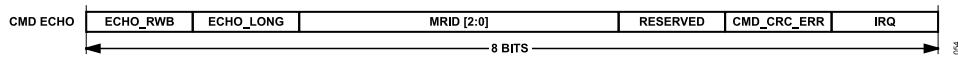

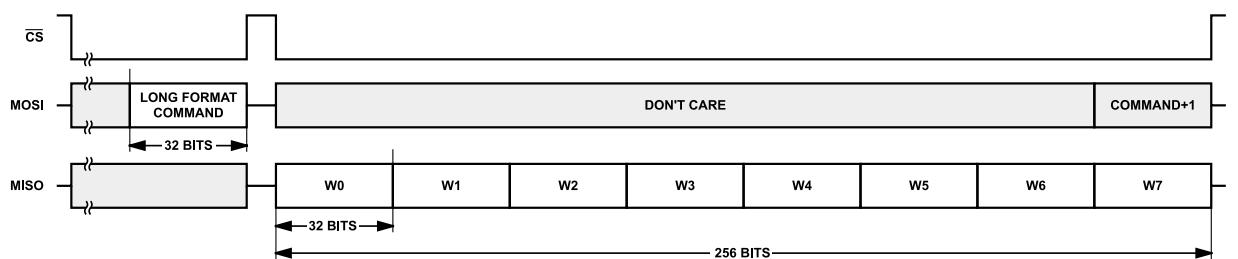

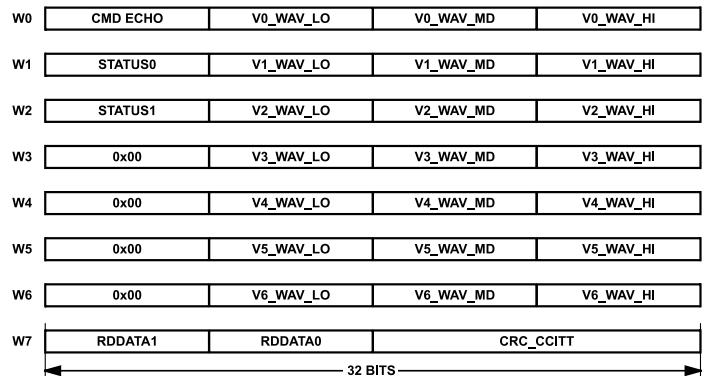

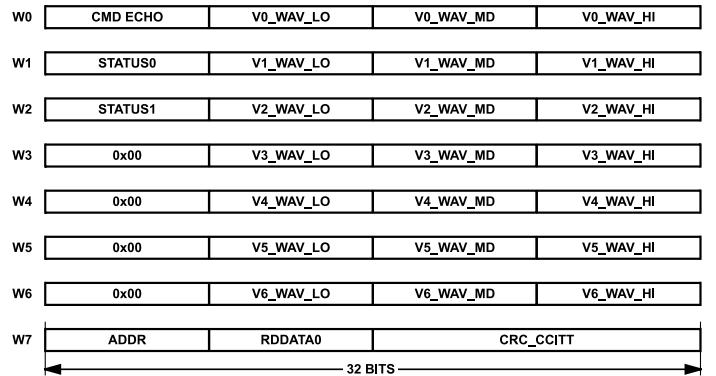

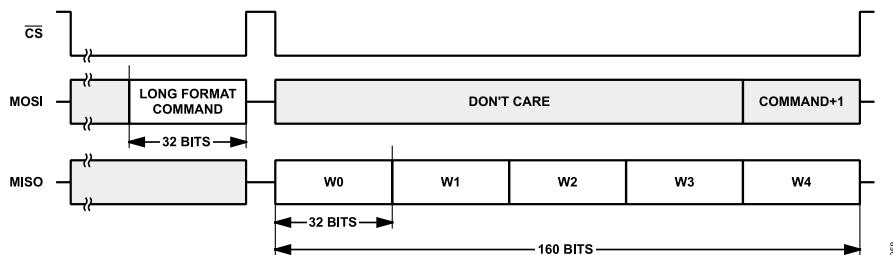

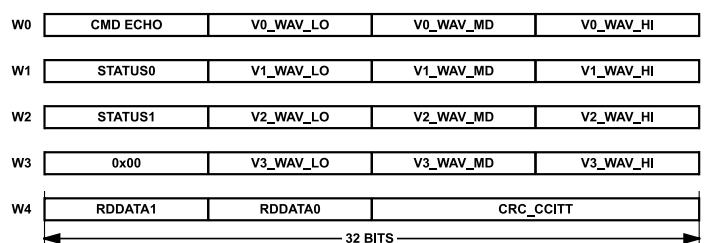

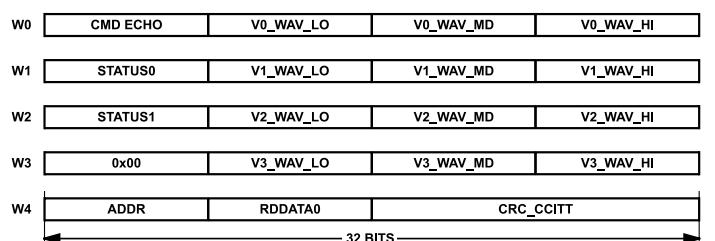

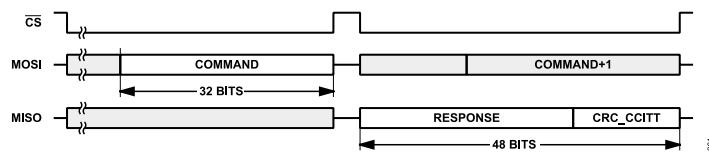

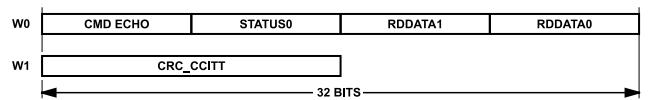

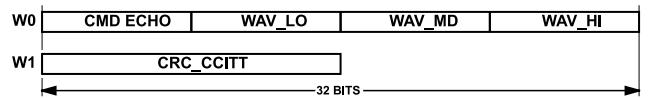

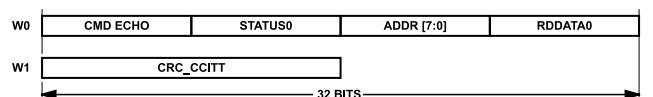

Upon providing the ADEMA124/ADEMA127 a 3.3V power supply and clock, the ADC immediately begins to produce samples per