---

# ACCELERATION SENSOR WSEN-ITDS USER MANUAL

---

2533020201601

VERSION 1.3

OCTOBER 10, 2019

## Revision history

| Manual version | Product version | Notes                                                                                                            | Date         |

|----------------|-----------------|------------------------------------------------------------------------------------------------------------------|--------------|

| 1.0            | 1.0             | <ul style="list-style-type: none"><li>Initial release of the manual</li></ul>                                    | April 2019   |

| 1.1            | 1.0             | <ul style="list-style-type: none"><li>Additional table in the register description chapter</li></ul>             | May 2019     |

| 1.2            | 1.0             | <ul style="list-style-type: none"><li>Device ID changed in the chapter 7.3.1</li></ul>                           | July 2019    |

| 1.3            | 1.0             | <ul style="list-style-type: none"><li>Chapter 2.3 Current consumption in power down mode changed to nA</li></ul> | October 2019 |

## Abbreviations

| Abbreviation     | Description                     |

|------------------|---------------------------------|

| BDU              | Block update data               |

| DRDY             | Data ready                      |

| DC               | Direct current                  |

| ESD              | Electrostatic discharge         |

| FIFO             | First-in first-out              |

| I <sup>2</sup> C | Inter integrated circuit        |

| LGA              | Land grid array                 |

| MEMS             | Micro-Electro Mechanical system |

| MSB              | Most significant bit            |

| ODR              | Output data rate                |

| PCB              | Printed circuit board           |

| LSB              | Least significant bit           |

# Contents

|                                                           |           |

|-----------------------------------------------------------|-----------|

| <b>1 Product description</b>                              | <b>7</b>  |

| 1.1 Introduction . . . . .                                | 7         |

| 1.2 Applications . . . . .                                | 7         |

| 1.3 Sensor features . . . . .                             | 7         |

| 1.4 Block diagram . . . . .                               | 8         |

| 1.5 Ordering information . . . . .                        | 8         |

| <b>2 Sensor and electrical specifications</b>             | <b>9</b>  |

| 2.1 Acceleration sensor specifications . . . . .          | 9         |

| 2.1.1 Acceleration sensitivity parameter . . . . .        | 10        |

| 2.2 Temperature sensor specifications . . . . .           | 10        |

| 2.3 Electrical specifications . . . . .                   | 11        |

| 2.4 Absolute maximum rating . . . . .                     | 12        |

| 2.5 General information . . . . .                         | 12        |

| <b>3 Pinning description</b>                              | <b>13</b> |

| <b>4 Application circuit</b>                              | <b>14</b> |

| <b>5 Digital interface</b>                                | <b>15</b> |

| 5.1 General characteristics . . . . .                     | 15        |

| 5.2 SDA and SCL logic levels . . . . .                    | 16        |

| 5.3 Communication phase . . . . .                         | 16        |

| 5.3.1 Idle state . . . . .                                | 16        |

| 5.3.2 START(S) and STOP(P) condition . . . . .            | 16        |

| 5.3.3 Data validity . . . . .                             | 17        |

| 5.3.4 Byte format . . . . .                               | 17        |

| 5.3.5 Acknowledge(ACK) and No-Acknowledge(NACK) . . . . . | 17        |

| 5.3.6 Slave address for the sensor . . . . .              | 18        |

| 5.3.7 Read/Write operation . . . . .                      | 19        |

| 5.4 I <sup>2</sup> C timing parameters . . . . .          | 20        |

| <b>6 Sensor specific parameters</b>                       | <b>21</b> |

| 6.1 Sensitivity . . . . .                                 | 21        |

| 6.2 0 g Level offset . . . . .                            | 21        |

| 6.3 Noise density . . . . .                               | 21        |

| <b>7 Quick start guide</b>                                | <b>22</b> |

| 7.1 Power supply . . . . .                                | 22        |

| 7.2 Boot status . . . . .                                 | 22        |

| 7.2.1 Soft reset . . . . .                                | 23        |

| 7.3 Flow chart . . . . .                                  | 23        |

| 7.3.1 Communication check . . . . .                       | 23        |

| 7.3.2 Sensor in operation . . . . .                       | 24        |

| <b>8 Operating modes</b>                                  | <b>26</b> |

| 8.1 High performance mode . . . . .                       | 26        |

| 8.2 Normal mode . . . . .                                 | 26        |

|           |                                                     |           |

|-----------|-----------------------------------------------------|-----------|

| 8.3       | Low power mode . . . . .                            | 26        |

| 8.4       | Single data conversion mode . . . . .               | 27        |

| <b>9</b>  | <b>Output data rate</b>                             | <b>30</b> |

| <b>10</b> | <b>Acceleration bandwidth and filtering chain</b>   | <b>31</b> |

| 10.1      | Low pass filter_1 . . . . .                         | 33        |

| 10.2      | Low pass filter_1 + Low pass filter_2 . . . . .     | 33        |

| 10.3      | Low pass filter_1 + High pass filter . . . . .      | 34        |

| 10.4      | User offset . . . . .                               | 34        |

| 10.5      | High pass filter path . . . . .                     | 34        |

|           | 10.5.1 Reference mode . . . . .                     | 35        |

| <b>11</b> | <b>First-In First-Out (FIFO) buffer</b>             | <b>36</b> |

| 11.1      | Bypass mode . . . . .                               | 37        |

| 11.2      | FIFO mode . . . . .                                 | 38        |

| 11.3      | Continuous mode . . . . .                           | 39        |

| 11.4      | Continuous to FIFO mode . . . . .                   | 40        |

| 11.5      | Bypass to continuous mode . . . . .                 | 41        |

| 11.6      | Understanding FIFO samples and interrupts . . . . . | 42        |

|           | 11.6.1 FIFO samples . . . . .                       | 42        |

|           | 11.6.2 FIFO interrupts . . . . .                    | 43        |

|           | 11.6.2.1 FIFO threshold (FIFO_FTH bit) . . . . .    | 43        |

|           | 11.6.2.2 FIFO full (Diff5 bit) . . . . .            | 43        |

|           | 11.6.2.3 FIFO overrun (FIFO_OVR) . . . . .          | 43        |

| 11.7      | How to read data from FIFO Buffer . . . . .         | 43        |

| <b>12</b> | <b>Interrupt pin and functionality</b>              | <b>45</b> |

| 12.1      | INT_0 and INT_1 . . . . .                           | 45        |

| 12.2      | Data ready - DRDY . . . . .                         | 46        |

| <b>13</b> | <b>Application specific sensor features</b>         | <b>47</b> |

| 13.1      | Single tap/Double tap . . . . .                     | 47        |

| 13.2      | Activity/Inactivity . . . . .                       | 47        |

| 13.3      | Stationary/Motion . . . . .                         | 47        |

| 13.4      | 6D Orientation . . . . .                            | 47        |

| 13.5      | Wake-Up . . . . .                                   | 47        |

| 13.6      | Free-Fall . . . . .                                 | 47        |

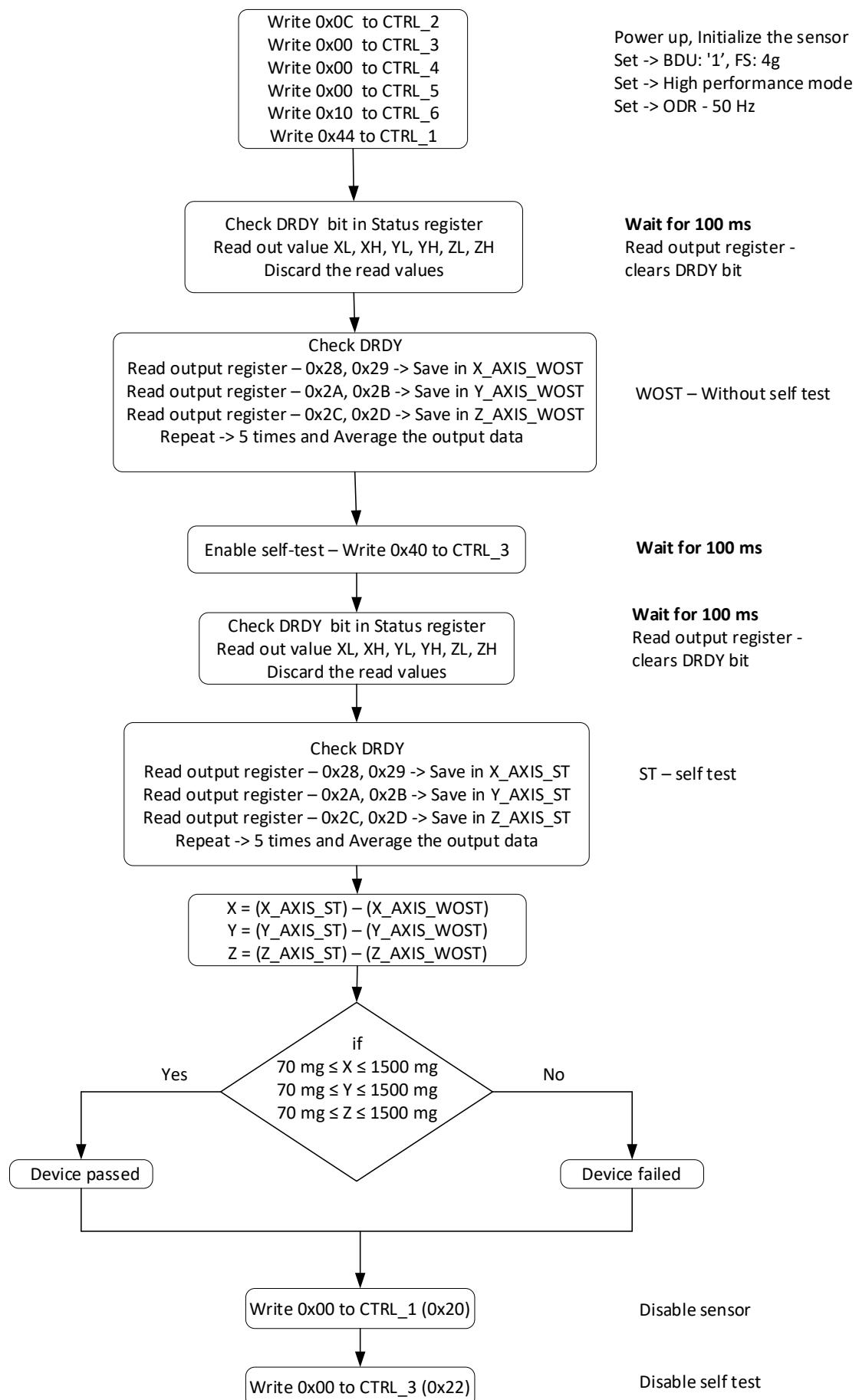

| <b>14</b> | <b>Self test</b>                                    | <b>48</b> |

| <b>15</b> | <b>Sensor output data</b>                           | <b>50</b> |

| 15.1      | Acceleration sensor . . . . .                       | 50        |

| 15.2      | Temperature sensor . . . . .                        | 51        |

| <b>16</b> | <b>Register mapping</b>                             | <b>53</b> |

| <b>17</b> | <b>Register description</b>                         | <b>54</b> |

| 17.1      | T_OUT_L (0x0D) . . . . .                            | 54        |

| 17.2      | T_OUT_H (0x0E) . . . . .                            | 54        |

|           |                                  |           |

|-----------|----------------------------------|-----------|

| 17.3      | Device_ID (0x0F)                 | 55        |

| 17.4      | CTRL_1 (0x20)                    | 55        |

| 17.5      | CTRL_2 (0x21)                    | 56        |

| 17.5.1    | Block data update (BDU)          | 57        |

| 17.6      | CTRL_3 (0x22)                    | 57        |

| 17.7      | CTRL_4 (0x23)                    | 58        |

| 17.8      | CTRL_5 (0x24)                    | 59        |

| 17.9      | CTRL_6 (0x25)                    | 60        |

| 17.10     | T_OUT (0x26)                     | 60        |

| 17.11     | STATUS (0x27)                    | 61        |

| 17.12     | X_OUT_L (0x28)                   | 62        |

| 17.13     | X_OUT_H (0x29)                   | 62        |

| 17.14     | Y_OUT_L (0x2A)                   | 63        |

| 17.15     | Y_OUT_H (0x2B)                   | 63        |

| 17.16     | Z_OUT_L (0x2C)                   | 64        |

| 17.17     | Z_OUT_H (0x2D)                   | 64        |

| 17.18     | FIFO_CTRL (0x2E)                 | 64        |

| 17.19     | FIFO_SAMPLES (0x2F)              | 65        |

| 17.20     | TAP_X_TH (0x30)                  | 65        |

| 17.21     | TAP_Y_TH (0x31)                  | 66        |

| 17.22     | TAP_Z_TH (0x32)                  | 67        |

| 17.23     | INT_DUR (0x33)                   | 67        |

| 17.24     | WAKE_UP_TH (0x34)                | 68        |

| 17.25     | WAKE_UP_DUR (0x35)               | 68        |

| 17.26     | FREE_FALL (0x36)                 | 69        |

| 17.27     | STATUS_DETECT (0x37)             | 70        |

| 17.28     | WAKE_UP_EVENT (0x38)             | 71        |

| 17.29     | TAP_EVENT (0x39)                 | 72        |

| 17.30     | 6D_EVENT (0x3A)                  | 73        |

| 17.31     | ALL_INT_EVENT (0x3B)             | 74        |

| 17.32     | X_OFS_USR (0x3C)                 | 75        |

| 17.33     | Y_OFS_USR (0x3D)                 | 75        |

| 17.34     | Z_OFS_USR (0x3E)                 | 75        |

| 17.35     | CTRL_7 (0x3F)                    | 76        |

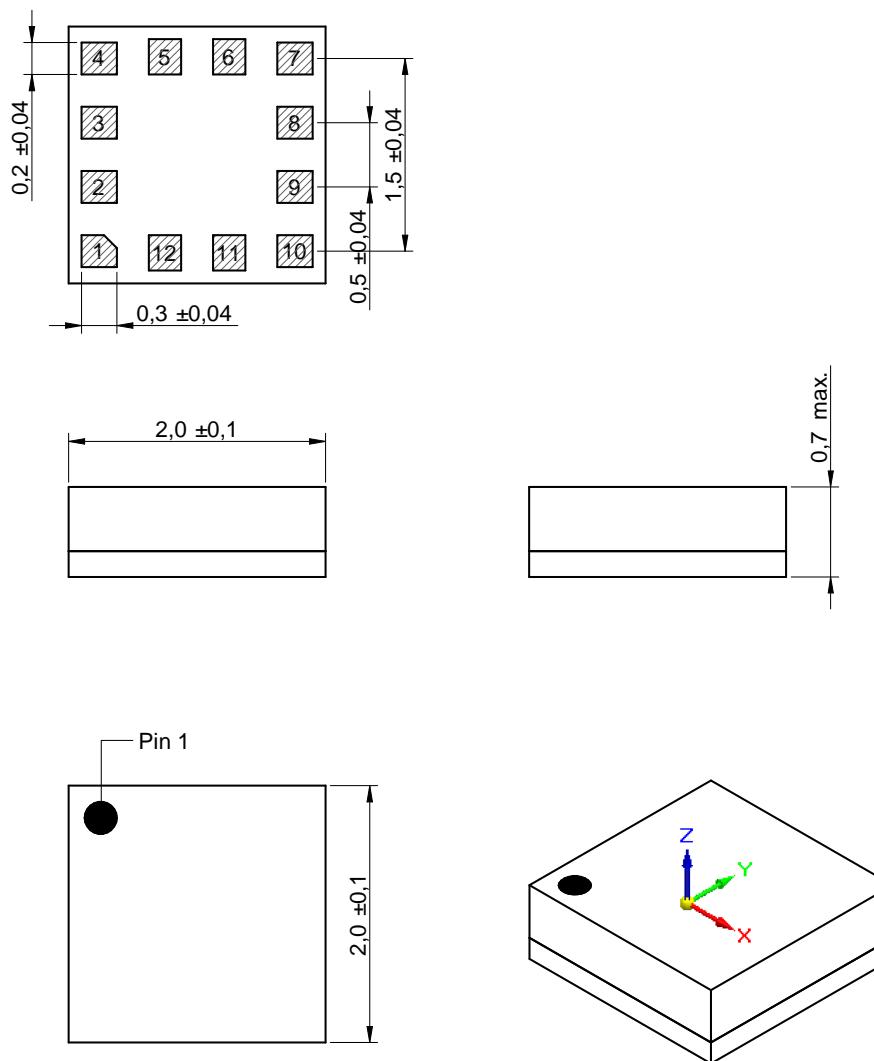

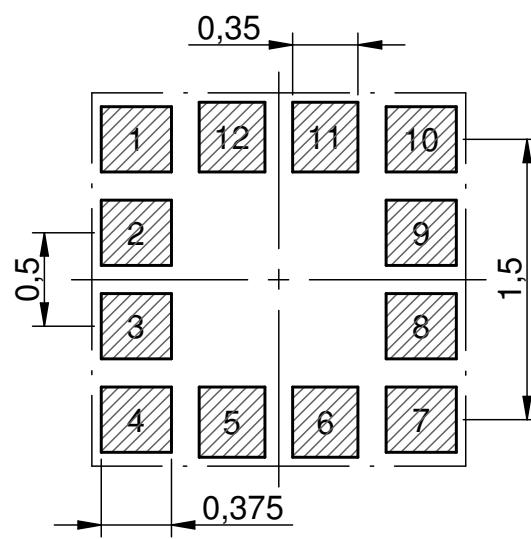

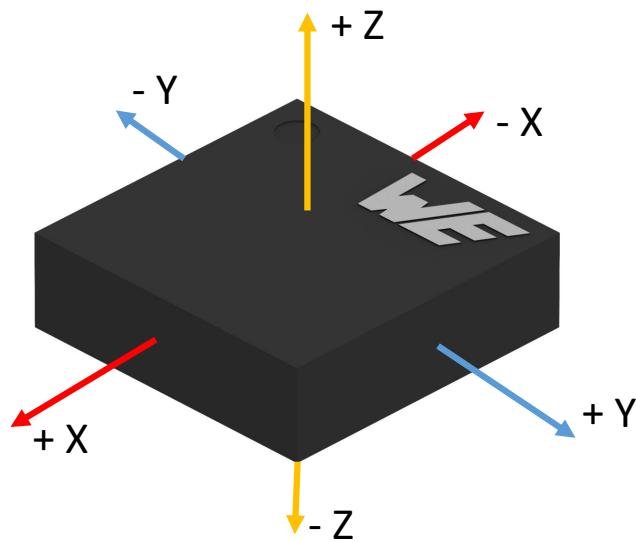

| <b>18</b> | <b>Physical dimensions</b>       | <b>77</b> |

| 18.1      | Module drawing                   | 77        |

| 18.2      | Footprint                        | 78        |

| 18.3      | Measurement axis of the sensor   | 78        |

| <b>19</b> | <b>Manufacturing information</b> | <b>79</b> |

| 19.1      | Moisture sensitivity level       | 79        |

| 19.2      | Soldering                        | 79        |

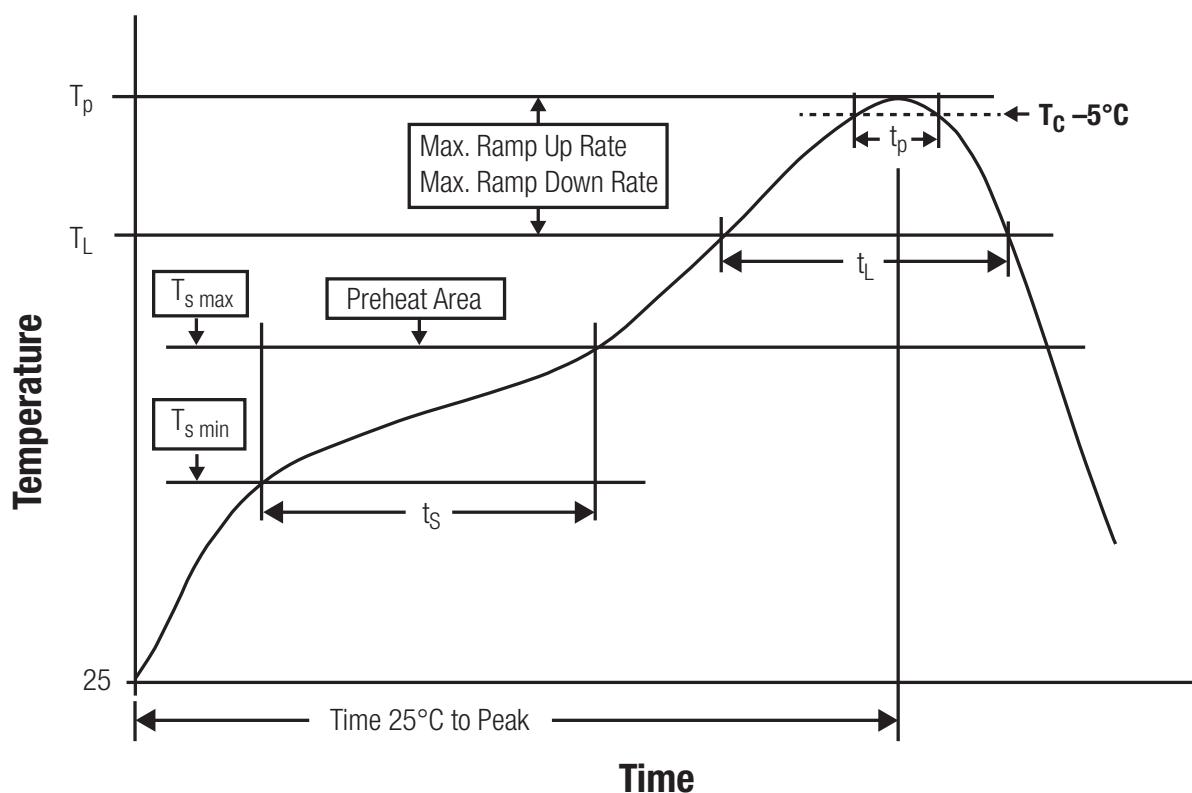

| 19.2.1    | Reflow soldering                 | 79        |

| 19.2.2    | Cleaning and washing             | 81        |

| 19.2.3    | Potting and coating              | 81        |

| 19.2.4    | Storage conditions               | 81        |

| 19.2.5    | Handling                         | 81        |

|                                                                                                              |           |

|--------------------------------------------------------------------------------------------------------------|-----------|

| <b>20 Important notes</b>                                                                                    | <b>83</b> |

| 20.1 General customer responsibility . . . . .                                                               | 83        |

| 20.2 Customer responsibility related to specific, in particular safety-relevant applications . . . . .       | 83        |

| 20.3 Best care and attention . . . . .                                                                       | 83        |

| 20.4 Customer support for product specifications . . . . .                                                   | 83        |

| 20.5 Product improvements . . . . .                                                                          | 84        |

| 20.6 Product life cycle . . . . .                                                                            | 84        |

| 20.7 Property rights . . . . .                                                                               | 84        |

| 20.8 General terms and conditions . . . . .                                                                  | 84        |

| <b>21 Legal notice</b>                                                                                       | <b>85</b> |

| 21.1 Exclusion of liability . . . . .                                                                        | 85        |

| 21.2 Suitability in customer applications . . . . .                                                          | 85        |

| 21.3 Usage restriction . . . . .                                                                             | 85        |

| <b>22 License terms for Würth Elektronik eiSos GmbH &amp; Co. KG sensor product software and source code</b> | <b>87</b> |

| 22.1 Limited license . . . . .                                                                               | 87        |

| 22.2 Usage and obligations . . . . .                                                                         | 87        |

| 22.3 Ownership . . . . .                                                                                     | 88        |

| 22.4 Disclaimer of warranty . . . . .                                                                        | 88        |

| 22.5 Limitation of liability . . . . .                                                                       | 88        |

| 22.6 Applicable law and jurisdiction . . . . .                                                               | 88        |

| 22.7 Severability clause . . . . .                                                                           | 89        |

| 22.8 Miscellaneous . . . . .                                                                                 | 89        |

# 1 Product description

## 1.1 Introduction

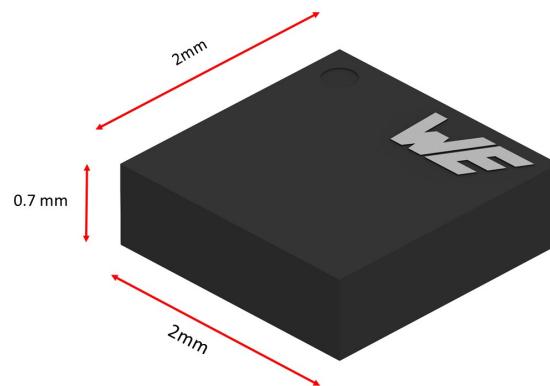

The acceleration sensor is a 14-bit digital ultra-low-power and high-performance three-axis linear accelerometer with digital output interface. It measures user selectable acceleration range of  $\pm 2g$ ,  $\pm 4g$ ,  $\pm 8g$ ,  $\pm 16g$  with an output data rate up to 1600 Hz. It consists of a 32 level FIFO buffer to store the output data. It is embedded with a temperature sensor for ambient temperature measurement. The sensor is capable of detecting events like free fall, tap recognition, wake up, stationary/motion, activity/inactivity and 6D orientation. The dimension of the sensor is 2.0 mm×2.0 mm×0.7 mm. It is available in land grid array package (LGA).

## 1.2 Applications

- Industrial IoT and connected devices

- Industrial tools and factory equipment

- Vibration monitoring

- Tilt/inclination measurements

- Impact recognition and logging

## 1.3 Sensor features

|                                    |                                                                                                                       |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| • Selectable full scale:           | $\pm 2g$ , $\pm 4g$ , $\pm 8g$ , $\pm 16g$                                                                            |

| • Output data rate:                | Up to 1600 Hz                                                                                                         |

| • Bandwidth:                       | 400 Hz                                                                                                                |

| • Operating modes:                 | High performance, normal, low power                                                                                   |

| • Noise density:                   | $90 \mu g / \sqrt{Hz}$<br>High performance mode: $155 \mu A$<br>Normal mode: $58 \mu A$<br>Low power mode: $16 \mu A$ |

| • Current consumption:             |                                                                                                                       |

| • FIFO:                            | 32-Level                                                                                                              |

| • Communication interface:         | I <sup>2</sup> C, two independent interrupt pins                                                                      |

| • Motion detection functionality:  | Free-fall, wake-up, tap, activity, motion, orientation:<br>4D/6D/portrait/landscape                                   |

| • Embedded temperature sensor      |                                                                                                                       |

| • Single data conversion on demand |                                                                                                                       |

| • Self-test functionality          |                                                                                                                       |

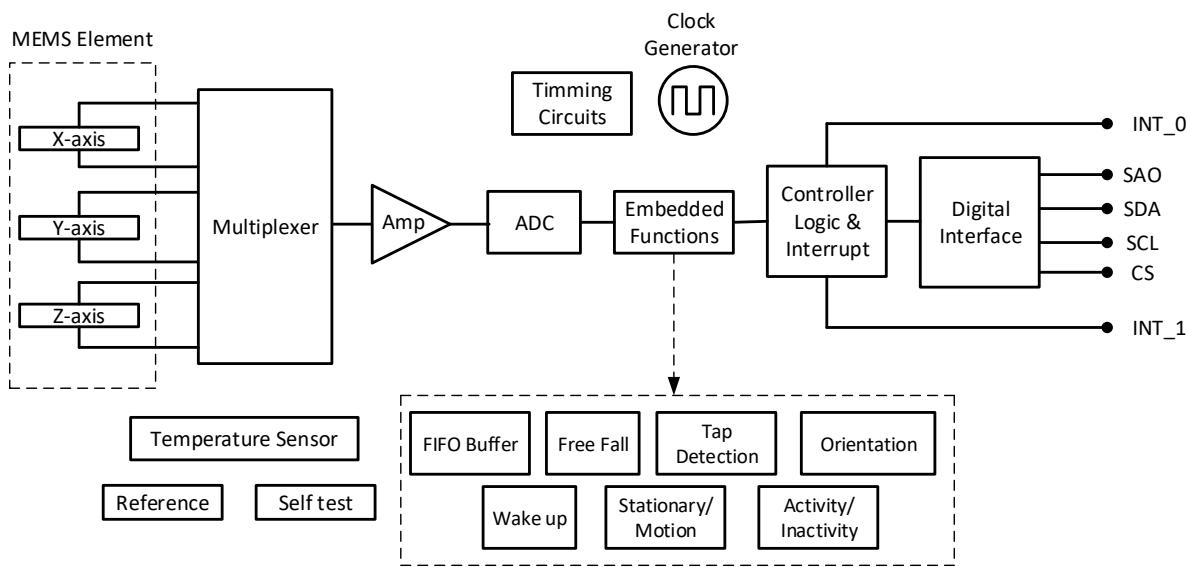

## 1.4 Block diagram

Figure 1: Block diagram

The sensor is a MEMS based capacitive acceleration sensor with an integrated ASIC. The MEMS element is capable of measuring both dynamic acceleration due to motion or vibration and also static acceleration due to gravity. The sensor measures the acceleration or vibration through MEMS capacitive sensing principle. The MEMS element consists of a fixed structure and movable structure. The movable structure is free to move in the direction of acceleration applied i.e. X, Y and Z direction. The force induced on the MEMS element produces change in the capacitance value that is proportional to the force exerted on it. Without any force on the sensor the capacitors will have a nominal capacitance value in the range of picofarad (pF). When an acceleration is applied, the change in the capacitance value is induced in the range of femtofarad (fF). The induced analog signal is converted to digital form using an analog to digital converter followed by filters and controller logic blocks. The final acceleration data from the output register can be accessed through an I<sup>2</sup>C digital communication interface using host processor.

## 1.5 Ordering information

| WE order code | Temperature Range | Description           |

|---------------|-------------------|-----------------------|

| 2533020201601 | -40 °C to +85 °C  | Tape & reel packaging |

Table 1: Ordering information

## 2 Sensor and electrical specifications

T=25 °C, supply voltage VDD = 3.3V, unless otherwise stated.

### 2.1 Acceleration sensor specifications

| Parameters                          | Symbol               | Test conditions                                               | Min. <sup>1</sup> | Typ.         | Max. <sup>1</sup> | Unit    |

|-------------------------------------|----------------------|---------------------------------------------------------------|-------------------|--------------|-------------------|---------|

| Axis                                |                      |                                                               |                   |              | 3                 |         |

| Measurement range                   | a <sub>RANGE</sub>   | User selectable                                               |                   | ±2,±4,±8,±16 |                   | g       |

| Output data rate                    | ODR                  | User selectable                                               | 1,6               |              | 1600              | Hz      |

| Bandwidth                           | f <sub>BW</sub>      | User selectable                                               | 0,08              |              | 400               | Hz      |

| Resolution                          | RES <sub>a</sub>     | High performance / normal mode                                |                   |              | 14                | bits    |

|                                     | RES <sub>a</sub>     | Low power mode                                                |                   |              | 12                | bits    |

| Sensitivity accuracy                | SEN <sub>a_ACC</sub> |                                                               | -3                |              | +3                | %       |

| Sensitivity change over temperature | SEN <sub>a_TC</sub>  |                                                               |                   | 0.01         |                   | %/°C    |

| Noise density <sup>2</sup>          | n <sub>D</sub>       | High performance mode, ±2g, ODR 200 Hz, Low noise bit enabled |                   | 90           | 160               | µg /√Hz |

| 0g Offset accuracy <sup>3</sup>     | a <sub>OFF</sub>     |                                                               | -30               | ±20          | +30               | mg      |

| 0g Offset change over temperature   | a <sub>TCO</sub>     |                                                               | -1                | ±0.2         | + 1               | mg /°C  |

| Resonant frequency                  | f <sub>res_X</sub>   | X                                                             |                   | 3.4          |                   | kHz     |

|                                     | f <sub>res_Y</sub>   | Y                                                             |                   | 3.4          |                   | kHz     |

|                                     | f <sub>res_Z</sub>   | Z                                                             |                   | 2.8          |                   | kHz     |

Table 2: Acceleration sensor specification

g: unit of acceleration, 1g = 9.81 m/s<sup>2</sup>

<sup>1</sup> Minimum and maximum values are based on characterization at 3σ.

<sup>2</sup> Noise density is same for all ODRs. Low noise setting enabled.

<sup>3</sup> Values after calibration test and trimming.

### 2.1.1 Acceleration sensitivity parameter

| Parameters                             | Symbol           | Test conditions                | Min. <sup>1</sup> | Typ.  | Max. <sup>1</sup> | Unit      |

|----------------------------------------|------------------|--------------------------------|-------------------|-------|-------------------|-----------|

| Sensitivity ( $\pm 2g$ ) <sup>2</sup>  | SEN <sub>a</sub> | High performance / Normal mode |                   | 0.244 |                   | mg /digit |

| Sensitivity ( $\pm 4g$ ) <sup>2</sup>  | SEN <sub>a</sub> | High performance / Normal mode |                   | 0.488 |                   | mg /digit |

| Sensitivity ( $\pm 8g$ ) <sup>2</sup>  | SEN <sub>a</sub> | High performance / Normal mode |                   | 0.976 |                   | mg /digit |

| Sensitivity ( $\pm 16g$ ) <sup>2</sup> | SEN <sub>a</sub> | High performance / Normal mode |                   | 1.952 |                   | mg /digit |

| Sensitivity ( $\pm 2g$ ) <sup>2</sup>  | SEN <sub>a</sub> | Low power mode                 |                   | 0.976 |                   | mg /digit |

| Sensitivity ( $\pm 4g$ ) <sup>2</sup>  | SEN <sub>a</sub> | Low power mode                 |                   | 1.952 |                   | mg /digit |

| Sensitivity ( $\pm 8g$ ) <sup>2</sup>  | SEN <sub>a</sub> | Low power mode                 |                   | 3.904 |                   | mg /digit |

| Sensitivity ( $\pm 16g$ ) <sup>2</sup> | SEN <sub>a</sub> | Low power mode                 |                   | 7.808 |                   | mg /digit |

Table 3: Acceleration sensitivity parameter

<sup>1</sup> Minimum and maximum values are based on characterization at  $3\sigma$ .

<sup>2</sup> Sensitivity values after factory calibration test and trimming.

### 2.2 Temperature sensor specifications

| Parameters        | Symbol                 | Test conditions   | Min. <sup>1</sup> | Typ.   | Max. <sup>1</sup> | Unit   |

|-------------------|------------------------|-------------------|-------------------|--------|-------------------|--------|

| Measurement range | T <sub>RANGE</sub>     |                   | -40               |        | +85               | °C     |

| Sensitivity       | SEN <sub>T_8bit</sub>  | 8 bit resolution  |                   | 1      |                   | °C/LSB |

|                   | SEN <sub>T_12bit</sub> | 12 bit resolution |                   | 0.0625 |                   | °C/LSB |

| Offset            | T <sub>OFF</sub>       |                   | -15               |        | +15               | °C     |

Table 4: Temperature sensor specification

<sup>1</sup> Minimum and maximum values are based on characterization at  $3\sigma$ .

## 2.3 Electrical specifications

| Parameters                                   | Symbol       | Test conditions              | Min. <sup>1</sup>  | Typ. | Max. <sup>1</sup>  | Unit    |

|----------------------------------------------|--------------|------------------------------|--------------------|------|--------------------|---------|

| Operating supply voltage                     | $V_{DD}$     |                              | 1.7                | 3.3  | 3.6                | V       |

| Operating supply voltage for I/O pins        | $V_{DD\_IO}$ |                              | 1.7                |      | $V_{DD} + 0.1$     | V       |

| Current consumption in high performance mode | $I_{DD\_HP}$ | ODR 200 Hz                   |                    | 155  |                    | $\mu A$ |

| Current consumption in normal mode           | $I_{DD\_NM}$ | ODR 200 Hz                   |                    | 58   |                    | $\mu A$ |

| Current consumption in low power mode        | $I_{DD\_LP}$ | ODR 200 Hz                   |                    | 16   |                    | $\mu A$ |

| Current consumption in power down mode       | $I_{DD\_PD}$ |                              |                    |      | 100                | nA      |

| Digital input voltage - high-level           | $V_{IH}$     |                              | $0.8 * V_{DD\_IO}$ |      |                    | V       |

| Digital input voltage - low-level            | $V_{IL}$     |                              |                    |      | $0.2 * V_{DD\_IO}$ | V       |

| Digital output voltage - high-level          | $V_{OH}$     | $I_{OH} = 4$ mA <sup>2</sup> | $V_{DD\_IO} - 0.2$ |      |                    | V       |

| Digital output voltage - low-level           | $V_{OL}$     | $I_{OL} = 4$ mA <sup>2</sup> |                    |      | 0.2                | V       |

Table 5: Electrical specification

<sup>1</sup> Minimum and maximum values are based on characterization at  $3\sigma$ .

<sup>2</sup> 4 mA is the maximum driving capability i.e. the maximum DC current that can be sourced/-sunk by digital pin in order to guarantee correct digital output voltage levels  $V_{OH}$  and  $V_{OL}$ .

## 2.4 Absolute maximum rating

| Parameter                                       | Symbol            | Test conditions | Min. <sup>1</sup> | Max. <sup>1</sup>  | Unit |

|-------------------------------------------------|-------------------|-----------------|-------------------|--------------------|------|

| Input voltage $V_{DD}$ pin                      | $V_{DD\_Max}$     |                 | -0.3              | 4.8                | V    |

| Input voltage $V_{DD\_IO}$ pin                  | $V_{DD\_IO\_Max}$ |                 | -0.3              | 4.8                | V    |

| Input voltage $SDA$ , $SCL$ , $CS$ & $SAO$ pins | $V_{IN\_Max}$     |                 | -0.3              | $V_{DD\_IO} + 0.3$ | V    |

| Acceleration                                    | $a_{MAX}$         | for 0.5 ms      |                   | 3000               | $g$  |

Table 6: Absolute maximum rating

<sup>1</sup> Minimum and maximum values are based on characterization at  $3\sigma$ .

Supply voltage on any pin should never exceed 4.8 V

## 2.5 General information

| Parameters                              | Values            |

|-----------------------------------------|-------------------|

| Operating temperature                   | -40 °C to +85 °C  |

| Storage temperature                     | -40 °C to +125 °C |

| Communication interface                 | I <sup>2</sup> C  |

| Moisture sensitivity level (MSL)        | 3                 |

| Electrostatic discharge protection(HBM) | 2 kV              |

Table 7: General information

The device is susceptible to damage by electrostatic discharge (ESD). Always use proper ESD precautions when handling. Improper handling of the device can cause performance degradation or permanent damage to the part

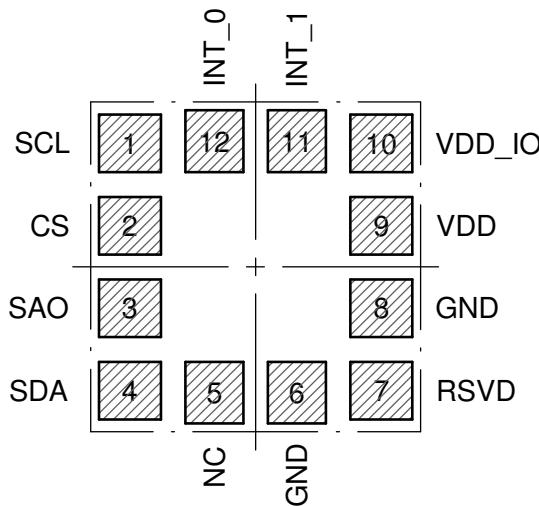

### 3 Pinning description

Figure 2: Pinout (top view)

| No | Function      | Description                                   | Input/Output |

|----|---------------|-----------------------------------------------|--------------|

| 1  | <i>SCL</i>    | $\text{I}^2\text{C}$ serial clock             | Input        |

| 2  | <i>CS</i>     | $\text{I}^2\text{C}$ enable/disable           | Input        |

| 3  | <i>SAO</i>    | $\text{I}^2\text{C}$ device address selection | Input        |

| 4  | <i>SDA</i>    | $\text{I}^2\text{C}$ serial data              | Input/Output |

| 5  | <i>NC</i>     | No connection                                 | -            |

| 6  | <i>GND</i>    | Negative supply voltage                       | Supply       |

| 7  | <i>RSVD</i>   | Reserved, connect to GND                      | Input        |

| 8  | <i>GND</i>    | Negative supply voltage                       | Supply       |

| 9  | <i>VDD</i>    | Positive supply voltage                       | Supply       |

| 10 | <i>VDD_IO</i> | Positive supply voltage for I/O pins          | Supply       |

| 11 | <i>INT_1</i>  | Interrupt pin 1                               | Input/Output |

| 12 | <i>INT_0</i>  | Interrupt pin 0                               | Output       |

Table 8: Pin description

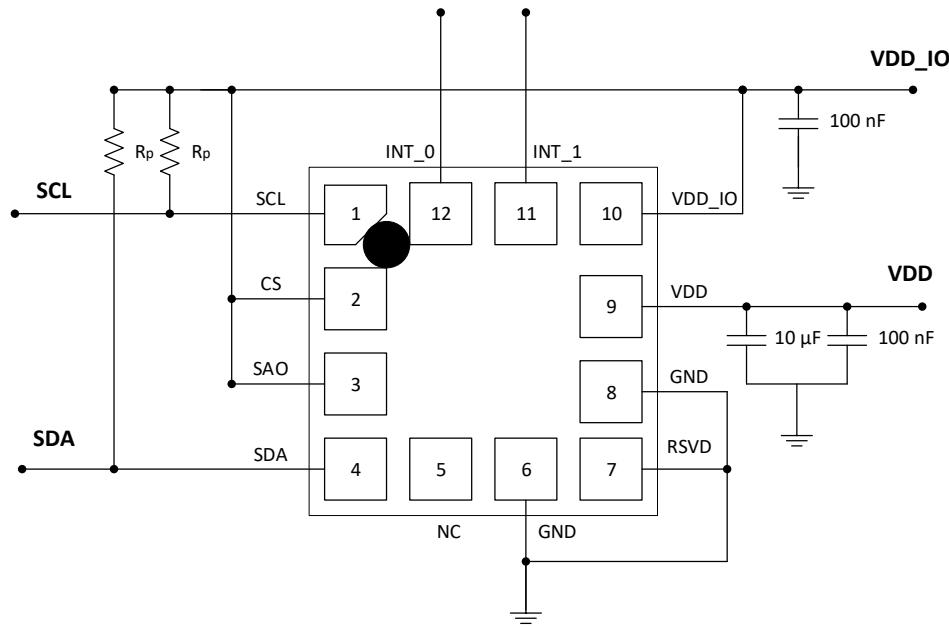

## 4 Application circuit

Figure 3: Electrical connection (top view)

A positive supply voltage is applied to the sensor through *VDD* pin and I/O supply voltage for digital interface through *VDD\_IO*. The decoupling capacitor of 100 nF and 10μF in parallel is highly recommended and should be placed as close as possible to the *VDD* pin. The communication to the sensor is still possible, even if the supply voltage to the *VDD* pin is removed but maintaining the *VDD\_IO*. In this case, measurement process of the sensor is not active.

The *CS* pin should be connected to *VDD\_IO* in order to enable the I<sup>2</sup>C communication interface. It is possible to have two I<sup>2</sup>C slave addresses by connecting *SAO* pin either to *VDD\_IO* or *GND*. In the above connection the *SAO* pin is connected to *VDD\_IO*. *R<sub>p</sub>* are the recommended pull up resistors for I<sup>2</sup>C communication interface which should be connected parallel between I/O supply voltage *VDD\_IO* and *SCL* and *SDA* pins.

The *SAO* and *CS* pins are internally pulled up. The internal pull up resistor values of *SAO* and *CS* pins for different supply voltage of the I/O pins are given below in table 9.

| <i>VDD_IO</i> | Resistor value of <i>SAO</i> and <i>CS</i> (Typ.) |

|---------------|---------------------------------------------------|

| 1.7V          | 54.4 KΩ                                           |

| 1.8V          | 49.2 KΩ                                           |

| 2.5V          | 30.4 KΩ                                           |

| 3.6V          | 20.4 KΩ                                           |

Table 9: Internal pull up values (typ) for *SAO* and *CS* pins

## 5 Digital interface

The acceleration sensor supports standard I<sup>2</sup>C (Inter-IC) bus protocol. Further information of the I<sup>2</sup>C interface can be found at <https://www.nxp.com/docs/en/user-guide/UM10204.pdf>. I<sup>2</sup>C is a serial 8-bit protocol with two-wire interface which supports communication between different ICs. For example, between the microcontroller and other peripheral devices.

### 5.1 General characteristics

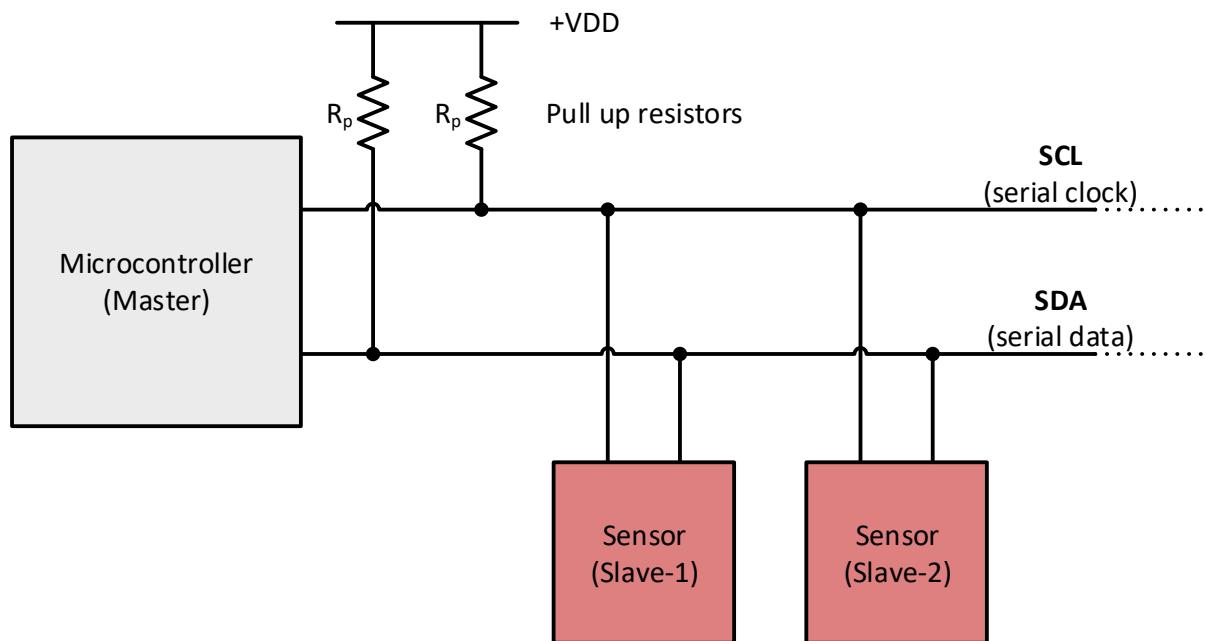

A serial data line (*SDA*) and a serial clock line (*SCL*) are required for the communication between the devices connected via I<sup>2</sup>C bus. Both *SDA* and *SCL* lines are bidirectional. The output stages of devices connected to the bus must have an open-drain or open-collector. Hence, the *SDA* and *SCL* lines are connected to a positive supply voltage via pull-up resistors. In I<sup>2</sup>C protocol, the communication is realized through master-slave principle. The master device generates the clock pulse, a start command and a stop command for the data transfer. Each connected device on the bus is addressable via a unique address. Master and slave can act as a transmitter or a receiver depending upon whether the data needs to be transmitted or received.

The sensor behaves like a slave device on the I<sup>2</sup>C bus

Figure 4: Master-slave concept

## 5.2 *SDA* and *SCL* logic levels

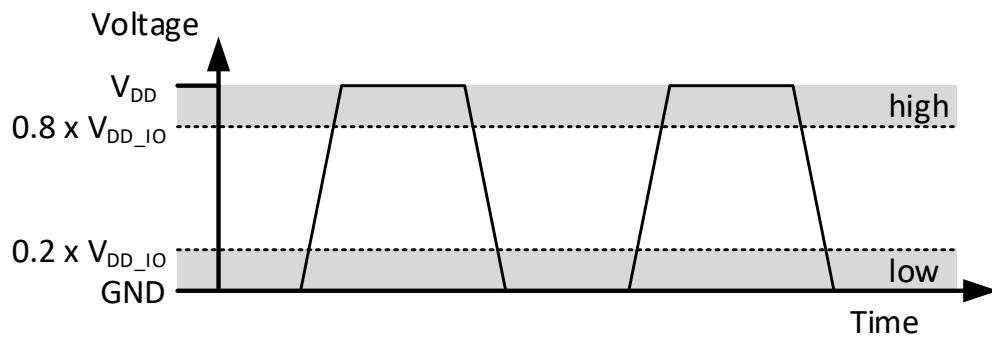

The positive supply voltage to which *SDA* and *SCL* lines are pulled up (through pull-up resistors), in turn determines the high level input for the slave devices. The sensor has separate supply voltage *VDD<sub>IO</sub>* for the *SDA* and *SCL* lines. The logic high '1' and logic low '0' levels for the *SDA* and *SCL* lines then depend on the *VDD<sub>IO</sub>*. Input reference levels for the acceleration sensor are set as  $0.8 * VDD_{IO}$  (for logic high) and  $0.2 * VDD_{IO}$  (for logic low). See in figure 5.

Figure 5: *SDA* and *SCL* logic levels

## 5.3 Communication phase

### 5.3.1 Idle state

During the idle state, the bus is free and both *SDA* and *SCL* lines are in logic high '1' state.

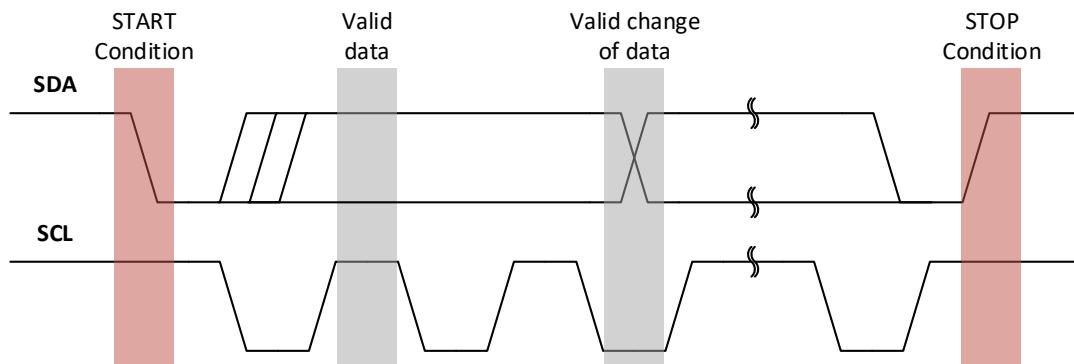

### 5.3.2 START(S) and STOP(P) condition

Data transfer on the bus starts with a START command, which is generated by the master. A start condition is defined as a high-to-low transition on the *SDA* line while the *SCL* line is held high. The bus is considered busy after the start condition.

Data transfer on the bus is terminated with a STOP command, which is also generated by the master. A low-to-high transition on the *SDA* line, while the *SCL* line being high is defined as a STOP condition. After the stop condition, the bus is again considered free and is in idle state. Figure 6 shows the I<sup>2</sup>C bus START and STOP conditions.

Master can also send a REPEATED START (SR) command instead of STOP command. REPEATED START condition is same as the START condition.

### 5.3.3 Data validity

After the start condition, one data bit is transmitted with each clock pulse. The transmitted data is only valid when the *SDA* line data is stable (high or low) during the high period of the clock pulse. High or low state of the data line can only change when the clock pulse is in low state.

Figure 6: Data validity, START and STOP condition

### 5.3.4 Byte format

Data transmission on the *SDA* line is always done in bytes, with each byte being 8-bits long. Data is transmitted with the most significant bit (MSB) followed by other bits.

If the slave cannot receive or transmit another complete byte of data, it can force the master into a wait state by holding *SCL* LOW. Data transfer continues when the slave is ready which is indicated by releasing the *SCL* pin.

### 5.3.5 Acknowledge(ACK) and No-Acknowledge(NAACK)

Each byte transmitted on the data line must follow an Acknowledge bit. The receiver (master or slave) generates an Acknowledge signal to indicate that the data byte was received successfully and ready to receive next data byte.

After one byte is transmitted, the master generates an additional Acknowledge clock pulse to continue the data transfer. The transmitter releases the *SDA* line during this clock pulse so that the receiver can pull the *SDA* line to low state in such a way that the *SDA* line remains stable low during the entire high period of the clock pulse. It is considered as an Acknowledge signal.

If the receiver does not want to receive any further byte, it will not pull down the *SDA* line and it remains in stable high state during the entire clock pulse. It is considered as a No-Acknowledge signal and the master can generate either a stop condition to terminate the data transfer or a repeated start condition to initiate a new data transfer.

### 5.3.6 Slave address for the sensor

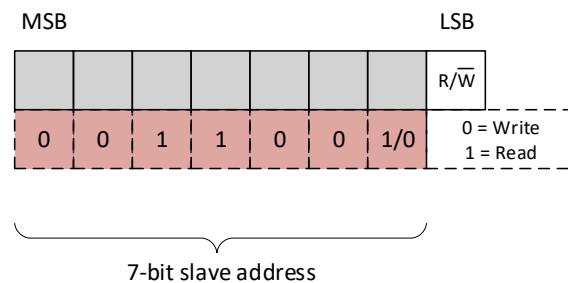

The slave address is transmitted after sending the start condition. Each device on the I<sup>2</sup>C bus has a unique address. Master selects the slave by sending corresponding slave address after the start condition. A slave address is a 7 bits long followed by a Read/Write bit.

Figure 7: Slave address format

The 7-bit slave address of the acceleration sensor is 001100xb. LSB of the 7-bit slave address can be modified with the SAO pin. If SAO is connected to positive supply voltage i.e. LSB is '1', making 7-bit slave address 0011001b (0x19). If SAO is connected to ground i.e. LSB is '0', making 7-bit address 0011000b (0x18).

The R/W bit determines the data direction. A '0' indicates a write operation (transmission from master to slave) and a '1' indicates a read operation (data request from slave).

Figure 8: Complete data transfer

7-bit slave address of the acceleration sensor is 001100xb. LSB of the 7-bit slave address depends on the SAO pin connection

| Slave address[6:1] | Slave address[0] | 7-bit slave address | R/W | Slave address + R/W |

|--------------------|------------------|---------------------|-----|---------------------|

| 001100             | SAO = 0          | 0011000 (0x18)      | 0   | 00110000 (0x30)     |

| 001100             |                  |                     | 1   | 00110001 (0x31)     |

| 001100             | SAO = 1          | 0011001 (0x19)      | 0   | 00110010 (0x32)     |

| 001100             |                  |                     | 1   | 00110011 (0x33)     |

Table 10: Slave address and Read/Write commands

### 5.3.7 Read/Write operation

#### a) I<sup>2</sup>C write: Master writing data to slave

|   |                       |     |                  |     |      |     |   |

|---|-----------------------|-----|------------------|-----|------|-----|---|

| S | Slave address + Write | ACK | Register address | ACK | Data | ACK | P |

|---|-----------------------|-----|------------------|-----|------|-----|---|

#### b) I<sup>2</sup>C read: Master reading multiple data bytes from slave

|   |                       |     |                  |     |    |                      |     |      |     |      |      |   |

|---|-----------------------|-----|------------------|-----|----|----------------------|-----|------|-----|------|------|---|

| S | Slave address + Write | ACK | Register address | ACK | SR | Slave address + Read | ACK | Data | ACK | Data | NACK | P |

|---|-----------------------|-----|------------------|-----|----|----------------------|-----|------|-----|------|------|---|

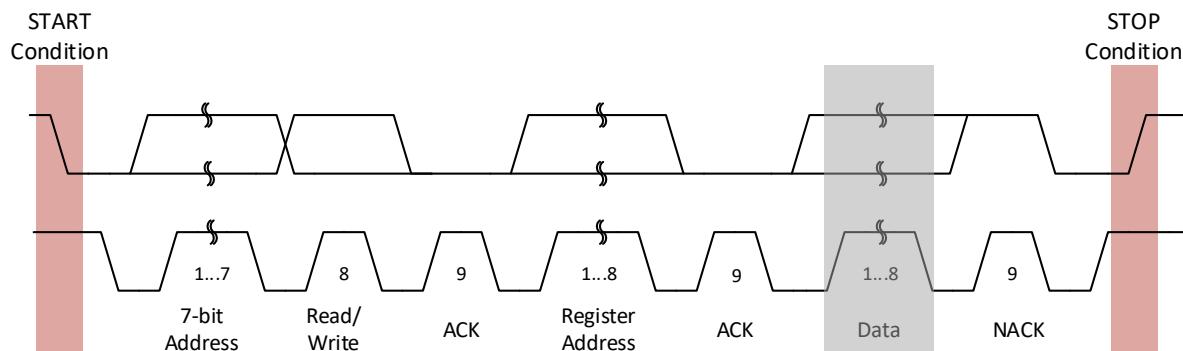

Figure 9: Write and read operations of the sensor

Once the slave-address and data direction bit is transmitted, the slave acknowledges the master. The next byte is transmitted by the master, which must be a register-address of the

sensor. It indicates the address of the register where data needs to be written to or read from.

After receiving the register address, the slave sends an Acknowledgement (ACK). If the master is still writing to the slave (R/W bit = 0), it will transmit the data to slave in the same direction. If the master wants to read from the addressed register (R/W bit =1), a repeated start (SR) condition must be transmitted to the slave. Master acknowledges the slave after receiving each data byte. If the master no longer wants to receive further data from the slave, it would send No-Acknowledge (NACK). Afterwards, master can send a STOP condition to terminate the data transfer. Figure 9 shows the writing and reading procedures between the master and the slave device (sensor).

## 5.4 I<sup>2</sup>C timing parameters

| Parameter                                      | Symbol                | Standard mode |      | Fast mode |     | Unit |

|------------------------------------------------|-----------------------|---------------|------|-----------|-----|------|

|                                                |                       | Min           | Max  | Min       | Max |      |

| SCL clock frequency                            | f <sub>SCL</sub>      | 0             | 100  | 0         | 400 | kHz  |

| LOW period for SCL clock                       | t <sub>LOW_SCL</sub>  | 4.7           |      | 1.3       |     | μs   |

| HIGH period for SCL clock                      | t <sub>HIGH_SCL</sub> | 4.0           |      | 0.6       |     | μs   |

| Hold time for START condition                  | t <sub>HD_S</sub>     | 4             |      | 0.6       |     | μs   |

| Setup time for (repeated) START condition      | f <sub>SCL</sub>      | 4.7           |      | 0.6       | 400 | μs   |

| SDA setup time                                 | t <sub>SU_SDA</sub>   | 250           |      | 100       |     | ns   |

| SDA data hold time                             | t <sub>HD_SDA</sub>   | 0             | 3.45 | 0         | 0.9 | μs   |

| Setup time for STOP condition                  | t <sub>SU_P</sub>     | 4             |      | 0.6       |     | μs   |

| Bus free time between STOP and START condition | t <sub>BUF</sub>      | 4.7           |      | 1.3       |     | μs   |

Table 11: I<sup>2</sup>C timing parameters

## 6 Sensor specific parameters

### 6.1 Sensitivity

Sensitivity is defined as the ratio of change in input acceleration to the change in the output signal. The unit of sensitivity is typically expressed in mg/digit. It can be measured by pointing the sensor horizontally downwards, an acceleration of 1g is measured due to earth's gravity (9.807 m/s<sup>2</sup>). Similarly by pointing sensor horizontally upwards (rotation of 180 degree), again an acceleration of 1g is measured due to earth's gravity (9.807 m/s<sup>2</sup>). By subtracting the larger measured output value from the smaller measured output value and dividing by two gives the actual sensitivity of the acceleration sensor.

The sensitivity value will drift over time and temperature.

$$\text{Sensitivity} = \frac{\text{larger value} - \text{smaller value}}{2} \quad (1)$$

### 6.2 0 g Level offset

0 g level is the output level when there is no acceleration or motion acting on the sensor i.e. zero input. A sensor placed on a perfect horizontal plane will give 0 g output on X-axis and Y-axis but 1 g on Z-axis. The deviation of an actual output value from the ideal value gives the 0 g level offset. 0 g offset value is influenced by external parameters like temperature and stress. External stress on the sensor will affect the sensor performance significantly. The 0 g level offset will also drift over temperature.

External stress: Vias under the sensor on a PCB, PCB warpage, external mechanical stress to the sensor.

### 6.3 Noise density

Noise density of the sensor is expressed as  $\mu\text{g}/\sqrt{\text{Hz}}$ . Noise density of the acceleration sensor is dependent on the output data rate. The values are expressed in the chapter 8. The noise of the acceleration sensor is determined by the equivalent noise bandwidth of the output filter and coefficient of the filter order. In general, the noise density is determined by the equation:

$$\text{Noise density} = \frac{\text{rms noise}}{\sqrt{\text{Bandwidth} * \text{filter coefficient}}} \quad [\mu\text{g}/\sqrt{\text{Hz}}] \quad (2)$$

## 7 Quick start guide

This chapter describes the start up sequence of the acceleration sensor.

### 7.1 Power supply

The sensor has two individual supply voltage pins.

- $VDD$  is main supply voltage

- $VDD\_IO$  is the I/O pin supply voltage for the digital I<sup>2</sup>C communication interface

It should be noted that  $VDD$  level should never be lower than  $VDD\_IO$  i.e. proper power up should be  $VDD > VDD\_IO$ . It is possible to remove  $VDD$  by keeping  $VDD\_IO$  pin without communication interruption but the measurement chain of the sensor is turned off i.e.  $VDD = 0$  with  $VDD\_IO$  "high" is allowed. In this case, the measurement chain is turned off but the communication to the sensor is possible without interruption.

Power up sequence should be  $VDD > VDD\_IO$ .

### 7.2 Boot status

By proper powering up of the sensor with correct voltage level to the respective pins, the sensor enters into a 20 ms boot sequence to load the trimming parameters. After completion of the boot up sequence the sensor automatically enters to power down mode.

It is also possible to initiate the boot sequence manually by the user. It is performed by setting the BOOT bit of the *CTRL\_2* register to '1', then the boot sequence is initiated and trimming parameters are reloaded. In this case, the device operation mode does not change after boot procedure. No toggle of the power is required and the content of the device control registers is not modified.

During the 20ms boot sequence the registers are not accessible.

The boot status signal is identified by setting the INT1\_BOOT bit of the *CTRL\_5* register to '1'. When the sensor is in boot sequence, INT\_1 interrupt pin is driven high. Similarly when the boot sequence is completed, INT\_0 interrupt pin is driven low.

### 7.2.1 Soft reset

If required, the soft reset of the sensor is possible. It resets the default value of the control registers. The soft reset procedure will take 5  $\mu$ s.

The below steps should be considered for setting the BOOT bit manually:

1. Write SOFT\_RESET bit to '1'

2. Wait for 5  $\mu$ s

3. Write BOOT bit to '1'

4. wait for 20 ms

| Parameter           | Time      |

|---------------------|-----------|

| Boot sequence       | 20 ms     |

| Soft reset duration | 5 $\mu$ s |

Table 12: Time consumption

## 7.3 Flow chart

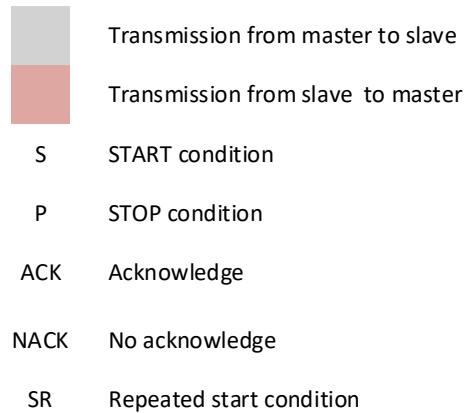

### 7.3.1 Communication check

After proper powering of the sensor, the first step is to check the communication to the sensor with I<sup>2</sup>C digital interface. It can be verified by reading the *DEVICE\_ID* register(0x0F). If the value from the *DEVICE\_ID* register(0x0F) is 0x44, then the communication to the sensor is successful.

Figure 10: Communication check

### 7.3.2 Sensor in operation

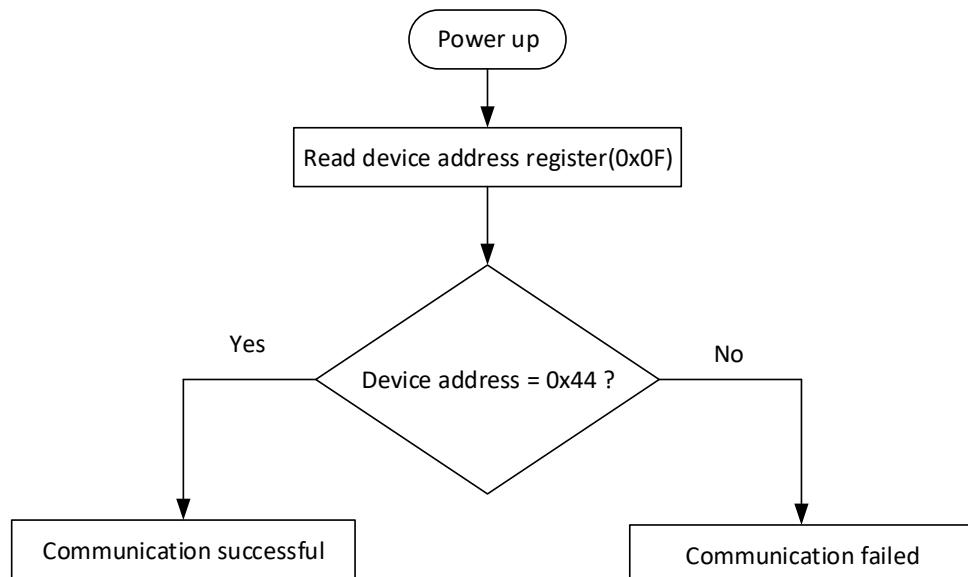

The following flow chart is an initialization example to operate the sensor in high performance mode with output data rate of 200 Hz.

Figure 11: Sensor in operation

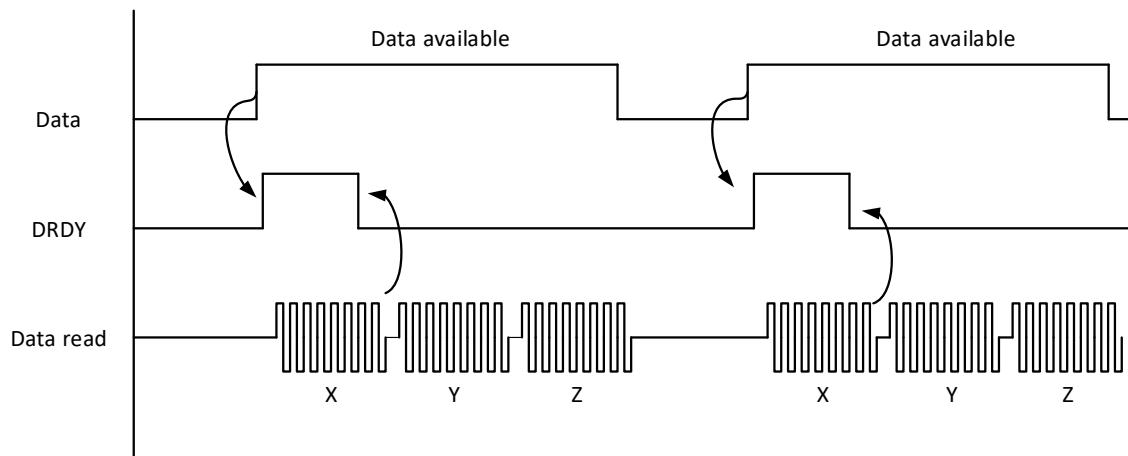

In order to set the sensor in one of the operation modes, the sensor needs to be initialized. The initialization of the sensor can be performed by defining output data rate, full scale setting and filtering path. After initializing the sensor, it is recommended to check if the data samples are available. It can be verified by reading DRDY bit in *STATUS* register(0x27). If the DRDY bit is enabled, the output data of three axes from the registers 0x28, 0x29, 0x2A, 0x2B, 0x2C and 0x2D are available. The acceleration value of the sensor is obtained by multiplying output data with necessary sensitivity parameter value based on the selected full scale range. Sensitivity parameter values are mentioned in the table 3.

## 8 Operating modes

The acceleration sensor can be operated in three different operation modes which provides different combination of noise and current consumption values. These operating modes are selected by using the MODE[1:0] bits in the *CTRL\_1* register(0x20).

- High performance mode

- Normal mode

- Low power mode

| High performance mode | Normal mode | Low power mode |

|-----------------------|-------------|----------------|

| 14 bit                | 14 bit      | 12 bit         |

Table 13: Acceleration resolution

By default after powering up of the sensor, it goes to power down mode. In power down mode all internal blocks are turned off to minimize the power consumption. After selecting one of the three operating modes, two configurable noise parameter options are available. This configuration is selected by writing LOW\_NOISE bit in the *CTRL\_6* register(0x25).

- Low-noise enabled (Noise is reduced)

- Low-noise disabled (Current consumption is reduced)

### 8.1 High performance mode

High performance mode provides the best performance in terms of noise. For example, a low noise level of  $90 \mu\text{g}/\sqrt{\text{Hz}}$  can be achieved with full scale range of  $\pm 2g$ , low noise bit enabled and ODR of 200 Hz. In this mode the output data rate can be configured between 12.5 Hz and 1600 Hz using *CTRL\_1* register.

### 8.2 Normal mode

The normal mode operation is a trade off between the noise and current consumption of the sensor. In this mode the output data rate can be configured between 1.6 Hz and 200 Hz using *CTRL\_1* register.

### 8.3 Low power mode

In this mode a low current consumption down to 1  $\mu\text{A}$  with ODR of 1.6 Hz can be achieved. The output data rate (ODR) can be configured between 1.6 Hz and 200 Hz using *CTRL\_1* register.

The table 14 and table 15 shows the noise and current consumption parameters for three different operating modes, which are verified at characterization level.

| Output data rate | High performance mode |                  | Normal mode      |                  | Low power mode   |                  |

|------------------|-----------------------|------------------|------------------|------------------|------------------|------------------|

|                  | Low Noise bit: 0      | Low Noise bit: 1 | Low Noise bit: 0 | Low Noise bit: 1 | Low Noise bit: 0 | Low Noise bit: 1 |

| 1.6 Hz           | -                     | -                | 2.2              | 2.6              | 1                | 1.2              |

| 12.5 Hz          | 126                   | 155              | 2.3              | 4                | 1.4              | 1.6              |

| 25.5 Hz          | 126                   | 155              | 6.9              | 7.5              | 2.4              | 2.7              |

| 50 Hz            | 126                   | 155              | 13               | 15               | 4                | 4.5              |

| 100 Hz           | 126                   | 155              | 25               | 29               | 7.2              | 8.3              |

| 200 Hz           | 126                   | 155              | 49.5             | 58               | 13.8             | 16               |

| 400/800/1600 Hz  | 126                   | 155              | -                | -                | -                | -                |

Table 14: Current consumption ( $\mu$ A)

| Full scale | High performance mode |                  | Normal mode      |                  | Low power mode   |                  |

|------------|-----------------------|------------------|------------------|------------------|------------------|------------------|

|            | Low Noise bit: 0      | Low Noise bit: 1 | Low Noise bit: 0 | Low Noise bit: 1 | Low Noise bit: 0 | Low Noise bit: 1 |

| $\pm 2g$   | 110                   | 90               | 210              | 180              | 550              | 450              |

| $\pm 4g$   | 110                   | 100              | 230              | 190              | 650              | 540              |

| $\pm 8g$   | 130                   | 120              | 240              | 210              | 680              | 580              |

| $\pm 16g$  | 170                   | 160              | 270              | 240              | 770              | 700              |

Table 15: Noise density at ODR = 200 Hz ( $\mu$ g / $\sqrt{\text{Hz}}$ )

## 8.4 Single data conversion mode

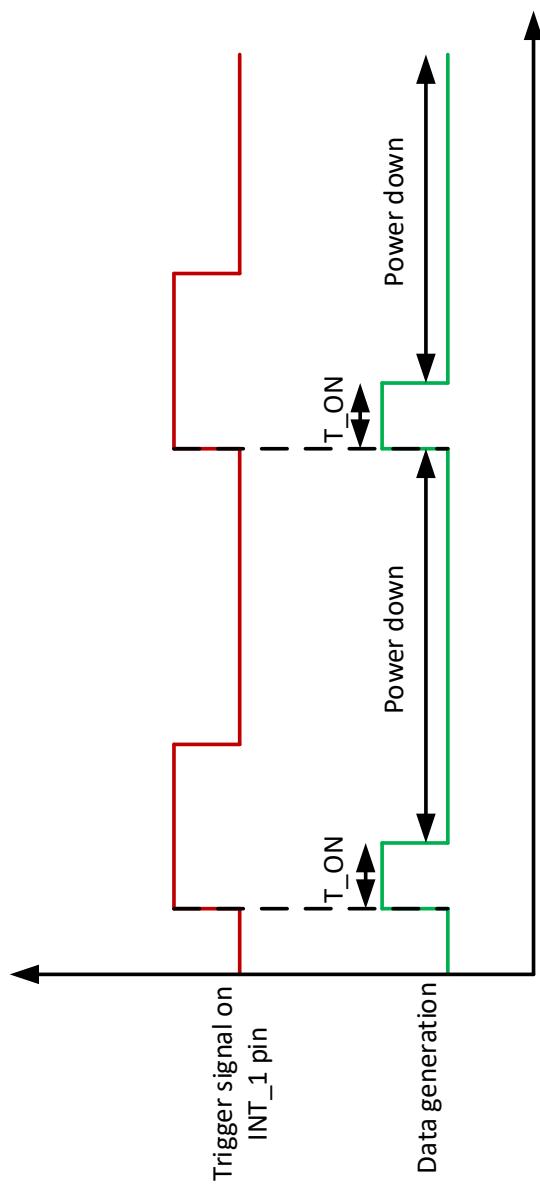

This mode is available only in the normal and low power mode. It is enabled by using the MODE[1:0] bits in *CTRL\_1* register(0x20). In this mode, the sensor waits for a trigger signal or enabling SLP\_MODE\_SEL bit to generate new data. After that the sensor immediately goes to power down mode. The maximum output data rate using single data conversion mode is 200 Hz.

In this mode, the data generation is achieved by two following ways:

### 1. A rising edge trigger signal on the INT\_1 pin

In this configuration, the sensor waits for a trigger signal to generate a new data. It can be performed by sending a trigger signal from the processor to INT\_1 pin. In this case, the SLP\_MODE\_SEL should be set to '0'. The user can detect the status of the conversion using the DRDY bit in the *STATUS* register (0x27). The status signal can also be routed to the

INT\_0 pin by writing '1' to INT0\_DRDY bit in the register *CTRL\_4* . The minimum duration of trigger signal high level is 20 ns.

## 2. Writing SLP\_MODE\_1 bit to '1' in *CTRL\_3* register

In this configuration, the data generation takes place by enabling SLP\_MODE\_1 bit in *CTRL\_3* register. In this case the SLP\_MODE\_SEL should be set to '0'. The user can detect the status of the conversion using DRDY bit/signal or by checking when the SLP\_MODE\_1 bit in *CTRL\_3* register(0x22) is automatically cleared.

The conversion time (T\_ON) in the normal and low power mode is mentioned in table 16

| Operating mode | Conversion time (T_ON) |

|----------------|------------------------|

| Normal mode    | 2.30 ms                |

| Low power mode | 1.20 ms                |

Table 16: Conversion time

Figure 12: Single data conversion using an external trigger signal

## 9 Output data rate

The data sampling rate of the sensor is defined by output data rate. After the device is powered up with one of the three operating modes, the device is in continuous conversion of data. One of the following output data rates can be selected through the ODR bits in *CTRL\_1*. In high performance mode the output data rate of the sensor can be configured between 12.5 Hz and 1600 Hz. In normal/low power mode the output data rate of the sensor can be configured between 1.6 Hz and 200 Hz.

| Output data rate ODR[3:0] | High performance mode | Normal Mode / Low power mode |

|---------------------------|-----------------------|------------------------------|

| 0000                      | Power down            |                              |

| 0001                      | 12.5 Hz               | 1.6 Hz                       |

| 0010                      | 12.5 Hz               |                              |

| 0011                      | 25 Hz                 |                              |

| 0100                      | 50 Hz                 |                              |

| 0101                      | 100 Hz                |                              |

| 0110                      | 200 Hz                |                              |

| 0111                      | 400 Hz                | 200 Hz                       |

| 1000                      | 800 Hz                | 200 Hz                       |

| 1001                      | 1600 Hz               | 200 Hz                       |

Table 17: Output data rate

## 10 Acceleration bandwidth and filtering chain

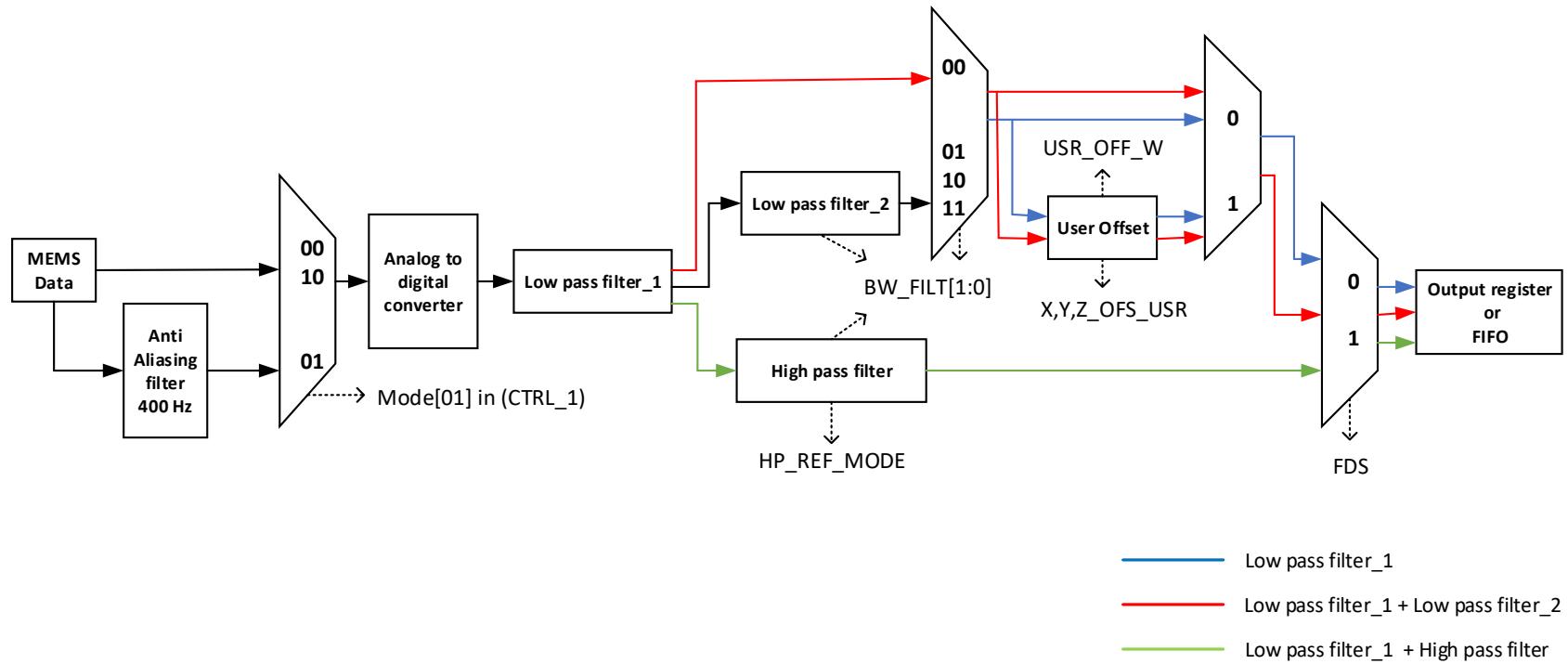

The acceleration sensor sampling chain consists of a series of blocks from MEMS data to output register as shown in figure 13.

- MEMS data

- Anti-Aliasing filter

- Analog to digital converter

- Low pass filter 1 and Low pass filter 2

- High pass filter

- User offset

- Output register or FIFO buffer

The output data in the output registers can be generated through three different filtering paths as shown in the figure 13. The filter setting determines the data path.

The cut-off frequency and number of samples to discard for those three filtering paths are described in the chapter 10.1, chapter 10.2 and chapter 10.3. The register settings for the three different data paths are mentioned below.

- **Low pass filter \_1** (red path)

By setting FDS bit to '0' and BW\_FILT[1:0] to '00' in register *CTRL\_6*

- **Low pass filter \_1 + Low pass filter \_2** (blue path)

By setting FDS bit to '0' and BW\_FILT[1:0] to '01'/'10'/'11' in register *CTRL\_6*

- **Low pass filter \_1 + High pass filter** (green path)

By setting FDS bit to '1' in register *CTRL\_6*

Figure 13: Block diagram of filtering chain

## 10.1 Low pass filter\_1

| Mode             | Output date rate | BW_FILT[1:0]=00                                 |             |

|------------------|------------------|-------------------------------------------------|-------------|

|                  |                  | Samples to discard <sup>1</sup><br>Settling@95% | Cutoff (Hz) |

| Low power        | 1.6 Hz to 200 Hz | 0                                               | 3200        |

| Normal           | 1.6 Hz to 200 Hz | 0                                               | 360         |

| High performance | 12.5 Hz to 50 Hz | 0                                               | ODR/2       |

|                  | 100 Hz to 800 Hz | 1                                               | ODR/2       |

|                  | 1600 Hz          | 2                                               | 400         |

Table 18: Low pass filter 1

<sup>1</sup>The starting condition of output data rate, operating mode and bandwidth do not impact the sample values to discard. Turn-on time (first sample available starting from power-down condition) is 1 / ODR.

## 10.2 Low pass filter \_1 + Low pass filter \_2

| Mode             | Output date rate  | BW_FILT[1:0]=01                                 |             | BW_FILT[1:0]=10                                 |             | BW_FILT[1:0]=11                                 |             |

|------------------|-------------------|-------------------------------------------------|-------------|-------------------------------------------------|-------------|-------------------------------------------------|-------------|

|                  |                   | Samples to discard <sup>1</sup><br>Settling@95% | Cutoff (Hz) | Samples to discard <sup>1</sup><br>Settling@95% | Cutoff (Hz) | Samples to discard <sup>1</sup><br>Settling@95% | Cutoff (Hz) |

| Low power        | 1.6 Hz to 200 Hz  | 1                                               | ODR/4       | 5                                               | ODR/10      | 11                                              | ODR/20      |

| Normal           | 1.6 Hz to 200 Hz  | 1                                               | ODR/4       | 5                                               | ODR/10      | 11                                              | ODR/20      |

| High performance | 12.5 Hz to 100 Hz | 1                                               | ODR/4       | 5                                               | ODR/10      | 11                                              | ODR/20      |

| High performance | 200 Hz to 800 Hz  | 2                                               | ODR/4       | 5                                               | ODR/10      | 11                                              | ODR/20      |

| High performance | 1600 Hz           | 3                                               | ODR/4       | 6                                               | ODR/10      | 12                                              | ODR/20      |

Table 19: Low pass filter\_1 + Low pass filter \_2

<sup>1</sup>The starting condition of output data rate, operating mode and bandwidth do not impact the sample values to discard.

## 10.3 Low pass filter \_1 + High pass filter

| Mode             | Output data rate  | BW_FILT[1:0]=01 or 00                           |             | BW_FILT[1:0]=10                                 |             | BW_FILT[1:0]=11                                 |             |

|------------------|-------------------|-------------------------------------------------|-------------|-------------------------------------------------|-------------|-------------------------------------------------|-------------|

|                  |                   | Samples to discard <sup>1</sup><br>Settling@95% | Cutoff (Hz) | Samples to discard <sup>1</sup><br>Settling@95% | Cutoff (Hz) | Samples to discard <sup>1</sup><br>Settling@95% | Cutoff (Hz) |

| Low power        | 1.6 Hz to 200 Hz  | 1                                               | ODR/4       | 5                                               | ODR/10      | 11                                              | ODR/20      |

| Normal           | 1.6 Hz to 200 Hz  | 1                                               | ODR/4       | 5                                               | ODR/10      | 11                                              | ODR/20      |

| High performance | 12.5 Hz to 100 Hz | 1                                               | ODR/4       | 5                                               | ODR/10      | 11                                              | ODR/20      |

| High performance | 200 Hz to 800 Hz  | 2                                               | ODR/4       | 5                                               | ODR/10      | 11                                              | ODR/20      |

| High performance | 1600 Hz           | 3                                               | ODR/4       | 6                                               | ODR/10      | 12                                              | ODR/20      |

Table 20: Low pass filter\_1 + High pass filter

<sup>1</sup> The starting condition of output data rate, operating mode and bandwidth do not impact the sample values to discard.

## 10.4 User offset

In order to define user offset for X, Y, and Z axis, the USR\_OFF\_ON\_OUT is set to '1' and FDS is set to '0'. User defined offsets are subtracted from the values measured. The weight of the bits in the offset registers X\_OFS\_USR, Y\_OFS\_USR, Z\_OFS\_USR is defined through the USR\_OFF\_W bit in CTRL\_7 register.

The offset values are signed values with two's complement

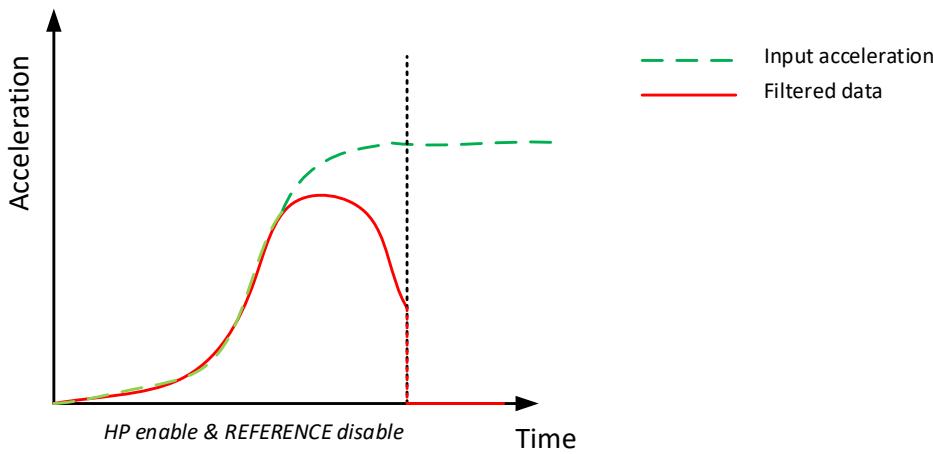

## 10.5 High pass filter path

The acceleration sensor includes an embedded high-pass filtering capability to easily remove the DC component of the measured acceleration. As shown in the figure 13, with the FDS bit in register CTRL\_6 the user can route the filter outputs to the output registers.

It is also possible to independently apply the filter to the embedded function data (Free-fall, wake up, tap detection and etc). This means that it is possible to get filtered data while the interrupt generation works on unfiltered data.

### 10.5.1 Reference mode

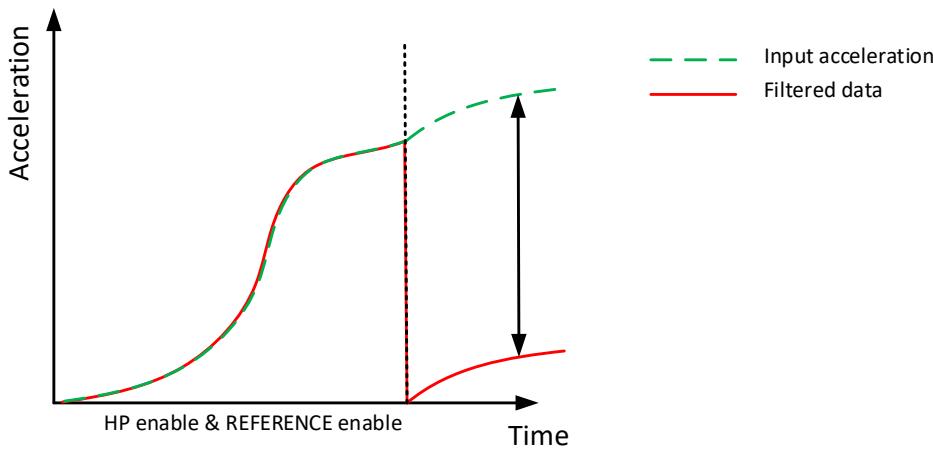

The high-pass filter can be configured in the reference mode. It can be activated using HP\_REF\_MODE bit in *CTRL\_7* register. In this configuration the output data is calculated as the difference between the input acceleration and the values captured when reference mode was enabled. In this way only the difference is applied without any filtering.

Figure 14: High pass filter without REFERENCE mode

Figure 15: High pass filter with REFERENCE mode

## 11 First-In First-Out (FIFO) buffer

The acceleration sensor provides a FIFO (first-in first-out) buffer functionality to prevent continuous communication between the processor and sensor. As a result, it reduces considerable system power consumption. It can store up to 32 output data from all three axis X, Y and Z. The processor can be notified only when it is necessary to initiate burst read out of the FIFO buffer content. The interrupt pins INT\_0 and/or INT\_1 is used to generate interrupt signals, if the FIFO buffer is full.

The FIFO buffer can be operated using five different modes:

- Bypass mode

- FIFO mode

- Continuous to FIFO mode

- Bypass to Continuous mode

- Continuous mode

Figure 16: First-in First-out Buffer

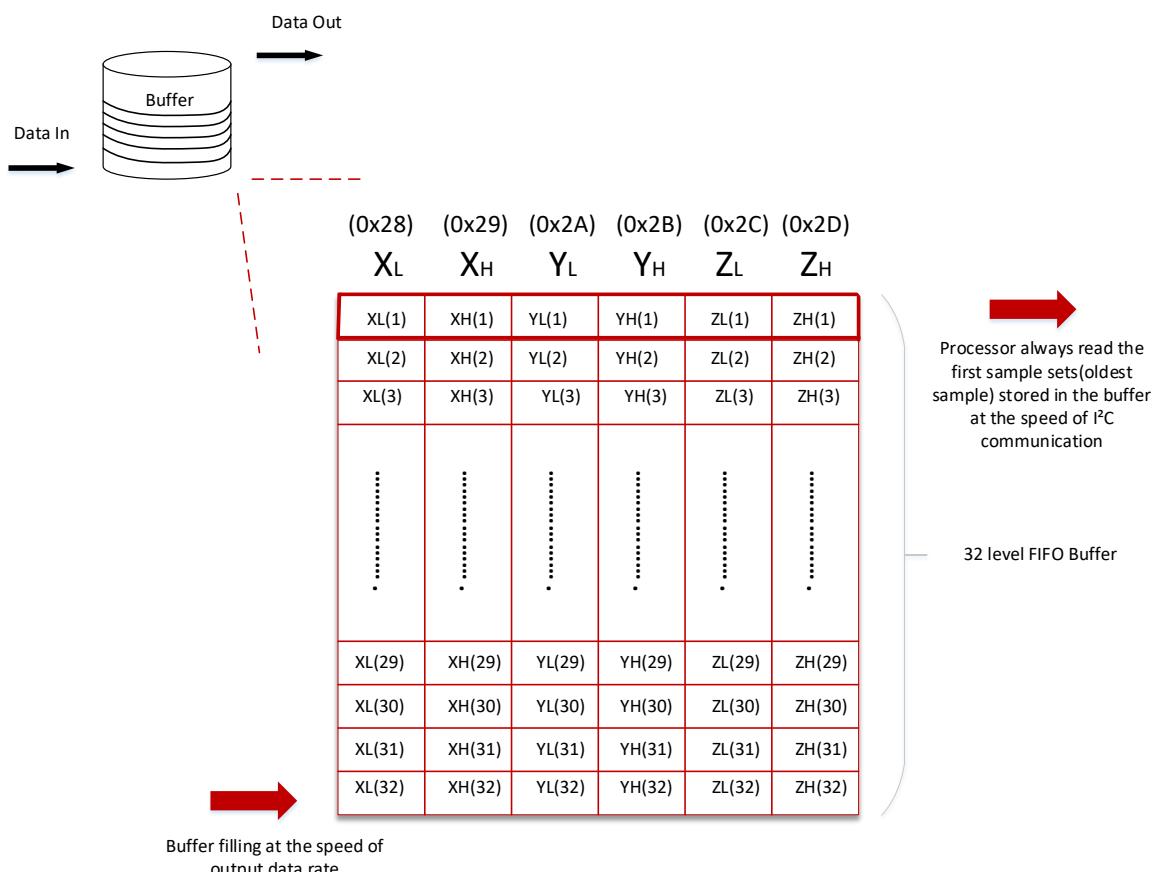

The FIFO buffer stores new data sets in the blocks until all the 32 slots are full. If additional new data is available, the new data replaces the old data in the buffer. The first data enters the lowest level of the buffer. When the second data is available to be stored in FIFO buffer, the first data moves one level up and the second data is stored in the lowest level and this process repeats until the buffer is full. The FIFO buffer can store the data samples with respect to the selected resolution i.e high performance/normal mode - 14 bits and low power mode - 12 bits. The rate at which data is stored in the FIFO buffer depends on the selected output data rate in *CTRL\_1* register. After enabling the buffer, the output registers (from 0x28 to 0x2D) will get the oldest data sets from the FIFO buffer except for bypass mode.

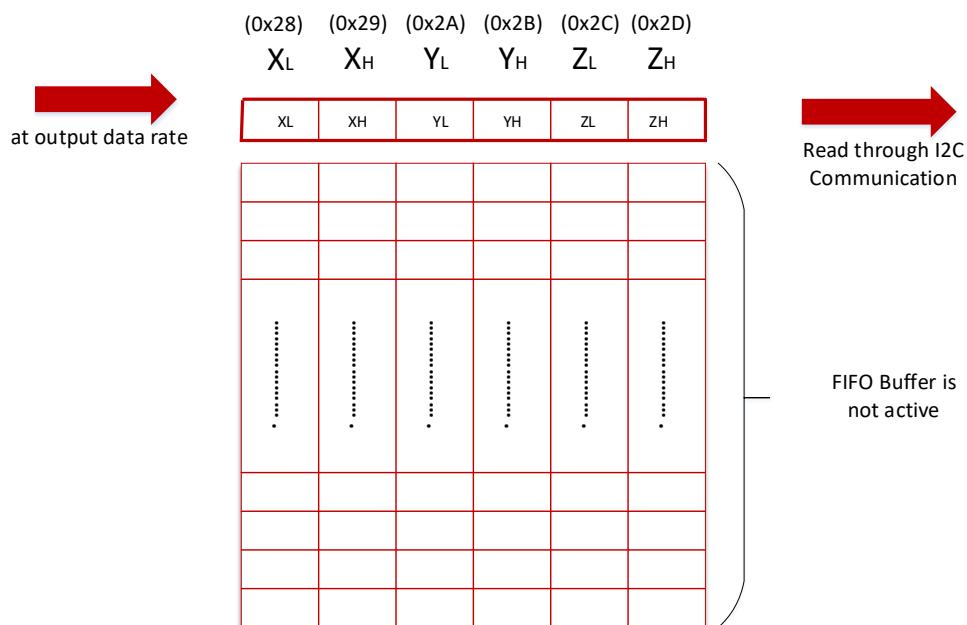

## 11.1 Bypass mode

In Bypass mode, the generated data is directly available in the output registers. FIFO buffer is not active in this mode. This mode is activated by writing FMODE[2:0] bits in *FIFO\_CTRL* register. Bypass mode is also used to clear the content of the FIFO buffer or to reset the buffer in FIFO mode.

Figure 17: Bypass mode

## 11.2 FIFO mode

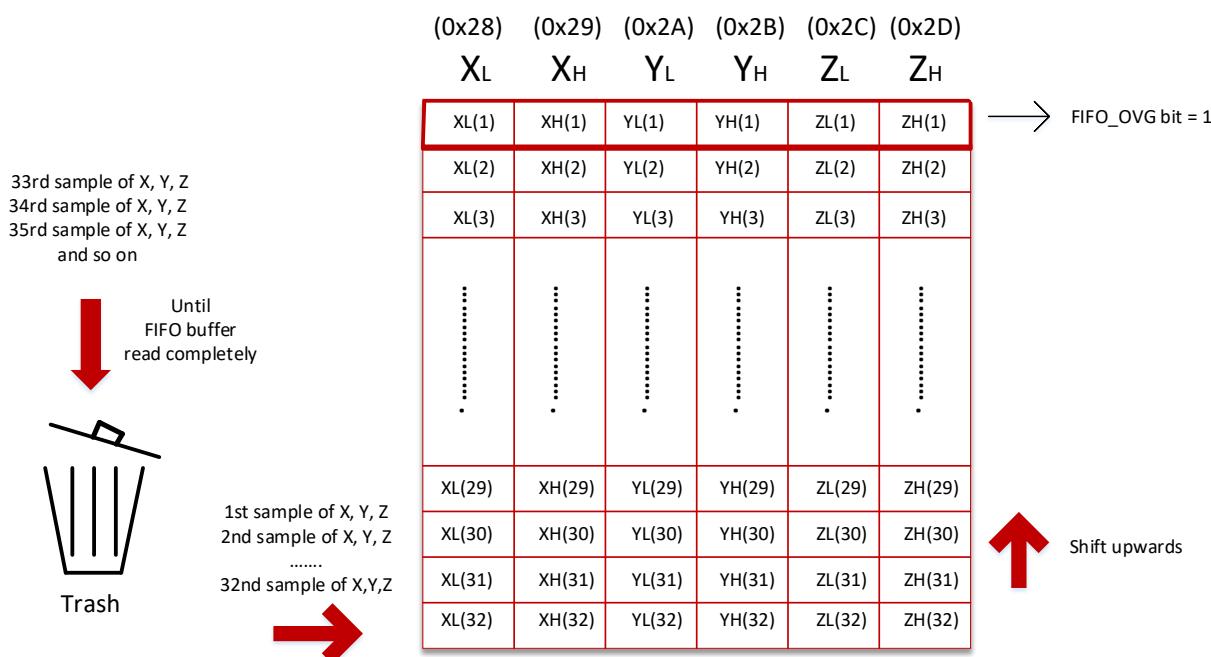

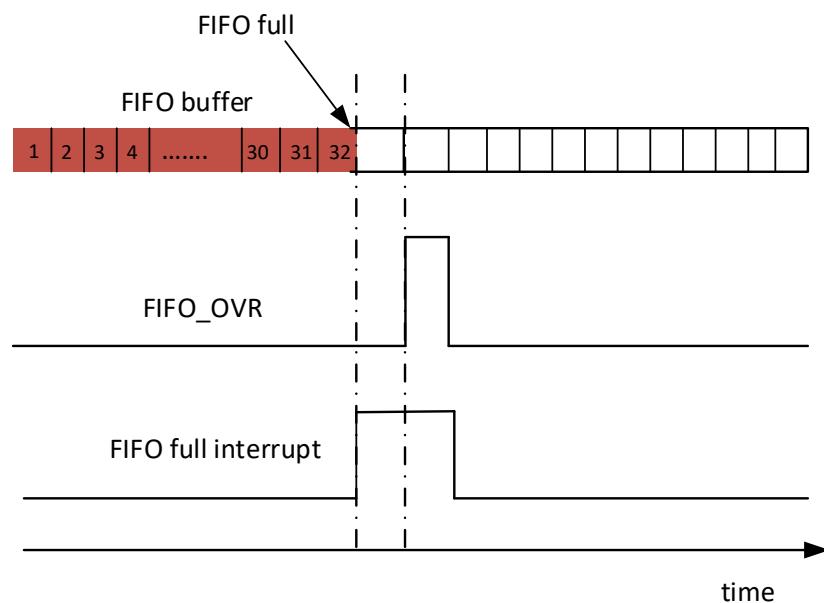

In FIFO mode, the 32 levels in FIFO buffer are filled with data samples continuously. When the buffer is completely filled, the FIFO\_OVR bit goes to '1', the buffer stops collecting the data. The FIFO mode is activated by writing '001' in FMODE[2:0] field in the *FIFO\_CTRL* register.

While FIFO buffer starts collecting data, DIFF[5:0] bits in the *FIFO\_SAMPLES* register changes with respect to the number of samples stored. The speed at which the processor reads the data from the FIFO buffer is not important. Because the data collection is stopped after the buffer is full and there is no risk that buffer will overwrite the data.

Figure 18: FIFO mode

In order to serve the FIFO full (DIFF[5] bit) event as soon as possible, it is recommended to route the Diff5 bit to the interrupt pin (INT\_0 or INT\_1) in order to generate an interrupt rather than FIFO\_OVR bit. The difference between the FIFO\_OVR bit and Diff5 bit is explained in figure 19.

When the FIFO mode is enabled, the buffer starts collecting the data at selected output data rate. The buffer stops collecting the data after the 32 levels are filled i.e. the incoming new data samples are ignored. The user can read the data from FIFO buffer any time, it is maintained unchanged until the Bypass mode is enabled. The FIFO\_OVR bit is reset when the first sample set has been read by the processor. By enabling the Bypass mode the FIFO mode will be reset.

Figure 19: FIFO mode interrupts

### 11.3 Continuous mode

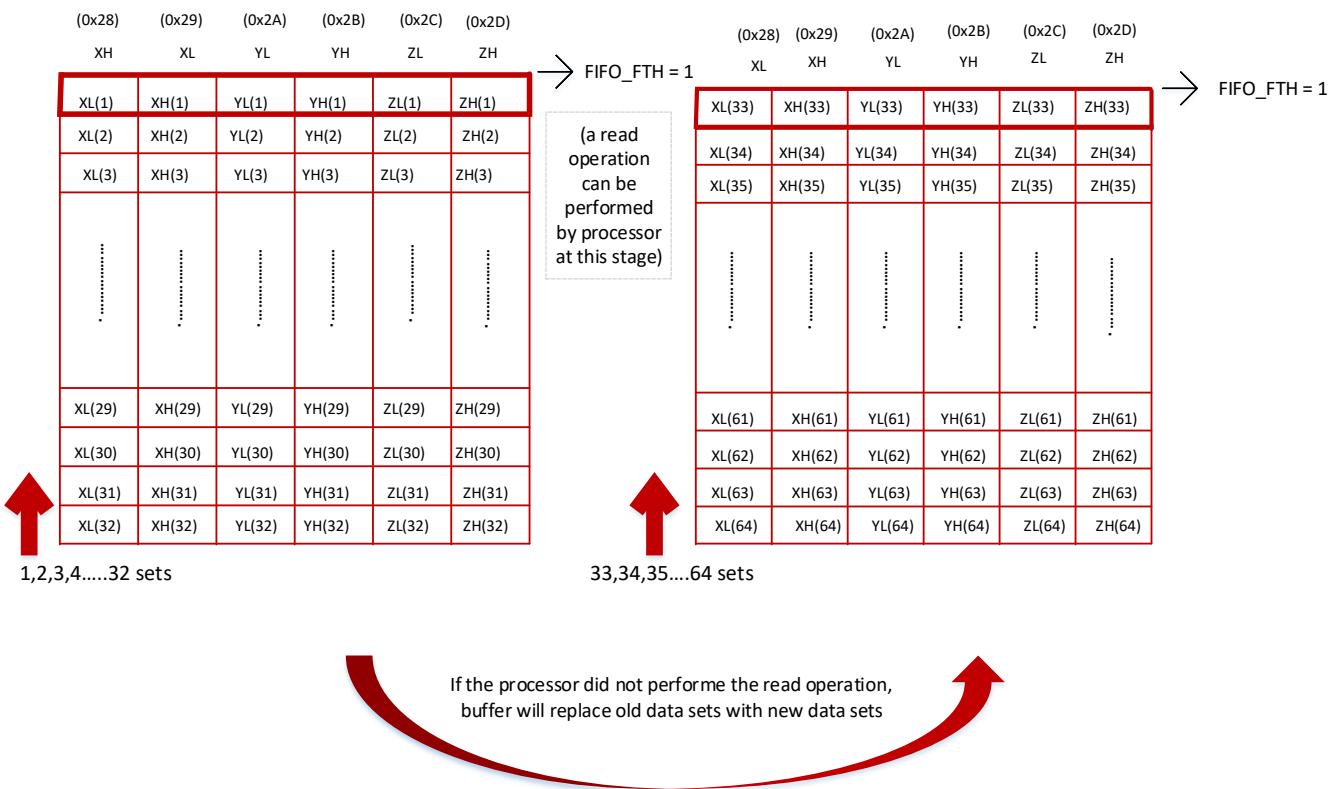

In continuous mode, the 32 levels of the FIFO buffer is continuously filled and starts to replace new data in the place of old data, when the buffer is full. This process continues until the processor initiates a read operation to the output registers. When the 32 level buffer is completely filled, the FIFO\_FTH bit goes to '1' and it can be routed to interrupt pin which triggers the processor to read the content of FIFO buffer. This mode can be terminated by enabling Bypass mode.

The speed at which the processor read the data sets should be faster than output data rate of the sensor in order to not lose the stored data sets

When a read operation is initiated by the processor to the sensor, the content of the output registers is moved to the I<sup>2</sup>C register. The current oldest FIFO sample is shifted into the output registers in order to allow the next read operation.

Figure 20: Continuous mode

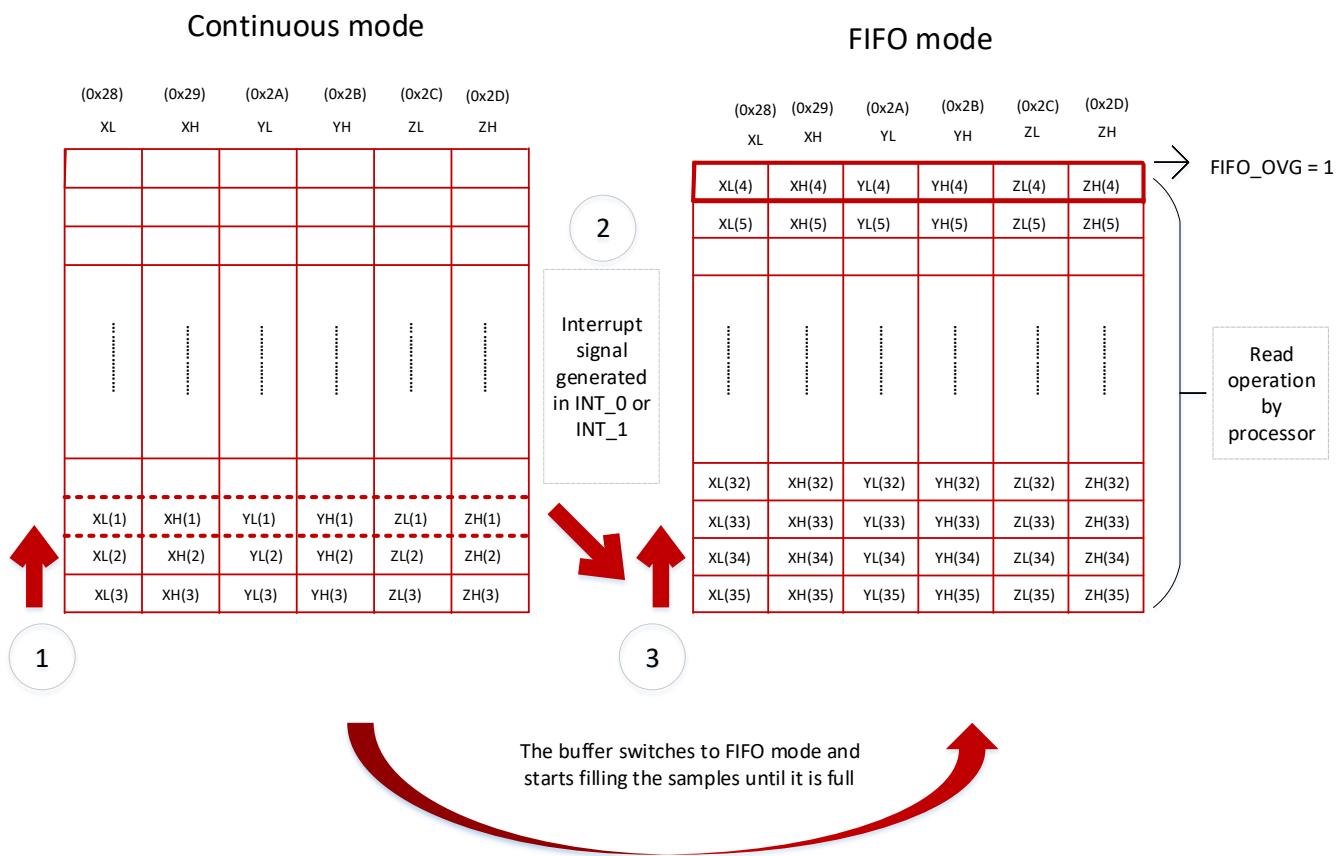

## 11.4 Continuous to FIFO mode

In this mode, initially the buffer starts operating in continuous mode and switches to FIFO mode when the selected interrupt (wake-up, free-fall, motion, etc) occurs. This mode helps to collect and analyse the output data samples after an interrupt signal (tap, motion, free-fall, etc) is generated. During this mode, the buffer works initially in continuous mode. In continuous mode, the buffer starts collecting the data samples continuously. As soon as the activated interrupt signal is generated, the FIFO mode is active and it starts collecting the output samples until it is full. When the buffer is full, the FIFO\_OVG bit is set to '1' when the next samples overwrite the oldest and the FIFO stops collecting the data.

When the selected interrupt occurs, the FIFO mode change is triggered only if the interrupt signal is routed to INT\_0 or INT\_1 pin.

The following steps are recommended to enable continuous to FIFO mode.

- Step 1: Enable interrupt features (tap, free-fall, motion and etc)

- Step 2: Route the interrupt signal to either INT\_0 or INT\_1 pin

- Step 2: Enable the continuous to FIFO mode using FMODE[2:0] in *FIFO\_CTRL* register

Figure 21: Continuous to FIFO mode

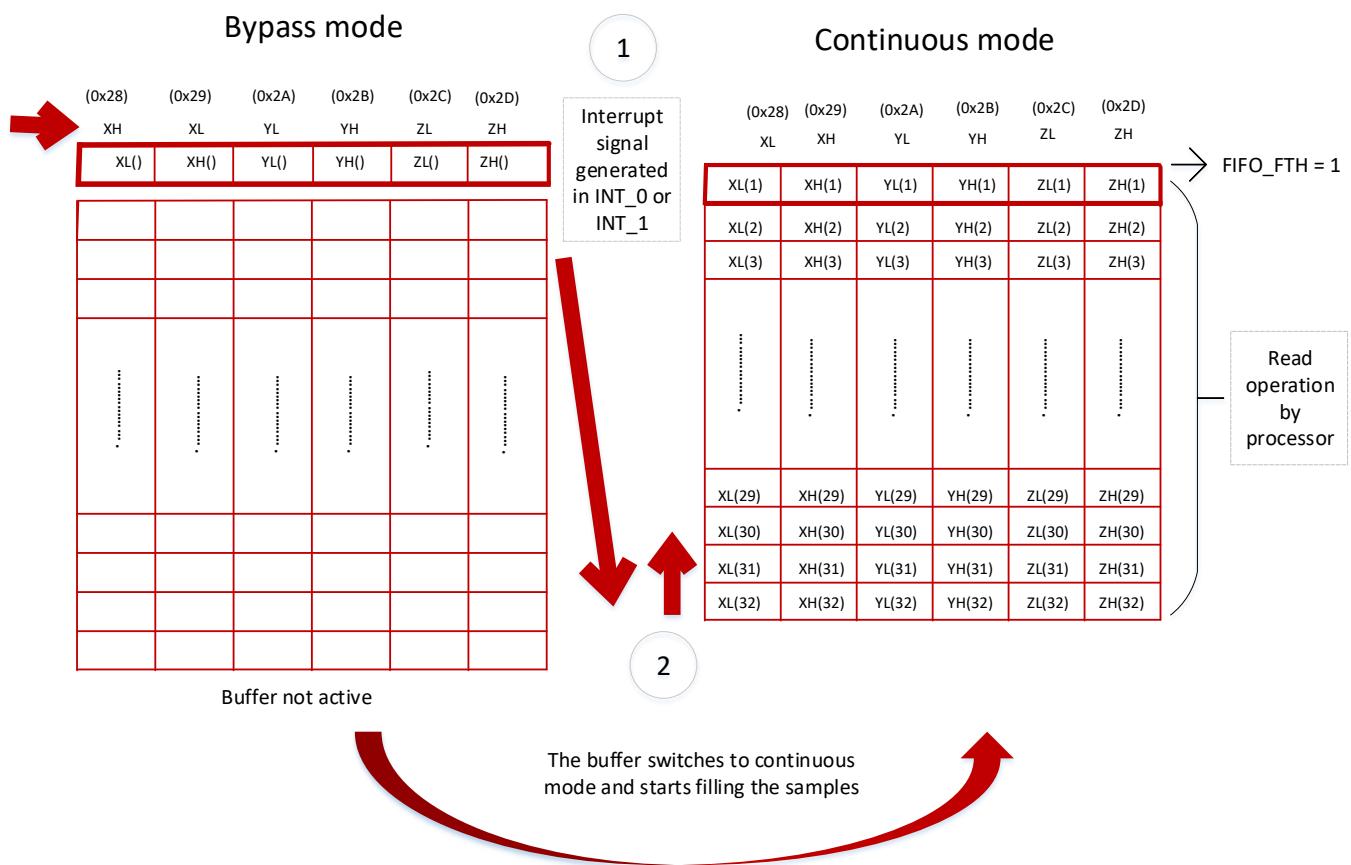

## 11.5 Bypass to continuous mode

In this mode, initially the buffer works in bypass mode and as soon as the selected interrupt signal is generated the buffer switches to continuous mode.

The following steps are recommended to enable Bypass to Continuous mode.

- Step 1: Enable interrupt features (tap, free-fall, motion and etc)

- Step 1: Set FTH[4:0] to 31

- Step 2: Route the interrupt signal to either INT\_0 or INT\_1 pin

- Step 2: Enable the Continuous to FIFO mode using FMODE[2:0] in *FIFO\_CTRL* register

Initially the buffer works in Bypass mode, so no data is stored in the buffer. When a selected interrupt signal is generated, the buffer switches to continuous mode and starts to fill the data at selected output data rate. When the programmed threshold is reached, the FIFO\_FTH interrupt goes high, and the processor can start reading all FIFO samples (32 \* 6 bytes) as soon as possible to avoid loss of data. If the FIFO\_OVG bit was set, it will change to '0', when the first FIFO data is read creating space for new data.

Figure 22: Bypass to Continuous mode

If the processor does not initiate read operation, the buffer starts replacing old data with new data. This process will continue until the generated interrupt flag is cleared or buffer goes to Bypass mode, then the buffer stops collecting the data.

## 11.6 Understanding FIFO samples and interrupts

### 11.6.1 FIFO samples

The samples are stored in the buffer at the rate of selected output data rate. The threshold values are defined using the FIFO\_SAMPLES register.

| Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1 | Bit 0 |

|----------|----------|-------|-------|-----------|-------|-------|-------|

| FIFO_FTH | FIFO_OVR |       |       | DIFF[5:0] |       |       |       |

Table 21: FIFO\_Samples register

- FIFO\_FTH bit is used to notify whether the FIFO content is greater than or equal to the watermark level defined by DIFF[5:0]. This signal can be routed to either INT\_0 or INT\_1 pin.

- FIFO\_OVR bit defines whether the 32 level buffer is full or not. It can be used to notify the processor to read whole content of the buffer. When the processor starts reading the first sample in the buffer, this bit is set to '0'.

- DIFF[5:0] gives the information about number of levels in the buffer filled with data samples or number of samples in the buffer read by processor( '000000b' for FIFO empty and '100000b' for FIFO is full). This signal also be routed to either INT\_0 or INT\_1

## 11.6.2 FIFO interrupts

### 11.6.2.1 FIFO threshold (FIFO\_FTH bit)

The FIFO threshold is a configurable feature which can be used to produce a specific interrupt, to know whether the FIFO buffer contains at least the number of samples defined as the threshold level. The user can select the desired level in a range from 0 to 31 using the FTH[4:0] bits in the *FIFO\_CTRL* register. If the number of entries in FIFO (Diff[5:0]) is greater than or equal to the value programmed in FTH[4:0], the FIFO\_FTH bit is set high in the *FIFO\_SAMPLES* register. Diff[5:0] increases by one step at the ODR frequency and decreases by one step every time that a sample reading is performed by the host controller.

### 11.6.2.2 FIFO full (Diff5 bit)

When the buffer is full, the sensor can be configured to generate an interrupt signal using Diff5 bit. In order to perform this, set the INT0\_DIFF5 bit in the *CTRL\_4* register to '1' or INT1\_DIFF5 bit in the *CTRL\_5* register to '1'. To avoid losing samples, the FIFO reading operation must start and complete inside 1 ODR window.

### 11.6.2.3 FIFO overrun (FIFO\_OVR)

It is possible to configure the device to generate an interrupt using FIFO\_OVR, if the overrun event occurs in FIFO buffer. In order to initiate this, set the INT1\_OVR bit of the *CTRL\_5* register to '1'.

## 11.7 How to read data from FIFO Buffer

When any of the operating FIFO buffer mode is selected except Bypass mode, the first sample stored in the buffer is always read from the output registers. After reading the output data registers, the FIFO blocks are moved one level up vertically to allocate space to store new samples. The whole content of the FIFO buffer i.e. 32 level of 6 bytes (total of 192 bytes) of data samples from X\_L, X\_H, Y\_L, Y\_H, Z\_L and Z\_H can be read at once. The content of the FIFO buffer will be the same even after reading the data and it will be replaced only when new set of samples stored in FIFO buffer. When the processor initiates a read operation to the output register 0x28, the automatic increment of the address 0x29, 0x2A, 0x2B, 0x2C and 0x2D will be performed, if the IF\_ADD\_INC bit is enabled in *CTRL\_2* register.

The standard I<sup>2</sup>C communication protocol has two clock frequencies, standard mode of 100 kHz and full speed mode of 400 kHz clock. In order to perform read operation, the I<sup>2</sup>C communication takes 29 clock signals to initiate read operation for a specific register. It starts

with a start condition + slave address + write register + read register. Additionally, to read every byte (8 bit register value) 9 clock pulses are necessary. In total 83 clock pulses are used to read a one sample set from the output registers of X, Y and Z axis (0x28, 0x29, 0x2A, 0x2B, 0x2C and 0x2D). In order to read single sample set from output register it takes 83 pulses \* 1/100 kHz (830 µs). To read the whole content of the buffer, a total of 17.57 ms (29 + 9 \* 192) time is necessary.

In order to not lose samples, the application should read samples before the FIFO becomes full, setting a threshold and using the FTH interrupt.

| Output data rate (Hz) | FTH_TH (I <sup>2</sup> C - 100 kHz) | FTH_TH (I <sup>2</sup> C - 400 kHz) |

|-----------------------|-------------------------------------|-------------------------------------|

| 50                    | 32                                  | 32                                  |

| 100                   | 17                                  | 32                                  |

| 200                   | 8                                   | 32                                  |

| 400                   | 4                                   | 17                                  |

| 800                   | 1                                   | 8                                   |

| 1600                  | -                                   | 4                                   |

Table 22: Threshold function

## 12 Interrupt pin and functionality

The two independent interrupt pins INT\_0 and INT\_1 of the sensor can be used to route the following signals.

- Motion detection interrupt signal

- DRDY signal

- FIFO notification signal

### 12.1 INT\_0 and INT\_1

All the motion detection interrupt signals can be routed to the physical interrupt (either INT\_0 or INT\_1) pins by writing '1' to INTERRUPTS\_ENABLE bit in *CTRL\_7* register, otherwise it can be identified by reading their corresponding status or source register. By default, the bits in the control registers (*CTRL\_4* and *CTRL\_5*) are disabled i.e '0'. Any specific motion detection interrupt signals can be routed to the physical interrupt pins by enabling the following bits in the registers *CTRL\_4* and *CTRL\_5*.