# **VEK280 Evaluation Board User Guide (UG1612)**

## Introduction

- Overview

- Navigating Content by Design Process

- Additional Resources

- Block Diagram

- Board Features

- Board Specifications

## Board Setup and Configuration

- Standard ESD Measures

- Board Component Location

- Default Jumper and Switch Settings

- Versal Device Configuration

## Board Component Descriptions

- Overview

- Component Descriptions

## VITA 57.4 FMCP Connector Pinouts

- Overview

## Xilinx Design Constraints

- Overview

- CE Information

- Compliance Markings

## Regulatory and Compliance Information

- Finding Additional Documentation

- Support Resources

- References

- Revision History

- Please Read: Important Legal Notices

# Introduction

## Overview

The VEK280 evaluation board features the AMD Versal™ XCVE2802 device. The VEK280 board enables the demonstration, evaluation, and development of the applications listed here, as well as other customer applications. Many features found on the VEK280 board are subsets of existing Versal adaptive SoC boards (for example, the VCK190 and VMK180 boards).

- Fiber optic

- Communications

- Automotive

- Data center compute acceleration

- Aerospace and defense

- Test and measurement

The VEK280 evaluation board is equipped with many of the common board-level features needed for design development, including:

- HDMI support

- PCIe® support

- CAN support

- PMOD support

- SFP28 optical transceiver support

- LPDDR4 component memory

- USB

- Ethernet networking interfaces

- One FMC+ expansion port

## Models of Boards

The following table lists the models for the VEK280 evaluation board. See the [VEK280 Evaluation Board](#) product page for details.

**Table: Models of VEK280 Evaluation Boards**

| Kit | Description |

|-----|-------------|

|     |             |

| Kit           | Description                                                   |

|---------------|---------------------------------------------------------------|

| EK-VEK280-G   | AMD Versal adaptive SoC VEK280 evaluation kit                 |

| EK-VEK280-G-J | AMD Versal adaptive SoC VEK280 evaluation kit, Japan specific |

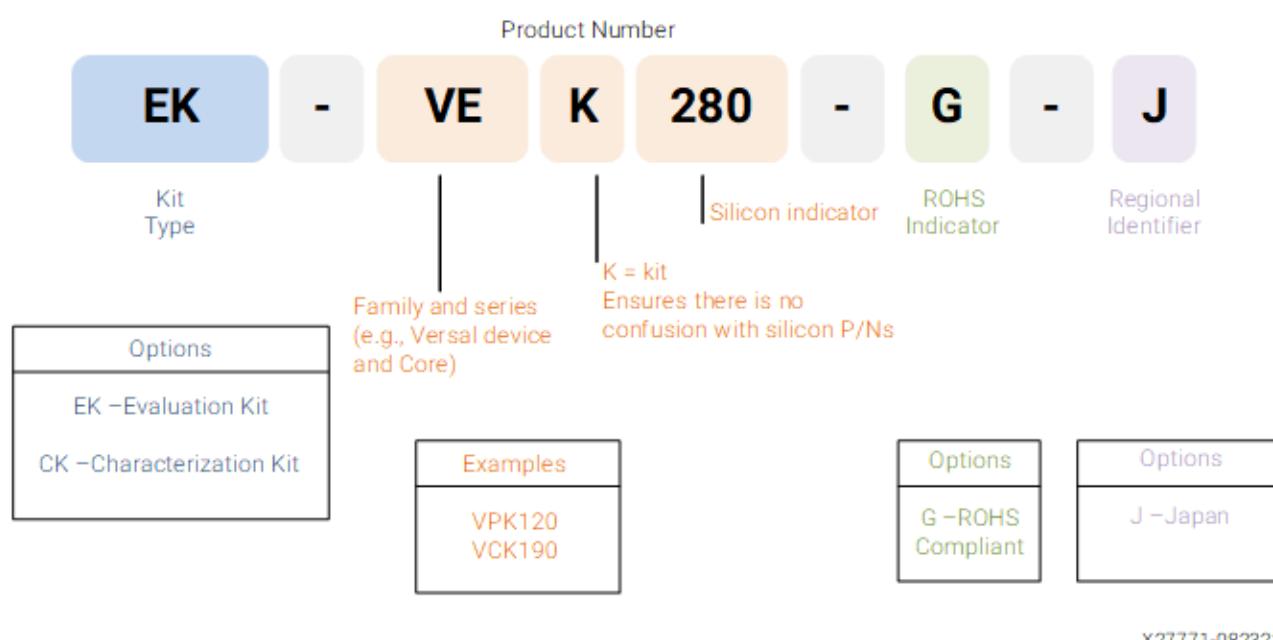

## Versal Device Kit Numbering

The Versal device kit numbering is illustrated in the following figure.

**Figure: Kit Numbering**

X27771-082323

## Navigating Content by Design Process

AMD Adaptive Computing documentation is organized around a set of standard design processes to help you find relevant content for your current development task. You can access the AMD Versal™ adaptive SoC design processes on the [Design Hubs](#) page. You can also use the [Design Flow Assistant](#) to better understand the design flows and find content that is specific to your intended design needs.

### Board System Design

Designing a PCB through schematics and board layout. Also involves power, thermal, and signal integrity considerations. For more information, see [Versal Adaptive SoC Design Process Documentation Board System Design](#).

# Additional Resources

See [Additional Resources and Legal Notices](#) for references to documents, files, and resources relevant to the VEK280 evaluation board.

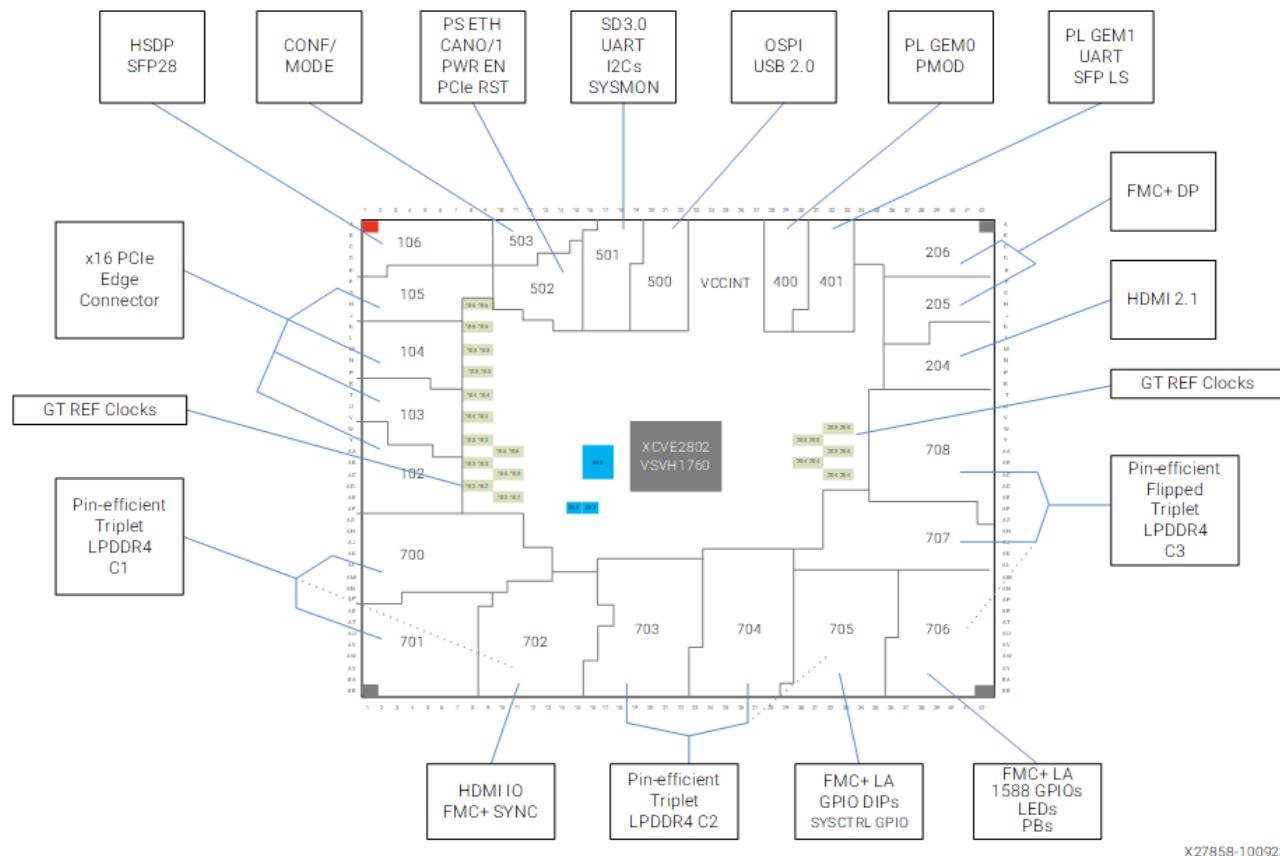

## Block Diagram

A block diagram of the VEK280 evaluation board is shown in the following figure.

**Figure: Evaluation Board Block Diagram**

## Board Features

The VEK280 evaluation board features are listed here. Detailed information for each feature is provided in [Board Component Descriptions](#).

- XCVE2802, VSVH2802 package

- Form factor: see [Board Specifications](#)

- Onboard configuration from:

- USB-to-JTAG bridge

- JTAG pod 2 mm 2x7 flat cable connector

- microSD card (PS MIO I/F)

- Quad SPI (QSPI)/eMMC (system controller I/F)

- OSPI

- Clocks

- Versal device bank 702/5/6 RC21008A SYS\_CLK\_0/1/2 (DIMM) 200 MHz

- Versal device bank GTY205/6 RC21008A\_GTCLK1\_OUT6/7 100 MHz

- Versal device bank GTY106 RC21008A RC21008A\_GTCLK1\_OUT8 156.25 MHz

- Versal device bank GTY106 626L15625 HSDP\_156\_25\_REFCLK 156.25 MHz

- Versal device bank GTY204 8T49N241 HDMI\_8T49N241\_OUT design dependent

- Versal device bank GTY204 TMDS1204 HDMI\_RCLK\_OUT design dependent

- Versal device bank 503 RC21008A PS\_REF\_CLK 33.3333 MHz

- Versal device bank 503 RTC Xtal 32.768 kHz

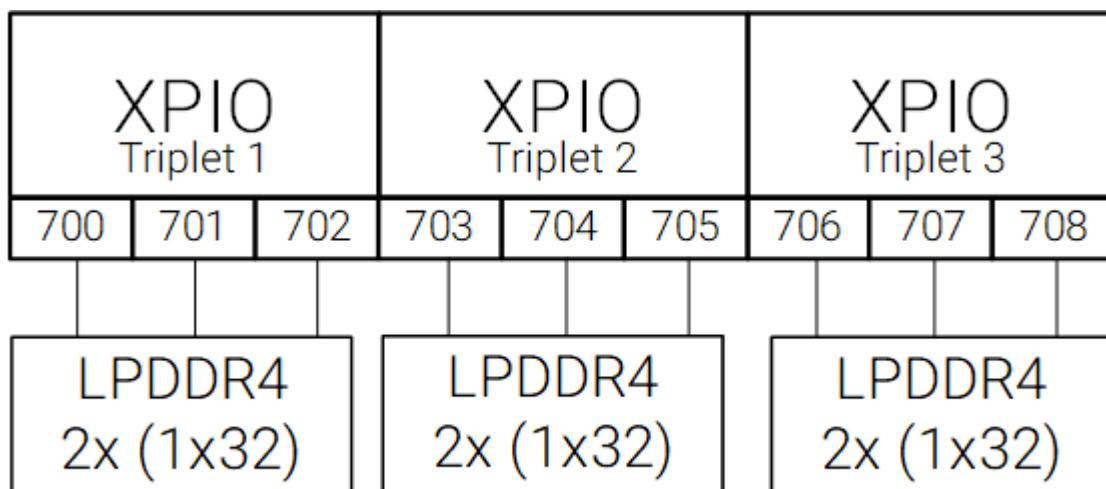

- Three pin-efficient mode LPDDR4 interfaces (2x32-bit 4 GB components each)

- XPIO triplet 1 (banks 700, 701, 702)

- XPIO triplet 2 (banks 703, 704, 705)

- XPIO triplet 3 (banks 706, 707, 708)

- PL FMCP HSPC (FMC+) connectivity

- FMCP1 HSPC full LA[00:33] bus

- PL GPIO connections

- PL UART1 to FTDI

- PL GPIO DIP switch (4-position)

- PL GPIO LEDs (four)

- PL GPIO pushbuttons (two)

- PL SYSCTRLR\_GPIO[0:7]

- PL 1588\_GPIO[0:7, SMA\_CLK I/O]

- 32 PL GTYP transceivers (8 quads)

- Not used (1, bank GTYP106)

- System controller HSDP (1, banks GTYP106)

- USB-C HSDP (1, banks GTYP106)

- SFP28 (1, bank GTYP106)

- PCIe Gen 4 (16, banks GTYP102-GTYP105)

- FMCP1 HSPC DP (8, banks GTYP205, GTYP206)

- PS PMC MIO connectivity

- PS MIO[0:12]: boot configuration OSPI

- PS MIO[13:25]: USB2.0

- PS MIO[26:36, 51]: SD1 I/F

- PS MIO[37]: ZU4\_TRIGGER/CANFD0\_INH (J406)

- PS MIO[38]: CAN0\_nSTB

- PS MIO[39:41]: SYSMON\_I2C

- PS MIO[42:43]: UART0 to FTDI

- PS MIO[44:47]: I2C1, I2C0

- PS MIO[48], PS LPD MIO[0:11, 24:25]: GEM0 RGMII Ethernet RJ-45

- PS MIO[11,49] and LPD MIO[12,13,20,23]: power enables

- PS MIO[50] and LPD MIO[18:19]: PCIe status

- PS LPD MIO [21:22]: optional fan interface

- LPD MIO[23]: VADJ\_FMC power rail

- Security: PSBATT button battery backup

- SYSMON header

- Operational switches (power on/off, POR\_B, boot mode DIP switch)

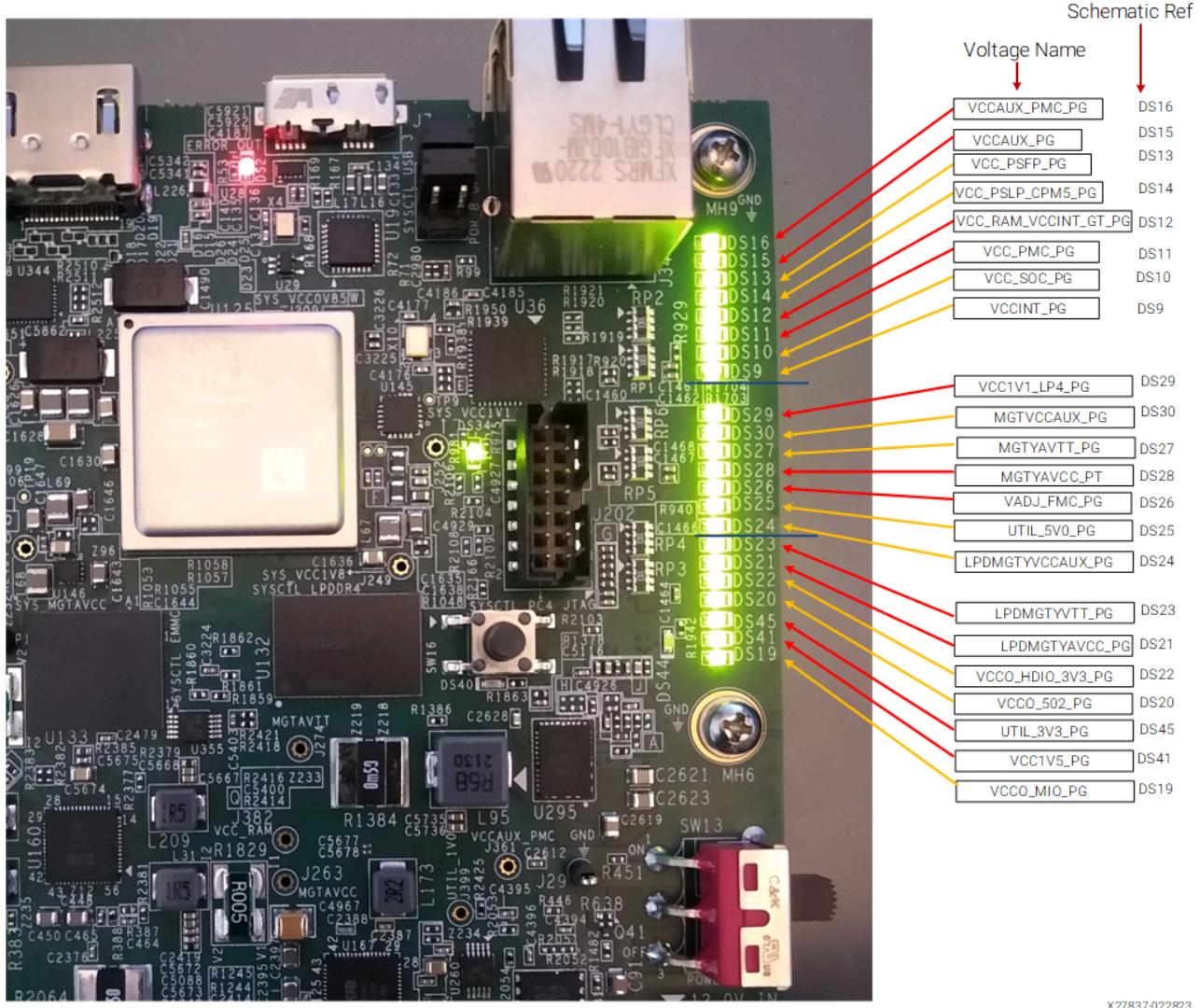

- Operational status LEDs (INIT, DONE, PS STATUS, PGOOD)

- See [Power and Status LEDs](#)

- Power management

- System controller (XCZU4EG)

The VEK280 evaluation board provides a rapid prototyping platform using the XCVE2802-2MSEVSVH device. See the *Versal Architecture and Product Data Sheet: Overview* ([DS950](#)) for a feature set overview, description, and ordering information.

# Board Specifications

## Dimensions

### PCB

Height: 7.517 inches (19.09 cm)

Length: 9.470 inches (24.05 cm)

Thickness: 64.5 mil  $\pm$ 5 mil (1.64 mm  $\pm$ 0.13 mm)

### Evaluation Board

Thickness fully assembled: 1.976 inches (5.017 cm)

Fully assembled, from table to bottom of PCB: 0.673 inches (1.710 cm)

---

**Note:** A 3D model of this board is not available.

See the [VEK280 Evaluation Kit](#) website for the XDC listing and board schematics.

## Environmental

---

**Note:** The operating temperature range is not fully tested across the specified temperature range. It is for general guidelines only. Customers should use the VEK280 evaluation board for evaluation purposes only in a normal lab environment and should not operate beyond room temperature.

---

### Temperature

Operating: 0°C to +45°C

Storage: -25°C to +60°C

### Humidity

5% to 95% non-condensing

## Operating Voltage

+12 V<sub>DC</sub>

## Mechanical

The VEK280 evaluation board includes a mechanical stiffener to help ensure success with the board under normal lab conditions and use. While it is

recommended to not remove this stiffener, it is understood that it might be necessary to remove it for continued evaluation.

The mechanical stiffener screw torque is 4.5 in-lbs. When attaching or removing the mechanical stiffener, ensure proper ESD precautions are taken. See [Standard ESD Measures](#) for suggestions on best practices.

- **Removing the Stiffener**

With power and other cabling unplugged, carefully unscrew the eleven 4-40 screws in any order. Care needs to be taken with the cooling solution as the board is manipulated due to potential excessive forces.

- **Attaching the Stiffener**

With power and other cabling unplugged, carefully align the PCBA standoff holes to the sheet metal tray (stiffener) standoffs. Next, it is suggested to insert two screws in opposite corners of the board/tray combination. Loosely tighten the screws to aid in alignment. Add the remaining nine screws and loosely tighten. Finally, in a left to right or right to left pattern, tighten all eleven screws to 4.5 in-lbs.

---

**Note:** The tray will only fit one direction with the transceiver connectors having cutouts below. See [Board Component Descriptions](#) for more information.

---

## Board Setup and Configuration

### Standard ESD Measures

---

**⚠ CAUTION!** ESD can damage electronic components when they are improperly handled, and can result in total or intermittent failures. Always follow ESD-prevention procedures when removing and replacing components.

---

To prevent ESD damage:

- Attach a wrist strap to an unpainted metal surface of your hardware to prevent electrostatic discharge from damaging your hardware.

- When you are using a wrist strap, follow all electrical safety procedures. A wrist strap is for static control. It does not increase or decrease your risk of receiving electric shock when you are using or working on electrical equipment.

- If you do not have a wrist strap, before you remove the product from ESD packaging and installing or replacing hardware, touch an unpainted metal surface of the system for a minimum of five seconds.

- Do not remove the device from the antistatic bag until you are ready to install the device in the system.

- With the device still in its antistatic bag, touch it to the metal frame of the system.

- Grasp cards and boards by the edges. Avoid touching the components and gold connectors on the adapter.

- If you need to lay the device down while it is out of the antistatic bag, lay it on the antistatic bag. Before you pick it up again, touch the antistatic bag and the metal frame of the system at the same time.

- Handle the devices carefully to prevent permanent damage.

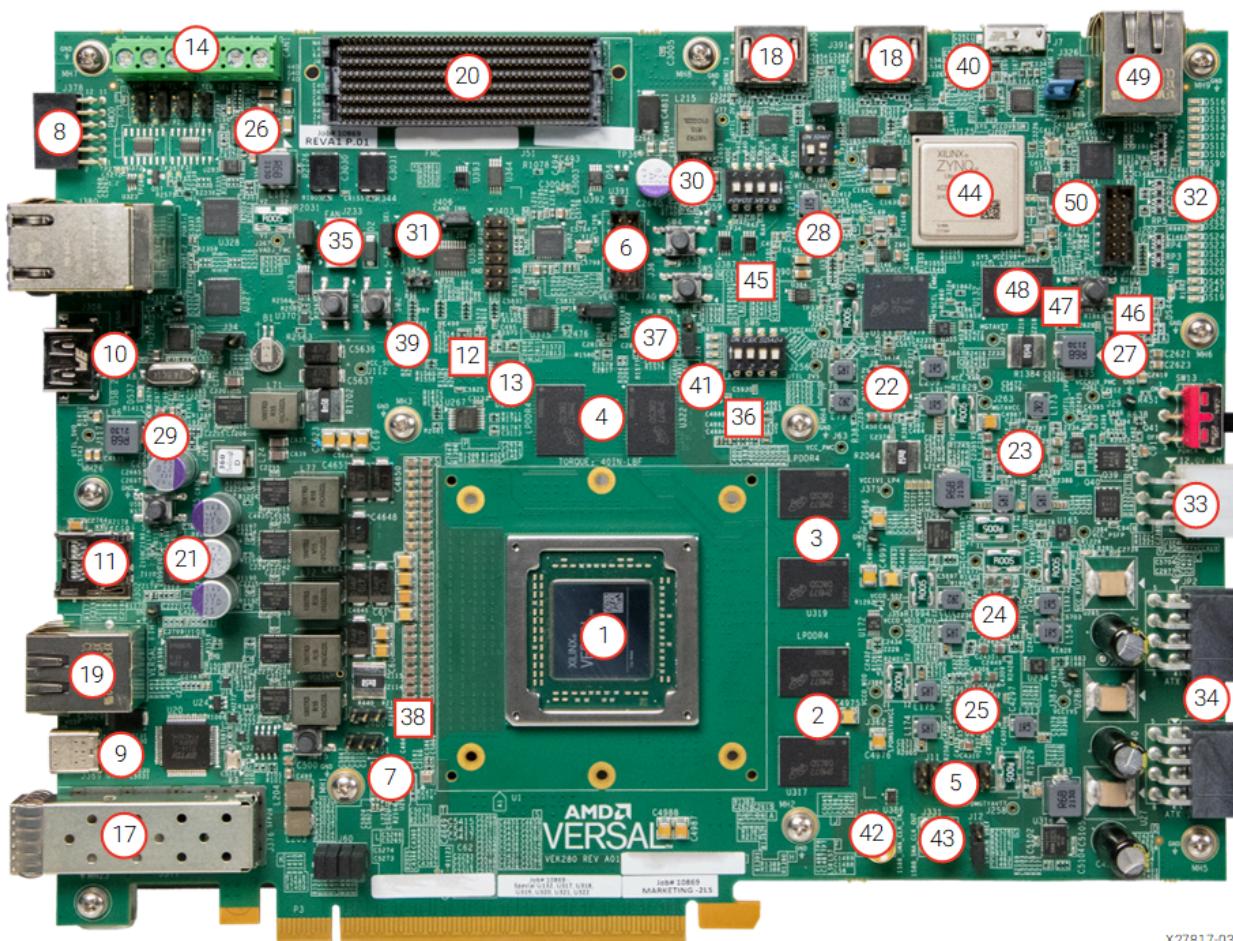

## Board Component Location

The following figure shows the VEK280 board component locations. Each numbered component shown in the figure is keyed to the table in [Board Component Descriptions](#).

---

**!! Important:** The following figure is for visual reference only and might not reflect the current revision of the board.

---

**!! Important:** There could be multiple revisions of this board. The specific details concerning the differences between revisions are not captured in this document. This document is not intended to be a reference design guide and the information herein should not be used as such. Always refer to the schematic, layout, and XDC files of the specific VEK280 version of interest for such details.

---

### Figure: Evaluation Board Component Locations

00 Round callout references a component on the front side of the board

00 Square callout references a component on the back side of the board

X27817-030223

## Board Component Descriptions

The following table identifies the components and references the respective schematic (038-05127-01) page numbers.

**⚠ CAUTION!** Do NOT plug a PC ATX power supply 6-pin connector into the VEK280 board power connector J16. The ATX 6-pin connector has a different pinout than J16. Connecting an ATX 6-pin connector into J16 damages the VEK280 board and voids the board warranty.

**Table: Board Component Locations**

| Callout Ref. Des. | Feature       | Notes                                                                          | Schematic Page |

|-------------------|---------------|--------------------------------------------------------------------------------|----------------|

| 1                 | U1            | AMD Versal™ adaptive SoC<br>The heatsink <sup>1</sup> is not shown in Figure 1 | 3-16           |

| 2                 | U317,<br>U318 | LPDDR4 16 GBIT comp. memory<br>Micron<br>MT53E512M32D1ZW-046                   | 3,22,23        |

| Callout | Ref. Des.     | Feature                                                  | Notes                                                                       | Schematic Page |

|---------|---------------|----------------------------------------------------------|-----------------------------------------------------------------------------|----------------|

|         |               | (B700-B702 IF)                                           | IC SDRAM LPDDR4<br>512Mx32 2133 MHz                                         |                |

| 3       | U319,<br>U320 | LPDDR4 16 GBIT<br>comp. memory<br>(B703-B705 IF)         | Micron<br>MT53E512M32D1ZW-046<br>IC SDRAM LPDDR4<br>512Mx32 2133 MHz        | 4,24,25        |

| 4       | U321,<br>U322 | LPDDR4 16 GBIT<br>comp. memory<br>(B706-B708 IF)         | Micron<br>MT53E512M32D1ZW-046<br>IC SDRAM LPDDR4<br>512Mx32 2133 MHz        | 5,26,27        |

| 5       | J11           | SYSMON header                                            | Sullins PBC06DAAN<br>Conn. hdr. vert. 12 pos. 2x6<br>2.54 mm pitch          | 10             |

| 6       | J36           | Adaptive SoC<br>JTAG 2 mm 2x7<br>flat-cable<br>connector | Molex 0878321420<br>Conn. hdr. male vert. 14<br>pos 2x7 2 mm                | 20             |

| 7       | U298          | PCIe® clock buffer                                       | Renesas RC19004AGNL                                                         | 49             |

| 8       | J378          | PMOD 2x6<br>connector                                    | Sullins PPPC062LJBN-RC<br>Conn Hdr Female RA 12<br>Pos 2x6 2.54 mm P TH     | 48             |

| 9       | J369,<br>U20  | USB-UART bridge,<br>USB Type-C<br>connector<br>(USB2.0)  | Amphenol 12401598E4#2A<br>FTDI FT4232HL-REEL                                | 21             |

| 10      | J308,<br>U99  | USB 2.0 type-A<br>connector, USB<br>ULPI transceiver     | Wurth 629104190121, USB<br>2.0 type-A<br>Microchip USB3320C USB<br>2.0 Xcvr | 37             |

| 11      | J302,<br>U104 | SD card socket,<br>Versal adaptive                       | Molex 5025700893<br>Micro SD card cage                                      | 35             |

| Callout | Ref. Des.     | Feature                                   | Notes                                                                                               | Schematic Page |

|---------|---------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------|

|         |               | SoC SD 3.0 level translator circuit       |                                                                                                     |                |

| 12      | U33           | I2C bus switches                          | Texas Instruments<br>TCA9548APWR<br>IC switch bus 1-In 8-Outs<br>I2C 400 kHz<br>Bottom of board     | 39             |

| 13      | U233          | I2C bus expander                          | Texas Instruments<br>TCA6416APWR<br>IC exp. GPIO 16-bit I2C 400 kHz<br>Bottom of board              | 39             |

| 14      | J392,<br>J393 | CAN bus connectors                        | Phoenix 1935174<br>Conn Term Blk RA 3 Pos<br>1x3 5 mm P 17.5A 250V<br>Green TH 14-26AWG Screw Clamp | 41             |

| 17      | J376          | zSFP+ connector                           | Molex 1703820001<br>zSFP+ connector and cage                                                        | 29             |

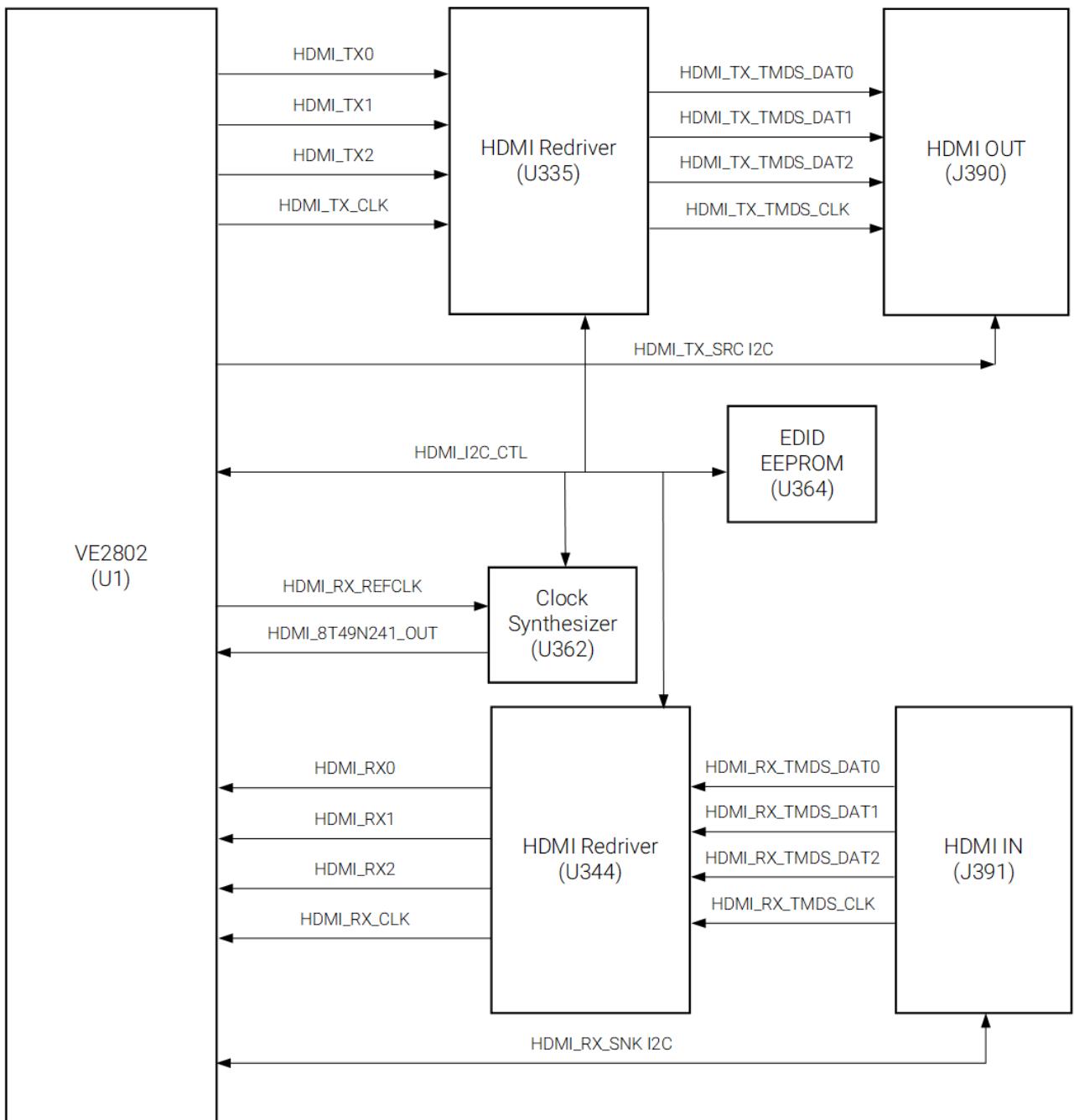

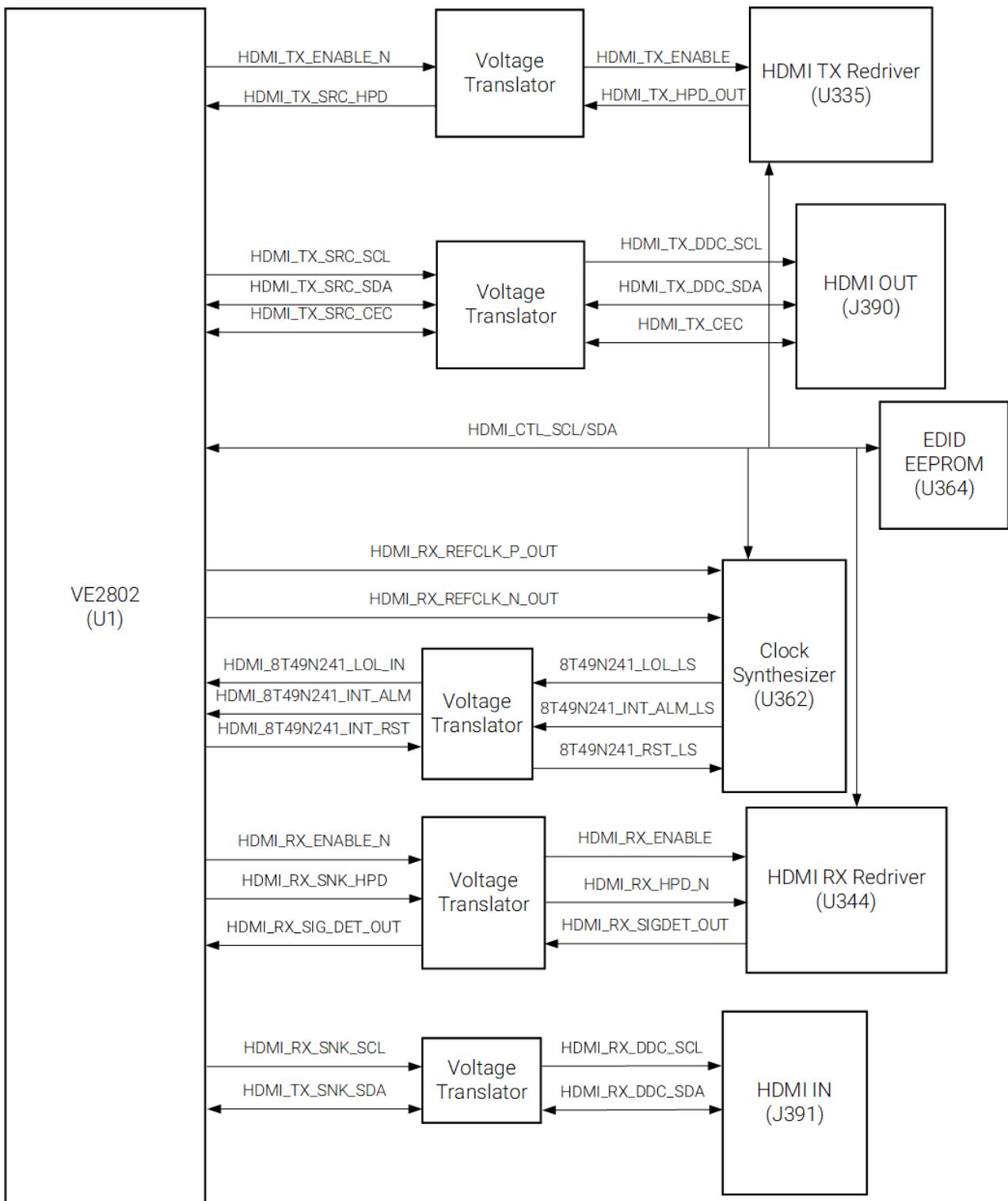

| 18      | J390,<br>J391 | HDMI™ TX and HDMI RX connectors           | Molex 2086581061<br>Conn Rcpt HDMI 2.1 RA                                                           | 44-45          |

| 19      | J307          | GEM0 SGMII Ethernet PHY, 0x01, RJ45 w/mag | Halo HFJ11-1G01E-L12RL<br>RJ-45 Gigabit connector                                                   | 36             |

| 20      | J51           | FMCP1                                     | Samtec ASP-184329-01<br>560 pos. connector 14x40<br>1.27 mm                                         | 30-34          |

| 21      | Various       | Adaptive SoC power management             | Infineon regulators                                                                                 | 51-56          |

| Callout | Ref. Des.  | Feature                      | Notes                                                                | Schematic Page     |

|---------|------------|------------------------------|----------------------------------------------------------------------|--------------------|

|         |            | system (VCCINT, VCC_SOC)     |                                                                      |                    |

| 22      | U160       | VCC_PMC/UTIL_2V5/ regulator  | VCC_PMC/UTIL_2V5/ regulator<br>IC PMU 5-Ch step-down<br>DC/DC        | VCC_PMC/UTIL_2V5/  |

| 23      | U167, U316 | LPDMGTYAVTT/VCCAUX regulator | LPDMGTYAVTT/VCCAUX<br>IC PMU 5-Ch step-down<br>DC/DC                 | LPDMGTYAVTT/VCCAUX |

| 24      | U175       | VCCO_HDIO_3V3/VCCO regulator | VCCO_HDIO_3V3/VCCO<br>IC PMU 5-Ch step-down<br>DC/DC                 | VCCO_HDIO_3V3/VCCO |

| 25      | U279, U292 | VCC1V1_LP4/VCC1V5 regulator  | VCC1V1_LP4/VCC1V5<br>IC PMU 5-Ch step-down<br>DC/DC                  | VCC1V1_LP4/VCC1V5  |

| 26      | U282       | VADJ_FMC regulator           | Infineon IR38060MTRPB<br>F IC V. reg. step-down DC/DC<br>sync        | 66                 |

| 27      | U295       | MGTAVTT regulator            | Infineon<br>IR38164MTRPBFAUMA1<br>IC V. reg. step-down DC/DC<br>sync | 67                 |

| 28      | U354       | UTIL_1V8 regulator           | Infineon IR38060MTRPB<br>F IC REG BUCK ADJ 6A                        | 68                 |

| 29      | U191       | UTIL_3V3 regulator           | Infineon<br>IR3889MTRPBFAUMA1<br>IC V. reg. step-down DC/DC<br>sync  | 69                 |

| 30      | U190       | UTIL_5V0 regulator           | Infineon<br>IR3889MTRPBFAUMA1<br>IC V. reg. step-down DC/DC<br>sync  | 70                 |

| Callout | Ref. Des.   | Feature                                                                      | Notes                                                                       | Schematic Page |

|---------|-------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------|

| 31      | J325        | PMBus 3-pin header                                                           | Sullins PBC03SAAN<br>Conn. hdr. vert. 3 pos. 1x3<br>2.54 mm                 | 55             |

| 32      | Various     | Power good LEDs (see <a href="#">Power and Status LEDs</a> for more details) | Various; see the Bill of Materials                                          | 72             |

| 33      | J16         | Power connector, 2x3, for AC-DC power adapter                                | Molex 0039301060<br>Conn. ddr. RA 6 pos. 2x3<br>4.2 mm                      | 50             |

| 34      | JP1,<br>JP2 | Power connector, 2x4, for ATX PCIe power                                     | Astron 6652208-T0003T-H<br>Conn. hdr. male RA 8 pos.<br>2x4 4.2 mm          | 50             |

| 35      | J233        | Fan header (keyed 4-pin)                                                     | Molex 0470533000<br>Keyed fan header 4 pos.<br>0.100" vert.                 | 50             |

| 36      | U299        | MGT and system clock generators                                              | Renesas<br>RC21008A065GND#BB0                                               | 93             |

| 37      | J374        | RC21008A_GTCLK header                                                        | Molex 0878321820                                                            | 93             |

| 38      | U297        | Adaptive SoC U1 OSPI                                                         | Micron<br>MT35XU02GCBA1G12-0SIT<br>IC flash Xccela 2 Gb SPI<br>200 MHz 1.8V | 28             |

| 39      | DS1         | Done LED (Active-High-Z and pulled High)                                     | Lumex SML-LX0603GW-TR<br>LED green                                          | 12             |

| 40      | DS2         | Error out LED (Active-High-Z and pulled High)                                | Lumex SML-LX0603IW-TR<br>LED red                                            | 12             |

| Callout | Ref. Des.                   | Feature                                             | Notes                                                                              | Schematic Page |

|---------|-----------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------|----------------|

| 41      | DS3,<br>DS4,<br>DS5,<br>DS6 | User LEDS                                           | Lumex SML-LX0603GW-TR<br>LED green                                                 | 48             |

| 42      | J405                        | IEEE-1588 eCPRI<br>CLK in SMA                       | Rosenberger 32K10K-<br>400L5<br>Conn. rcpt. SMA vert. 50R<br>12.4 GHz              | 92             |

| 43      | J331                        | IEEE-1588 eCPRI<br>CLK out SMA                      | Rosenberger 32K10K-<br>400L5<br>Conn. rcpt. SMA vert. 50R<br>12.4 GHz              | 92             |

| 44      | U125                        | XCZU4EG system<br>controller                        | AMD XCZU4EG-2SFVC784E<br>AMD Zynq™ UltraScale+™<br>MPSoC                           | 73-83          |

| 45      | U301                        | SYSCTRLR<br>clock156.25 MHz<br>HSDP REFCLK          | CTS 626L15625I3T<br>Osc 156.25 MHz 3.3V 25<br>PPM LVDS with OE                     | 89             |

| 46      | U302                        | SYSCTRLR clock<br>33.33 MHz<br>REFCLK               | Renesas<br>XUJ716033.33333I<br>Osc 33.333333 MHz 1.8V<br>25 PPM LVCMOS with OE     | 89             |

| 47      | U304                        | SYSCTRLR clock 26<br>MHz USB REFCLK                 | Raltron XC0583IV11-<br>26.000<br>Osc 26 MHz 3.3V 30 PPM<br>LVDS with OE            | 89             |

| 48      | U132                        | System controller<br>LPDDR4 16 GBIT<br>comp. memory | Micron<br>MT53E512M32D1ZW-046<br>WT:D<br>IC SDRAM LPDDR4 16 Gb<br>512Mx32 2133 MHz | 86             |

| Callout                                                                                   | Ref. Des. | Feature                                                  | Notes                                             | Schematic Page |

|-------------------------------------------------------------------------------------------|-----------|----------------------------------------------------------|---------------------------------------------------|----------------|

| 49                                                                                        | J349      | System controller<br>SGMII Ethernet,<br>RJ45 w/magnetics | Halo HFJ11-1G01E-L12RL<br>RJ-45 Gigabit connector | 84             |

| 50                                                                                        | DS34      | System controller<br>done LED (active-High)              | Lumex SML-LX0603GW-TR<br>LED green                | 77             |

| 1. The VEK280 evaluation board includes a heatsink with a thermal resistance of 0.46°C/W. |           |                                                          |                                                   |                |

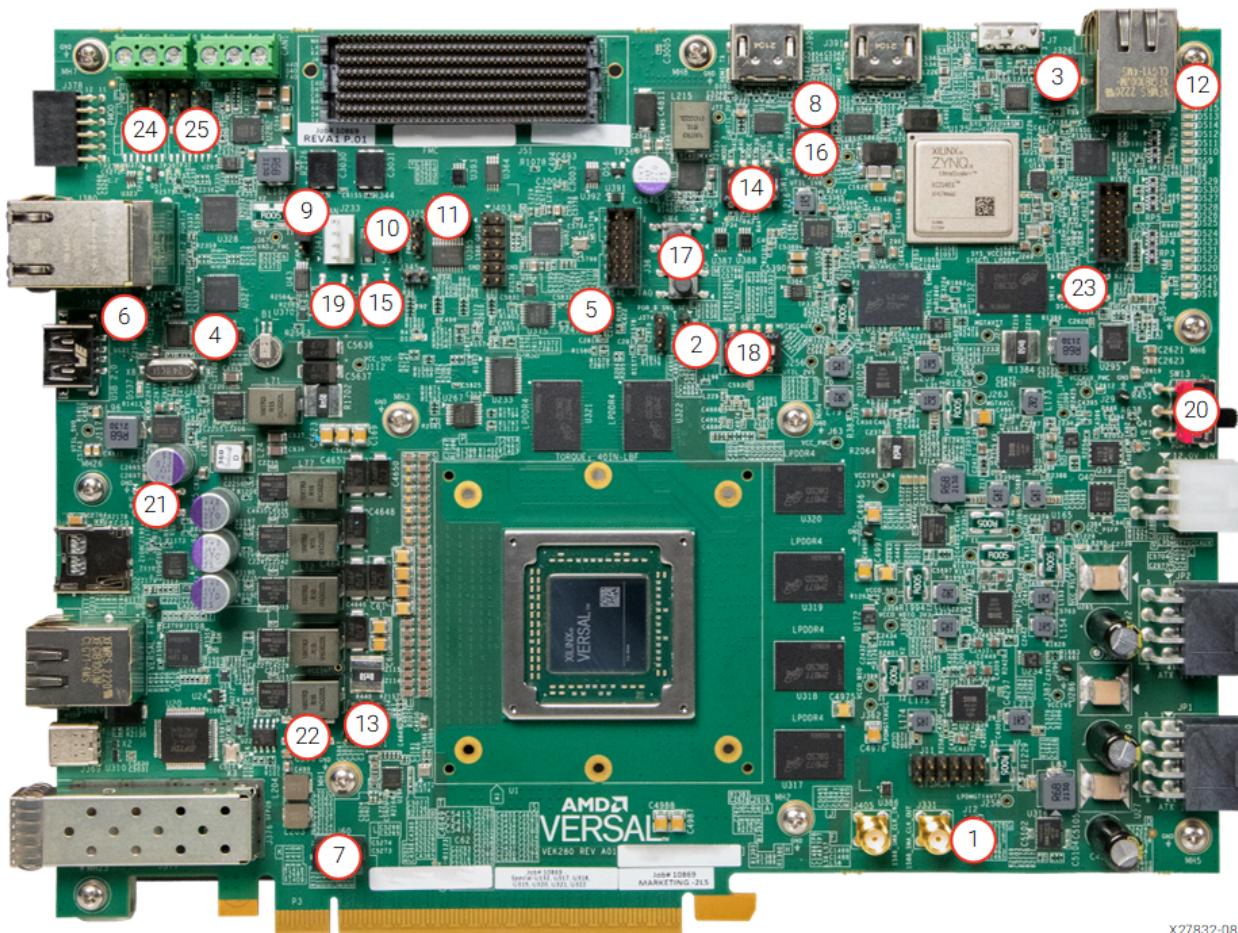

## Default Jumper and Switch Settings

The following figure shows the VEK280 board jumper header and switch locations. Each numbered component shown in the figure is keyed to the applicable table in this section. Both tables reference the respective schematic page numbers.

**Figure: Board Jumper Header and Switch Locations**

00 Round callout references a component on the front side of the board

00 Square callout references a component on the back side of the board

X27832-081123

## Jumpers

The following table lists the default jumper settings.

**Table: Default Jumper Settings**

| Callout | Ref Des. | Function                                                                                                   | Default              | Schematic Page |

|---------|----------|------------------------------------------------------------------------------------------------------------|----------------------|----------------|

| 1       | J12      | SYSMON VREFP SEL<br>1-2: External VREF<br>2-3: Disable external VREF                                       | 1-2                  | 10             |

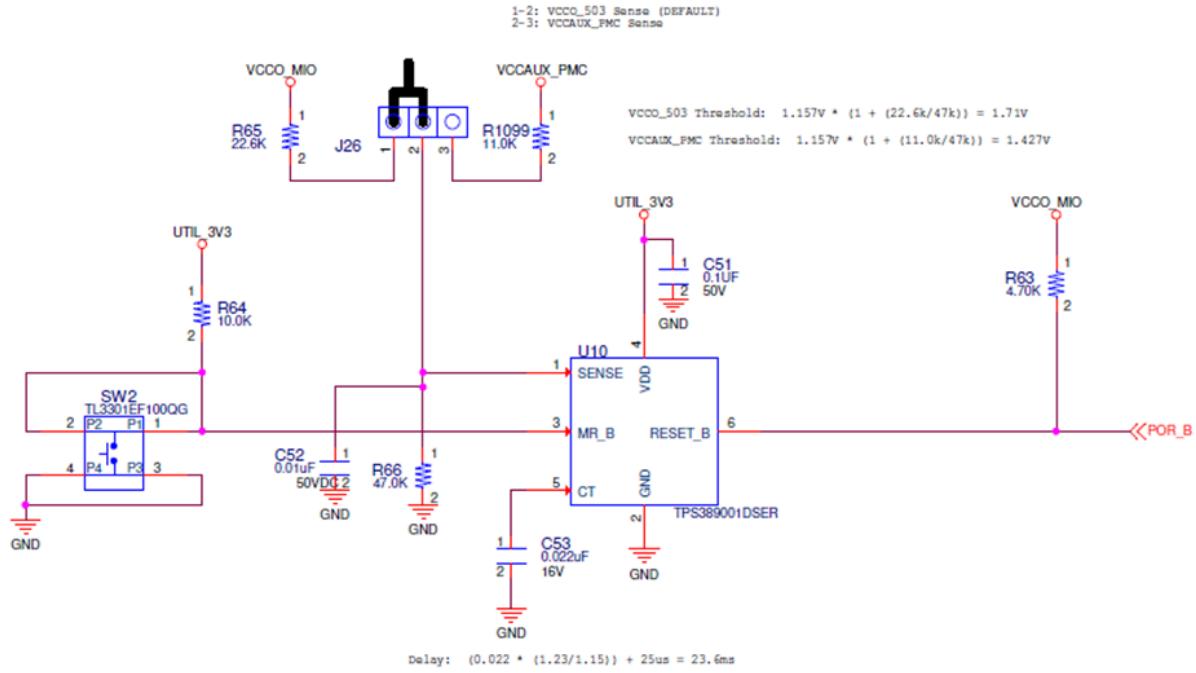

| 2       | J26      | POR_B supervisor SENSE input<br>1-2: VCCO_MIO ramp-up sense (1.8V)<br>2-3: VCCAUX_PMC ramp-up sense (1.5V) | 2-3                  | 13             |

| 3       | J326     | POR_B enable header<br>1-2: SYSCTRL can drive POR_B                                                        | 1-2, 3-4<br>jumpered | 13             |

| Callout | Ref Des. | Function                                                                                                            | Default            | Schematic Page |

|---------|----------|---------------------------------------------------------------------------------------------------------------------|--------------------|----------------|

|         |          | 3-4: PC4 can drive POR_B<br>5-6: FTDI can drive POR_B<br>Open: POR_B source not connected                           | 5-6 open           |                |

| 4       | J34      | VCC Fuse programming enable<br>1-2: Fuse programming enabled<br>2-3: Fuse programming disabled                      | 2-3                | 15             |

| 5       | J37      | JTAG source enable<br>1-2: JTAG sources disabled<br>2-3: JTAG sources enabled                                       | 2-3                | 20             |

| 6       | J300     | USB shield GND<br>1-2: USB connector DC grounded<br>2-3: USB connector no DC grounded                               | 1-2                | 37             |

| 7       | J60      | PCIe PRSNT_B WIDTH SEL<br>1-2: x1<br>3-4: x4<br>5-6: x8<br>7-8: x16                                                 | 1-2, 3-4, 5-6, 7-8 | 40             |

| 8       | J203     | SYSCTRL POR_B supervisor enable<br>1-2: SYSCTRL POR_B supervisor enabled<br>Open: SYSCTRL POR_B supervisor disabled | 1-2                | 77             |

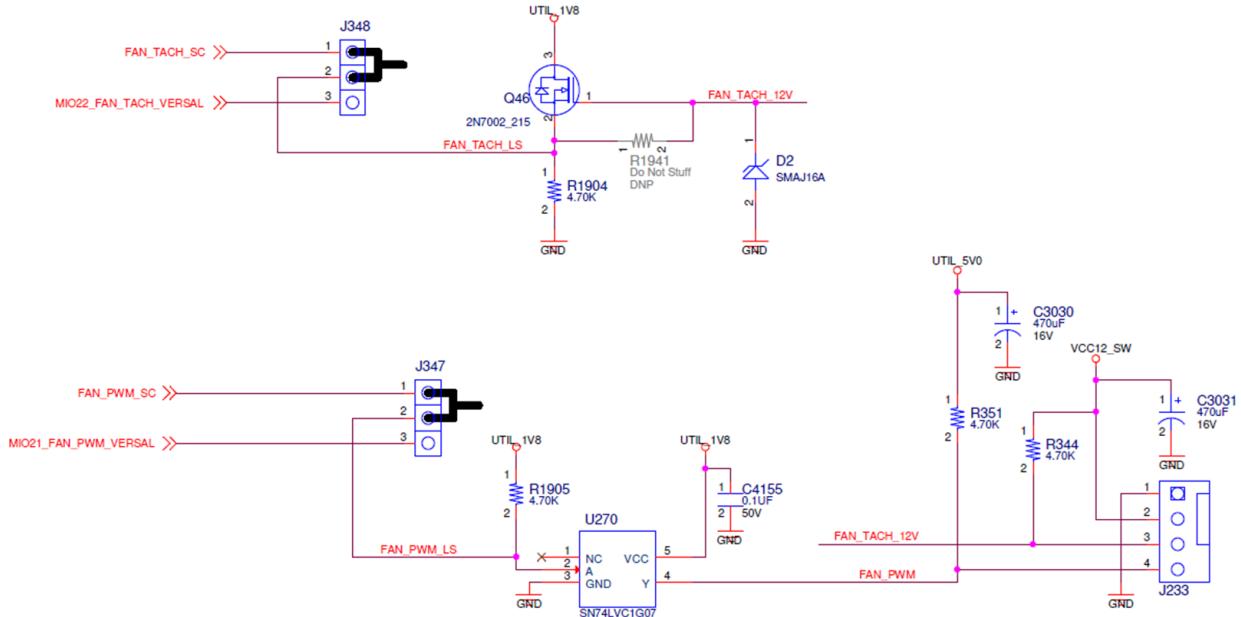

| 9       | J347     | Fan type<br>1-2: System controller PWM<br>2-3: Versal device MIO PWM                                                | 1-2                | 50             |

| 10      | J348     | TACH type<br>1-2: System controller TACH<br>2-3: Versal device MIO TACH                                             | 1-2                | 50             |

| 11      | J406     | MIO37 selection<br>1-2: ZU4_TRIGGER<br>2-3: CANFD0_INH_B                                                            | 1-2                | 10             |

| Callout | Ref Des.      | Function                                                | Default   | Schematic Page |

|---------|---------------|---------------------------------------------------------|-----------|----------------|

| 12      | J407          | SYSCTRL JTAG mode<br>Default: QSPI32<br>Installed: JTAG | DNP       | 77             |

| 13      | J400,<br>J401 | SFP RS0/1 input<br>1-2: Full BW RX<br>2-3: Low BW Rx    | Open      | 29             |

| 24      | J395,<br>J396 | CAN0 termination option                                 | Installed | 41             |

| 25      | J398,<br>J397 | CAN1 termination option                                 | Installed | 41             |

## Switches

The following table lists the default switch settings.

**Table: Default Switch Settings**

| Callout | Ref Des. | Function                                                                                                                                                                                 | Default           | Schematic Page |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|

| 14      | SW1      | U1 mode 4-pole DIP switch<br>Switch OFF = 1 = high; ON = 0 = low<br>Mode = SW1[1:4] = Mode[0:3]<br>SD = ON,OFF,OFF,OFF = 0111<br>OSPI = ON,ON,ON,OFF = 0001<br>JTAG = ON,ON,ON,ON = 0000 | ON, ON,<br>ON, ON | 12             |

| 15      | SW2      | VEK280 power-on reset (POR_B)                                                                                                                                                            | Open              | 13             |

| 16      | SW3      | SYSCTRL JTAG source selection<br>Switch OFF = 1 = high; ON = 0 = low<br>SYSCTRL JTAG SOURCE SEL = SW3[1:2] = SEL[0:1]<br>PL JTAG = ON,ON = 00<br>FTDI JTAG = OFF,ON = 10                 | OFF, ON           | 20             |

| Callout Number | Ref Des.    | Function                                                                                                                                                                                 | Default               | Schematic Page |

|----------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------|

| 17             | SW4,<br>SW5 | User pushbutton inputs<br><br> <b>Note:</b> Pushbutton switch default = open = logic low (not pressed). | Open                  | 48             |

| 18             | SW6         | User GPIO DIP<br>Switch OFF = 0 = low; ON = 1 = high                                                                                                                                     | OFF, OFF,<br>OFF, OFF | 48             |

| 19             | SW12        | System controller power-on reset (SYSCTL_POR_B)                                                                                                                                          | Open                  | 77             |

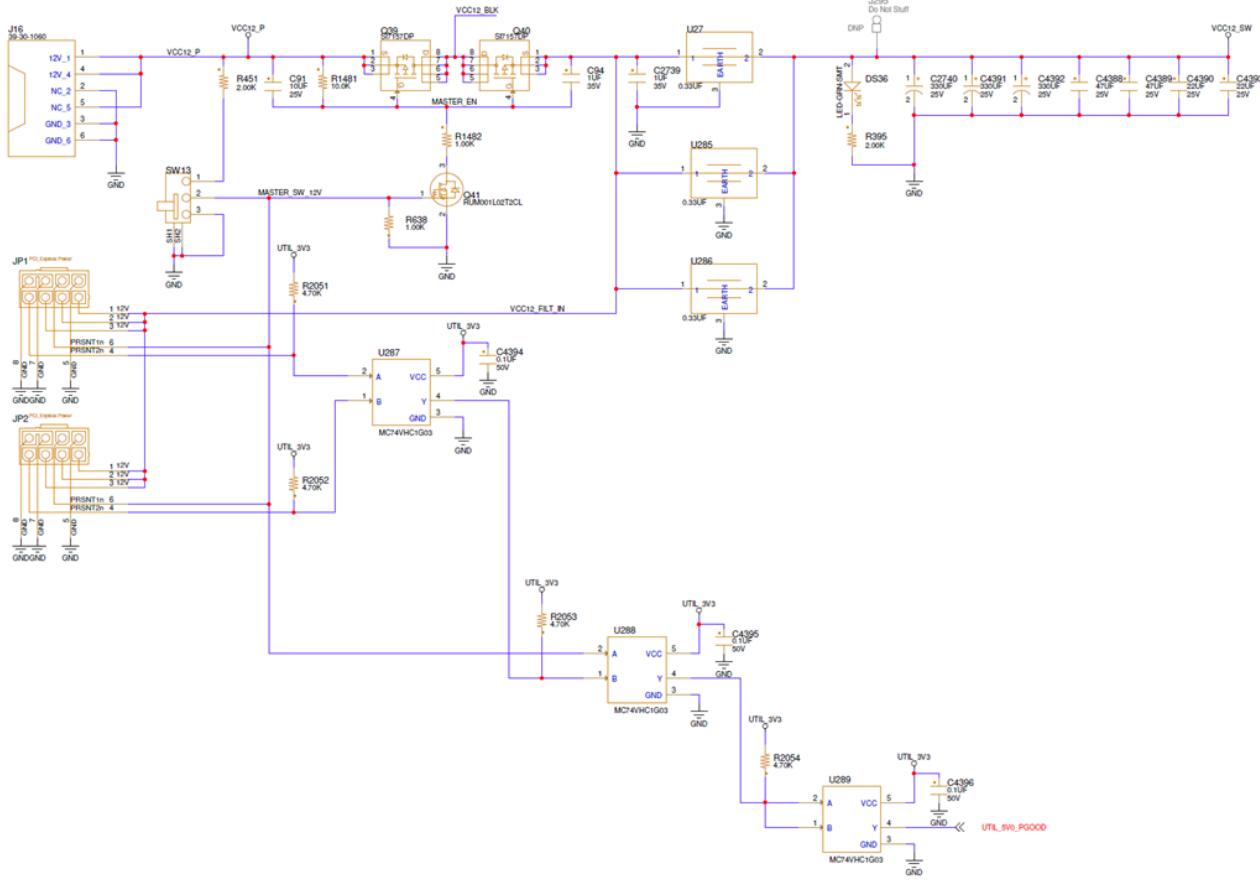

| 20             | SW13        | Main power                                                                                                                                                                               | OFF                   | 50             |

| 21             | SW14        | User USB reset                                                                                                                                                                           | Open                  | 37             |

| 22             | SW15        | User GEM reset                                                                                                                                                                           | Open                  | 36             |

| 23             | SW16        | System controller FWUEN pushbutton (SYSCTRLR_MIO12_FWUEN_C2M_B)<br>See BEAM wiki for more information                                                                                    | Open                  | 76             |

## Versal Device Configuration

The “Platform Boot, Control, and Status” section of the *Versal Adaptive SoC Technical Reference Manual (AM011)* describes the Versal XCVE2802 device boot process. The VEK280 board supports a subset of the modes documented in the technical reference manual via onboard boot options. The mode DIP switch SW1 configuration option settings are listed in the following table.

**Table: Mode Switch SW1 Configuration Option Settings**

| Boot Mode | Mode Pins [0:3] <sup>2</sup> | Mode SW1 [1:4] <sup>2</sup> |

|-----------|------------------------------|-----------------------------|

| JTAG      | 0000 <sup>1,3</sup>          | ON, ON, ON, ON              |

| OSPI      | 0001                         | ON, ON, ON, OFF             |

| Boot Mode    | Mode Pins [0:3] <sup>2</sup> | Mode SW1 [1:4] <sup>2</sup> |

|--------------|------------------------------|-----------------------------|

| SD1 (SD 3.0) | 0111                         | ON, OFF, OFF, OFF           |

1. Default switch setting.

2. Mode DIP SW1 poles [1:4] correspond to U1 XCVE2802 MODE[0:3].

3. Mode DIP SW1 individual switches ON=LOW (p/d to GND)=0, OFF=HIGH (p/u to VCCO)=1.

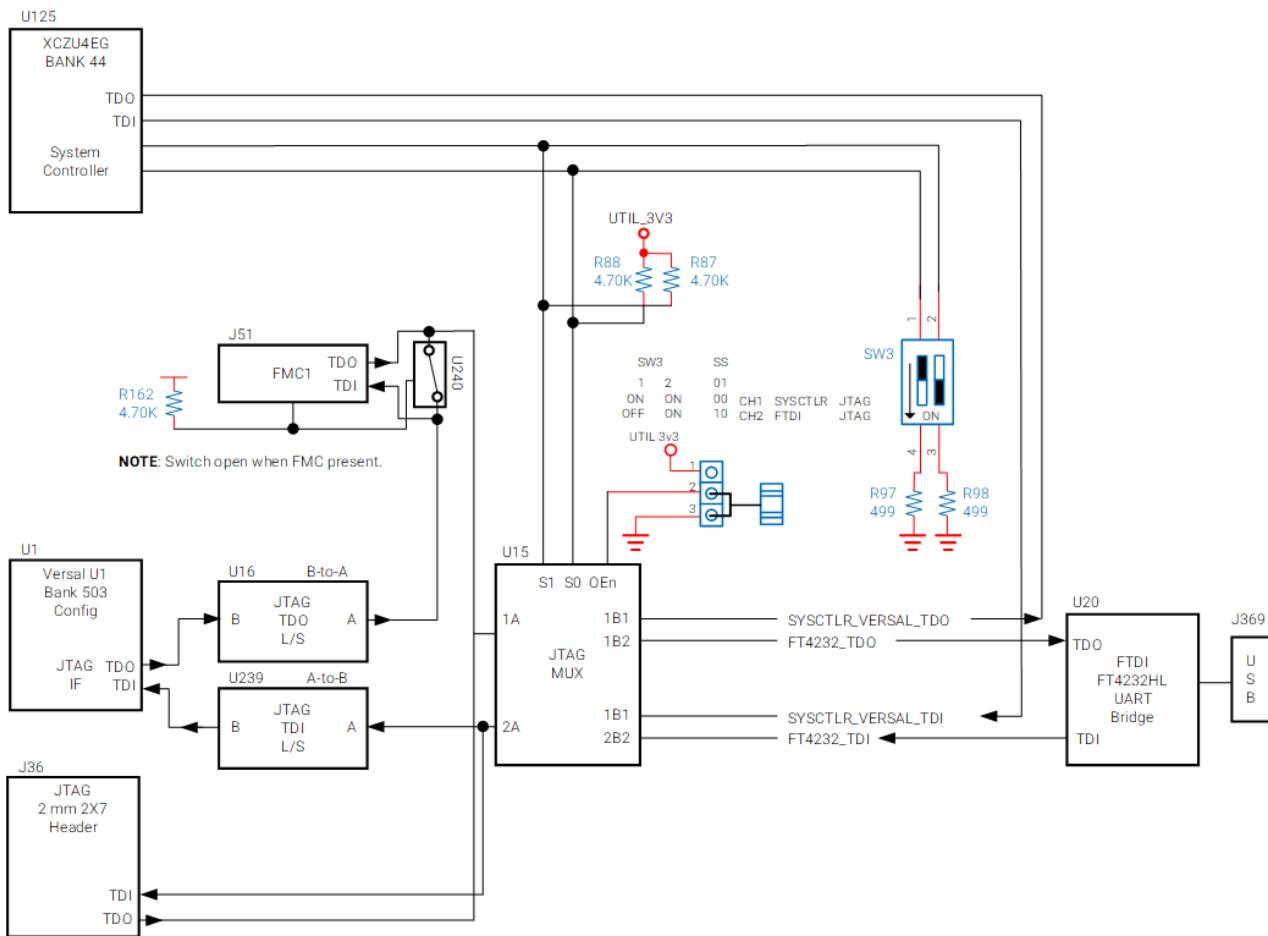

## JTAG

The AMD Vivado™, AMD SDK, or third-party tools can establish a JTAG connection to the Versal device in the two ways described in this section.

- FTDI FT4232 USB-to-JTAG/USB-UART device (U20) connected to USB 2.0 type-C connector (J369), which requires:

- Set boot mode SW1 for JTAG as indicated in the "Mode Switch SW1 Configuration Option Settings" table in [Versal Device Configuration](#).

- On the 3-pin JTAG MUX, enable header J37 to enable the JTAG MUX. Move the 2-pin jumper to be installed on pins 2-3. See [Default Jumper and Switch Settings](#) for defaults and [Board Component Location](#) for location.

- Set 2-pole DIP SW3[1:2] set to 10 (OFF, ON) for JTAG MUX channel 2 FT4232 U20 bridge.

- Power-cycle the VEK280 evaluation board or press the power-on reset (POR) pushbutton (SW2). SW2 is near the USB-C JTAG port J369 in the figure in [Board Component Location](#)).

- JTAG pod flat cable connector J36 (2 mm 2x7 shrouded/keyed), which requires:

---

**Note:** In this mode, the FT4232 device (U20) UART functionality continues to be available.

---

- Set boot mode SW1 for JTAG as indicated in the "Mode Switch SW1 Configuration Option Settings" table in [Versal Device Configuration](#).

- On the 3-pin JTAG MUX, enable header J37 to inhibit the JTAG MUX. Move the 2-pin jumper to be installed on pins 1-2 for high-z mode. See [Default Jumper and Switch Settings](#) for defaults and [Board Component Location](#) for location.

- 2-pole DIP SW3[1:2] setting does not matter as the MUX is inhibited/turned off.

- Power-cycle the VEK280 board or press the power-on reset pushbutton (SW2). SW2 is near the USB-C JTAG port J369 in the figure in [Board Component Location](#).

## OSPI

This boot mode is supported onboard and is wired to the XCVE2802 U1 bank 500 PMC\_MIO[0:12] pins. The octal SPI controller can access two devices using several different methods. See the Flash Memory Controllers section of the *Versal Adaptive SoC Technical Reference Manual (AM011)* for more information. To boot from OSPI:

1. Store a valid XCVE2802 adaptive SoC boot image file in the OSPI.

2. Set boot mode SW1 for OSPI as indicated in the "Mode Switch SW1 Configuration Option Settings" table in [Versal Device Configuration](#).

3. Power-cycle the VEK280 board or press the POR pushbutton SW2. SW2 is near the USB-C JTAG port J369 in the figure in [Board Component Location](#).

## SD1\_3.0

To boot from a SD card installed in microSD card socket J302:

1. Store a valid XCVE2802 device boot image file on a microSD card. Plug the SD card into the VEK280 evaluation board SD socket J302 connected to the XCVE2802 U1 bank 501 MIO SD interface.

2. Set boot MODE SW1 for SD1\_3.0 as indicated in the table in [Versal Device Configuration](#).

3. Power-cycle the VEK280 board or press the POR pushbutton SW2. SW2 is near the USB-C JTAG port J369 in the figure in [Board Component Location](#).

# Board Component Descriptions

## Overview

This chapter provides a detailed functional description of the board's components and features. The "Board Component Locations" table in [Board Component Descriptions](#) identifies the components and references the respective schematic page numbers. Component locations are shown in the "Evaluation Board Component Locations" figure in [Board Component Location](#).

## Component Descriptions

### Versal Device

[[Figure 1](#), callout 1]

The VEK280 evaluation board is populated with the AMD Versal™ XCVE2802-2MSEVSVH2802 device, which combines a powerful processing system (PS) and programmable logic (PL) in the same device. The PS in a Versal device features the Arm® flagship Cortex®-A72 64-bit dual-core processor and Cortex-R5F dual-core real-time processor. For additional information on the Versal XCVE2802-2MSEVSVH2802 device, see the *Versal Premium Series Data Sheet: DC and AC Switching Characteristics (DS959)*. See the *Versal Adaptive SoC Technical Reference Manual (AM011)* for more information about Versal device configuration options.

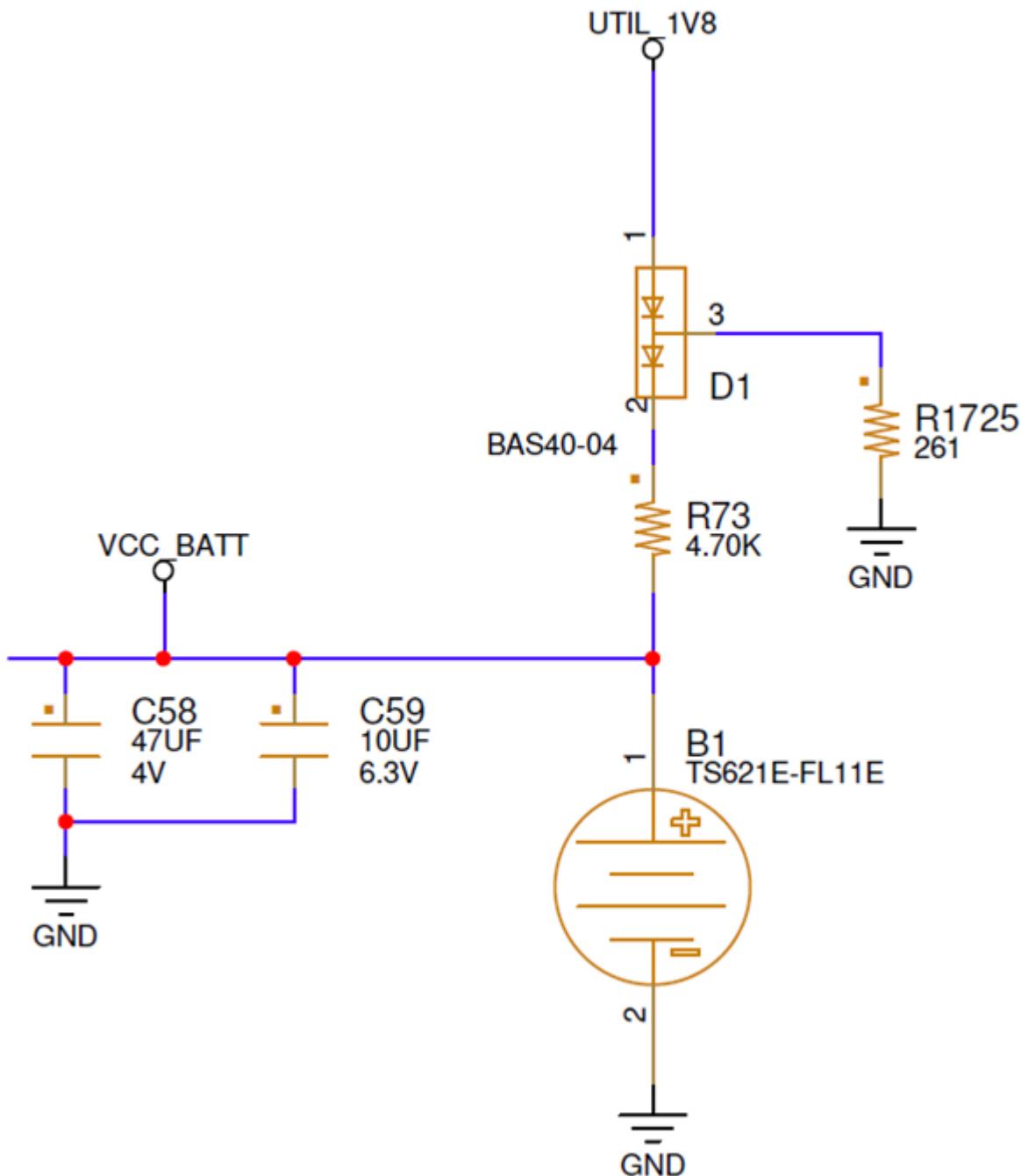

### Encryption Key Battery Backup Circuit

The XCVE2802 device U1 implements bitstream encryption key technology. The VEK280 board provides the encryption key backup battery circuit shown in the following figure.

### Figure: Encryption Key Backup Circuit

X27818-022223

The Seiko TS621E rechargeable 1.5V lithium button-type battery B1 is soldered to the board with the positive output connected to the XCVE2802 device U1 VCC\_BATT bank pin AN20. The battery supply current IBATT specification is 150 nA maximum when board power is off. Battery B1 is charged from the VCC1V8 1.8V rail through a 2 series diode with the first forward drop to yield between 0.24V to 0.46V over temperature per fixed 5 mA load, R1725, and limiting 1.56V max at the device pin, PSVBATT. The second diode and 4.7 kΩ current limit resistor allows the battery to trickle charge and prevent battery B1 from back powering R1725.

## I/O Voltage Rails

The XCVE2802 device PL I/O bank voltages on the VEK280 board are listed in the following table.

---

**!! Important:** See [LPD MIO\[23\]: VADJ\\_FMC Power Rail](#) for more details on the VADJ\_FMC power rail.

---

**Note:** See the *Versal Premium Series Data Sheet: DC and AC Switching Characteristics* (DS959) for more information. See the *Versal Adaptive SoC Technical Reference Manual* (AM011) for more information about Versal device configuration options.

---

**Table: I/O Voltage Rails**

| Versal Device (UPI) Bank | Supply Rail           | Voltagename | Description                                                                                                                                 |

|--------------------------|-----------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| XPIO Bank 700            | VCC1V1_LP4            | 1.1V        | LPDDR4 TRIP1 CH0                                                                                                                            |

| XPIO Bank 701            | VCC1V1_LP4            | 1.1V        | LPDDR4 TRIP1 CH1                                                                                                                            |

| XPIO Bank 702            | VCC1V5_LP4            | 1.5V        | LPDDR4 TRIP1 CH0/1 reset, HDMI control signals, GPIO LEDs                                                                                   |

| XPIO Bank 703            | VCC1V1_LP4            | 1.1V        | LPDDR4 TRIP2 CH0                                                                                                                            |

| XPIO Bank 704            | VCC1V1_LP4            | 1.1V        | LPDDR4 TRIP2 CH1                                                                                                                            |

| XPIO Bank 705            | VADJ_FMC <sup>1</sup> | 1.5V        | LPDDR4 TRIP2 CH0/1 reset, HDMI control signals, GPIO DIP,PB0/1, SYSCTRL GPIO[0:7], SYS_CLK_1, FMCP1_LA[00:01]_CC, FMCP1_LA[02:16],FMCP_CLK0 |

| XPIO Bank 706            | VADJ_FMC <sup>1</sup> | 1.5V        | FMCP1_SYNC_M2C/C2M, LPDDR4 TRIP3 CH0/1 reset, SYS_CLK_2, 1588_GPIO[0:5], FMCP1_REFCLK_C2M, FMCP1_LA[17:18]_CC,                              |

| Versal Device (Up) Bank & Supply Rail                                                                                                     | Bank Name     | Volts             | Description                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                           |               |                   | FMCP1_LA[19:33],<br>FMCP1_CLK1_M2C                                                                                                             |

| XPIO Bank 707                                                                                                                             | VCC1V1_LP4    | 1.1V              | LPDDR4 TRIP3 CH1                                                                                                                               |

| XPIO Bank 708                                                                                                                             | VCC1V1_LP4    | 1.1V              | LPDDR4 TRIP3 CH0                                                                                                                               |

| XPIO Bank 400                                                                                                                             | VCCO_HDIO_3V3 | 3.3V<br>(default) | PL_GEM0 MDIO/MDC,<br>PMOD_IO[0:7], PL_GEM0_RX/TX                                                                                               |

| XPIO Bank 401                                                                                                                             | VCCO_HDIO_3V3 | 3.3V<br>(default) | PL_GEM1_MDIO/MDC,<br>PL_GEM[0:1]_RST, SFP_TX_FAULT,<br>SFP_RX_LOS, UART1_TXD/RXD,<br>SYSCTRL_UART0, PL_GEM1_RX/TX                              |

| PMC MIO 500                                                                                                                               | VCCO_MIO      | 1.8V              | SYSMON, USB ULPI 2.0 interface,<br>OSPI interface                                                                                              |

| PMC MIO 501                                                                                                                               | VCCO_MIO      | 1.8V              | SD bus power, PCIe controls,<br>I2C0/21, UART0, CAN0_nSTB,<br>System Controller I2C/[trigger OR<br>CANFD0_INH], SD card controls,<br>GEM reset |

| LPD MIO 502                                                                                                                               | VCCO_502      | 1.8V              | GEM interface/controls, power<br>enables, PCIe PERST, fan tach, fan<br>PWM                                                                     |

| 1. The VEK280 board is shipped with VADJ_FMC set to 1.5V. This value<br>cannot be changed. Care must be taken when using FMC accessories. |               |                   |                                                                                                                                                |

See [LPD MIO\[23\]: VADJ\\_FMC Power Rail](#) for more details.

## LPDDR4 Component Memory

[[Figure 1](#), callout 2, 3, 4]

The VEK280 XCVE2802 device PL DDR memory interface performance is documented in the *Versal Premium Series Data Sheet: DC and AC Switching*

**Characteristics (DS959).** The VEK280 board LPDDR4 component memory interfaces adhere to the constraints guidelines documented in the "PCB guidelines for Memory Interfaces" section of the *Versal Adaptive SoC PCB Design User Guide (UG863)*. The VEK280 DDR4 component interface is a 40Ω impedance implementation. Other memory interface details are also available in the *Versal Adaptive SoC Memory Resources Architecture Manual (AM007)*. For more memory component details, see the Micron MT53E512M32D1ZW data sheet on the [Micron](#) website. For the most current part number, see the Bill of Materials (BOM) located on the [VEK280 Evaluation Board](#) website. The detailed device connections for the feature described in this section are documented in the VEK280 board XDC file, referenced in [Xilinx Design Constraints](#).

The VEK280 evaluation board hosts three LPDDR4 memory systems, each with a component configuration of 2x (1x32-bit component).

**Figure: LPDDR4 Component Memory**

X26003-080522

XCVE2802 U1 has been configured with three triplet banks.

- XPIO triplet 1 (banks 700/701/702)

- XPIO triplet 2 (banks 703/704/705)

- XPIO triplet 3 (banks 706/707/708)

Each support two independent 32-bit 2 GB component interfaces (4 GB per triplet). The VEK280 evaluation board uses the LPDDR4 memory components as follows:

- Manufacturer: Micron

- Part number: MT53E512M32D1ZW-046 WT:B (dual die LPDDR4 SDRAM)

- Component description

- 16 Gb (512 Mb x 32)

- 1.1V 200-ball TFBGA

- LPDDR4-2133

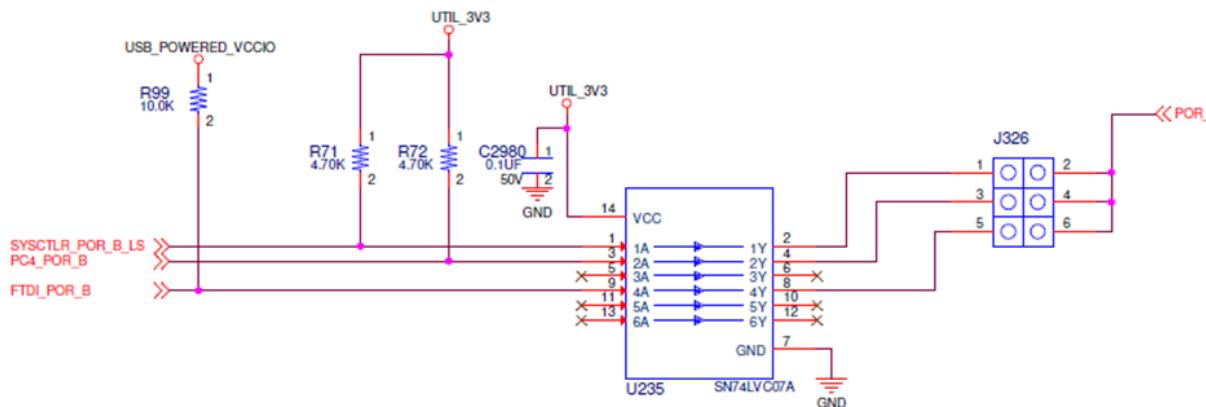

## System Reset POR\_B

[Figure 1, callout 2]

POR\_B is the Versal device processor reset, which can be controlled by:

- SYSCTRL (U125)

- PC4 header (J36)

- FTDI USB JTAG chip (U20)

The VEK280 board POR circuit is shown in the following figure. U235 allows directional open drain level shifting for all of these masters, and J326 allows them to be bused together if desired. The TPS389001 U10 supervisor chip holds POR\_B off until power is valid.

### Figure: POR\_B Reset Circuit

## PMC and LPD MIO

The following sections provide the MIO peripheral mapping implemented on the VEK280 evaluation board. See the *Versal Adaptive SoC Technical Reference Manual (AM011)* for more information on MIO peripheral mapping. Additional signal connectivity can be located in the following schematic sections:

- Bank 500: See schematic page 10

- Bank 501: See schematic page 10

- Bank 502: See schematic page 11

The following table provides MIO peripheral mapping implemented on the VEK280 evaluation board. The Versal device bank 500, 501, and 502 mappings are listed in the following table.

**Table: MIO Peripheral Mapping**

| Bank | MIO #                       | Device | Signal                   | I/O                         | Notes |

|------|-----------------------------|--------|--------------------------|-----------------------------|-------|

| 500  | 0                           | OSPI   | PMC_MIO0_OSPI_CLK        | O                           |       |

|      | 1                           |        | PMC_MIO1_OSPI_DQ0        | I/O                         |       |

|      | 2                           |        | PMC_MIO2_OSPI_DQ1        | I/O                         |       |

|      | 3                           |        | PMC_MIO3_OSPI_DQ2        | I/O                         |       |

|      | 4                           |        | PMC_MIO4_OSPI_DQ3        | I/O                         |       |

|      | 5                           |        | PMC_MIO5_OSPI_DQ4        | I/O                         |       |

|      | 6                           |        | PMC_MIO6_OSPI_DQS        | I/O                         |       |

|      | 7                           |        | PMC_MIO7_OSPI_DQ5        | I/O                         |       |

|      | 8                           |        | PMC_MIO8_OSPI_DQ6        | I/O                         |       |

|      | 9                           |        | PMC_MIO9_OSPI_DQ7        | I/O                         |       |

|      | 10                          |        | PMC_MIO10_OSPI0_CS_BO    |                             |       |

| 11   | Regulator<br>Enable<br>GPIO |        | PMC_MIO11_VCC_AUX_102_EN | See <a href="#">Table 1</a> |       |

| 12   | OSPI                        |        | PMC_MIO12_OSPI_RST_BO    |                             |       |

| 13   | USB                         |        | PMC_MIO13_USB_RST_BO     |                             |       |

| 14   |                             |        | PMC_MIO14_USB_DAT0       | I/O                         |       |

| 15   |                             |        | PMC_MIO15_USB_DAT1       | I/O                         |       |

| 16   |                             |        | PMC_MIO16_USB_DAT2       | I/O                         |       |

| 17   |                             |        | PMC_MIO17_USB_DAT3       | I/O                         |       |

| Bank | MIO # | Device                                                    | Signal               | I/O | Notes                                    |

|------|-------|-----------------------------------------------------------|----------------------|-----|------------------------------------------|

|      | 18    |                                                           | PMC_MIO18_USB_CLKOU0 |     |                                          |

|      | 19    |                                                           | PMC_MIO19_USB_DAT4   | I/O |                                          |

|      | 20    |                                                           | PMC_MIO20_USB_DAT5   | I/O |                                          |

|      | 21    |                                                           | PMC_MIO21_USB_DAT6   | I/O |                                          |

|      | 22    |                                                           | PMC_MIO22_USB_DAT7   | I/O |                                          |

|      | 23    |                                                           | PMC_MIO23_USB_DIR    | I/O |                                          |

|      | 24    |                                                           | PMC_MIO24_USB_STP    | O   |                                          |

|      | 25    |                                                           | PMC_MIO25_USB_NXT    | I/O |                                          |

| 501  | 26    | SD                                                        | PMC_MIO26_SD_CLK     | O   |                                          |

|      | 27    |                                                           | PMC_MIO27_SD_DIR1    | O   |                                          |

|      | 28    |                                                           | PMC_MIO28_SD_DET     | I   |                                          |

|      | 29    |                                                           | PMC_MIO29_SD_CMD     | I/O |                                          |

|      | 30    |                                                           | PMC_MIO30_SD_DAT0    | I/O |                                          |

|      | 31    |                                                           | PMC_MIO31_SD_DAT1    | I/O |                                          |

|      | 32    |                                                           | PMC_MIO32_SD_DAT2    | I/O |                                          |

|      | 33    |                                                           | PMC_MIO33_SD_DAT3    | I/O |                                          |

|      | 34    |                                                           | PMC_MIO34_SD_SEL     | I/O |                                          |

|      | 35    |                                                           | PMC_MIO35_SD_DIR_CMD |     |                                          |

|      | 36    |                                                           | PMC_MIO36_SD_DIR0    | O   |                                          |

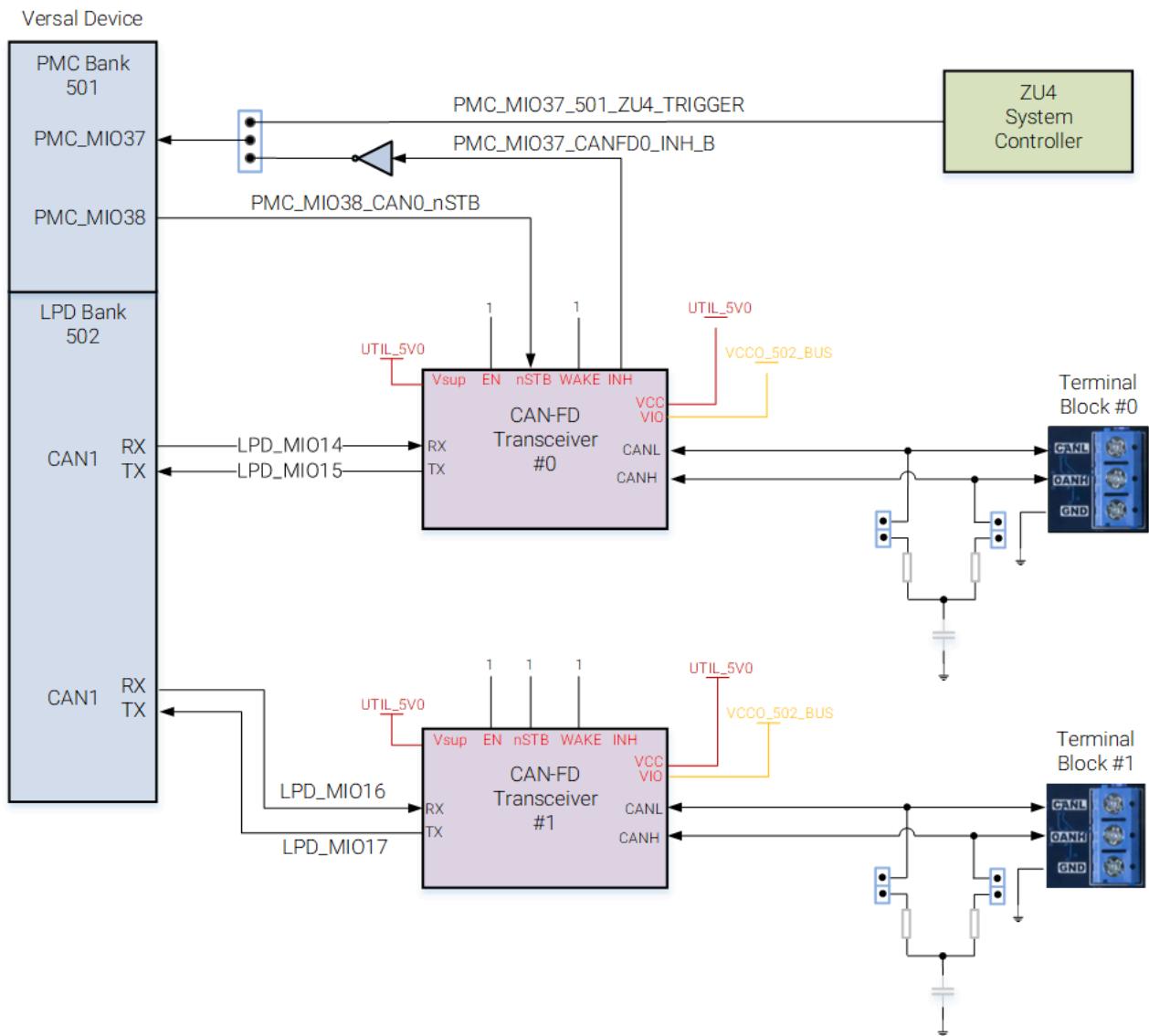

|      | 37    | Factory/CANFD0_INH_B<br>See <a href="#">CAN Interface</a> | PMC_MIO37_COMBINED   | I/O | Selectable J406,<br>Factory/CANFD0_INH_B |

|      | 38    | CANFD0                                                    | PMC_MIO38_CAN0_nSTBO |     | Standby mode<br>control input            |

| Bank | MIO # | Device                | Signal                     | I/O | Notes                       |

|------|-------|-----------------------|----------------------------|-----|-----------------------------|

|      |       | See CAN Interface     |                            |     |                             |

|      | 39    | SYSMON I2C            | PMC_MIO39_SYSMON_I2O_SCL   |     |                             |

|      | 40    |                       | PMC_MIO40_SYSMON_I2O_SDA   |     |                             |

|      | 41    |                       | PMC_MIO41_SYSMON_I2O_ALERT |     |                             |

|      | 42    | UART                  | PMC_MIO42_501_RX_IN_I      |     |                             |

|      | 43    |                       | PMC_MIO43_501_TX_OUTD      |     |                             |

|      | 44    | I2C1                  | PMC_MIO44_501_LP_I2C0_SCL  |     |                             |

|      | 45    |                       | PMC_MIO45_501_LP_I2C0_SDA  |     |                             |

|      | 46    | I2C0                  | PMC_MIO46_501_I2C0_S0I0    |     |                             |

|      | 47    |                       | PMC_MIO47_501_I2C0_S0D0    |     |                             |

|      | 48    | GEM0                  | PMC_MIO48_GEM_RST_BO       |     |                             |

|      | 49    | Regulator Enable GPIO | PMC_MIO49_VCC_PSLP_EN      |     | See <a href="#">Table 1</a> |

|      | 50    | PCIe                  | PMC_MIO50_PCIE_WAKE_OB     |     |                             |

|      | 51    | SD                    | PMC_MIO51_SD_BUSPWRO       |     |                             |

| 502  | 0     | GEM0                  | LPD_MIO0_GEM_TX_CLK_O      |     |                             |

|      | 1     |                       | LPD_MIO1_GEM_TX_D0_I/O     |     |                             |

|      | 2     |                       | LPD_MIO2_GEM_TX_D1_I/O     |     |                             |

|      | 3     |                       | LPD_MIO3_GEM_TX_D2_I/O     |     |                             |

|      | 4     |                       | LPD_MIO4_GEM_TX_D3_I/O     |     |                             |

|      | 5     |                       | LPD_MIO5_GEM_TX_CTL_I/O    |     |                             |

|      | 6     |                       | LPD_MIO6_GEM_RX_CLK_I      |     |                             |

| Bank | MIO #                                           | Device | Signal                | I/O | Notes                       |

|------|-------------------------------------------------|--------|-----------------------|-----|-----------------------------|

|      | 7                                               |        | LPD_MIO7_GEM_RX_D0    | I/O |                             |

|      | 8                                               |        | LPD_MIO8_GEM_RX_D1    | I/O |                             |

|      | 9                                               |        | LPD_MIO9_GEM_RX_D2    | I/O |                             |

|      | 10                                              |        | LPD_MIO10_GEM_RX_D3   | I/O |                             |

|      | 11                                              |        | LPD_MIO11_GEM_RX_CTL  | I/O |                             |

| 12   | Regulator<br>Enable<br>GPIO                     |        | LPD_MIO12_VCC_PSFP_EN |     | See <a href="#">Table 1</a> |

| 13   | Regulator<br>Enable<br>GPIO                     |        | LPD_MIO13_VCC_SOC_EN  |     | See <a href="#">Table 1</a> |

| 14   | CANFD0<br>See <a href="#">CAN<br/>Interface</a> |        | LPD_MIO14_CANFD0_RX   | I   |                             |

| 15   |                                                 |        | LPD_MIO15_CANFD0_TX   | O   |                             |

| 16   | CANFD1<br>See <a href="#">CAN<br/>Interface</a> |        | LPD_MIO16_CANFD1_TX   | O   |                             |

| 17   |                                                 |        | LPD_MIO17_CANFD1_RX   | I   |                             |

| 18   | PCIe                                            |        | PCIE_PERST_B          | I   |                             |

| 19   |                                                 |        | PCIE_PERST_B          | I   |                             |

| 20   | Regulator<br>Enable<br>GPIO                     |        | LPD_MIO20_VCC_PL_EN   | O   | See <a href="#">Table 1</a> |

| 21   | Fan                                             |        | MIO21_FAN_PWM_VERSA   | O   | Versal device fan<br>PWM    |

| 22   |                                                 |        | MIO22_FAN_TACH_VERSA  | O   | Versal device fan<br>tach   |

| 23   | Regulator<br>Enable                             |        | LPD_MIO23_VADJ_FMC_EN |     | VADJ_FMC enable             |

| Bank | MIO # | Device | Signal | I/O | Notes |

|------|-------|--------|--------|-----|-------|

|      | GPIO  |        |        |     |       |

|      |       |        |        |     |       |

|      |       |        |        |     |       |

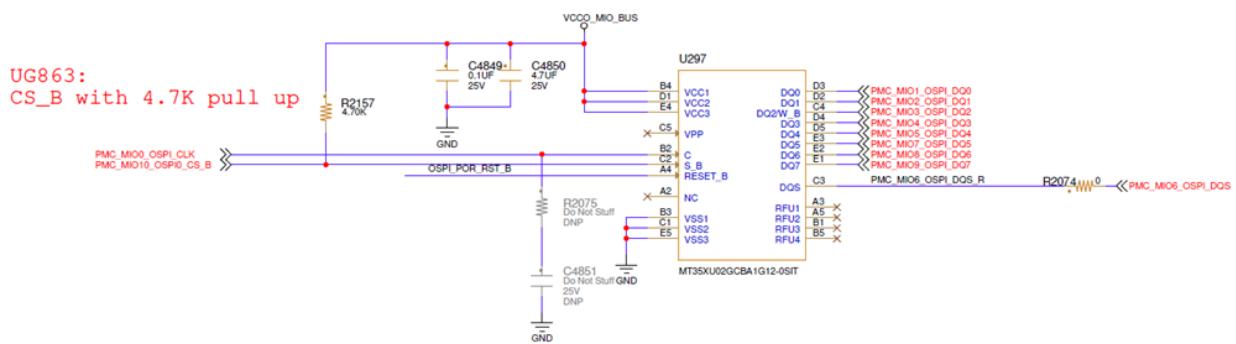

## PMC MIO[0–10,12] Bank 500: OSPI U297

### [Figure 1, callout 38]

The VEK280 evaluation board uses one Micron MT35XU02GCBA1G12-0SIT 8-bit serial peripheral interface (octal SPI) flash device. This 2 Gb NOR flash device can be used as onboard boot, as well as non-volatile storage memory. When used as a boot source, it is selectable from SW1. See [Switches](#) for more information.

See schematic page 28.

**Figure: Dual Parallel OSPI Circuit**

X27819-022223

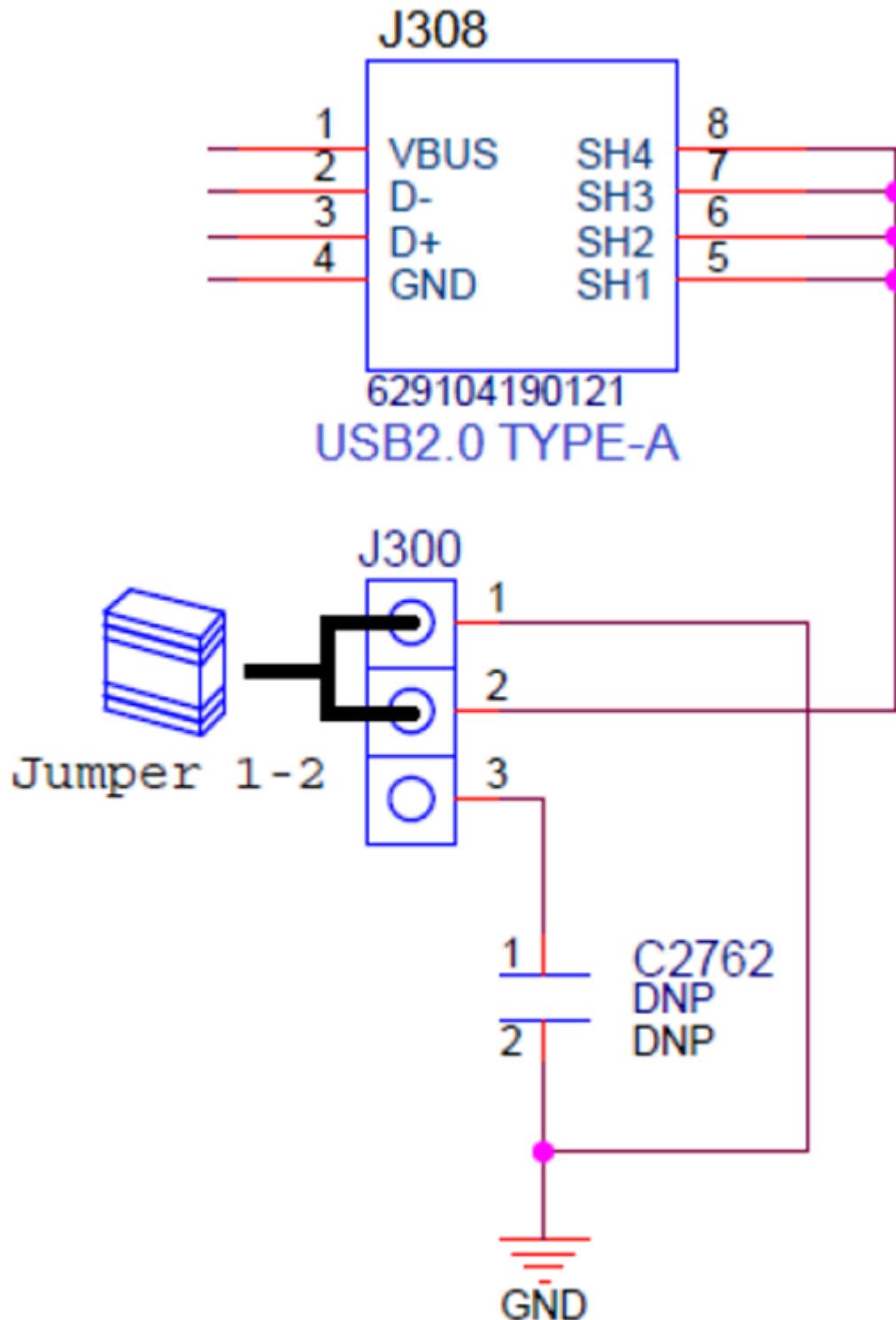

## PMC MIO[13:25] Bank 500: USB 2.0 ULPI PHY

The VEK280 evaluation board uses a Standard Microsystems Corporation USB3320 USB 2.0 ULPI transceiver (U99) to support a USB 2.0 type-A connector (J308). The USB3320 is a high-speed USB 2.0 PHY supporting the UTMI+ low pin interface (ULPI) interface standard. The ULPI standard defines the interface between the USB controller IP and the PHY device, which drives the physical USB signaling. Using the ULPI standard reduces the interface pin count between the USB controller IP and the PHY device.

The USB3320 is clocked by a 24 MHz crystal (X8). See the [Standard Microsystems Corporation](#) (SMSC) USB3320 data sheet for clocking mode details. The interface to the USB3320 PHY is implemented through the IP in the XCVE2802 device PS.

The USB3320 ULPI transceiver circuit has a Micrel MIC2544 high-side programmable current limit switch (U100). This switch has an open-drain output fault flag on pin 2, which turns on red LED DS37 if over current or thermal shutdown conditions are detected.

---

**Note:** As shown in the following figure, the shield for the USB 2.0 type-A connector (J308) can be tied to GND by a jumper on header J300 pins 1-2 (see [Default Jumper and Switch Settings](#)). The USB shield can optionally be connected through a series capacitor to GND by installing a capacitor (body size 0402) at location C2762 and inserting a jumper across pins 2-3 on header J300.

---

### Figure: USB3320 USB2.0 Connector J308 Shield Connection Options

X26017-100923

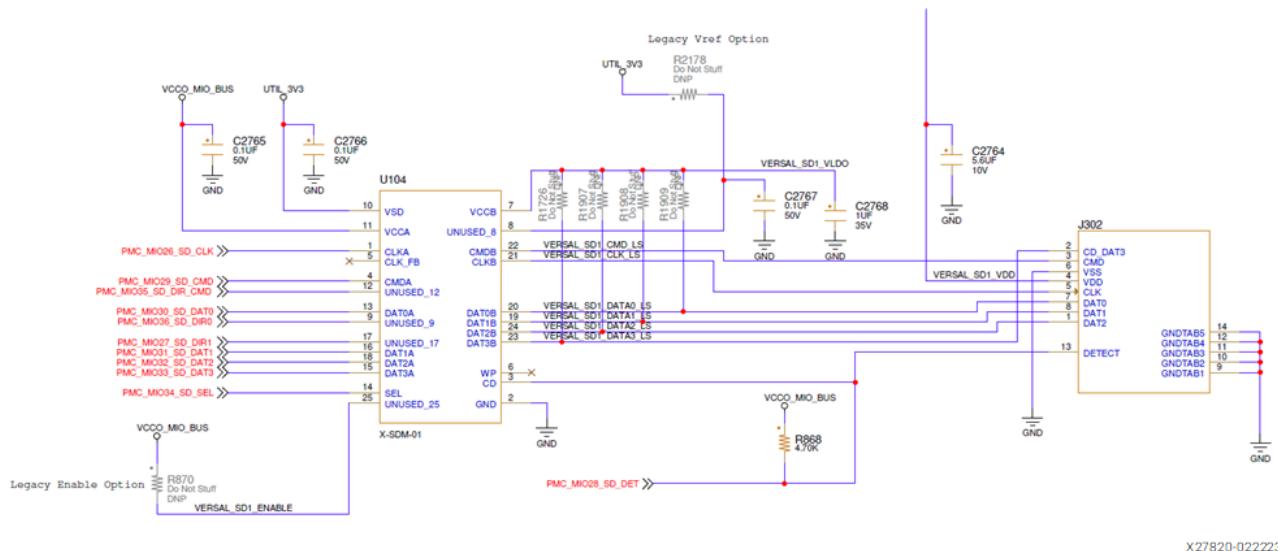

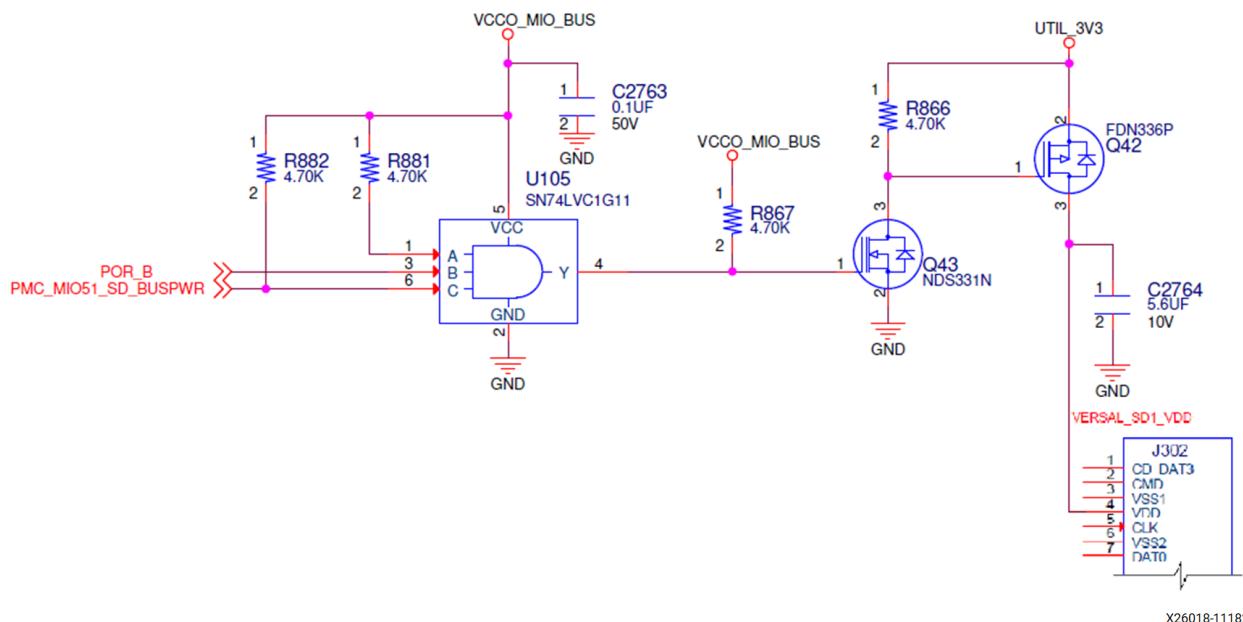

## PMC MIO[26:36, 51] Bank 501: Secure Digital (SD) Card IF

[Figure 1, callout 11]

The VEK280 evaluation board includes a secure digital input/output (SDIO) interface to provide access to general purpose non-volatile SDIO memory cards and

peripherals. This interface is used for the SD boot mode and supports SD2.0 and SD3.0 access.

The SDIO interface signals PMC\_MIO[26:36, 51] are connected to XCVE2802 device bank 501, which has its VCCO set to 1.8V. Six SD interface nets PMC\_MIO[26, 29, 30:33] are passed through a NXP NVT4857UK SD 3.0-compliant voltage level-translator U104. This translator is present between the Versal device and the SD card connector (J302). The NXP NVT4857UK U104 device provides SD3.0 capability with SDR104 performance. The following figure shows the connections of the SD card interface on the VEK280 evaluation board.

**Figure: SD Card Interface Connections**

X27820-022222

The following table lists the NVT4857UK U104 adapter pinout.

**Table: NVT4857UK U104 Adapter Pinout**

| Aries Adapter Pin Number | NVT4857UKAZ Pin Number | NVT4857UKAZ Pin Name |

|--------------------------|------------------------|----------------------|

| 1                        | D2                     | CLKA                 |

| 2                        | C3, C2                 | GND                  |

| 3                        | B2                     | CD                   |

| 4                        | C1                     | CMDA                 |

| 5                        | E2                     | CLK_FB               |

| 6                        | Unused                 | Unused               |

| 7                        | B3                     | VCCB                 |

| Aries Adapter Pin Number | NVT4857UKAZ Pin Number | NVT4857UKAZ Pin Name |

|--------------------------|------------------------|----------------------|

| 8                        | Unused                 | Unused               |

| 9                        | Unused                 | Unused               |

| 10                       | A3                     | VSD                  |

| 11                       | A2                     | VCCA                 |

| 12                       | Unused                 | Unused               |

| 13                       | D1                     | DATA0                |

| 14                       | E3                     | SEL                  |

| 15                       | B1                     | DAT3A                |

| 16                       | E1                     | DAT1A                |

| 17                       | Unused                 | Unused               |

| 18                       | A1                     | DAT2A                |

| 19                       | E4                     | DAT1B                |

| 20                       | D4                     | DAT0B                |

| 21                       | D3                     | CLKB                 |

| 22                       | C4                     | CMDB                 |

| 23                       | B4                     | DAT3B                |

| 24                       | A4                     | DAT2B                |

| 25                       | Unused                 | Unused               |

The Versal device (U1) also has control over the power for the SDCARD, which allows the Versal device to remove power to the SD card as needed.

**Figure: SD Socket J302 Power Control**

X26018-111821

Information for the SD I/O card specification can be found at the [SanDisk Corporation](#) or [SD Association](#) websites. The VEK280 SD card interface supports the SD1 (2.0) and SD2 (3.0) configuration boot modes documented in the *Versal Adaptive SoC Technical Reference Manual (AM011)*. See schematic page 35 for more details.

For NVP NVT4857UK component details, see the NVT4857UK data sheet on the [NXP](#) website.

The detailed Versal device connections for the feature described in this section are documented in the VEK280 board XDC file, referenced in [Xilinx Design Constraints](#).

## PS MIO[37] Selectable

The Versal device PS bank 501 MIO37 is jumper selectable as factory reserved [1:2] or as CANFD0\_INH\_B [2:3]. The default is [1:2].

## PS MIO[38] CAN0 Standby Mode

The Versal device PS bank 501 MIO38 controls the CAN0 standby mode. This control is an output from the Versal device and an input to the CAN transceiver.

## PMC MIO[39:41] System Monitor I2C

The Versal device PS bank 501 MIO39 (PMC\_MIO39\_SYSMON\_I2C\_SCL), MIO40 (PMC\_MIO40\_SYSMON\_I2C\_SDA), and MIO41 (PMC\_MIO41\_SYSMON\_I2C\_ALERT) are connected to the system controller for use with the system controller related applications and alerts.

## PMC MIO[42:43] UART0

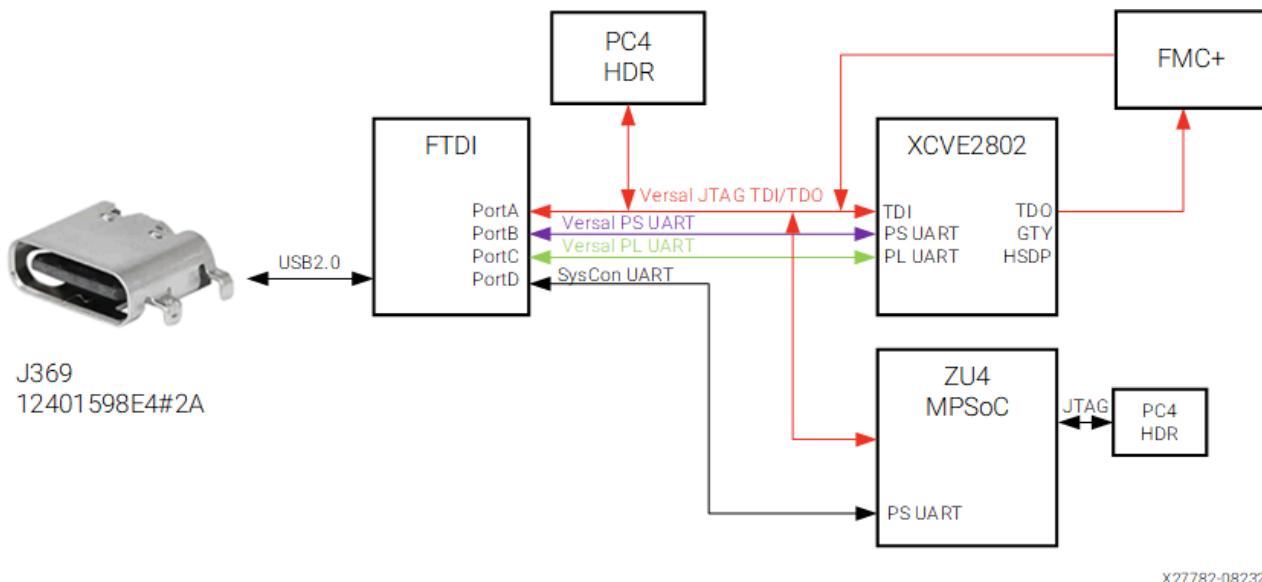

### [Figure 1, callout 9]

This is the primary Versal device PS-side UART interface. MIO42 (RX\_IN) and MIO43 (TX\_OUT) are connected to FTDI FT4232HL U20 USB-to-Quad-UART bridge port BD through TI SN74AVC4T245 level-shifters U18 and U271. The FT4232HL U20 port assignments are listed in the following table.

**Table: FT4232HL Port Assignments**

| FT4232HL U34  | Versal Device U1           |

|---------------|----------------------------|

| Port AD JTAG  | VEK280 JTAG chain          |

| Port BD UART0 | PS_UART0 (MIO 42-43)       |

| Port CD UART1 | PL_UART1 bank 401          |

| Port DD UART2 | U20 system controller UART |

The FT4232HL UART interface connections are shown in the following figure.

**Figure: FT4232HL UART Connections**

X27782-082323

For more information on the FT4232HL, see the [Future Technology Devices International Ltd.](#) website.

---

**Note:** The FTDI configuration image can be programmed with the Vivado tools. See the Programming FTDI Devices for Vivado Hardware Manager Support section in the *Vivado Design Suite User Guide: Programming and Debugging (UG908)*. Alternatively, a JTAG-SMT2 or similar from [Digilent](#) is recommended.

The detailed device connections for the feature described in this section are documented in the VEK280 board XDC file, referenced in [Xilinx Design Constraints](#).

## PMC MIO[44:45] I2C1 Bus

[Figure 1, callout 12]

Bus I2C1 connects the XCVE2802 U1 PS bank 501 and the XCZU4EG system controller U125 PS bank 501.

The detailed device connections for the feature described in this section are documented in the VEK280 evaluation board XDC file, referenced in [Xilinx Design Constraints](#).

**Figure: I2C1 Bus Topology**

X27821-082323

U34 is an I2C addressable 128-Kbit serial I2C bus EEPROM. It has two addresses associated with it. Address 0x54 is used when the memory array is accessed. When using 0x5C, the identification page is accessed.

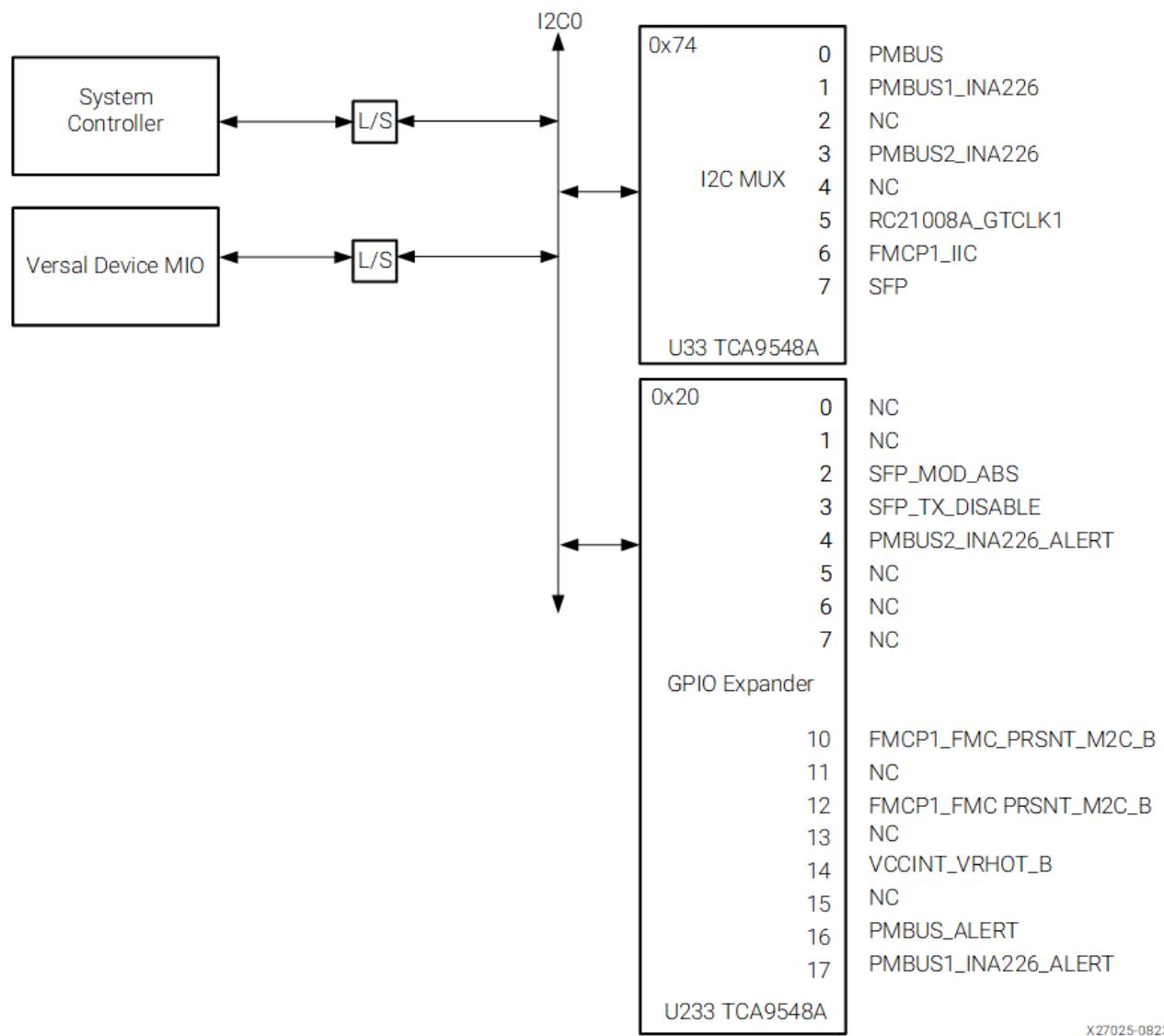

## PMC MIO[46:47] I2C0 Bus

[Figure 1, callout 12]

Bus I2C0 connects the XCVP1802 U1 PS bank 501 and the XCZU4EG system controller U125 PS bank 501 to a GPIO 16-bit port expander (TCA6416A U233) and I2C switch (TCA9548A U33). The port expander enables accepting various SFP, FMCP connector, and power system status inputs and outputs. Bus I2C0 also provides access to power system PMBus power controllers and INA226 power monitors, as well as RC21008A clock components via the U33 TCA9548A switch. TCA6416A U233 is pin-strapped to respond to I2C address 0x20. The TCA9548A

U33 switch is set to 0x74. Details for controlling the U33 TCA9548A switch can be located in the data sheet located on the [Texas Instruments](#) website. The detailed device connections for the feature described in this section are documented in the VEK280 board schematic and XDC file, referenced in [Xilinx Design Constraints](#).

**Figure: I2C0 Bus Topology**

The devices on each port of the I2C0 U233 TCA6416A port expander and on each bus of the I2C0 U33 TCA9548A switch are listed in the following tables.

**Table: I2C0 Port Expander TCA6416A U233 Address 0x20 Connections**

| I2C0 Port Expander TCA6416A U233 Address 0x20 Connections |         |           |        |

|-----------------------------------------------------------|---------|-----------|--------|

| I2C Devices                                               | Port    | Direction | Device |

| NC                                                        | P00-P01 | N/A       | N/A    |

| I2C0 Port Expander TCA6416A U233 Address 0x20 Connections |         |           |                                                                                          |

|-----------------------------------------------------------|---------|-----------|------------------------------------------------------------------------------------------|

| I2C Devices                                               | Port    | Direction | Device                                                                                   |

| SFP_MOD_ABS                                               | P02     | Out       | J376 SFP+ connector                                                                      |

| SFP_TX_DISABLE                                            | P03     | Out       | J376 SFP+ connector                                                                      |

| PMBUS2_INA226_ALERT_P04                                   |         | In        | U125 (ZU4), U166, U168, U172, U174, U176, U177, U188, U234, U264, U265, U281, U306, U309 |

| NC                                                        | P05-P09 | N/A       | N/A                                                                                      |

| FMCP1_FMC_PRSNT_M20_B                                     |         | In        | J51 FMCP HSPC                                                                            |

| NC                                                        | P11     | N/A       | N/A                                                                                      |

| FMCP1_FMCP_PRSNT_N20_B                                    |         | In        | J51 FMCP HSPC                                                                            |

| N/A                                                       | P13     | N/A       | N/A                                                                                      |

| VCCINT_VRHOT_B                                            | P14     | In        | U152 IR35215                                                                             |

| N/A                                                       | P15     | N/A       | N/A                                                                                      |

| PMBUS_ALERT                                               | P16     | In        | U125 (ZU4), U152, U160, U167, U175, U275, U282, U295, U354                               |

| PMBUS1_INA226_ALERT_P17                                   |         | In        | U65, U125 (ZU4), U161, U163, U165<br>U260, U355, U356                                    |

**Table: I2C0 Multiplexer TCA9548A U33 Address 0x74 Connections**

| I2C Devices   | I2C Switch Pos. | I2C Address                                         | Devices |

|---------------|-----------------|-----------------------------------------------------|---------|

| PMBUS         | 0               | See Schematic, <a href="#">PMBus Regulators Map</a> |         |

| PMBUS1_INA226 | 1               | See Schematic, <a href="#">PMBus Regulators Map</a> |         |

| No connect    | 2               |                                                     | N/A     |

| PMBUS2_INA226 | 3               | See Schematic, <a href="#">PMBus Regulators Map</a> |         |

| I2C Devices     | I2C Switch Pos. | I2C Address | Devices |

|-----------------|-----------------|-------------|---------|

| No connect      | 4               |             | N/A     |

| RC21008A_GTCLK1 | 5               |             | 0x09    |

| FMCP1_IIC       | 6               |             | 0x##    |

| SFP             | 7               |             | 0x##    |

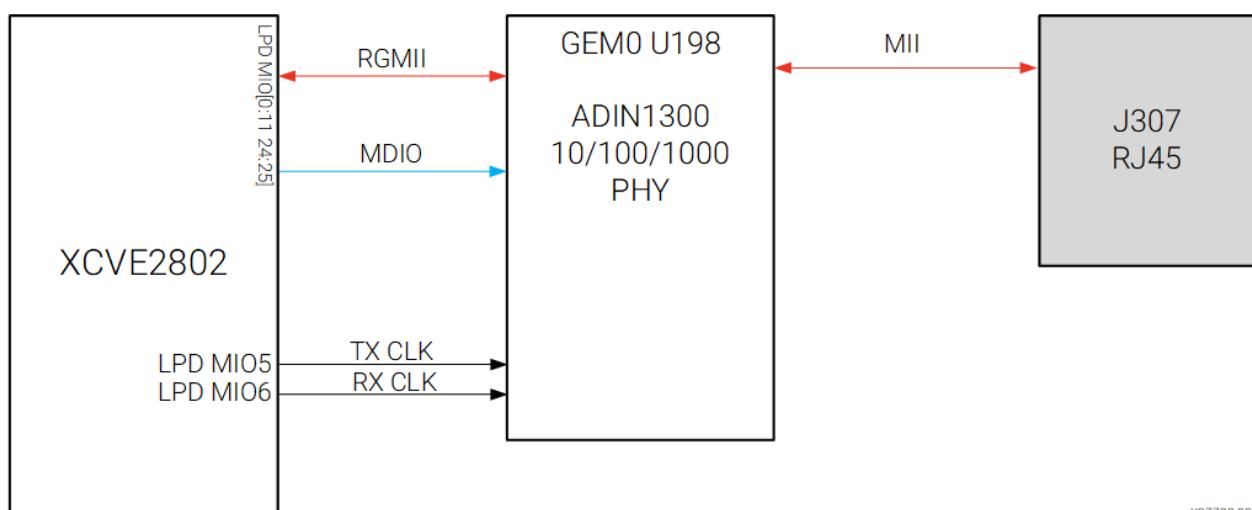

## PMC MIO[48] and LPD\_MIO[0:11, 24:25]: GEM0 Ethernet

### [Figure 1, callout 19]

A PS Gigabit Ethernet MAC (GEM) implements a 10/100/1000 Mbps Ethernet interface. In the following figure, the device (U1) is connected to ADI ADIN1300 U198 Ethernet RGMII PHY before being routed to an RJ45 Ethernet connector J307. The RGMII Ethernet PHY is boot strapped to PHY address (0x01) and Auto Negotiation is set to Enable.

**Figure: RGMII Ethernet**

X27783-082323

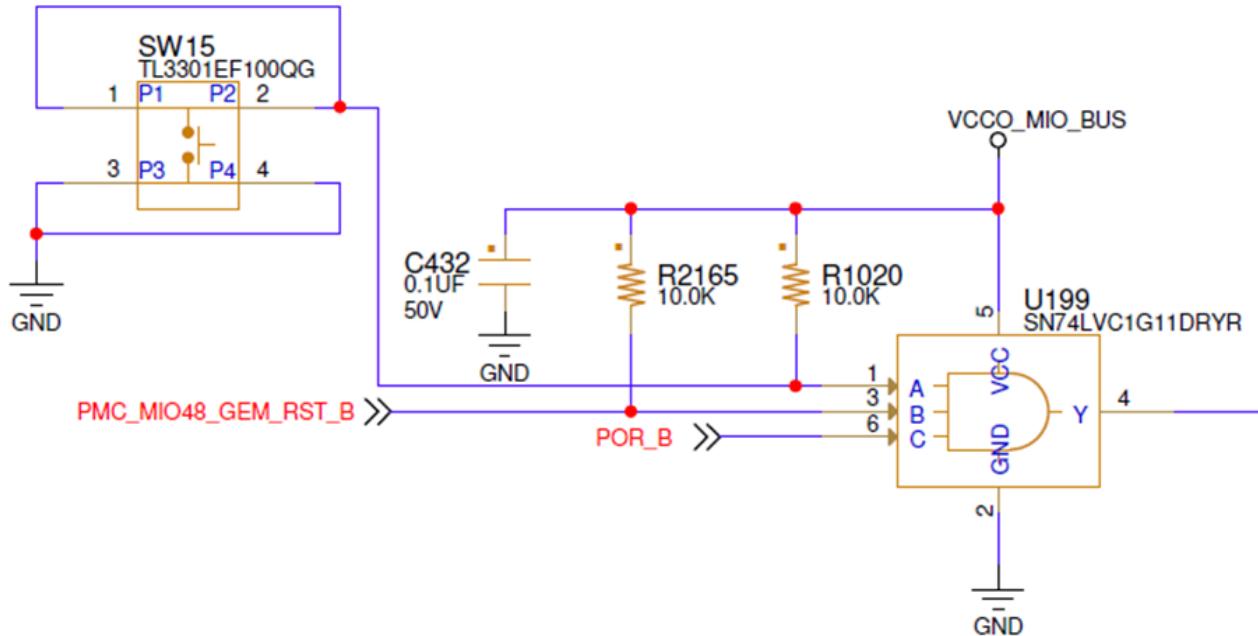

## Ethernet PHY (Three Resets)

### [Figure 1, callout 19]

The ADIN1300 PHY (GEM0 U198) is reset by its GEM0\_RESET\_B generated by dedicated pushbutton switch (SW15) and PMC\_MIO signals as shown in the following figure. The POR\_B signal generated by the TPS389001DSER U10 POR device is wired in parallel to each Ethernet PHY reset circuit. The POR device is activated by pushbutton SW2. See [System Reset POR\\_B](#) for more details.

**Figure: Ethernet PHY Reset Circuit**

X27822-022223

## Ethernet PHY LED Interface

[[Figure 1](#), callout 19]

The ADIN1300 PHY (GEM0 U198) controls two LEDs in the J307 two port connector bezel. The PHY signal LED0 drives the green LED, and LED1 drives the yellow LED. The LED functional description is listed in the following table.

**Table: Ethernet PHY LED Functional Description**

| ADIN1300 PHY Pin |        | Description                                                                                                                                                                                                                                                     |

|------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name             | Number |                                                                                                                                                                                                                                                                 |

| LED_1            | 26     | By default, this pin indicates that 100BASE-T link is established. Additional functionality is configurable using LEDCR1[7:4] register bits. The LINK_ST pin is a general-purpose output used to indicate to the MAC whether a valid link has been established. |

| LED_0            | 21     | By default, this pin indicates that link is established. Additional functionality is configurable using LEDCR1[3:0] register bits.                                                                                                                              |

| ADIN1300 PHY Pin |        | Description                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name             | Number |                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  |        | <p>The LED_0 can be used to indicate the speed of operation, link status, and duplex mode. By default, LED_0 illuminates when a link is established and blinks when there is activity. The default LED operation can be overwritten in software using the PHY LED control registers, LED_CTRL_1, LED_CTRL_2, and LED_CTRL_3 (Register Address 0x001B, Register Address 0x001C, and Register Address 0x001D, respectively).</p> |

The LED functions can be repurposed with a LEDCR1 register write available via the PHY's management data interface, MDIO/MDC.

See the ADI ADIN1300 RGMII PHY data sheet at the [Analog Devices](#) website for component details.

The detailed device connections for the feature described in this section are documented in the VEK280 board XDC file, referenced in [Xilinx Design Constraints](#).

## PMC MIO[11,49] and LPD MIO[12,13,20,23]: Power Enable

[[Figure 1](#), callout 22-30]