## NMUX1237; 2-channel analog multiplexer/ demultiplexer evaluation board

**Abstract:** This user manual describes the NMUX1237 evaluation board module.

**Keywords:** NMUX1237; 2-channel analog multiplexer/demultiplexer evaluation board (EVB)

## 1. Introduction

The NMUX1237 is a versatile CMOS bidirectional (SPDT) single-pole double-throw analog switch with digital control pins that support 1.8 V logic thresholds independent of the supply voltage.

Supporting a wide supply voltage range of 1.08 V to 5.5 V, the device additionally features integrated circuitry to minimize analog signal overshoot when switching between channels. No power sequencing is required, as both digital and analog back-power protection are implemented.

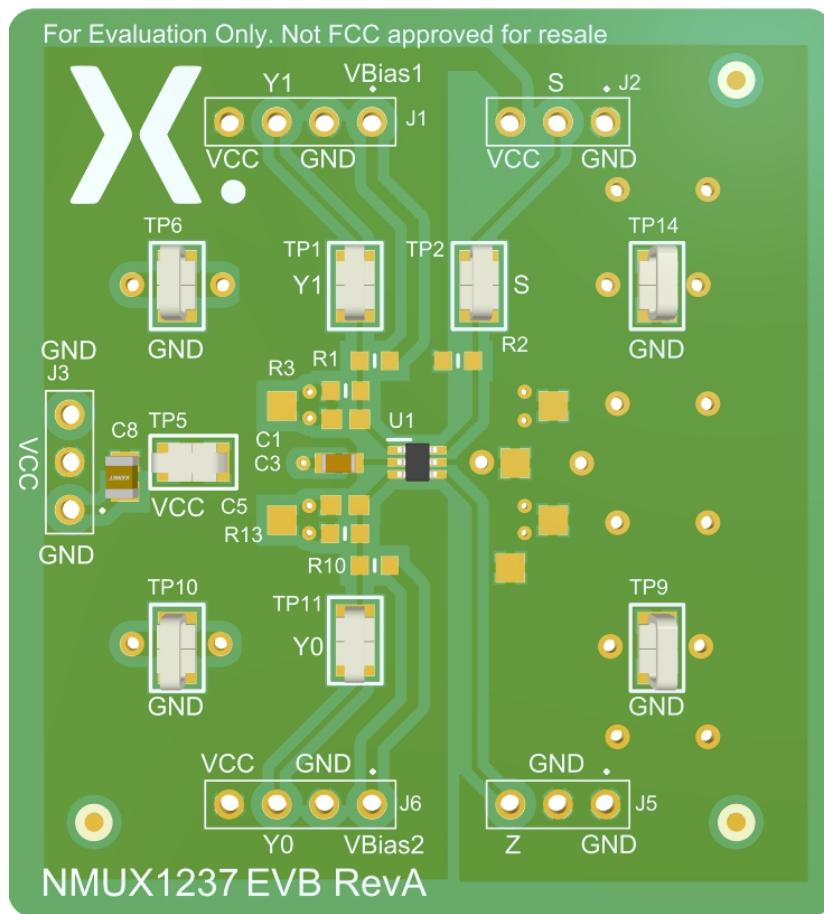

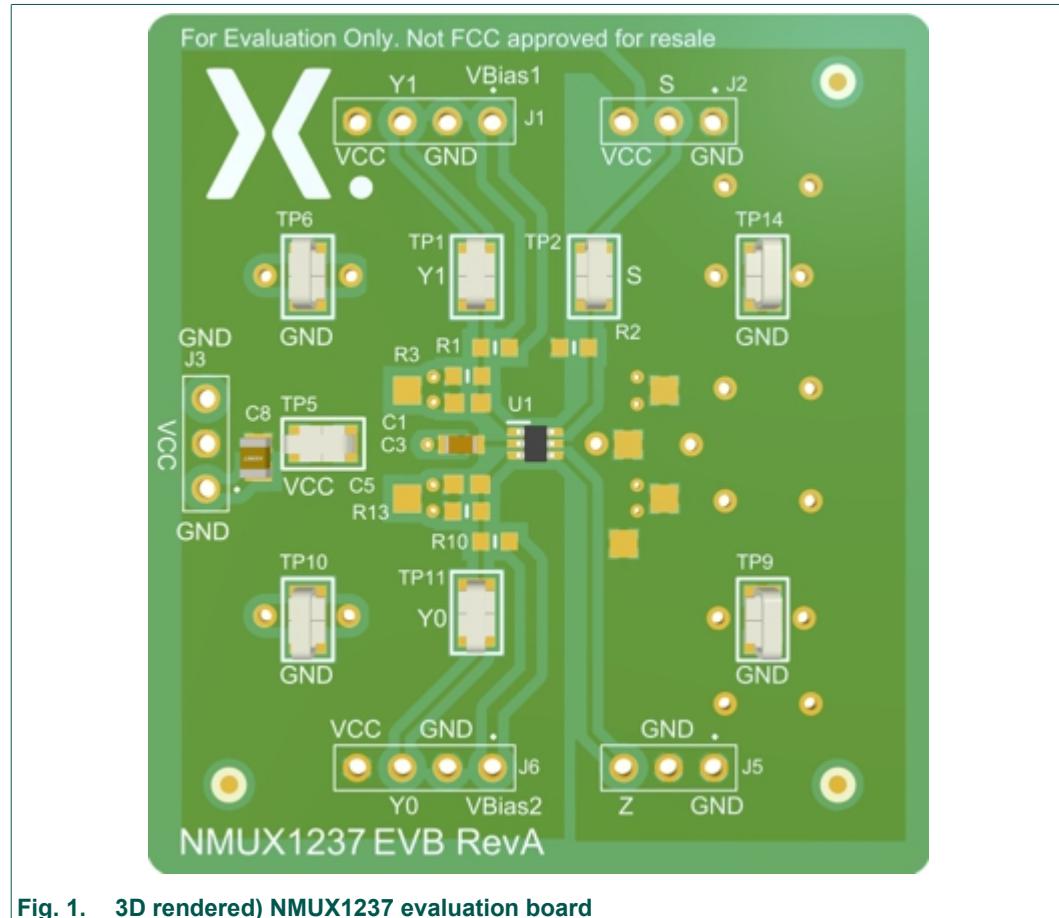

The evaluation board (EVB) arrives enclosed in an antistatic ESD bag with labeling. The board's silkscreen text allows for an easy reference to pin names and locations. Convenient test points for GND,  $V_{CC}$ ,  $Y_n$ , Z, and S pins are included as well. Footprints for 0603 resistors and capacitors are also included on the two analog channels, allowing the user to create a customized voltage divider if needed.

### Key parameters and features

The list below gives a summary of the key parameters and most important features of the NMUX1237.

- Integrated suppression circuit to minimize signal overshoot.

- Wide operating range: 1.08 V to 5.5 V

- Control signal pins maintains 1.8 V logic compatibility across fully supply operating range.

- Rail-to-Rail operation on analog signal pins

- Break-before-make switching.

- Very low ON-resistance: 4  $\Omega$  (typical)

- Specified from -40 °C to +85 °C and from -40 °C to +125 °C

## 2. Hardware setup

Higher level configuration summary:

- Test points on V<sub>CC</sub>, GND, Y<sub>n</sub>, Z, and S pins

- Passive footprints for customized divider circuit

- Selectable header shunts to connect inputs to V<sub>CC</sub> or GND

- Board supports NMUX1237GW (TSSOP6/SOT363-2) footprints.

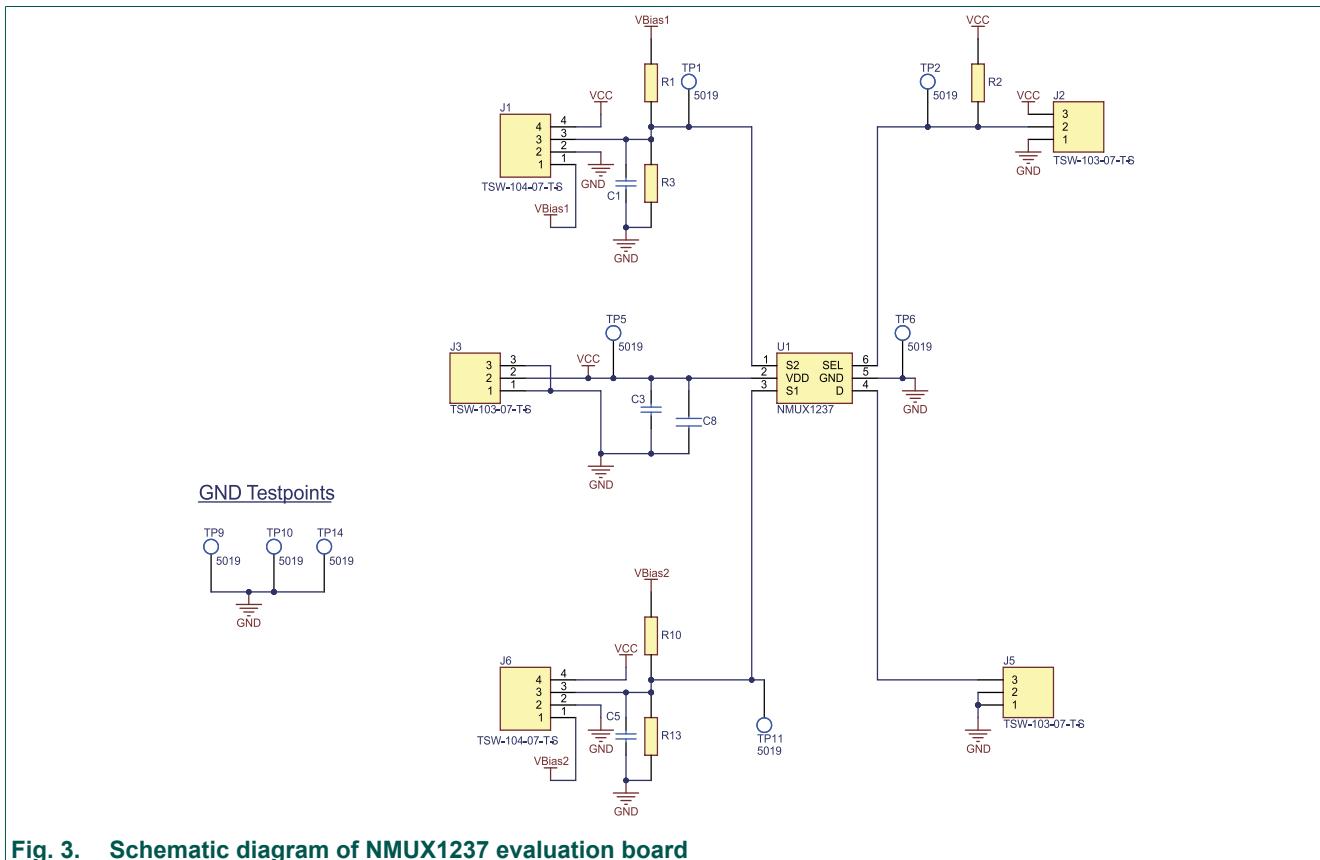

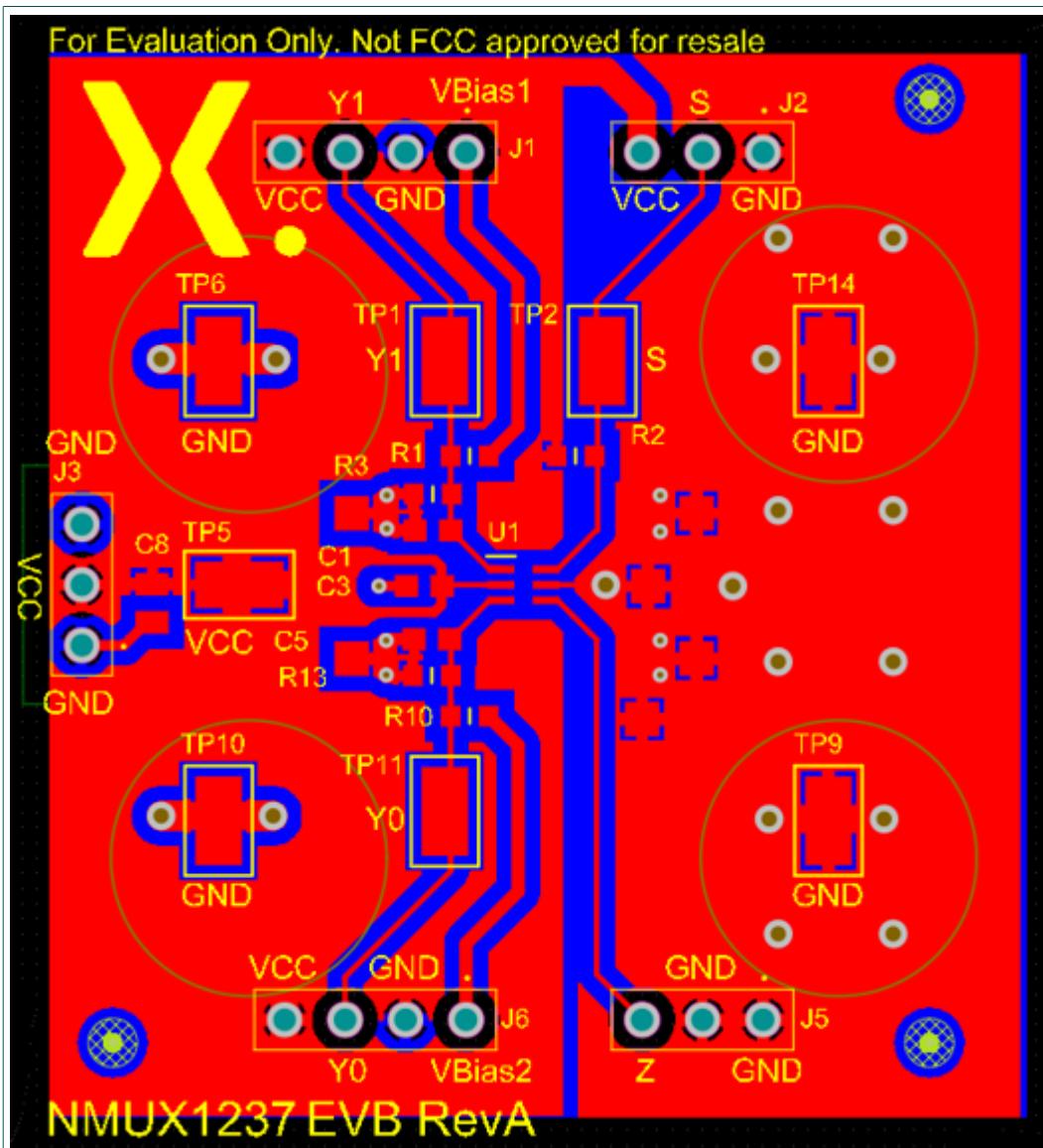

Fig. 1. 3D rendered) NMUX1237 evaluation board

### 3. Test points $V_{CC}$ [+] and GND [-]

TP5 ( $V_{CC}$ ) and TP6, TP9, TP10, TP14 (GND), or J3, serve as the physical connection for the external supply. A portion of the top plane connects to  $V_{CC}$ , while the bottom and top right planes connect to GND. Device input pins,  $Y_n$ , can connect to  $V_{CC}$  or GND through their respective 2.54 mm shunt locations. This is illustrated in [Table 1](#) and [Table 2](#).

**Table 1. Detailed description of supply connections**

| Symbol net names | Header/Pin number          | Description                         |

|------------------|----------------------------|-------------------------------------|

| $V_{CC}$         | TP5 or J3                  | External supply $V_{CC}$ connection |

| GND              | TP6, TP9, TP10, TP14 or J3 | External supply GND connection      |

Each pin of the device is brought out to a male header. The user can directly make connections to their respective headers or attach clips to their respective test points. Additionally, the analog inputs  $Y_n$  can be manually connected to  $V_{CC}$  or GND through 2.54 mm shunts.

**Table 2. Detailed description of the header**

| NMUX1237 pin number | Header connection | Test point clip label | NMUX1237 pin name | 2.5 mm shunt connection description                                                                    |

|---------------------|-------------------|-----------------------|-------------------|--------------------------------------------------------------------------------------------------------|

| 1                   | J1-3              | TP1                   | Y1                | <ul style="list-style-type: none"> <li>• 3-2 GND [-]</li> <li>• 4-3 <math>V_{CC}</math> [+]</li> </ul> |

| 2                   | J3-2              | TP5                   | $V_{CC}$          | NA                                                                                                     |

| 3                   | J6-3              | TP11                  | Y0                | <ul style="list-style-type: none"> <li>• 3-2 GND [-]</li> <li>• 4-3 <math>V_{CC}</math> [+]</li> </ul> |

| 4                   | J5-3              | NA                    | Z                 | NA                                                                                                     |

| 5                   | NA                | TP6, TP9, TP10, TP14  | GND               | NA                                                                                                     |

| 6                   | J2-2              | TP2                   | S                 | <ul style="list-style-type: none"> <li>• 1-2 GND [-]</li> <li>• 2-3 <math>V_{CC}</math> [+]</li> </ul> |

The analog pins of the NMUX1237 evaluation board include options to integrate pull-up/pull-down resistors, which can also be optionally populated to allow a voltage divider network for header pin  $V_{bias}$ . This is accomplished by populating the 0603 footprints on the EVB. Additionally, 0603 ceramic capacitor footprints are also included in case the user wishes to add capacitance to the signal net.

Fig. 2. Input pins passive footprints

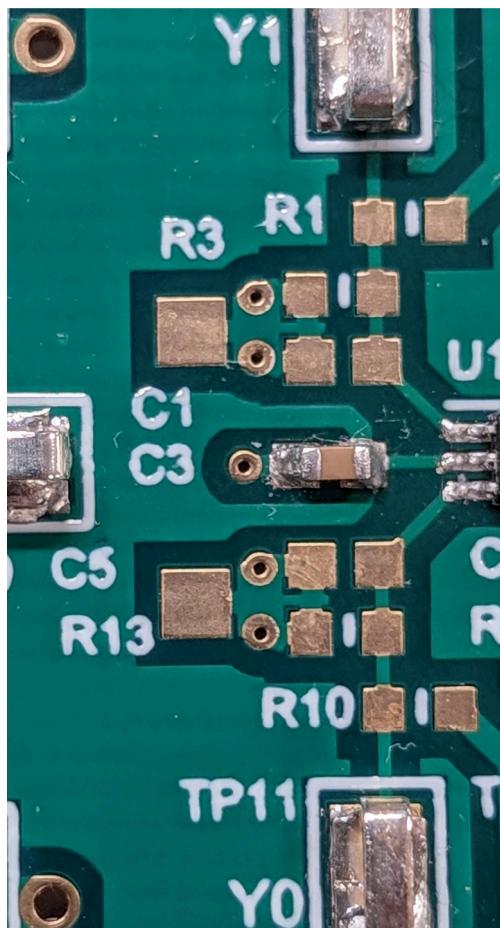

## 4. Schematic diagram

Fig. 3. Schematic diagram of NMUX1237 evaluation board

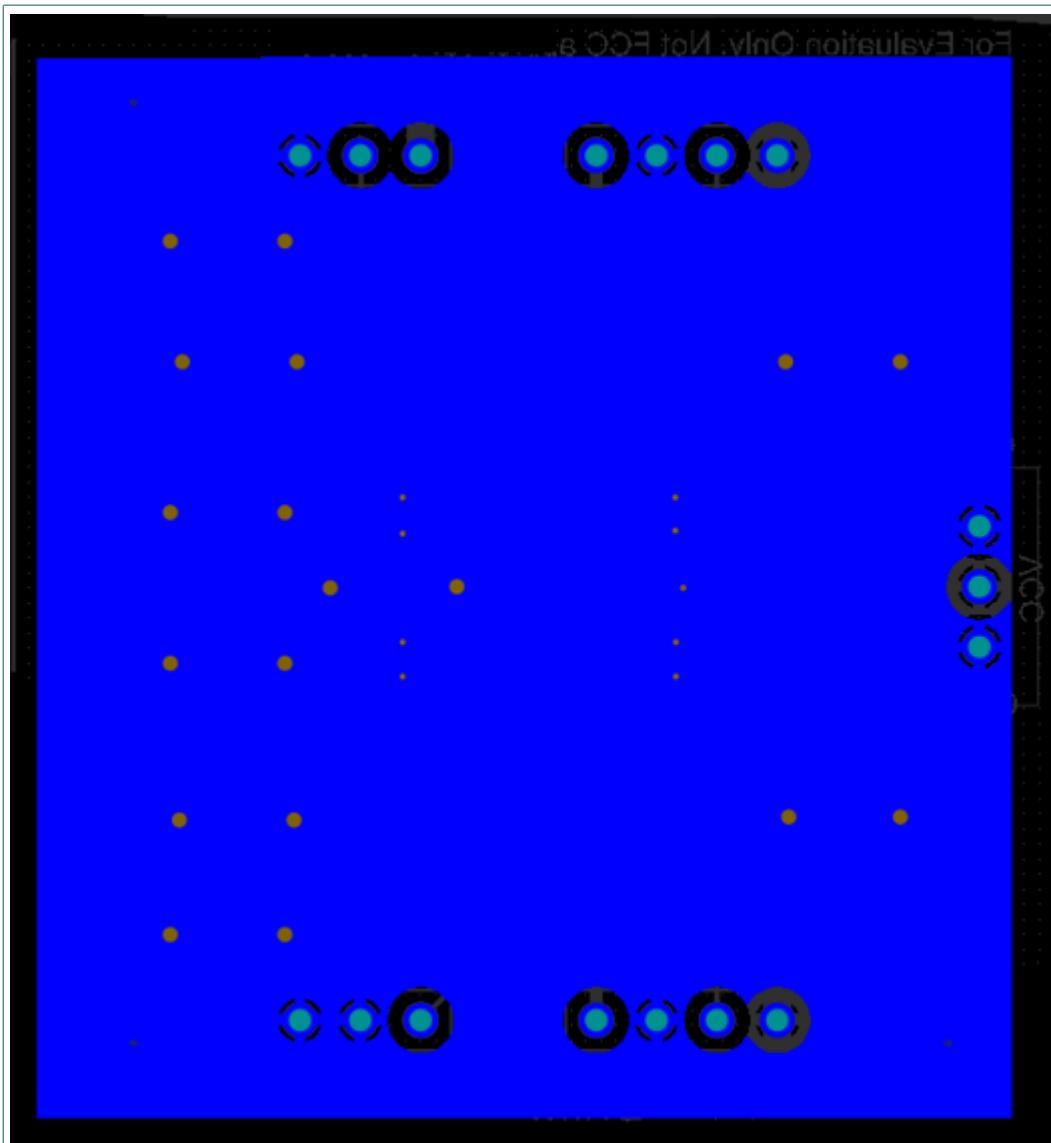

## 5. PCB layout

Fig. 4. Printed Circuit Board (PCB) layout top side

Fig. 5. Printed Circuit Board (PCB) layout back side

## 6. Bill of material

Table 3. Bill of Material (BOM)

| Part number        | Designator                                | Quantity |

|--------------------|-------------------------------------------|----------|

| CC0603KRX7R7BB104  | C3                                        | 1        |

| C0805C105K5RAC7800 | C8                                        | 1        |

| FID                | FID1, FID2, FID3                          | 3        |

| SJ-5303 (CLEAR)    | H1, H2, H3, H4                            | 4        |

| TSW-104-07-T-S     | J1, J6                                    | 2        |

| TSW-103-07-T-S     | J2, J3, J5                                | 3        |

| 5019               | TP1, TP2, TP5, TP6, TP9, TP10, TP11, TP14 | 8        |

| NMUX1237GW         | U1                                        | 1        |

## 7. Revision history

**Table 4. Revision history**

| Revision number | Date     | Description     |

|-----------------|----------|-----------------|

| UM90037 v.1     | 20240718 | Initial version |

## 8. Legal information

### Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

### Disclaimers

**Limited warranty and liability** — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.

In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.

**Right to make changes** — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Nexperia product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). Nexperia does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

### Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

## Contents

|                                                     |    |

|-----------------------------------------------------|----|

| 1. Introduction.....                                | 2  |

| 2. Hardware setup.....                              | 3  |

| 3. Test points V <sub>CC</sub> [+] and GND [-]..... | 4  |

| 4. Schematic diagram.....                           | 6  |

| 5. PCB layout.....                                  | 7  |

| 6. Bill of material.....                            | 8  |

| 7. Revision history.....                            | 9  |

| 8. Legal information.....                           | 10 |

---

© Nexperia B.V. 2024. All rights reserved

For more information, please visit: <http://www.nexperia.com>

For sales office addresses, please send an email to: [salesaddresses@nexperia.com](mailto:salesaddresses@nexperia.com)

Date of release: 18 July 2024

---