## Training Getting Started with AVR® DB OPAMP, XOSHF and MVIO - Atmel Studio

### Prerequisites

Authors: Martin Mostad, Martin Thomaz, Microchip Technology Inc.

- **Hardware Prerequisites**

- The Microchip AVR128DB48 Curiosity Nano Curiosity Nano Evaluation Kit [EV35L43A](#)

- Micro-USB cable (Type-A/Micro-B)

- Logic Analyzer or oscilloscope with 100 MHz sampling speed (only needed for Assignment 2)

- **Software Prerequisites**

- [Atmel Studio 7.0.2397](#) or later

- Atmel Studio Dx\_DFP version 1.4.308 or above

- [Atmel Start](#) version 1.8.457 or later (only needed for Assignment 4)

- [MPLAB® Data Visualizer Stand-alone](#) version 1.1.793 or above

- [MPLAB® Mindi™ Analog Simulator](#)

- **Other**

- The Atmel Studio projects are available at:

[View Code Example on GitHub](#)

Click to browse repository

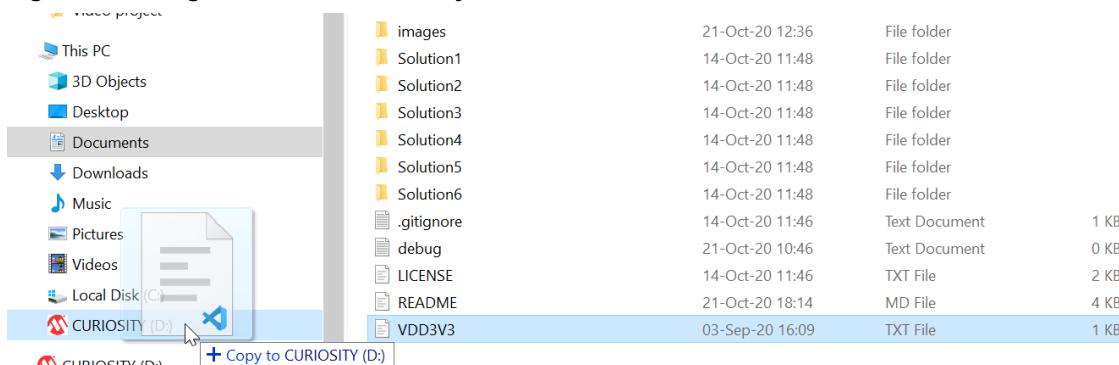

- The AVR128DB48 Curiosity Nano needs to be running at 3.3V. This can be achieved by dragging the VDD3V3.txt file located in the GitHub repository over to the CURIOSITY memory device, as shown in [Figure 1](#).

**Figure 1. Setting AVR128DB48 Curiosity Nano to 3.3V**

- **Estimated Completion Time: 210 minutes**

## Table of Contents

|                                                                                                               |    |

|---------------------------------------------------------------------------------------------------------------|----|

| Prerequisites.....                                                                                            | 1  |

| 1. Introduction.....                                                                                          | 3  |

| 2. Icon Key Identifiers.....                                                                                  | 4  |

| 3. Assignment 1: CLKCTRL - External High-Frequency Oscillator (XOSCHF) and Clock Failure Detection (CFD)..... | 5  |

| 3.1. Configure the Main Clock to Use XOSCHF.....                                                              | 5  |

| 3.2. Configure the CFD to Detect Failures on the Main Clock.....                                              | 8  |

| 4. Assignment 2: CLKCTRL - High Frequency TCD using PLL.....                                                  | 10 |

| 4.1. Configure TCD to Use the PLL as a Clock Source.....                                                      | 10 |

| 5. Assignment 3: OPAMP - Voltage Follower.....                                                                | 12 |

| 5.1. Configure OP0 as a Voltage Follower.....                                                                 | 12 |

| 5.2. Plot Graph In MPLAB® Data Visualizer.....                                                                | 14 |

| 6. Assignment 4: OPAMP - Non-Inverting PGA.....                                                               | 18 |

| 6.1. Simulating Non-Inverting PGA in Mindi™ .....                                                             | 18 |

| 6.2. Configure OP0 as a Non-Inverting PGA Using Atmel START.....                                              | 20 |

| 7. Assignment 5: MVIO - OPAMP as a Regulated Power Supply for VDDIO2.....                                     | 26 |

| 7.1. MVIO Hardware Setup.....                                                                                 | 26 |

| 7.2. Measuring VDDIO2 Using the ADC.....                                                                      | 28 |

| 8. Assignment 6: MVIO - VDDIO2 Failure Detection.....                                                         | 30 |

| 8.1. Set Up VDDIO2 Failure Detection.....                                                                     | 30 |

| 9. Revision History.....                                                                                      | 32 |

| The Microchip Website.....                                                                                    | 33 |

| Product Change Notification Service.....                                                                      | 33 |

| Customer Support.....                                                                                         | 33 |

| Microchip Devices Code Protection Feature.....                                                                | 33 |

| Legal Notice.....                                                                                             | 34 |

| Trademarks.....                                                                                               | 34 |

| Quality Management System.....                                                                                | 35 |

| Worldwide Sales and Service.....                                                                              | 36 |

## 1. Introduction

This training document contains assignments that give a general introduction to the new features of the AVR® DB Family. Each assignment starts with a basic introduction, then the functionality is verified through the MPLAB® *Data Visualizer*. Every assignment is provided with a preconfigured code, where most of the code is already in place, and only essential modules for the specific assignment need to be configured. Each assignment comes with a solution.

The new AVR® DB Family of microcontrollers comes with three features that will be highlighted in this training. The features are a new Clock Controller (CLKCTRL), Analog Signal Conditioning (OPAMP), and Multi-Voltage I/O (MVIO).

The new CLKCTRL has a new clock source called the High Frequency Crystal Oscillator (XOSCHF) and Clock Failure Detection (CFD). The XOSCHF enables the use of an external crystal or an external clock signal up to 32 MHz. This can be used as a clock source for the Main Clock (CLK\_MAIN), the Real-Time Counter (RTC), and the 12-bit Timer/Counter Type D (TCDn). The CFD feature can be used to detect if the output from a clock source stops and can switch the Main Clock to a different clock source.

The OPAMP peripheral features up to three internal operational amplifiers (op amps) as well as a resistor ladder for each op amp. The resistor ladder can be used to create a variety of classical op amp configurations. The main purpose of op amps is to condition the analog signals before an acquisition or to provide the necessary output drive in control applications.

The MVIO allows a subset of the I/O pins to be powered by a different I/O voltage domain called  $V_{DDIO2}$ . The rest of the I/O pins runs on  $V_{DD}$ , which may remove the need for external level shifters when communicating with other devices running on a different target voltage.

This training covers the following topics:

- Assignment 1: CLKCTRL - External High-Frequency Oscillator (XOSCHF) and Clock Failure Detection (CFD)

- Assignment 2: CLKCTRL - High Frequency TCD using PLL

- Assignment 3: OPAMP - Voltage Follower

- Assignment 4: OPAMP - Non-Inverting PGA

- Assignment 5: MVIO - OPAMP as a Regulated Power Supply for VDDIO2

- Assignment 6: MVIO - VDDIO2 Failure Detection

## 2. Icon Key Identifiers

The following icons are used in this document to identify different assignment sections and to reduce complexity.

**Info:** Delivers contextual information about a specific topic.

**Tip:** Highlights useful tips and techniques.

**To do:** Highlights objectives to be completed.

**Result:** Highlights the expected result of an assignment step.

Indicates important information.

**Execute:** Highlights actions to be executed out of the target when necessary.

### 3. Assignment 1: CLKCTRL - External High-Frequency Oscillator (XOSCHF) and Clock Failure Detection (CFD)

In this assignment, the AVR128DB48 Curiosity Nano will be configured to use the external high-frequency oscillator (XOSCHF) as the main clock source.

The clock failure detection will be configured to detect failures on the main clock. A failure on the main clock will result in a Non-Maskable Interrupt (NMI).

A failure will be triggered by the software when the switch (SW0) on the AVR128DB48 Curiosity Nano is pressed.

The AVR128DB48 Curiosity Nano will blink an LED with a frequency dependent on the main clock to show how the main clock source will be switched back to the default internal source when an error is detected.

The starting point for this assignment is the Atmel Studio Solution *Assignment1* found in *Assignment1*.

- **Objectives**

- Configure the main clock to use XOSCHF as its clock source

- Configure the CFD to generate an NMI on the failure of the main clock

- Trigger a failure on the main clock using the built-in test functionality of the CFD

#### 3.1 Configure the Main Clock to Use XOSCHF

**To do:**

- Edit the `CLOCK_XOSCHF_crystal_init()` function so that the main clock uses the XOSCHF as a clock source

**Info:**

Almost all the registers in the Clock Controller (CLKCTRL) peripheral are under Configuration Change Protection (CCP), which means that for write to this register, a certain key must first be written to the CPU.CCP register, followed by a write to the protected bits within four CPU instructions. To make sure this criterion is met when writing to the protected registers, the function `ccp_write_io()` is used, which can be found in the `avr/cpufunc.h` file. The function takes two arguments: A `uint8_t` pointer and the values to be written to the register. The register macros provided by the `io.h` file are not `uint8_t` pointers, so typecasting is therefore needed. A useful template showing how to use the function is:

```

ccp_write_io((uint8_t *) &<register>, new_value)

```

1. Configure the XOSCHF to use an external crystal, have a start-up time of four thousand cycles, a frequency range of 16 MHz, to always run, and enable XOSCHF. All this can be done by adding the following to `CLOCK_XOSCHF_crystal_init()`:

```

ccp_write_io((uint8_t *) &CLKCTRL_XOSCHFCTRLA, CLKCTRL_RUNSTDBY_bm

| CLKCTRL_CSUTHF_4K_gc

| CLKCTRL_FRQRANGE_16M_gc

| CLKCTRL_SELHF_CRYSTAL_gc

| CLKCTRL_ENABLE_bm);

```

**Info:** The frequency range setting determines the maximum frequency for the crystal that is supported. The larger the range, the higher the current consumption.

**Info:** The XOSCHF is set to always run so we can verify that the clock source is stable before being used. This setting will later be turned off to save power.

2. Wait until the external high-frequency crystal is stable by adding:

```

while(! (CLKCTRL.MCLKSTATUS & CLKCTRL_EXTS_bm))

{

;

}

```

3. Set the main clock source to be XOSCHF and enable the clock output pin by writing:

```

ccp_write_io((uint8_t *) &CLKCTRL.MCLKCTRLA, CLKCTRL_CLKSEL_EXTCLK_gc

| CLKCTRL_CLKOUT_bm);

```

**Info:** By enabling the clock out pin, it is possible to observe the main clock frequency on the CLKOUT (PA7) pin.

4. Wait for the main clock to switch successfully by polling the Main Clock Oscillator Change (SOSC) bit field in Main Clock Status (CLKCTRL.MCLKSTATUS) register:

```

while(CLKCTRL.MCLKSTATUS & CLKCTRL_SOSC_bm)

{

;

}

```

5. To save power, clear the Run Standby (RUNSTDBY) bit, so the oscillator is not running when it is not needed:

```

ccp_write_io((uint8_t *) &CLKCTRL.XOSCHFCTRLA, CLKCTRL_XOSCHFCTRLA &

~CLKCTRL_RUNSTDBY_bm);

```

**Result:** After adding all the code to configure XOSCHF, the `CLOCK_XOSCHF_crystal_init()` function will look like this:

```

void CLOCK_XOSCHF_crystal_init(void)

{

/* Enable crystal oscillator

* with frequency range 16MHz and 4K cycles start-up time

*/

ccp_write_io((uint8_t *) &CLKCTRL.XOSCHFCTRLA, CLKCTRL_RUNSTDBY_bm

| CLKCTRL_CSUTHF_4K_gc

| CLKCTRL_FRQRANGE_16M_gc

| CLKCTRL_SELHF_CRYSTAL_gc

| CLKCTRL_ENABLE_bm);

/* Confirm crystal oscillator start-up */

while(!(CLKCTRL.MCLKSTATUS & CLKCTRL_EXTS_bm))

{

;

}

//PORTA.DIRSET = PIN7_bm;

/* Set the main clock to use XOSCHF as source, and enable the CLKOUT pin */

ccp_write_io((uint8_t *) &CLKCTRL.MCLKCTRLA, CLKCTRL_CLKSEL_EXTCLK_gc

| CLKCTRL_CLKOUT_bm);

/* Wait for system oscillator changing to complete */

while(CLKCTRL.MCLKSTATUS & CLKCTRL_SOSC_bm)

{

;

}

/* Clear RUNSTDBY for power save when not in use */

ccp_write_io((uint8_t *) &CLKCTRL.XOSCHFCTRLA, CLKCTRL_XOSCHFCTRLA &

~CLKCTRL_RUNSTDBY_bm);

/* Change complete and the main clock is 16 MHz */

}

```

**Info:** The main function will be as follows, containing a call to the `CLOCK_XOSCHF_crystal_init()` function.

```

int main(void)

{

CLOCK_XOSCHF_crystal_init();

CLOCK_CFD_CLKMAIN_init();

LED0_init();

SW0_init();

/* Enable global interrupts */

sei();

/* Replace with your application code */

while(1)

{

LED0_toggle();

_delay_ms(200);

}

}

```

## 3.2

## Configure the CFD to Detect Failures on the Main Clock

## To do:

- Edit the `CLOCK_CFD_CLKMAIN_init()` function so that the CFD is set up to monitor the main clock and generates an NMI upon clock failure

- Set up the NMI handler

- Create a main clock failure using the software test

1. Enable the CFD and set the main clock as the source by adding:

```

ccp_write_io((uint8_t *) &CLKCTRL.MCLKCTRLC, CLKCTRL_CFDSRC_CLKMAIN_gc

| CLKCTRL_CFDEN_bm);

```

to `CLOCK_CFD_CLKMAIN_init()`.

2. Enable the CFD interrupt and set the interrupt type to NMI by writing:

```

ccp_write_io((uint8_t *) &CLKCTRL.MCLKINTCTRL, CLKCTRL_INNTYPE_bm

| CLKCTRL_CFD_bm);

```

**Info:** The CFD can create a normal interrupt or non-maskable interrupt depending on the setting in the Interrupt Type (INNTYPE) bit in the Main Clock Interrupt Control (CLKCTRL.MCLKINTCTRL) register. The advantage with an NMI is that the interrupt will trigger even if the microcontroller is in an interrupt or the global interrupt is disabled. This ensures that the interrupt will be executed straight away, and the error can be handled straight away. The only way to exit an NMI is by a device reset.

3. In the `ISR(NMI_vect)`, add the code to check if a CFD triggered the NMI and to blink the LED:

```

if(CLKCTRL.MCLKINTFLAGS & CLKCTRL_CFD_bm)

{

/* This interrupt will trigger if the source for the main clock fails

* and the CFD is able to switch to a different working clock.

* In this case that means XOSCHF has failed and is replaced by OSCHF.

* The main clock is therefore reduced to 4 MHz.

*/

/* Toggle the LED forever */

while(1)

{

LED0_toggle();

_delay_ms(200); // 200 ms calculated from 16 MHz == 800 ms

}

}

else

{

/* A different NMI has been triggered */

}

```

**Info:** There is only one interrupt vector for all the NMIs, so to be sure which NMI caused the interrupt, check the respective interrupt flags.

4. In the `ISR(PORTB_PORT_vect)`, add the code to trigger a clock failure when SW0 is pressed:

```

ccp_write_io((uint8_t *) &CLKCTRL.MCLKCTRLC, CLKCTRL_MCLKCTRLC | CLKCTRL_CFDST_bm);

```

**Info:** When setting the Clock Failure Detection Test (CFDTST) bit in the Main Clock Control C (MCLKCTRL) register, hardware simulates a clock failure to test the CFD feature.

5. Verify that the solution/project builds by selecting the *Build* → *Build Solution* from the top menu bar in Atmel Studio or by pressing the *F7* key.

6. Flash the device by selecting the *Debug* → *Start without debugging* from the top menu bar in Atmel Studio or by pressing the *Ctrl+Alt+F5* keys.

**Result:** After pressing SW0, the LED0 will start blinking with a lower frequency. This because the main clock source is switched to the start-up clock source, and the Main Clock Control B (CLKCTRL.MCLKCTRLB) register will be written to the reset value when a clock failure is detected. The number of clock ticks needed to create the `delay_ms` (200) is calculated using the XOSCHF clock frequency of 16 MHz, resulting in the `delay_ms` being four times as slow when the clock source is switched to the 4 MHz internal clock.

**Info:** The start-up clock source is decided by the Clock Select (CLKSEL) bit field in the Oscillator Configuration (OSCCFG) fuse.

As the MCLKCTRLB register is written to its default values by the CFD, the clock will not be available on the CLKOUT pin until it is set by the user again.

## 4. Assignment 2: CLKCTRL - High Frequency TCD using PLL

In this assignment, the AVR128DB48 Curiosity Nano will be configured to create a high-resolution PWM signal using TCD with the PLL as a clock source.

The PLL will increase the clock frequency of OSCHF.

The output from the PLL will be used as a clock source for TCD, which will create a high-resolution PWM signal.

The starting point for this assignment is the Atmel Studio Solution *Assignment2* found in *Assignment2*.

- **Objectives**

- Configure the PLL to use OSCHF as a clock source

- Configure the TCD to use the PLL as a clock source and output a PWM signal

- Visualize the PWM signal using a logic analyzer or an oscilloscope

### 4.1 Configure TCD to Use the PLL as a Clock Source

**To do:**

- Edit the `CLOCK_OSCHF_crystal_PLL_init()` to configure the PLL to use OSCHF as a source and multiply it by 3x

- Edit the `TIMER_TCDO_init()` so the TCD uses the PLL as a clock source and creates a PWM signal

- Plot the PWM signal using a logic analyzer

1. Edit `CLOCK_OSCHF_crystal_PLL_init()` so it sets the OSCHF frequency to 16 MHz by adding:

```

ccp_write_io((uint8_t *) &CLKCTRL.OSCHFCTRLA, CLKCTRL_FREQSEL_16M_gc);

```

**Info:** The minimum input frequency to the PLL is 16 MHz, and it has a maximum output of 48 MHz.

2. Set the PLL multiplication factor to 3x by adding the following to `CLOCK_OSCHF_crystal_PLL_init()`:

```

ccp_write_io((uint8_t *) &CLKCTRL.PLLCTRLA, CLKCTRL_MULFAC_3x_gc);

```

**Info:** The PLL has two input sources: The OSCHF and XOSCHF. The default source is OSCHF, but the XOSCHF can be configured by setting the Select Source for PLL (SOURCE) bit in the PLL Control A (PLLCTRLA) register.

3. Edit `TIMER_TCDO_init()` to include the following to set the PLL as the clock source with no prescaler:

```

TCD0.CTRLA = TCD_CLKSEL_PLL_gc | TCD_CNTPRES_DIV1_gc | TCD_SYNCCTRLA_gc;

```

4. Set the TCD to one ramp PWM mode by writing:

```

TCD0.CTRLB = TCD_WGMODE_ONERAMP_gc;

```

5. Make the PWM signal available on the pins by adding:

```

/*Set TCD pins as output*/

PORTA.DIRSET = PIN4_bm | PIN5_bm;

ccp_write_io((uint8_t *) &TCD0.FAULTCTRL, TCD_CMPAEN_bm | TCD_CMPBEN_bm);

```

# AVR® DB Family

## Assignment 2: CLKCTRL - High Frequency TCD ...

6. Enable the TCD by first ensuring that the Enable Ready (ENRDY) bit in the Status (TCDn.STATUS) register is set to '1' and then setting the ENABLE bit in Control A (TCDn.CTRLA) register:

```

/* Wait for synchronization */

while(! (TCD0.STATUS & TCD_ENRDY_bm))

{

;

}

/* Enable TCD0 */

TCD0.CTRLA |= TCD_ENABLE_bm;

```

**Info:** In addition to the configurations that have been set, the TCD is set to increment the duty cycle of WOA by one bit after every period. See `ISR(TCD0_OVF_vect)` how this is implemented.

7. Verify that the solution/project builds by selecting the *Build* → *Build Solution* from the top menu bar in Atmel Studio or by pressing the *F7* key.

8. Flash the device by selecting the *Debug* → *Start without debugging* from the top menu bar in Atmel Studio or by pressing the *Ctrl+Alt+F5* keys.

9. Plot the PWM signal using a Logic Analyzer the output for WOA is available on PA4, while the output for WOB is available on PA5.

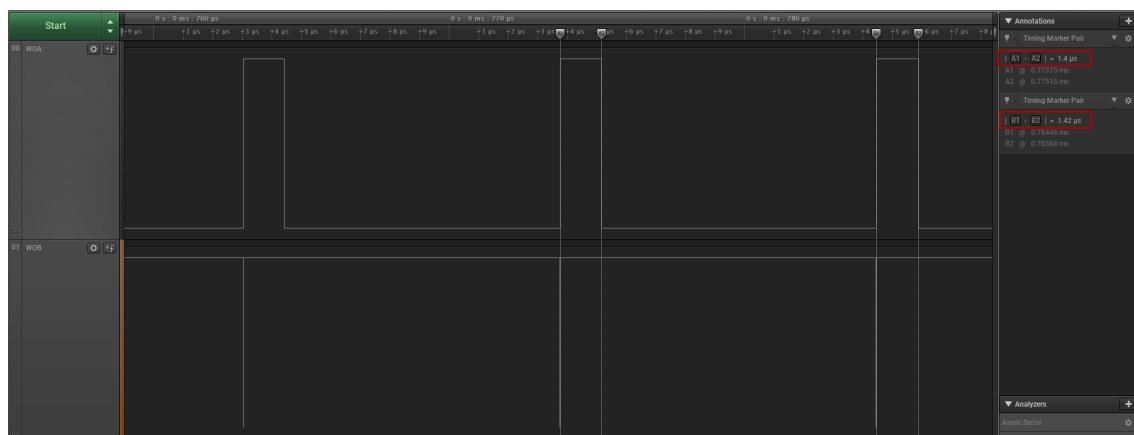

**Result:** The PLL and TCD are combined to create a very high-resolution PWM signal. In [Figure 4-1](#), you can see that the duty cycle is increased by about 20 ns from 1.4  $\mu$ s to 1.42  $\mu$ s after each period showing the high-resolution of the PWM signal.

**Figure 4-1. Assignment 2: Result**

## 5. Assignment 3: OPAMP - Voltage Follower

In this assignment, the AVR128DB48 Curiosity Nano will be configured to use the op amp OP0 in the Analog Signal Conditioning (OPAMP) peripheral as a voltage follower.

The Digital-to-Analog Converter (DAC) is configured to create a sinusoidal signal, which will be used as an input to the op amp.

The Analog-to-Digital Converter (ADC) is configured to sample the output of the op amp.

Both the input and output of the op amp are streamed over to the MPLAB® Data Visualizer using the data streamer protocol.

The starting point for this assignment is the Atmel Studio Solution *Assignment3* found in *Assignment3*.

- **Objectives**

- Understand the necessary steps to configure an op amp instance in the OPAMP peripheral

- Configure OP0 as a voltage follower

- Plot the input and output from OP0 using the MPLAB® Data Visualizer

### 5.1 Configure OP0 as a Voltage Follower

#### To do:

- Edit the `OPAMP0_init()` so it configures OP0 to be a voltage follower

- Plot the input and output of OP0 in the MPLAB® Data Visualizer

1. Edit `OPAMP0_init()` to set the time base for the OPAMP peripheral by writing:

```

OPAMP.TIMEBASE = OPAMP_TIMEBASE_US;

```

**Info:** For internal timing purposes, the Timebase (OPAMP.TIMBASE) register needs the maximum number of CLK\_PER cycles to achieve a timing interval equal to or larger than 1  $\mu$ s. The rule to determine what number to write into the TIMBASE is: Determine the number of CLK\_PER cycles equal to 1  $\mu$ s. If this is an integer, subtract one. If not, round it down. The following macro can be used to calculate the value for the TIMEBASE register:

```

#define OPAMP_TIMEBASE_US (ceil(F_CPU / 1e6) -1)

```

2. Set the output mode to normal and the Always On (ALWAYSON) bit for OP0 by writing:

```

OPAMP.OP0CTRLA = OPAMP_OP0CTRLA_OUTMODE_NORMAL_gc | OPAMP_ALWAYSON_bm;

```

**Info:** Each op amp instance in the OPAMP peripheral has an independent output mode. The two modes are off and normal. In the off mode, the output driver for the op amp is off but can be overwritten by the DRIVE event. In the normal mode, the driver is always on.

**Info:** Each op amp instance in the OPAMP peripheral can be individually turned on or off. This can be achieved either by setting/clearing the ALWAYSON bit or by the ENABLEn/DISABLEn events. If events are used to control the op amp, the ALWAYSON bit has to be cleared.

The Event Enable (EVENTEN) bit must be set in the OPnCTRA register to control the op amp using events

- Configure OP0 to be a voltage follower with the DAC as an input by writing:

```

OPAMP.OP0INMUX = OPAMP_OP0INMUX_MUXNEG_OUT_gc | OPAMP_OP0INMUX_MUXPOS_DAC_gc;

/* Configure the Op Amp n Resistor Wiper Multiplexer */

OPAMP.OP0RESMUX = OPAMP_OP0RESMUX_MUXBOT_OFF_gc | OPAMP_OP0RESMUX_MUXWIP_WIP0_gc |

OPAMP_OP0RESMUX_MUXTOP_OFF_gc;

```

**Info:**

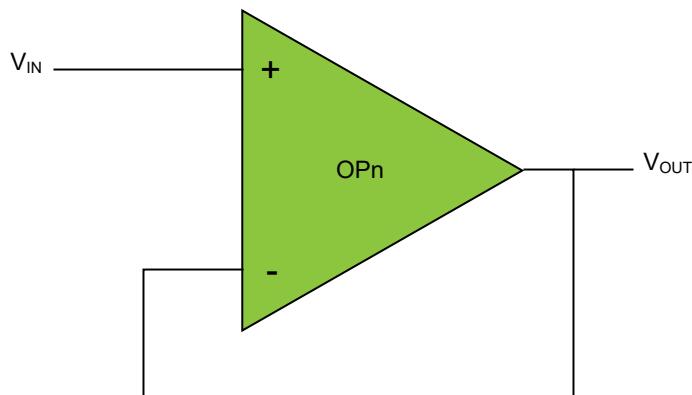

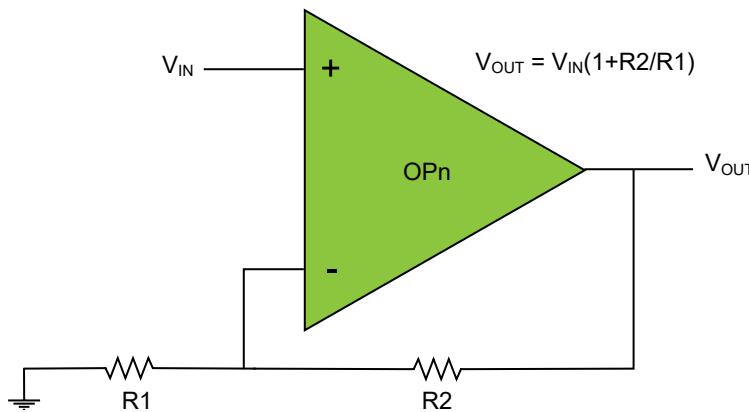

**Figure 5-1. Op Amp in Voltage Follower Configuration**

To achieve a voltage follower configuration, the output of the op amp needs to be connected directly to the negative input. This is done by setting the Multiplexer for Negative Input (MUXNEG) bit field in the Op Amp n Input Multiplexer (OPnMUX) register to OUT. The output of the DAC and the positive input to OP0 are connected through an internal channel by setting the Multiplexer for Positive Input (MUXPOS) bit field in the OPnMUX register to DAC. There is no need to use the resistor ladder in the voltage follower, so all the bit fields in the Op Amp n Resistor Ladder Multiplexer (OPnRESMUX) register can be set to their default values.

- Set the settling time by writing:

```

OPAMP.OP0SETTLE = OPAMP_MAX_SETTLE;

```

**Info:** The value in the Op Amp n Settle Timer (OPnSETTLE) register is the number of microseconds needed for the output of the op amp to settle. This time is highly application dependent. If it is not known, it is recommended to set it to the max value 0x7F. This value, together with the value in the TIMEBASE register, is used by an internal timer to determine when to generate the READYn event and set the SETTLED flag in the OPnSTATUS register.

- Enable the OPAMP peripheral by writing:

```

OPAMP.CTRLA = OPAMP_ENABLE_bm;

```

6. Wait for the op amp to settle before leaving the initialization by checking the Op Amp has Settled (SETTLED) bit field in the Op Amp n Status (OPnSTATUS) register:

```

while ( !(OPAMP.OP0STATUS & OPAMP_SETTLED_bm) )

{

;

}

```

7. Verify that the solution/project builds by selecting the *Build* → *Build Solution* from the top menu bar in Atmel Studio or by pressing the *F7* key.

8. Flash the device by selecting the *Debug* → *Start without debugging* from the top menu bar in Atmel Studio or by pressing the *Ctrl+Alt+F5* keys.

**Result:** The device is now flashed and ready to start streaming data to the MPLAB® *Data Visualizer*.

## 5.2 Plot Graph In MPLAB® Data Visualizer

The MPLAB® *Data Visualizer* is a program used to process and visualize data from a running embedded target. The program may be accessed as an MPLAB X IDE plugin or a stand-alone program. In this assignment, the *Data Visualizer* will be configured to graph the input and output of OP0 received over USART. The configuration is done through a saved workspace, and the basics of how to display the data are explained. To find out how to set up your own workspace, a detailed guide can be found by clicking on the *Documentation* button in MPLAB *Data Visualizer*.

**To do:** Configure MPLAB *Data Visualizer* to graph received OP0 input and output samples.

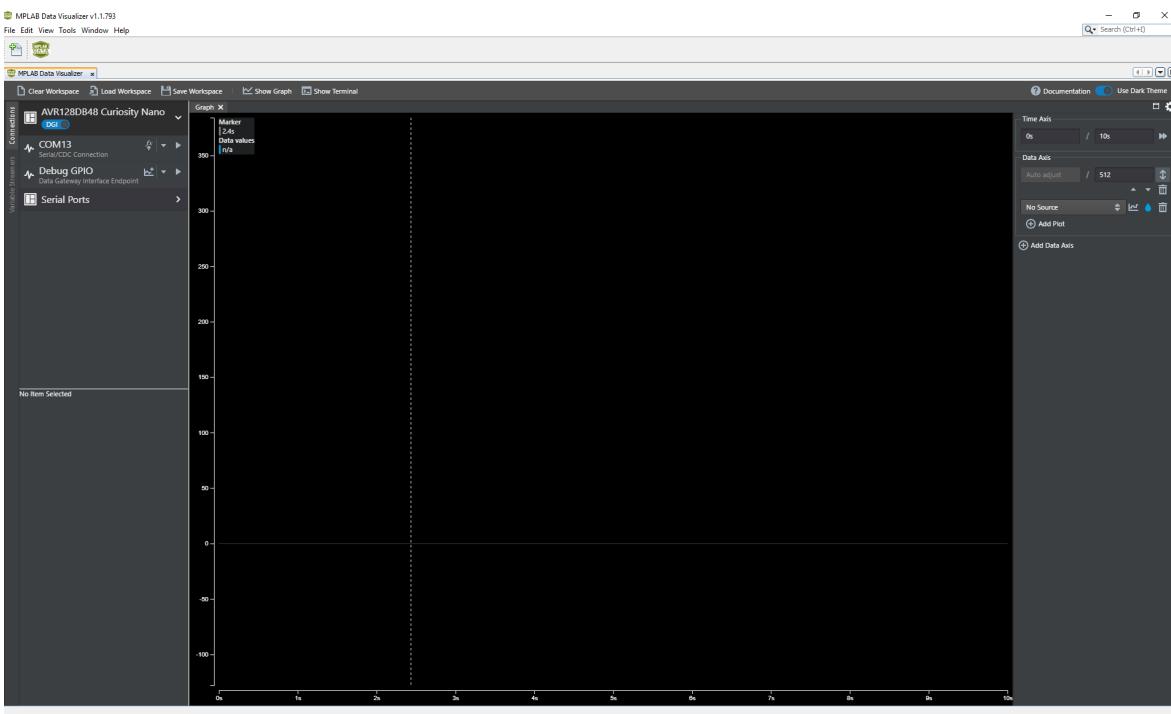

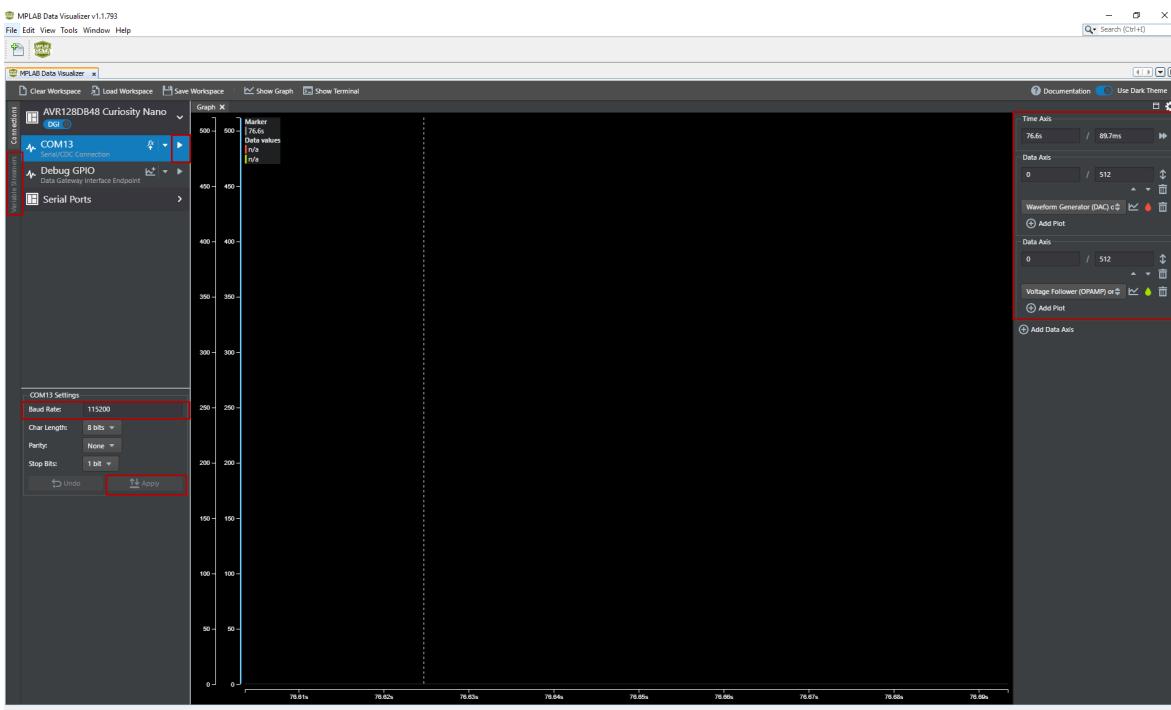

1. Open the program and plug in an already flashed device. Make sure the COM-port used for USART communication is not already in use. The start screen will be similar to [Figure 5-2](#).

# AVR® DB Family

## Assignment 3: OPAMP - Voltage Follower

Figure 5-2. Assignment 3: MPLAB® Data Visualizer Starting Page

- Load the workspace. Press the *Load Workspace* button and add the workspace-file called *Assignment3.json*. All the workspaces for this training can be found in *DataVisualizer*. Two axes appear in the graph. These can be configured on the panel on the right-hand side, as illustrated in [Figure 5-3](#).

Figure 5-3. Assignment 3: Data Visualizer Loaded Work Space

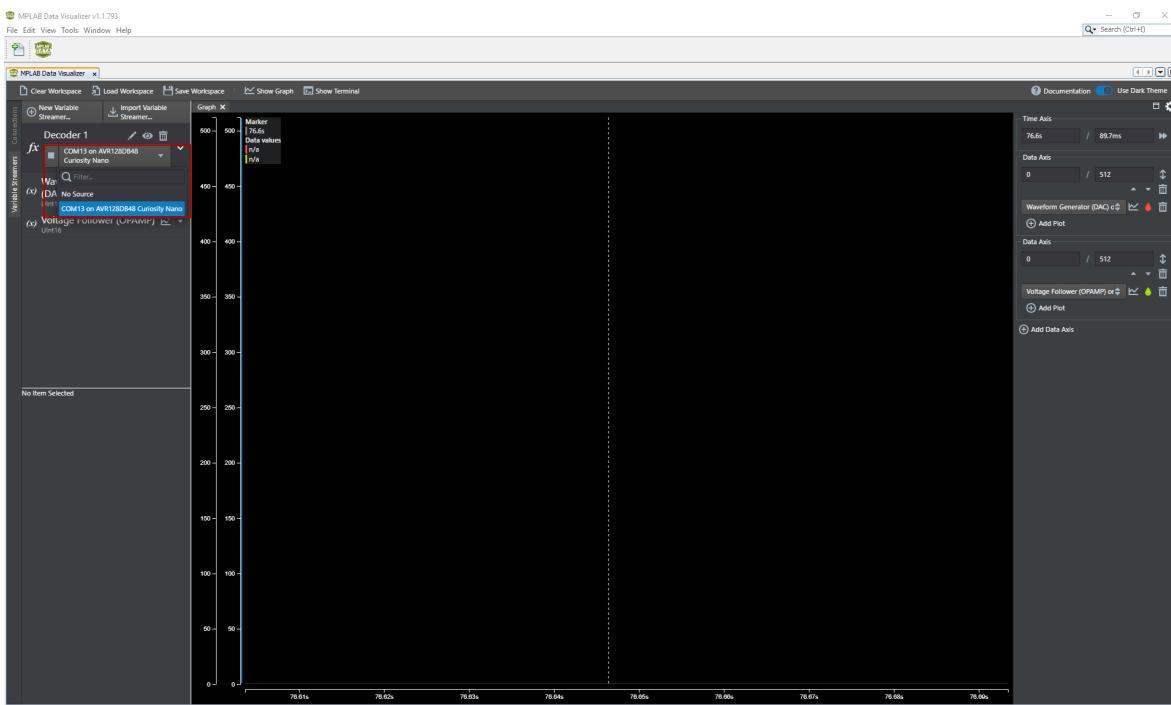

- Choose the COM-port on the left-hand side panel seen in [Figure 5-3](#) to plot the data. Make sure the *Baud Rate* is 115200 and press the *Apply* button to set the baud rate. Press the *Play* button next to the COM field

# AVR® DB Family

## Assignment 3: OPAMP - Voltage Follower

shown in [Figure 5-3](#). Press the *Variable Streamers* button to connect the decoder to the USART data stream. Set the COM port as input to Decoder 1, as shown in [Figure 5-4](#).

**Figure 5-4. Assignment 3: Variable Streamers**

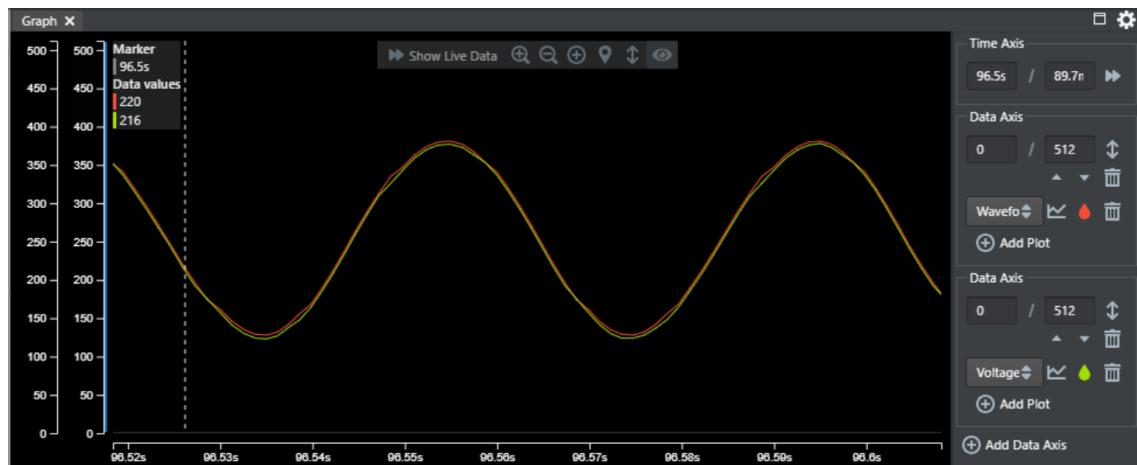

4. Press *Show Live Data* to start plotting live data from the device.

# AVR® DB Family

## Assignment 3: OPAMP - Voltage Follower

**Result:** The data streamed to the PC over USART are plotted in the MPLAB® Data Visualizer, as shown in [Figure 5-5](#). The red waveform is the output from the DAC, while the green is the output from the op amp. As expected, we can see that the output of the op amp closely follows the input to the op amp.

**Figure 5-5. Assignment 3: Result**

**Info:** The DAC outputs a 50 Hz sinusoidal wave with 256 mV<sub>pp</sub> and 256 mV DC offset. The sinusoidal wave is pre-calculated at startup in the `sine_wave_table_init()` function, and DAC updated with values upon TCB0 ISR (`SINE_WAVE_TIMER_vect`).

```

void sine_wave_table_init(void)

{

for(uint16_t i = 0; i < SINE_WAVE_STEPS; i++)

{

sine_wave[i] = SINE_DC_OFFSET + SINE_AMPLITUDE * sin(i * M_2PI /

SINE_WAVE_STEPS);

}

}

ISR(SINE_WAVE_TIMER_vect) {

volatile static uint16_t sine_wave_index = 0

data_stream.dacVal = sine_wave[sine_wave_index];

DAC0_setVal(data_stream.dacVal);

sine_wave_index++;

sine_wave_index = sine_wave_index % SINE_WAVE_STEPS;

/* Clear interrupt flag */

SINE_WAVE_TIMER.INTFLAGS = TCB_CAPT_bm;

}

```

## 6. Assignment 4: OPAMP - Non-Inverting PGA

In this assignment, the AVR128DB48 Curiosity Nano will be configured to use the op amp OP0 in the Analog Signal Conditioning (OPAMP) peripheral as a non-inverting programmable gain amplifier, shown in the block diagram below.

The configuration is done through Atmel START.

The Digital-to-Analog Converter (DAC) is configured to create a sinusoidal signal, which will be used as an input to the op amp.

The Analog-to-Digital Converter (ADC) is configured to sample the output of the op amp. Both the input and output of the op amp is streamed over to the MPLAB® Data Visualizer using the data streamer protocol.

The circuit will also be simulated using MPLAB® Mindi™ Analog Simulator and a pre-made schematic containing a full model of the AVR DB op amp. The schematic is available at [github.com/microchip-pic-avr-examples/avrdb-opamp-mindi-non-inverting-pga](https://github.com/microchip-pic-avr-examples/avrdb-opamp-mindi-non-inverting-pga).

**Info:** The schematic file (\*.wxsch), uses the encrypted model (\*.lb) so as to not count towards the node simulation limit in Mindi™. If desired an unencrypted version of the model (\*.txt) can be found in the same location, for use with a full version of simulation tools.

The starting point for this assignment is the Atmel Studio Solution *Assignment4* found in *Assignment4*.

- **Objectives**

- Simulate the non-inverting PGA using the pre-made schematic containing a model of the AVR DB op amp

- Understand how to configure an op amp in Atmel START

- Configure OP0 instance of the OPAMP, as non-inverting PGA using Atmel START

- Plot the input and output from OP0 using the MPLAB® Data Visualizer

### 6.1 Simulating Non-Inverting PGA in Mindi™

#### To do:

- Download the pre-made non-inverting PGA simulation file containing the AVR DB op amp model

- Run the simulation

# AVR® DB Family

## Assignment 4: OPAMP - Non-Inverting PGA

1. Go to [github.com/microchip-pic-avr-examples/avrdb-opamp-mindi-non-inverting-pga/releases](https://github.com/microchip-pic-avr-examples/avrdb-opamp-mindi-non-inverting-pga/releases) and press the Source code (zip) link to download the simulation.

**Info:** All the pre-made simulations can be found at [github.com/search?l=&q=org%3Amicrochip-pic-avr-examples+avrdb+in%3Aname+extension%3Awxsch&type=repositories](https://github.com/search?l=&q=org%3Amicrochip-pic-avr-examples+avrdb+in%3Aname+extension%3Awxsch&type=repositories).

2. Unzip the folder to your location of choice.

3. Open MPLAB® Mindi™, press *File*→*Open* or *Ctrl+o*, and locate the file *Non\_Inverting\_PGA.wxsch* in the location where the zip file was extracted.

4. Simulate by pressing the *Run Schematic* button.

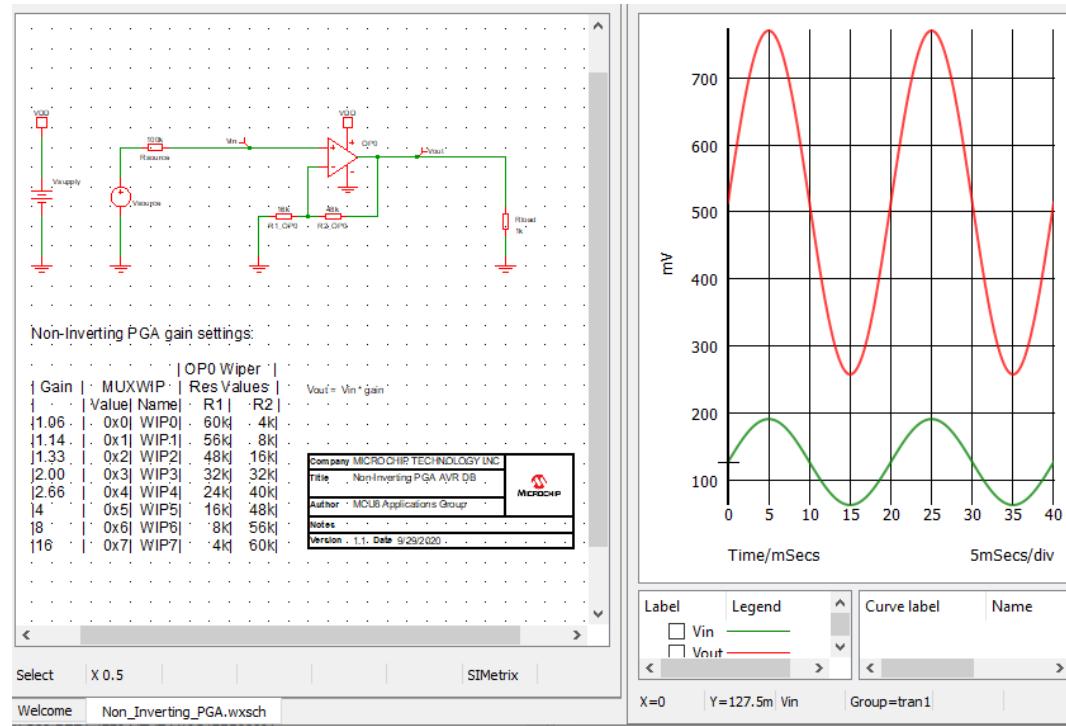

**Result:** If everything worked correctly, the plot of the simulation, as shown in [Figure 6-1](#), should come up.

**Figure 6-1. Assignment 4: MPLAB® Mindi™ Plot**

5. Change the resistors R1\_OP0 and R2\_OP0 to the ones corresponding to WIP3. This will set the gain to 2x.

6. Simulate with the new resistor values by pressing *Run Schematic*.

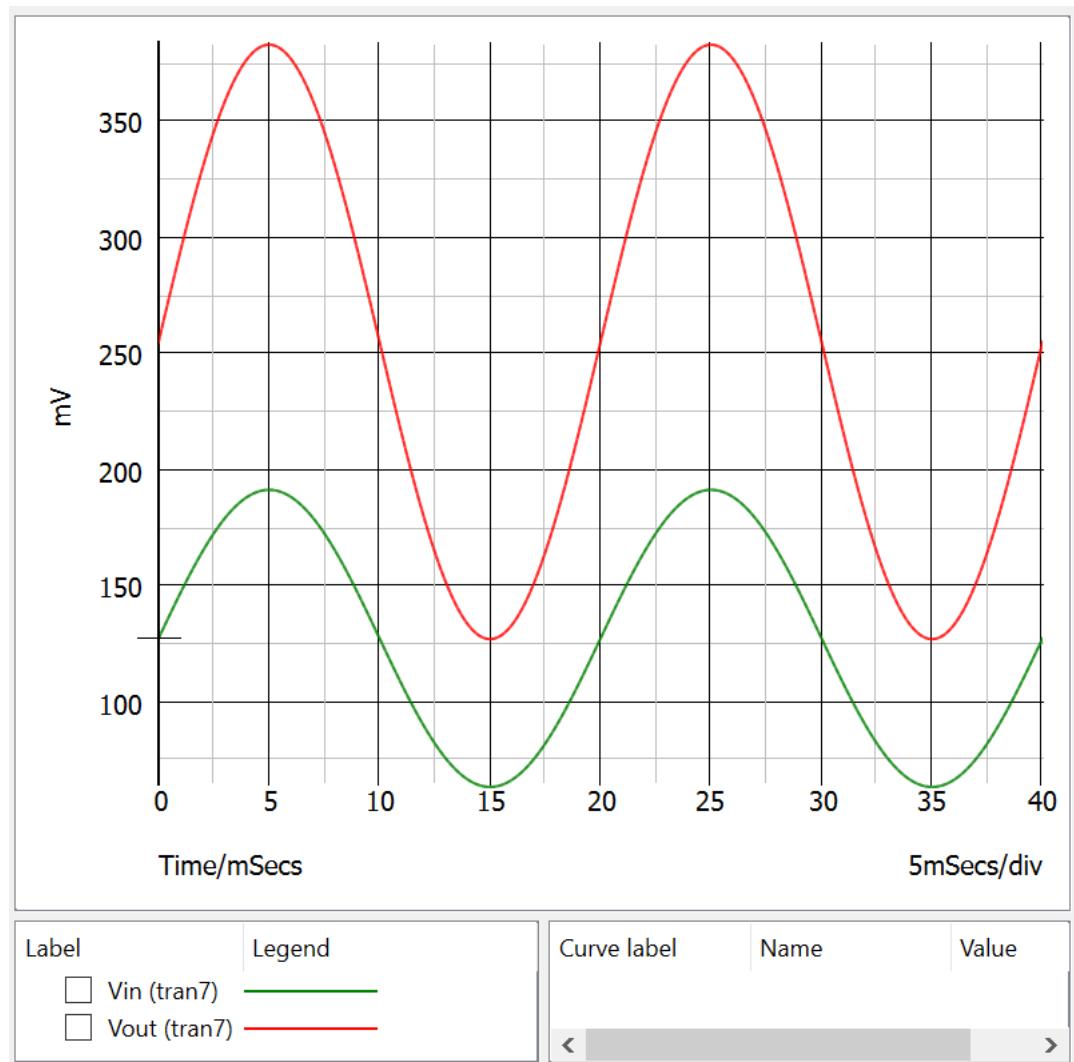

**Result:** The plot in MPLAB® Mindi™ should look similar to the one in [Figure 6-2](#), where the red waveform is the output from the op amp, and the green is the input. As expected, the output is twice as large as the input.

**Figure 6-2. Assignment 4: Mindi™ Result**

## 6.2

### Configure OP0 as a Non-Inverting PGA Using Atmel START

#### To do:

- Edit the Atmel START project, so OP0 is configured as a non-inverting PGA

- Plot the input and output of OP0 in the MPLAB® Data Visualizer

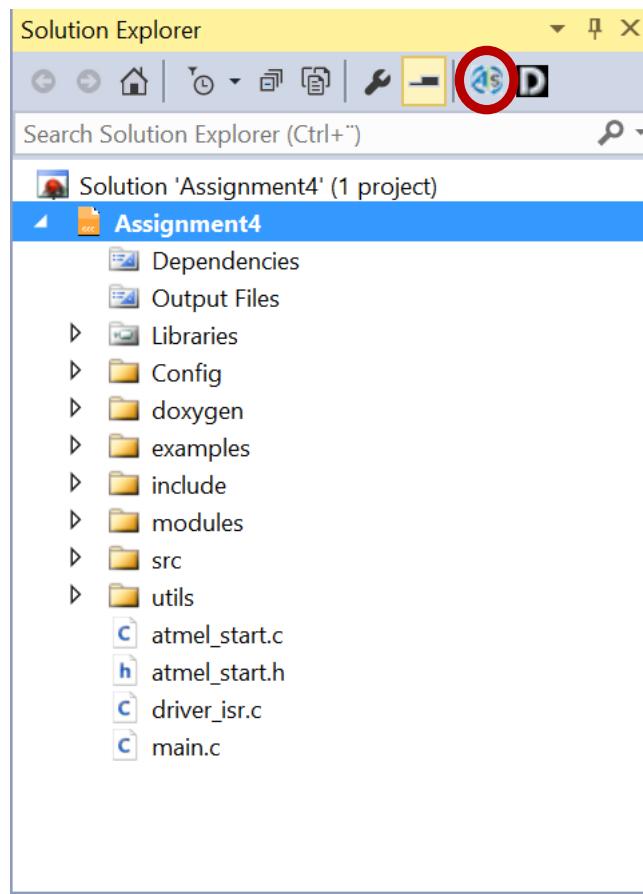

1. Press the *Reconfigure Atmel Start Project* button marked with a red circle in [Figure 6-3](#) to reconfigure the project.

Figure 6-3. Assignment 4: Reconfigure Atmel START

2. Press the *Add software component* button, search for op amp, press the plus button and the *Add component(s)* to add the op amp driver to the project.

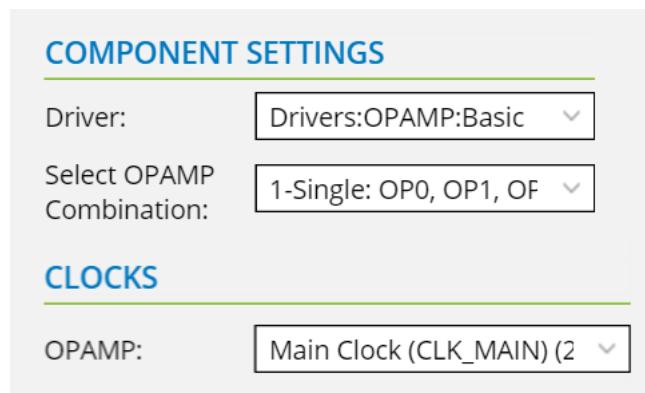

3. Press the *OPERATIONAL\_AMPLIFIER\_0* to be able to configure the OPAMP peripheral.

4. Make sure the COMPONENT SETTINGS and CLOCK is as shown in [Figure 6-4](#).

Figure 6-4. Assignment 4: Component Settings

# AVR® DB Family

## Assignment 4: OPAMP - Non-Inverting PGA

**Info:** The Select OPAMP combination determines if the op amps are configured individually or combined to create multi op amp configurations. Not every configuration is available for every combination of op amps. See the START driver user guide for an overview. It is also provided below.

**Figure 6-5. Assignment 4: OPAMP User Guid**

| Single OPAMP               | OP0 | OP1 | OP2 |

|----------------------------|-----|-----|-----|

| Directly Connected to Pins | X   | X   | X   |

| Non-Inverting PGA          | X   | X   | X   |

| Inverting PGA              | X   | X   | X   |

| Voltage Follower           | X   | X   | X   |

| Integrator                 | X   | X   | X   |

| Custom                     | X   | X   | X   |

| Dual OPAMP                               | OP0-OP1 | OP1-OP2 | OP2-OP0 |

|------------------------------------------|---------|---------|---------|

| Differential Amplifier using Two Op Amps | X       | X       | X       |

| Cascaded (Two) Non-Inverting PGA         | X       | X       |         |

| Cascaded (Two) Inverting PGA             | X       | X       | X       |

| Triple OPAMP               | OP0-OP1-OP2 | OP1-OP2-OP0 | OP2-OP0-OP1 |

|----------------------------|-------------|-------------|-------------|

| Instrumentation Amplifier  | X           |             |             |

| Cascaded Non-Inverting PGA | X           |             |             |

| Cascaded Inverting PGA     | X           | X           | X           |

'X' represents supported instances

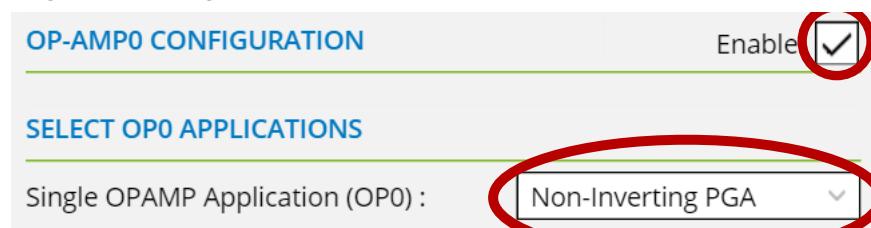

5. Make sure that OP0 is enabled by checking the OP-AMP0 CONFIGURATION Enable. Checkmark and configure the op amp as a non-inverting PGA by selecting Non-Inverting PGA in the Single OPAMP Application (OP0) drop-down menu as shown in [Figure 6-6](#).

**Figure 6-6. Assignment 4: Single OPAMP Applications**

6. Set the OPAMP0 SETTINGS, as shown in [Figure 6-7](#). This will set the DAC as an input to the op amp, and the non-inverting PGA will have a gain of 2.

**Figure 6-7. Assignment 4: OPAMP0 SETTINGS**

**OPAMP0 SETTINGS**

|                                            |                                                                                         |

|--------------------------------------------|-----------------------------------------------------------------------------------------|

| MUXPOS: Multiplexer for Positive input:    | <input type="button" value="?"/> <input type="button" value="DAC output"/>              |

| MUXNEG: Multiplexer for Negative input:    | <input type="button" value="?"/> <input type="button" value="Wiper from OPn's resis"/>  |

| MUXTOP: Multiplexer for Top:               | <input type="button" value="?"/> <input type="button" value="OPn output"/>              |

| MUXBOT: Multiplexer for Bottom:            | <input type="button" value="?"/> <input type="button" value="Ground"/>                  |

| MUXWIP: Multiplexer for Wiper Multiplexer: | <input type="button" value="?"/> <input type="button" value="R1 = 8R, R2 = 8R, R2/R1"/> |

| Gain:                                      | <input type="button" value="2"/>                                                        |

**Info:** The grayed out options are options that cannot change as that will break the chosen configurations, but they are still visible to inform the user what kind of settings are needed for the configuration.

7. Set the HARDWARE SETTINGS to what is shown in [Figure 6-8](#). It should be the default values.

**Figure 6-8. Assignment 4: Hardware Settings**

**HARDWARE SETTINGS**

|                                |                                                                                       |

|--------------------------------|---------------------------------------------------------------------------------------|

| ALWAYSON: Always ON:           | <input checked="checked" type="checkbox"/>                                            |

| EVENTEN: Event Enable:         | <input type="checkbox"/>                                                              |

| OUTMODE: Output Mode:          | <input type="button" value="?"/> <input type="button" value="Output Driver in Norm"/> |

| RUNSTDBY: Run is standby mode: | <input type="checkbox"/>                                                              |

| Settle Time:                   | <input type="button" value="?"/> <input type="button" value="0x7f"/> hex              |

8. Press *GENERATE PROJECT* to regenerate the start project with the newly added op amp settings.

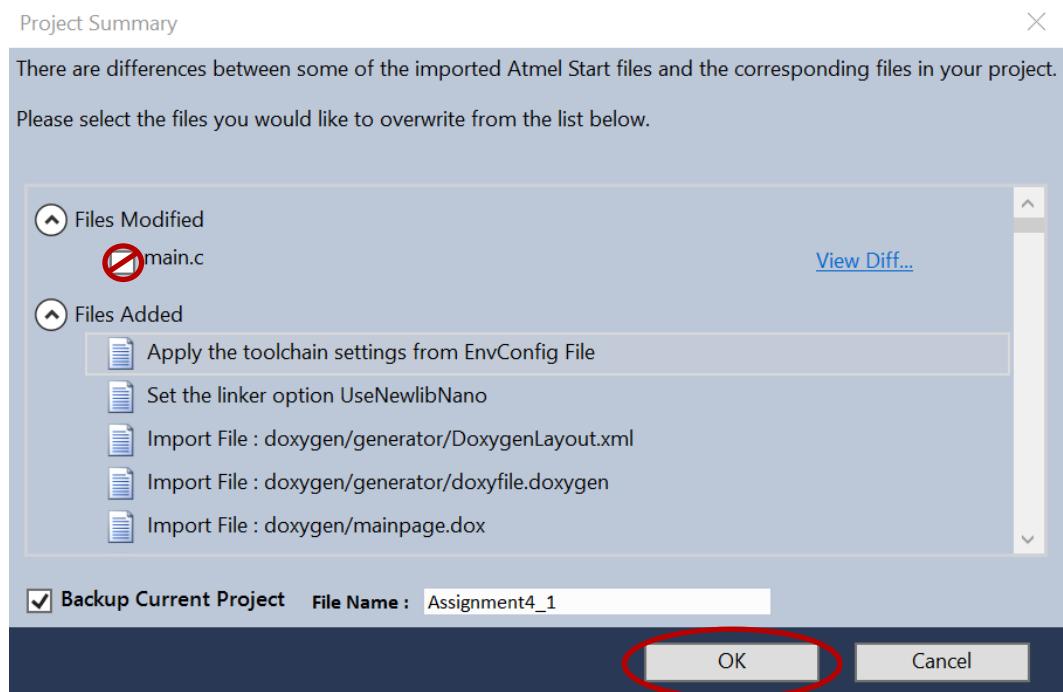

There will pop up a window called Project Summary shown in [Figure 6-9](#). Press okay and do not check the checkmark next to main.c. If this is done, the project custom changes in main.c will be overwritten and lost, and the project will not work.

**Figure 6-9. Assignment 4: Project Summary**

9. Verify that the solution/project builds by selecting the *Build* → *Build Solution* from the top menu bar in Atmel Studio or by pressing the *F7* key.

10. Flash the device by selecting the *Debug* → *Start without debugging* from the top menu bar in Atmel Studio or by pressing the *Ctrl+Alt+F5* keys.

11. Plot the DAC output vs. the op amp output using the **MPLAB® Data Visualizer** by loading the workspace *Assignment4.json*.

**Info:** The DAC outputs a 50 Hz sinusoidal wave with 128 mV<sub>pp</sub> and a DC offset of 128 mV.

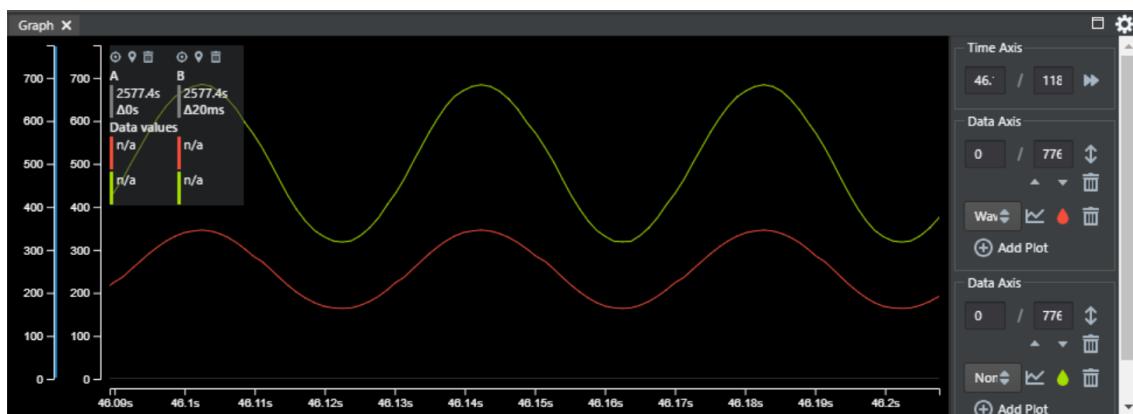

**Result:** The plot in the MPLAB® Data Visualizer should look similar to the one in Figure 6-10. The red waveform is the output from the DAC, while the green is the output from the op amp. As expected, the output from the op amp is two times as large as the output from the DAC. This also matches what we saw in the simulations earlier in the assignment.

**Figure 6-10. Assignment 4: Result**

## 7. Assignment 5: MVIO - OPAMP as a Regulated Power Supply for VDDIO2

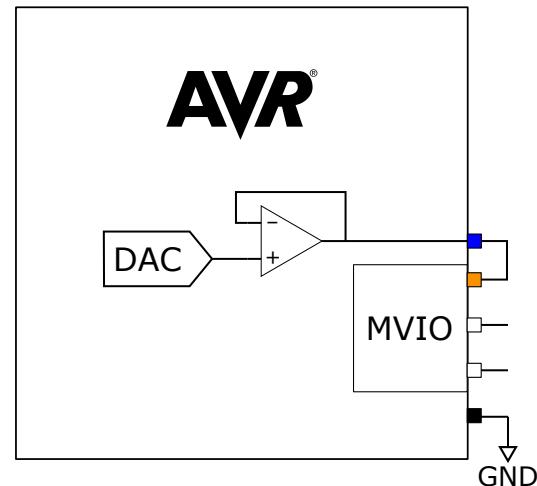

In this assignment, the AVR128DB48 Curiosity Nano will be configured to use two voltage domains  $V_{DD}$  and  $V_{DDIO2}$ .  $V_{DD}$  is supplied by the CNANO voltage regulator, while  $V_{DDIO2}$  is supplied by OP0, which is configured as a voltage follower with the DAC as an input. The reason the DAC is not used directly to supplying  $V_{DDIO2}$  is that the DAC can source very little current compared to the op amp.

The Digital-to-Analog Converter (DAC) is configured to create the input voltage to OP0. Therefore, the output from the DAC will be the voltage level for  $V_{DDIO2}$ .

The Analog-to-Digital Converter (ADC) is configured to sample  $V_{DDIO2}$  divided by 10. The measured  $V_{DDIO2}$  is streamed over to the MPLAB® Data Visualizer using the data streamer protocol.

The starting point for this assignment is the Atmel Studio Solution *Assignment5* found in *Assignment5*.

- **Objectives**

- Understand how the AVR DB can work with two different voltage domains

- Use the ADC to measure  $V_{DDIO2}$  using the internal connection

- Plot the measured  $V_{DDIO2}$  using the MPLAB® Data Visualizer

### 7.1 MVIO Hardware Setup

#### To do:

- Modify the AVR128DB48 Curiosity Nano to work with two voltage domains

- Set the AVR128DB48 Curiosity Nano fuses so it operates with two voltage domains

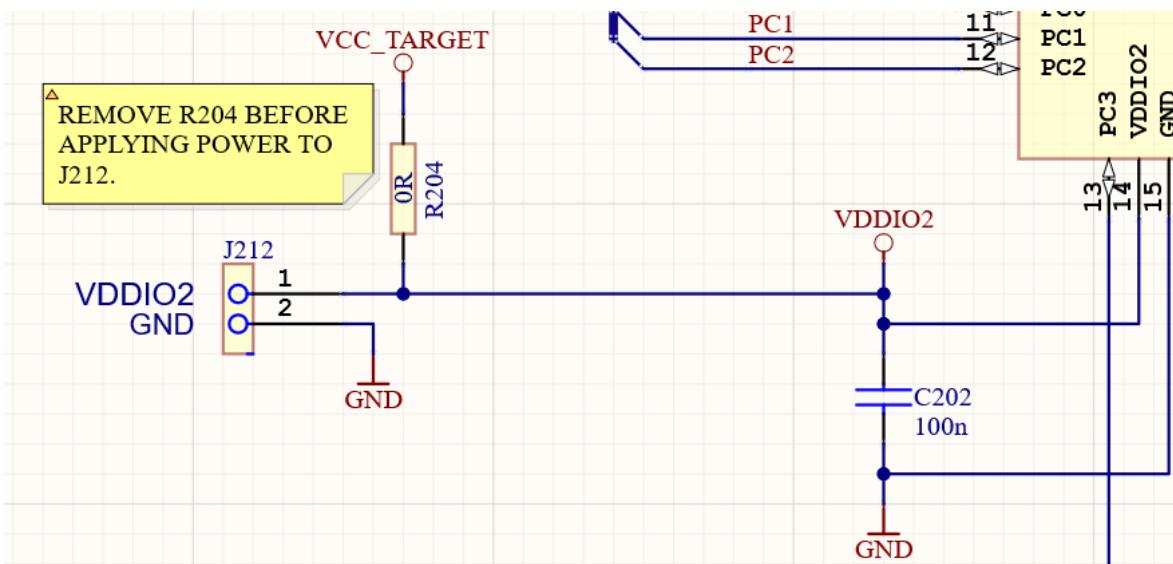

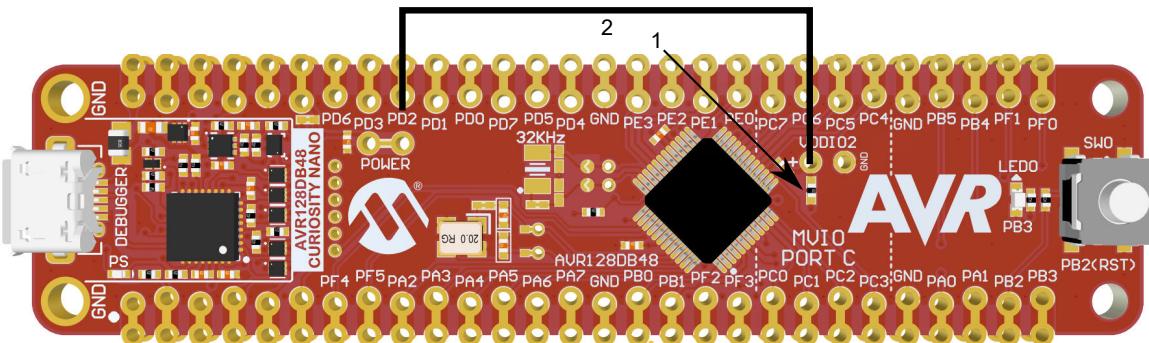

1. Remove the resistor right below the VDDIO2 label to disconnect VDDIO2 from VDD. This is the resistor R204 in [Figure 7-1](#), pointed to by the arrow in [Figure 7-2](#).

**Figure 7-1. Assignment 6: VDDIO2 Schematic**

2. Connect a wire between PD2 and VDDIO2+, as shown in [Figure 7-2](#).

## Figure 7-2. Assignment 5: Curiosity Nano AVR128DB48

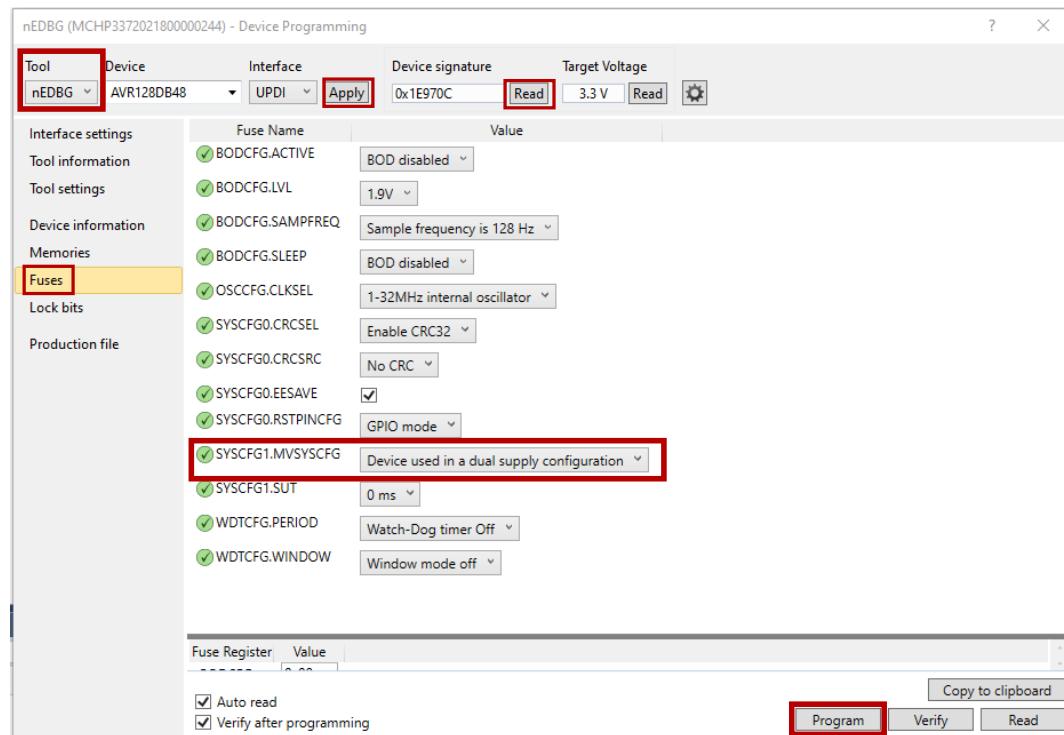

3. Set the MVSYSCFG bit field in the System Configuration 1 (SYSCFG) fuse to DUAL.

**Info:** To program fuses in Atmel Studio, press *Tools*→*Device Programming* to get the Device Programming window. Under Tools, select the nEDBG, then press *Apply* followed by *Read*. Press *Fuses* and set SYSCFG1.MVSYSCFG to “Device used in a dual supply configuration.” The window should then look like in [Figure 7-3](#). Press *Program* to program the current fuse settings onto the device.

**Figure 7-3. Assignment 5: Atmel Studio Fuse Programming**

**Result:** The AVR128DB48 Curiosity Nano CNANO is ready to run with two power domains.

## 7.2 Measuring VDDIO2 Using the ADC

### To do:

- Understand how the op amp and DAC combine to create a power supply for V<sub>DDIO2</sub>

- Edit `adc0_init()` so it configures the ADC to measure V<sub>DDIO2</sub>

- Plot the measured V<sub>DDIO2</sub> values in MPLAB® Data Visualizer

1. Study the `op_amp_init()` function to see how OP0 is configured as a voltage follower with the DAC as an input.

2. Study the `dac_init()` function to see how it outputs a constant voltage called V<sub>DDIO2</sub>, which is defined in `dac.h`.

**Info:** Combining the DAC and op amp with the hardware modifications used earlier in this assignment, the op amp will be a power supply for V<sub>DDIO2</sub>. This is illustrated in [Figure 7-4](#).

**Figure 7-4. Assignment 5: Op Amp as a Power Supply**

3. In the `adc0_init()` function, set VDDIO2DIV10 as an input to the ADC by writing:

```

ADC0.MUXPOS = ADC_MUXPOS_VDDIO2DIV10_gc;

```

4. Verify that the solution/project builds by selecting the *Build* → *Build Solution* from the top menu bar in Atmel Studio or by pressing the *F7* key.

5. Flash the device by selecting the *Debug* → *Start without debugging* from the top menu bar in Atmel Studio or by pressing the *Ctrl+Alt+F5* keys.

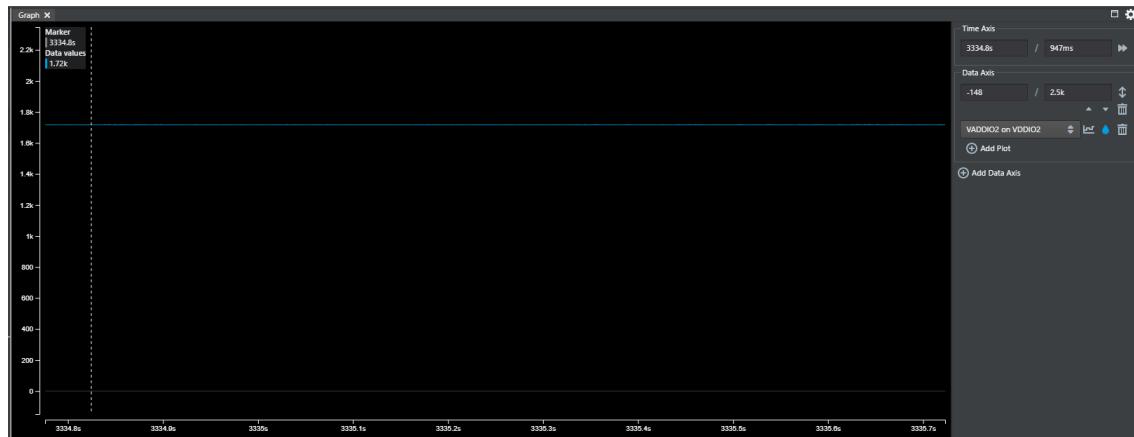

6. Plot the measured ADC reading in the MPLAB® Data Visualizer by loading the workspace *Assignment6.json*.

**Result:** The ADC measurements are plotted in MPLAB® Data Visualizer, as shown in [Figure 7-5](#). Note that the unit is millivolts.

**Figure 7-5. Assignment 5: Result**

## 8. Assignment 6: MVIO - VDDIO2 Failure Detection

In this assignment, the AVR128DB48 Curiosity Nano will be configured to use two voltage domains  $V_{DD}$  and  $V_{DDIO2}$ .  $V_{DD}$  is supplied by the CNANO voltage regulator, while  $V_{DDIO2}$  is supplied by OP0, which is configured as a voltage follower with the DAC as an input.

The Digital-to-Analog Converter (DAC) is configured to create the input voltage to OP0. The output from the DAC will therefore be the voltage level for  $V_{DDIO2}$ .

The Analog-to-Digital Converter (ADC) is configured to sample  $V_{DDIO2}$  divided by 10. The measured  $V_{DDIO2}$  is streamed over to the MPLAB® Data Visualizer using the data streamer protocol.

When SW0 is pressed, the output from the DAC will be reduced, resulting in a VDDIO2 interrupt detecting the failure on the VDDIO2 line.

The starting point for this assignment is the Atmel Studio Solution *Assignment6* found in *Assignment6*.

- **Objectives**

- Introduce an error to  $V_{DDIO2}$  by lowering the supply voltage below its specifications

- Understand how the AVR DB can detect that  $V_{DDIO2}$  falls below its minimum requirement

- Use the ADC to measure  $V_{DDIO2}$  using the internal connection

- Plot the measured  $V_{DDIO2}$  using the MPLAB® Data Visualizer

### 8.1 Set Up VDDIO2 Failure Detection

**To do:**

- Edit `mvio_init()` so it enables the VDDIO2 status change interrupt

- Edit `ISR(MVIO_MVIO_vect)` to handle the VDDIO2 status change interrupt

- Plot the measured  $V_{DDIO2}$  values in MPLAB® Data Visualizer

This assignment assumes the hardware setup steps described in Assignment 6 have been completed. If they have not been completed, the step-by-step instructions can be found in [7.1 MVIO Hardware Setup](#).

**Info:** The DAC, ADC and OPAMP peripheral are all configured in the same way as it was done for assignment 6. The description of the setup can be found in [7.2 Measuring VDDIO2 Using the ADC](#).

1. Enable the VDDIO2 status change interrupt by editing `mvio_init()` to include:

```

MVIO.INTCTRL = MVIO_VDDIO2IE_bm;

```

2. Handle the interrupt by clearing the interrupt flag and toggling LED0 by adding the following to `ISR(MVIO_MVIO_vect)`:

```

MVIO.INTFLAGS = MVIO_VDDIO2IF_bm;

LED0_toggle();

```

3. Understand how the  $V_{DDIO2}$  fault is injected when SW0 is pressed by lowering the op amp output by looking at the `ISR(PORTB_PORT_vect)` found in `gpio.c`.

**Info:** When  $V_{DDIO2}$  goes below the acceptable range, the VDDIO2 Status bit goes low, triggering the VDDIO2 status change interrupt. When  $V_{DDIO2}$  is below the acceptable range, all the pins on PORTC are tri-stated. When  $V_{DDIO2}$  goes back up again, the values from the PORTC registers are loaded again.

---

4. Verify that the solution/project builds by selecting the *Build* → *Build Solution* from the top menu bar in Atmel Studio or by pressing the *F7* key.

5. Flash the device by selecting the *Debug* → *Start without debugging* from the top menu bar in Atmel Studio or by pressing the *Ctrl+Alt+F5* keys.

6. Plot the measured ADC reading and the status of LED0 in *MPLAB® Data Visualizer* by loading the workspace Assignment7.json.

**Info:** LED0 is active low, so the plot in *MPLAB® Data Visualizer* will show '0' when the led is lighting and '1' when it is off.

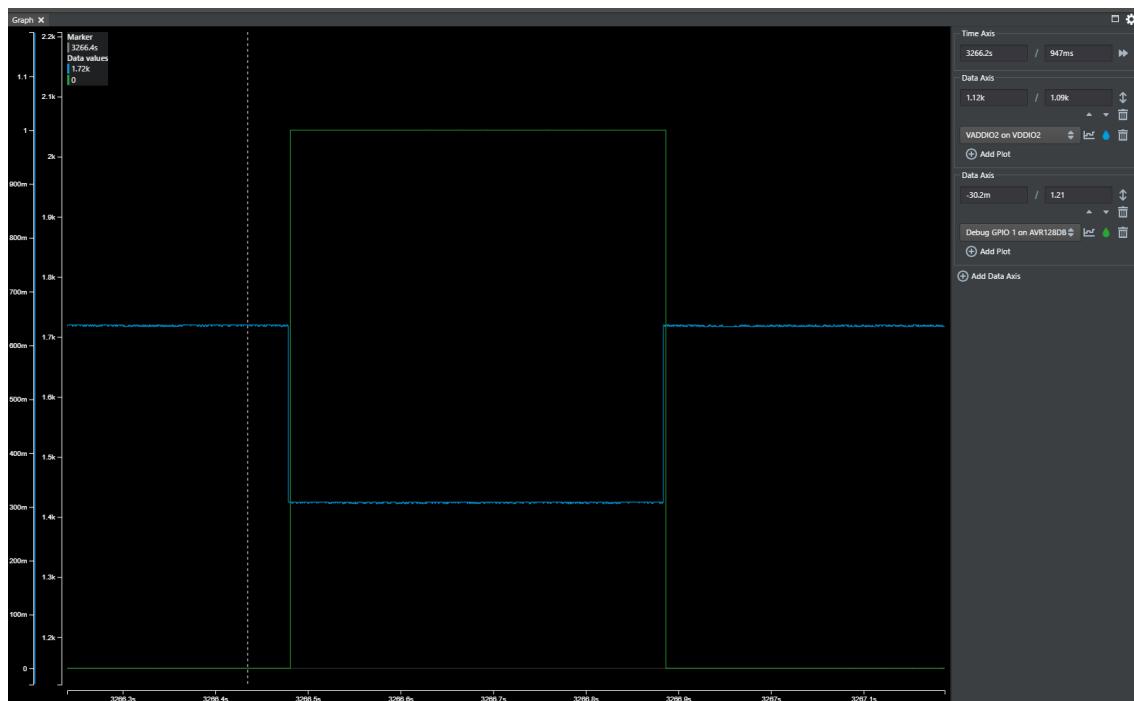

**Result:** The ADC measurements and SW0 states are plotted in *MPLAB® Data Visualizer*, as shown in [Figure 8-1](#). It can be seen that as soon as SW0 is pressed and  $V_{DDIO2}$  goes below the acceptable value, the VDDIO2 status change interrupt triggers, and the LED0 line goes high. When SW0 is pressed again and  $V_{DDIO2}$  goes back into the acceptable range, the LED0 goes back low. The blue line is the  $V_{DDIO2}$  reading, while the green line is LED0.

**Figure 8-1. Assignment 6: Result**

## **9. Revision History**

| Doc. Rev. | Date    | Comments                 |

|-----------|---------|--------------------------|

| A         | 11/2020 | Initial document release |

## The Microchip Website

Microchip provides online support via our website at [www.microchip.com/](http://www.microchip.com/). This website is used to make files and information easily available to customers. Some of the content available includes:

- **Product Support** – Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- **General Technical Support** – Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- **Business of Microchip** – Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## Product Change Notification Service

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to [www.microchip.com/pcn](http://www.microchip.com/pcn) and follow the registration instructions.

## Customer Support

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Embedded Solutions Engineer (ESE)

- Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: [www.microchip.com/support](http://www.microchip.com/support)

## Microchip Devices Code Protection Feature

Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features of the Microchip devices. We believe that these methods require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is "unbreakable." Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

## Legal Notice

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUENTIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

## Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SMART-I.S., storClad, SQi, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2020, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-7066-3

## **Quality Management System**

---

For information regarding Microchip's Quality Management Systems, please visit [www.microchip.com/quality](http://www.microchip.com/quality).

## Worldwide Sales and Service

| AMERICAS                                                                                                                                                                                                                                                                                               | ASIA/PACIFIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ASIA/PACIFIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | EUROPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Corporate Office</b><br>2355 West Chandler Blvd.<br>Chandler, AZ 85224-6199<br>Tel: 480-792-7200<br>Fax: 480-792-7277<br>Technical Support:<br><a href="http://www.microchip.com/support">www.microchip.com/support</a><br>Web Address:<br><a href="http://www.microchip.com">www.microchip.com</a> | <b>Australia - Sydney</b><br>Tel: 61-2-9868-6733<br><b>China - Beijing</b><br>Tel: 86-10-8569-7000<br><b>China - Chengdu</b><br>Tel: 86-28-8665-5511<br><b>China - Chongqing</b><br>Tel: 86-23-8980-9588<br><b>China - Dongguan</b><br>Tel: 86-769-8702-9880<br><b>China - Guangzhou</b><br>Tel: 86-20-8755-8029<br><b>China - Hangzhou</b><br>Tel: 86-571-8792-8115<br><b>China - Hong Kong SAR</b><br>Tel: 852-2943-5100<br><b>China - Nanjing</b><br>Tel: 86-25-8473-2460<br><b>China - Qingdao</b><br>Tel: 86-532-8502-7355<br><b>China - Shanghai</b><br>Tel: 86-21-3326-8000<br><b>China - Shenyang</b><br>Tel: 86-24-2334-2829<br><b>China - Shenzhen</b><br>Tel: 86-755-8864-2200<br><b>China - Suzhou</b><br>Tel: 86-186-6233-1526<br><b>China - Wuhan</b><br>Tel: 86-27-5980-5300<br><b>China - Xian</b><br>Tel: 86-29-8833-7252<br><b>China - Xiamen</b><br>Tel: 86-592-2388138<br><b>China - Zhuhai</b><br>Tel: 86-756-3210040 | <b>India - Bangalore</b><br>Tel: 91-80-3090-4444<br><b>India - New Delhi</b><br>Tel: 91-11-4160-8631<br><b>India - Pune</b><br>Tel: 91-20-4121-0141<br><b>Japan - Osaka</b><br>Tel: 81-6-6152-7160<br><b>Japan - Tokyo</b><br>Tel: 81-3-6880- 3770<br><b>Korea - Daegu</b><br>Tel: 82-53-744-4301<br><b>Korea - Seoul</b><br>Tel: 82-2-554-7200<br><b>Malaysia - Kuala Lumpur</b><br>Tel: 60-3-7651-7906<br><b>Malaysia - Penang</b><br>Tel: 60-4-227-8870<br><b>Philippines - Manila</b><br>Tel: 63-2-634-9065<br><b>Singapore</b><br>Tel: 65-6334-8870<br><b>Taiwan - Hsin Chu</b><br>Tel: 886-3-577-8366<br><b>Taiwan - Kaohsiung</b><br>Tel: 886-7-213-7830<br><b>Taiwan - Taipei</b><br>Tel: 886-2-2508-8600<br><b>Thailand - Bangkok</b><br>Tel: 66-2-694-1351<br><b>Vietnam - Ho Chi Minh</b><br>Tel: 84-28-5448-2100 | <b>Austria - Wels</b><br>Tel: 43-7242-2244-39<br>Fax: 43-7242-2244-393<br><b>Denmark - Copenhagen</b><br>Tel: 45-4485-5910<br>Fax: 45-4485-2829<br><b>Finland - Espoo</b><br>Tel: 358-9-4520-820<br><b>France - Paris</b><br>Tel: 33-1-69-53-63-20<br>Fax: 33-1-69-30-90-79<br><b>Germany - Garching</b><br>Tel: 49-8931-9700<br><b>Germany - Haan</b><br>Tel: 49-2129-3766400<br><b>Germany - Heilbronn</b><br>Tel: 49-7131-72400<br><b>Germany - Karlsruhe</b><br>Tel: 49-721-625370<br><b>Germany - Munich</b><br>Tel: 49-89-627-144-0<br>Fax: 49-89-627-144-44<br><b>Germany - Rosenheim</b><br>Tel: 49-8031-354-560<br><b>Israel - Ra'anana</b><br>Tel: 972-9-744-7705<br><b>Italy - Milan</b><br>Tel: 39-0331-742611<br>Fax: 39-0331-466781<br><b>Italy - Padova</b><br>Tel: 39-049-7625286<br><b>Netherlands - Drunen</b><br>Tel: 31-416-690399<br>Fax: 31-416-690340<br><b>Norway - Trondheim</b><br>Tel: 47-72884388<br><b>Poland - Warsaw</b><br>Tel: 48-22-3325737<br><b>Romania - Bucharest</b><br>Tel: 40-21-407-87-50<br><b>Spain - Madrid</b><br>Tel: 34-91-708-08-90<br>Fax: 34-91-708-08-91<br><b>Sweden - Gothenberg</b><br>Tel: 46-31-704-60-40<br><b>Sweden - Stockholm</b><br>Tel: 46-8-5090-4654<br><b>UK - Wokingham</b><br>Tel: 44-118-921-5800<br>Fax: 44-118-921-5820 |