The RAA306012 is a smart gate driver IC for 3-phase brushless DC (BLDC) motor applications.

## Index

|                                                                                        |    |

|----------------------------------------------------------------------------------------|----|

| <b>Chapter 1 Overview</b>                                                              | 3  |

| 1.1 Features                                                                           | 5  |

| 1.2 Applications                                                                       | 5  |

| 1.3 Pin Configurations                                                                 | 6  |

| 1.4 Pin Descriptions                                                                   | 7  |

| 1.5 Typical Application Circuits                                                       | 9  |

| 1.5.1 Hall Sensor Motor Drive by Using 3 Comparators                                   | 9  |

| 1.5.2 Sensor-less Motor Drive by BEMF Sensing Comparator                               | 10 |

| 1.5.3 3 Shunt Sensor-less FOC Motor Drive                                              | 11 |

| 1.5.4 3 Shunt Sensor-less FOC Motor Drive with 5V MCU Supply                           | 12 |

| <b>Chapter 2 Pin Settings and Register Settings</b>                                    | 13 |

| 2.1 Pin Settings                                                                       | 13 |

| 2.1.1 EN Pin                                                                           | 13 |

| 2.1.2 SPI Communication Pins (Slave Side): SDO, SDI, SCLK, nSCS                        | 13 |

| 2.1.3 INz (z = 1, 2, 3, 4, 5, 6) Pins                                                  | 14 |

| 2.1.4 nFAULT Pin                                                                       | 14 |

| 2.1.5 DAzO (z = 1, 2, 3) Pins                                                          | 15 |

| 2.1.6 CMPzO (z = 1, 2, 3) Pins                                                         | 15 |

| 2.1.7 nSMPL Pin                                                                        | 16 |

| 2.2 Control Register                                                                   | 17 |

| 2.2.1 Register Description                                                             | 18 |

| 2.3 Register Settings for Motor Control                                                | 28 |

| 2.3.1 Hall Sensor Motor Drive by Using 3 Comparators                                   | 28 |

| 2.3.2 Sensor-less Motor Drive by BEMF Sensing Comparator                               | 32 |

| 2.3.3 3 Shunt Sensor-less FOC Motor Drive                                              | 35 |

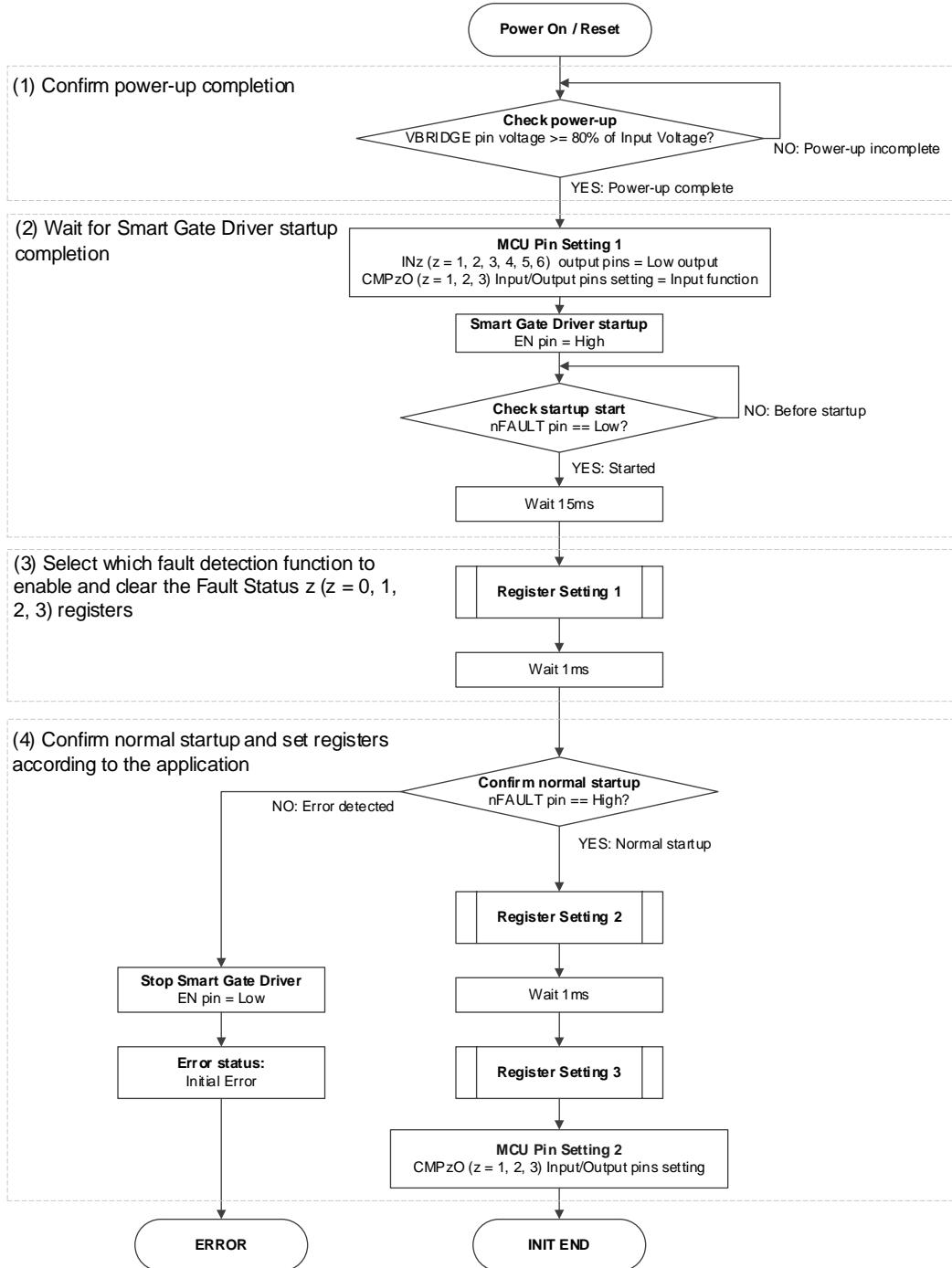

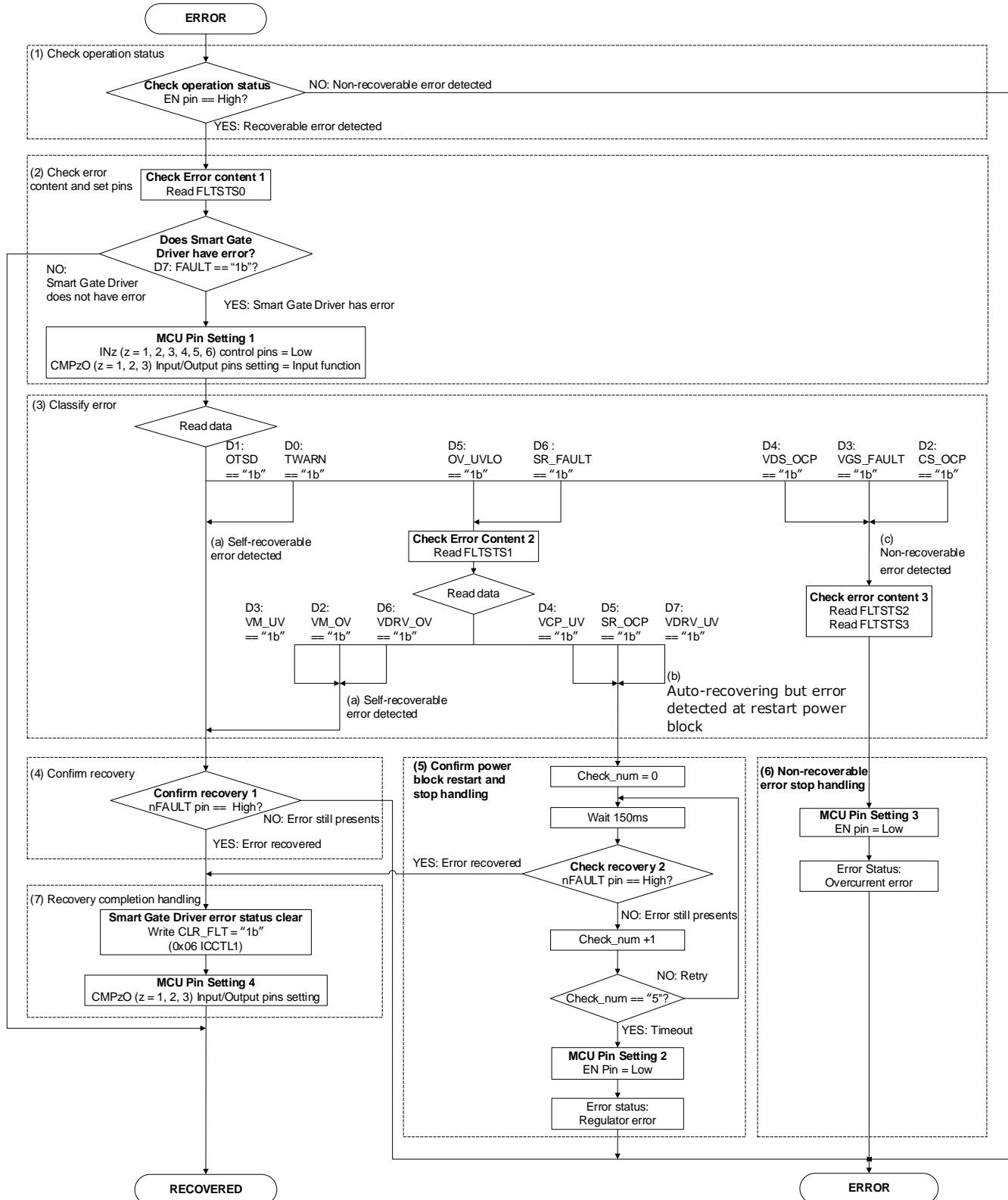

| <b>Chapter 3 Control Sequence</b>                                                      | 37 |

| 3.1 Start-up Sequence Example                                                          | 37 |

| 3.2 Error Recovery Sequence Example                                                    | 40 |

| <b>Chapter 4 Circuit Design, Component Selection, and Board Layout Recommendations</b> | 43 |

| 4.1 Circuit Design, Component Selection, and Precautions                               | 43 |

| 4.1.1 VM, VBRIDGE Pin Capacitors (C1a, C1b, C1c, C1d)                                  | 45 |

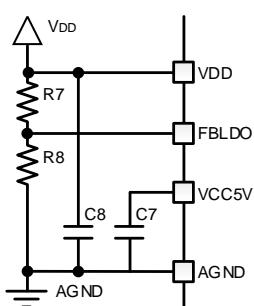

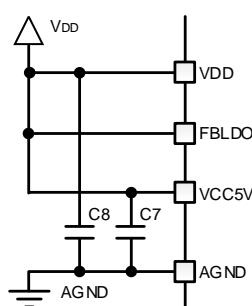

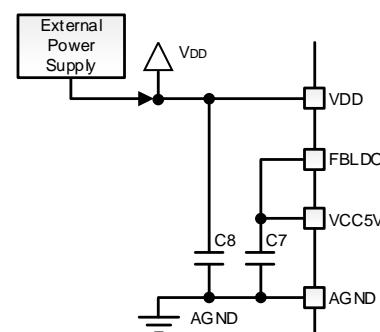

| 4.1.2 Linear Regulator Components (C7, C8, R7, R8)                                     | 45 |

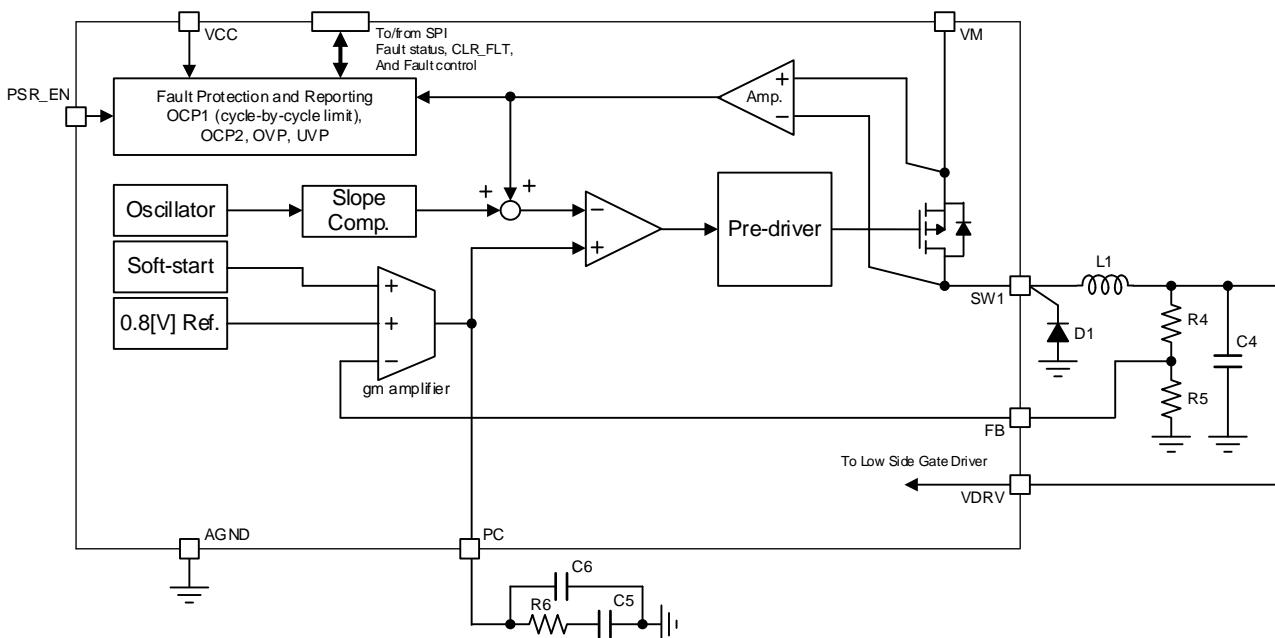

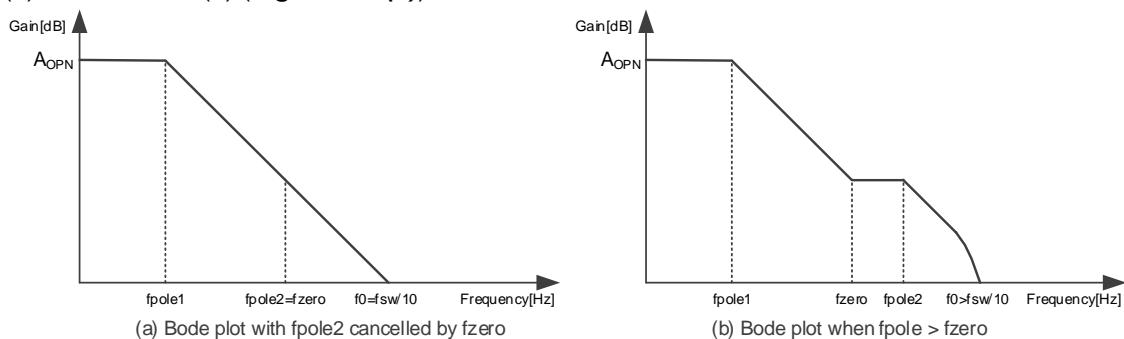

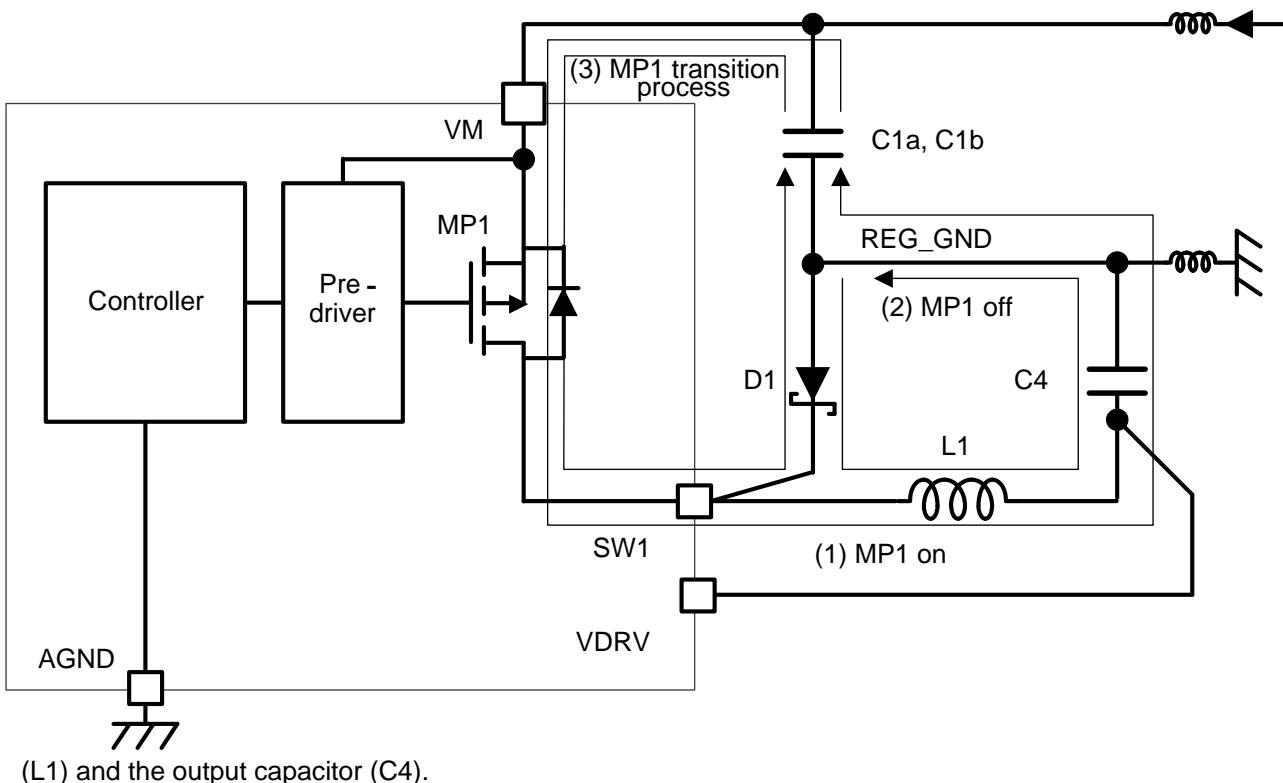

| 4.1.3 Components for Buck Switching Regulator (R4, R5, L1, C4, C5, R6)                 | 47 |

| 4.1.4 Charge Pump Output Capacitor (C2), Pumping Capacitor (C3)                        | 52 |

| 4.1.5 External MOSFETs (M1 to M6) and Register Settings                                | 52 |

| 4.1.6 Current Sensing Shunt Resistors (R1, R2, R3) and Differential Amplifier Gain     | 54 |

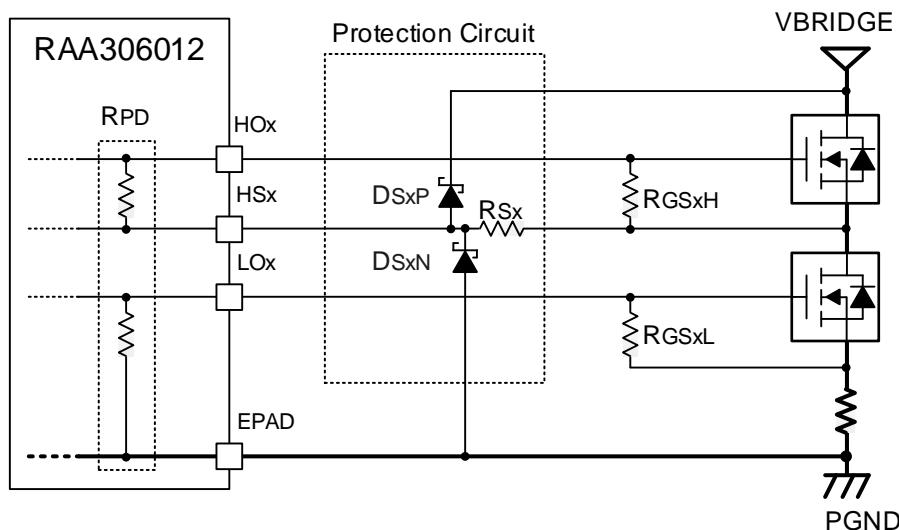

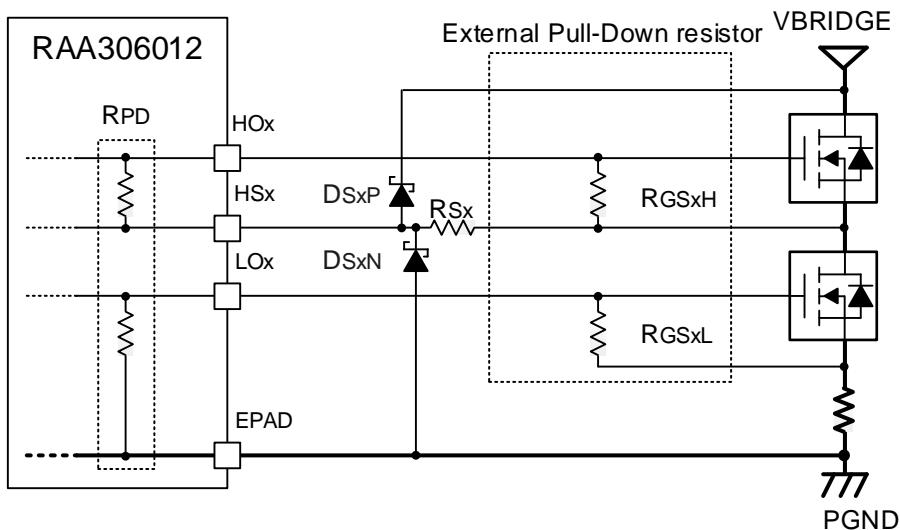

| 4.1.7 External Protection Circuit Example                                              | 55 |

| 4.2 Board Layout Recommendations                                                       | 57 |

| 4.2.1 GND Nets                                                                         | 57 |

| 4.2.2 Capacitors and Wirings for Power Supply Pins                                     | 59 |

|                                            |           |

|--------------------------------------------|-----------|

| 4.2.3 Buck Switching Regulator.....        | 60        |

| 4.2.4 N-ch MOSFET Bridge.....              | 61        |

| 4.2.5 Charge Pump.....                     | 61        |

| 4.2.6 Shunt Current Sensing .....          | 61        |

| <b>Chapter 5 Precautions for Use .....</b> | <b>62</b> |

| 5.1 High Temperature Operation.....        | 62        |

| <b>Revision History .....</b>              | <b>63</b> |

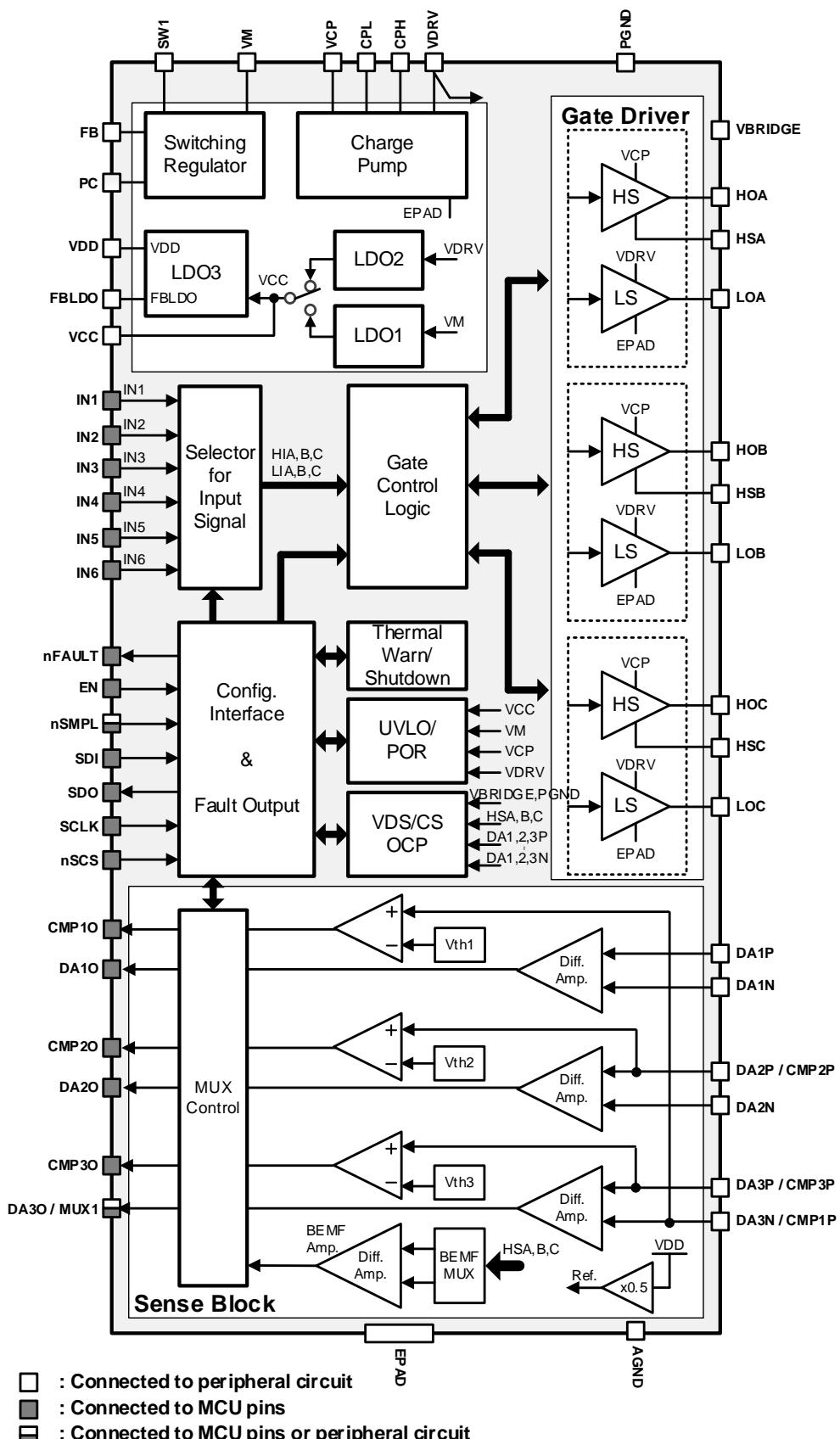

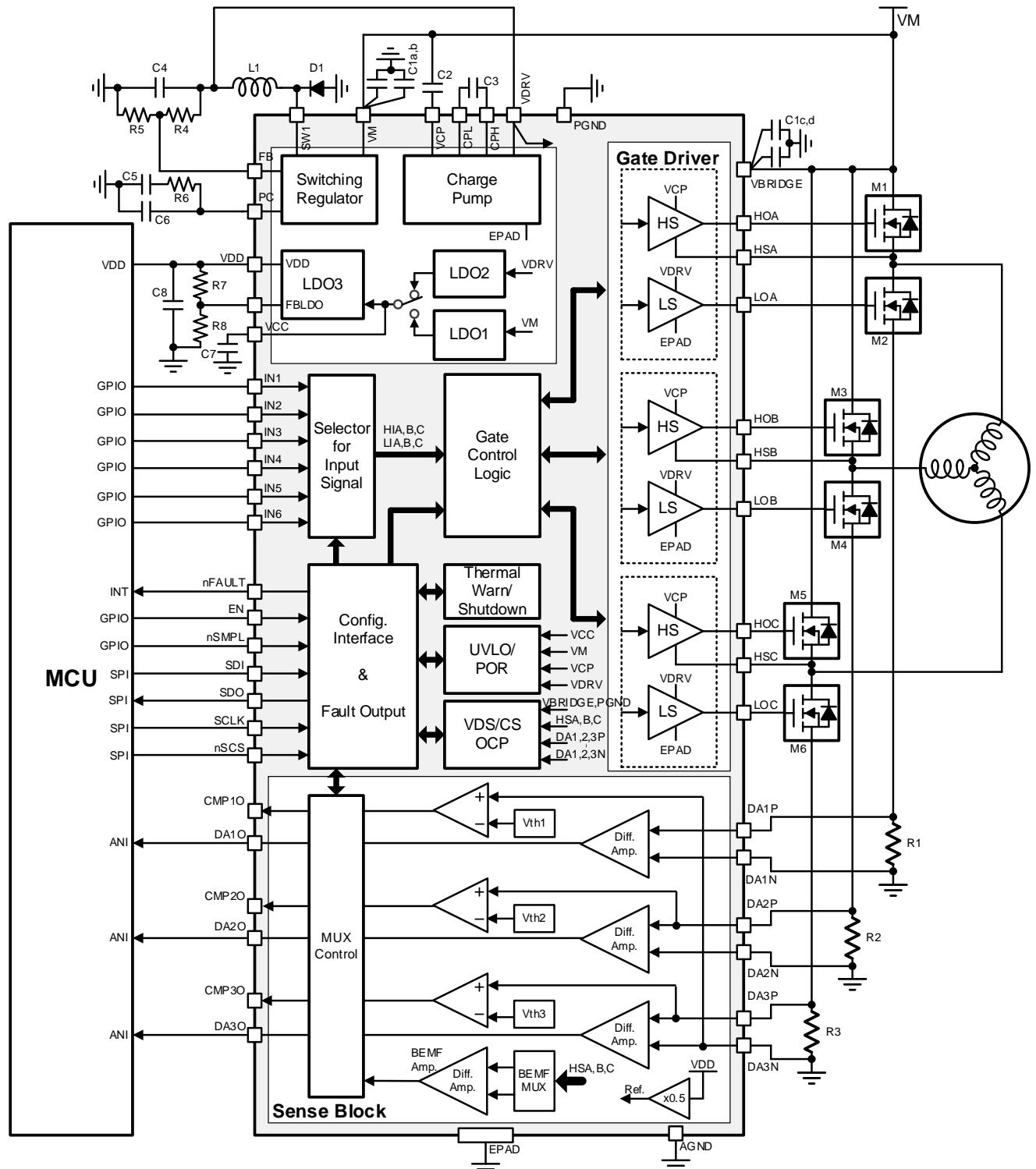

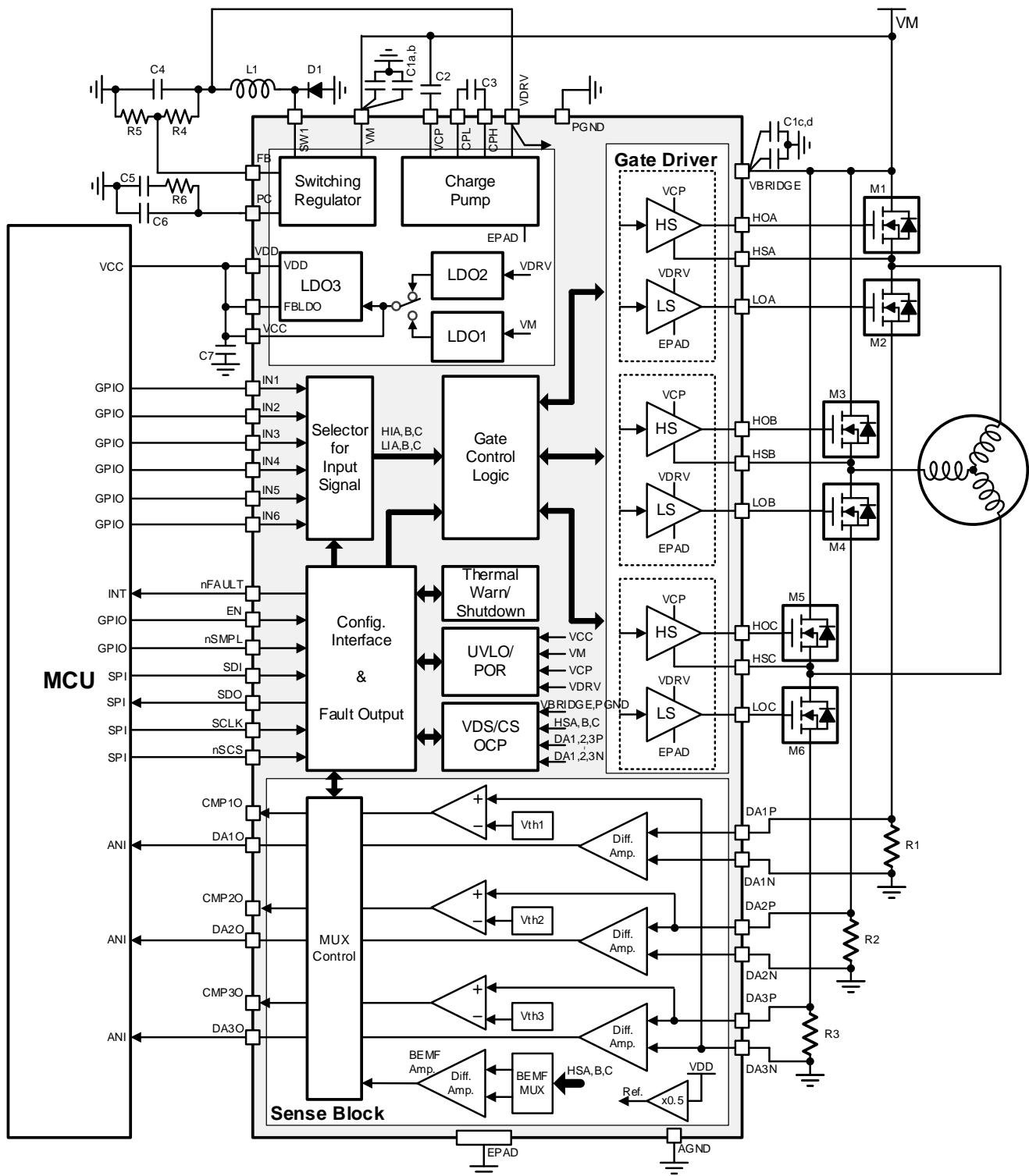

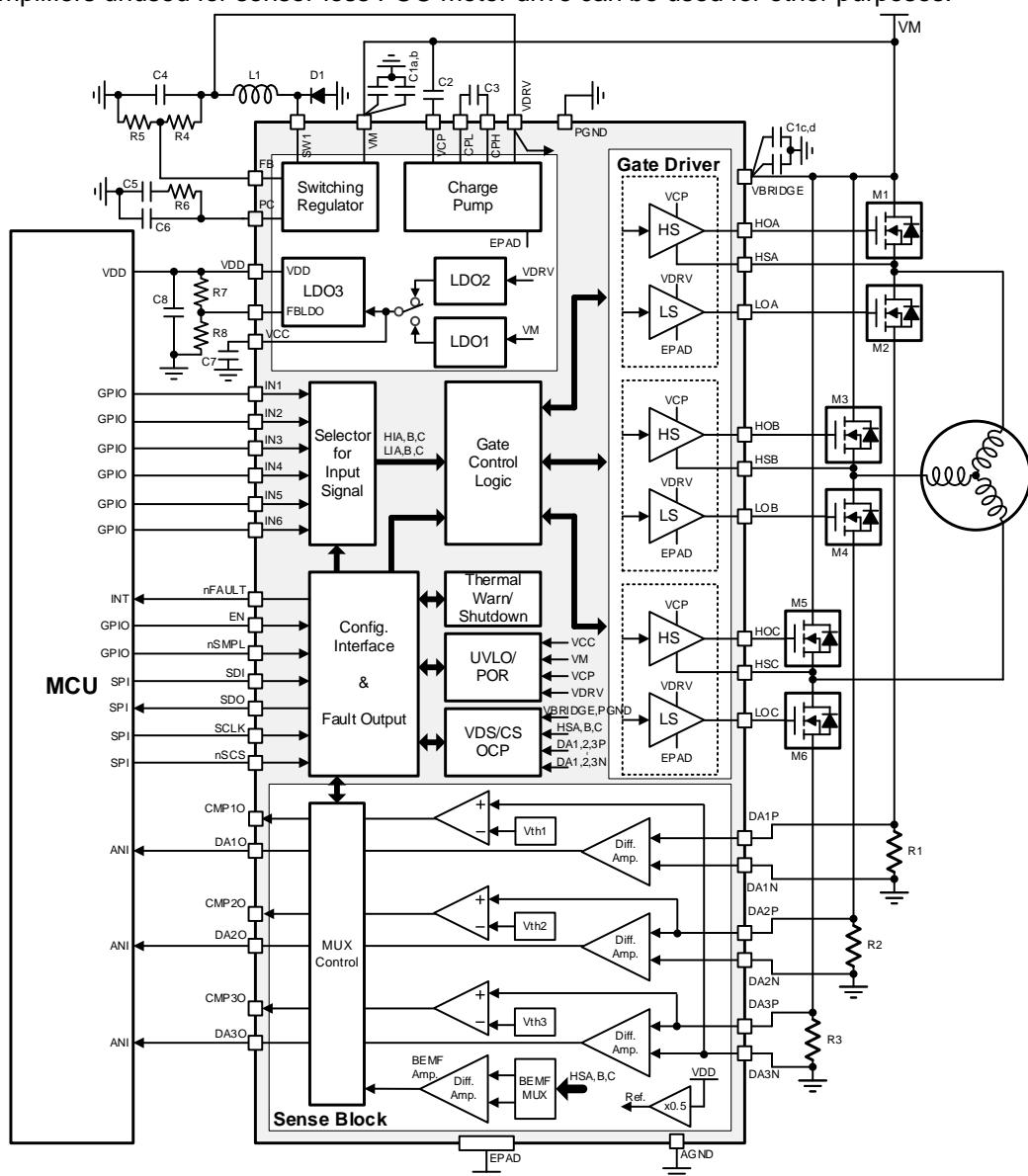

## Chapter 1 Overview

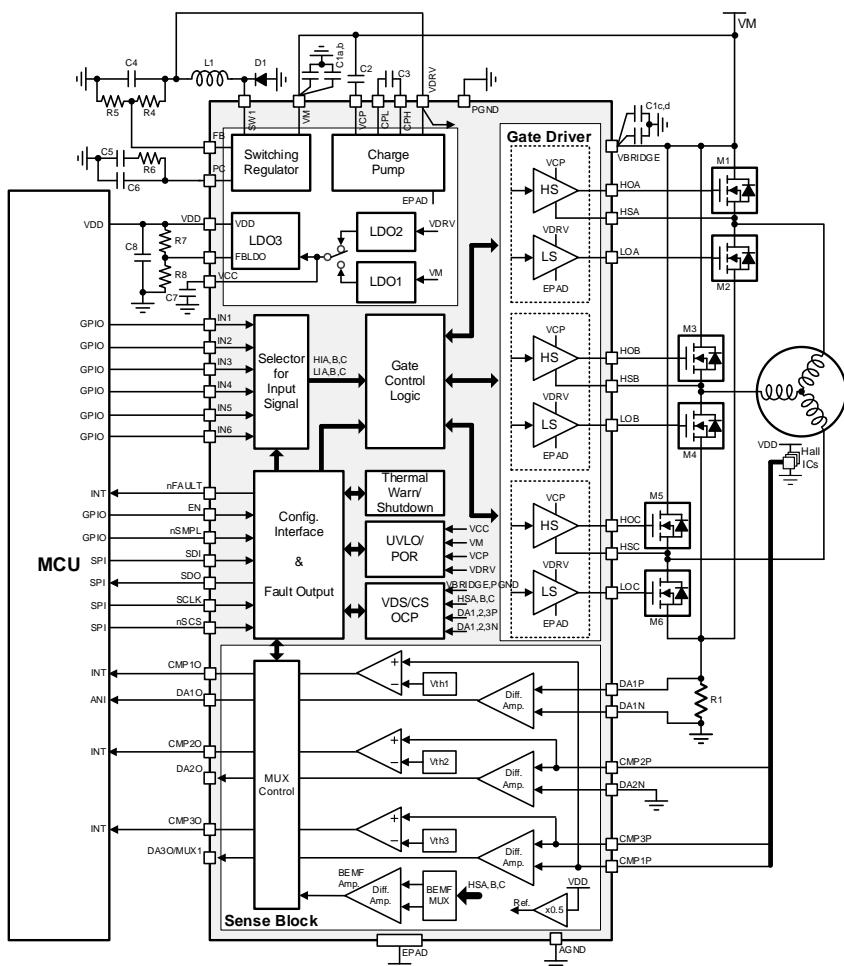

This device includes three half-bridge gate drivers, a buck switching regulator and a charge pump for the gate drive voltage, two LDOs for the internal analog and logic circuitry and MCU, three accurate differential amplifiers, a BEMF sense amplifier, three general purpose comparators, and extensive protection functions.

The three half-bridge gate drivers are capable of driving up to three N-channel MOSFET bridges and support bridge voltages from 6V to 65V. Each gate driver supports up to 0.64A source and 1.28A sink peak drive current with adjustable drive strength control. The driver control input supports both 3-phase HI/LI mode and 3-phase PWM mode. Adaptive and adjustable dead-times are implemented to ensure robustness and flexibility. The active gate holding mechanism prevents miller effect induced cross-conduction and further enhances robustness.

The device also features a low-power sleep mode that consumes only 28 $\mu$ A to maximize battery life in portable applications. Three accurate differential amplifiers with adjustable gain support ground-side shunt current sensing for each bridge. The device can also support both BLDC sensor/sensor-less motor drive by the three general purpose comparators or a BEMF sense amplifier.

The device can be configured to use SPI interface. All the parameters can be set through the SPI interface and allows better monitoring.

The protection functions include supply voltage OV/UV protection, buck regulator OV/UV/OC protection, charge pump UV protection, MOSFET VDS OC protection, current sense OC protection, MOSFET VGS fault, thermal warning, and thermal shutdown. Fault conditions are reported on the nFAULT signal and each status bit in the Fault Status registers.

To control the smart gate driver effectively, it is important to configure not only the control signals from the MCU, but also the peripheral circuits and register settings according to the application.

For detail on this device specification, refer to the "[RAA306012 Datasheet \(R18DS0037EJ\)](#)".

Figure 1-1 RAA306012 Internal Block Diagram

## 1.1 Features

### Recommended operating power supply voltage conditions

- VBRIDGE: 6 to 65V (Abs. Max 78V)

- VM: 6 to 60V (Abs. Max 65V)

### Ambient operating temperature range

- -40 to +125°C

### 3-phase gate drivers for BLDC Motors

- Switching frequency range up to 200kHz

- Peak 0.64A/1.28A source/sink current with 16 adjustable drive strength through SPI interface

- Adaptive and adjustable dead time

### Flexible configuration for gate driver

- 3-phase HI/LI mode and 3-phase PWM mode

- Input control signal configuration

- Support half-bridge, full-bridge configuration

### Fully integrated power supply architecture

- Two VCC LDOs allow for Sleep mode low IQ

- 500mA buck switching regulator generates drive voltage (5V to 15V adjustable)

- 100mA adjustable output LDO for MCU supplies

### Three accurate differential amplifiers (for current sensing)

- Four levels of sense gain setting (x5, x10, x20, x40)

- Supports DC offset calibration during power-up and on-the-fly

### BEMF sense amplifier (for sensor-less motor drive)

### 3 general purpose comparators (for Hall sensor motor drive)

### Extensive protection functions (fault detection functions)

- VCC undervoltage (VCC\_UV)

- VM undervoltage (VM\_UV)

- VM overvoltage (VM\_OV)

- VCP undervoltage (VCP\_UV) for charge pump

- MOSFET  $V_{DS}$  overcurrent (VDS\_OCP)

- Current sense over current (CS\_OCP)

- MOSFET  $V_{GS}$  fault (VGS\_FAULT)

- Thermal warning (TWARN)

- Thermal shutdown (OTSD)

- Buck regulator overcurrent limiting (SR\_OC1)

- Buck regulator overcurrent protection (SR\_OCP)

- Buck regulator undervoltage (VDRV\_UV)

- Buck regulator overvoltage (VDRV\_OV)

- Fault indicator (nFAULT pin)

### 7mmx7mm 48 Ld QFN package (0.5mm pitch)

## 1.2 Applications

Power tools and Garden tools, Printers, Vacuum cleaners, Fans, Pumps, and Robotics

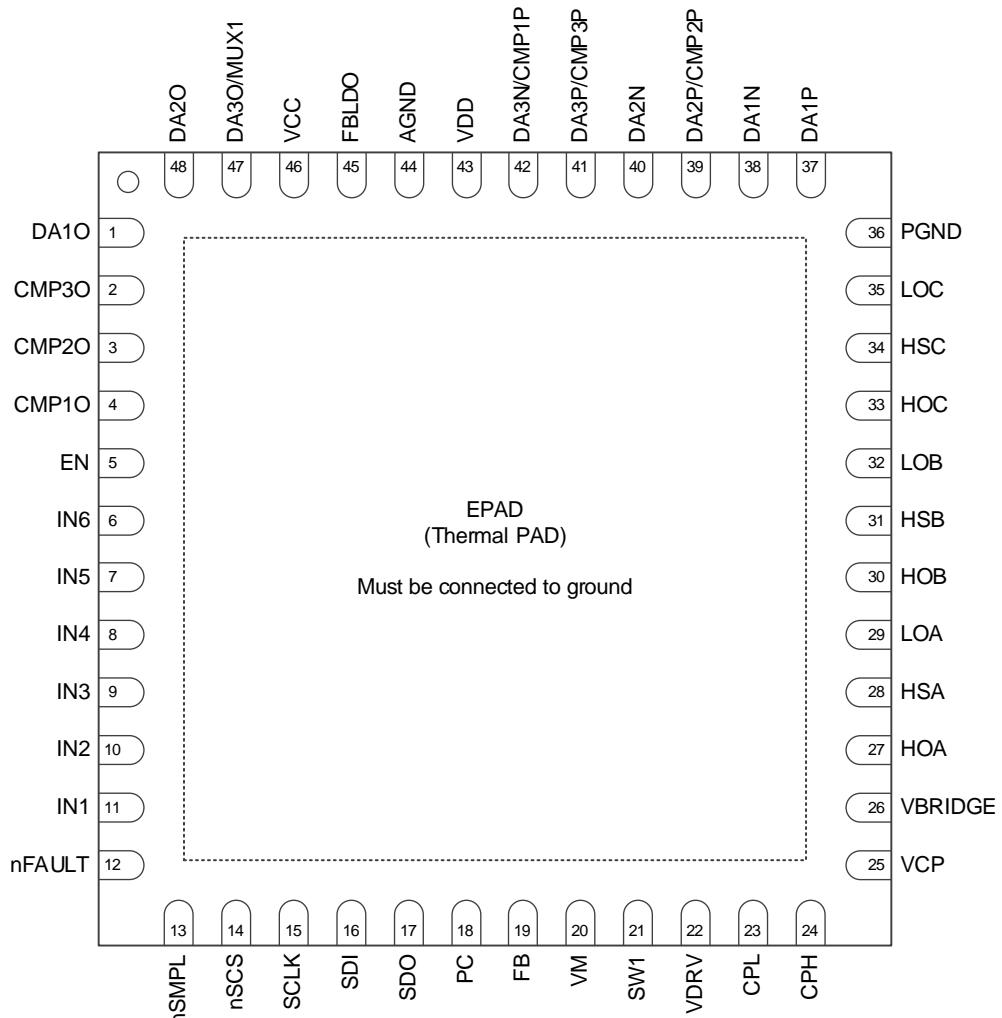

## 1.3 Pin Configurations

Figure 1-2 Pin Configuration Diagram (Top View)

## 1.4 Pin Descriptions

Table 1-1 Pin Descriptions (1/2)

| Pin    |        | I/O   |                |                      |                                       | Function                                                                                                                                                | Note |

|--------|--------|-------|----------------|----------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Number | Name   | level | type           | Initial (EN=Low)     | Enable Control                        |                                                                                                                                                         |      |

| 1      | DA1O   | VDD   | OUT            | 330kΩ, pull-down     | DA1_EN bit                            | Output of differential amplifier 1<br>Pull-down resistor is disabled when differential amplifier 1 is enabled.                                          |      |

| 2      | CMP3O  | VDD   | IN/OUT         | OUT/380kΩ, pull-down | CMP3_VTH / BEMF_PH bit                | Control input for the detect phase selection of BEMF sense amplifier.<br>Output of comparator 3.<br>The pin function is selected by BEMF_PH bits.       | 1    |

| 3      | CMP2O  | VDD   | IN/OUT         | OUT/380kΩ, pull-down | CMP2_VTH / BEMF_PH bit                | Control input for the detect phase selection of BEMF sense amplifier.<br>Output of comparator 2.<br>The pin function is selected by BEMF_PH bits.       | 1    |

| 4      | CMP1O  | VDD   | IN/OUT         | OUT/380kΩ, pull-down | CMP1_VTH / BEMF_PH bit                | Control input for the detect phase selection of BEMF sense amplifier.<br>Output of comparator 1.<br>The pin function is selected by BEMF_PH bits.       | 1    |

| 5      | EN     | VDD   | IN             | 100kΩ, pull-down     | —                                     | Enable control pin for Operation Mode.<br>When this pin is logic low, the device goes to a low-power sleep mode.                                        | 1, 2 |

| 6      | IN6    | VDD   | IN             | 380kΩ, pull-down     | EN pin                                | Gate driver control input 6.<br>The control input for each phase gate driver is selectable by the register setting.                                     | 2    |

| 7      | IN5    | VDD   | IN             | 380kΩ, pull-down     | EN pin                                | Gate driver control input 5.<br>The control input for each phase gate driver is selectable by the register setting.                                     | 2    |

| 8      | IN4    | VDD   | IN             | 380kΩ, pull-down     | EN pin                                | Gate driver control input 4.<br>The control input for each phase gate driver is selectable by the register setting.                                     | 2    |

| 9      | IN3    | VDD   | IN             | 380kΩ, pull-down     | EN pin                                | Gate driver control input 3.<br>The control input for each phase gate driver is selectable by the register setting.                                     | 2    |

| 10     | IN2    | VDD   | IN             | 380kΩ, pull-down     | EN pin                                | Gate driver control input 2.<br>The control input for each phase gate driver is selectable by the register setting.                                     | 2    |

| 11     | IN1    | VDD   | IN             | 380kΩ, pull-down     | EN pin                                | Gate driver control input 1.<br>The control input for each phase gate driver is selectable by the register setting.                                     | 2    |

| 12     | nFAULT | VDD   | Open drain OUT | Hi-Z                 | EN pin                                | Fault indicator output<br>The pull-up resistor option of MCU or external pull-up resistor is required.                                                  | 3    |

| 13     | nSMPL  | VDD   | IN             | 380kΩ, pull-down     | DAz_SH<br>(z = 1, 2, 3) / BEMF_SH bit | Sampling control input of BEMF sense amplifier or differential amplifiers.                                                                              |      |

| 14     | nSCS   | VDD   | IN             | 380kΩ, pull-up       | EN pin                                | SPI chip select input                                                                                                                                   | 4    |

| 15     | SCLK   | VDD   | IN             | 380kΩ, pull-down     | EN pin                                | SPI clock input                                                                                                                                         | 4    |

| 16     | SDI    | VDD   | IN             | 380kΩ, pull-down     | EN pin                                | SPI data input                                                                                                                                          | 4    |

| 17     | SDO    | VDD   | Open drain OUT | Hi-Z                 | EN pin                                | SPI data output<br>The pull-up resistor option of MCU or external pull-up resistor is required.                                                         | 3, 4 |

| 18     | PC     | VCC   | OUT            | 1kΩ, pull-down       | EN pin                                | gm amplifier output for phase compensation of buck switching regulator.<br>When the switching regulator is enabled, the pull-down resistor is disabled. |      |

| 19     | FB     | VCC   | IN             | -                    | EN pin                                | Voltage feedback input of buck switching regulator (Ref = 0.8V)                                                                                         |      |

| 20     | VM     | VM    | POWER          | -                    | —                                     | Power supply input.<br>Connect bypass capacitors between VM and AGND.                                                                                   |      |

| 21     | SW1    | VM    | OUT            | Hi-Z                 | EN pin                                | Switch node of buck switching regulator                                                                                                                 |      |

| 22     | VDRV   | VDRV  | POWER          | -                    | EN pin                                | Output of buck switching regulator, Low-side gate driver supply<br>Connect to bypass capacitors between VDRV and AGND.                                  |      |

| 23     | CPL    | VDRV  | OUT            | 100kΩ, pull-down     | EN pin                                | Charge pump low-side switch node.<br>Connect a flying capacitor between CPH and CPL pins.                                                               |      |

| 24     | CPH    | VCP   | OUT            | Hi-Z                 | EN pin                                | Charge pump high-side switch node.<br>Connect a flying capacitor between CPH and CPL pins.                                                              |      |

Note1: To avoid the collision by output signals of the MCU and this device, set the MCU ports to the digital input port before setting the EN pin to Low.

Note2: To avoid unexpected gate drive output, input the INz (z = 1, 2, 3, 4, 5, 6) pin to Low before setting EN pin to High or recovering from an abnormal condition. For details, refer to the smart gate driver control sequence in **Chapter 3**.

Note3: The pull-up resistor option of MCU can be used. It is necessary to verify that the actual SPI timings meet the specifications to determine the communication speed.

Note4: SPI communication is enabled after setting the EN pin to High.

Table 1-2 Pin Descriptions (1/2)

| Pin    |                    | I/O     |       |                          | Function                           | Note                                                                                                                                                            |   |

|--------|--------------------|---------|-------|--------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Number | Name               | level   | type  | Initial (EN=Low)         | Enable Control                     |                                                                                                                                                                 |   |

| 25     | VCP                | VCP     | POWER | -                        | EN pin                             | Charge pump output.<br>Connect a bypass capacitor between VCP and VBRIDGE pins.                                                                                 |   |

| 26     | VBRIDGE            | VBRIDGE | IN    | -                        | EN pin                             | Charge pump output reference and high-side MOSFET drain sense Input.<br>Connect a bypass capacitor between VBRIDGE pin and power ground.                        |   |

| 27     | HOA                | VCP     | OUT   | 200kΩ, pull-down to HSA  | EN pin                             | Phase A high-side gate driver output.<br>Connect to the high-side MOSFET gate.                                                                                  | 5 |

| 28     | HSA                | VBRIDGE | IN    | 300kΩ, pull-down         | EN pin                             | Phase A high-side source sense input.<br>Connect to the high-side MOSFET source.                                                                                |   |

| 29     | LOA                | VDRV    | OUT   | 200kΩ, pull-down to EPAD | EN pin                             | Phase A low-side gate driver output.<br>Connect to the low-side MOSFET gate.                                                                                    | 5 |

| 30     | HOB                | VCP     | OUT   | 200kΩ, pull-down to HSA  | EN pin                             | Phase B high-side gate driver output.<br>Connect to the high-side MOSFET gate.                                                                                  | 5 |

| 31     | HSB                | VBRIDGE | IN    | 300kΩ, pull-down         | EN pin                             | Phase B high-side source sense input.<br>Connect to the high-side MOSFET source.                                                                                |   |

| 32     | LOB                | VDRV    | OUT   | 200kΩ, pull-down to EPAD | EN pin                             | Phase B low-side gate driver output.<br>Connect to the low-side MOSFET gate.                                                                                    | 5 |

| 33     | HOC                | VCP     | OUT   | 200kΩ, pull-down to HSA  | EN pin                             | Phase C high-side gate driver output.<br>Connect to the high-side MOSFET gate.                                                                                  | 5 |

| 34     | HSC                | VBRIDGE | IN    | 300kΩ, pull-down         | EN pin                             | Phase C high-side source sense input.<br>Connect to the high-side MOSFET source.                                                                                |   |

| 35     | LOC                | VDRV    | OUT   | 200kΩ, pull-down to EPAD | EN pin                             | Phase C low-side gate driver output.<br>Connect to the low-side MOSFET gate.                                                                                    | 5 |

| 36     | PGND               | GND     | GND   | -                        | —                                  | Ground sense input of external power stage.                                                                                                                     |   |

| 37     | DA1P               | VDD     | IN    | -                        | DA1_EN / DIS_CS1OCP bit            | Positive input of differential amplifier 1.<br>When the all functions input from this pin are not used, connect to AGND.                                        |   |

| 38     | DA1N               | VDD     | IN    | -                        | DA1_EN / DIS_CS1OCP bit            | Negative input of differential amplifier 1.<br>When the all functions input from this pin are not used, connect to AGND.                                        |   |

| 39     | DA2P               | VDD     | IN    | -                        | DA2_EN / DIS_CS2OCP / CMP2_VTH bit | Positive input of differential amplifier 2 and positive input of comparator 2.<br>When the all functions input from this pin are not used, connect to AGND.     |   |

| 40     | DA2N               | VDD     | IN    | -                        | DA2_EN / DIS_CS2OCP bit            | Negative input of differential amplifier 2.<br>When the all functions input from this pin are not used, connect to AGND.                                        |   |

| 41     | DA3P               | VDD     | IN    | -                        | DA3_EN / DIS_CS3OCP / CMP3_VTH bit | Positive input of differential amplifier 3 and positive input of comparator 3.<br>When the all functions input from this pin are not used, connect to AGND.     |   |

| 42     | DA3N               | VDD     | IN    | -                        | DA3_EN / DIS_CS3OCP / CMP1_VTH bit | Negative input of differential amplifier 3 and positive input of comparator 1.<br>When the all functions input from this pin are not used, connect to AGND.     |   |

| 43     | VDD                | VDD     | POWER | -                        | —                                  | Internal series regulator output and power supply of output buffers.<br>Connect to a bypass capacitor between VDD and AGND.                                     | 6 |

| 44     | AGND               | GND     | GND   | -                        | —                                  | Device analog ground.                                                                                                                                           |   |

| 45     | FBLDO              | VCC     | IN    | -                        | —                                  | Voltage feedback input of internal series regulator (Ref.=1.2V).                                                                                                |   |

| 46     | VCC                | VCC     | POWER | -                        | —                                  | Internal series regulator output(5V).<br>Connect to a bypass capacitor between VCC and AGND.                                                                    | 6 |

| 47     | DA3O               | VDD     | OUT   | 330kΩ, pull-down         | MUX bit                            | Output of differential amplifier 3, BEMF sense amplifier, and multiplexer.<br>When MUX[2:0] is the setting other than 000b, the pull-down resistor is disabled. |   |

| 48     | DA2O               | VDD     | OUT   | 330kΩ, pull-down         | DA2_EN bit                         | Output of differential amplifier 2.<br>When the differential amplifier 2 is enabled, the pull-downresistor is disabled.                                         |   |

| -      | EPAD (Thermal PAD) | GND     | GND   | -                        | —                                  | Power ground for gate driver and charge pump.<br>Must be connected to power ground.                                                                             |   |

Note5: Although pull-down resistors are integrated between the HOx - HSx (x = A, B, C) pins and between the LOx (x = A, B, C) - EPAD, external pull-down resistors are required depending on the slew rate of the external MOSFETs power supply.

Note6: The capability of VDD and VCC load current depends on the EN pin and the operation mode. For recommended operating conditions, refer to 5.3 in the “**RAA306012 Datasheet (R18DS0037EJ)**”.

## 1.5 Typical Application Circuits

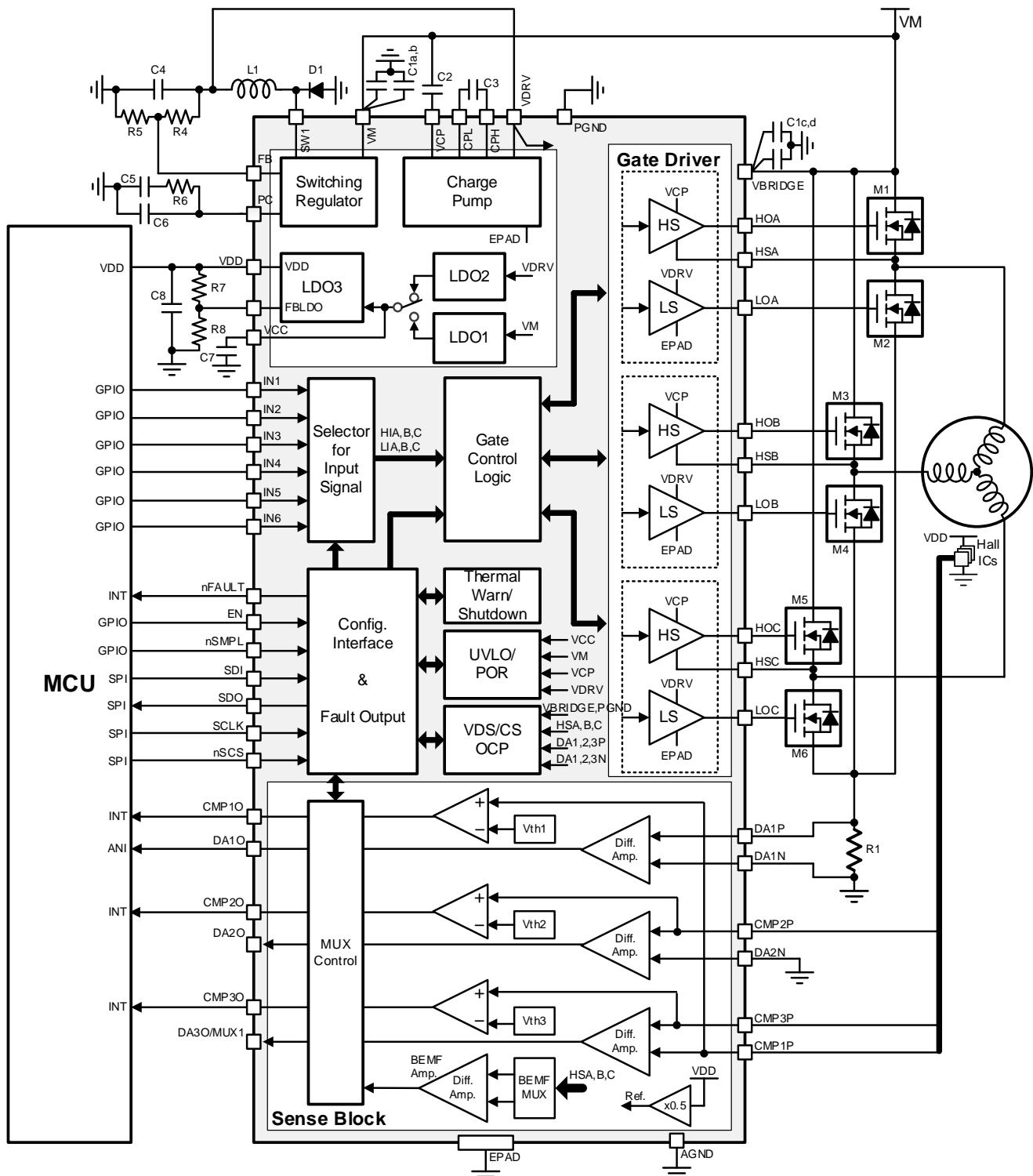

### 1.5.1 Hall Sensor Motor Drive by Using 3 Comparators

**Figure 1-3 Simplified Block Diagram and Application – Hall Sensor Motor Drive by Using 3 Comparators**

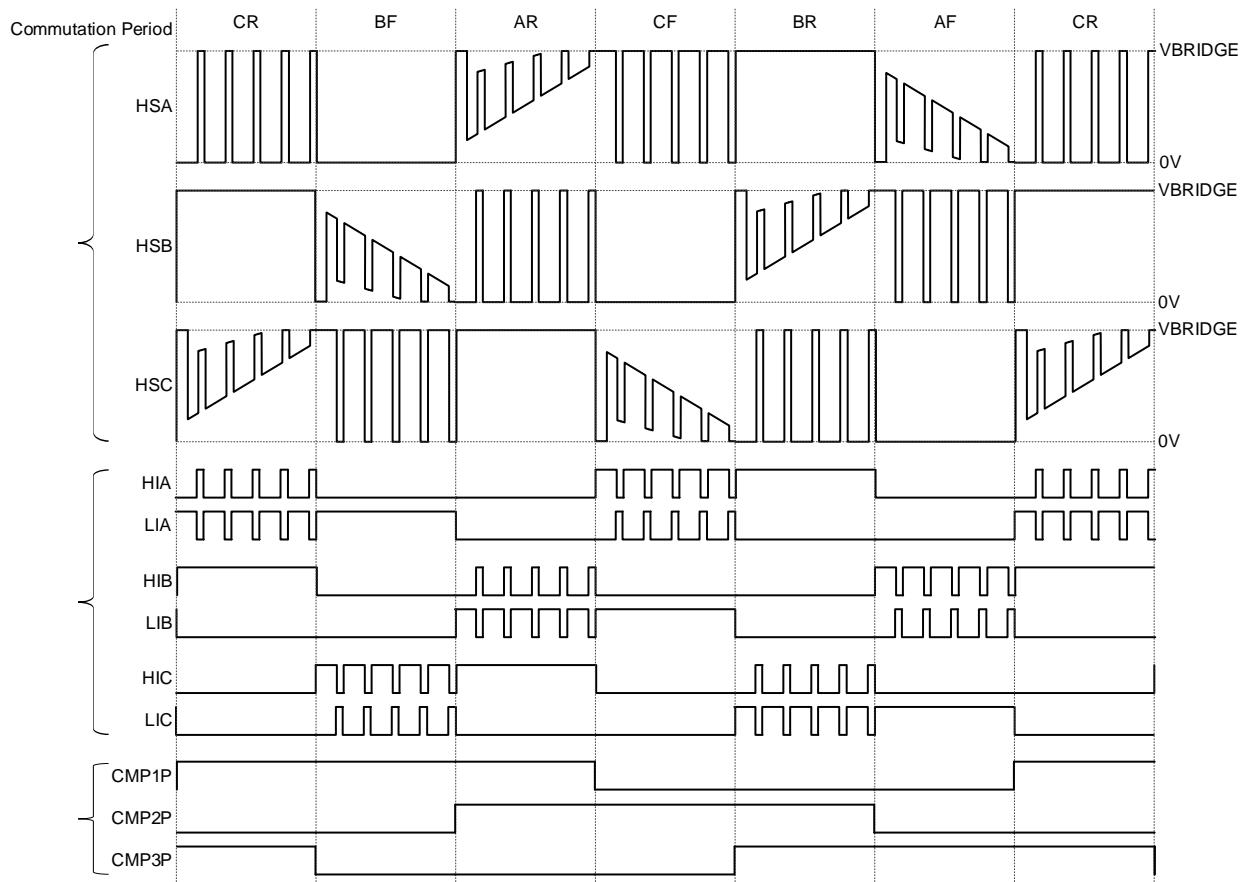

## 1.5.2 Sensor-less Motor Drive by BEMF Sensing Comparator

Figure 1-4 Simplified Block Diagram and Application – Sensor-less Motor Drive by BEMF Sensing Comparator

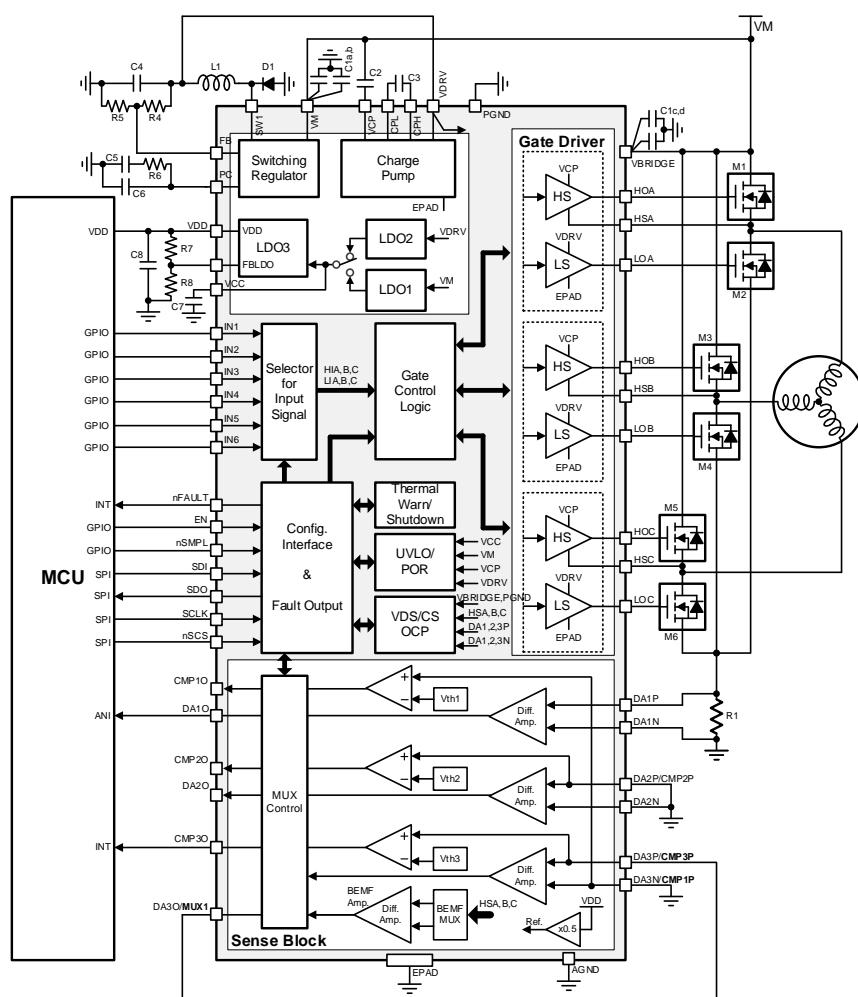

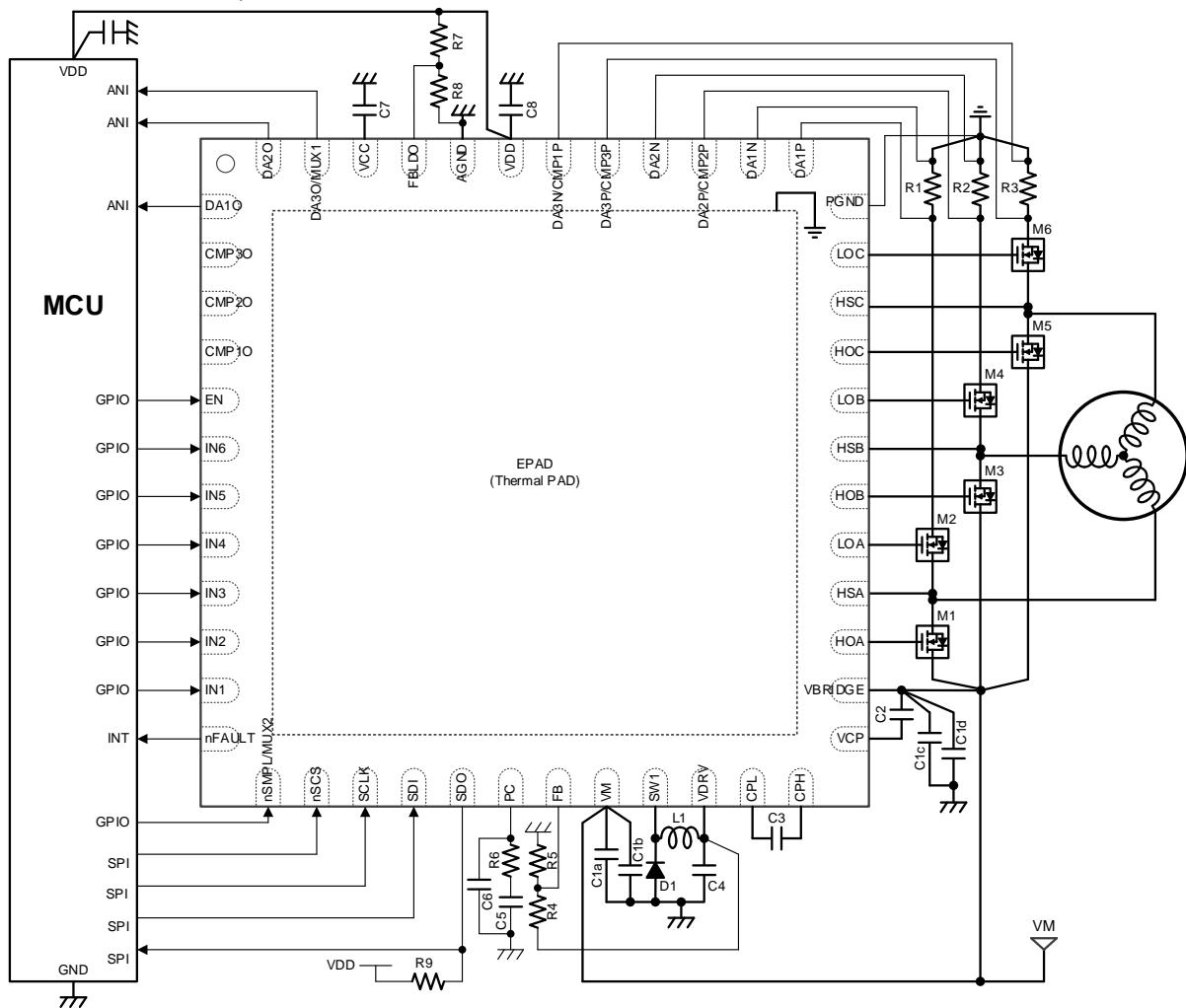

### 1.5.3 3 Shunt Sensor-less FOC Motor Drive

Figure 1-5 Simplified Block Diagram and Application – 3 Shunt Sensor-less FOC Motor Drive

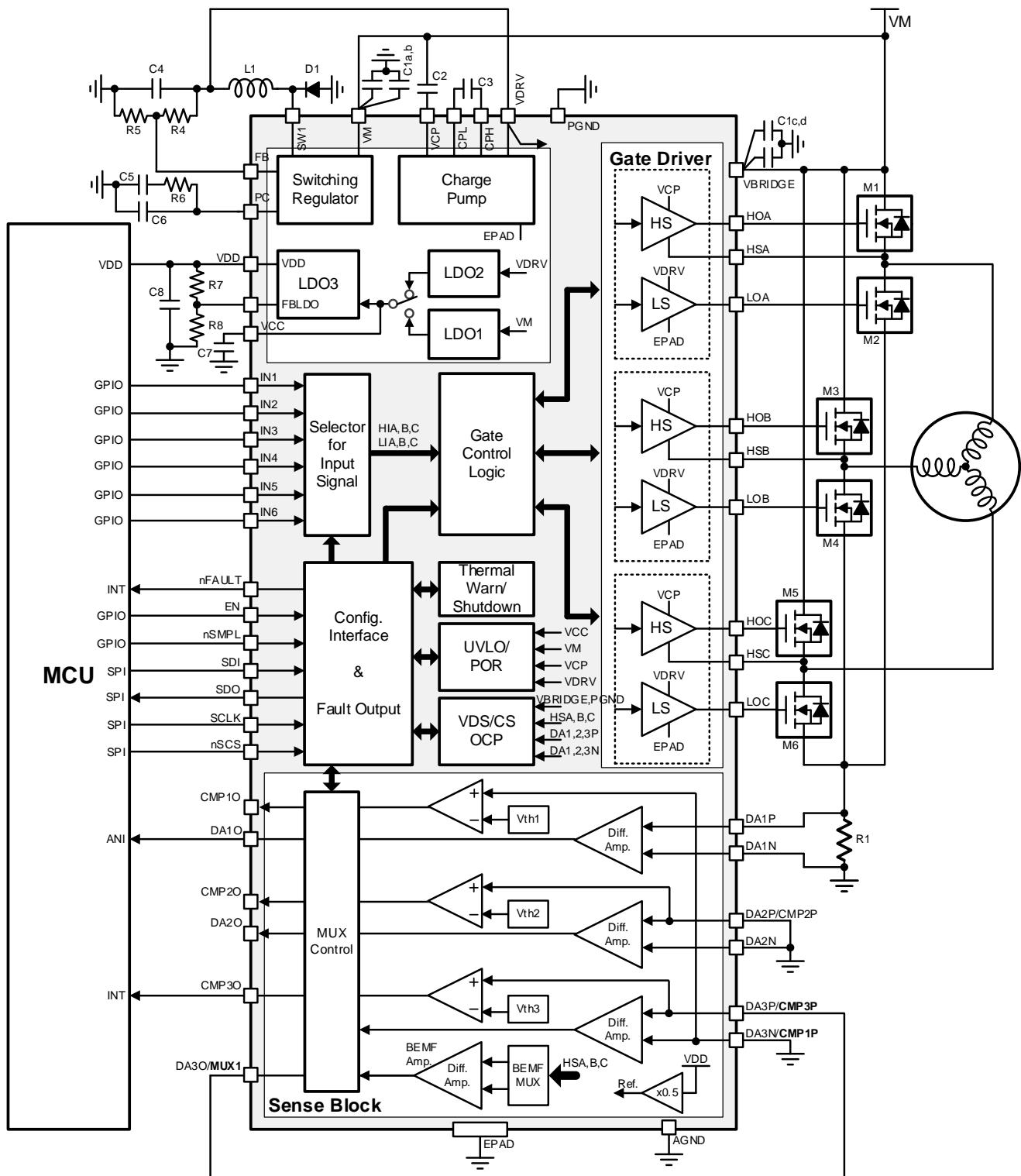

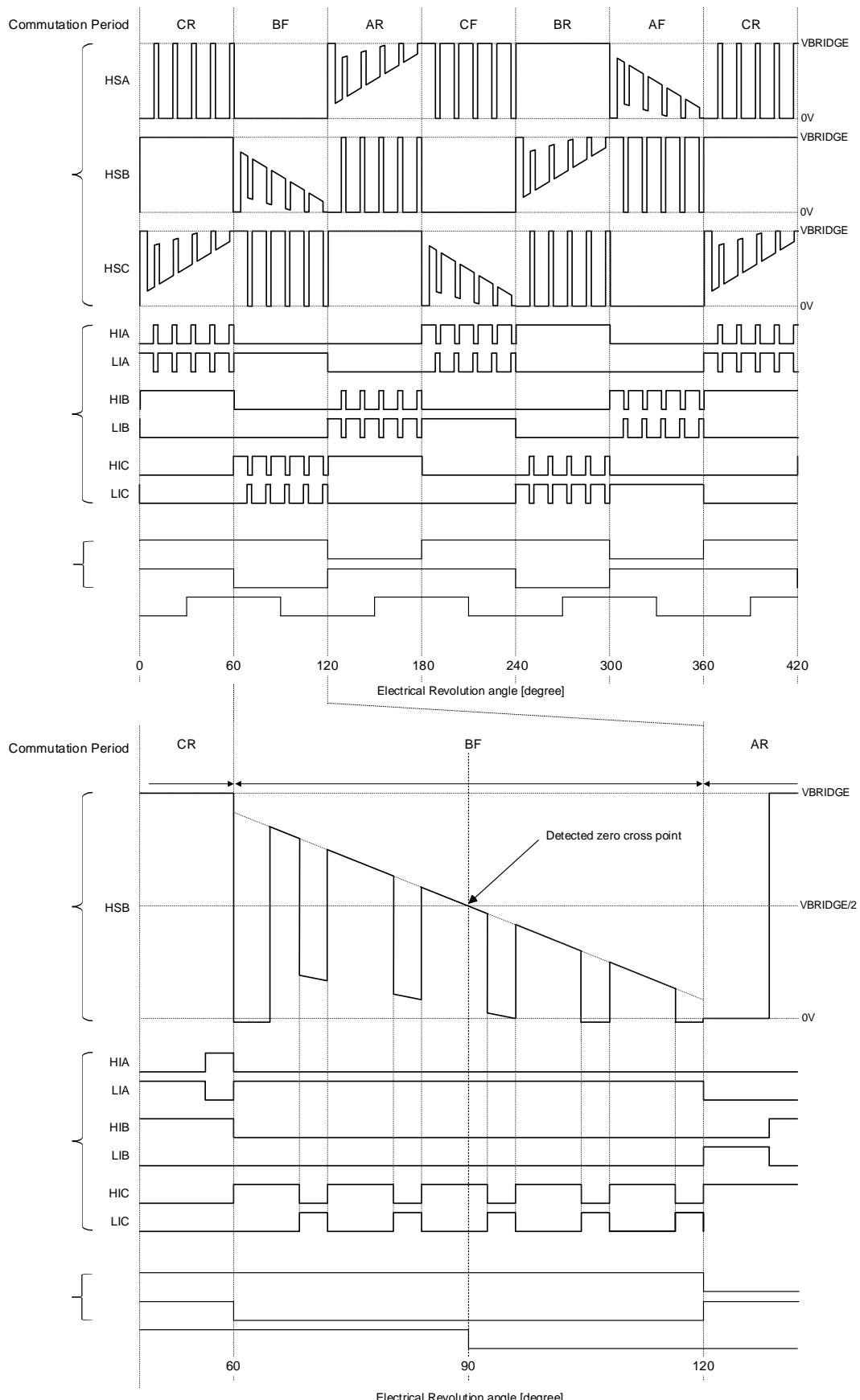

### 1.5.4 3 Shunt Sensor-less FOC Motor Drive with 5V MCU Supply

**Figure 1-6 Simplified Block Diagram and Application – 3 Shunt Sensor-less FOC Motor Drive with 5V MCU Supply**

## Chapter 2 Pin Settings and Register Settings

### 2.1 Pin Settings

#### 2.1.1 EN Pin

The EN pin is input pin of control the operation mode of the smart gate driver. Set the port (Now referred to as EN output port) of the MCU to the digital output port to control this pin. For details of the operation mode, refer to **6.1** of the “*RAA306012 Datasheet (R18DS0037EJ)*”.

- (1) After the MCU reset is released, the EN pin becomes Low by the smart gate driver pull-down resistor ( $100\text{k}\Omega$ ) even if the EN output port is an input function. Therefore, after the MCU reset is released, the operation mode of the smart gate driver is in Sleep Mode.

- (2) In the MCU port settings, it is recommended to set the EN output port to the digital output function to start from Low output.

- (3) When setting the EN output port to High, the smart gate driver enters the Operating Mode. It is important to set the other port settings before setting the EN output port to High because the control by signals other than the EN signal are enabled.

- (4) When stopping smart gate driver operation due to any abnormality, set the EN output port to low.

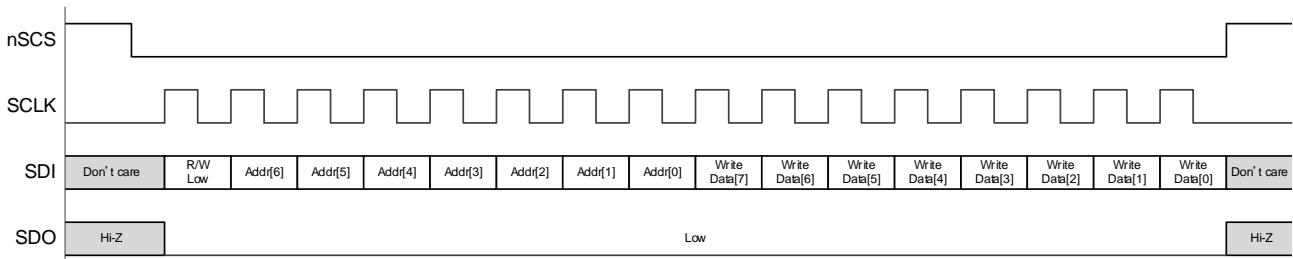

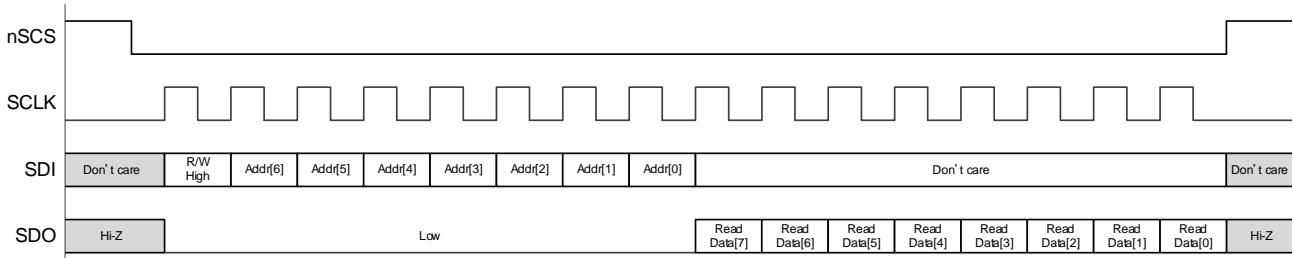

#### 2.1.2 SPI Communication Pins (Slave Side): SDO, SDI, SCLK, nSCS

The SPI communication pins are used to set smart gate driver registers and to check the fault status. SPI communication is performed by the 4-wire SPI communication function, or the 3-wire serial I/O and chip select signal with digital output function. Connect the MCU's SPI data output port to the SDI pin, the MCU's SPI data input port to the SDO pin, the MCU's SPI clock output port to the SCLK pin, and the MCU's SPI chip select output port to the nSCS pin. Since the SDO pin of the smart gate driver is an open drain output, the pull-up resistor option of MCU or external pull-up resistor is required. For SPI timing specifications and communication format of this device, refer to **5.5** and **6.6** of the “*RAA306012 Datasheet (R18DS0037EJ)*”, and for details of control registers, refer to **2.2**.

- (1) After the MCU reset is released, the SDI and SCLK pins of the smart gate driver are driven Low by a pull-down resistor ( $380\text{k}\Omega$ ) each and the nSCS pin is driven High by a pull-up resistor ( $380\text{k}\Omega$ ) even if all SPI communication ports of MCU are input function. However, the SDO pin is Hi-Z during non-communication because it is an open-drain output. Therefore, it is necessary to enable the pull-up resistor option of MCU when not mounting the external pull-up resistor.

- (2) In the MCU port settings, enable the SPI communication function of the corresponding ports. Set the communication speed (SCLK) to 5MHz or less. However, the operable communication speed depends on the wiring load on the SPI communication pins and the impedance of the pull-up resistor on the SDO pin. So, it is necessary to verify that the actual SPI timings meet the specifications to determine the communication speed.

- (3) SPI communication can be performed when the EN output pin is High (Operating Mode). When the EN output port is set to Low, SPI communication is disabled. For details of SPI communication sequence for the register setting and fault status check of the smart gate driver, refer to **Chapter 3**.

### 2.1.3 INz (z = 1, 2, 3, 4, 5, 6) Pins

The INz (z = 1, 2, 3, 4, 5, 6) pins are input pins to control each phase gate driver output of the smart gate driver. Connect to the MCU's PWM output ports (Now referred to as INz (z = 1, 2, 3, 4, 5, 6) output ports). The INz (z = 1, 2, 3, 4, 5, 6) pins are assigned to the gate driver control inputs Hlx and Llx (x = A, B, C) according to the register settings of the smart gate driver. The gate driver outputs are controlled based on the truth table (Refer to **6.4.2** in the **"RAA306012 Datasheet (R18DS0037EJ)"**) according to the polarity of Hlx and Llx (x = A, B, C).

- (1) After the MCU reset is released, these pins are driven Low by the pull-down resistors (380kΩ) on each INz (z = 1, 2, 3, 4, 5, 6) pin even if the EN output port is an input function.,

- (2) In the MCU port settings, set to the digital output port and Low output as the setting in Sleep Mode of the smart gate driver. These port settings prevent unexpected gate driver operation when the EN output port is set to High.

- (3) After the EN output port is set to High, set the Phase-A Gate Driver Input Selection Register (GDSELA), Phase-B Gate Driver Input Selection Register (GDSELB), and Phase-C Gate Driver Input Selection Register (GDSELC) to the suitable value to assign the gate driver control inputs Hlx and Llx (x = A, B, and C) from INz (z = 1, 2, 3, 4, 5, 6) pins. Note that INz (z = 1, 2, 3, 4, 5, 6) output ports should be kept Low during these register settings. These port settings prevent abnormal operation caused by register setting changes.

- (4) The smart gate driver register settings are reset when the EN pin goes Low. Therefore, when setting the EN output port to Low, set the INz (z = 1, 2, 3, 4, 5, 6) output ports to Low first and then set the EN output port to Low.

- (5) When the nFAULT input port goes Low due to a fault detection and the gate driver is disabled, set the INz (z = 1, 2, 3, 4, 5, 6) output ports to Low. When the smart gate driver is recovered from a fault condition, the gate driver is enabled according to the fault condition. These port settings prevent unexpected gate driver operation. For the fault and recovery action of the gate driver, refer to **6.2** in the **"RAA306012 Datasheet (R18DS0038EJ)"**.

### 2.1.4 nFAULT Pin

The nFAULT pin is output pin for the fault indicator of the smart gate driver. It is recommended to connect the MCU port (Now referred to as nFAULT input port) with an external interrupt function to this pin. It is pulled low if any of the fault conditions occur. It is pulled high when all the fault conditions are removed, and all chip power rail start-ups are done. The smart gate driver can be configured to enable or disable each fault detection by register settings. For details of the Fault Control Registers, refer to **2.2.1.5** and **2.2.1.6**.

- (1) After the MCU reset is released, the nFAULT input port might be a digital input function by the MCU default setting. And the nFAULT pin becomes Hi-Z by the open-drain output. Therefore, after the MCU reset is released, it is necessary to enable the pull-up resistor option of MCU.

- (2) In the MCU port settings, set to the digital input port or interrupt function to confirm the fault indicator of the smart gate driver. Also, the pull-up resistor option must be enabled.

- (3) At power-on, when the EN output port is Low and the nFAULT pin has pull-up resistor, the nFAULT input port goes High. The nFAULT input port switches to Low when the EN output port is set to High. The nFAULT input port goes High again if all power rail start-ups of smart gate driver have been done and all fault conditions are removed. For the control sequence considering the nFAULT behavior, refer to **Chapter 3**.

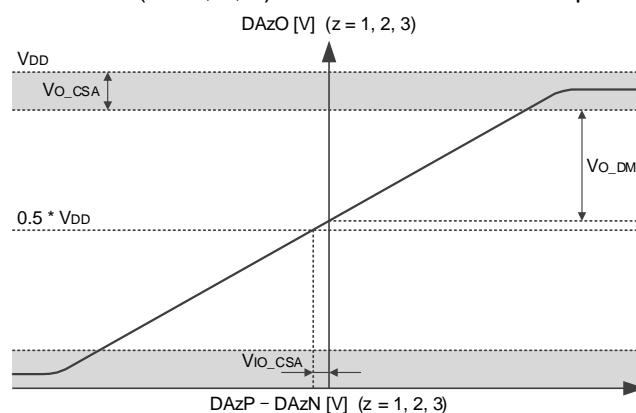

## 2.1.5 DAzO (z = 1, 2, 3) Pins

DAzO (z = 1, 2, 3) pin are analog output pins for the differential amplifiers, BEMF sense amplifier, or analog multiplexer in the smart gate driver. Connect the analog input function ports of the MCU (Now referred to as DAzO (z = 1, 2, 3) input ports) to these pins.

- (1) After the MCU reset is released, these ports become analog input ports by the MCU default setting, but are driven Low by the pull-down resistor (330kΩ) on the DAzO (z = 1, 2, 3) pins of the smart gate driver.

- (2) In the MCU port settings, set to the analog input port for A/D conversion of the analog output signal from the smart gate driver.

- (3) When the EN output port is high, the output of the DA3O pin can be changed by the analog multiplexer according to the register setting of the smart gate driver. When DA3O output is not used, set the MUX bit in the Sense Block Control 5 register (SNSCTL5) of the smart gate driver to “000b”, and the pull-down resistor (330kΩ) is enabled. For details, refer to Section **6.5.5** of the “*RAA306012 Datasheet (R18DS0037EJ)*”.

## 2.1.6 CMPzO (z = 1, 2, 3) Pins

The CMPzO (z = 1, 2, 3) pins are used as general-purpose comparator output pins for the smart gate driver or as input pins to control the detect phase selection of the BEMF sense amplifier. When used as output pins to a general-purpose comparator, it is recommended to connect the digital input function or the external interrupt function ports of the MCU (Now referred to as CMPzO (z = 1, 2, 3) input/output ports). When used as the detect phase selection for the BEMF sense amplifier, connect the digital output ports of the MCU. The CMPzO (z = 1, 2, 3) pin functions are switched by the register settings of the smart gate driver. For details of the control register, refer to **2.2.1.15**, and for details of the detect phase selection of the BEMF sense amplifier, refer to Section **6.5.3** of the “*RAA306012 Datasheet (R18DS0037EJ)*”.

- (1) After the MCU reset is released, the CMPzO (z = 1, 2, 3) input/output ports become digital input ports by the MCU default setting. The CMPzO (z = 1, 2, 3) pins are driven Low by the pull-down resistor (380kΩ) by the smart gate driver.

- (2) Since the default function of the CMPzO (z = 1, 2, 3) pins of the smart gate driver is a general purpose comparator output, set to the digital input function or interrupt function for the CMPzO (z = 1, 2, 3) input/output ports.

- (3) To use CMPzO (z = 1, 2, 3) pins for detect phase selection of the BEMF sense amplifier, the register settings of the smart gate driver must be set to switch the pin function of the smart gate driver to the detect phase selection input first for avoiding the collision by output signals of the MCU and smart gate driver. And after the register setting, the MCU ports used for the detect phase selection must be set to the digital output port. Note that the detect phase of the BEMF sense amplifier is selected from the two pins CMP1O/2O or CMP1O/3O. The MCU ports not used as detect phase selection can be used as input port for general purpose comparator output. In this case, set to the digital input port or interrupt function. The pin not used as detect phase selection can be used as input pin for general-purpose comparator output. In this case, set the digital input function or the external interrupt function.

- (4) The register settings of the smart gate driver are reset when the EN pin goes Low. To avoid the collision by output signals of the MCU and smart gate driver caused by the reset of register settings, when setting the EN output port to Low, set CMPzO (z = 1, 2, 3) input/output ports to digital input ports first, and then set the EN output port to Low.

## 2.1.7 nSMPL Pin

The nSMPL pin is an input pin to control the S/H function of the differential amplifier or the BEMF sense amplifier of the smart gate driver. Connect the digital output function port of the MCU (Now referred to as nSMPL output port). For details of the S/H function, refer to **6.5.2** and **6.5.3** of the “**RAA306012 Datasheet (R18DS0037EJ)**”.

- (1) After the MCU reset is released, the nSMPL pin is driven Low by the smart gate driver pull-down resistor (380kΩ) even if the nSMPL output port is an input function.

- (2) In the MCU port settings, when using the S/H function, set to the digital output function and Low output. When not using the S/H function, connect the nSMPL pin to GND.

- (3) After the S/H function is enabled by the register setting of the smart gate driver, sampling operation is performed when the nSMPL pin is Low, and hold operation is performed when the nSMPL pin is High. Note that the S/H operation of the BEMF sense amplifier has a period of hold operation even when the nSMPL output pin is Low. Refer to Section **6.5.3** in the “**RAA306012 Datasheet (R18DS0037EJ)**”.

## 2.2 Control Register

This device has built-in Control Registers for checking fault status, enabling/disabling fault detections and function blocks, adjusting gate driver switching characteristics, setting operation mode and gain settings, etc. of sense block. SPI communication and register settings are enabled after setting the EN pin to High. However, it is recommended that the register settings of the smart gate driver be executed after the smart gate driver mode enters Operating Mode. All registers are reset when the smart gate driver mode enters Sleep Mode or Shutdown Mode, so it is necessary to set each register again after entering Operating Mode.

**Figure 2-1** shows SPI communication format. **Table 2-1** shows the Control Register map. For the SPI communication port settings of the MCU, refer to **2.1.2**.

### Write Protocol

### Read Protocol

**Figure 2-1 SPI Communication Format**

**Table 2-1 Control Register Map**

| Address | Register Name                       | Symbol  | Access Type | Initial value | 7            | 6            | 5            | 4            | 3            | 2             | 1            | 0            |

|---------|-------------------------------------|---------|-------------|---------------|--------------|--------------|--------------|--------------|--------------|---------------|--------------|--------------|

| 0x00    | Fault Status 0                      | FLTSTS0 | R           | 00h           | FAULT        | SR_FAULT     | OV_UVLO      | VDS_OCP      | VGS_FAULT    | CS_OCP        | OTSD         | TWARN        |

| 0x01    | Fault Status 1                      | FLTSTS1 | R           | 00h           | VDRV_UV      | VDRV_OV      | SR_OCP       | VCP_UV       | VM_UV        | VM_OV         | N/A          | N/A          |

| 0x02    | Fault Status 2                      | FLTSTS2 | R           | 00h           | VDSHA_OCP    | VDSL_A_OCP   | VGSHA_FAULT  | VGSLA_FAULT  | VDSHB_OCP    | VDSL_B_OCP    | VGSHB_FAULT  | VGSLB_FAULT  |

| 0x03    | Fault Status 3                      | FLTSTS3 | R           | 00h           | VDSHC_OCP    | VDSL_C_OCP   | VGSHC_FAULT  | VGSLC_FAULT  | N/A          | CS1_OCP       | CS2_OCP      | CS3_OCP      |

| 0x04    | Fault Control 1                     | FLTCTL1 | R/W         | 00h           | DIS_VDRVUV   | DIS_VDRVUV   | DIS_SR0C     | DIS_VCPUV    | DIS_VMUV     | DIS_VMOV      | DIS_OTSD     | TWARN REP    |

| 0x05    | Fault Control 2                     | FLTCTL2 | R/W         | 07h           | CSOCP_MODE1  | CSOCP_MODE0  | VDSOCP_MODE1 | VDSOCP_MODE0 | DIS_VGSFLT   | DIS_CS1OCP    | DIS_CS2OCP   | DIS_CS3OCP   |

| 0x06    | IC Control 1                        | ICCTL1  | R/W         | 35h           | CLR_FLT      | WRITE_LOCK2  | WRITE_LOCK1  | WRITE_LOCK0  | PWMMODE      | CSOCP_TH2     | CSOCP_TH1    | CSOCP_TH0    |

| 0x07    | IC Control 2                        | ICCTL2  | R/W         | 50h           | DEAD_TIME1   | DEAD_TIME0   | T_GT1        | T_GT0        | BEMF_EN      | DA1_EN        | DA2_EN       | DA3_EN       |

| 0x08    | Gate Driver Control                 | GDCTL   | R/W         | FFh           | ISRC_HS3     | ISRC_HS2     | ISRC_HS1     | ISRC_HS0     | ISRC_LS3     | ISRC_LS2      | ISRC_LS1     | ISRC_LS0     |

| 0x09    | Over Current Protection Control     | OCPCTL  | R/W         | 00h           | VDS_TH3      | VDS_TH2      | VDS_TH1      | VDS_TH0      | TRETRY_CSOCP | TRETRY_VDSOCP | DEG_TIME1    | DEG_TIME0    |

| 0x0A    | Phase-A Gate Driver Input Selection | GDSELA  | R/W         | 14h           | CMP1_HYS     | HOA_SEL2     | HOA_SEL1     | HOA_SEL0     | VMUV_TH      | LOA_SEL2      | LOA_SEL1     | LOA_SEL0     |

| 0x0B    | Phase-B Gate Driver Input Selection | GDSELB  | R/W         | 25h           | CMP2_HYS     | HOB_SEL2     | HOB_SEL1     | HOB_SEL0     | PDMODE       | LOB_SEL2      | LOB_SEL1     | LOB_SEL0     |

| 0x0C    | Phase-C Gate Driver Input Selection | GDSELC  | R/W         | 36h           | CMP3_HYS     | HOC_SEL2     | HOC_SEL1     | HOC_SEL0     | CPUV_TH      | LOC_SEL2      | LOC_SEL1     | LOC_SEL0     |

| 0x0D    | Sense Block Control 1               | SNSCTL1 | R/W         | AAh           | BEMF_GAIN1   | BEMF_GAIN0   | DA1_GAIN1    | DA1_GAIN0    | DA2_GAIN1    | DA2_GAIN0     | DA3_GAIN1    | DA3_GAIN0    |

| 0x0E    | Sense Block Control 2               | SNSCTL2 | R/W         | 00h           | CAL_BCONN    | BEMF_PH2     | BEMF_PH1     | BEMF_PH0     | BEMF_SH      | DA1_SH        | DA2_SH       | DA3_SH       |

| 0x0F    | Sense Block Control 3               | SNSCTL3 | R/W         | 88h           | CMP1_VTH3    | CMP1_VTH2    | CMP1_VTH1    | CMP1_VTH0    | CMP2_VTH3    | CMP2_VTH2     | CMP2_VTH1    | CMP2_VTH0    |

| 0x10    | Sense Block Control 4               | SNSCTL4 | R/W         | 80h           | CMP3_VTH3    | CMP3_VTH2    | CMP3_VTH1    | CMP3_VTH0    | CAL_CONN     | CAL_DA1       | CAL_DA2      | CAL_DA3/BEMF |

| 0x11    | Sense Block Control 5               | SNSCTL5 | R/W         | 00h           | DIS_SADT     | RESERVED11_6 | CTL6_UNLOCK  | RESERVED11_4 | RESERVED11_3 | MUX2          | MUX1         | MUX0         |

| 0x12    | Sense Block Control 6               | SNSCTL6 | R/W         | 40h           | RESERVED12_7 | BEMF_OFFSET  | RESERVED12_5 | RESERVED12_4 | RESERVED12_3 | RESERVED12_2  | RESERVED12_1 | GD_AOR       |

## 2.2.1 Register Description

### 2.2.1.1 Fault Status 0 Register: FLTSTS0 (Address = 0x00) [Default = 0x00]

**Table 2-2** and **Table 2-3** show the details of Fault Status 0 register.

**Table 2-2 Fault Status 0 Register FLTSTS0**

| 7     | 6        | 5       | 4       | 3         | 2      | 1     | 0     |

|-------|----------|---------|---------|-----------|--------|-------|-------|

| FAULT | SR_FAULT | OV_UVLO | VDS_OCP | VGS_FAULT | CS_OCP | OTSD  | TWARN |

| R: 0b | R: 0b    | R: 0b   | R: 0b   | R: 0b     | R: 0b  | R: 0b | R: 0b |

**Table 2-3 Fault Status 0 Register FLTSTS0 Description [1]**

| Bit | Field     | Type | Default | Description                                                                                |

|-----|-----------|------|---------|--------------------------------------------------------------------------------------------|

| 7   | FAULT     | R    | 0b      | Logic OR of all Fault Status bits                                                          |

| 6   | SR_FAULT  | R    | 0b      | Logic OR of the Fault Status bits for buck switching regulator: VDRV_UV, VDRV_OV, SR_OCP   |

| 5   | OV_UVLO   | R    | 0b      | Logic OR of the Fault Status bits for undervoltage and overvoltage: VCP_UV, VM_UV, VM_OV   |

| 4   | VDS_OCP   | R    | 0b      | Logic OR of the Fault Status bits for V <sub>DS</sub> overcurrent: VDSHx_OCP, VDSLx_OCP    |

| 3   | VGS_FAULT | R    | 0b      | Logic OR of the Fault Status bits for V <sub>GS</sub> fault : VGSHx_FAULT, VGSLx_FAULT     |

| 2   | CS_OCP    | R    | 0b      | Logic OR of the Fault Status bits for current sense overcurrent: CS1_OCP, CS2_OCP, CS3_OCP |

| 1   | OTSD      | R    | 0b      | Indicator of thermal shutdown                                                              |

| 0   | TWARN     | R    | 0b      | Indicator of thermal warning                                                               |

Note1: Fault Status registers are reset by writing 1b to CLR\_FLT of ICCTL1 register, or recovery low pulse (> tsleep: 0.85ms) on EN pin.

### 2.2.1.2 Fault Status 1 Register: FLTSTS1 (Address = 0x01) [Default = 0x00]

**Table 2-4** and **Table 2-5** show the details of Fault Status 1 register.

**Table 2-4 Fault Status 1 Register FLTSTS1**

| 7       | 6       | 5      | 4      | 3     | 2     | 1     | 0     |

|---------|---------|--------|--------|-------|-------|-------|-------|

| VDRV_UV | VDRV_OV | SR_OCP | VCP_UV | VM_UV | VM_OV | N/A   | N/A   |

| R: 0b   | R: 0b   | R: 0b  | R: 0b  | R: 0b | R: 0b | R: 0b | R: 0b |

**Table 2-5 Fault Status 1 Register FLTSTS1 Description [1]**

| Bit | Field   | Type | Default | Description                                                              |

|-----|---------|------|---------|--------------------------------------------------------------------------|

| 7   | VDRV_UV | R    | 0b      | Indicator of VDRV undervoltage (V <sub>DRVUV</sub> )                     |

| 6   | VDRV_OV | R    | 0b      | Indicator of VDRV overvoltage (V <sub>DRVOV</sub> )                      |

| 5   | SR_OCP  | R    | 0b      | Indicator of buck switching regulator overcurrent (I <sub>OC2_SR</sub> ) |

| 4   | VCP_UV  | R    | 0b      | Indicator of VCP undervoltage (V <sub>CPUV</sub> )                       |

| 3   | VM_UV   | R    | 0b      | Indicator of VM undervoltage (V <sub>MUV</sub> )                         |

| 2   | VM_OV   | R    | 0b      | Indicator of VM overvoltage (V <sub>MOV</sub> )                          |

| 1   | N/A     | R    | 0b      | Not assigned                                                             |

| 0   | N/A     | R    | 0b      | Not assigned                                                             |

Note1: Fault Status registers are reset by writing 1b to CLR\_FLT of ICCTL1 register, or recovery low pulse (> tsleep: 0.85ms) on EN pin.

**2.2.1.3 Fault Status 2 Register: FLTSTS2 (Address = 0x02) [Default = 0x00]****Table 2-6** and **Table 2-7** show the details of Fault Status 2 register.**Table 2-6 Fault Status 2 Register FLTSTS2**

| 7         | 6          | 5           | 4            | 3         | 2          | 1           | 0            |

|-----------|------------|-------------|--------------|-----------|------------|-------------|--------------|

| VDSHA_OCP | VDSL_A_OCP | VGSHA_FAULT | VGSL_A_FAULT | VDSHB_OCP | VDSL_B_OCP | VGSHB_FAULT | VGSL_B_FAULT |

| R: 0b     | R: 0b      | R: 0b       | R: 0b        | R: 0b     | R: 0b      | R: 0b       | R: 0b        |

**Table 2-7 Fault Status 2 Register FLTSTS2 Description [1]**

| Bit | Field        | Type | Default | Description                                                          |

|-----|--------------|------|---------|----------------------------------------------------------------------|

| 7   | VDSHA_OCP    | R    | 0b      | Indicator of V <sub>ds</sub> overcurrent on Phase-A high-side MOSFET |

| 6   | VDSL_A_OCP   | R    | 0b      | Indicator of V <sub>ds</sub> overcurrent on Phase-A low-side MOSFET  |

| 5   | VGSHA_FAULT  | R    | 0b      | Indicator of V <sub>gs</sub> fault on Phase-A high-side MOSFET       |

| 4   | VGSL_A_FAULT | R    | 0b      | Indicator of V <sub>gs</sub> fault on Phase-A low-side MOSFET        |

| 3   | VDSHB_OCP    | R    | 0b      | Indicator of V <sub>ds</sub> overcurrent on Phase-B high-side MOSFET |

| 2   | VDSL_B_OCP   | R    | 0b      | Indicator of V <sub>ds</sub> overcurrent on Phase-B low-side MOSFET  |

| 1   | VGSHB_FAULT  | R    | 0b      | Indicator of V <sub>gs</sub> fault on Phase-B high-side MOSFET       |

| 0   | VGSL_B_FAULT | R    | 0b      | Indicator of V <sub>gs</sub> fault on Phase-B low-side MOSFET        |

Note1: Fault Status registers are reset by writing 1b to CLR\_FLT of ICCTL1 register, or recovery low pulse (&gt; tsleep: 0.85ms) on EN pin.

**2.2.1.4 Fault Status 3 Register: FLTSTS3 (Address = 0x03) [Default = 0x00]****Table 2-8** and **Table 2-9** show the details of Fault Status 3 register.**Table 2-8 Fault Status 3 Register FLTSTS3**

| 7         | 6          | 5           | 4            | 3     | 2       | 1       | 0       |

|-----------|------------|-------------|--------------|-------|---------|---------|---------|

| VDSHC_OCP | VDSL_C_OCP | VGSHC_FAULT | VGSL_C_FAULT | N/A   | CS1_OCP | CS2_OCP | CS3_OCP |

| R: 0b     | R: 0b      | R: 0b       | R: 0b        | R: 0b | R: 0b   | R: 0b   | R: 0b   |

**Table 2-9 Fault Status 3 Register FLTSTS3 Description [1]**

| Bit | Field        | Type | Default | Description                                                          |

|-----|--------------|------|---------|----------------------------------------------------------------------|

| 7   | VDSHC_OCP    | R    | 0b      | Indicator of V <sub>ds</sub> overcurrent on Phase-C high-side MOSFET |

| 6   | VDSL_C_OCP   | R    | 0b      | Indicator of V <sub>ds</sub> overcurrent on Phase-C low-side MOSFET  |

| 5   | VGSHC_FAULT  | R    | 0b      | Indicator of V <sub>gs</sub> fault on Phase-C high-side MOSFET       |

| 4   | VGSL_C_FAULT | R    | 0b      | Indicator of V <sub>gs</sub> fault on Phase-C low-side MOSFET        |

| 3   | N/A          | R    | 0b      | Not assigned                                                         |

| 2   | CS1_OCP      | R    | 0b      | Indicator of current sense overcurrent by DA1P, DA1N inputs          |

| 1   | CS2_OCP      | R    | 0b      | Indicator of current sense overcurrent by DA2P, DA2N inputs          |

| 0   | CS3_OCP      | R    | 0b      | Indicator of current sense overcurrent by DA3P, DA3N inputs          |

Note1: Fault Status registers are reset by writing 1b to CLR\_FLT of ICCTL1 register, or recovery low pulse (&gt; tsleep: 0.85ms) on EN pin.

**2.2.1.5 Fault Control 1 Register: FLTCTL1 (Address = 0x04) [Default = 0x00]****Table 2-10** and **Table 2-11** show the details of Fault Control 1 register.**Table 2-10 Fault Control 1 Register FLTCTL1**

| 7          | 6          | 5        | 4         | 3        | 2        | 1        | 0         |

|------------|------------|----------|-----------|----------|----------|----------|-----------|

| DIS_VDRVUV | DIS_VDRVUV | DIS_SROC | DIS_VCPUV | DIS_VMUV | DIS_VMOV | DIS_OTSD | TWARN_REP |

| R/W: 0b    | R/W: 0b    | R/W: 0b  | R/W: 0b   | R/W: 0b  | R/W: 0b  | R/W: 0b  | R/W: 0b   |

**Table 2-11 Fault Control 1 Register FLTCTL1 Description**

| Bit | Field      | Type | Default | Description                                                                                                                   |

|-----|------------|------|---------|-------------------------------------------------------------------------------------------------------------------------------|

| 7   | DIS_VDRVUV | R/W  | 0b      | Write 1b to report status only for VDRV undervoltage ( $V_{DRVUV}$ ) detection                                                |

| 6   | DIS_VDRVUV | R/W  | 0b      | Write 1b to report status only for VDRV overvoltage ( $V_{DRVUV}$ ) detection                                                 |

| 5   | DIS_SROC   | R/W  | 0b      | Write 1b to report status only for buck switching regulator overcurrent ( $I_{OC2\_SR}$ ) protection                          |

| 4   | DIS_VCPUV  | R/W  | 0b      | Write 1b to report status only for VCP undervoltage ( $V_{CPUV}$ ) detection                                                  |

| 3   | DIS_VMUV   | R/W  | 0b      | Write 1b to report status only for VM undervoltage ( $V_{VMUV}$ ) detection                                                   |

| 2   | DIS_VMOV   | R/W  | 0b      | Write 1b to report status only for VM overvoltage fault ( $V_{VMOV}$ ) detection                                              |

| 1   | DIS_OTSD   | R/W  | 0b      | Write 1b to report status only for thermal shutdown                                                                           |

| 0   | TWARN_REP  | R/W  | 0b      | 0b: Thermal warning is reported on only TWARN bit.<br>1b: Thermal warning is reported on nFAULT pin, FAULT bit and TWARN bit. |

**2.2.1.6 Fault Control 2 Register: FLTCTL2 (Address = 0x05) [Default = 0x07]****Table 2-12** and **Table 2-13** show the details of Fault Control 2 register.**Table 2-12 Fault Control 2 Register FLTCTL2**

| 7           | 6           | 5            | 4            | 3          | 2          | 1          | 0          |

|-------------|-------------|--------------|--------------|------------|------------|------------|------------|

| CSOCP_MODE1 | CSOCP_MODE0 | VDSOCP_MODE1 | VDSOCP_MODE0 | DIS_VGSFLT | DIS_CS1OCP | DIS_CS2OCP | DIS_CS3OCP |

| R/W: 0b     | R/W: 0b     | R/W: 0b      | R/W: 0b      | R/W: 0b    | R/W: 1b    | R/W: 1b    | R/W: 1b    |

**Table 2-13 Fault Control 2 Register FLTCTL2 Description**

| Bit | Field        | Type | Default | Description                                                                                                                                                      |

|-----|--------------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CSOCP_MODE1  | R/W  | 0b      | Response mode for current sense overcurrent<br>00b: Latch upon current sense overcurrent <sup>Note2</sup><br>01b: Automatic retry upon current sense overcurrent |

| 6   | CSOCP_MODE0  | R/W  | 0b      | 10b: Report on nFAULT pin, FAULT, CS_OCP and CS1/2/3_OCP bits only. No action takes place.<br>11b: Disable. No report and no action takes place.                 |

| 5   | VDSOCP_MODE1 | R/W  | 0b      | Response mode for $V_{DS}$ overcurrent<br>00b: Latch upon $V_{DS}$ overcurrent <sup>Note2</sup><br>01b: Automatic retry upon $V_{DS}$ overcurrent                |

| 4   | VDSOCP_MODE0 | R/W  | 0b      | 10b: Report on nFAULT pin, FAULT, VDS_OCP, VDSHx_OCP and VDSLx_OCP bits only.<br>No action takes place.<br>11b: Disable. No report and no action takes place     |

| 3   | DIS_VGSFLT   | R/W  | 0b      | Write 1b to disable $V_{GS}$ fault detection                                                                                                                     |

| 2   | DIS_CS1OCP   | R/W  | 1b      | Write 1b to disable current sense overcurrent by DA1P, DA1N inputs                                                                                               |

| 1   | DIS_CS2OCP   | R/W  | 1b      | Write 1b to disable current sense overcurrent by DA2P, DA2N inputs                                                                                               |

| 0   | DIS_CS3OCP   | R/W  | 1b      | Write 1b to disable current sense overcurrent by DA3P, DA3N inputs                                                                                               |

Note2: Latch is recovered by writing 1b to CLR\_FLT of ICCTL1 register, or recovery low pulse ( $> t_{sleep}$ : 0.85ms) on EN pin.

**2.2.1.7 IC Control 1 Register: ICCTL1 (Address = 0x06) [Default = 0x35]****Table 2-14** and **Table 2-15** show the details of IC Control 1 register.**Table 2-14 IC Control 1 Register ICCTL1**

| 7       | 6            | 5            | 4            | 3        | 2         | 1         | 0         |

|---------|--------------|--------------|--------------|----------|-----------|-----------|-----------|

| CLR_FLT | WRITER_LOCK2 | WRITER_LOCK1 | WRITER_LOCK0 | PWM MODE | CSOCP_TH2 | CSOCP_TH1 | CSOCP_TH0 |

| R/W: 0b | R/W: 0b      | R/W: 1b      | R/W: 1b      | R/W: 0b  | R/W: 1b   | R/W: 0b   | R/W: 1b   |

**Table 2-15 IC Control 1 Register ICCTL1 Description**

| Bit | Field        | Type | Default | Description                                                                                                                                                                                        |

|-----|--------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CLR_FLT      | R/W  | 0b      | Write 1b to clear the all flagged fault status bits. This bit is reset to 0b automatically.                                                                                                        |

| 6   | WRITER_LOCK2 | R/W  | 0b      |                                                                                                                                                                                                    |

| 5   | WRITER_LOCK1 | R/W  | 1b      |                                                                                                                                                                                                    |

| 4   | WRITER_LOCK0 | R/W  | 1b      | Write 110b to ignore all further register write except WRITER_LOCK[2:0].<br>Write 011b to unlock to allow register write.<br>Writing other values takes no effect.                                 |

| 3   | PWM MODE     | R/W  | 0b      | 0b: 3-Phase H/LI mode, 1b: 3-Phase PWM mode                                                                                                                                                        |

| 2   | CSOCP_TH2    | R/W  | 1b      |                                                                                                                                                                                                    |

| 1   | CSOCP_TH1    | R/W  | 0b      |                                                                                                                                                                                                    |

| 0   | CSOCP_TH0    | R/W  | 1b      | Threshold voltage setting of current sense overcurrent by DAzP, DAzN (z=1,2,3) inputs<br>000b: 51mV, 001b: 105mV, 010b: 157mV, 011b: 208mV,<br>100b: 260mV, 101b: 516mV, 110b: 773mV, 111b: 1029mV |

**2.2.1.8 IC Control 2 Register: ICCTL2 (Address = 0x07) [Default = 0x50]****Table 2-16** and **Table 2-17** show the details of IC Control 2 register.**Table 2-16 IC Control 2 Register ICCTL2**

| 7          | 6          | 5       | 4       | 3       | 2       | 1       | 0       |

|------------|------------|---------|---------|---------|---------|---------|---------|

| DEAD_TIME1 | DEAD_TIME0 | T_GT1   | T_GT0   | BEMF_EN | DA1_EN  | DA2_EN  | DA3_EN  |

| R/W: 0b    | R/W: 1b    | R/W: 0b | R/W: 1b | R/W: 0b | R/W: 0b | R/W: 0b | R/W: 0b |

**Table 2-17 IC Control 2 Register Description**

| Bit | Field      | Type | Default | Description                                                                                                                                    |

|-----|------------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DEAD_TIME1 | R/W  | 0b      | Dead time from V <sub>GS</sub> voltage monitor output to start timing of another-side turn on<br>00b: 50ns, 01b: 100ns, 10b: 200ns, 11b: 400ns |

| 6   | DEAD_TIME0 | R/W  | 1b      |                                                                                                                                                |

| 5   | T_GT1      | R/W  | 0b      | Maximum gate transition time<br>00b: 500ns, 01b: 1000ns, 10b: 2000ns, 11b: 4000ns                                                              |

| 4   | T_GT0      | R/W  | 1b      |                                                                                                                                                |

| 3   | BEMF_EN    | R/W  | 0b      | Write 1b to enable BEMF sense amplifier.                                                                                                       |

| 2   | DA1_EN     | R/W  | 0b      | Write 1b to enable differential amplifier 1.                                                                                                   |

| 1   | DA2_EN     | R/W  | 0b      | Write 1b to enable differential amplifier 2.                                                                                                   |

| 0   | DA3_EN     | R/W  | 0b      | Write 1b to enable differential amplifier 3.                                                                                                   |

**2.2.1.9 Gate Drive Control Register: GDCTL (Address = 0x08) [Default = 0xFF]****Table 2-18** and **Table 2-19** show the details of Gate Drive Control register.**Table 2-18 Gate Control Register GDCTL**

| 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|----------|----------|----------|----------|----------|----------|----------|----------|

| ISRC_HS3 | ISRC_HS2 | ISRC_HS1 | ISRC_HS0 | ISRC_LS3 | ISRC_LS2 | ISRC_LS1 | ISRC_LS0 |

| R/W: 1b  |

**Table 2-19 Gate Control Register GDCTL Description**

| Bit | Field    | Type | Default | Description                                                                                                                                                                                                                                                                                                             |

|-----|----------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ISRC_HS3 | R/W  | 1b      | High-side gate driver output source current. Sink current is 2*(source current).<br>0000b: 50mA, 0001b: 60mA, 0010b: 70mA, 0011b: 80mA,<br>0100b: 100mA, 0101b: 120mA, 0110b: 140mA, 0111b: 160mA,<br>1000b: 200mA, 1001b: 240mA, 1010b: 280mA, 1011b: 320mA,<br>1100b: 400mA, 1101b: 480mA, 1110b: 560mA, 1111b: 640mA |

| 6   | ISRC_HS2 | R/W  | 1b      |                                                                                                                                                                                                                                                                                                                         |

| 5   | ISRC_HS1 | R/W  | 1b      |                                                                                                                                                                                                                                                                                                                         |

| 4   | ISRC_HS0 | R/W  | 1b      |                                                                                                                                                                                                                                                                                                                         |

| 3   | ISRC_LS3 | R/W  | 1b      | Low-side gate driver output source current. Sink current is 2*(source current).<br>0000b: 50mA, 0001b: 60mA, 0010b: 70mA, 0011b: 80mA,<br>0100b: 100mA, 0101b: 120mA, 0110b: 140mA, 0111b: 160mA,<br>1000b: 200mA, 1001b: 240mA, 1010b: 280mA, 1011b: 320mA,<br>1100b: 400mA, 1101b: 480mA, 1110b: 560mA, 1111b: 640mA  |

| 2   | ISRC_LS2 | R/W  | 1b      |                                                                                                                                                                                                                                                                                                                         |

| 1   | ISRC_LS1 | R/W  | 1b      |                                                                                                                                                                                                                                                                                                                         |

| 0   | ISRC_LS0 | R/W  | 1b      |                                                                                                                                                                                                                                                                                                                         |

**2.2.1.10 Overcurrent Protection Control Register: OCPCTL (Address = 0x09) [Default = 0x00]****Table 2-20** and **Table 2-21** show the details of Overcurrent Protection Control register.**Table 2-20 Overcurrent Protection Control Register OCPCTL**

| 7       | 6       | 5       | 4       | 3            | 2             | 1         | 0         |

|---------|---------|---------|---------|--------------|---------------|-----------|-----------|

| VDS_TH3 | VDS_TH2 | VDS_TH1 | VDS_TH0 | TRETRY_CSOPC | TRETRY_VDSOPC | DEG_TIME1 | DEG_TIME0 |

| R/W: 0b      | R/W: 0b       | R/W: 0b   | R/W: 0b   |

**Table 2-21 Overcurrent Protection Control Register OCPCTL Description**

| Bit | Field         | Type | Default | Description                                                                                                                                                                                                                                                                                               |

|-----|---------------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VDS_TH3       | R/W  | 0b      | Threshold voltage setting of V <sub>ds</sub> overcurrent fault<br>0000b: 40mV, 0001b: 60mV, 0010b: 80mV, 0011b: 120mV,<br>0100b: 160mV, 0101b: 200mV, 0110b: 240mV, 0111b: 320mV,<br>1000b: 400mV, 1001b: 480mV, 1010b: 600mV, 1011b: 720mV,<br>1100b: 960mV, 1101b: 1200mV, 1110b: 1600mV, 1111b: 2000mV |

| 6   | VDS_TH2       | R/W  | 0b      |                                                                                                                                                                                                                                                                                                           |

| 5   | VDS_TH1       | R/W  | 0b      |                                                                                                                                                                                                                                                                                                           |

| 4   | VDS_TH0       | R/W  | 0b      |                                                                                                                                                                                                                                                                                                           |

| 3   | TRETRY_CSOPC  | R/W  | 0b      | Retry time for current sense overcurrent fault with CSOPC_MODE=01b,<br>0b: 4000μs, 1b: 70μs                                                                                                                                                                                                               |

| 2   | TRETRY_VDSOPC | R/W  | 0b      | Retry time for V <sub>ds</sub> overcurrent fault with VDSOPC_MODE=01b,<br>0b: 4000μs, 1b: 70μs                                                                                                                                                                                                            |

| 1   | DEG_TIME1     | R/W  | 0b      | Deglitch time for both current sense and V <sub>ds</sub> overcurrent fault<br>00b: 1.57μs, 01b: 2.38μs, 10b: 3.49μs, 11b: 5.73μs                                                                                                                                                                          |

| 0   | DEG_TIME0     | R/W  | 0b      |                                                                                                                                                                                                                                                                                                           |

**2.2.1.11 Phase-A Gate Driver Input Selection Register: GDSEL A (Address = 0x0A) [Default = 0x14]****Table 2-22** and **Table 2-23** show the details of Phase-A Gate Driver Input Selection register.**Table 2-22 Phase-A Gate Driver Input Selection Register GDSEL A**

| 7        | 6        | 5        | 4        | 3       | 2        | 1        | 0        |

|----------|----------|----------|----------|---------|----------|----------|----------|

| CMP1_HYS | HOA_SEL2 | HOA_SEL1 | HOA_SEL0 | VMUV_TH | LOA_SEL2 | LOA_SEL1 | LOA_SEL0 |

| R/W: 0b  | R/W: 0b  | R/W: 0b  | R/W: 1b  | R/W: 0b | R/W: 1b  | R/W: 0b  | R/W: 0b  |

**Table 2-23 Phase-A Gate Driver Input Selection Register GDSEL A Description**

| Bit | Field    | Type | Default | Description                                                                                 |

|-----|----------|------|---------|---------------------------------------------------------------------------------------------|

| 7   | CMP1_HYS | R/W  | 0b      | Comparator 1 hysteresis setting, 0b: +/-44mV, 1b: 0mV                                       |

| 6   | HOA_SEL2 | R/W  | 0b      | Input selection for Phase-A high-side gate driver <sup>Note3</sup>                          |

| 5   | HOA_SEL1 | R/W  | 0b      | 000b: Low fix, 001b: IN1, 010b: IN2, 011b: IN3, 100b: IN4, 101b: IN5, 110b: IN6, 111b: Hi-Z |

| 4   | HOA_SEL0 | R/W  | 1b      |                                                                                             |

| 3   | VMUV_TH  | R/W  | 0b      | VM under voltage threshold setting, 0b: 5.3V, 1b: 7.5V                                      |

| 2   | LOA_SEL2 | R/W  | 1b      | Input selection for Phase-A low-side gate driver <sup>Note3</sup>                           |

| 1   | LOA_SEL1 | R/W  | 0b      | 000b: Low fix, 001b: IN1, 010b: IN2, 011b: IN3, 100b: IN4, 101b: IN5, 110b: IN6, 111b: Hi-Z |

| 0   | LOA_SEL0 | R/W  | 0b      |                                                                                             |

Note3: When HOx\_SEL or LOx\_SEL bits set to 111b, the source/sink current of gate driver becomes off (Hi-Z).

**2.2.1.12 Phase-B Gate Driver Input Selection Register: GDSEL B (Address = 0x0B) [Default = 0x25]****Table 2-24** and **Table 2-25** show the details of Phase-B Gate Driver Input Selection register.**Table 2-24 Phase-B Gate Driver Input Selection Register GDSEL B**

| 7        | 6        | 5        | 4        | 3       | 2        | 1        | 0        |

|----------|----------|----------|----------|---------|----------|----------|----------|

| CMP2_HYS | HOB_SEL2 | HOB_SEL1 | HOB_SEL0 | PDMODE  | LOB_SEL2 | LOB_SEL1 | LOB_SEL0 |

| R/W: 0b  | R/W: 0b  | R/W: 1b  | R/W: 0b  | R/W: 0b | R/W: 1b  | R/W: 0b  | R/W: 1b  |

**Table 2-25 Phase-B Gate Driver Input Selection Register GDSEL B Description**

| Bit | Field    | Type | Default | Description                                                                                 |

|-----|----------|------|---------|---------------------------------------------------------------------------------------------|

| 7   | CMP2_HYS | R/W  | 0b      | Comparator 2 hysteresis setting, 0b: +/-44mV, 1b: 0mV                                       |

| 6   | HOB_SEL2 | R/W  | 0b      | Input selection for Phase-B high-side gate driver <sup>Note3</sup>                          |

| 5   | HOB_SEL1 | R/W  | 1b      | 000b: Low fix, 001b: IN1, 010b: IN2, 011b: IN3, 100b: IN4, 101b: IN5, 110b: IN6, 111b: Hi-Z |

| 4   | HOB_SEL0 | R/W  | 0b      |                                                                                             |

| 3   | PDMODE   | R/W  | 0b      | Gate driver pulldown mode after VDS_OCP, CS_OCP, 0b: Hi-Z pulldown, 1b: driver output low   |

| 2   | LOB_SEL2 | R/W  | 1b      | Input selection for Phase-B low-side gate driver <sup>Note3</sup>                           |

| 1   | LOB_SEL1 | R/W  | 0b      | 000b: Low fix, 001b: IN1, 010b: IN2, 011b: IN3, 100b: IN4, 101b: IN5, 110b: IN6, 111b: Hi-Z |

| 0   | LOB_SEL0 | R/W  | 1b      |                                                                                             |

Note3: When HOx\_SEL or LOx\_SEL bits set to 111b, the source/sink current of gate driver becomes off (Hi-Z).

**2.2.1.13 Phase-C Gate Driver Input Selection Register: GDSELC (Address = 0x0Ch) [Default = 0x36]**

**Table 2-26** and **Table 2-27** show the details of Phase-C Gate Driver Input Selection register.

**Table 2-26 Phase-C Gate Driver Input Selection Register GDSELC**

| 7        | 6        | 5        | 4        | 3       | 2        | 1        | 0        |

|----------|----------|----------|----------|---------|----------|----------|----------|

| CMP3_HYS | HOC_SEL2 | HOC_SEL1 | HOC_SEL0 | CPUV_TH | LOC_SEL2 | LOC_SEL1 | LOC_SEL0 |

| R/W: 0b  | R/W: 0b  | R/W: 1b  | R/W: 1b  | R/W: 0b | R/W: 1b  | R/W: 1b  | R/W: 0b  |

**Table 2-27 Phase-C Gate Driver Input Selection Register GDSELC Description**

| Bit | Field    | Type | Default | Description                                                      |

|-----|----------|------|---------|------------------------------------------------------------------|

| 7   | CMP3_HYS | R/W  | 0b      | Comparator 3 hysteresis setting, 0b: +/-44mV, 1b: 0mV            |

| 6   | HOC_SEL2 | R/W  | 0b      |                                                                  |

| 5   | HOC_SEL1 | R/W  | 1b      |                                                                  |

| 4   | HOC_SEL0 | R/W  | 1b      |                                                                  |

| 3   | CPUV_TH  | R/W  | 0b      | VCP under voltage threshold setting, 0b: 0.58*VDRV, 1b: 0.8*VDRV |

| 2   | LOC_SEL2 | R/W  | 1b      |                                                                  |

| 1   | LOC_SEL1 | R/W  | 1b      |                                                                  |

| 0   | LOC_SEL0 | R/W  | 0b      |                                                                  |

Note3: When HO<sub>x</sub>\_SEL or LO<sub>x</sub>\_SEL bits set to 111b, the source/sink current of gate driver becomes off (Hi-Z).

**2.2.1.14 Sense Block Control 1 Register: SNSCTL1 (Address = 0x0D) [Default = 0xAA]**

**Table 2-28** and **Table 2-29** show the details of Sense Block Control 1 register.

**Table 2-28 Sense Block Control 1 Register SNSCTL1**

| 7          | 6          | 5         | 4         | 3         | 2         | 1         | 0         |

|------------|------------|-----------|-----------|-----------|-----------|-----------|-----------|

| BEMF_GAIN1 | BEMF_GAIN0 | DA1_GAIN1 | DA1_GAIN0 | DA2_GAIN1 | DA2_GAIN0 | DA3_GAIN1 | DA3_GAIN0 |

| R/W: 1b    | R/W: 0b    | R/W: 1b   | R/W: 0b   | R/W: 1b   | R/W: 0b   | R/W: 1b   | R/W: 0b   |

**Table 2-29 Sense Block Control 1 Register SNSCTL1 Description**

| Bit | Field      | Type | Default | Description                                                                                                   |

|-----|------------|------|---------|---------------------------------------------------------------------------------------------------------------|

| 7   | BEMF_GAIN1 | R/W  | 1b      | Gain setting of BEMF sense amplifier with DA3_GAIN=00b<br>00b: 0.05V/V, 01b: 0.1V/V, 10b: 0.5V/V, 11b: 1.0V/V |

| 6   | BEMF_GAIN0 | R/W  | 0b      |                                                                                                               |

| 5   | DA1_GAIN1  | R/W  | 1b      | Gain setting of differential amplifier 1<br>00b: 5V/V, 01b: 10V/V, 10b: 20V/V, 11b: 40V/V                     |

| 4   | DA1_GAIN0  | R/W  | 0b      |                                                                                                               |

| 3   | DA2_GAIN1  | R/W  | 1b      | Gain setting of differential amplifier 2<br>00b: 5V/V, 01b: 10V/V, 10b: 20V/V, 11b: 40V/V                     |