# **COM-HPC® Carrier Design Guide**

***Guidelines for Designing COM-HPC® Carrier Boards***

---

August 10, 2023

**Rev. 2.1**

This Design Guide is not a specification. It provides COM-HPC® Carrier implementation information but does not replace the PICMG COM-HPC® specification.

The full COM-HPC® specification is needed in conjunction with this Design Guide for signal descriptions, signal integrity information and loss budgets, Module and Carrier connector pin-outs, PCB mechanical details and more.

---

© Copyright 2021, 2022, 2023 PCI Industrial Computer Manufacturers Group. The attention of adopters is directed to the possibility that compliance with or adoption of PICMG® specifications may require use of an invention covered by patent rights. PICMG® shall not be responsible for identifying patents for which a license may be required by any PICMG® specification or for conducting legal inquiries into the legal validity or scope of those patents that are brought to its attention. PICMG® specifications are prospective and advisory only. Prospective users are responsible for protecting themselves against liability for infringement of patents.

NOTICE: The information contained in this document is subject to change without notice. The material in this document details a PICMG® specification in accordance with the license and notices set forth on this page. This document does not represent a commitment to implement any portion of this specification in any company's products.

WHILE THE INFORMATION IN THIS PUBLICATION IS BELIEVED TO BE ACCURATE, PICMG® MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL INCLUDING, BUT NOT LIMITED TO, ANY WARRANTY OF TITLE OR OWNERSHIP, IMPLIED WARRANTY OF MERCHANTABILITY OR WARRANTY OF FITNESS FOR PARTICULAR PURPOSE OR USE.

In no event shall PICMG® be liable for errors contained herein or for indirect, incidental, special, consequential, reliance or cover damages, including loss of profits, revenue, data or use, incurred by any user or any third party. Compliance with this specification does not absolve manufacturers of equipment from the requirements of safety and regulatory agencies (UL, CSA, FCC, IEC, etc.).

**IMPORTANT NOTICE:** This document includes references to specifications, standards or other material not created by PICMG. Such referenced materials will typically have been created by organizations that operate under IPR policies with terms that vary widely, and under process controls with varying degrees of strictness and efficacy. PICMG has not made any enquiry into the nature or effectiveness of any such policies, processes or controls, and therefore ANY USE OF REFERENCED MATERIALS IS ENTIRELY AT THE RISK OF THE USER. Users should therefore make such investigations regarding referenced materials, and the organizations that have created them, as they deem appropriate.

PICMG®, COM-HPC®, CompactPCI®, AdvancedTCA®, ATCA®, AdvancedMC®, CompactPCI® Express, COM-HPC®, MicroTCA®, SHB Express®, and the PICMG, CompactPCI, AdvancedTCA, μTCA and ATCA logos are registered trademarks, and cPCI Serial Space™, xTCA™, IRTM™ and the IRTM logo are trademarks of the PCI Industrial Computer Manufacturers Group. All other brand or product names may be trademarks or registered trademarks of their respective holders.

---

## Table of Contents

|                                                                                           |           |

|-------------------------------------------------------------------------------------------|-----------|

| <b>1. Preface.....</b>                                                                    | <b>9</b>  |

| <b>1.1. About This Document.....</b>                                                      | <b>9</b>  |

| <b>1.2. Intended Audience.....</b>                                                        | <b>9</b>  |

| <b>1.3. No Special Word Usage.....</b>                                                    | <b>9</b>  |

| <b>1.4. No Statements of Compliance.....</b>                                              | <b>9</b>  |

| <b>1.5. Correctness Disclaimer.....</b>                                                   | <b>9</b>  |

| <b>1.6. Name and Logo Usage.....</b>                                                      | <b>9</b>  |

| <b>1.7. Intellectual Property.....</b>                                                    | <b>11</b> |

| 1.7.1. Necessary IPR Claims (Referring to Mandatory or Recommended Features).....         | 11        |

| 1.7.2. Unnecessary Claims (Referring to Optional Features or Non-normative Elements)..... | 11        |

| 1.7.3. Third Party Disclosures.....                                                       | 12        |

| 1.7.4. Copyright Notice.....                                                              | 12        |

| 1.7.5. Trademarks.....                                                                    | 12        |

| <b>1.8. Acronyms, Abbreviations and Definitions Used.....</b>                             | <b>13</b> |

| <b>1.9. Applicable Documents and Standards.....</b>                                       | <b>16</b> |

| <b>2. COM-HPC Interfaces.....</b>                                                         | <b>18</b> |

| <b>2.1. COM-HPC Client and Server Pinout Differences.....</b>                             | <b>18</b> |

| <b>3. Reference Schematics and Block Diagrams.....</b>                                    | <b>22</b> |

| <b>3.1. Sources for Technical Materials.....</b>                                          | <b>22</b> |

| <b>3.2. Schematic Conventions.....</b>                                                    | <b>22</b> |

| <b>3.3. Ethernet NBASE-T.....</b>                                                         | <b>23</b> |

| <b>3.4. Ethernet KR and KR4.....</b>                                                      | <b>24</b> |

| 3.4.1. Ethernet KR CEI Block Diagrams.....                                                | 24        |

| 3.4.2. PHY Addresses.....                                                                 | 32        |

| <b>3.5. Serial ATA.....</b>                                                               | <b>33</b> |

| 3.5.1. Cabled SATA.....                                                                   | 33        |

| 3.5.2. mSATA SSDs.....                                                                    | 34        |

| 3.5.3. M.2 SATA SSDs.....                                                                 | 34        |

| <b>3.6. PCI Express.....</b>                                                              | <b>35</b> |

| 3.6.1. General Notes.....                                                                 | 35        |

| 3.6.2. PCI Express Coupling Capacitor Locations.....                                      | 36        |

| 3.6.3. PCIe Group 0 Low Examples: Device Down, mini-PCIe, M.2 E-Key, M.2 B-Key.....       | 37        |

| 3.6.4. Dual PCIe x4 M.2 M Key NVME SSDs Examples on PCIe Group 0 High.....                | 42        |

| 3.6.5. PCIe x16 Slot Card Site on PCIe Group 1.....                                       | 45        |

| 3.6.6. PCIe Group 2.....                                                                  | 46        |

| 3.6.7. MXM-3 Graphics Card Module on Carrier.....                                         | 50        |

| 3.6.8. PCIe Reference Clocks.....                                                         | 51        |

| 3.6.9. PCIe Redrivers and Retimers.....                                                   | 56        |

| <b>3.7. USB.....</b>                                                                      | <b>57</b> |

| 3.7.1. USB Terms and General Information.....                                             | 57        |

| 3.7.2. USB 2.0 Type-A Example.....                                                        | 59        |

| 3.7.3. USB 3.2 Gen 1 and Gen 2 Type-A.....                                                | 60        |

| 3.7.4. USB 3 Redrivers.....                                                               | 60        |

| 3.7.5. USB Type-C Overview.....                                                           | 61        |

---

|                                                                                             |            |

|---------------------------------------------------------------------------------------------|------------|

| 3.7.6. USB Type-C Port Multiplexers.....                                                    | 65         |

| 3.7.7. USB Type-C Power Delivery Controllers.....                                           | 66         |

| 3.7.8. USB Type-C Port Protection Components.....                                           | 67         |

| 3.7.9. USB 3.2 Gen 2x1 Type-C Basic Implementation.....                                     | 68         |

| 3.7.10. USB 3.2 Gen 2x2 Type-C Example Implementation.....                                  | 70         |

| 3.7.11. USB4.....                                                                           | 76         |

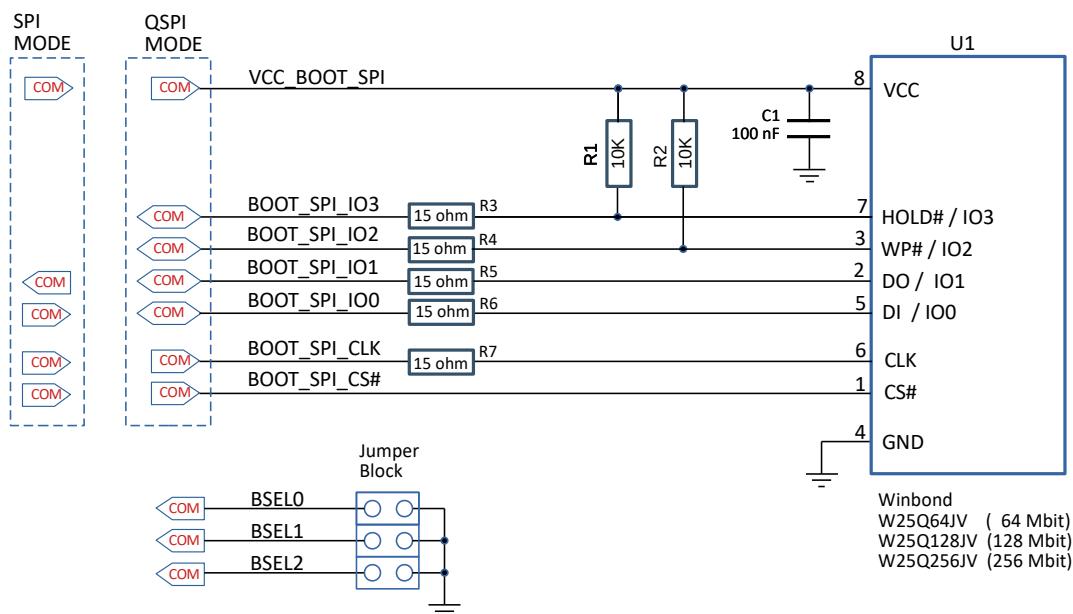

| <b>3.8. Boot SPI on Carrier.....</b>                                                        | <b>82</b>  |

| 3.9. eSPI.....                                                                              | 86         |

| <b>3.10. DisplayPort Over DDI.....</b>                                                      | <b>87</b>  |

| <b>3.11. HDMI Over DDI.....</b>                                                             | <b>90</b>  |

| <b>3.12. eDP.....</b>                                                                       | <b>92</b>  |

| 3.12.1. eDP / DP Conversions to Other Video Formats.....                                    | 94         |

| <b>3.13. MIPI-CSI Camera Interface.....</b>                                                 | <b>95</b>  |

| <b>3.14. Audio Interfaces.....</b>                                                          | <b>96</b>  |

| 3.14.1. General Discussion.....                                                             | 96         |

| 3.14.2. MIPI SoundWire Summary.....                                                         | 96         |

| 3.14.3. I2S Implementations on COM-HPC.....                                                 | 99         |

| <b>3.15. Asynchronous Serial Port Interfaces.....</b>                                       | <b>100</b> |

| 3.15.1. COM-HPC UART Interfaces.....                                                        | 100        |

| 3.15.2. Legacy Compatibility With 16C550 UART Register Set.....                             | 101        |

| 3.15.3. Alternative / Additional Carrier Board UART Implementations.....                    | 102        |

| <b>3.16. I2C / I3C Ports.....</b>                                                           | <b>103</b> |

| 3.16.1. I2C Addressing.....                                                                 | 104        |

| 3.16.2. I2C0 Example: Carrier I2C Device in S0 Power Domain.....                            | 105        |

| 3.16.3. I2C Bus Buffers / Level Translators.....                                            | 105        |

| 3.16.4. I2C1 (COM-HPC) and Optional I3C Support.....                                        | 106        |

| <b>3.17. Port 80h Debug Display Over COM-HPC USB_PD_I2C.....</b>                            | <b>107</b> |

| <b>3.18. Carrier BMC with IPMB Link to Module.....</b>                                      | <b>108</b> |

| <b>3.19. General Purpose SPI.....</b>                                                       | <b>112</b> |

| <b>3.20. Rapid Shutdown.....</b>                                                            | <b>112</b> |

| <b>3.21. Thermal Protection.....</b>                                                        | <b>113</b> |

| <b>3.22. System Management Bus (SMBus).....</b>                                             | <b>114</b> |

| <b>3.23. General Purpose Inputs / Outputs.....</b>                                          | <b>115</b> |

| <b>3.24. Module Type Detection and Protection.....</b>                                      | <b>116</b> |

| <b>4. PCB Design Rule Summaries.....</b>                                                    | <b>118</b> |

| <b>4.1. High Speed PCB Design Information – Design Guides and Books.....</b>                | <b>118</b> |

| 4.1.1. Intel and AMD Design Guides.....                                                     | 118        |

| 4.1.2. Books on High Speed PCB Design Principles.....                                       | 119        |

| <b>4.2. High Speed Serial Interfaces – General PCB Design Rules.....</b>                    | <b>120</b> |

| <b>4.3. PCB Design Rule Summaries - High Speed Differential Pair Serial Interfaces.....</b> | <b>123</b> |

| 4.3.1. NBASE-T Design Rule Summary.....                                                     | 123        |

| 4.3.2. Ethernet KR Design Rule Summary.....                                                 | 124        |

| 4.3.3. SATA Design Rule Summary.....                                                        | 125        |

| 4.3.4. PCIe Design Rule Summary.....                                                        | 126        |

| 4.3.5. USB 2.0 Design Rule Summary.....                                                     | 127        |

| 4.3.6. USB 3.2 and USB4 Design Rule Summaries.....                                          | 128        |

---

|                                                                               |            |

|-------------------------------------------------------------------------------|------------|

| 4.3.7. DisplayPort Design Rule Summary.....                                   | 130        |

| 4.3.8. eDP Design Rule Summary.....                                           | 131        |

| 4.3.9. HDMI Design Rule Summary.....                                          | 132        |

| <b>4.4. PCB Design Rules for Single Ended (SE) Interfaces.....</b>            | <b>133</b> |

| <b>5. Mechanical Considerations.....</b>                                      | <b>134</b> |

| <b>5.1. Heat Spreader / Module / Carrier Attachment Details.....</b>          | <b>134</b> |

| 5.1.1. Heat Spreader to Module Attachment Notes.....                          | 134        |

| 5.1.2. Heat Spreader / Module Assembly Attachment to Carrier and Chassis..... | 135        |

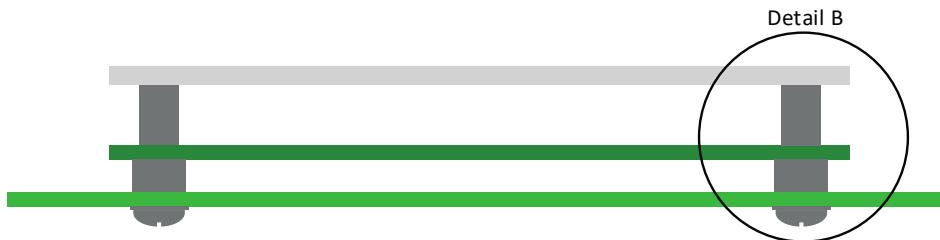

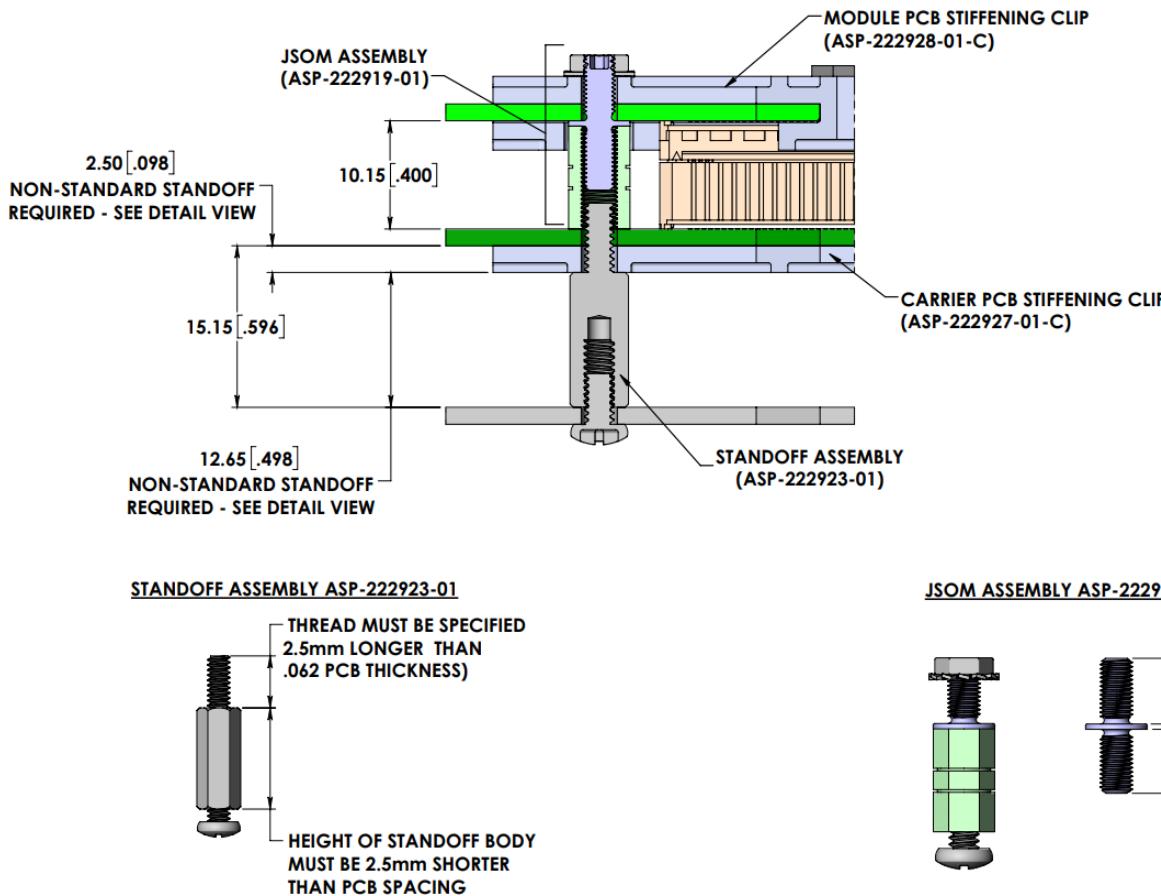

| <b>5.2. Alternative COM-HPC Board Stack Assembly Suggestion.....</b>          | <b>140</b> |

| 5.2.1. Precision Jack Screw Standoffs.....                                    | 140        |

| <b>5.3. Carrier Board Stiffener.....</b>                                      | <b>142</b> |

| <b>6. Appendices.....</b>                                                     | <b>146</b> |

| <b>6.1. Appendix A: Synchronous Ethernet.....</b>                             | <b>146</b> |

| <b>6.2. Appendix B: Alternative eDP Example.....</b>                          | <b>150</b> |

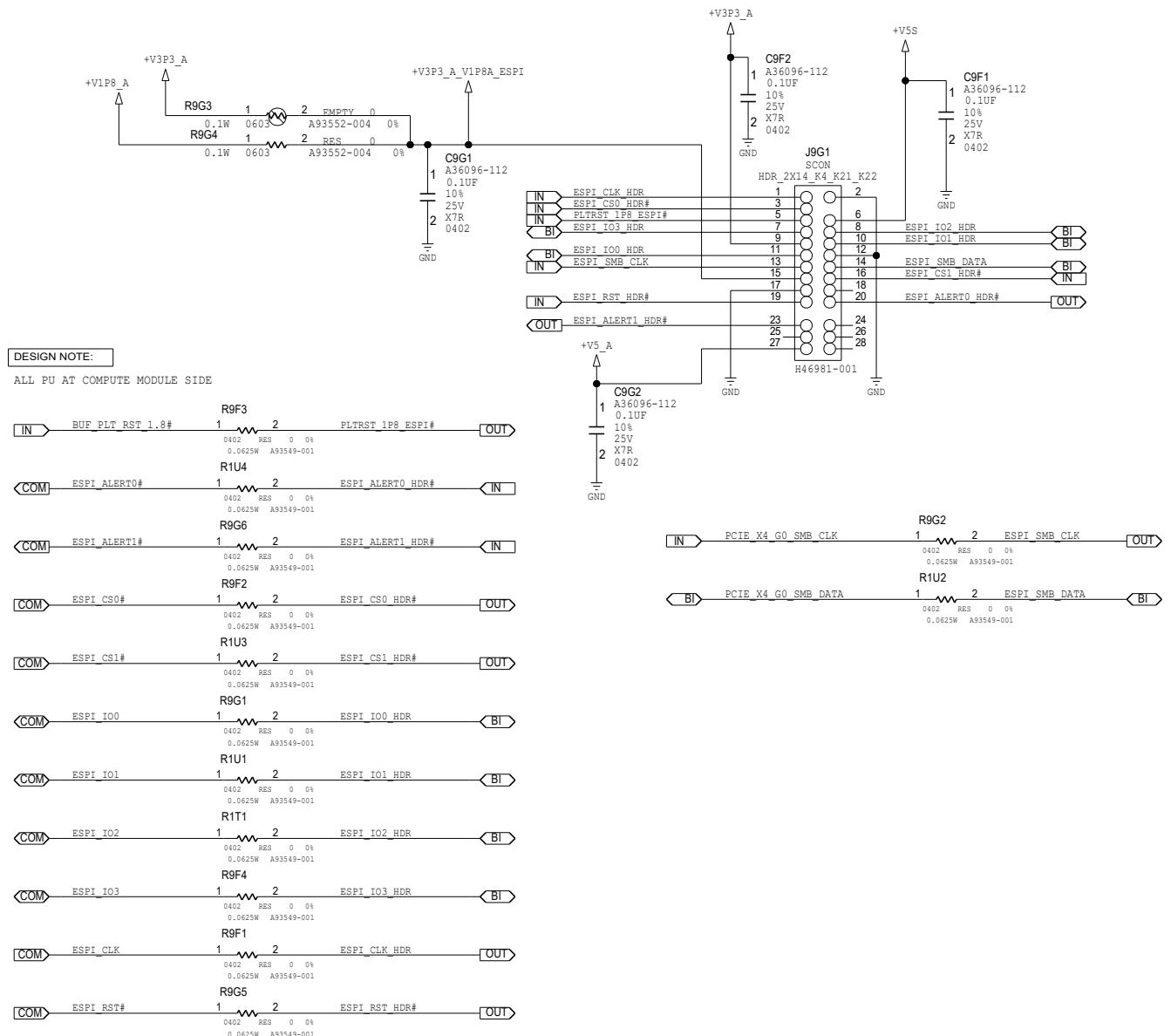

| <b>6.3. Appendix C: eSPI Header Example.....</b>                              | <b>157</b> |

| <b>6.4. Appendix D: Useful Books – General x86 Computer Topics.....</b>       | <b>158</b> |

| <b>6.5. Appendix E: Revision History.....</b>                                 | <b>159</b> |

---

## Index of Tables

|                                                                             |     |

|-----------------------------------------------------------------------------|-----|

| Table 1: Acronyms, Abbreviations and Definitions Used.....                  | 13  |

| Table 2: Client and Server Type Pinout Difference Table.....                | 18  |

| Table 3: Power Net Naming.....                                              | 22  |

| Table 4: MDIO Addresses for Intel POR External PHYs.....                    | 32  |

| Table 5: mSATA Pin Mapping Relative to miniPCIe.....                        | 34  |

| Table 6: PCIe Maximum Allowable Clock Jitter.....                           | 51  |

| Table 7: PCIe Clock Buffer Modes.....                                       | 52  |

| Table 8: PCIe Clock Buffer Vendors and Part Numbers.....                    | 53  |

| Table 9: PCIe Redrivers and Retimers.....                                   | 56  |

| Table 10: USB.org Branding Term Summary.....                                | 57  |

| Table 11: USB Type-A Pin-Out.....                                           | 58  |

| Table 12: USB 3 Redrivers.....                                              | 60  |

| Table 13: USB Type-C Connector Pin-out.....                                 | 62  |

| Table 14: USB Type-C Port Multiplexers – Possible Modes.....                | 65  |

| Table 15: Boot SPI Socket Suggestions.....                                  | 84  |

| Table 16: DisplayPort Redrivers and Retimers.....                           | 89  |

| Table 17: SoundWire Audio CODECs.....                                       | 97  |

| Table 18: Alternative / Additional Carrier Board UART Implementations.....  | 102 |

| Table 19: I2C Operating Modes.....                                          | 103 |

| Table 20: I2C Bus Buffers / Level Translators / Power Domain Isolation..... | 105 |

| Table 21: COM-HPC Type Definitions.....                                     | 116 |

| Table 22: Intel and AMD Design Guides.....                                  | 118 |

| Table 23: General Design Rules for High Speed Serial interfaces.....        | 121 |

| Table 24: NBASE-T Design Rule Summary.....                                  | 123 |

| Table 25: Ethernet KR Design Rule Summary.....                              | 124 |

| Table 26: SATA Design Rule Summary.....                                     | 125 |

| Table 27: PCIe Design Rule Summary.....                                     | 126 |

| Table 28: USB 2.0 Design Rule Summary.....                                  | 127 |

| Table 29: USB 3.2 and USB4 Design Rule Summaries.....                       | 128 |

| Table 30: DisplayPort Design Rule Summary.....                              | 130 |

| Table 31: HDMI Design Rule Summary.....                                     | 132 |

| Table 32: Design Rules for Single Ended Interfaces.....                     | 133 |

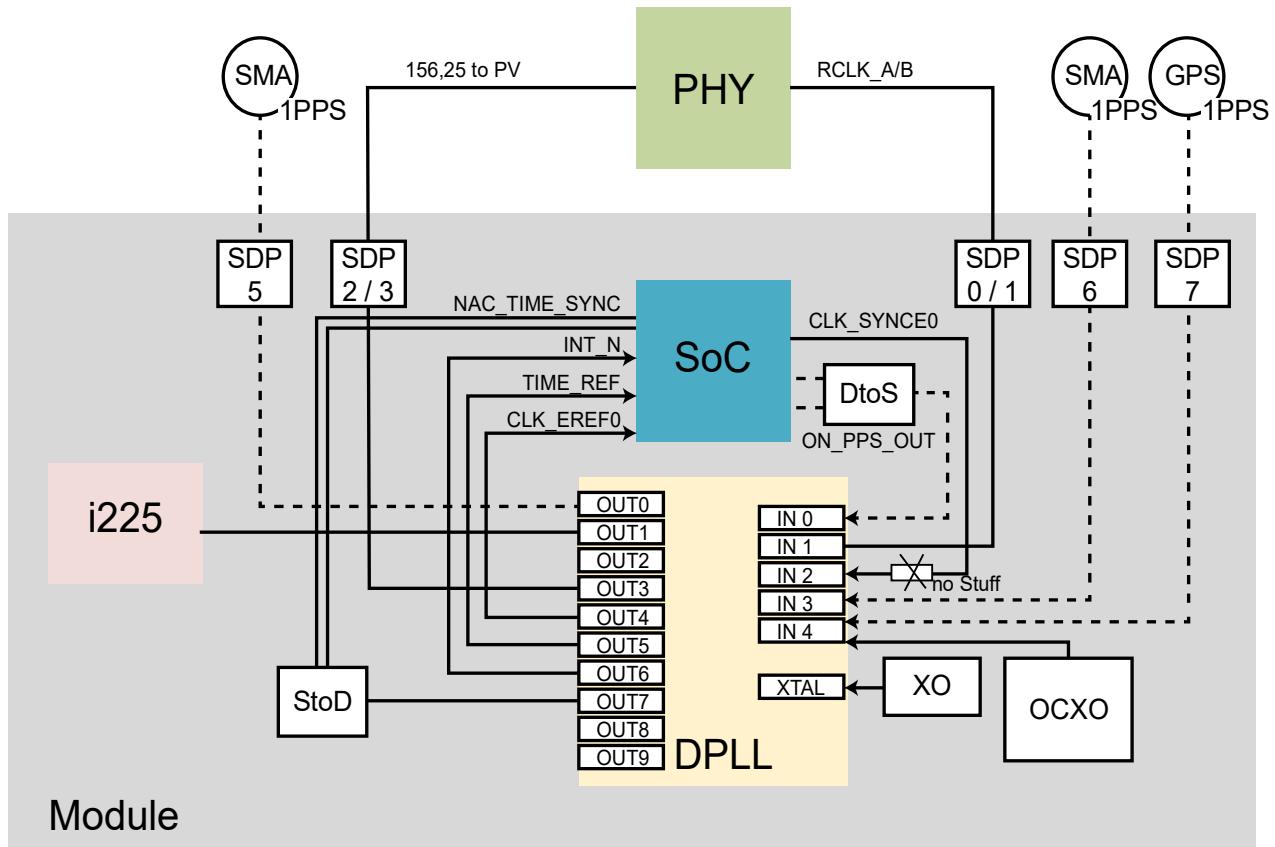

| Table 33: SDP Use in Figure Above.....                                      | 148 |

| Table 34: SyncE / PTP Matrix.....                                           | 149 |

| Table 35: General Books on x86 Computer Topics.....                         | 158 |

| Table 36: Revision History.....                                             | 159 |

---

## Table of Figures

|                                                                                                        |    |

|--------------------------------------------------------------------------------------------------------|----|

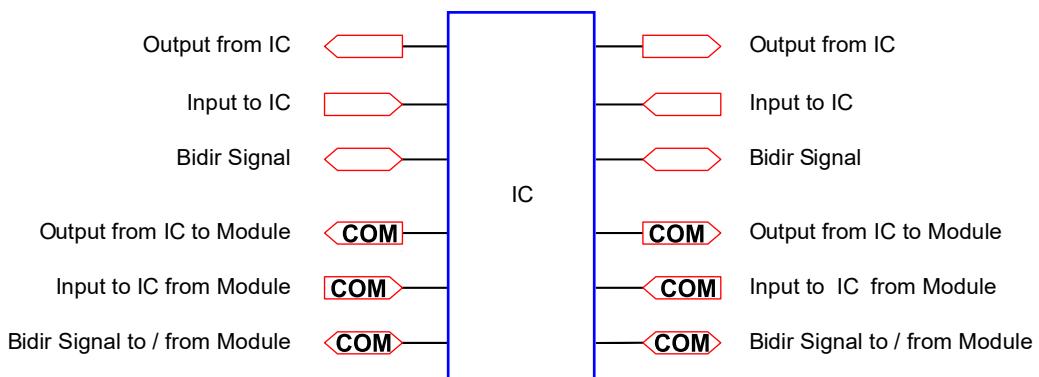

| Figure 1: Schematic Conventions.....                                                                   | 22 |

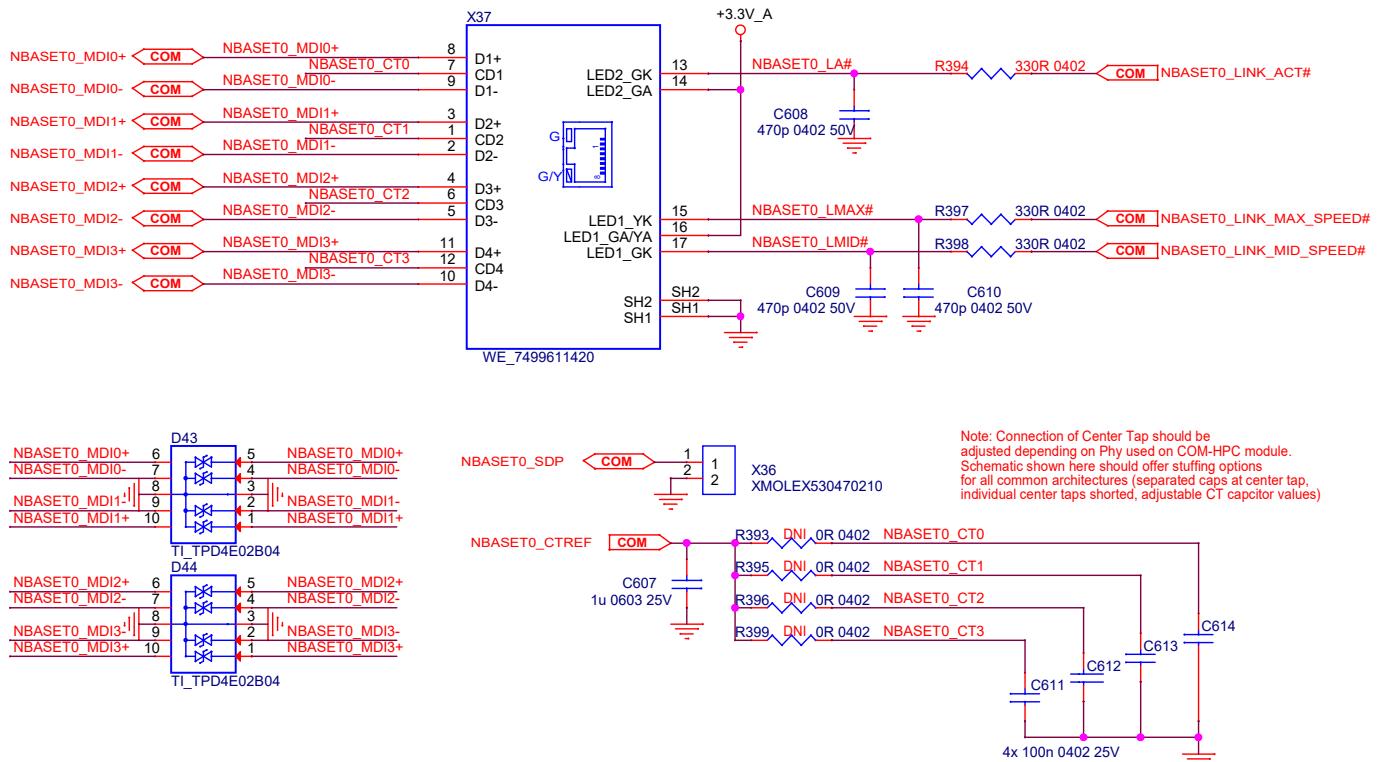

| Figure 2: NBASE-T.....                                                                                 | 23 |

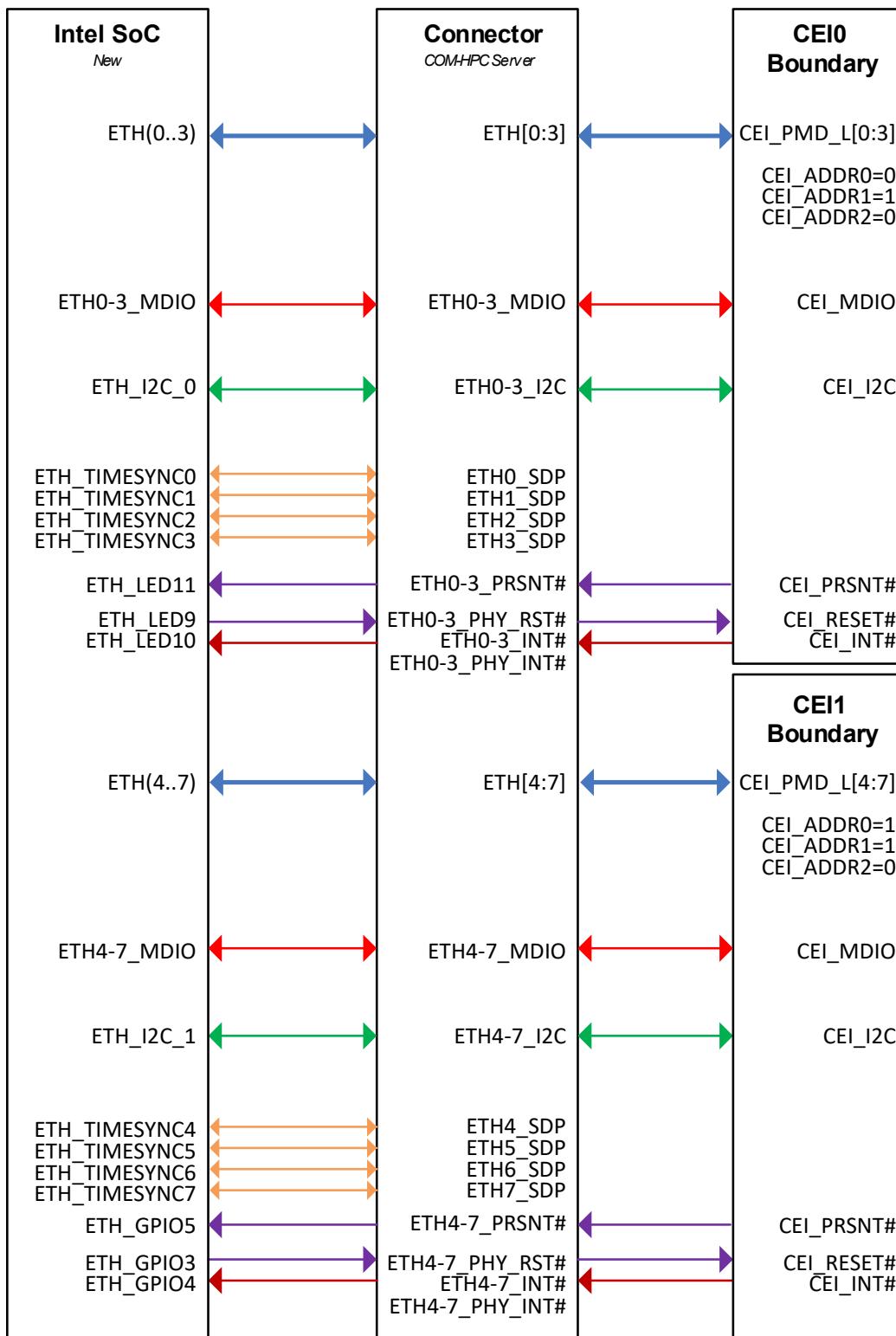

| Figure 3: Intel SoC with CEI Boundary.....                                                             | 25 |

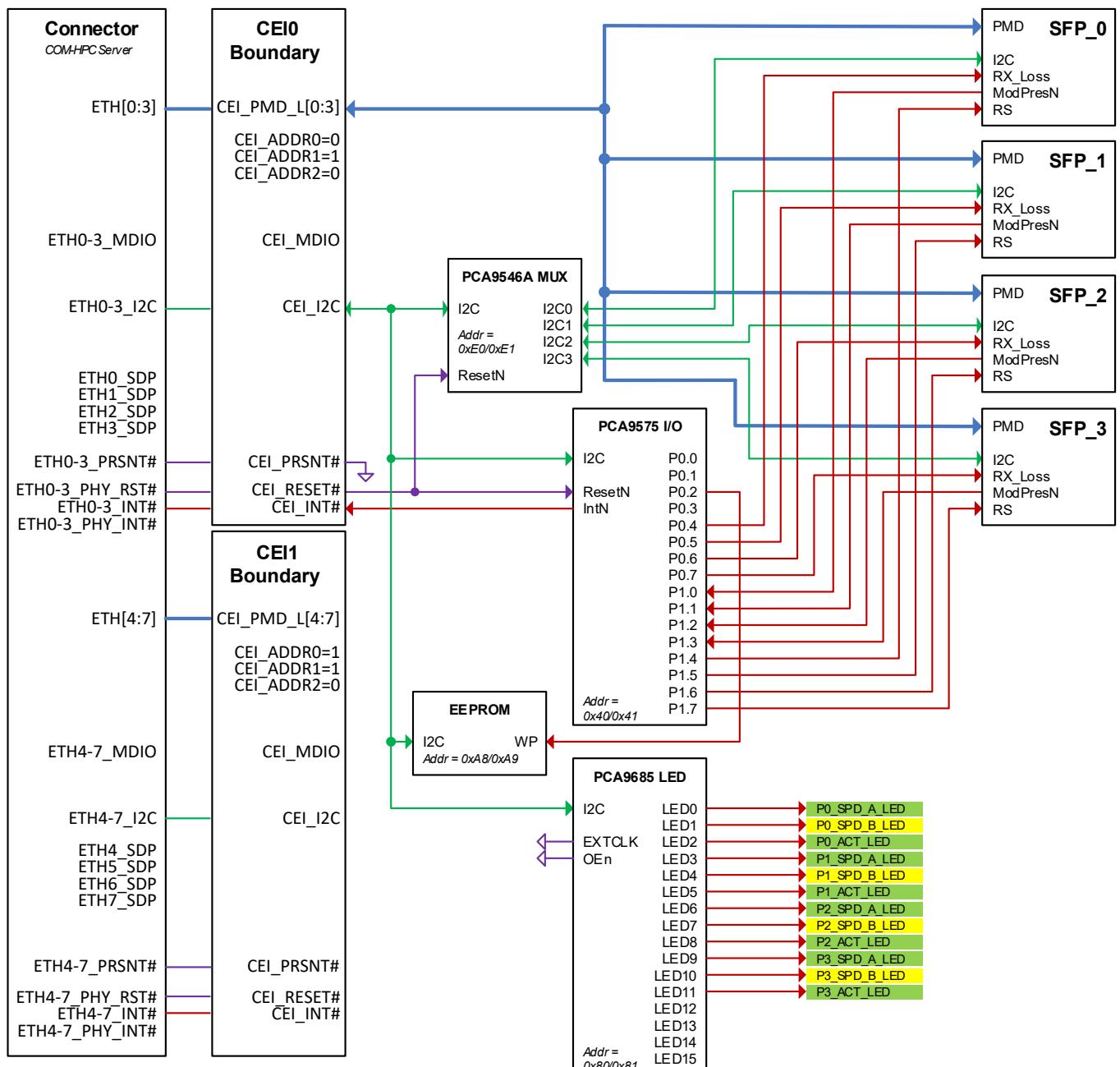

| Figure 4: Intel CEI 4x SFP28.....                                                                      | 26 |

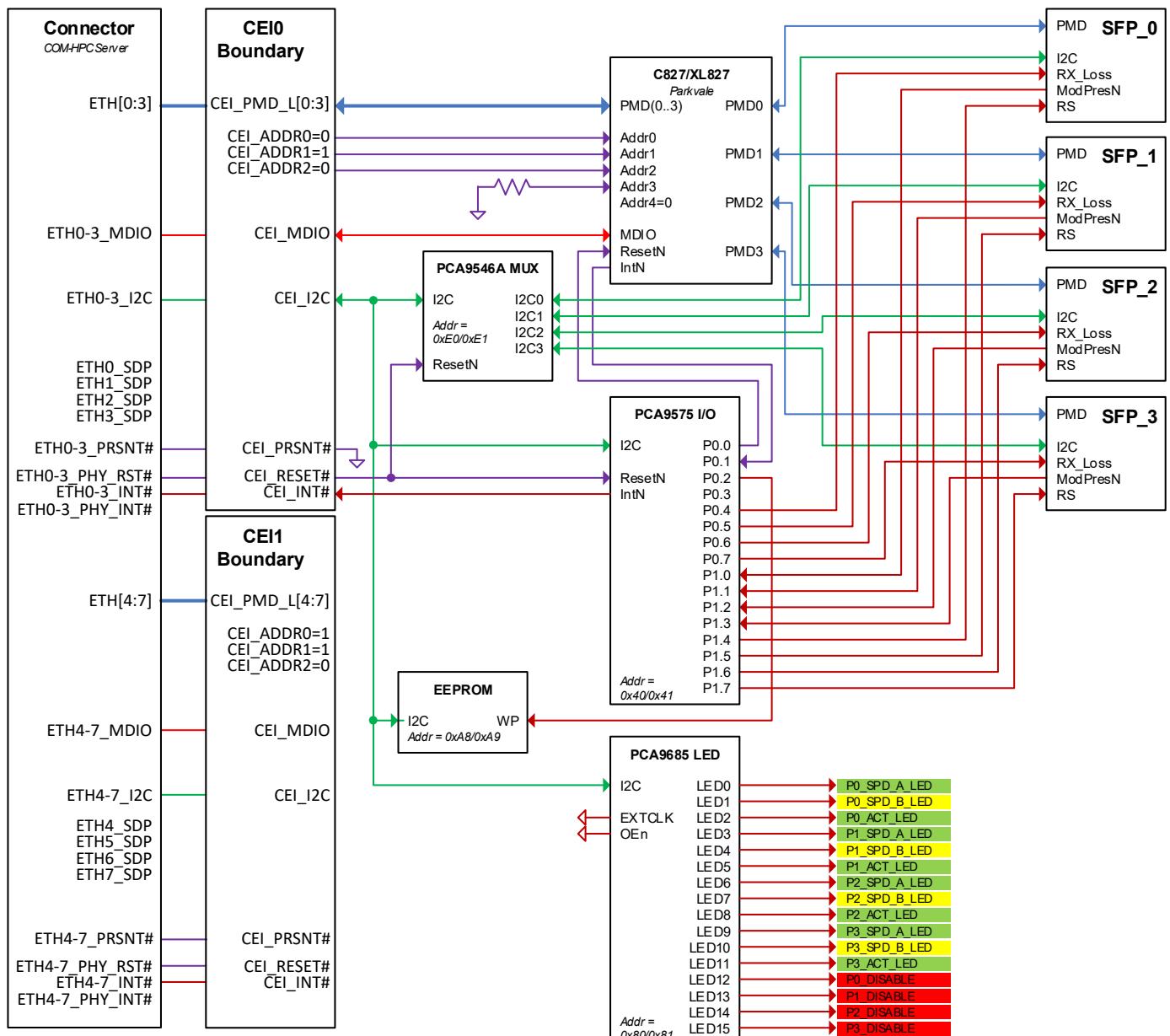

| Figure 5: Intel CEI 4x SFP28 with Retimer C827/XL827.....                                              | 27 |

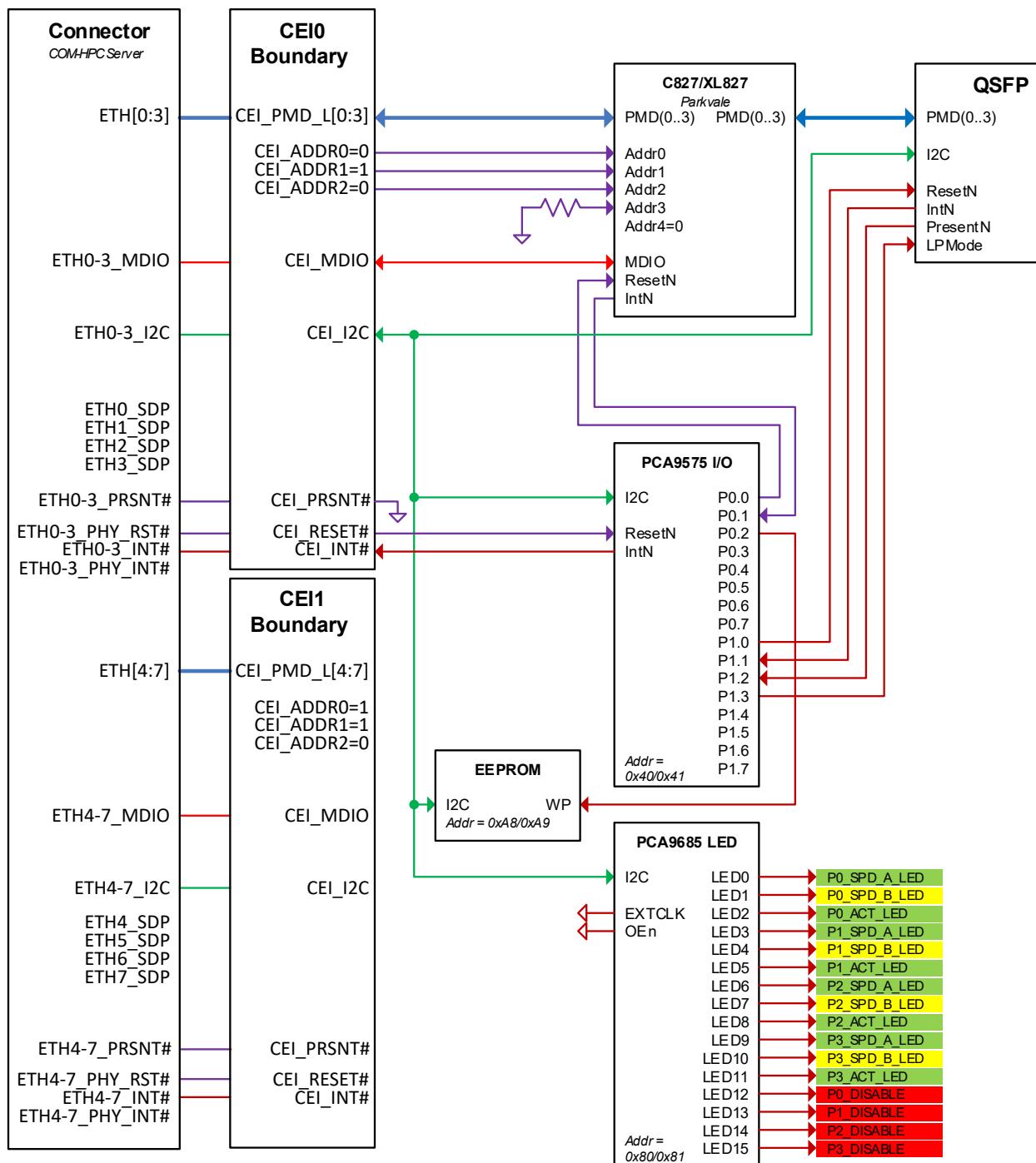

| Figure 6: Intel CEI QSFP28 with Retimer C827/XL827.....                                                | 28 |

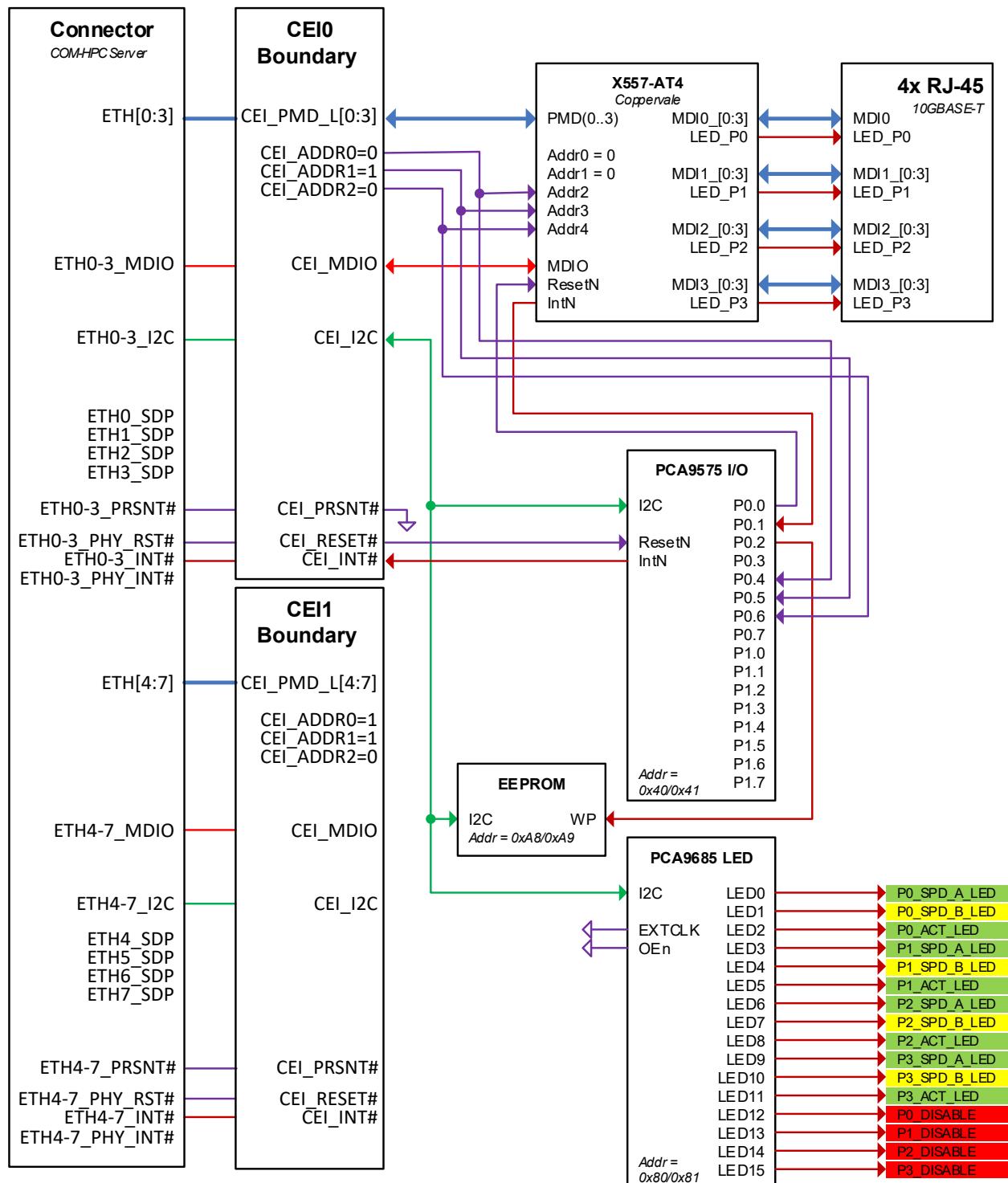

| Figure 7: Intel CEI 4x 10GBASE-T Copper PHY X557-AT4.....                                              | 29 |

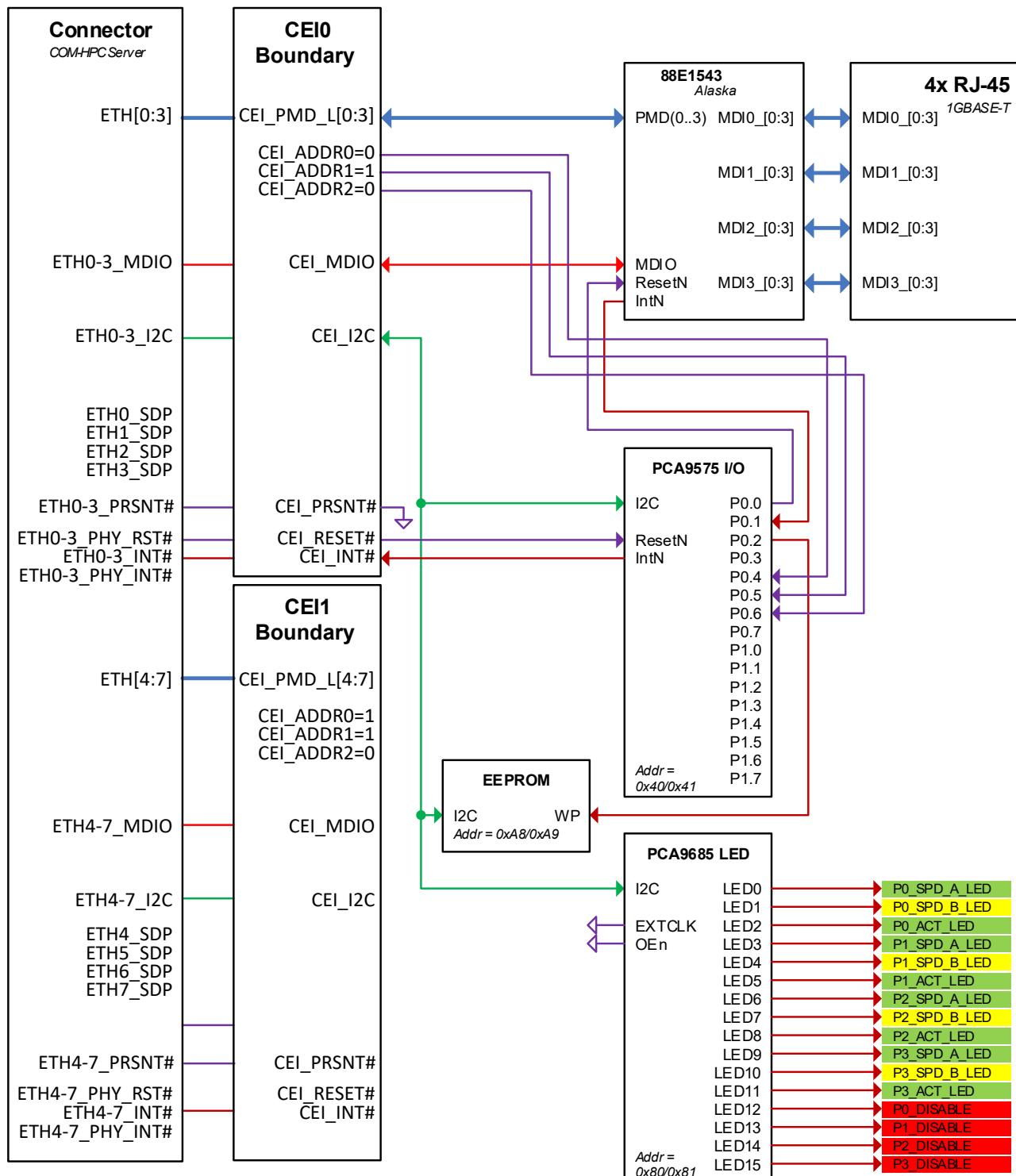

| Figure 8: Intel CEI 4x 1GBASE-T Copper PHY Marvell 88E1543.....                                        | 30 |

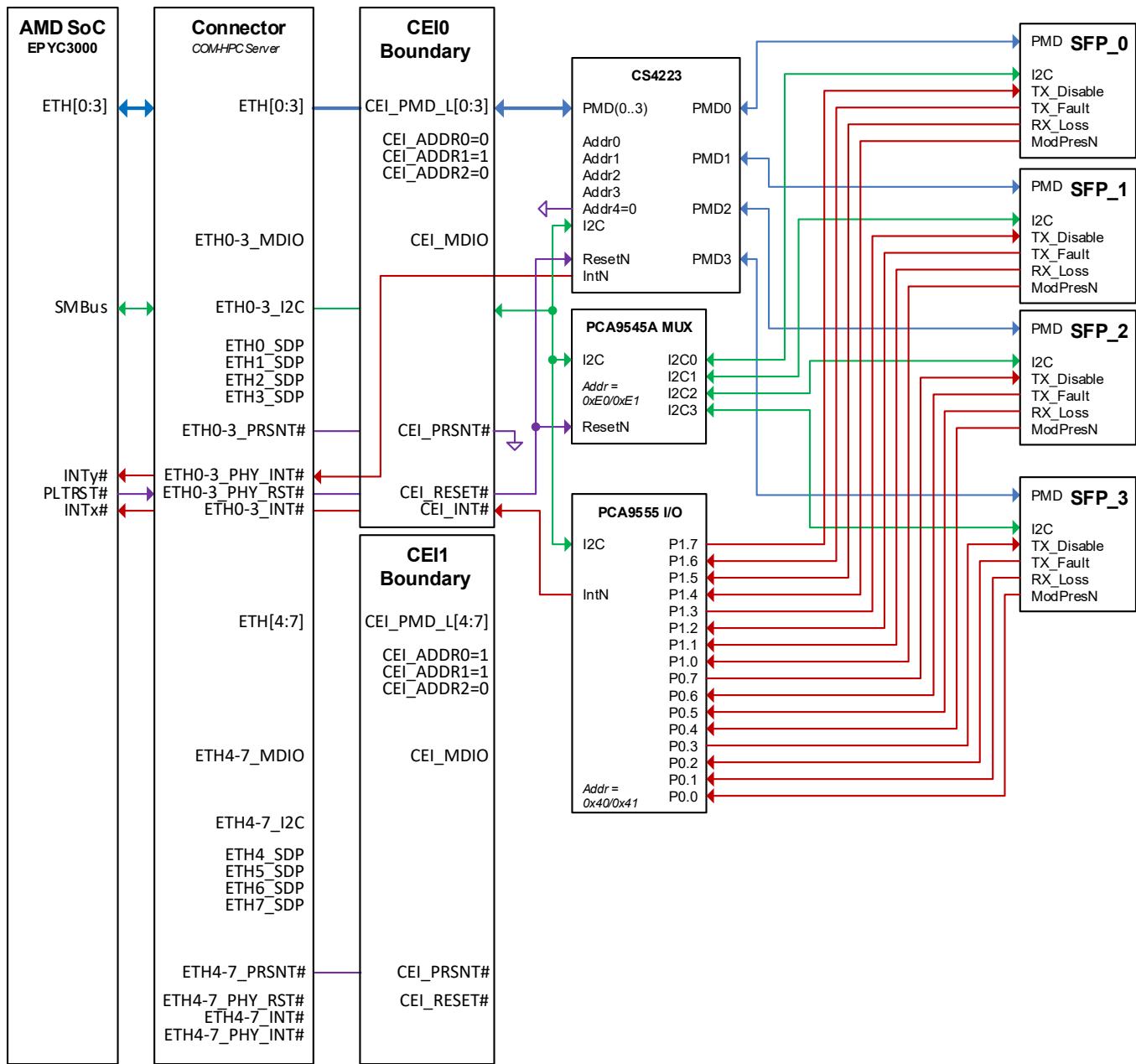

| Figure 9: AMD SoC 4xSFP+ with CS4223 Retimer.....                                                      | 31 |

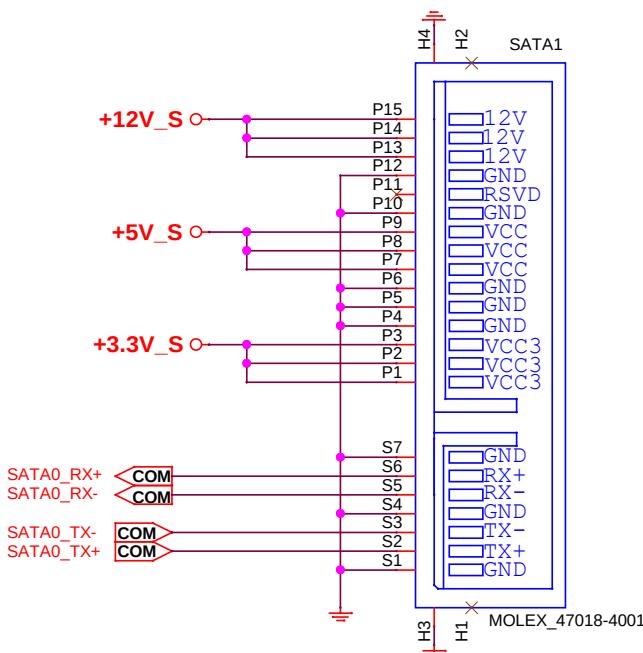

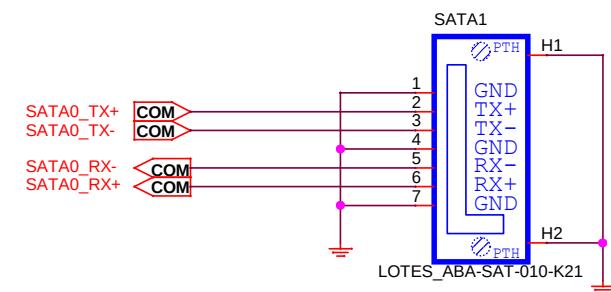

| Figure 10: Serial ATA - Cabled.....                                                                    | 33 |

| Figure 11: PCIe Data Line Coupling Capacitor Positions (MXM-3 Cards Excluded).....                     | 36 |

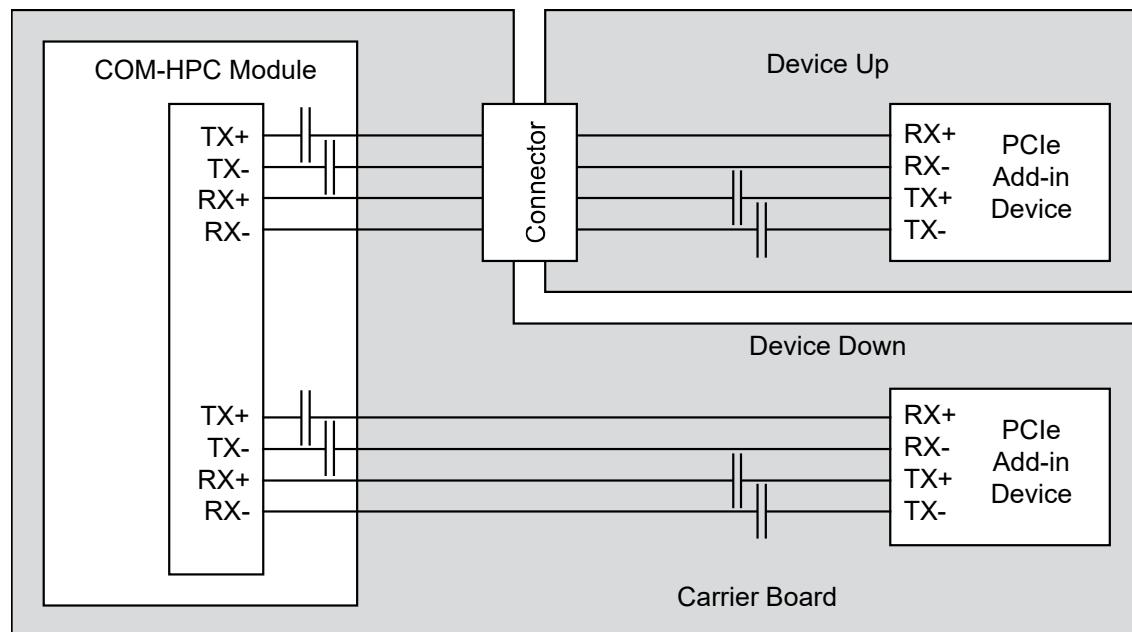

| Figure 12: PCIe Device Down on Carrier – PCIe Group 0 Low – PCIe Lane 0.....                           | 37 |

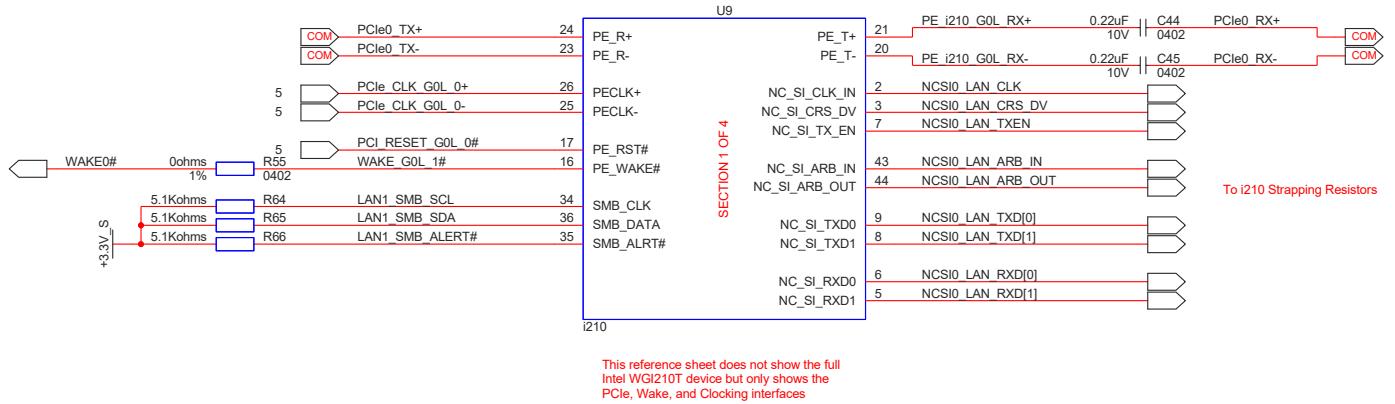

| Figure 13: Mini PCIe Site – PCIe Group 0 Low – PCIe Lane 1.....                                        | 38 |

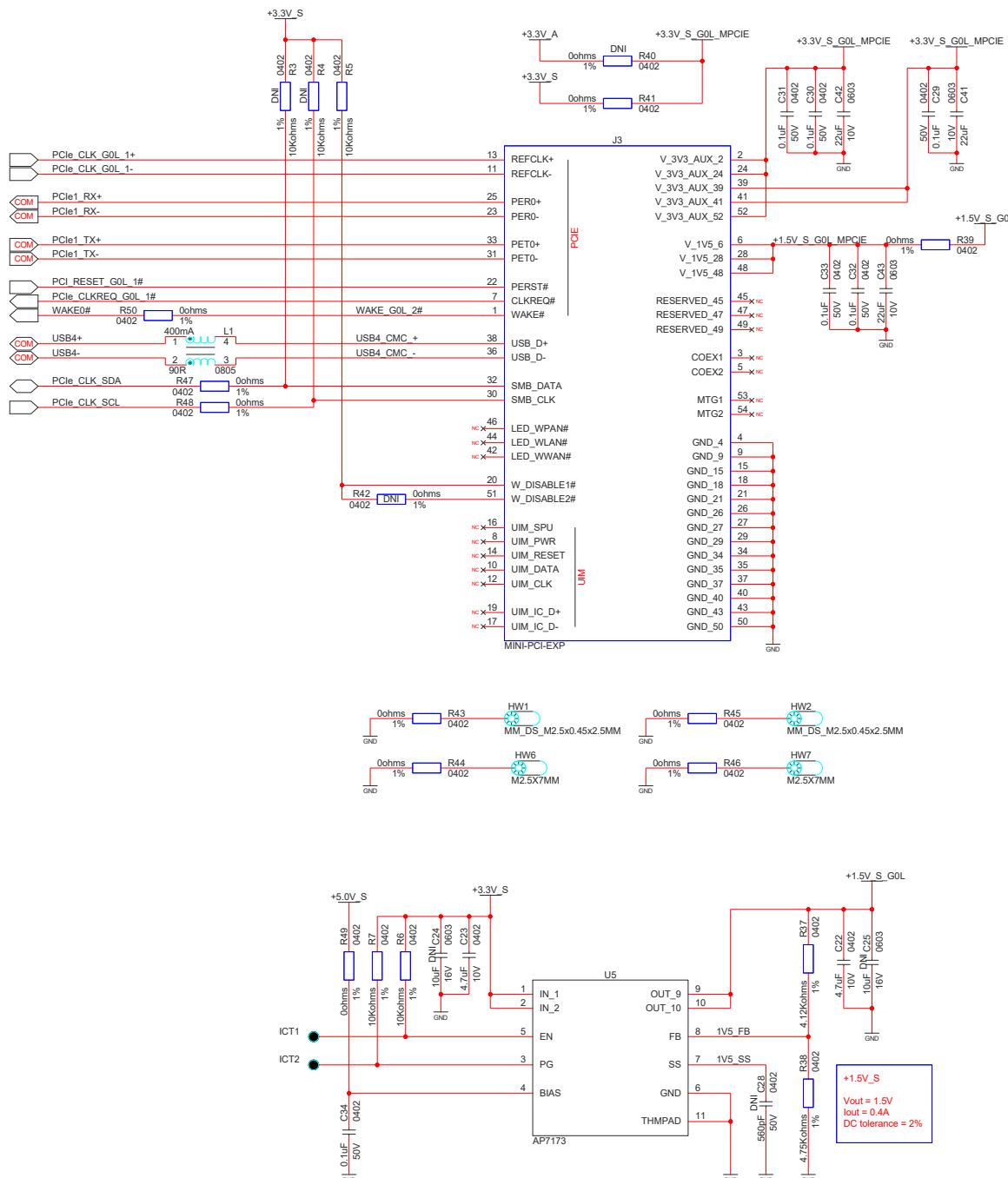

| Figure 14: M.2 E-Key Site – WiFi Cards – PCIe Group 0 Low – PCIe Lane 2.....                           | 39 |

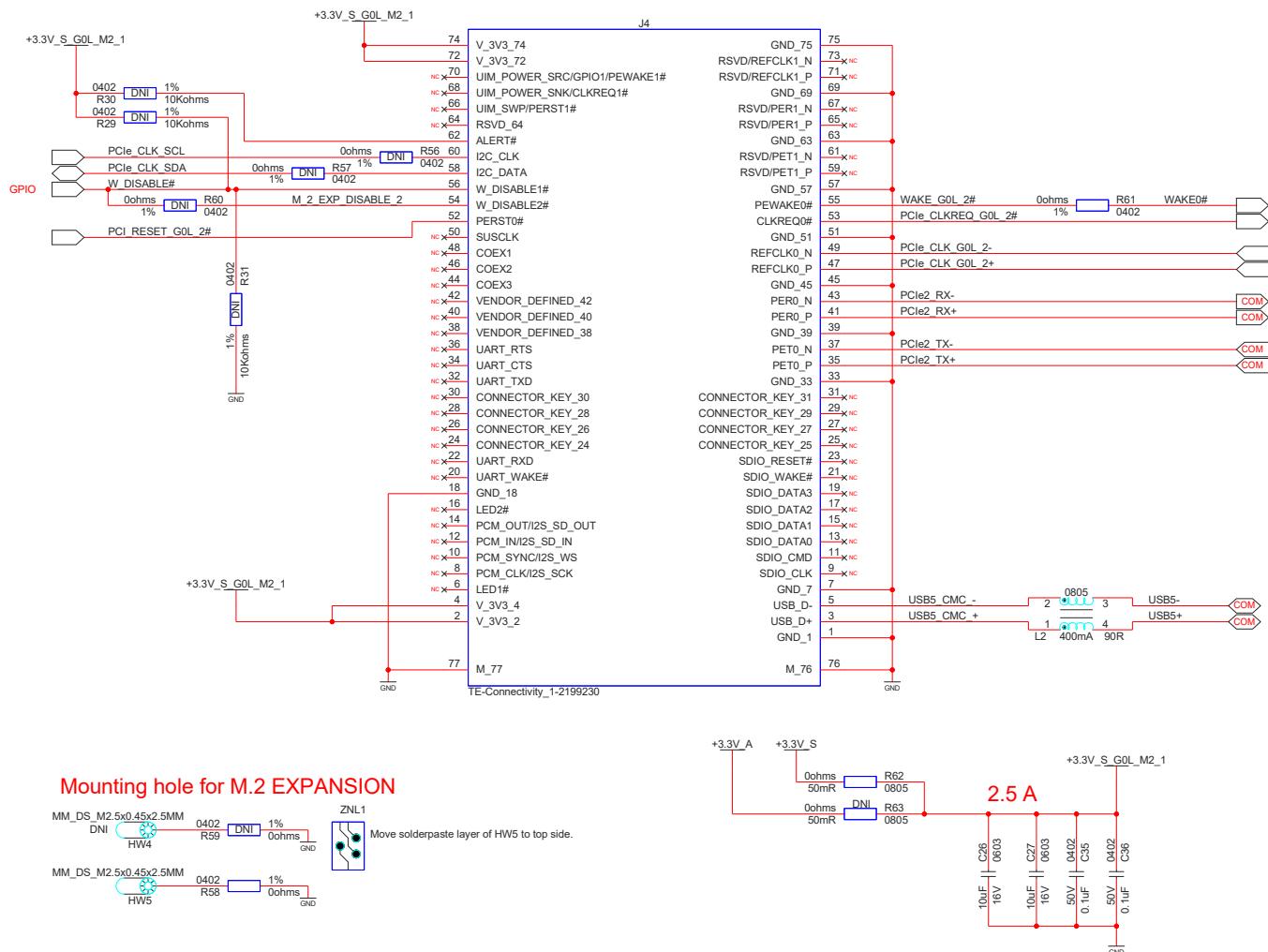

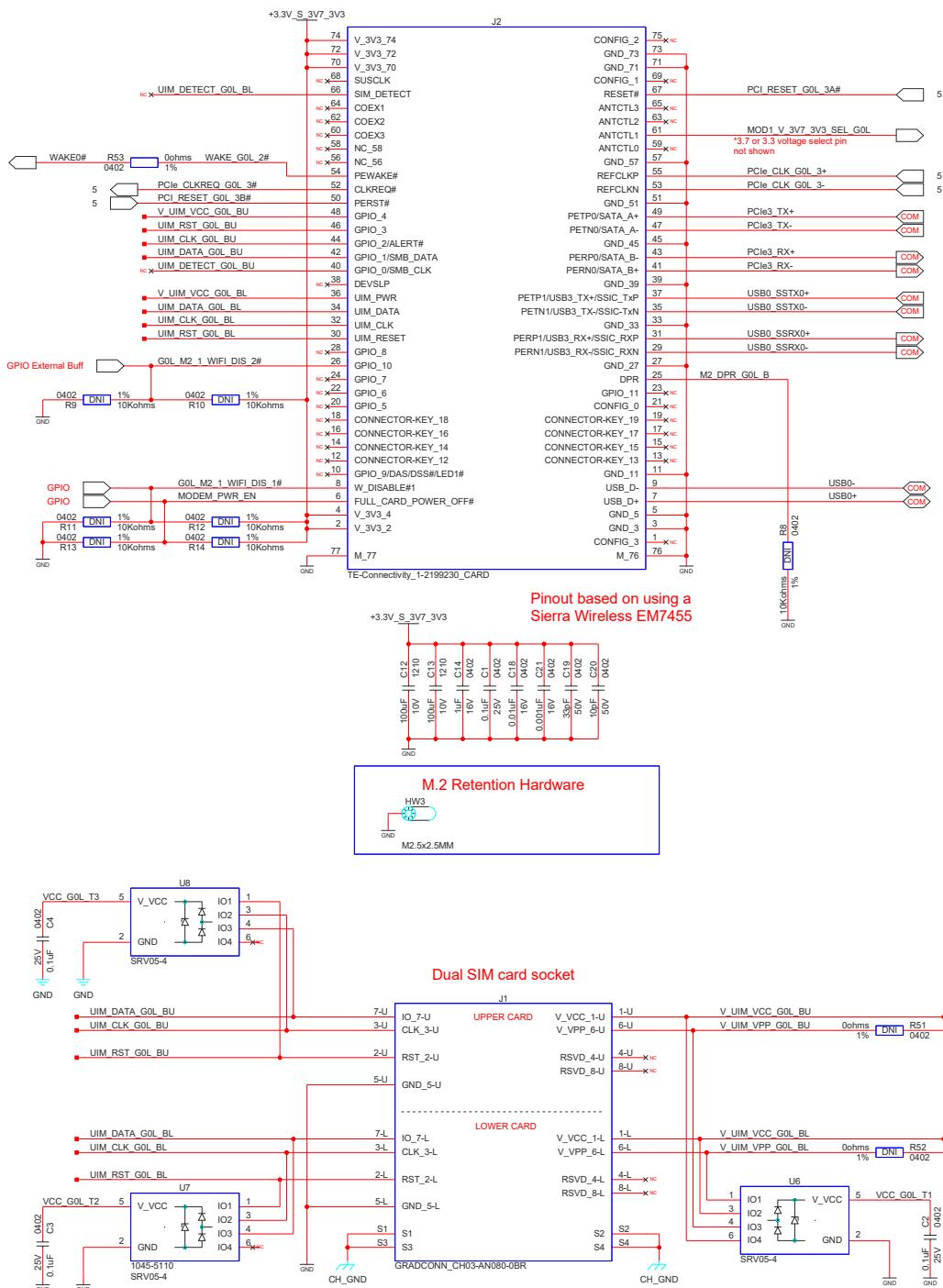

| Figure 15: M.2 B-Key Site – Cell Modem Cards – PCIe Group 0 Low – PCIe Lane 3.....                     | 40 |

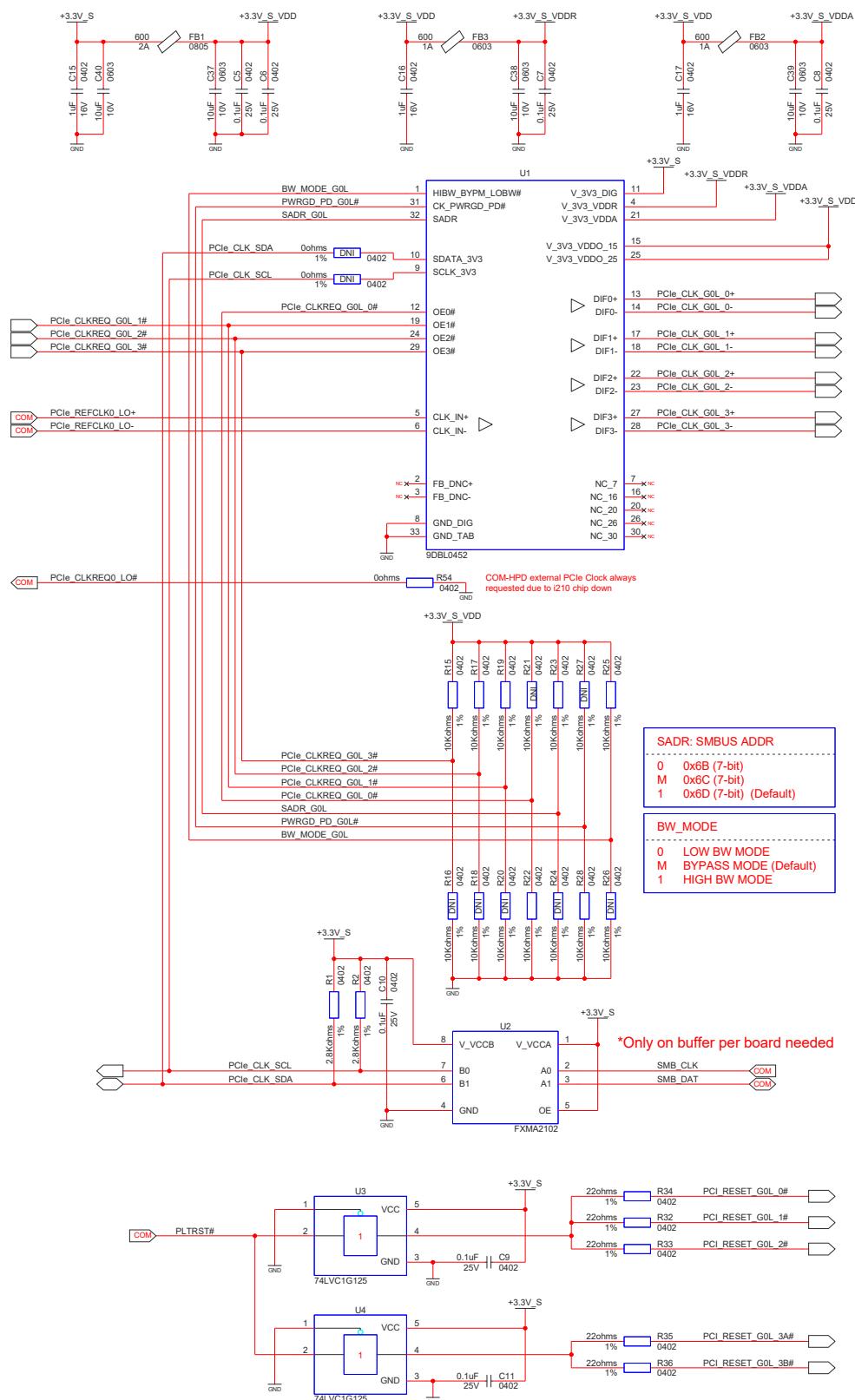

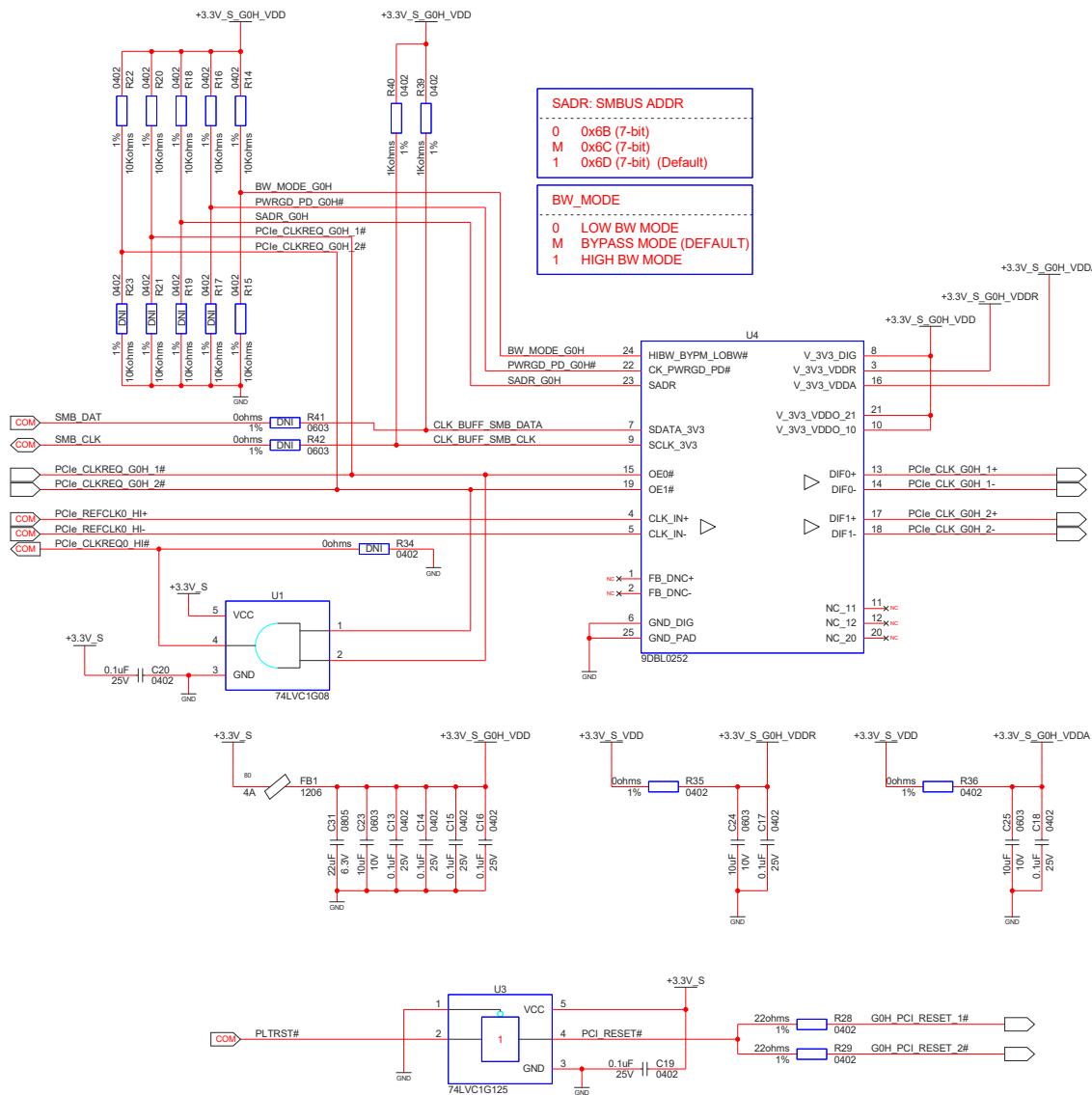

| Figure 16: Clock and Reset Buffers for PCIe Group 0 Low Example Circuits.....                          | 41 |

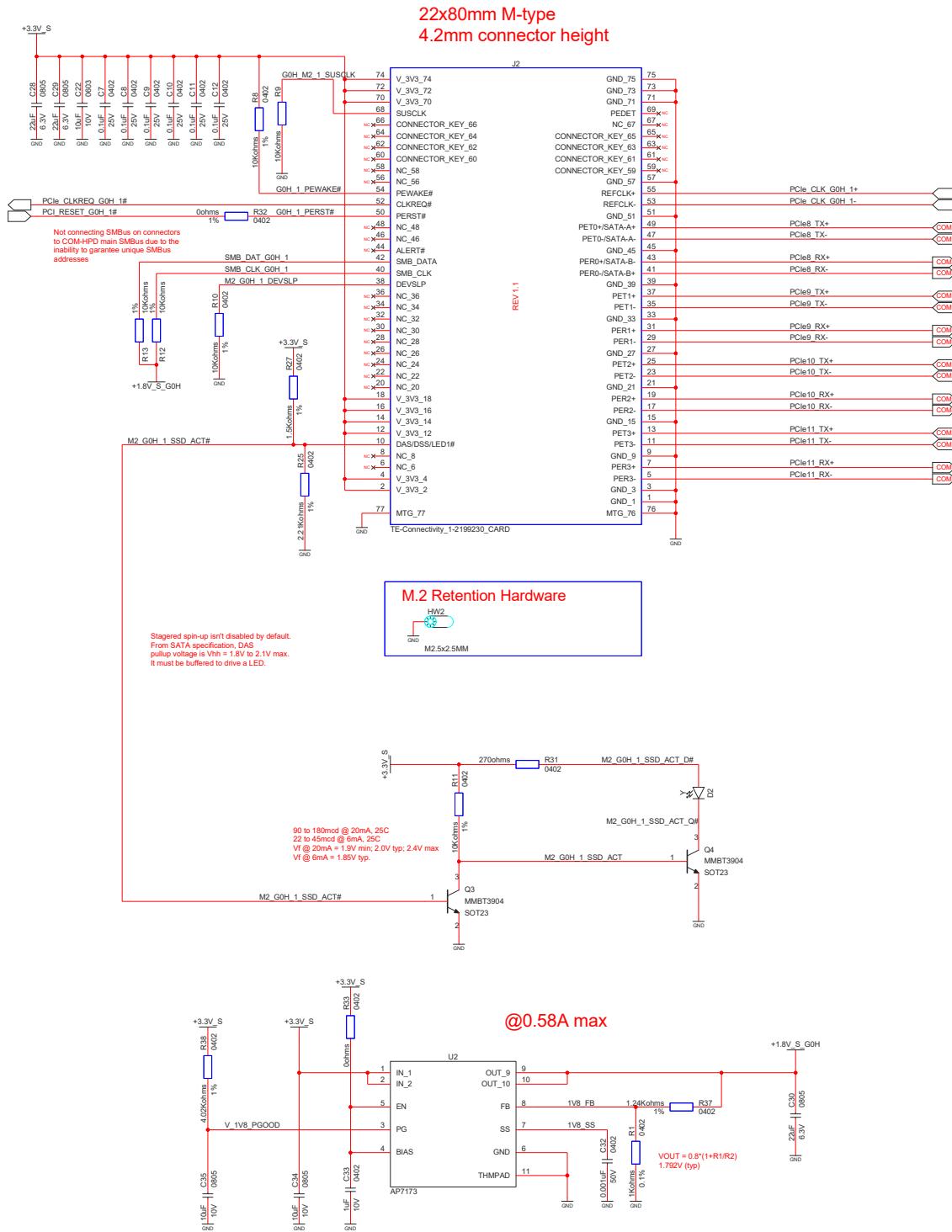

| Figure 17: M.2 M-Key Site for NVME SSD Card #1 in Group 0 High PCIe Lanes 8:11.....                    | 42 |

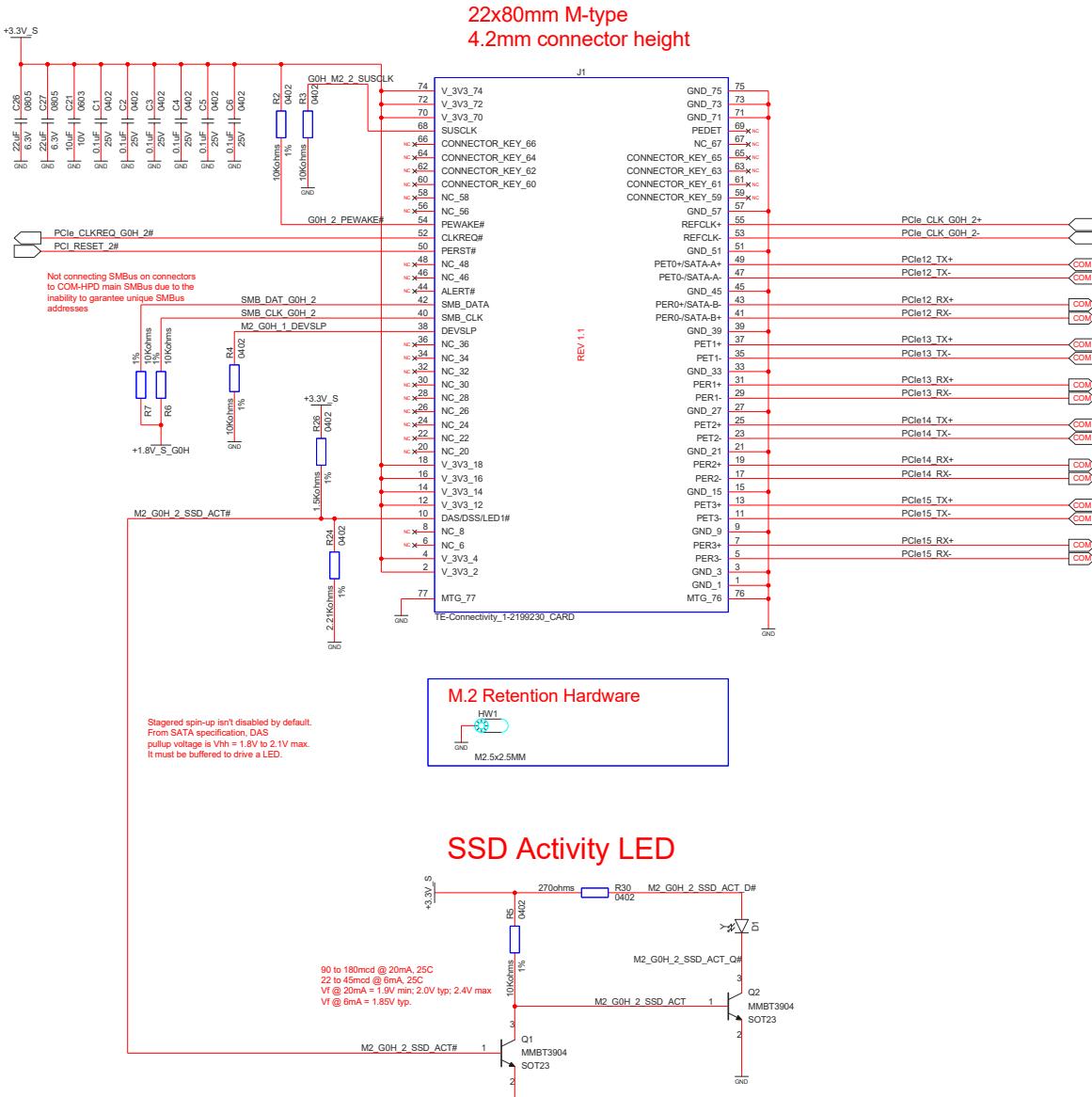

| Figure 18: M.2 M -Key Site for NVME SSD #2 in Group 0 PCIe Lanes 12:15.....                            | 43 |

| Figure 19: Clock Buffer and Reset for PCIe Dual M.2 NVME SSD PCIe Group 0 High.....                    | 44 |

| Figure 20: PCIe x16 Slot Card Site on PCIe Group 1 PCIe Lanes 16:31.....                               | 45 |

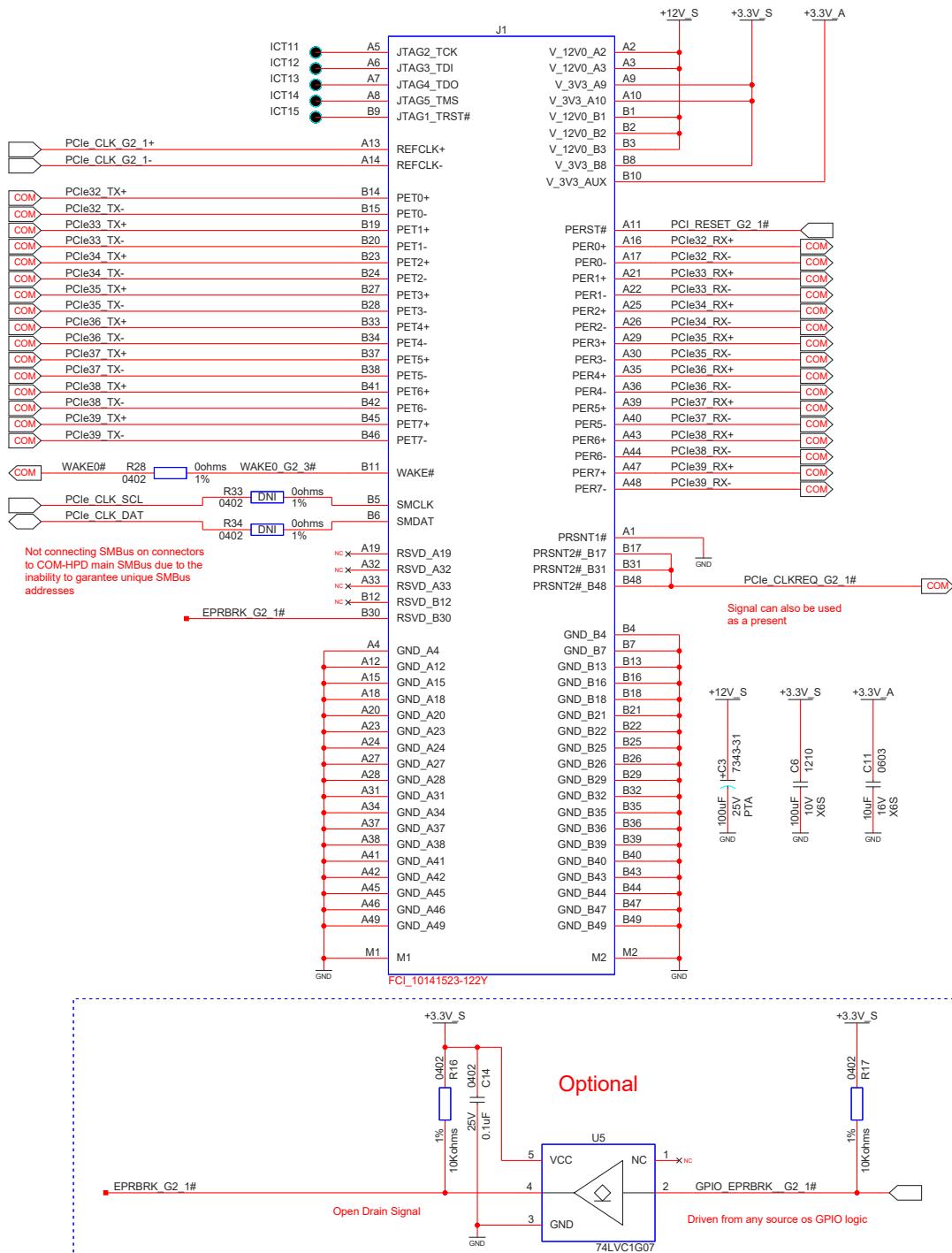

| Figure 21: PCIe x8 Slot Card Site on PCIe Group 2 PCIe Lanes 32:39.....                                | 46 |

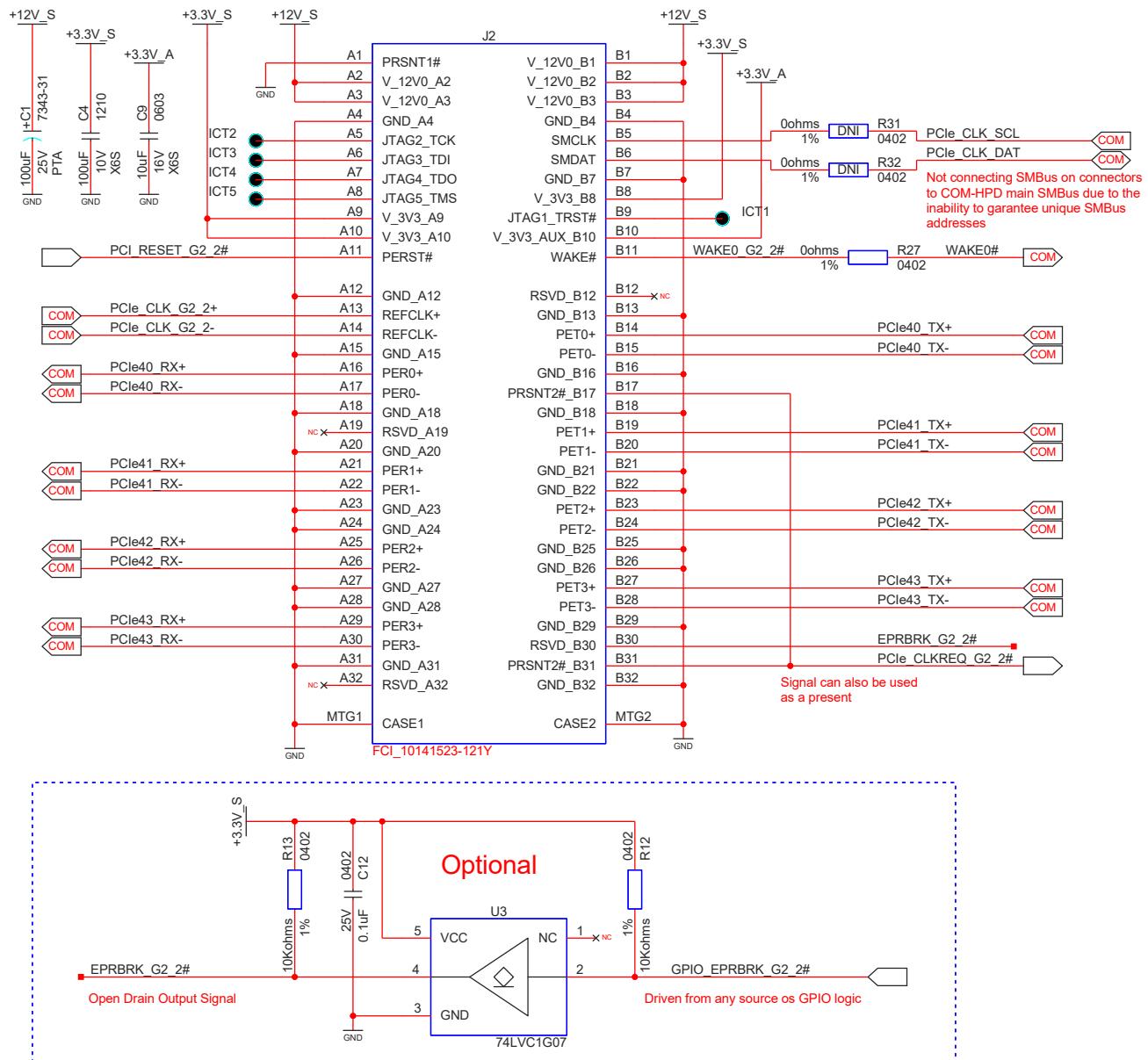

| Figure 22: PCIe x4 Slot Card Site on PCIe Group 2 PCIe Lanes 40:43.....                                | 47 |

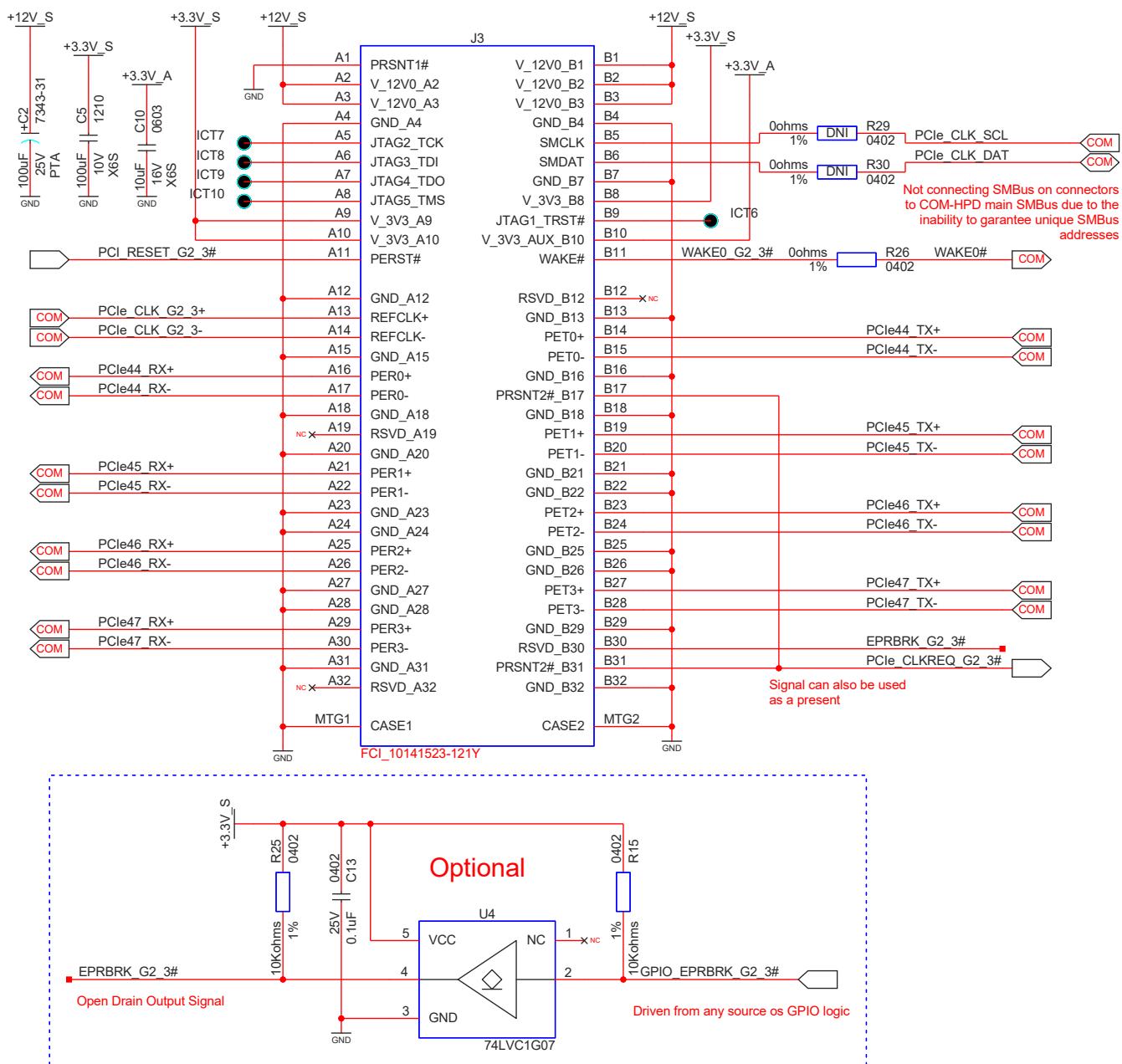

| Figure 23: PCIe x4 Slot Card Site on PCIe Group 2 PCIe Lanes 44:47.....                                | 48 |

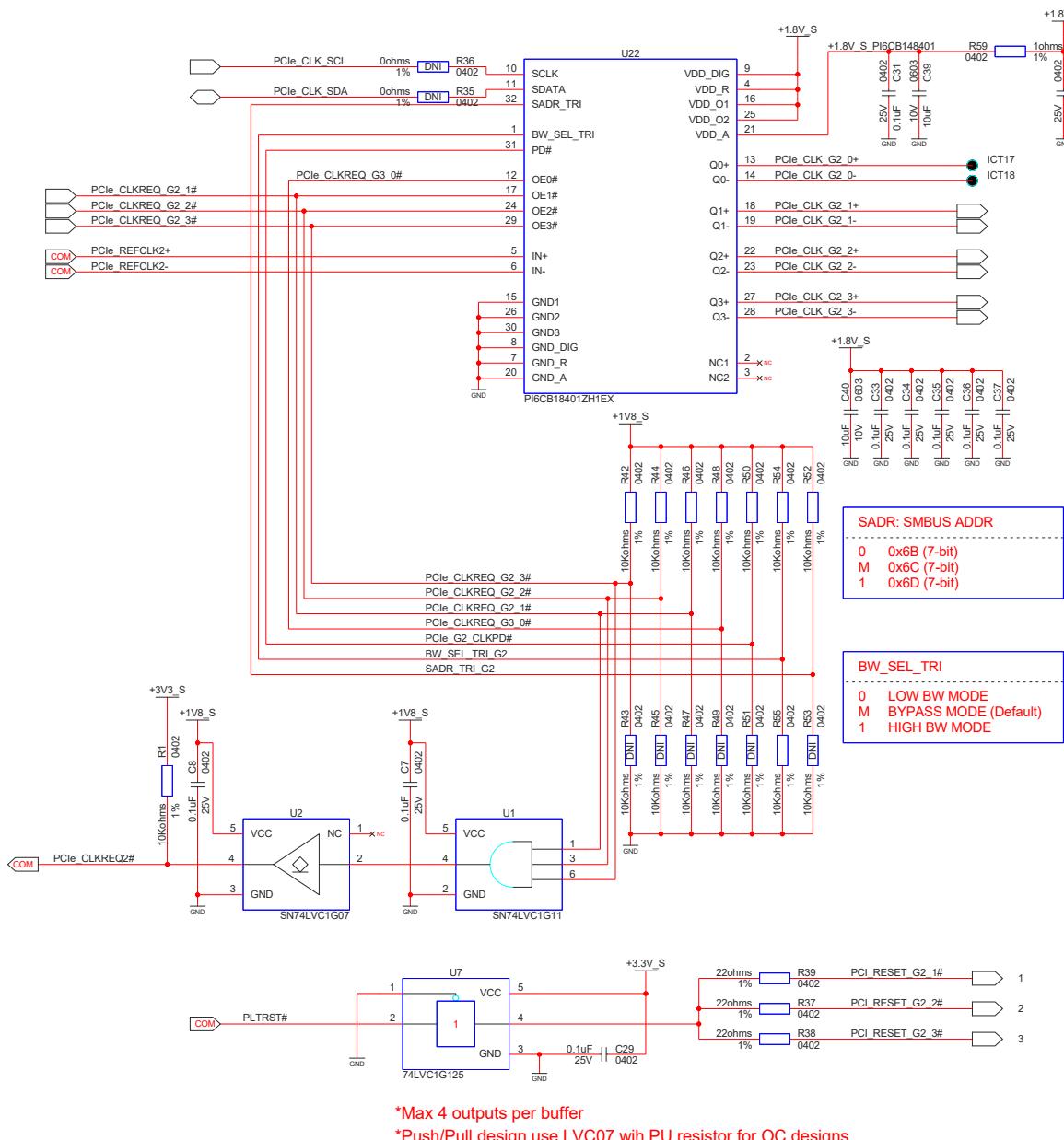

| Figure 24: PCIe Clock Buffer and Reset Buffer for PCIe Group 2 Example.....                            | 49 |

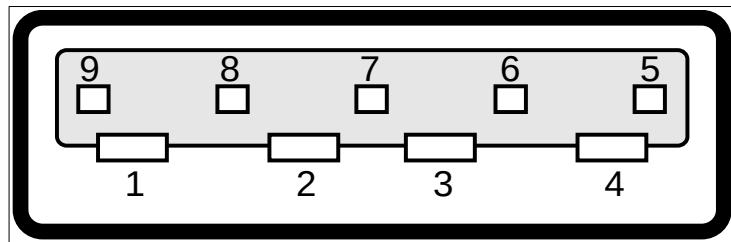

| Figure 26: USB 2.0 Type-A Example.....                                                                 | 59 |

| Figure 27: USB Type-C Receptacle and Plug Images.....                                                  | 62 |

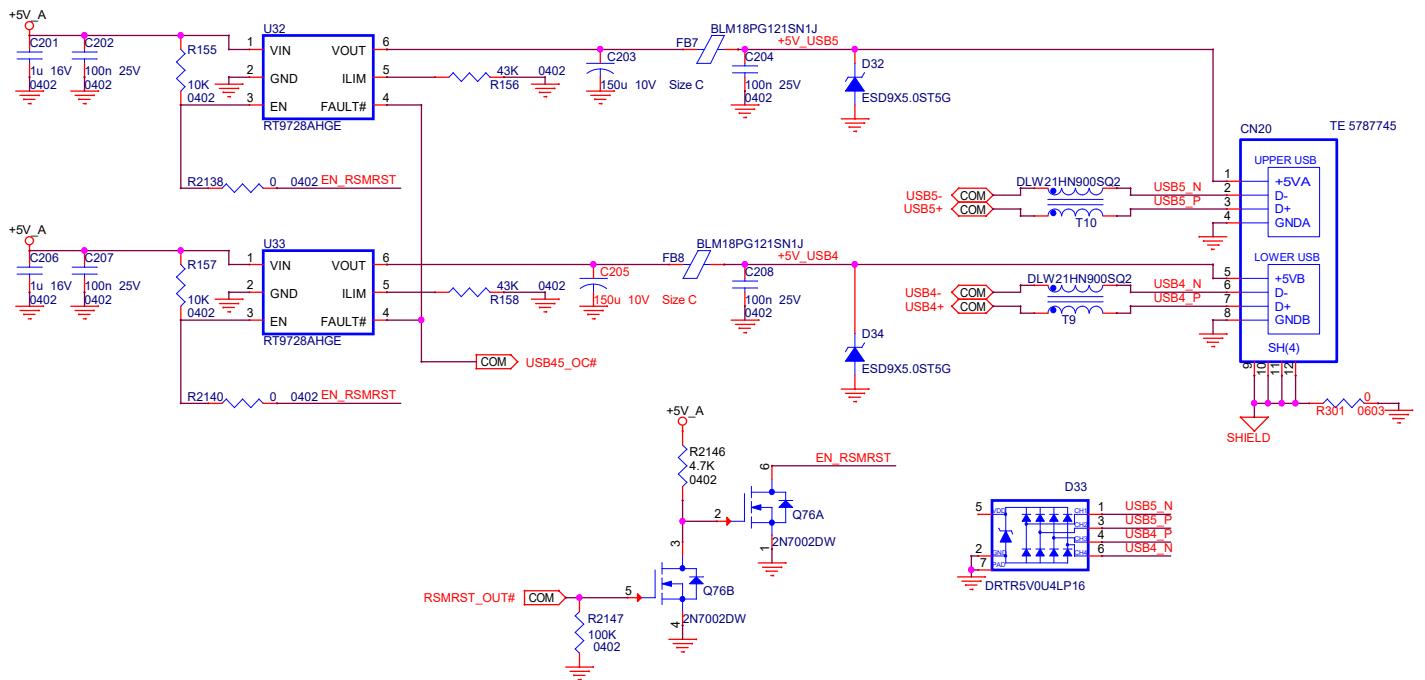

| Figure 28: USB Type-C Receptacle Pin-Out – Looking Into Carrier Receptacle.....                        | 62 |

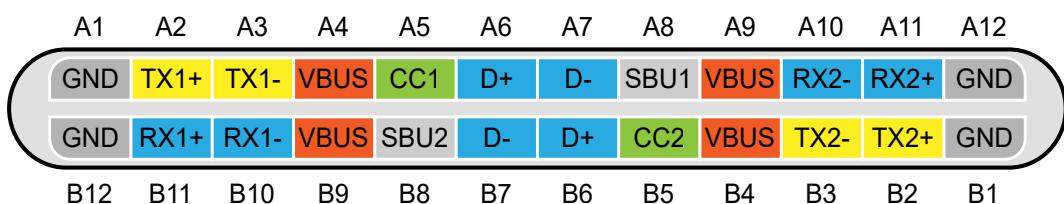

| Figure 29: USB Type-C Basic Implementation: USB 3.2 Gen 1 and Gen 2.....                               | 69 |

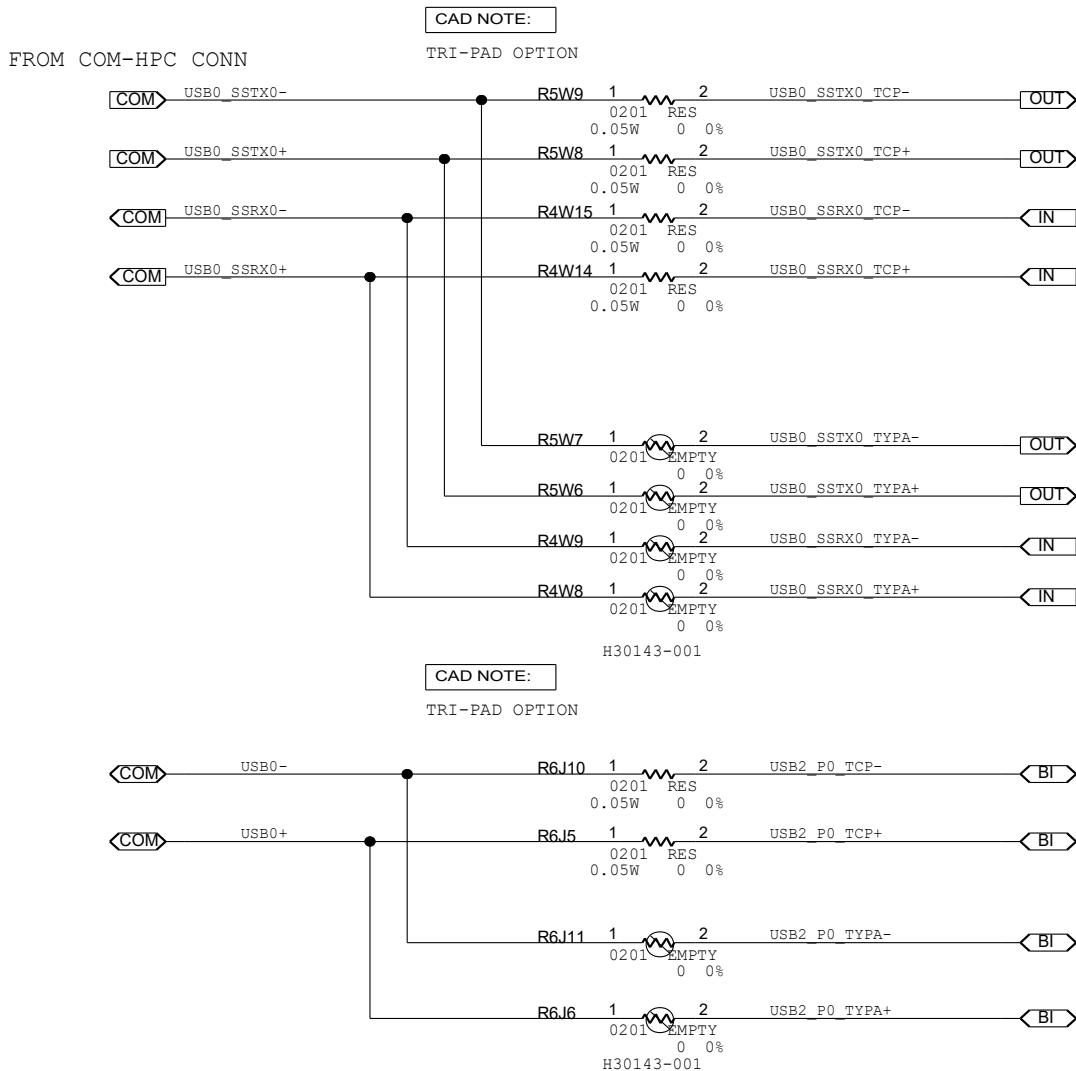

| Figure 30: USB 3.2 Gen 2x2 Type-C (1 of 6): Option Resistors for Type-C or Type-A.....                 | 70 |

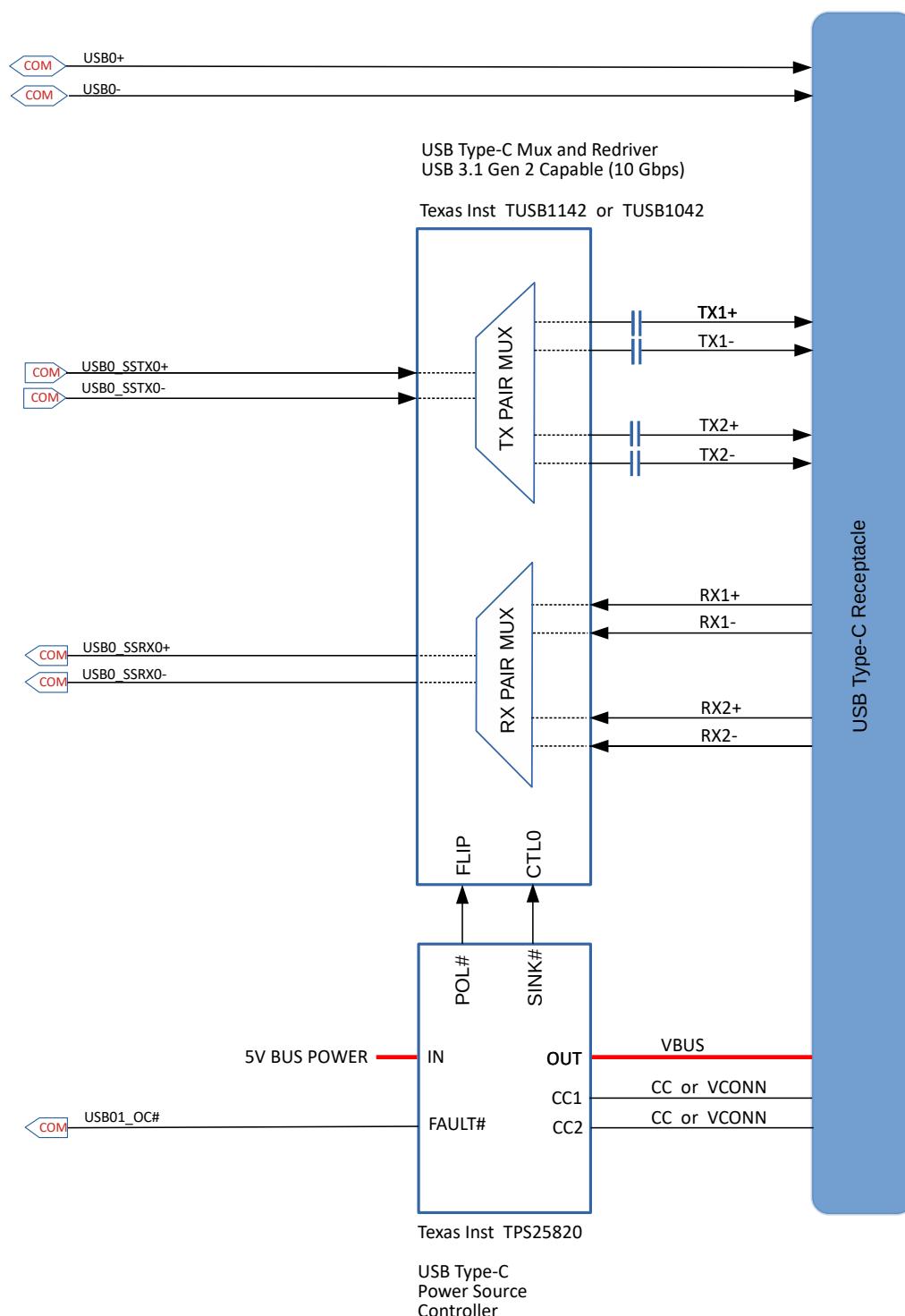

| Figure 31: USB 3.2 Gen 2x2 Type-C (2 of 6): Port Multiplexer and Redriver.....                         | 71 |

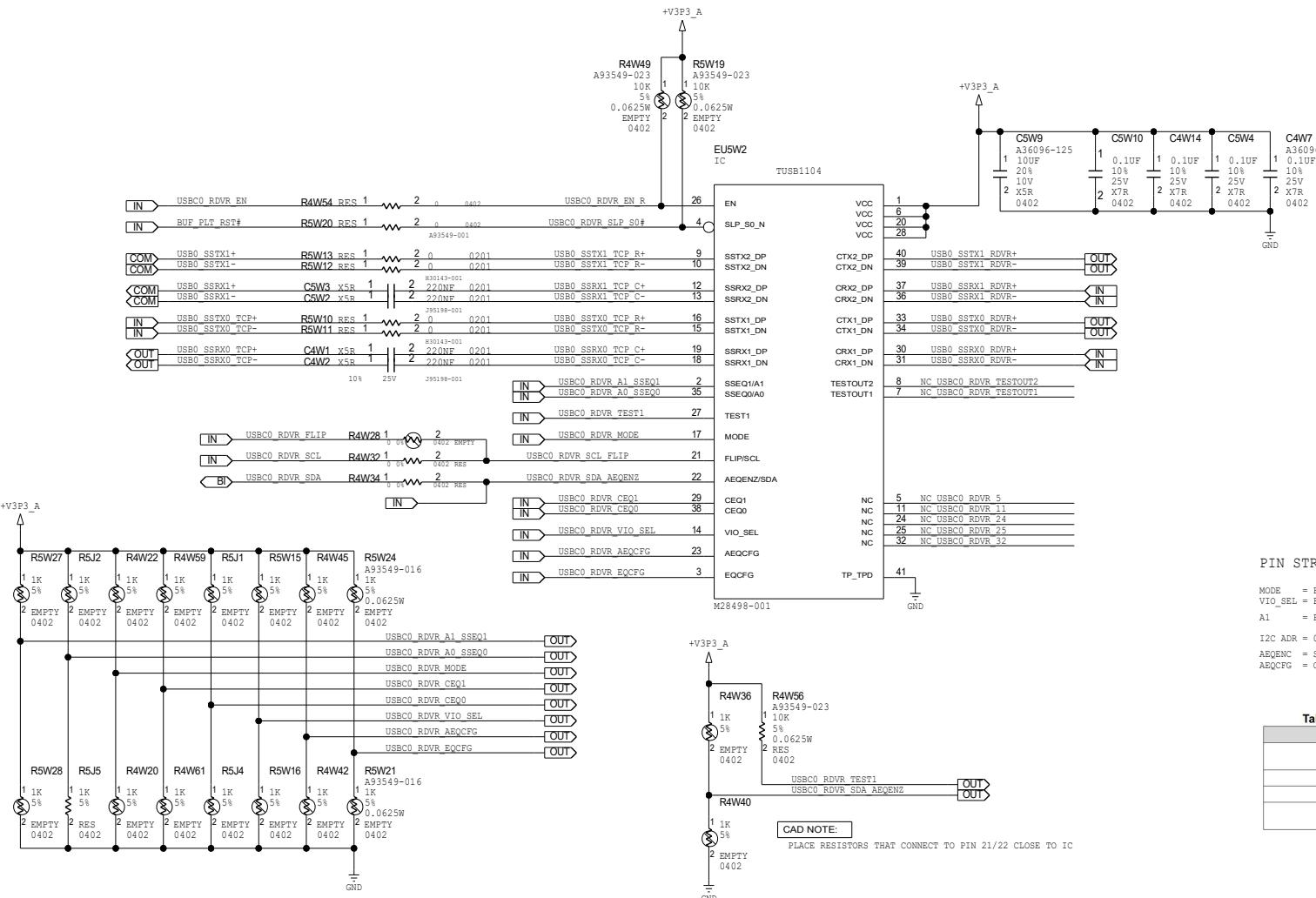

| Figure 32: USB 3.2 Gen 2x2 Type-C (3 of 6): EMI Mitigation and ESD Protection.....                     | 72 |

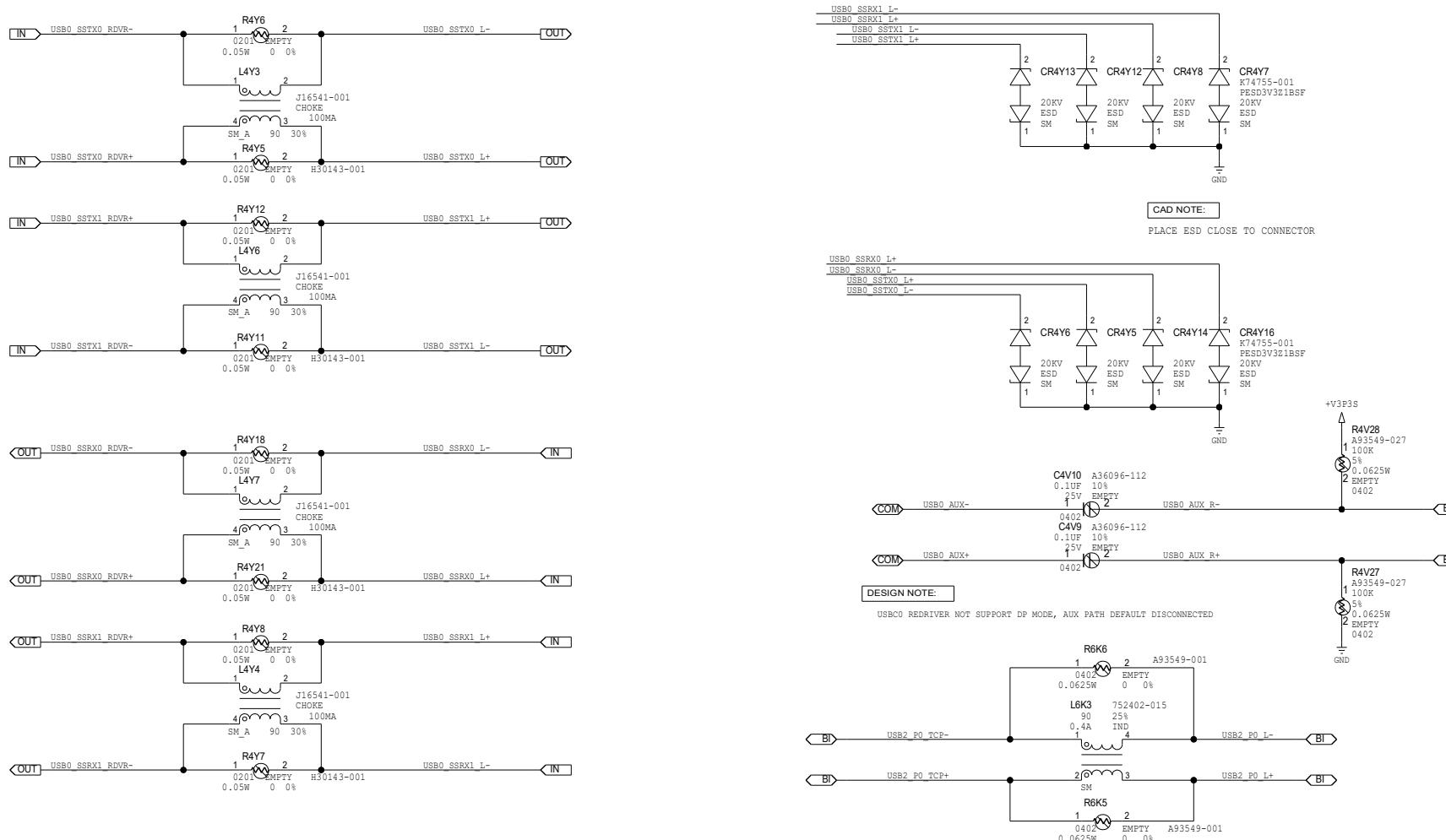

| Figure 33: USB 3.2 Gen 2x2 Type-C (4 of 6): Port Port Mux / Redriver Coupling Capacitors.....          | 73 |

| Figure 34: USB 3.2 Gen 2x2 Type-C (5 of 6): Type-C Power Delivery Controller.....                      | 74 |

| Figure 35: USB 3.2 Gen 2x2 Type-C (6 of 6): Type-C Connector and Port Protection.....                  | 75 |

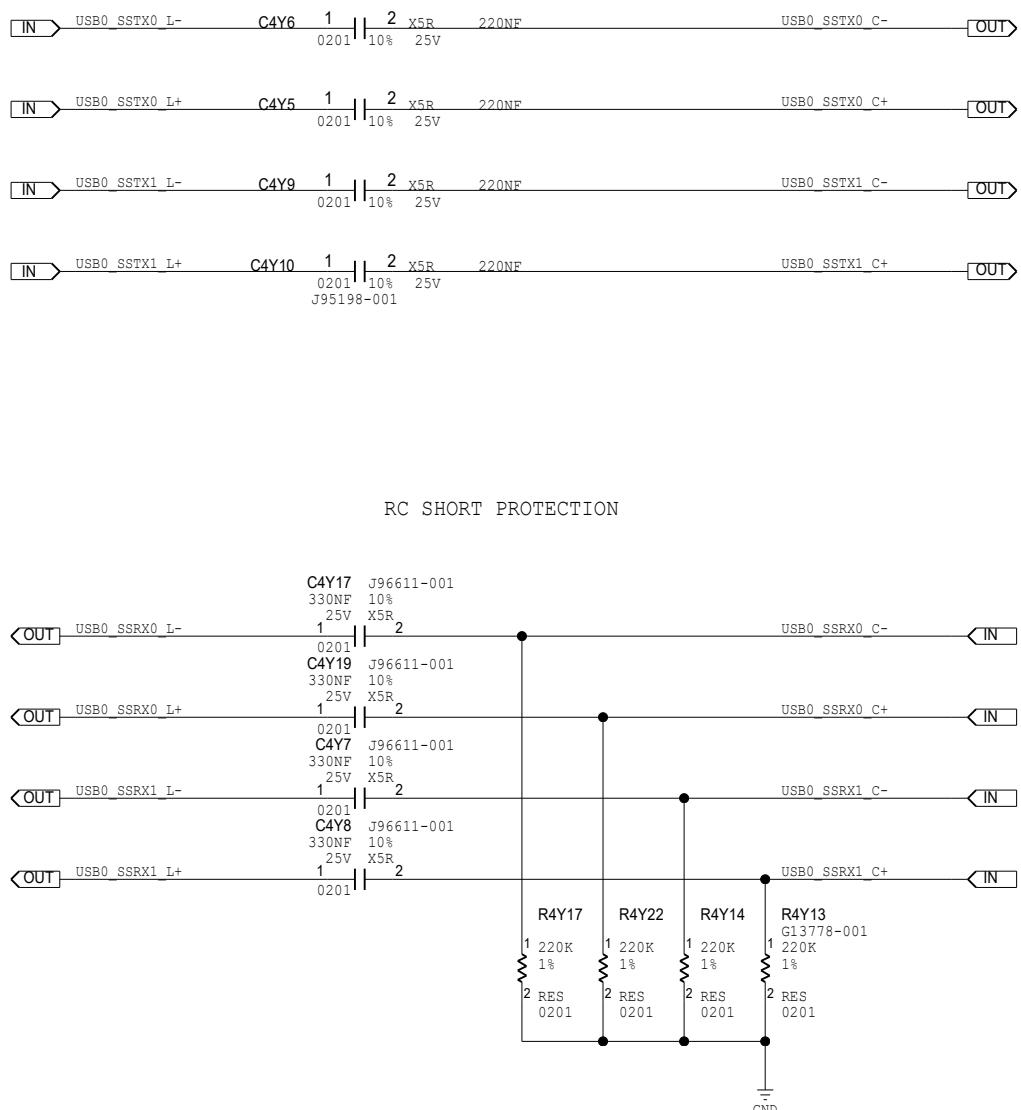

| Figure 36: USB4 on COM-HPC USB Port 2 (Fig 1 of 6): COM-HPC Side RX Coupling Caps.....                 | 76 |

| Figure 37: USB4 on COM-HPC USB Port 2 (Fig 2 of 6): Intel JHL8040R Thunderbolt Retimer Part 1.....     | 77 |

| Figure 38: USB4 on COM-HPC USB Port 2 (Fig 3 of 6): Intel JHL8040R Thunderbolt Retimer Part 2.....     | 78 |

| Figure 39: USB4 on COM-HPC USB Port 2 (Fig 4 of 6): Output Coupling and Protection.....                | 79 |

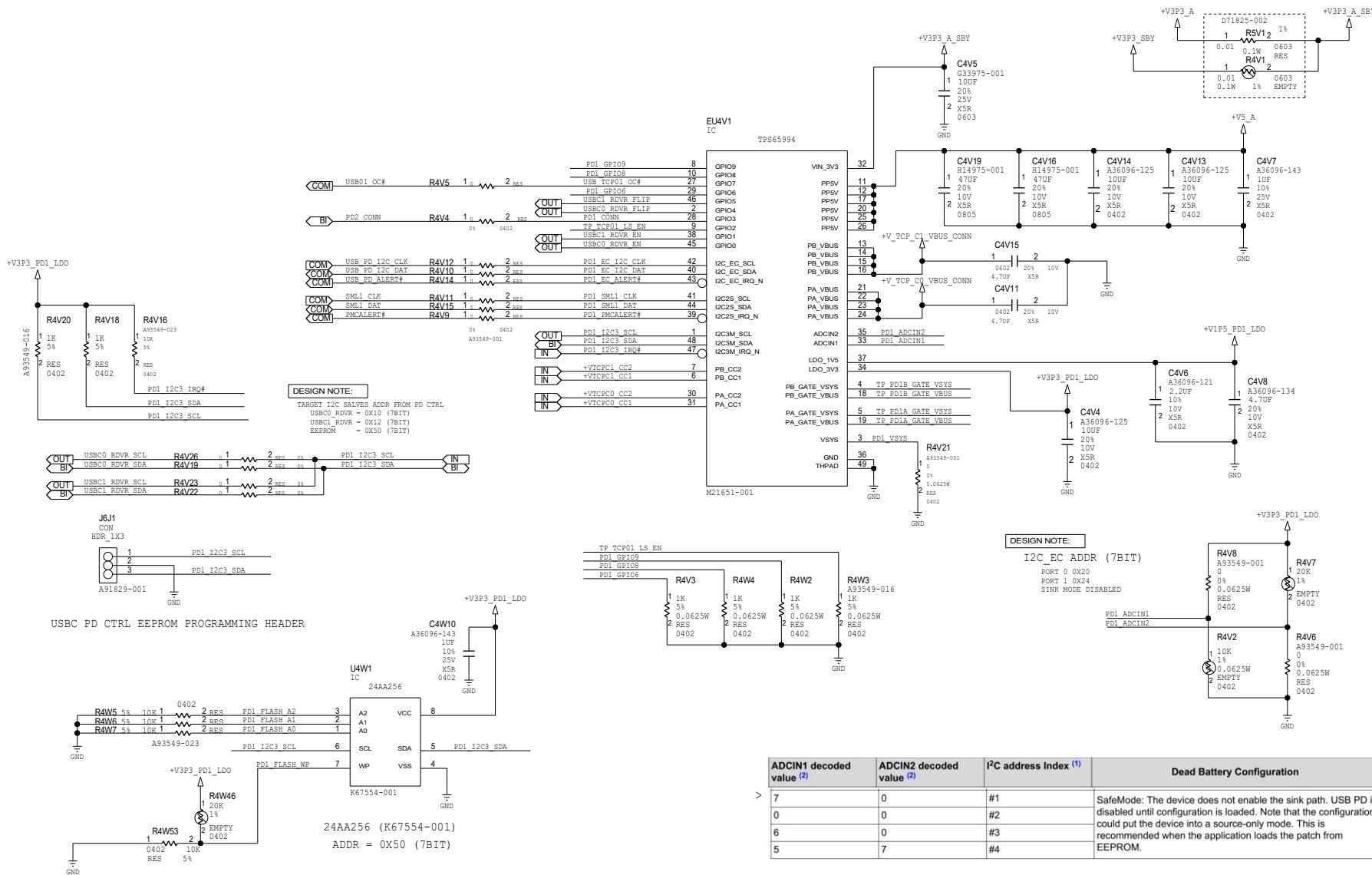

| Figure 40: USB4 on COM-HPC USB Port 2 (Fig 5 of 6): Power Delivery Controller.....                     | 80 |

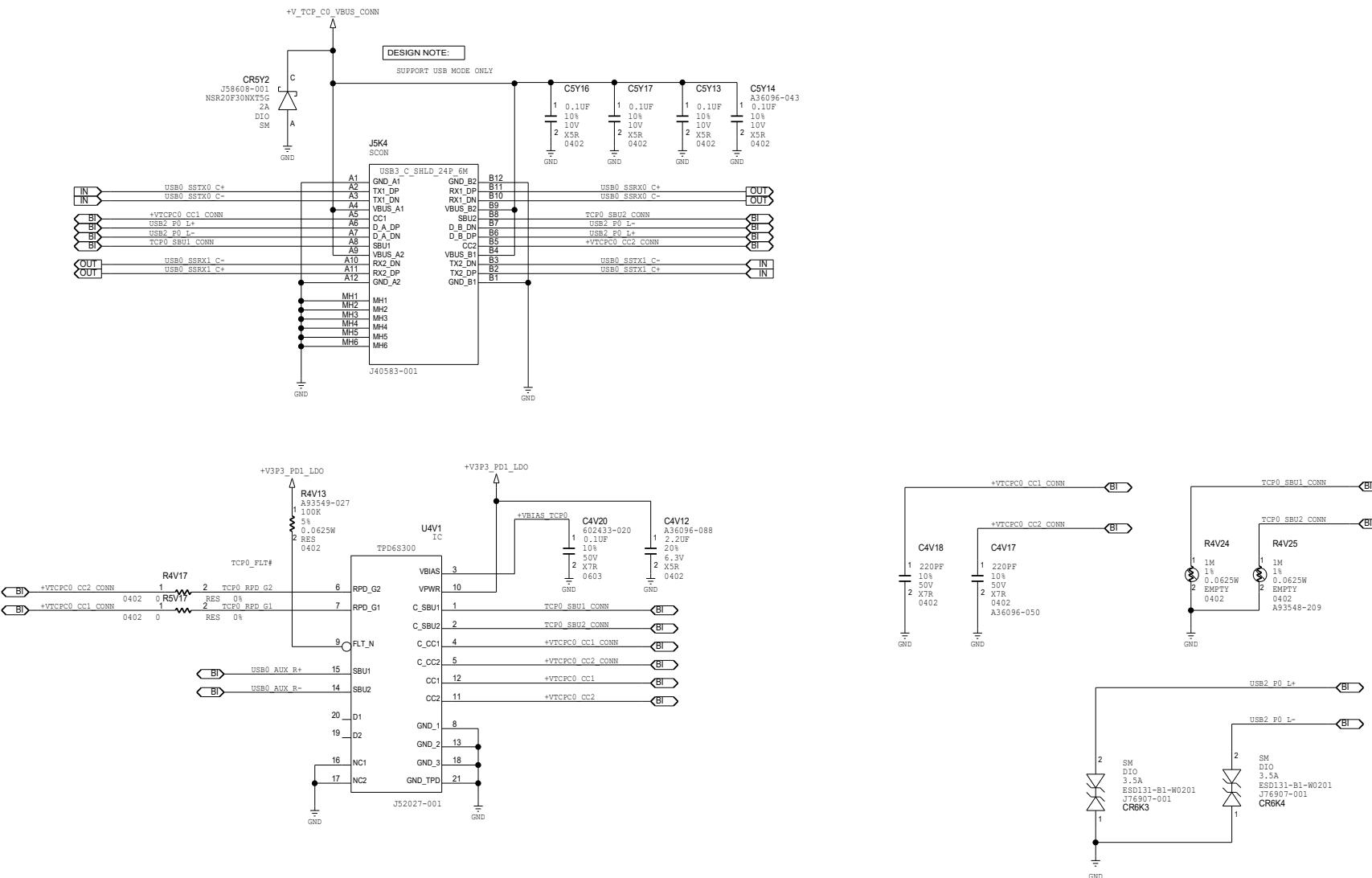

| Figure 41: USB4 on COM-HPC USB Port 2 (Fig 6 of 6): Type-C Connector and USB Port Protector.....       | 81 |

| Figure 42: Boot SPI on Carrier (Example 1).....                                                        | 82 |

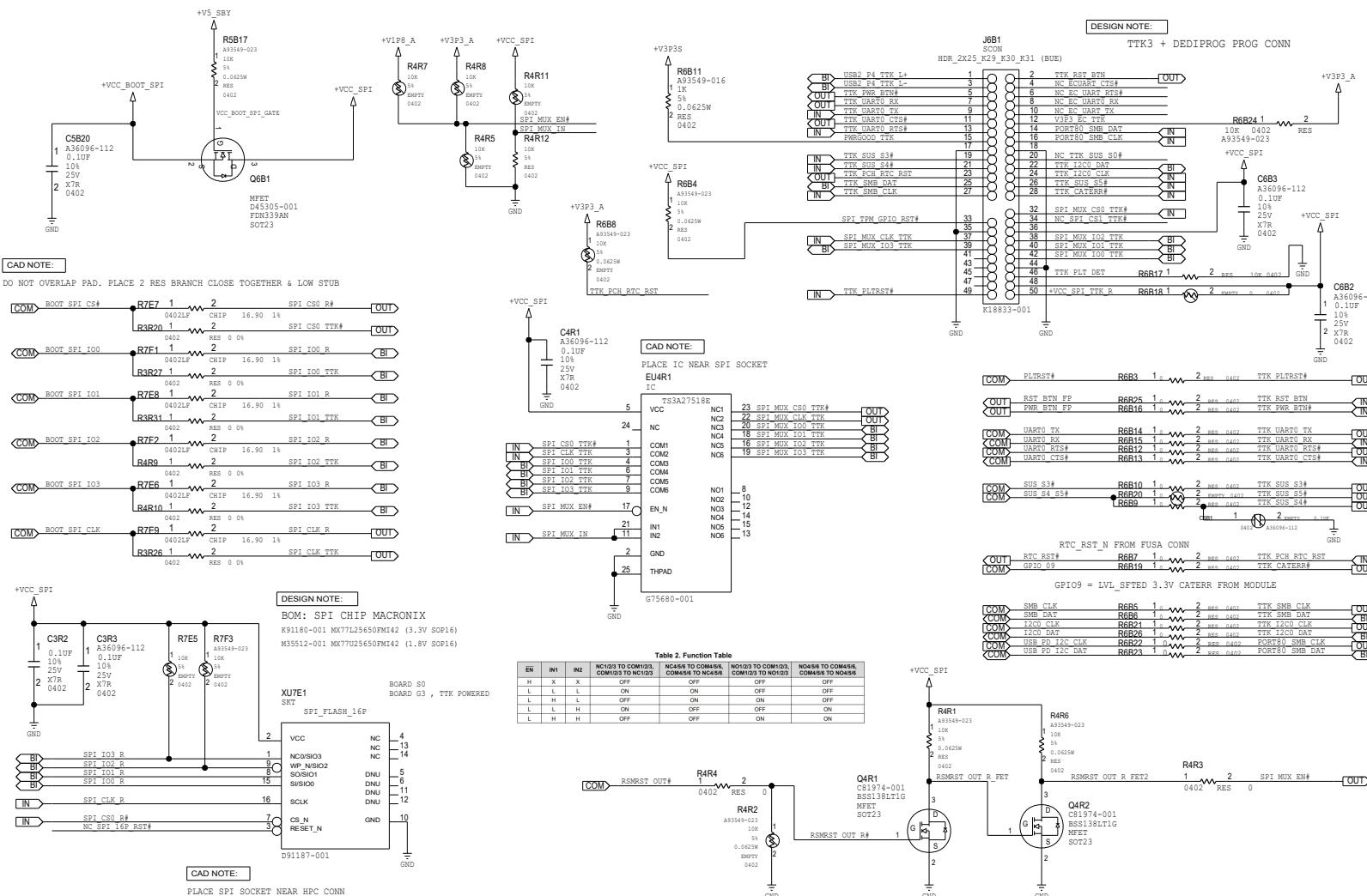

| Figure 43: Boot SPI on Carrier – Socketed Flash and Multiplexer to External Programmer.....            | 85 |

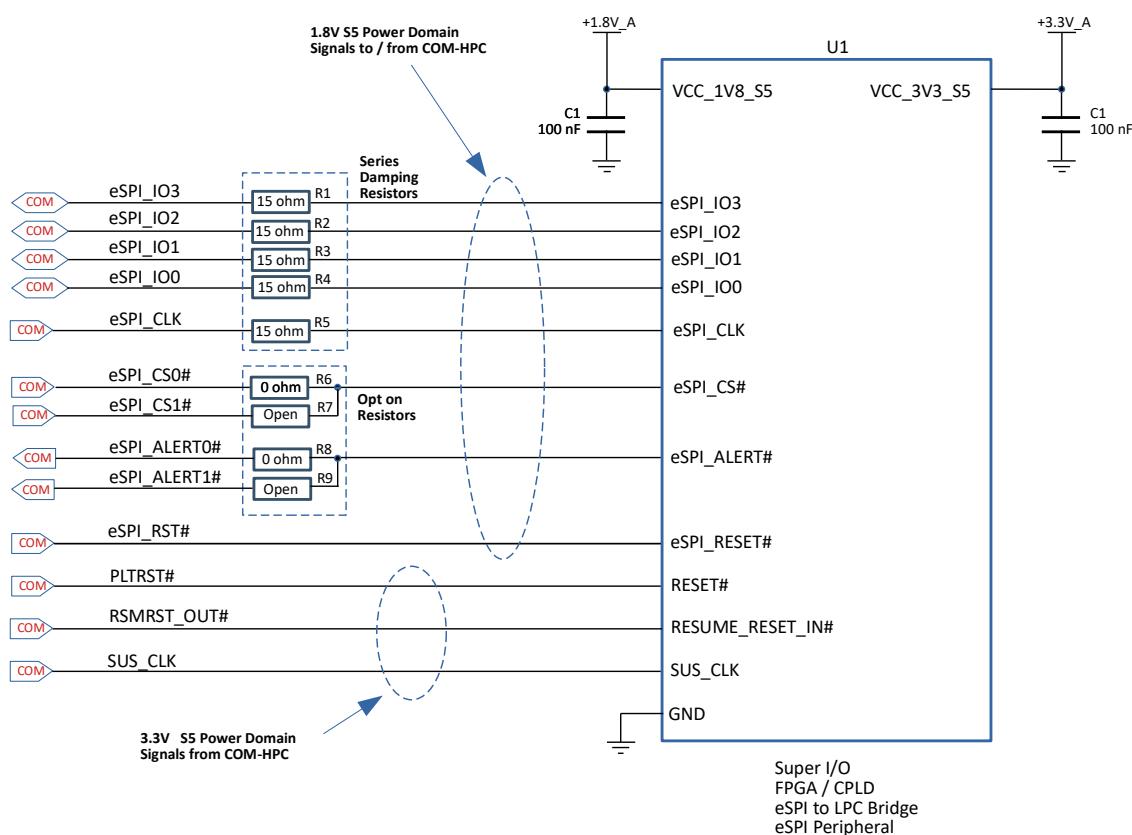

| Figure 44: eSPI Generic Interface Example: SIO, FPGA, LPC Bridge, or Other Peripheral eSPI Device..... | 86 |

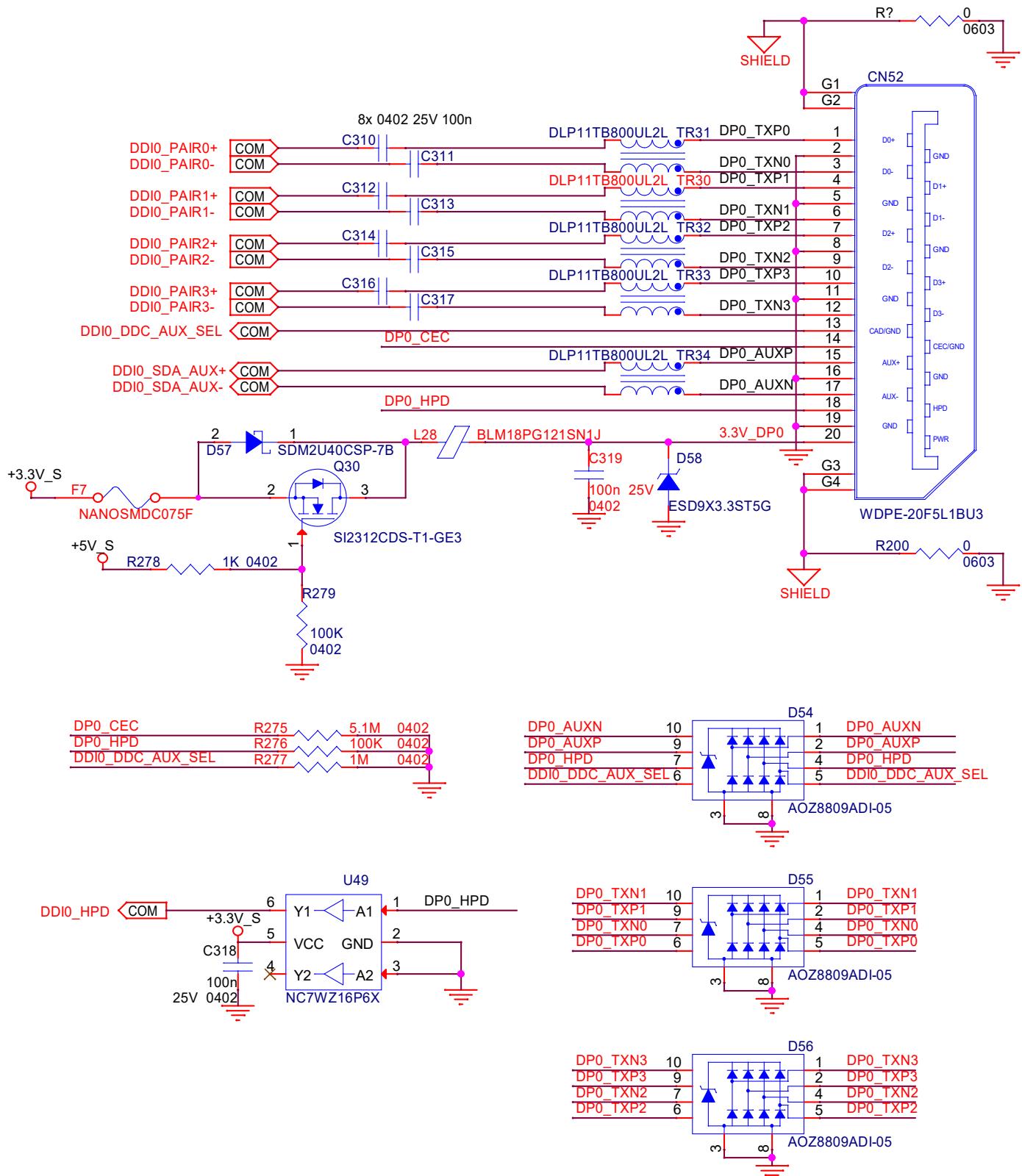

| Figure 45: DisplayPort Over DDI.....                                                                   | 87 |

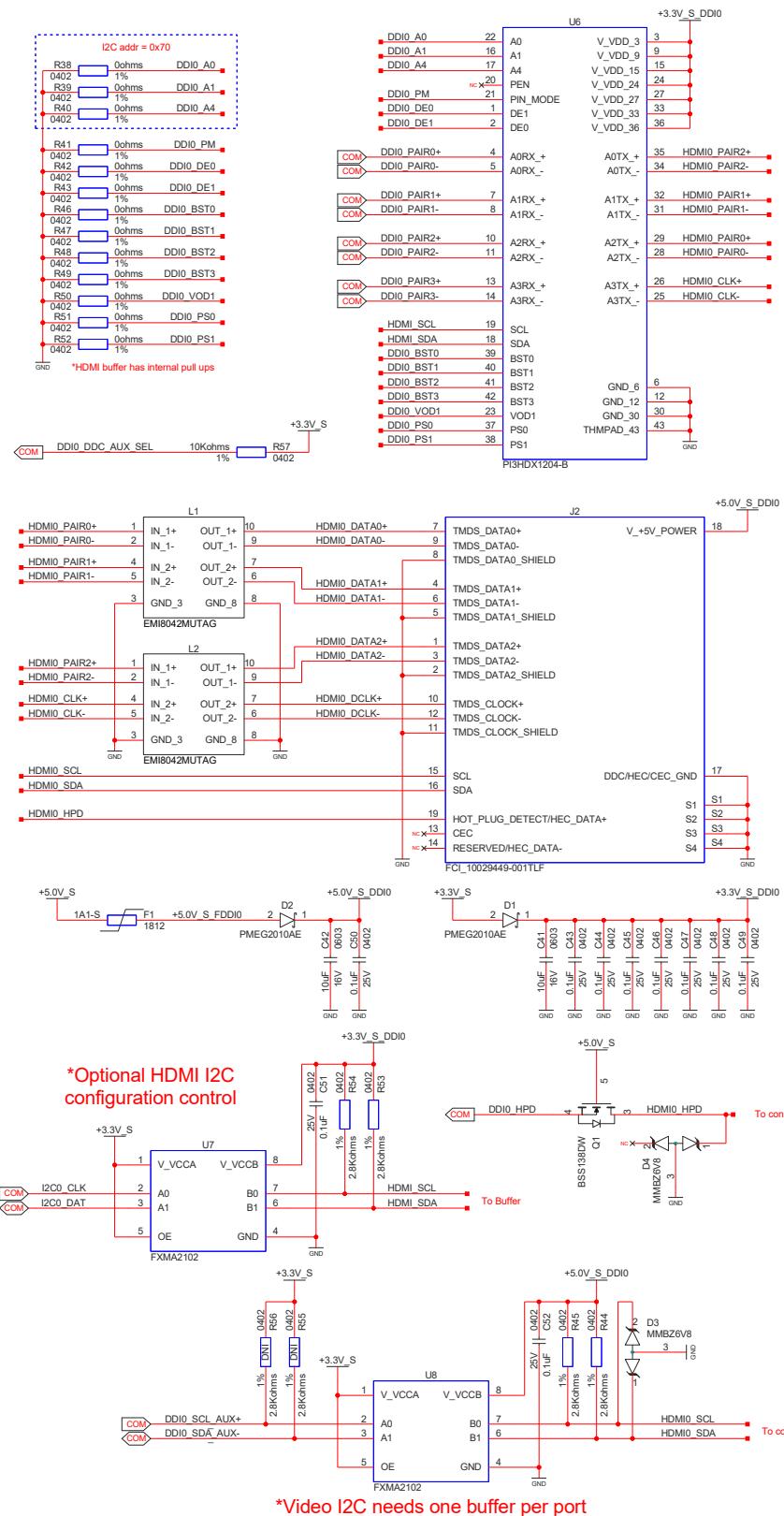

| Figure 46: HDMI Over DDI.....                                                                          | 90 |

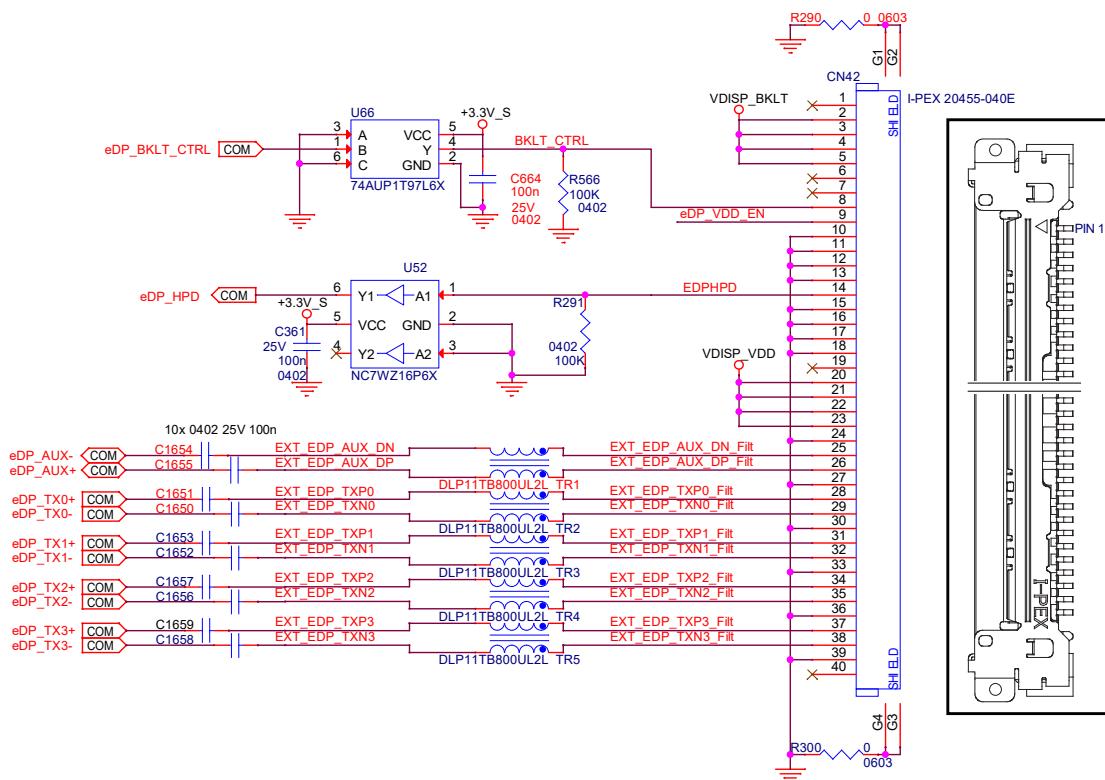

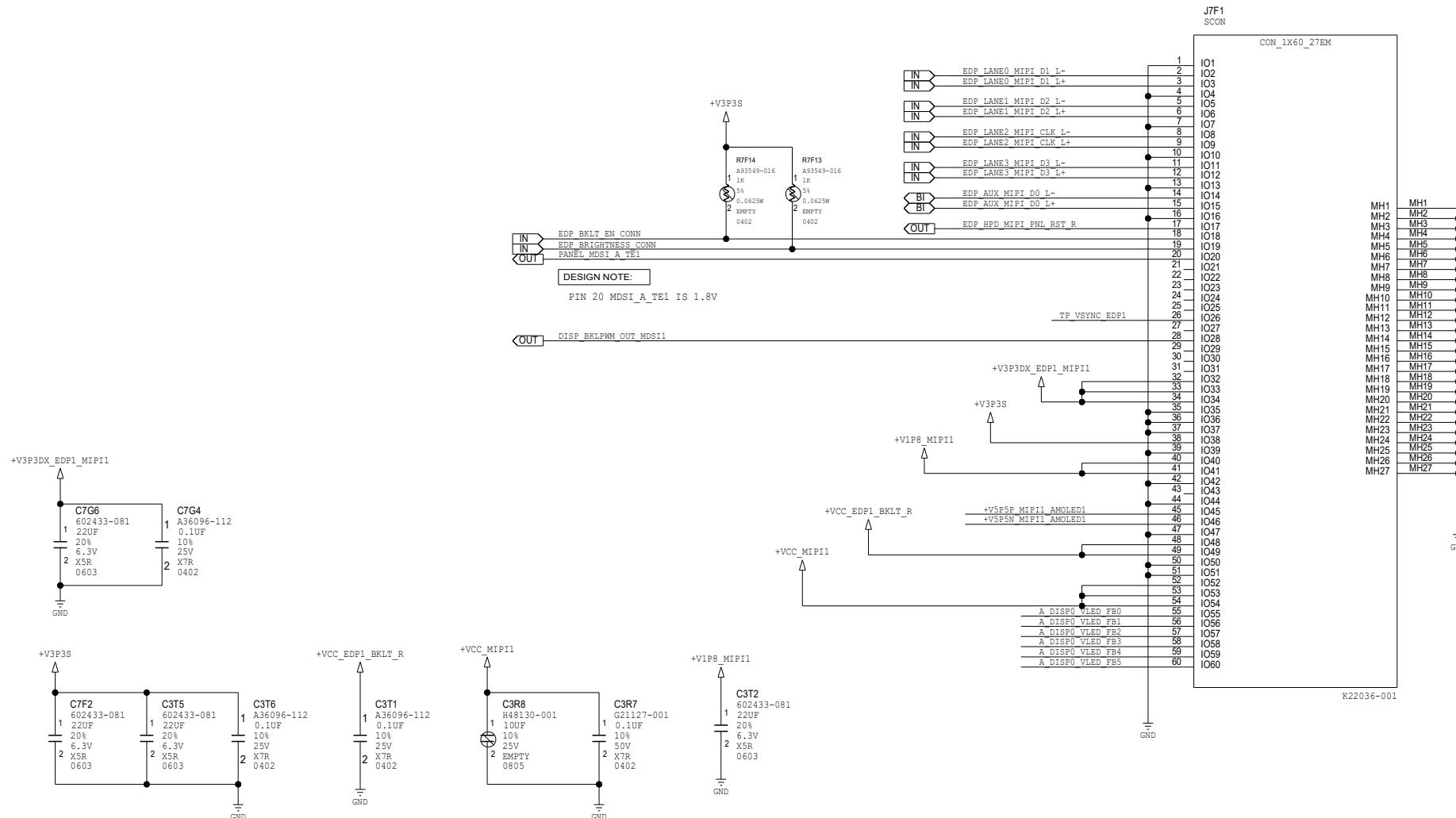

| Figure 47: eDP Schematic Example.....                                                                  | 92 |

---

|                                                                                                             |     |

|-------------------------------------------------------------------------------------------------------------|-----|

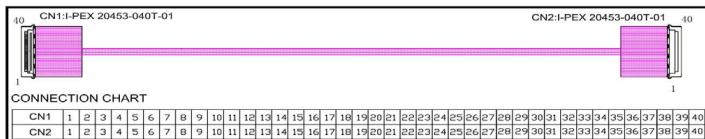

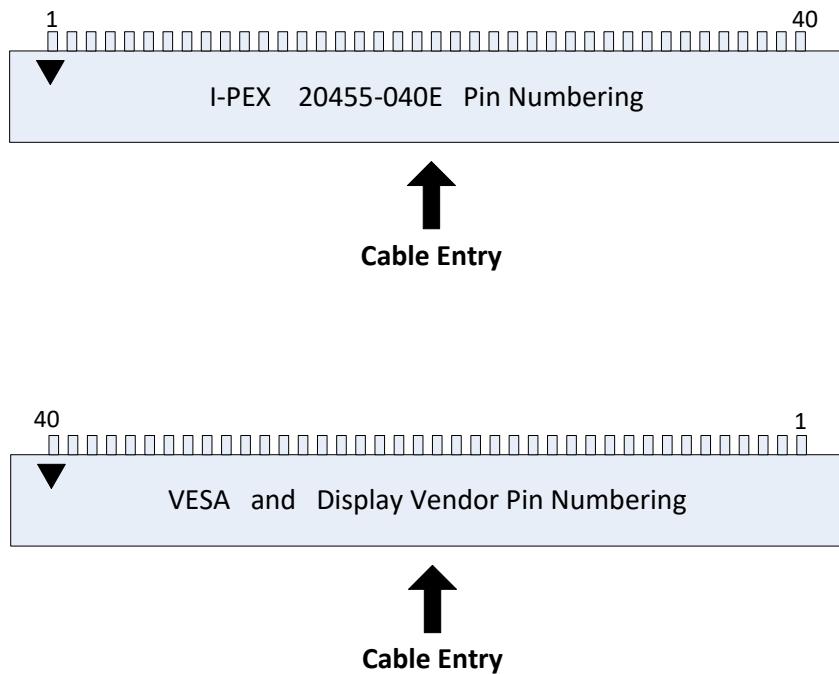

| Figure 48: eDP Connector Pin Numbering.....                                                                 | 93  |

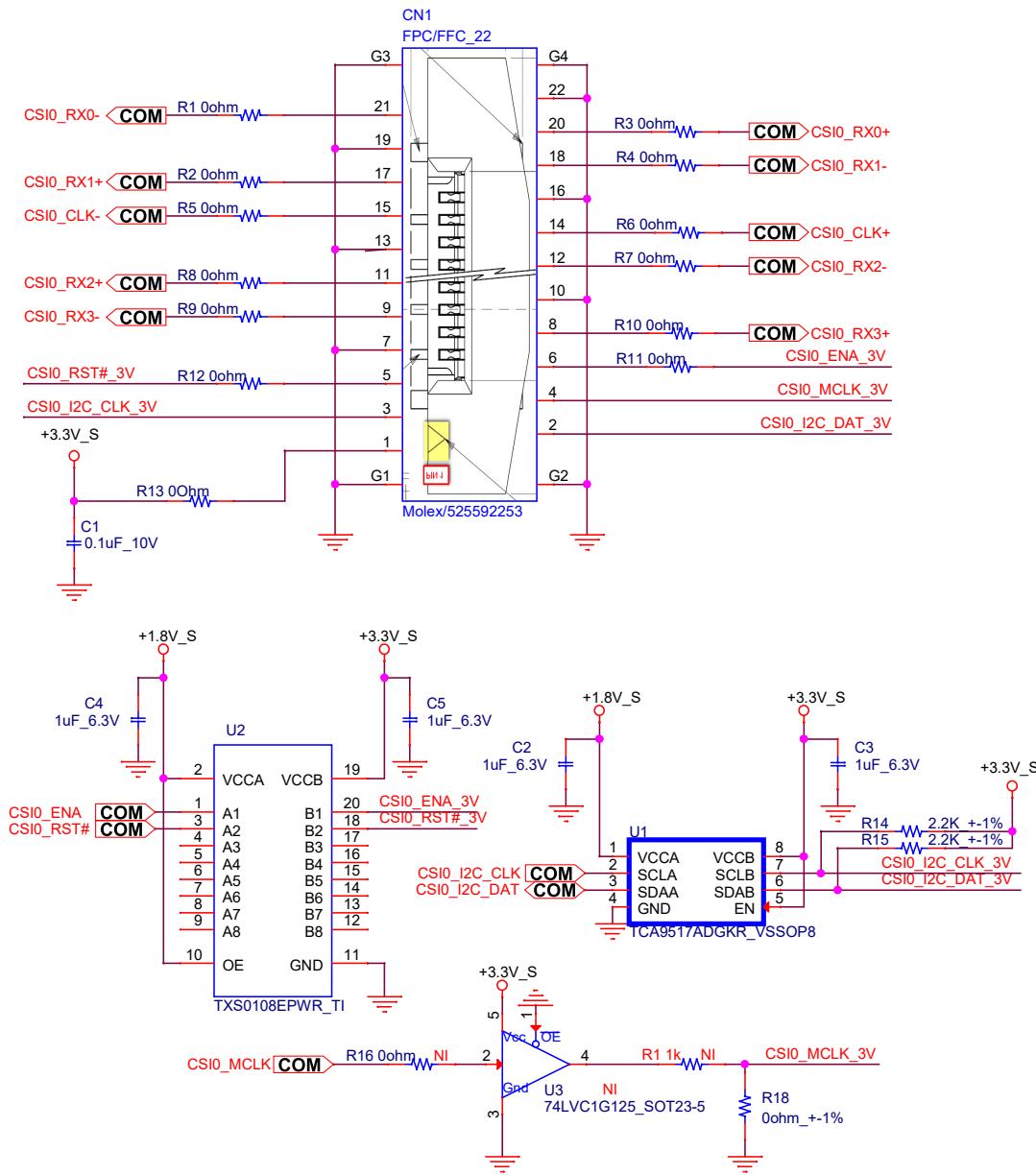

| Figure 49: MIPI-CSI.....                                                                                    | 95  |

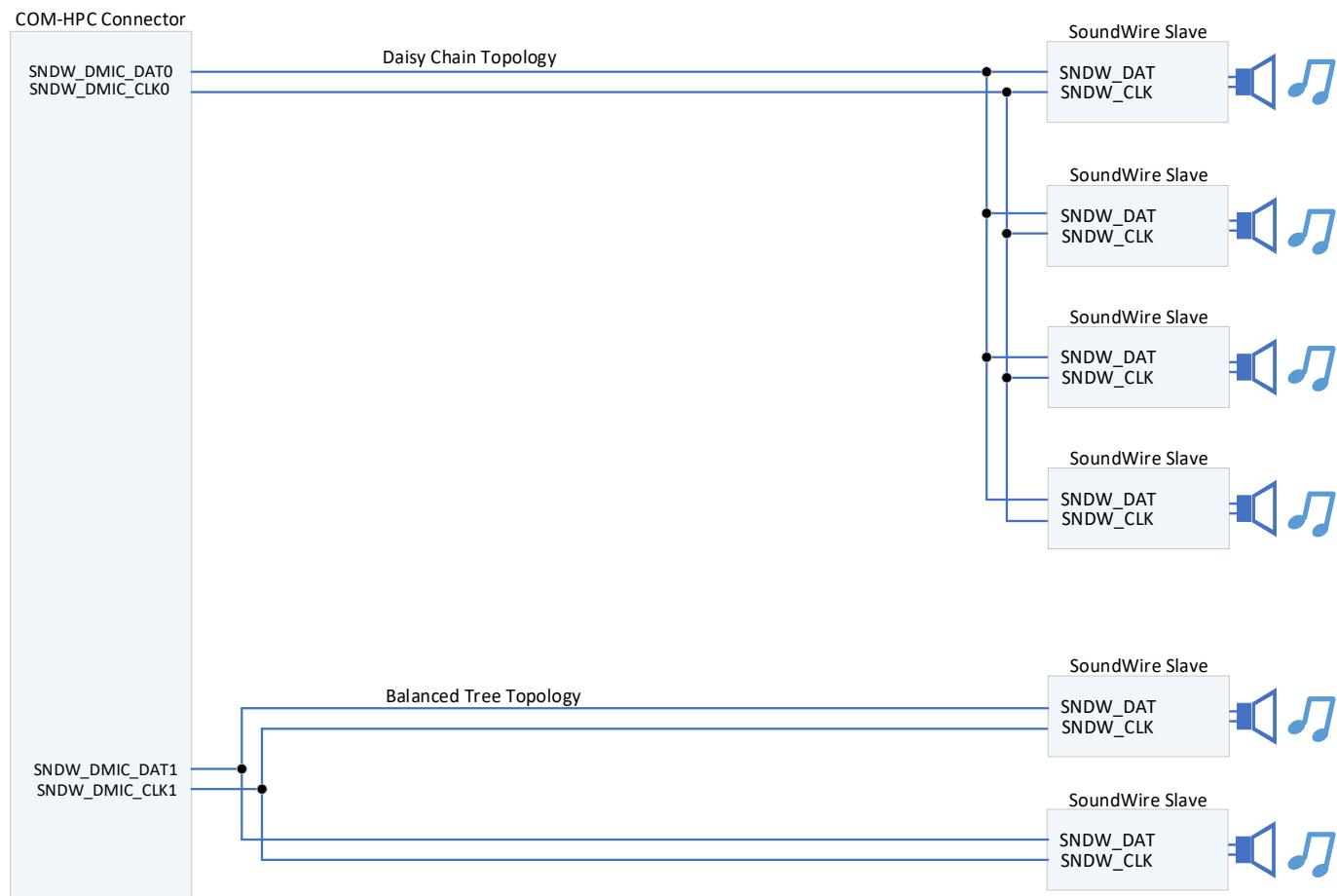

| Figure 50: MIPI SoundWire Routing Topologies.....                                                           | 98  |

| Figure 51: MIPI SoundWire Point to Point Connection With SI Components.....                                 | 98  |

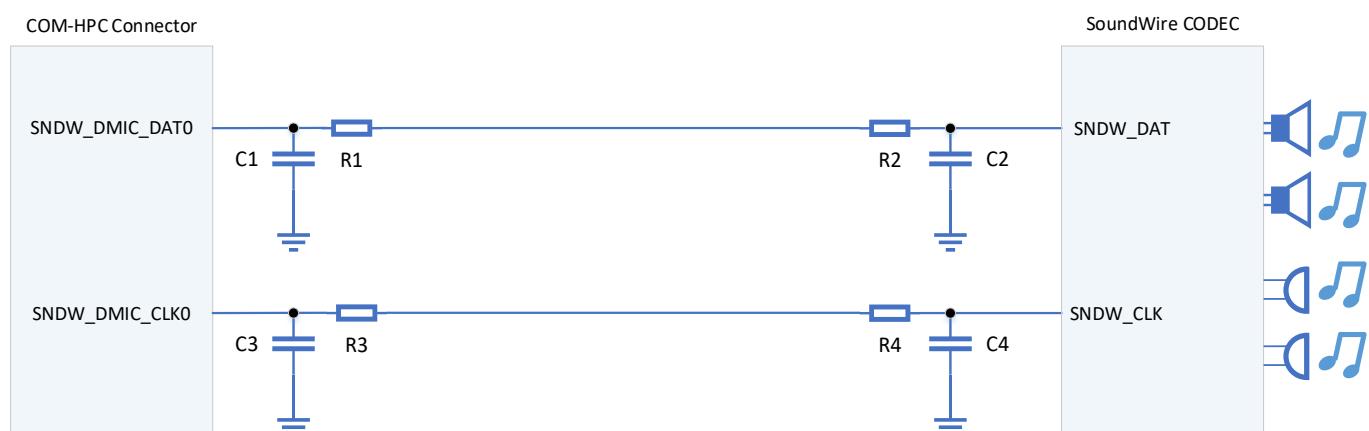

| Figure 52: UART0 and UART1 RS-232 Level Translated Asynchronous Serial Ports.....                           | 101 |

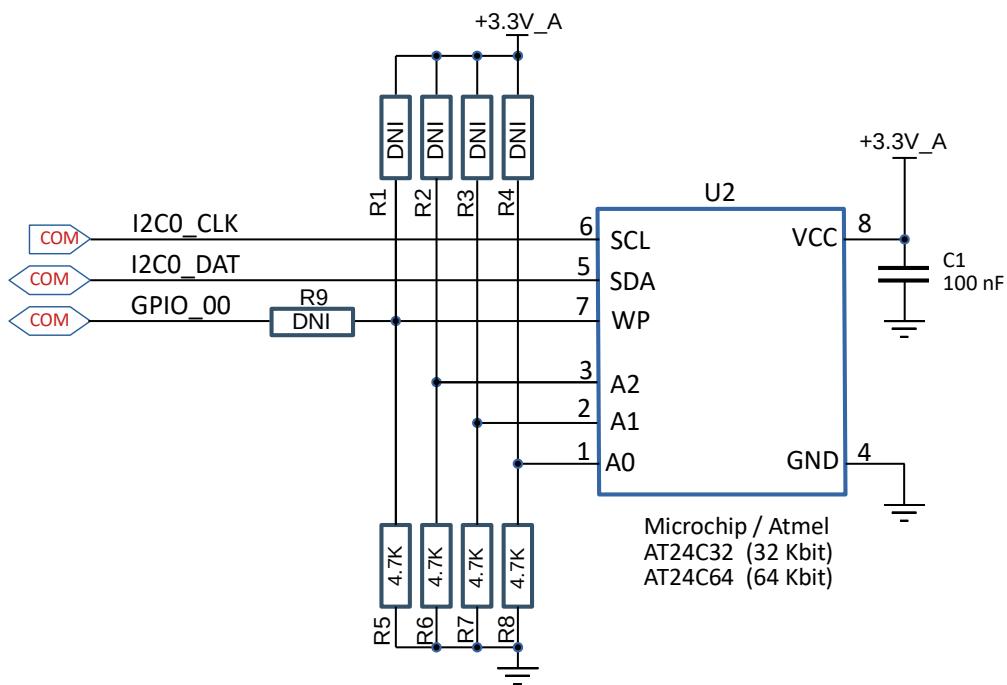

| Figure 53: I2C0 Example: Carrier EEPROM in S5 Power Domain.....                                             | 104 |

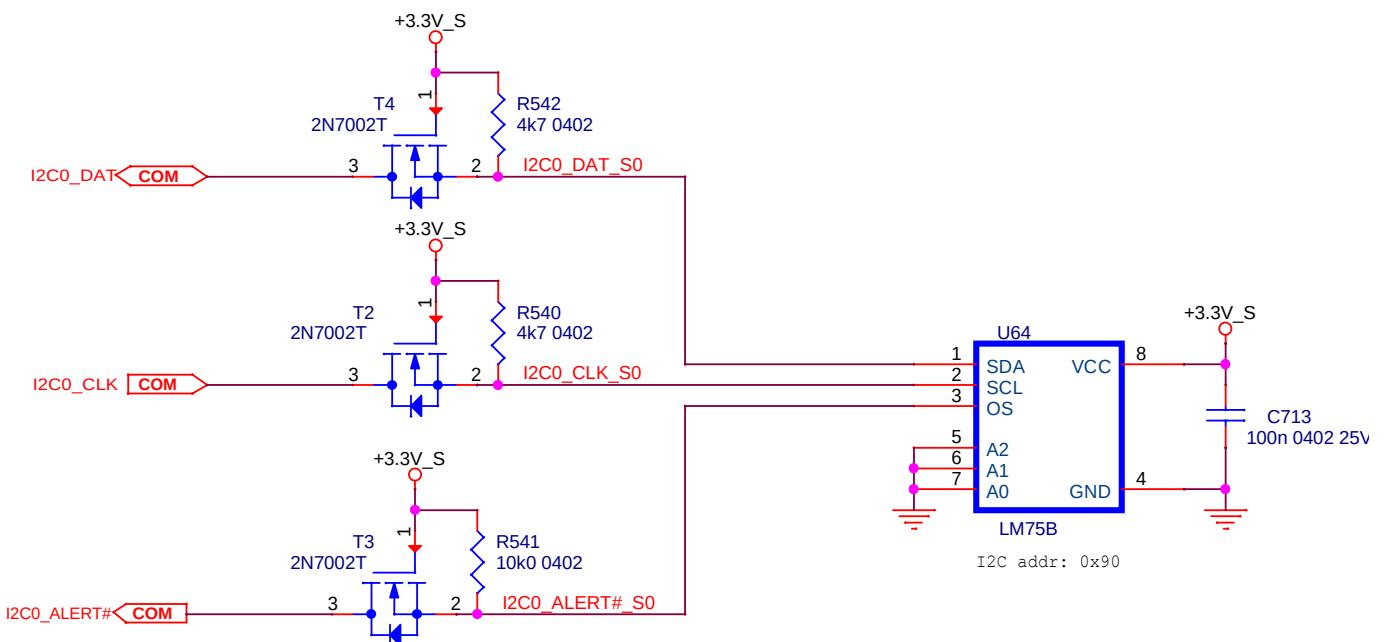

| Figure 54: I2C0 Example: Carrier Temperature Sensor in S0 Power Domain.....                                 | 105 |

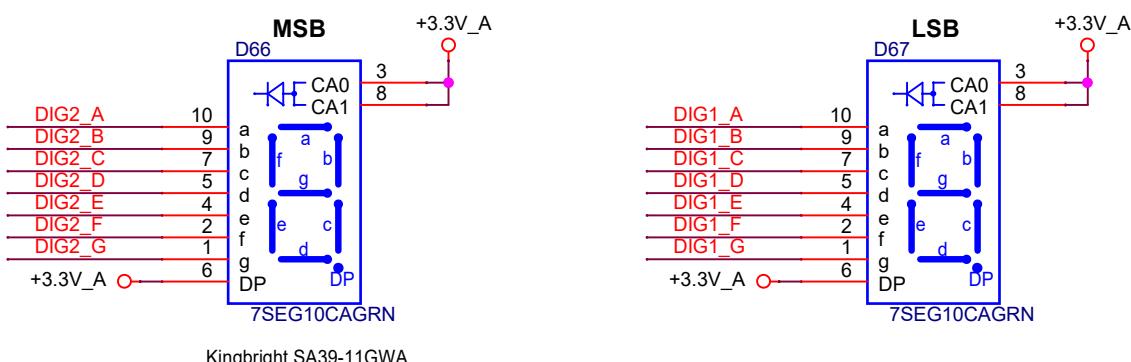

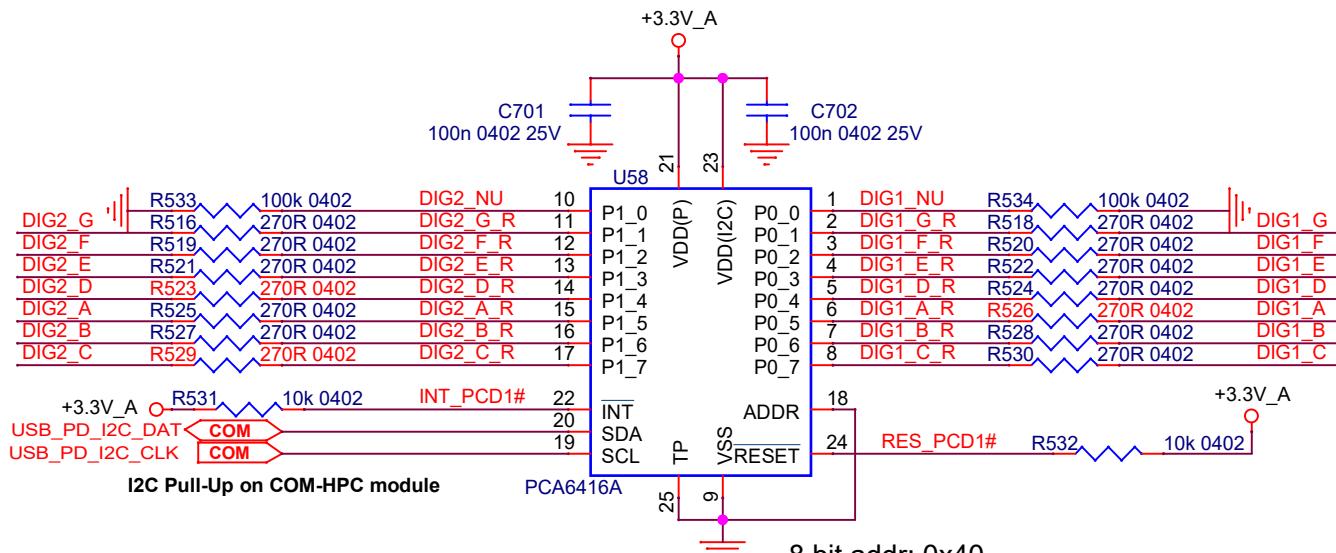

| Figure 55: Port 80h Debug Display Over COM-HPC USB_PD_I2C.....                                              | 107 |

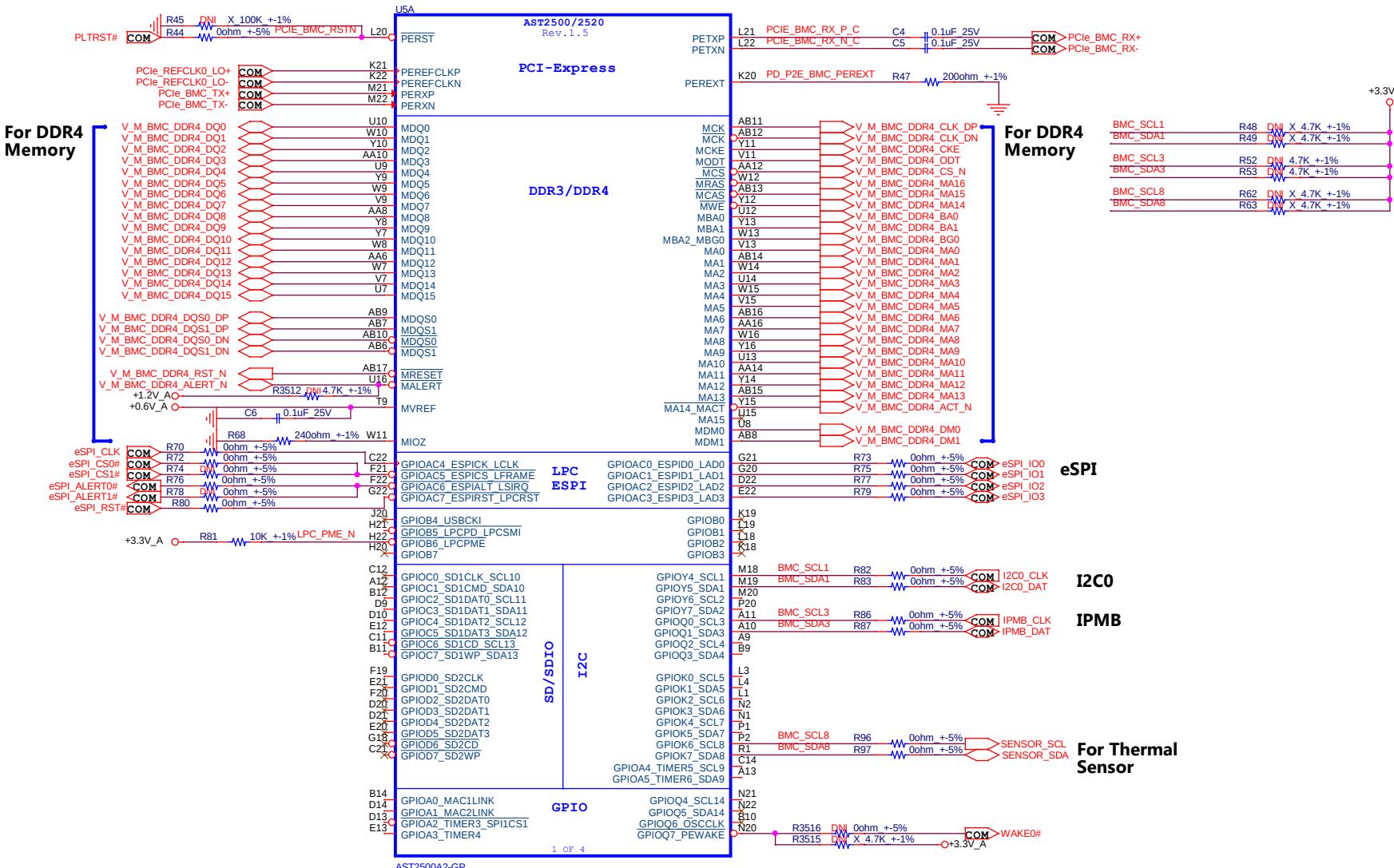

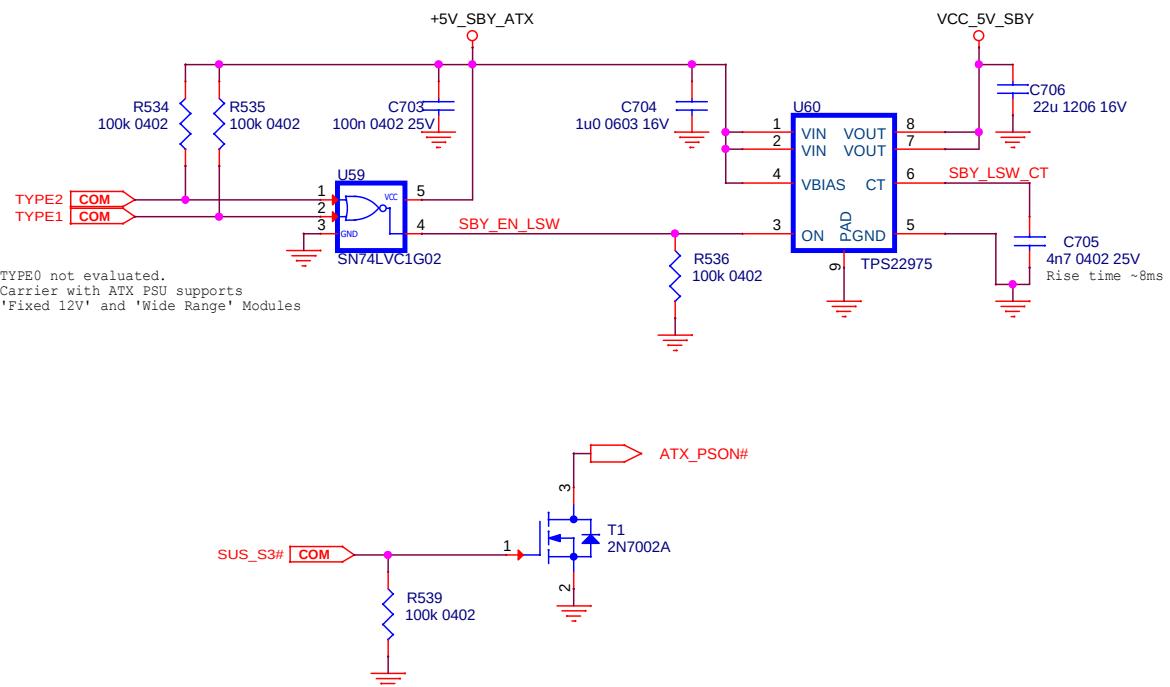

| Figure 56: Carrier BMC with IPMB Link to Module – Sheet 1.....                                              | 109 |

| Figure 57: Carrier BMC with IPMB Link to Module – Sheet 2.....                                              | 110 |

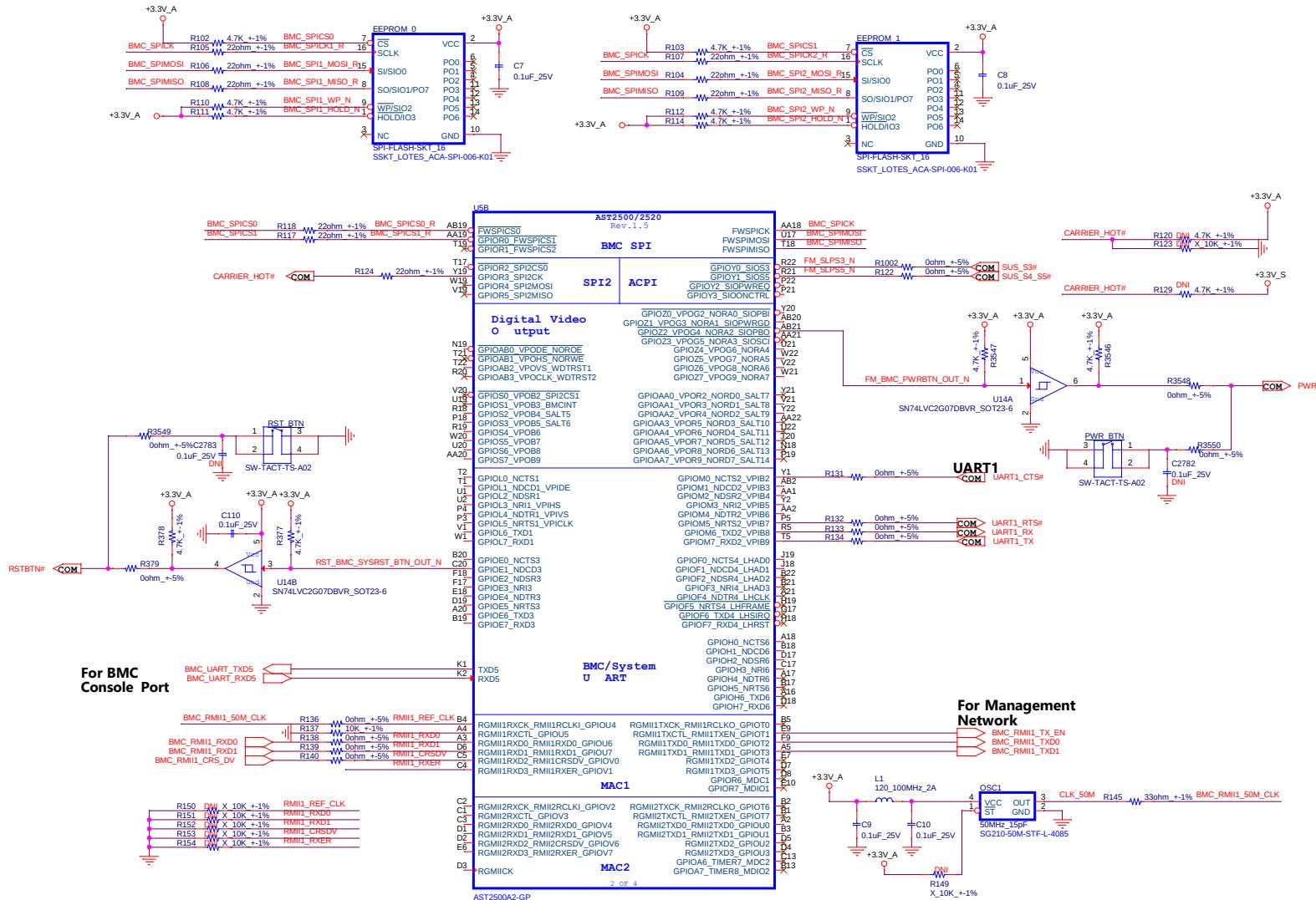

| Figure 58: Carrier BMC with IPMB Link to Module – Sheet 3.....                                              | 111 |

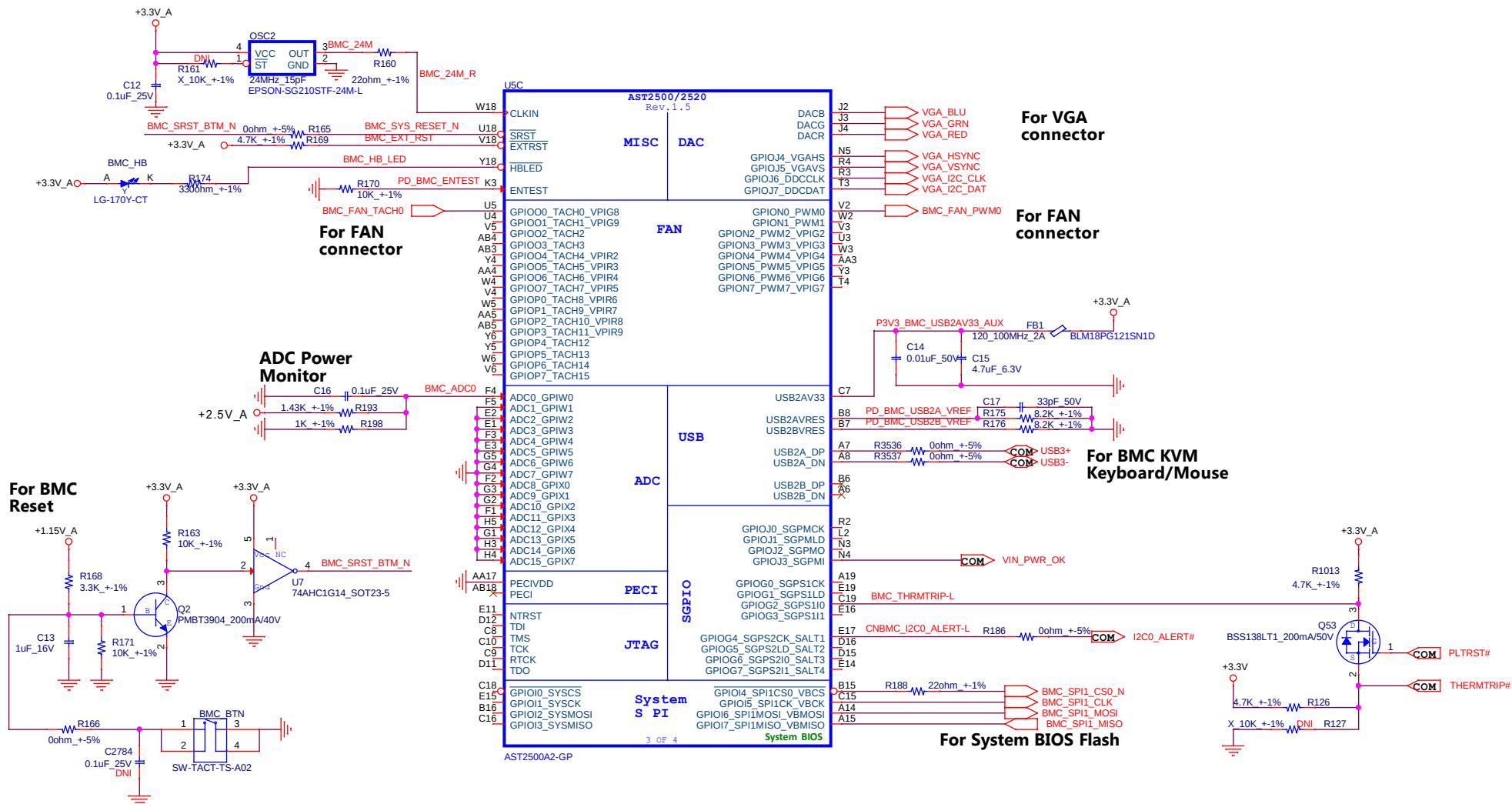

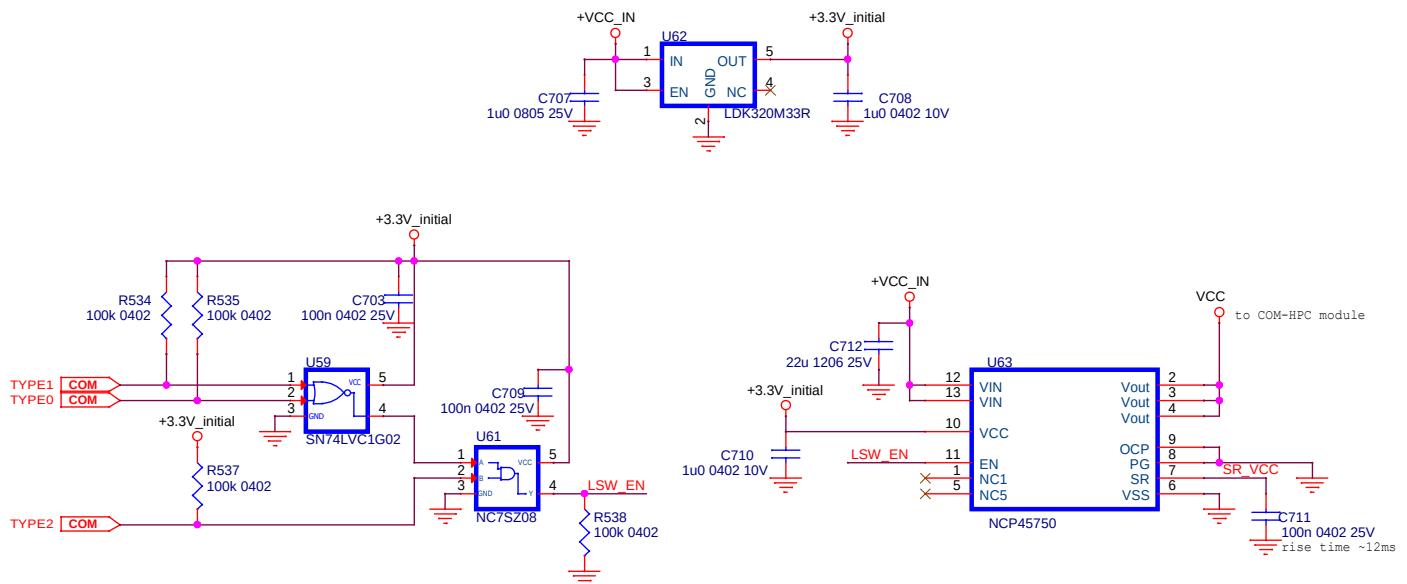

| Figure 59: Module Type Detection / Protection – ATX Power Supply and Client Type Module / Carrier.....      | 117 |

| Figure 60: Module Type Detection / Protection – AT Power Supply and Server Type Module / Carrier.....       | 117 |

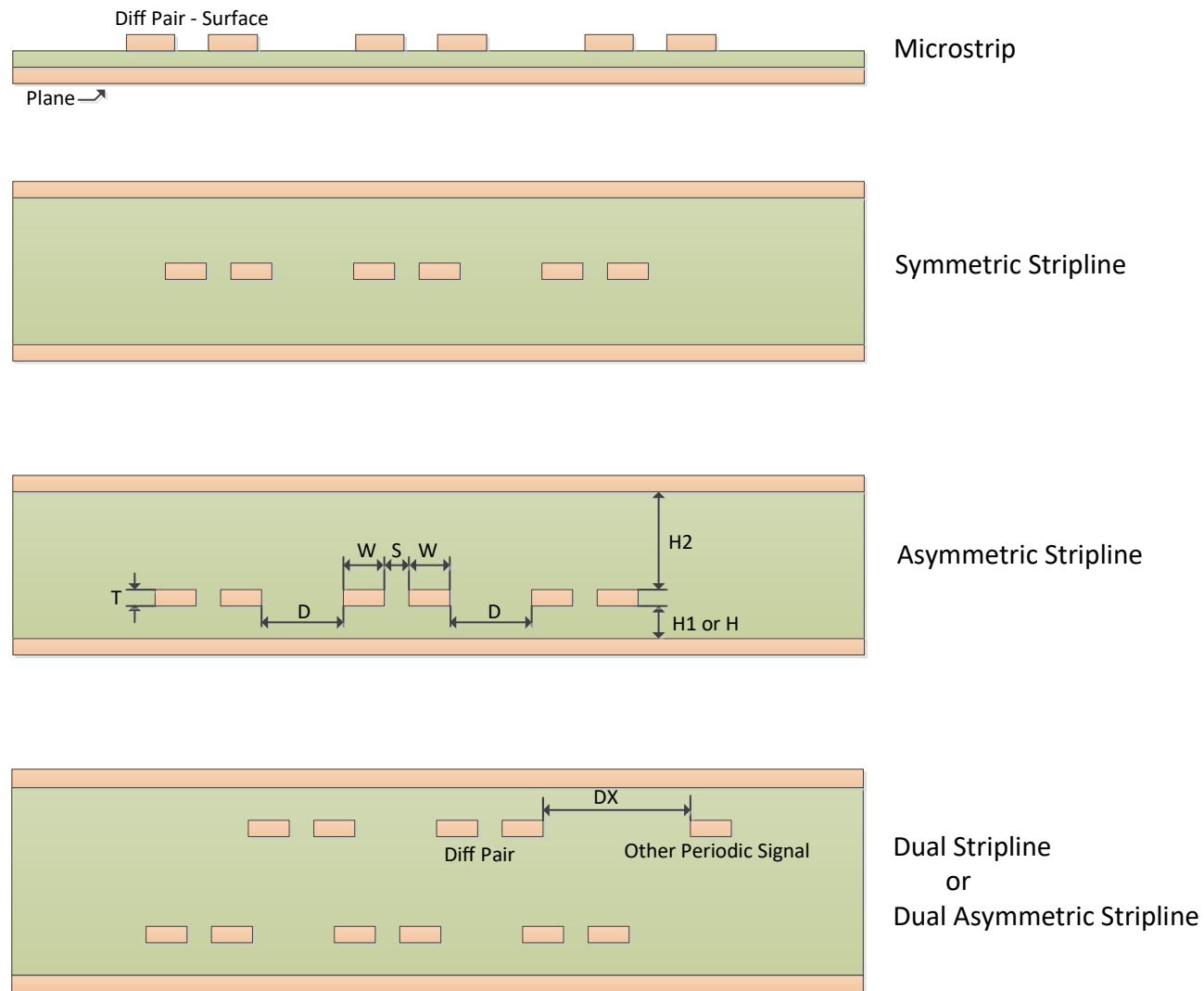

| Figure 61: PCB Cross Section Terms and Notations.....                                                       | 120 |

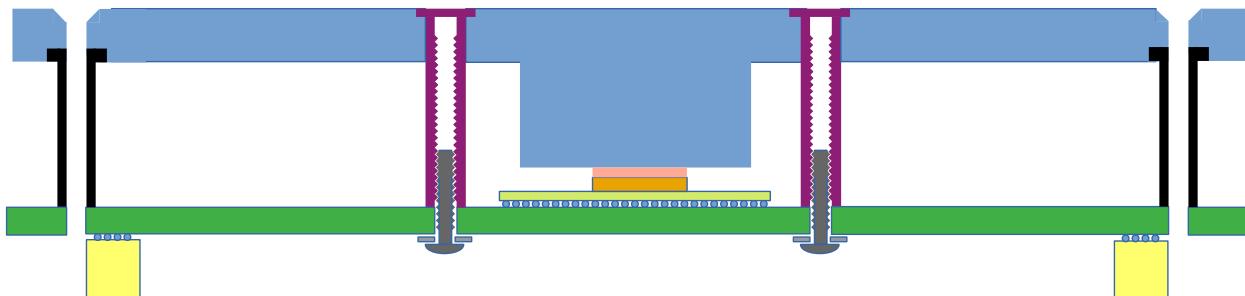

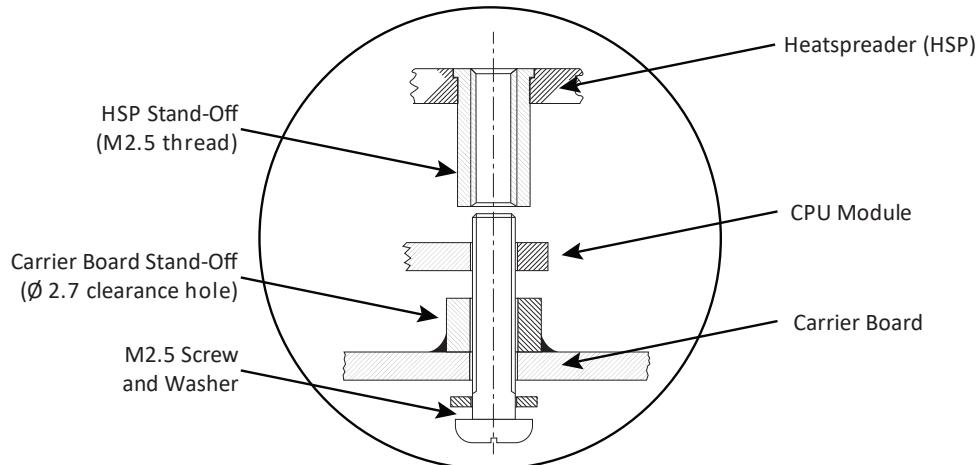

| Figure 62: Vendor Specific Heat Spreader to Module Attachment – Bottom Side Module PCB Access.....          | 134 |

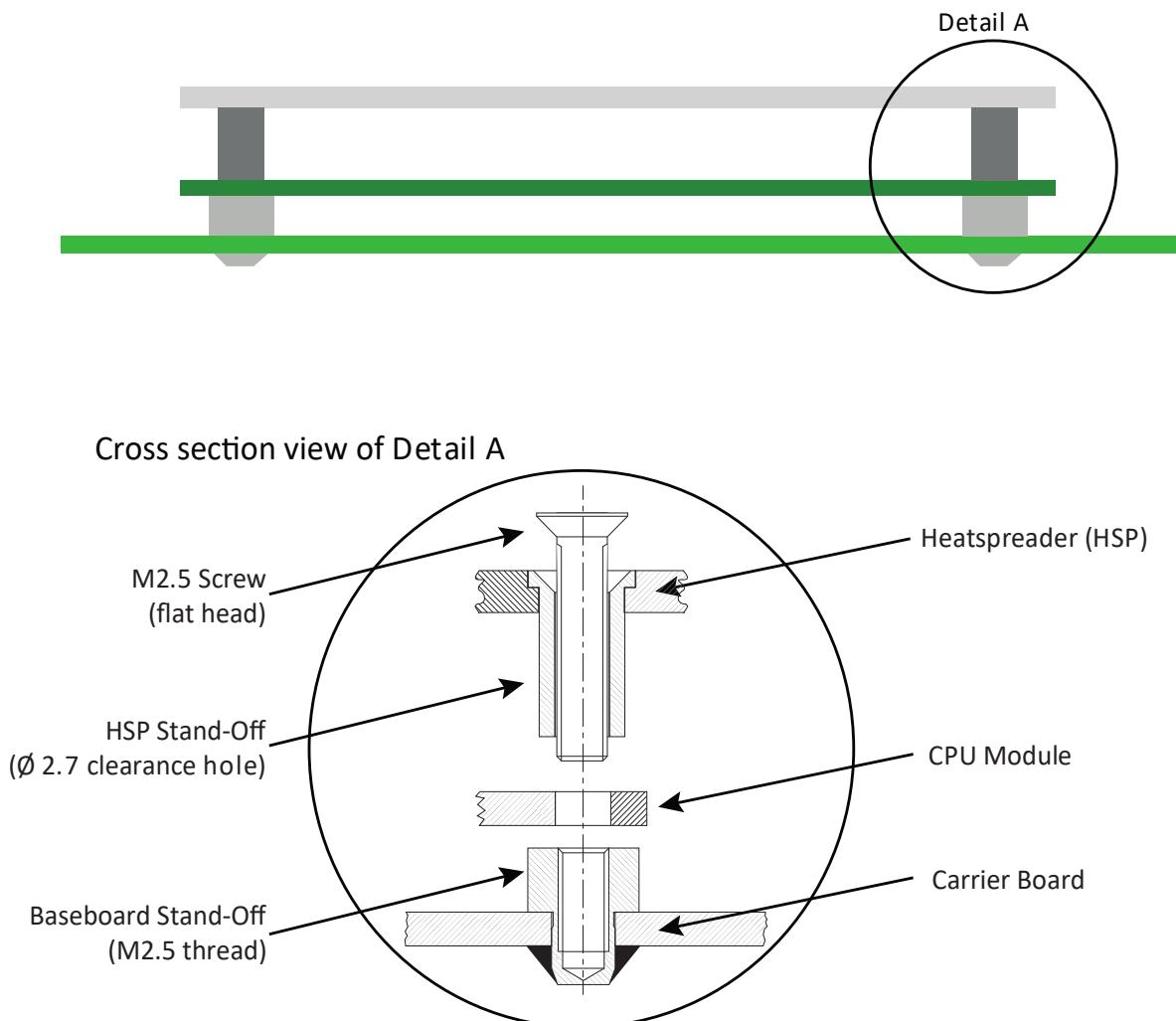

| Figure 63: Heat Spreader Assembly Mounting to Carrier – Bottom Side Screw Access.....                       | 135 |

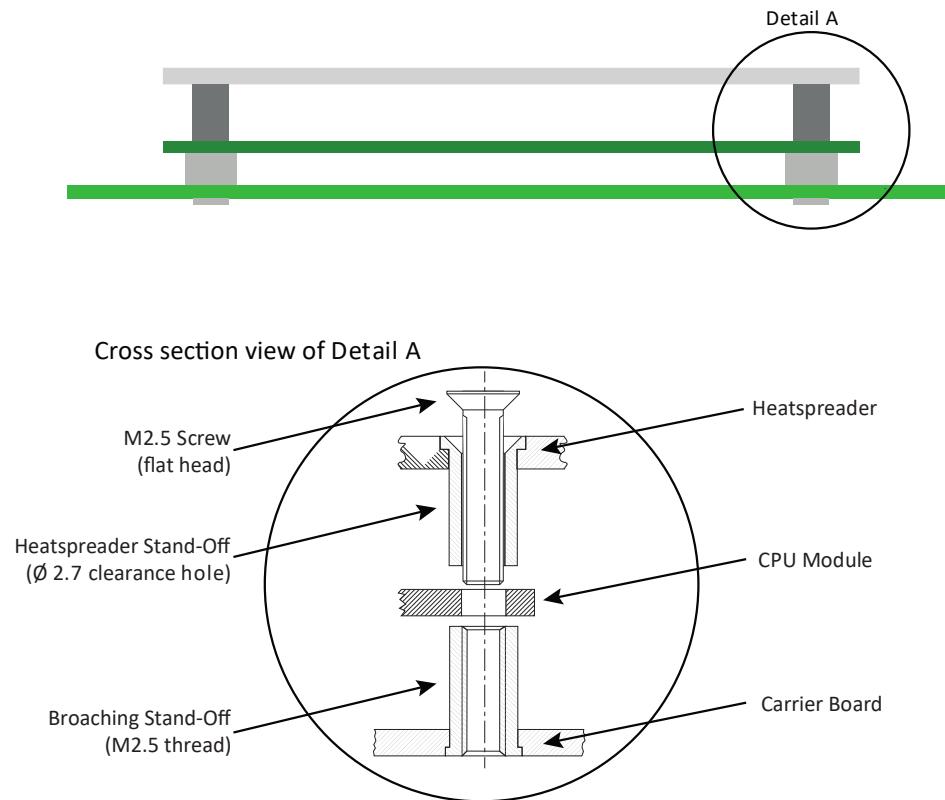

| Figure 64: Heat Spreader Assembly Mounting to Carrier – Top Side Screw Access.....                          | 136 |

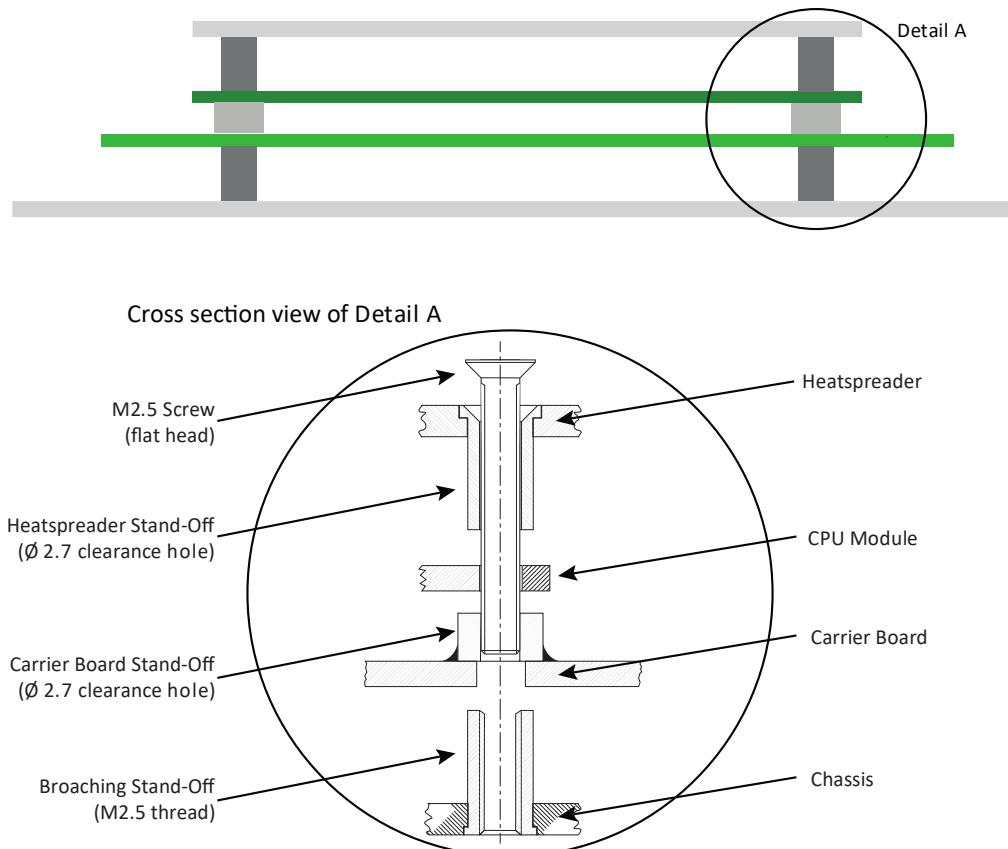

| Figure 65: Heat Spreader Assembly Mounting to Carrier With Broaching Nut – Top Side Screw Access.....       | 137 |

| Figure 66: Heat Spreader Assembly Mounting to Carrier and Chassis – Top Side Screw Access.....              | 138 |

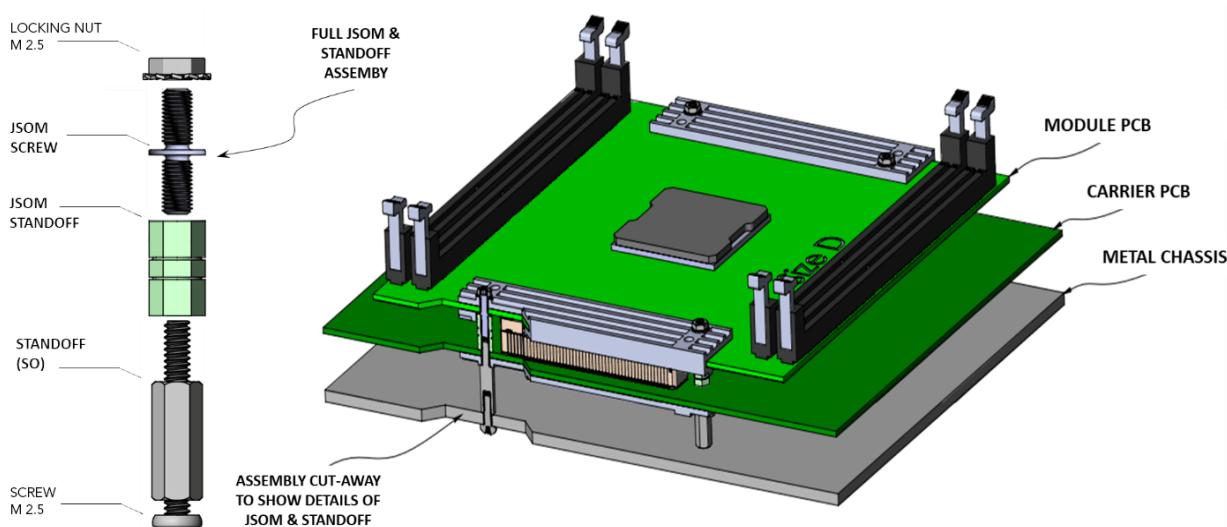

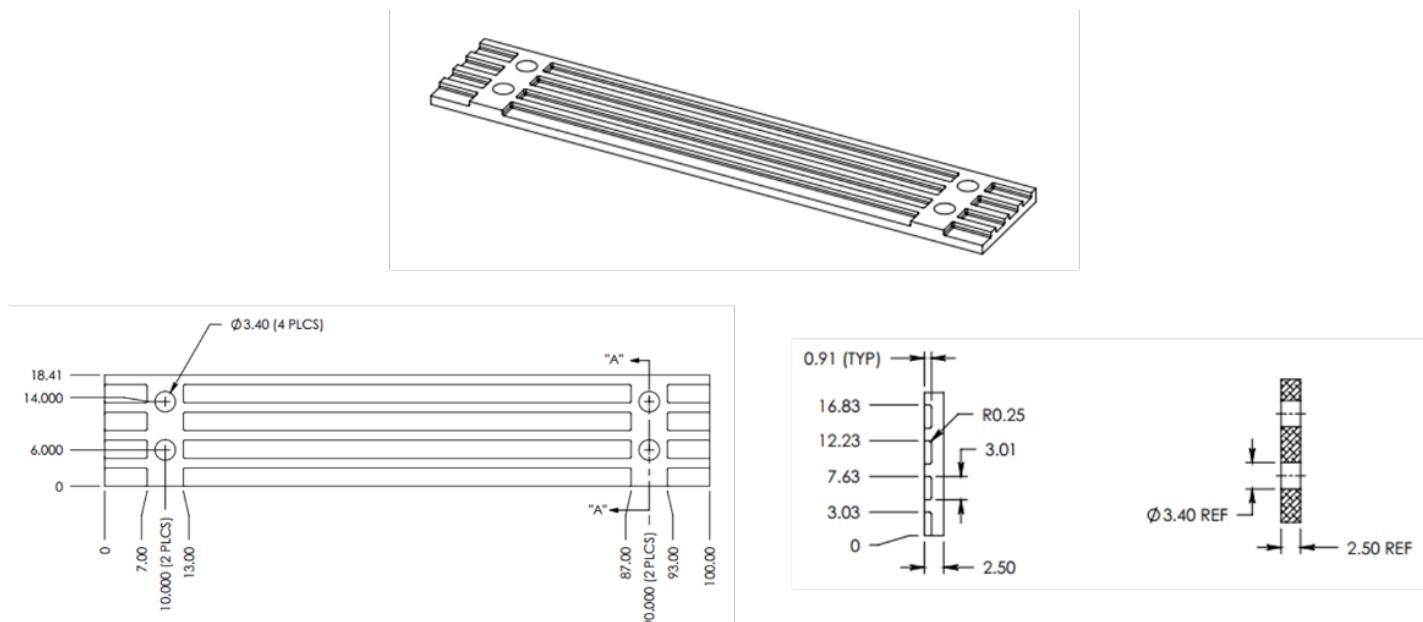

| Figure 67: JSOM (Jack Screw Standoff – Micro) Diagram and Application Cutaway.....                          | 140 |

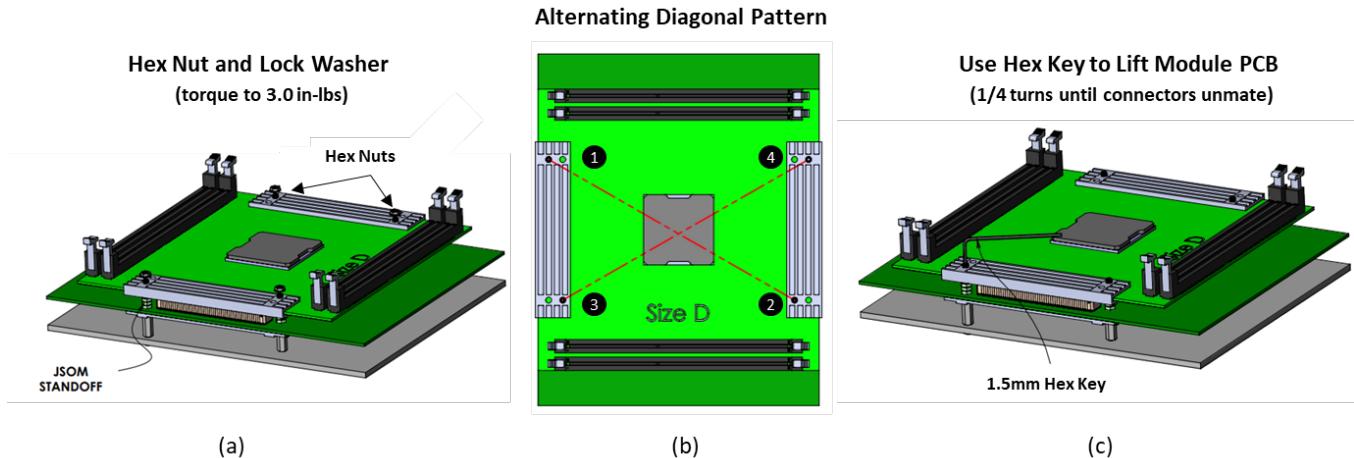

| Figure 68: (a) Hex Nuts to Torque (b) Diagonal Torque Application / De-application (c) Hex Screw Turns..... | 141 |

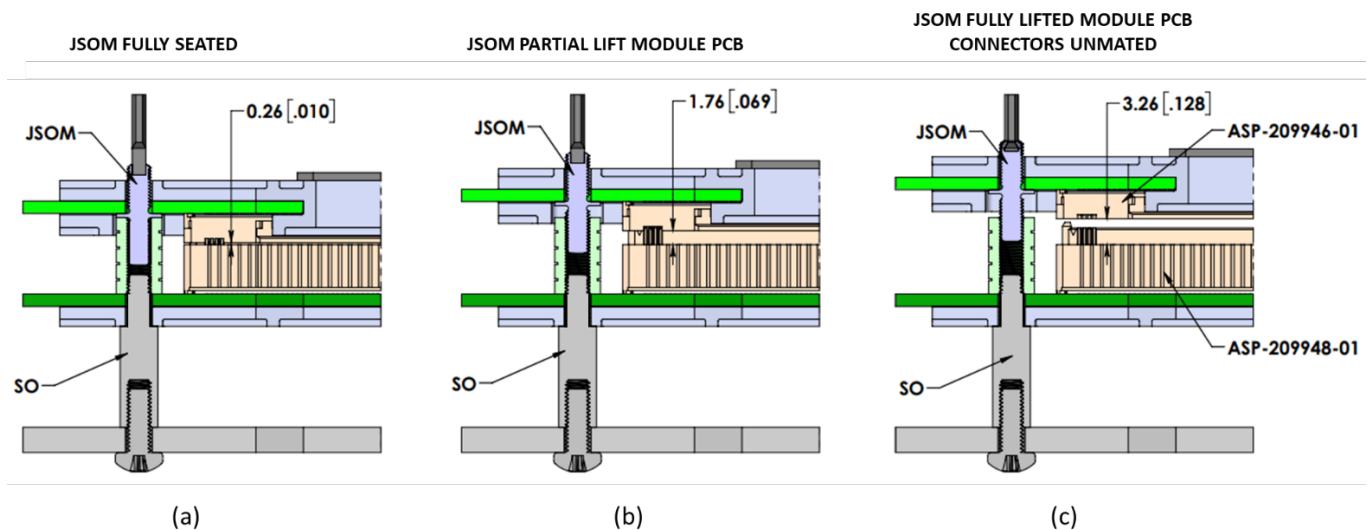

| Figure 69: COM-HPC Stack Dis-assembly Procedure Using JSOM Hardware.....                                    | 141 |

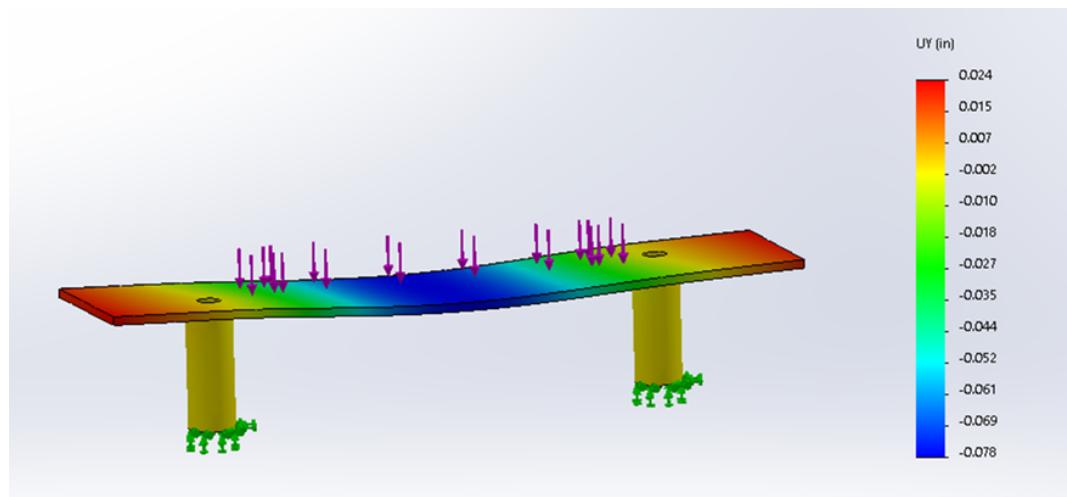

| Figure 70: FEM Simulation Results – 0.0625" FR4 Carrier – No Stiffener.....                                 | 142 |

| Figure 71: Mechanical Carrier Stiffener Possibility.....                                                    | 143 |

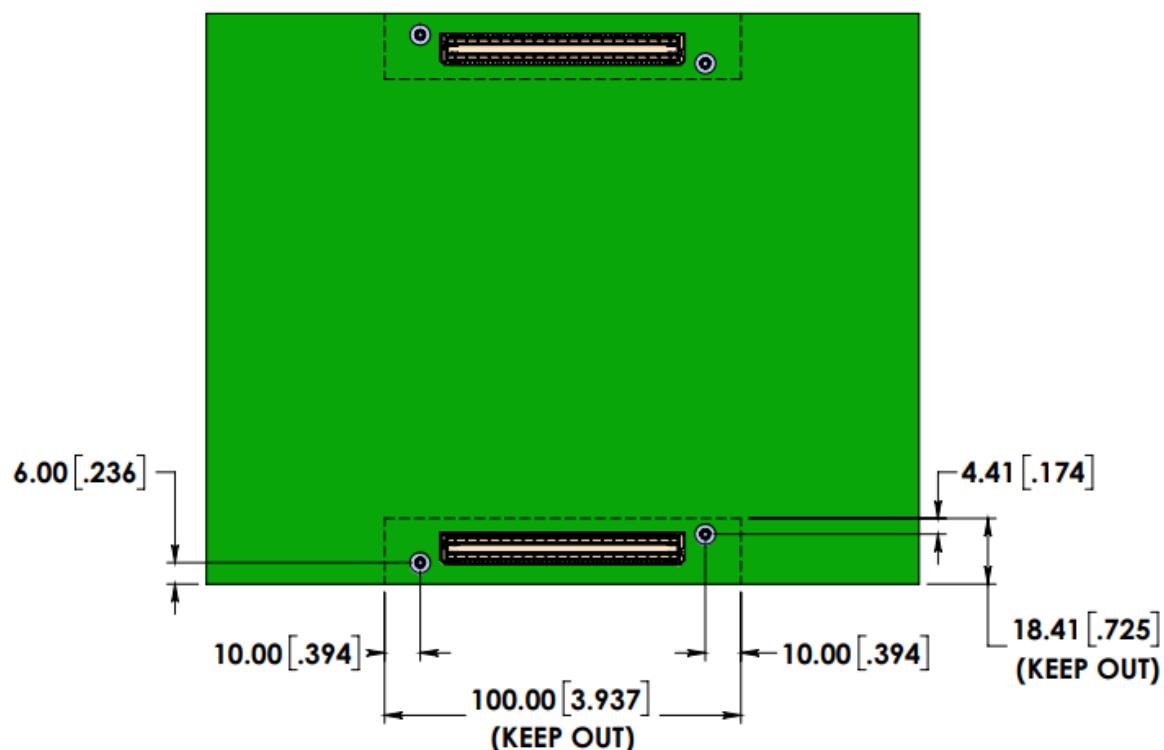

| Figure 72: Carrier Board Stiffener Keep-Out Region (Seen Through Carrier).....                              | 144 |

| Figure 73: Application Specific Part Number (ASP) Reference Guide.....                                      | 145 |

| Figure 74: Synchronous Ethernet Overview.....                                                               | 147 |

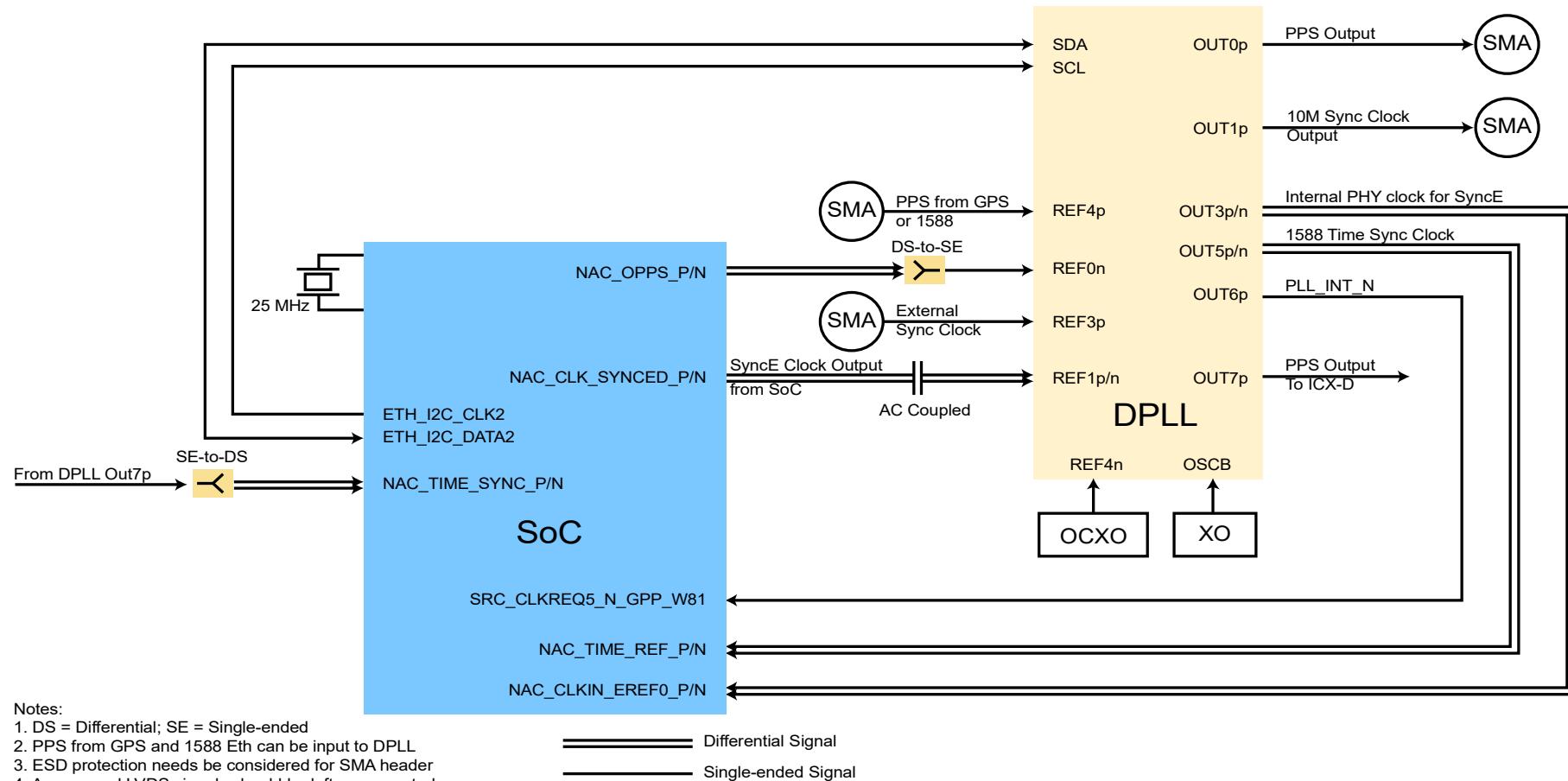

| Figure 75: Synchronous Ethernet Example Implementation.....                                                 | 148 |

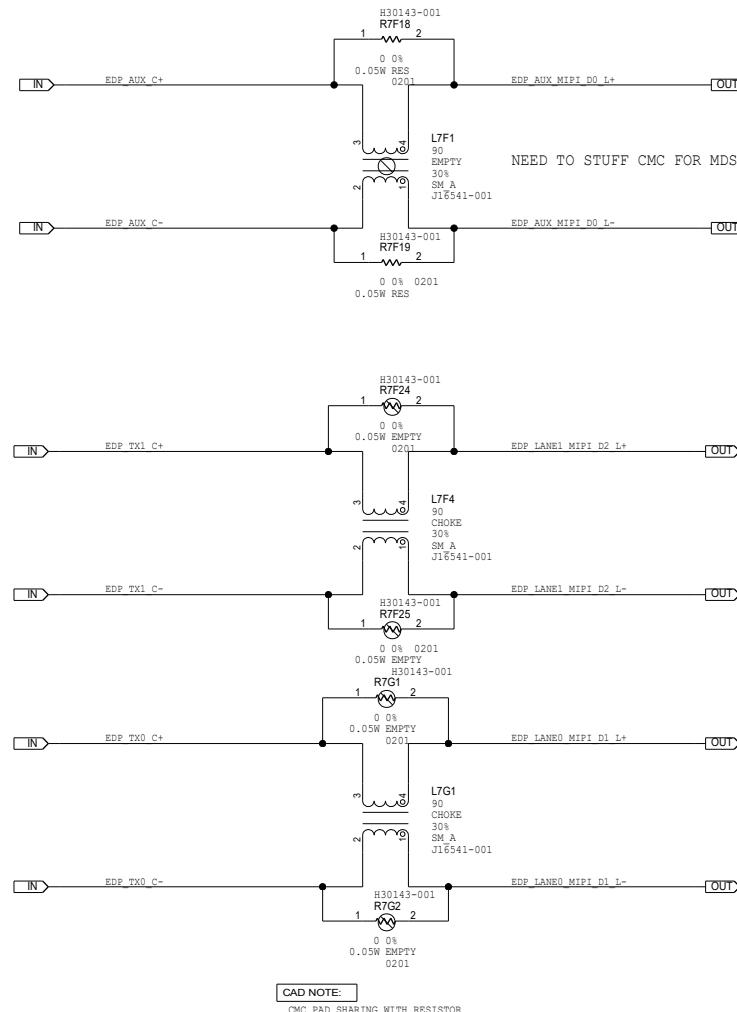

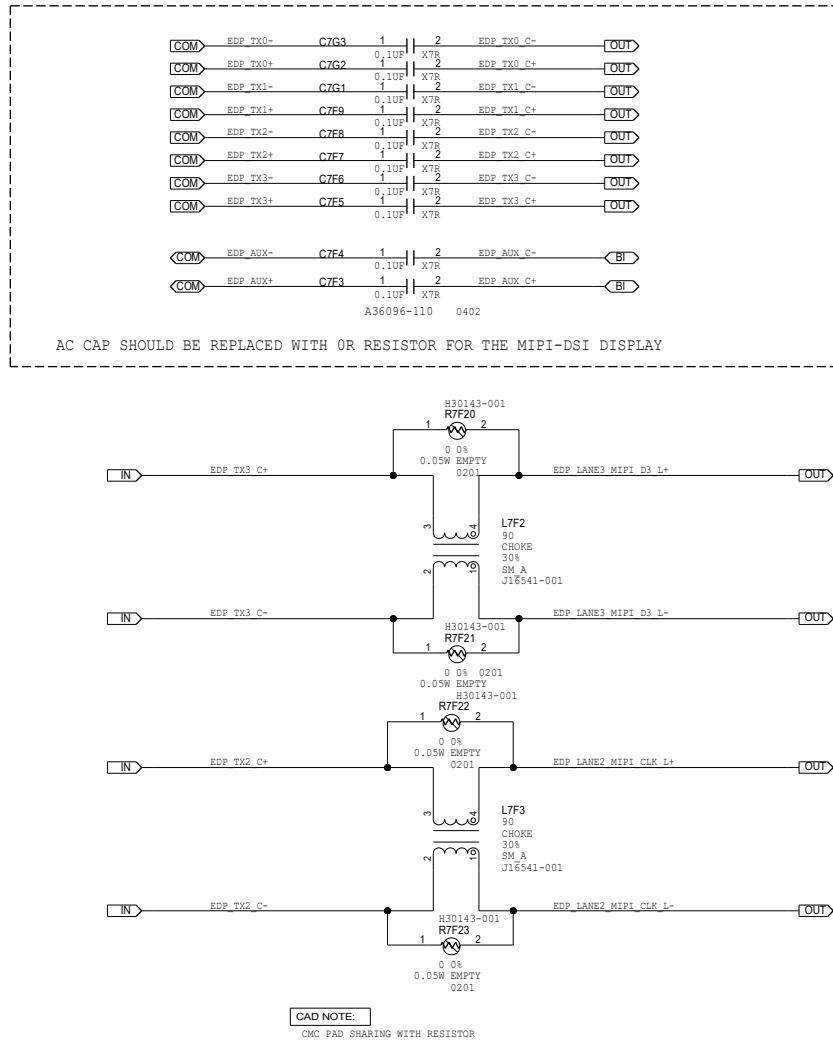

| Figure 76: Alternative eDP Example (Sheet 1 of 6): Passive Stuffing Options – eDP and DSI.....              | 151 |

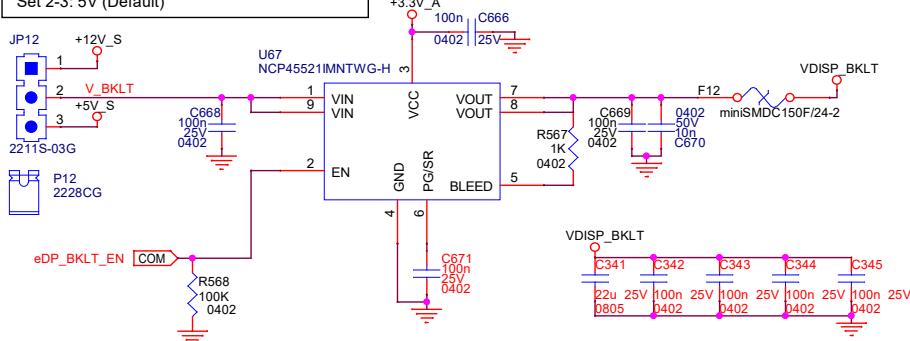

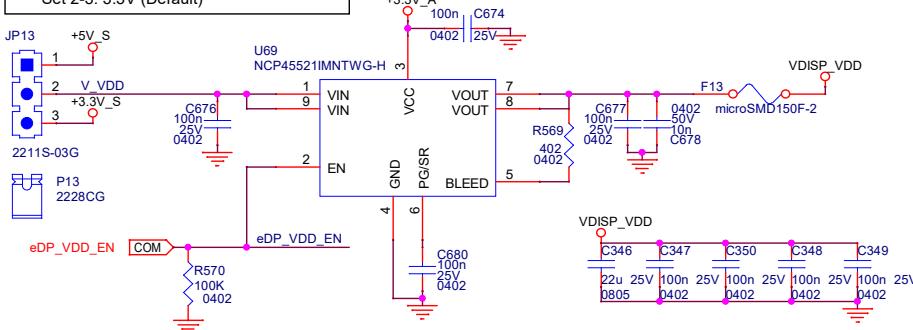

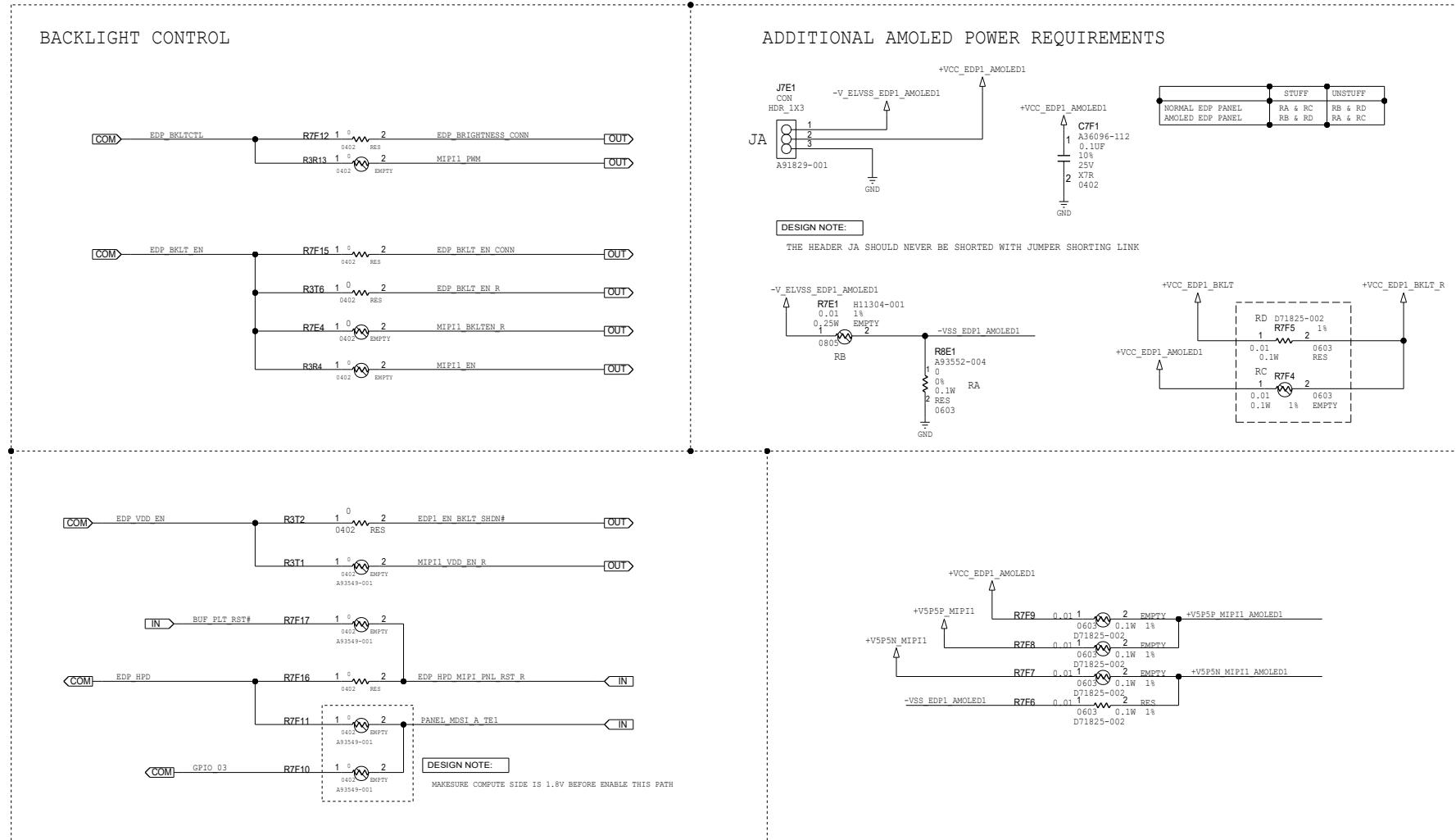

| Figure 77: Alternative eDP Example (Sheet 2 of 6): Backlight Control Options.....                           | 152 |

| Figure 78: Alternative eDP Example (Sheet 3 of 6): Connector to Display Panel Assembly.....                 | 153 |

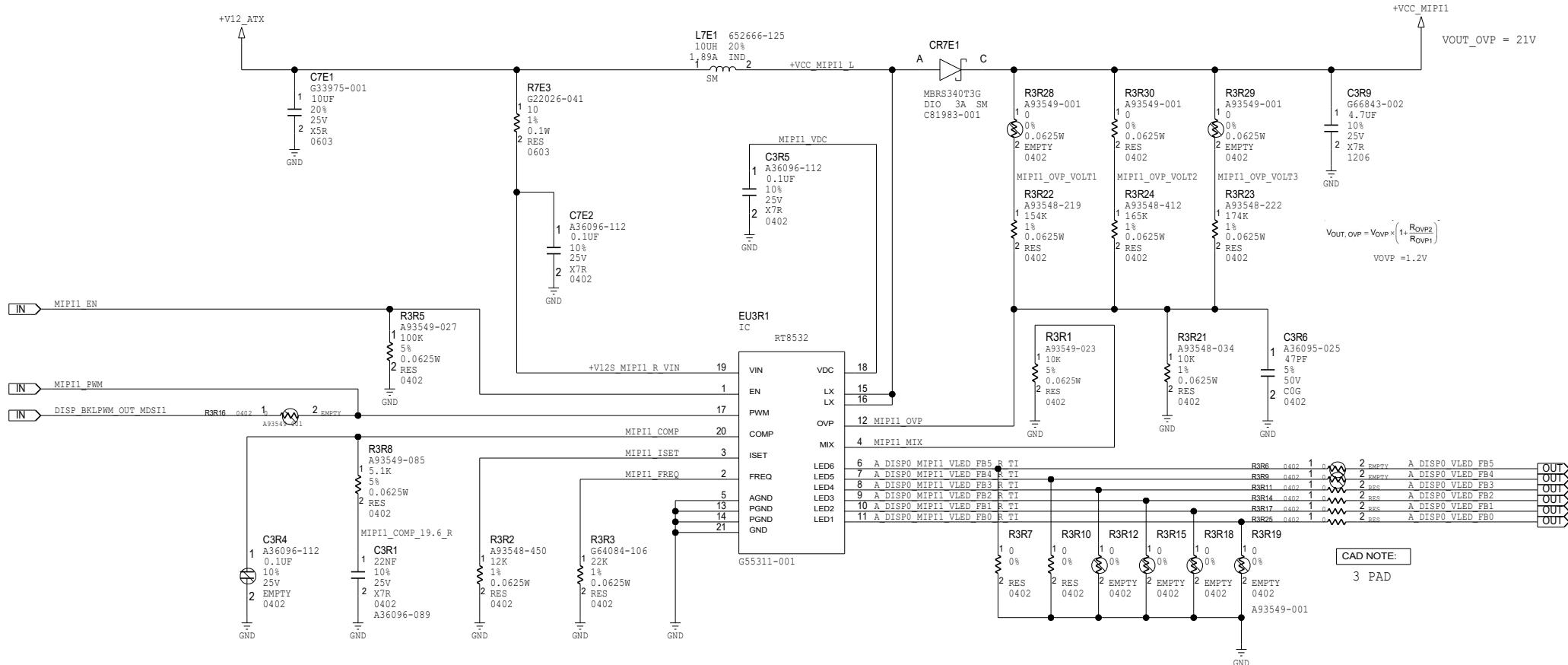

| Figure 79: Alternative eDP Example (Sheet 4 of 6): Backlight LED Driver.....                                | 154 |

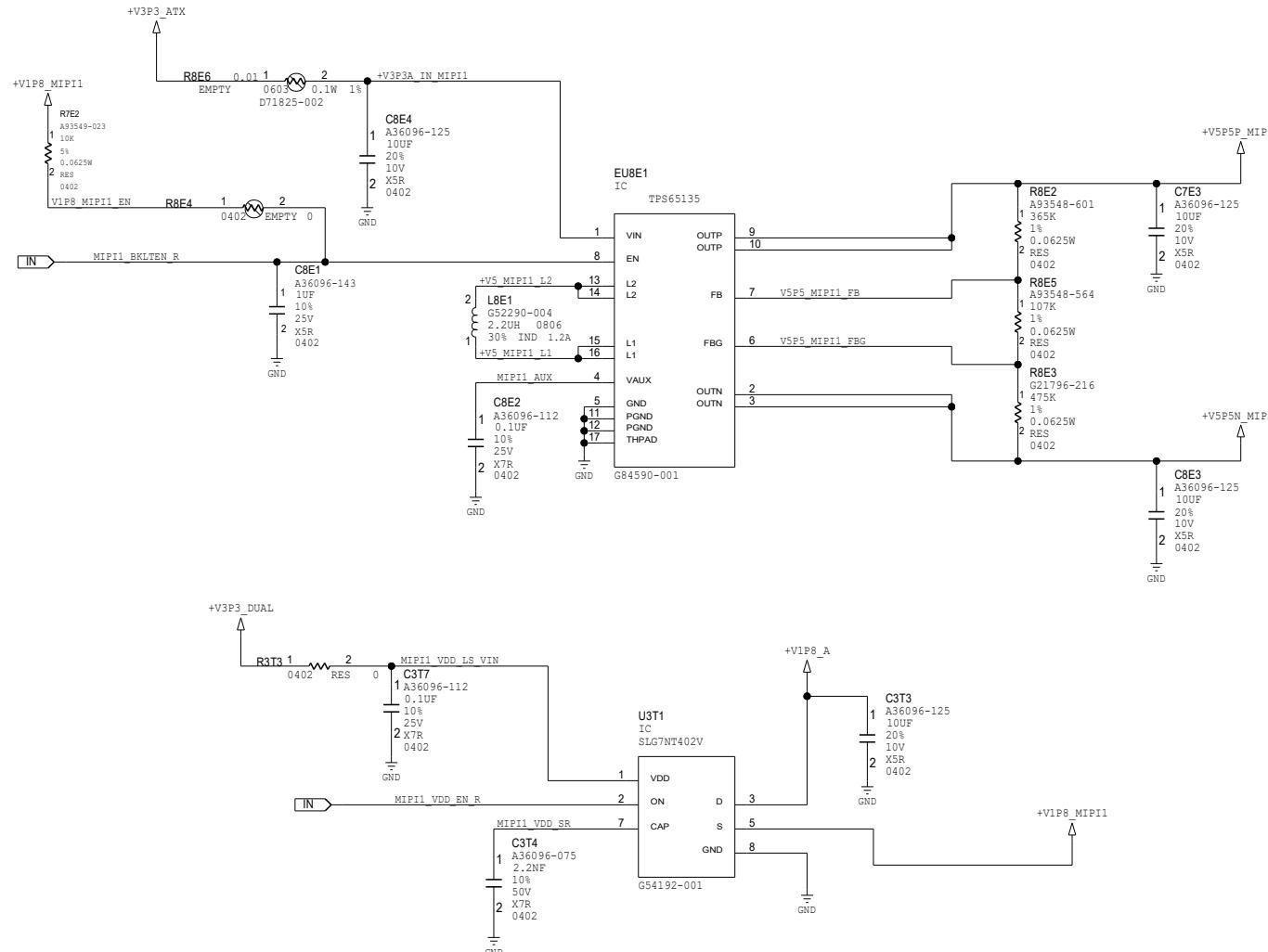

| Figure 80: Alternative eDP Example (Sheet 5 of 6): Split Rail (Pos / Neg) PS for AMOLED.....                | 155 |

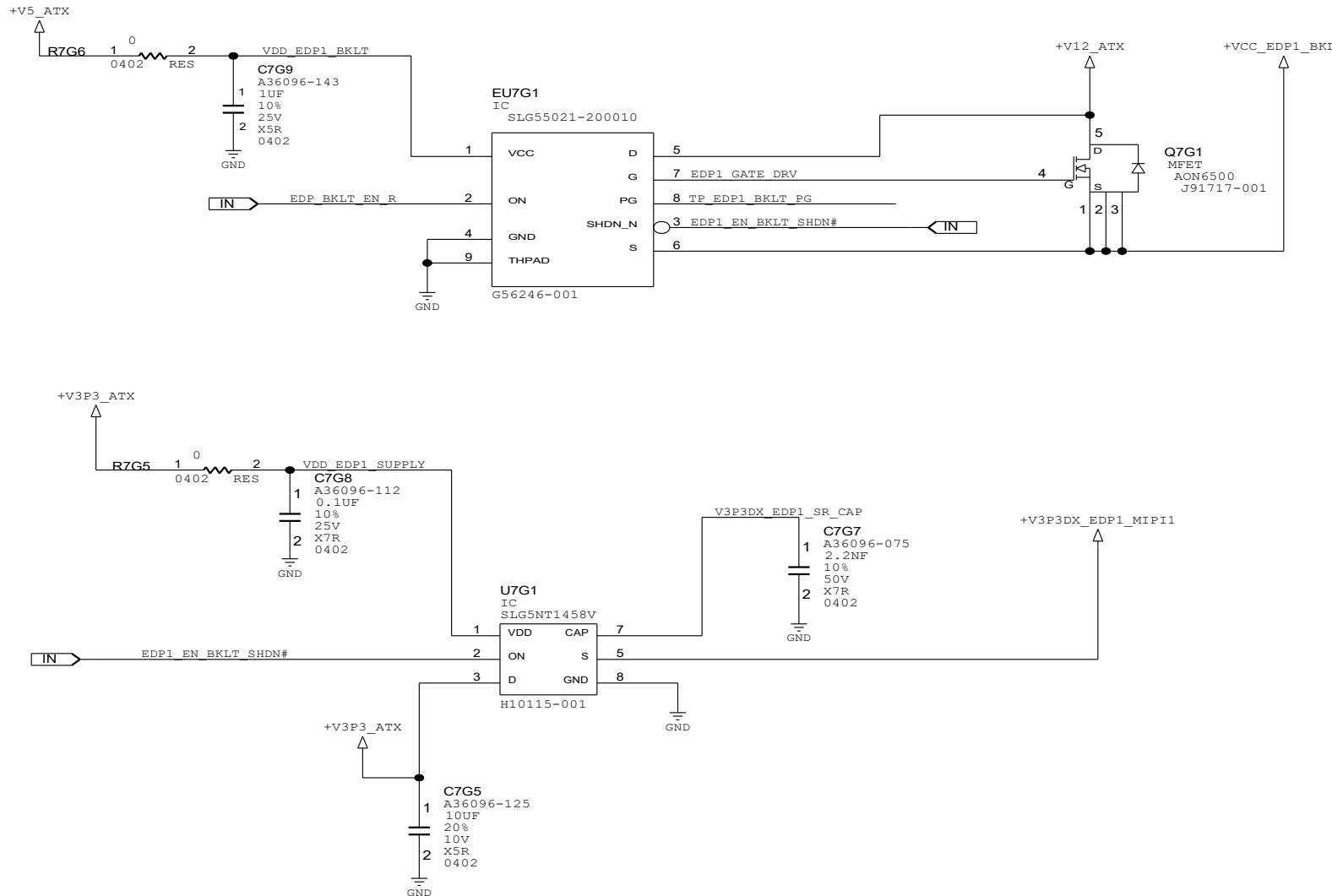

| Figure 81: Alternative eDP Example (Sheet 6 of 6): High Side Gate Driver for eDP Backlight.....             | 156 |

| Figure 82: eSPI Header Example.....                                                                         | 157 |

# 1. Preface

---

## 1.1. About This Document

This document provides information for designing project specific Carrier Boards for systems using COM-HPC Modules. This document is a design guide and not a specification document. It should be used together with the **COM-HPC Base Specification**, with other industry specifications (listed in Section 1.9. below), with silicon and component vendor's documentation and with your COM-HPC Module vendor's product documentation.

The PICMG **COM Express Carrier Board Design Guide** is also a very useful additional source of information. The COM-HPC and COM Express pin names are not the same, but it is not hard to correlate them. The COM Express design guide document is available for free download on the public PICMG website ([www.picmg.org](http://www.picmg.org)). No membership is required to download the design guides.

## 1.2. Intended Audience

This design guide is intended for electronics engineers and PCB layout engineers designing Carrier Boards for PICMG COM-HPC Modules. It may also be useful to COM-HPC Module designers for them to better understand how COM-HPC Modules are used, and to understand how some of the design rules (trace length recommendations, trace length matching recommendations etc.) are shared between Module and Carrier designs.

## 1.3. No Special Word Usage

Unlike a PICMG specification, which assigns special meanings to certain words such as "shall", "should" and "may", there is no such usage in this document. That is because this document is not a specification; it is a non-normative design guide.

## 1.4. No Statements of Compliance

As this document is not a specification but a set of guidelines, there should not be any statements of compliance made with reference to this document.

## 1.5. Correctness Disclaimer

The schematic examples given in this document are believed to be correct but no guarantee is given.

## 1.6. Name and Logo Usage

The PCI Industrial Computer Manufacturers Group policies regarding the use of its logos and trademarks are as follows:

Permission to use the PICMG® organization logo is automatically granted to designated members only as stipulated on the most recent Membership Privileges document (available at [www.picmg.org](http://www.picmg.org)) during the period of time for which their membership dues are paid. Nonmembers may not use the PICMG® organization logo.

---

The PICMG® organization logo must be printed in black or color as shown in the files available for download from the member's side of the Web site. Logos with or without the "Open Modular Computing Specifications" banner can be used. Nothing may be added or deleted from the PICMG® logo.

The use of the COM-HPC® logo is a privilege granted by the PICMG® organization to companies who have purchased the relevant specifications (or acquired them as a member benefit), and that believe their products comply with these specifications. Manufacturers' distributors and sales representatives may use the COM-HPC® logo in promoting products sold under the name of the manufacturer. Use of the logos by either members or non-members implies such compliance. Only PICMG Executive and Associate members may use the PICMG® logo. PICMG® may revoke permission to use logos if they are misused. The COM-HPC® logo can be found on the PICMG web site, [www.picmg.org](http://www.picmg.org).

The COM-HPC® logo must be used exactly as shown in the files available for download from the PICMG® Web site. The aspect ratios of the logos must be maintained, but the sizes may be varied. Nothing may be added to or deleted from the COM-HPC® logo.

The PICMG® name and logo and the COM-HPC® name and logo are registered trademarks of PICMG®. Registered trademarks must be followed by the ® symbol, and the following statement must appear in all published literature and advertising material in which the logo appears:

PICMG, the COM-HPC® name and logo and the PICMG logo are registered trademarks of the PCI Industrial Computers Manufacturers Group.

## 1.7. Intellectual Property

The PICMG Consortium draws attention to the fact that it is claimed that compliance with this specification may involve the use of a patent claim(s) ("IPR"). The PICMG Consortium takes no position concerning the evidence, validity or scope of this IPR.

The holder of this IPR has assured the Consortium that it is willing to license or sublicense all such IPR to those licensees (Members and non-Members alike) desiring to implement this specification. The statement of the holder of this IPR to such effect has been filed with the Consortium.

Attention is also drawn to the possibility that some of the elements of this specification may be the subject of IPR other than those identified below. The Consortium shall not be responsible for identifying any or all such IPR.

No representation is made as to the availability of any license rights for use of any IPR inherent in this specification for any purpose other than to implement this specification.

This specification conforms to the current PICMG® Intellectual Property Rights Policy and the Policies and Procedures for Specification Development and does not contain any known intellectual property that is not available for licensing under Reasonable and Non-discriminatory terms. In the course of Membership Review the following disclosures were made:

### 1.7.1. Necessary IPR Claims (Referring to Mandatory or Recommended Features)

Samtec Inc. has the following patents, which may cover some aspects of the PICMG® COM-HPC® Module and Carrier Board Connectors. Contact Samtec Inc. at [royalties@samtec.com](mailto:royalties@samtec.com) for further information.

China 202111274151.2

China 201921051845.8

China 202030159171.5

EPO 007814686-0001

EPO 007814686-0002

EPO 007814686-0003

EPO 007814686-0004

EPO 19830502.1

Taiwan 109138672

Taiwan M589915

Taiwan D209464

Taiwan 109304816

US 29/709518

### 1.7.2. Unnecessary Claims (Referring to Optional Features or Non-normative Elements)

US 9374900

CN 201480061913.2

TWM 505072

PCT 2021207390

TW 110112769

CN 11566924

US 17/817659

### 1.7.3. Third Party Disclosures

(Note that third party IPR submissions do not contain any claim of willingness to license the IPR.)

- US 10,404,014 B2, FCI USA LLC, Sep. 3, 2019, “STACKING ELECTRICAL CONNECTOR WITH REDUCED CROSS TALK”

Refer to PICMG® IPR Policies and Procedures and the company owner of the patent for terms and conditions of usage.

PICMG® makes no judgment as to the validity of these claims or the licensing terms offered by the claimants.

THIS SPECIFICATION IS BEING OFFERED WITHOUT ANY WARRANTY WHATSOEVER, AND IN PARTICULAR, ANY WARRANTY OF NON-INFRINGEMENT IS EXPRESSLY DISCLAIMED. ANY USE OF THIS SPECIFICATION SHALL BE MADE ENTIRELY AT THE IMPLEMENTER'S OWN RISK, AND NEITHER THE CONSORTIUM, NOR ANY OF ITS MEMBERS OR SUBMITTERS, SHALL HAVE ANY LIABILITY WHATSOEVER TO ANY IMPLEMENTER OR THIRD PARTY FOR ANY DAMAGES OF ANY NATURE WHATSOEVER, DIRECTLY OR INDIRECTLY, ARISING FROM THE USE OF THIS SPECIFICATION.

Compliance with this specification does not absolve manufacturers of COM-HPC® equipment from the requirements of safety and regulatory agencies (UL, CSA, FCC, IEC, etc.).

PICMG®, CompactPCI®, AdvancedTCA®, ATCA®, AdvancedMC®, CompactPCI® Express, COM Express®, COM-HPC®, MicroTCA®, SHB Express®, and the PICMG, CompactPCI, AdvancedTCA, μTCA and ATCA logos are registered trademarks, and xTCA™, IRTM™ and the IRTM logo are trademarks of the PCI Industrial Computer Manufacturers Group. All other brand or product names may be trademarks or registered trademarks of their respective holders.

### 1.7.4. Copyright Notice

© 2021, 2022, 2023 PICMG. All rights reserved. All text, pictures and graphics are protected by copyrights. No copying is permitted without written permission from PICMG.

PICMG has made every attempt to ensure that the information in this document is accurate yet the information contained within is supplied “as-is”.

### 1.7.5. Trademarks

Intel is a registered trademark of Intel Corporation. PCI Express is a registered trademark of Peripheral Component Interconnect Special Interest Group (PCI-SIG). COM-HPC® is a registered trademark of PCI Industrial Computer Manufacturers Group (PICMG). I2C is a registered trademark of NXP Semiconductors. Samtec is a registered trademark of Samtec Inc. All product names and logos referenced in this document are property of their owners. Thunderbolt is a registered trademark of the Intel corporation. Accelerate is a trademark of Samtec Inc.

## 1.8. Acronyms, Abbreviations and Definitions Used

**Table 1: Acronyms, Abbreviations and Definitions Used**

| Term                            | Definition                                                                                                                                                                                                                                                                    |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>10GBASE-KR</b>               | 10 Gbps internal copper interface. Operates over a single lane and uses the same physical layer coding (defined in IEEE 802.3 Clause 49) as 10GBASE-LR (Single Mode Fiber 1310 nm) / ER (Single Mode Fiber 1550 nm) /SR (Multi Mode Fiber 850 nm)                             |

| <b>25GBASE-KR</b>               | 25 Gb/s internal copper interface using 25GBASE-R encoding over one lane in each direction                                                                                                                                                                                    |

| <b>AC Coupled</b>               | This term means that series capacitors are inserted in the differential pair lines. This allows the transmit and receive lines to have their own, possibly separate DC common mode voltages.                                                                                  |

| <b>ACPI</b>                     | Advanced Configuration Power Interface                                                                                                                                                                                                                                        |

| <b>AMOLED</b>                   | Active Matrix Organic (semiconductor) Light Emitting Diode (a flat panel display technology)                                                                                                                                                                                  |

| <b>ARM</b>                      | Advanced RISC Machine – a low power alternative CPU architecture widely used in mobile and embedded systems                                                                                                                                                                   |

| <b>ATX</b>                      | Advanced Technology Extended – Industry standard PC Motherboard form factor and power supply definitions                                                                                                                                                                      |

| <b>BIDIR</b>                    | Bidirectional (in reference to electrical signals)                                                                                                                                                                                                                            |

| <b>BIOS</b>                     | Basic Input Output System                                                                                                                                                                                                                                                     |

| <b>BMC</b>                      | Baseboard Management Controller or Board Management Controller – located on Carrier for COM-HPC, if implemented                                                                                                                                                               |

| <b>Carrier Board</b>            | An application specific circuit board that accepts a COM-HPC Module                                                                                                                                                                                                           |

| <b>CCC</b>                      | Current Carrying Capability                                                                                                                                                                                                                                                   |

| <b>DDI</b>                      | Digital Display Interface – an interface that can serve DisplayPort and HDMI/DVI,                                                                                                                                                                                             |

| <b>DIMM</b>                     | Dual In-line Memory Module – larger format SDRAM memory module used in desk top systems and server PCs                                                                                                                                                                        |

| <b>DisplayPort DP</b>           | DisplayPort is a digital display interface standard put forth by the Video Electronics Standards Association (VESA). It defines a new license free, royalty free, digital audio/video interconnect, intended to be used primarily between a computer and its display monitor. |

| <b>DPLL</b>                     | Digital Phase Locked Loop                                                                                                                                                                                                                                                     |

| <b>DRAM</b>                     | Dynamic Random Access Memory                                                                                                                                                                                                                                                  |

| <b>DVI</b>                      | Digital Visual Interface - a Digital Display Working Group (DDWG) standard that defines a standard video interface supporting both digital and analog video signals. The digital signals use TMDS.                                                                            |

| <b>EAPI</b>                     | Embedded Application Programming Interface                                                                                                                                                                                                                                    |

| <b>EC</b>                       | Embedded Controller                                                                                                                                                                                                                                                           |

| <b>ECN</b>                      | Engineering Change Notice                                                                                                                                                                                                                                                     |

| <b>EEPROM</b>                   | Electrically Erasable Programmable Read-Only Memory                                                                                                                                                                                                                           |

| <b>Embedded DisplayPort eDP</b> | Embedded DisplayPort (eDP) is a digital display interface standard defined by the Video Electronics Standards Association (VESA) for digital interconnect of Audio and Video within a closed system such as a laptop computer or a piece of laboratory instrumentation.       |

| <b>ESD</b>                      | Electro Static Discharge                                                                                                                                                                                                                                                      |

| <b>eSPI</b>                     | Enhanced Serial Peripheral Interface                                                                                                                                                                                                                                          |

| <b>FAE</b>                      | Field Application Engineer                                                                                                                                                                                                                                                    |

| <b>Flash</b>                    | EEPROM memory used for code storage. It can be updated in place ("flashed").                                                                                                                                                                                                  |

| <b>FPGA</b>                     | Field Programmable Gate Array                                                                                                                                                                                                                                                 |

| <b>FR4</b>                      | A type of fiber-glass laminate commonly used for printed circuit boards.                                                                                                                                                                                                      |

| <b>Gb</b>                       | Gigabit                                                                                                                                                                                                                                                                       |

| <b>GbE</b>                      | Gigabit Ethernet                                                                                                                                                                                                                                                              |

| <b>Gbps</b>                     | Gigabits per second                                                                                                                                                                                                                                                           |

| <b>GPI</b>                      | General Purpose Input                                                                                                                                                                                                                                                         |

| <b>GPS</b>                      | Global Positioning System                                                                                                                                                                                                                                                     |

| <b>GPIO</b>                     | General Purpose Input Output                                                                                                                                                                                                                                                  |

| <b>GPO</b>                      | General Purpose Output                                                                                                                                                                                                                                                        |

| <b>GPU</b>                      | Graphics Processing Unit                                                                                                                                                                                                                                                      |

| Term                     | Definition                                                                                                                                                                                                                                                                                 |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Gtps, GT/sec</b>      | Giga Transfers per Second                                                                                                                                                                                                                                                                  |

| <b>HDA</b>               | Intel High Definition Audio (HD Audio) refers to the specification released by Intel in 2004 for delivering high definition audio.                                                                                                                                                         |

| <b>HDMI</b>              | High Definition Multimedia Interface – digital display interface widely used in consumer electronics such as digital TVs                                                                                                                                                                   |

| <b>I2C</b>               | Inter Integrated Circuit – 2 wire (clock and data) signaling scheme allowing communication between integrated circuits, primarily used to read and load register values.                                                                                                                   |

| <b>I2S</b>               | Inter IC Sound – a 5 wire serial data interface, used primarily for transmitting and receiving digital audio data                                                                                                                                                                          |

| <b>I3C</b>               | Improved Inter Integrated Circuit – builds on I2C and offers higher speeds and in-band interrupts                                                                                                                                                                                          |

| <b>IPMB</b>              | Intelligent Platform Management Bus                                                                                                                                                                                                                                                        |

| <b>IPMI</b>              | Intelligent Platform Management Interface                                                                                                                                                                                                                                                  |

| <b>IPR</b>               | Intellectual Property Rights                                                                                                                                                                                                                                                               |

| <b>LAN</b>               | Local Area Network                                                                                                                                                                                                                                                                         |

| <b>Legacy Device</b>     | Relics from the PC-AT computer that are not in use in contemporary PC systems: primarily the ISA bus, UART-based serial ports, parallel printer ports, PS-2 keyboards, and mice. Definitions vary as to what constitutes a legacy device. Some definitions include IDE as a legacy device. |

| <b>LPC</b>               | Low Pin-Count Interface: a low speed interface used for peripheral circuits such as Super I/O controllers, which typically combine legacy-device support into a single IC.                                                                                                                 |

| <b>LS</b>                | Least Significant                                                                                                                                                                                                                                                                          |

| <b>M.2</b>               | A small form factor add in card, for storage, WiFi, Cell Modems, etc. Interface options include PCIe x1, x2 or x4, SATA, USB and asynchronous serial. The standard is maintained by the PCI-SIG.                                                                                           |

| <b>MAC</b>               | Media Access Control – in this document, MAC refers to the physical hardware bridge device between a CPU interface such as PCIe, and a network interface such as MDI or 10GBASE-KR or many others. A PHY is needed between the MAC and the Ethernet physical layer                         |

| <b>MAFS</b>              | Term for Master Attached Flash Sharing where the Flash component is attached to the processor interface.                                                                                                                                                                                   |

| <b>MDI</b>               | Media Dependent Interface between a Ethernet PHY and the system magnetics and copper twisted pairs                                                                                                                                                                                         |

| <b>MDIO</b>              | Management Data Input/Output, or MDIO, is a 2-wire serial bus that is used to manage PHYs or physical layer devices in media access controllers (MACs).                                                                                                                                    |

| <b>ME</b>                | Management Engine – Intel term for a management microcontroller embedded into the chipset silicon. It is active before the main x86 CPU boots.                                                                                                                                             |

| <b>MIPI</b>              | Industry trade group that sets standards for mobile devices                                                                                                                                                                                                                                |

| <b>MMC</b>               | Module Management Controller – a small microcontroller on the Module that works in conjunction with a Carrier BMC to implement IPMI functions. Implementation is optional.                                                                                                                 |

| <b>MS</b>                | Most Significant                                                                                                                                                                                                                                                                           |

| <b>NA or N/A</b>         | Not Available, Not Applicable                                                                                                                                                                                                                                                              |

| <b>NBASE-KR</b>          | Ethernet back plane signaling on PCB differential pairs. 'N' signifies the speed – 25Gbps or 10Gbps                                                                                                                                                                                        |

| <b>NBASE-T</b>           | Ethernet physical layer signaling on twisted pairs. 'N' signifies the speed – 10Gbps, 5Gbps, 2.5Gbps, 1Gbps, 100Mbps or 10Mbps                                                                                                                                                             |

| <b>NC</b>                | No Connect                                                                                                                                                                                                                                                                                 |

| <b>NDA</b>               | Non-Disclosure Agreement                                                                                                                                                                                                                                                                   |

| <b>Nyquist Frequency</b> | The critical frequency, sometimes called the “folding frequency”, for a digital sampling system. It is (usually) $\frac{1}{2}$ of the maximum data rate for the system.                                                                                                                    |

| <b>NVME</b>              | Non Volatile Memory Express - non volatile memory with a PCIe interface – x1, x2 or x4 – often in an M.2 card form factor                                                                                                                                                                  |

| <b>OCXO</b>              | Oven Controlled Xtal (crystal) Oscillator                                                                                                                                                                                                                                                  |

| <b>OEM</b>               | Original Equipment Manufacturer                                                                                                                                                                                                                                                            |

| <b>OTP</b>               | One Time Programmable – an option offered by some silicon vendors to change IC parameters by programming or blowing device fuses once, before shipment.                                                                                                                                    |

| <b>PC-AT</b>             | “Personal Computer – Advanced Technology” – an IBM trademark term used to refer to Intel x86 based personal computers in the 1990s                                                                                                                                                         |

| <b>PCB</b>               | Printed Circuit Board                                                                                                                                                                                                                                                                      |

| <b>PCI</b>               | Peripheral Component Interconnect                                                                                                                                                                                                                                                          |

| Term                              | Definition                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>PCI Express</b><br><b>PCIe</b> | Peripheral Component Interconnect Express – serialized point-to-point version of PCI                                                                                                                                                                                                                                                                                                                                         |

| <b>PEG</b>                        | PCI Express Graphics                                                                                                                                                                                                                                                                                                                                                                                                         |

| <b>PHY</b>                        | Physical layer device, usually used in the context of                                                                                                                                                                                                                                                                                                                                                                        |

| <b>Pin-out Type</b>               | A reference to one of eight COM Express® or COM-HPC definitions for the signals that appear on the COM Express® Module connector pins.                                                                                                                                                                                                                                                                                       |

| <b>PMD</b>                        | Physical Medium Dependent – the physical layer of computer network protocols                                                                                                                                                                                                                                                                                                                                                 |

| <b>POR</b>                        | Plan of Record                                                                                                                                                                                                                                                                                                                                                                                                               |

| <b>PPS</b>                        | Pulse Per Second (for Ethernet)                                                                                                                                                                                                                                                                                                                                                                                              |

| <b>PTP</b>                        | Precision Time Protocol (for Ethernet)                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>PU</b><br><b>PD</b>            | Pull Up      A connection between a signal and a specified power rail, through a resistor<br>Pull Down                                                                                                                                                                                                                                                                                                                       |

| <b>R<sub>a</sub></b>              | Roughness Average – a measure of surface roughness, expressed in units of length.                                                                                                                                                                                                                                                                                                                                            |

| <b>ROM</b>                        | Read Only Memory – a legacy term – often the device referred to as a ROM can actually be written to, in a special mode. Such writable ROMs are sometimes called Flash ROMs. BIOS is stored in ROM or Flash ROM.                                                                                                                                                                                                              |

| <b>RSVD</b>                       | Reserved. If a pin is marked RSVD, nothing should be connected to it                                                                                                                                                                                                                                                                                                                                                         |

| <b>RTC</b>                        | Real Time Clock – battery backed circuit in PC-AT systems that keeps system time and date                                                                                                                                                                                                                                                                                                                                    |

| <b>S0, S1, S2, S3, S4, S5</b>     | System states describing the power and activity level<br>S0                      Full power, all devices powered<br>S1                      CPU powered, CPU and bus clocks off, not in common use<br>S2<br>S3 Suspend to RAM      System context stored in RAM; RAM is in standby<br>S4 Suspend to Disk      System context stored on disk<br>S5 Soft Off              Main power rail off, only standby power rail present |

| <b>SAFS</b>                       | Term for Slave Attached Flash Sharing where the Flash component is attached behind a BMC component.                                                                                                                                                                                                                                                                                                                          |

| <b>SATA</b>                       | Serial Advanced Technology Attachment: serial-interface standard for hard disks                                                                                                                                                                                                                                                                                                                                              |

| <b>SDP</b>                        | Software Definable Pin                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>SKU</b>                        | Stock Control Unit (a part number for a specific stockable item)                                                                                                                                                                                                                                                                                                                                                             |

| <b>SGMII</b>                      | Serial Gigabit Media Independent Interface                                                                                                                                                                                                                                                                                                                                                                                   |

| <b>SMA</b>                        | Sub Miniature type A – a small form factor circular connector used for miniature coax cables, for WiFi, GPS and Cell Modem antennas                                                                                                                                                                                                                                                                                          |

| <b>SMBus</b>                      | System Management Bus – a 3 wire bus – clock, data and alert – based in I2C – for system management                                                                                                                                                                                                                                                                                                                          |

| <b>SOC</b>                        | System On Chip                                                                                                                                                                                                                                                                                                                                                                                                               |

| <b>SO-DIMM</b>                    | Small Outline Dual In-line Memory Module – small form factor SDRAM module                                                                                                                                                                                                                                                                                                                                                    |

| <b>SPD</b>                        | Serial Presence Detect – refers to serial EEPROM on DRAMs that has DRAM Module configuration information                                                                                                                                                                                                                                                                                                                     |

| <b>SPI</b>                        | Serial Peripheral Interface                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>Super I/O</b>                  | An integrated circuit, typically interfaced via the LPC or eSPI bus that provides legacy PC I/O functions including PS2 keyboard and mouse ports, serial and parallel port(s) and a floppy interface.                                                                                                                                                                                                                        |

| <b>TFT</b>                        | Thin Film Transistor – refers to technology used in active matrix flat-panel displays, in which there is one thin film transistor per display pixel.                                                                                                                                                                                                                                                                         |

| <b>TMDS</b>                       | Transition Minimized Differential Signaling - a digital signaling protocol between the graphics subsystem and display. TMDS is used for the DVI digital signals.                                                                                                                                                                                                                                                             |

| <b>TPM</b>                        | Trusted Platform Module, chip to enhance the security features of a computer system.                                                                                                                                                                                                                                                                                                                                         |

| <b>USB</b>                        | Universal Serial Bus                                                                                                                                                                                                                                                                                                                                                                                                         |

| <b>WDT</b>                        | Watch Dog Timer.                                                                                                                                                                                                                                                                                                                                                                                                             |

| <b>XAU</b>                        | 10 Gbps Attachment Unit Interface.                                                                                                                                                                                                                                                                                                                                                                                           |

| <b>XGMII</b>                      | 10 Gbps Media Independent Interface                                                                                                                                                                                                                                                                                                                                                                                          |

| <b>XO</b>                         | Xtal (crystal) Oscillator                                                                                                                                                                                                                                                                                                                                                                                                    |

## 1.9. Applicable Documents and Standards

The list below is a partial list of documents and standards applicable to COM-HPC®. Many of the standards groups listed below (MIPI, PCI-SIG, USB, VESA etc.) have much more additional information available – ECNs, supplemental documents, test specifications, SI masks etc. These are too numerous to list here. Please explore the links below for additional documents that may be relevant.