# User Manual

## **PCIE-1842** **PCIE-1842L**

**8/4-ch, 14-bit, 10MS/s/ch

Simultaneous Analog Input PCI

Express DAQ Card**

**ADVANTECH**

*Enabling an Intelligent Planet*

## Copyright

The documentation and the software included with this product are copyrighted 2025 by Advantech Co., Ltd. All rights are reserved. Advantech Co., Ltd. reserves the right to make improvements in the products described in this manual at any time without notice. No part of this manual may be reproduced, copied, translated, or transmitted in any form or by any means without the prior written permission of Advantech Co., Ltd. The information provided in this manual is intended to be accurate and reliable. However, Advantech Co., Ltd. assumes no responsibility for its use, nor for any infringements of the rights of third parties that may result from its use.

## Acknowledgments

Intel and Pentium are trademarks of Intel Corporation.

Microsoft Windows and MS-DOS are registered trademarks of Microsoft Corp.

All other product names or trademarks are properties of their respective owners.

## Product Warranty (2 years)

Advantech warrants the original purchaser that each of its products will be free from defects in materials and workmanship for two years from the date of purchase.

This warranty does not apply to any products that have been repaired or altered by persons other than repair personnel authorized by Advantech, or products that have been subject to misuse, abuse, accident, or improper installation. Advantech assumes no liability under the terms of this warranty as a consequence of such events.

Because of Advantech's high quality-control standards and rigorous testing, most customers never need to use our repair service. If an Advantech product is defective, it will be repaired or replaced free of charge during the warranty period. For out-of-warranty repairs, customers will be billed according to the cost of replacement materials, service time, and freight. Please consult your dealer for more details.

If you believe your product to be defective, follow the steps outlined below.

1. Collect all the information about the problem encountered. (For example, CPU speed, Advantech products used, other hardware and software used, etc.) Note anything abnormal and list any onscreen messages displayed when the problem occurs.

2. Call your dealer and describe the problem. Please have your manual, product, and any helpful information readily available.

3. If your product is diagnosed as defective, obtain a return merchandise authorization (RMA) number from your dealer. This allows us to process your return more quickly.

4. Carefully pack the defective product, a completed Repair and Replacement Order Card, and a proof of purchase date (such as a photocopy of your sales receipt) into a shippable container. Products returned without a proof of purchase date are not eligible for warranty service.

5. Write the RMA number clearly on the outside of the package and ship the package prepaid to your dealer.

# Declaration of Conformity

## CE

This product has passed the CE test for environmental specifications when shielded cables are used for external wiring. We recommend the use of shielded cables. This type of cable is available from Advantech. Please contact your local supplier for ordering information.

Test conditions for passing also include the equipment being operated within an industrial enclosure. In order to protect the product from damage caused by electrostatic discharge (ESD) and EMI leakage, we strongly recommend the use of CE-compliant industrial enclosure products.

## FCC Class A

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy, and if not installed and used in accordance with the user manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference. In this event, users are required to correct the interference at their own expense.

## Technical Support and Assistance

1. Visit the Advantech website at [www.advantech.com/support](http://www.advantech.com/support) where you can find the latest information about the product.

2. Contact your distributor, sales representative, or Advantech's customer service center for technical support if you need additional assistance. Have the following information ready before you call:

- Product name and serial number

- Description of your peripheral attachments

- Description of your software (operating system, version, application software, etc.)

- A complete description of the problem

- The exact wording of any error messages

---

# Warnings, Cautions, and Notes

**Warning!** *Warnings indicate conditions that if not observed can cause personal injury!*

**Caution!** *Cautions are included to help prevent hardware damage and data losses. For example,*

*“Batteries are at risk of exploding if incorrectly installed. Do not attempt to recharge, force open, or heat the battery. Replace the battery only with the same or equivalent type as recommended by the manufacturer. Discard used batteries according to the manufacturer's instructions.”*

## Document Feedback

To assist us with improving this manual, we welcome all comments and constructive criticism. Please send all feedback in writing to support@advantech.com.

## Packing List

- PCIE-1842 or PCIE-1842L x 1

- Startup Manual x 1

## Ordering Information

---

|                    |                                               |

|--------------------|-----------------------------------------------|

| <b>PCIE-1842-A</b> | 10MS/s/ch, 14-bit, 8-ch, simultaneous AI card |

|--------------------|-----------------------------------------------|

---

|                     |                                               |

|---------------------|-----------------------------------------------|

| <b>PCIE-1842L-A</b> | 10MS/s/ch, 14-bit, 4-ch, simultaneous AI card |

|---------------------|-----------------------------------------------|

---

## Accessories

---

|                      |                                                   |

|----------------------|---------------------------------------------------|

| <b>1700030423-01</b> | 10-pin flat cable for MDSI synchronization, 10 cm |

|----------------------|---------------------------------------------------|

---

# Safety Instructions

1. Read these safety instructions carefully.

2. Retain this user manual for future reference.

3. Disconnect the equipment from all power outlets before cleaning. Use only a damp cloth for cleaning. Do not use liquid or spray detergents.

4. For pluggable equipment, the power outlet socket must be located near the equipment and easily accessible.

5. Protect the equipment from humidity.

6. Place the equipment on a reliable surface during installation. Dropping or letting the equipment fall may cause damage.

7. The openings on the enclosure are for air convection. Protect the equipment from overheating. Do not cover the openings.

8. Ensure that the voltage of the power source is correct before connecting the equipment to a power outlet.

9. Position the power cord away from high-traffic areas. Do not place anything over the power cord.

10. All cautions and warnings on the equipment should be noted.

11. If the equipment is not used for a long time, disconnect it from the power source to avoid damage from transient overvoltage.

12. Never pour liquid into an opening. This may cause fire or electrical shock.

13. Never open the equipment. For safety reasons, the equipment should be opened only by qualified service personnel.

14. If any of the following occurs, have the equipment checked by service personnel:

- The power cord or plug is damaged.

- Liquid has penetrated the equipment.

- The equipment has been exposed to moisture.

- The equipment is malfunctioning, or does not operate according to the user manual.

- The equipment has been dropped and damaged.

- The equipment shows obvious signs of breakage.

15. Do not leave the equipment in an environment with a storage temperature of below -20 °C (-4 °F) or above 60 °C (140 °F) as this may damage the components. The equipment should be kept in a controlled environment.

16. CAUTION: Batteries are at risk of exploding if incorrectly replaced. Replace only with the same or equivalent type as recommended by the manufacturer. Discard used batteries according to the manufacturer's instructions.

17. In accordance with IEC 704-1:1982 specifications, the sound pressure level at the operator's position does not exceed 70 dB (A).

**DISCLAIMER:** These instructions are provided according to IEC 704-1 standards. Advantech disclaims all responsibility for the accuracy of any statements contained herein.

---

## Safety Precaution - Static Electricity

Follow these simple precautions to protect yourself from harm and the products from damage.

1. To avoid electrical shock, always disconnect the power from your PC chassis before you work on it. Don't touch any components on the CPU card or other cards while the PC is on.

2. Disconnect the power before making any configuration changes. The sudden rush of power as you connect a jumper or install a card may damage sensitive electronic components.

# Contents

## Chapter 1 Start Using PCIE-1842/1842L.....1

|       |                                                 |   |

|-------|-------------------------------------------------|---|

| 1.1   | Product Overview.....                           | 2 |

|       | Figure 1.1 Card layout of PCIE-1842/1842L.....  | 2 |

|       | Table 1.1: List of connectors and switches..... | 2 |

| 1.2   | Product Features.....                           | 2 |

| 1.2.1 | Board ID.....                                   | 2 |

| 1.3   | Driver Installation .....                       | 3 |

|       | Figure 1.2 XNavi installation interface .....   | 3 |

| 1.4   | Software Utility .....                          | 3 |

| 1.5   | Software Development Using DAQNavi SDK .....    | 4 |

| 1.6   | FPGA Code Updates .....                         | 4 |

## Chapter 2 Installation Guide .....5

|       |                                                          |    |

|-------|----------------------------------------------------------|----|

| 2.1   | Initial Unpacking Check.....                             | 6  |

| 2.2   | Hardware Installation .....                              | 6  |

| 2.3   | Signal Connection and Pin Assignment.....                | 7  |

| 2.3.1 | Analog Input Connection.....                             | 7  |

|       | Figure 2.1 Analog input signal connection.....           | 7  |

| 2.3.2 | Digital Trigger Input Connection .....                   | 7  |

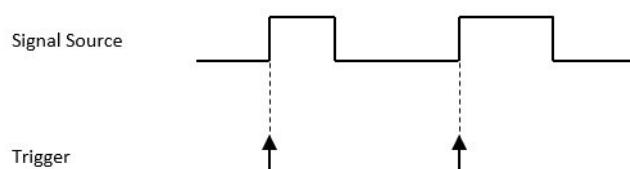

|       | Figure 2.2 Rising edge active digital trigger.....       | 7  |

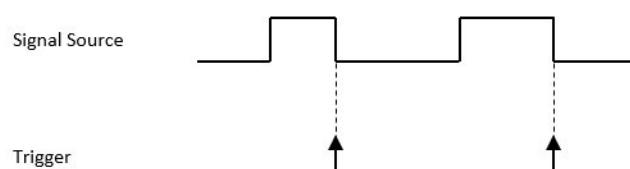

|       | Figure 2.3 Falling edge active digital trigger .....     | 7  |

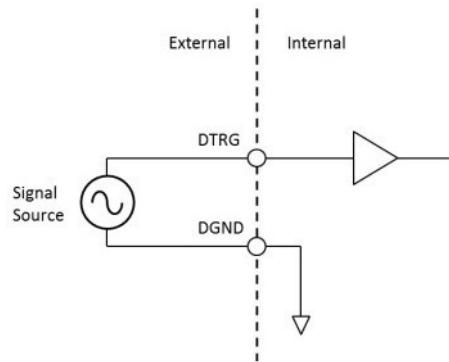

|       | Figure 2.4 Signal connection of the digital trigger..... | 8  |

| 2.3.3 | Pin Assignment.....                                      | 8  |

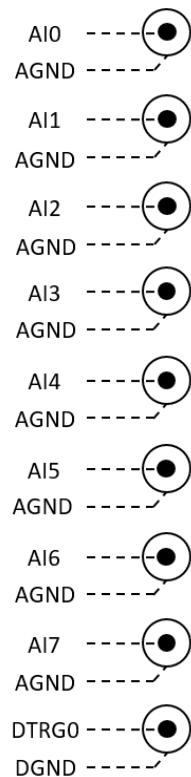

|       | Figure 2.5 Pin Assignment for PCIE-1842/PCIE-1842L ..... | 8  |

|       | Table 2.1: List of Pin Assignment.....                   | 9  |

| 2.4   | Field Wiring Considerations .....                        | 9  |

| 2.5   | Board ID Configuration.....                              | 9  |

|       | Table 2.2: SW1 position for Board ID .....               | 9  |

| 2.6   | Analog Input Configuration (JP1 - JP8).....              | 10 |

|       | Table 2.3: Analog Input Configuration (JP1 - JP8) .....  | 10 |

## Chapter 3 Function Details.....11

|       |                                                                                    |    |

|-------|------------------------------------------------------------------------------------|----|

| 3.1   | Analog Input.....                                                                  | 12 |

| 3.1.1 | Instant Analog Input Acquisition.....                                              | 12 |

|       | Figure 3.1 Instant analog input acquisition .....                                  | 12 |

| 3.1.2 | Buffered Analog Input Acquisition.....                                             | 13 |

|       | Figure 3.2 Buffered (hardware-timed) analog input acquisition .....                | 13 |

| 3.1.3 | Analog Input Low-Pass Filter .....                                                 | 13 |

| 3.2   | Trigger Signal.....                                                                | 14 |

| 3.2.1 | Digital Trigger.....                                                               | 14 |

|       | Figure 3.3 Rising edge active digital trigger.....                                 | 14 |

|       | Figure 3.4 Falling edge active digital trigger .....                               | 14 |

| 3.2.2 | Analog Trigger .....                                                               | 14 |

|       | Figure 3.5 Rising edge active analog trigger .....                                 | 14 |

|       | Figure 3.6 Falling edge active analog trigger .....                                | 15 |

| 3.3   | Synchronization.....                                                               | 15 |

| 3.3.1 | Synchronization via MDSI Cables.....                                               | 15 |

|       | Figure 3.7 Synchronize multiple devices through MDSI cables .....                  | 15 |

|       | Table 3.1: Software configuration for synchronization by using an MDSI cable ..... | 16 |

| 3.4   | Configuration for Buffered Analog Input Acquisition .....                          | 16 |

|       |                                                            |    |

|-------|------------------------------------------------------------|----|

| 3.4.1 | One-Buffered Analog Input Acquisition.....                 | 16 |

|       | Figure 3.8 Post-trigger acquisition.....                   | 16 |

|       | Figure 3.9 Post-trigger acquisition with delay.....        | 17 |

|       | Figure 3.10 Pre-trigger acquisition .....                  | 17 |

|       | Figure 3.11 About-trigger acquisition.....                 | 17 |

| 3.4.2 | Streaming Analog Input Acquisition.....                    | 18 |

|       | Figure 3.12 Streaming acquisition .....                    | 18 |

| 3.4.3 | Re-Triggerable Analog Input Acquisition .....              | 18 |

|       | Figure 3.13 Post-trigger acquisition with re-trigger.....  | 18 |

|       | Figure 3.14 Pre-trigger acquisition with re-trigger .....  | 18 |

|       | Figure 3.15 About-trigger acquisition with re-trigger..... | 19 |

|       | Figure 3.16 Streaming acquisition with re-trigger.....     | 19 |

| 3.5   | Analog Input Calibration.....                              | 19 |

|       | Figure 3.17 Calibration utility .....                      | 19 |

## Appendix A Specifications..... 21

|     |                                                                                                   |    |

|-----|---------------------------------------------------------------------------------------------------|----|

| A.1 | Analog Input.....                                                                                 | 22 |

| A.2 | Analog Input Characteristics .....                                                                | 23 |

|     | Table A.1: Idle Channel Noise .....                                                               | 23 |

|     | Table A.2: Signal-to-Noise Ratio (SNR, 1 kHz Input Tone, -1 dBFS Amplitude) .....                 | 23 |

|     | Table A.3: Total Harmonic Distortion (THD, 1 kHz Input Tone, -1 dBFS Amplitude) .....             | 23 |

|     | Table A.4: Total Harmonic Distortion Plus Noise (THD+N, 1 kHz Input Tone, -1 dBFS Amplitude)..... | 23 |

|     | Table A.5: Spurious-Free Dynamic Range (SFDR, 1 kHz Input Tone, -1 dBFS Amplitude).....           | 24 |

|     | Table A.6: Effective Number of Bits (ENOB, 1 kHz Input Tone, -1 dBFS Amplitude).....              | 24 |

|     | Table A.7: Signal to Noise and Distortion (SINAD, 1 kHz Input Tone, -1 dBFS Amplitude).....       | 24 |

|     | Table A.8: Crosstalk (1 kHz Input Tone, input amplitude is -1 dBFS) .....                         | 24 |

|     | Table A.9: Crosstalk (100 kHz Input Tone, input amplitude is -1 dBFS) .....                       | 24 |

| A.3 | Trigger.....                                                                                      | 25 |

|     | A.3.1 Analog Trigger .....                                                                        | 25 |

|     | A.3.2 Digital Trigger .....                                                                       | 25 |

| A.4 | Multi-Device Synchronization Interface (MDSI) .....                                               | 25 |

| A.5 | General .....                                                                                     | 25 |

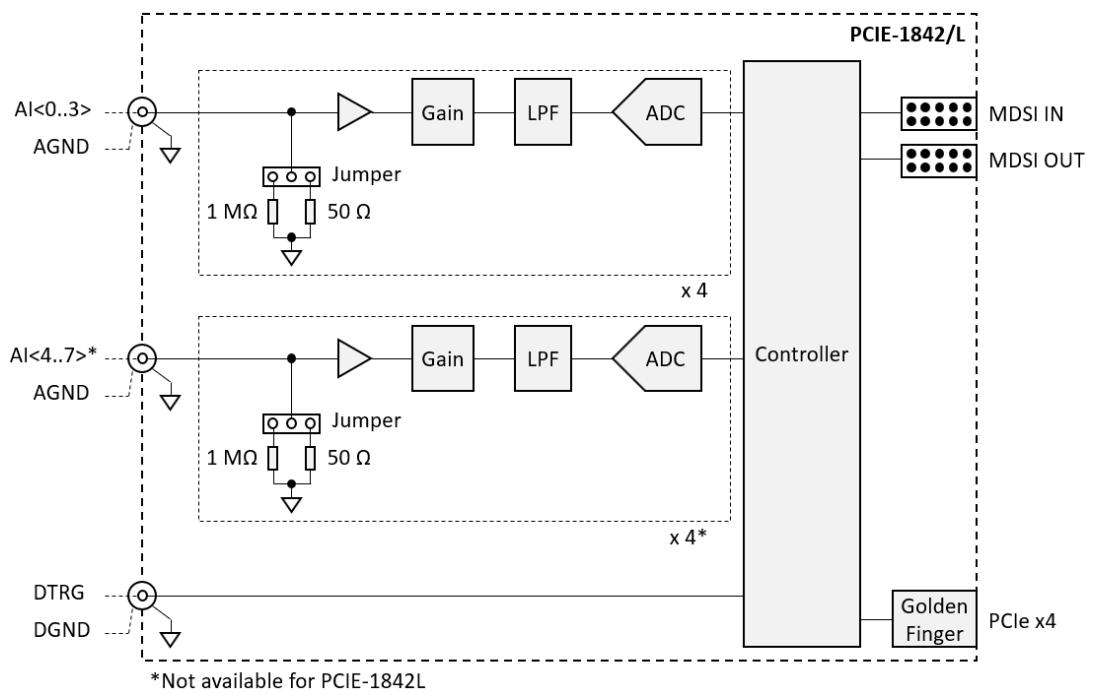

| A.6 | Function Block .....                                                                              | 26 |

|     | Figure A.1 Function block of PCIE-1842/1842L.....                                                 | 26 |

# Chapter 1

Start Using PCIE-1842/

1842L

## 1.1 Product Overview

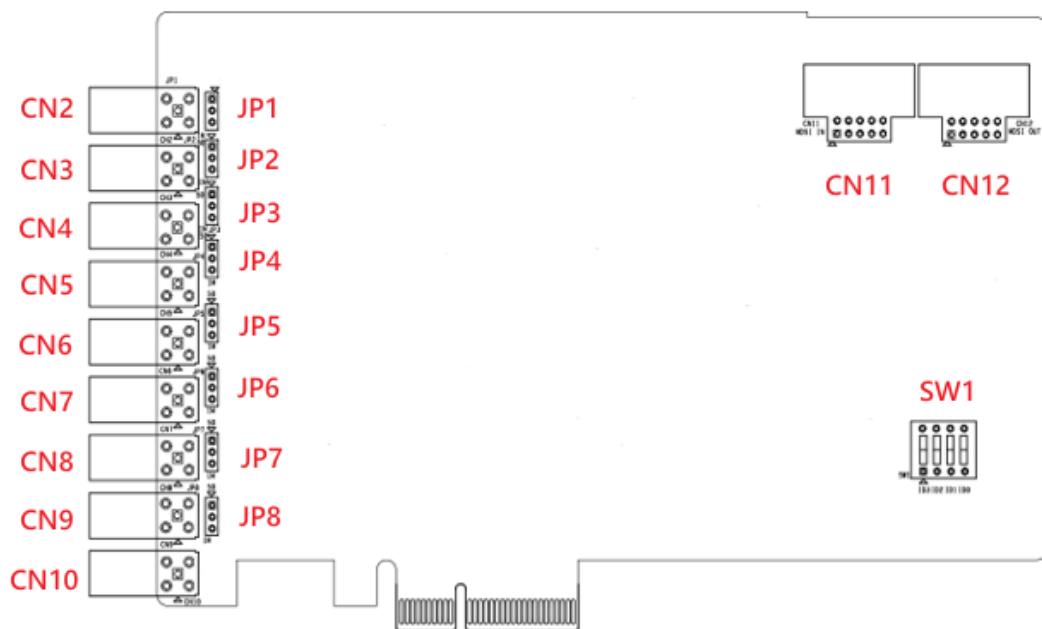

Figure 1.1 Card layout of PCIE-1842/1842L

**Table 1.1: List of connectors and switches**

| Component | Description          | Function                           |

|-----------|----------------------|------------------------------------|

| JP1-8     | Jumper for impedance | Impedance setting                  |

| CN2-10    | SMA Connector        | Main-function signal connection    |

| CN11      | MDSI IN              | Interface for MDSI synchronization |

| CN12      | MDSI OUT             | Interface for MDSI synchronization |

| SW1       | Board ID (BID)       | Board ID function                  |

## 1.2 Product Features

### 1.2.1 Board ID

A board ID (BID) can be assigned to Advantech DAQ devices (PCI/PCIe cards and USB modules) by the DIP switch. The board ID will be shown in the software and can be used to distinguish modules/devices. When there are multiple cards on the same chassis, this board ID switch is useful for identifying each card's device number.

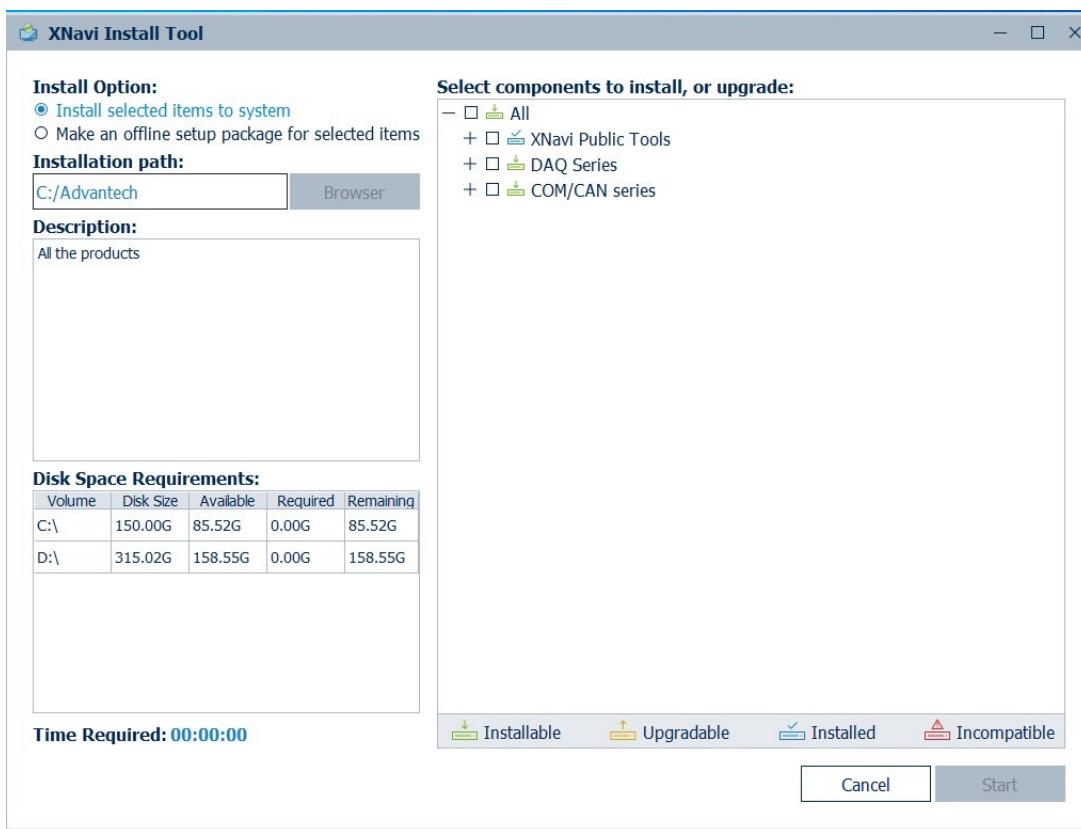

## 1.3 Driver Installation

The driver package can be found on the Advantech Support Portal (<https://www.advantech.com/support>). Search for PCIE-1842 or PCIE-1842L to locate the corresponding driver/SDK package. You'll receive the XNavi installer with the download which will start when the download finishes.

Execute the installer, then it will guide you through the session. You can choose the device and software components you'd like to install in the system (Figure 1.2). After selecting, click on **Start** to begin the installation.

Figure 1.2 XNavi installation interface

## 1.4 Software Utility

Advantech offers device drivers, SDKs, third-party driver support and application software to help fully exploit the functions of your DAQ devices. All these software packages are available on the Advantech website: <http://www.advantech.com/>.

The Advantech Navigator is a utility that allows you to set up, configure and test your device, and later stores your settings in a proprietary database.

1. To set up the I/O device for your card, you can first run the Advantech Navigator program (by accessing Start/Programs/Advantech Automation/DAQNavi/Advantech Navigator). The settings can also be saved.

2. You can then view the device(s) already installed on your system (if any) on the Installed Device tree view. When the software and hardware installations are completed, you will see the DAQ devices in the Installed Devices list.

---

## 1.5 Software Development Using DAQNavi SDK

DAQNavi SDK is the software development kit for programming applications with Advantech DAQ products. The necessary runtime DLL, header files, software manual and tutorial videos can be installed via the XNavi installer. They can be found under C:\Advantech\DAQNavi (default directory) after finishing the installation.

## 1.6 FPGA Code Updates

The FPGA can also be updated via the interface in Navigator. However, it is not advised to update FPGA without first doing some research. Advantech strongly suggests you consult your technical support before starting an FPGA update.

# Chapter 2

Installation Guide

## 2.1 Initial Unpacking Check

Before you install your DAQ devices, please make sure you have the following necessary components when unpacking the package:

- 1 x PCIE-1842 or PCIE-1842L card

- 1 x Startup Manual

If any of the above is missing, please contact your local support for further assistance.

## 2.2 Hardware Installation

After installation of the device drivers is complete, you can install the PCIE-1842/1842L card on your computer. However, it is suggested that you refer to the computer's user manual or related documentation if you have any doubts. Please follow the steps below to install the card onto your system.

1. Turn off your computer and unplug the power cord and cables. TURN OFF your computer before installing or removing any components on the computer.

2. Remove the cover of your computer.

3. Remove the slot cover on the back panel of your computer.

4. Touch the metal part on the surface of your computer to neutralize the static electricity that might be on your body.

5. Insert the PCIE-1842/1842L card into the PCI Express interface. Hold the card only by its edges and carefully align it with the slot. Insert the card firmly into place. Use of excessive force must be avoided; otherwise, the card might be damaged.

6. Connect the appropriate accessories (SMA cable etc.) to the card.

7. Replace the cover of your computer chassis. Re-connect the cables you removed in step 2.

8. Plug in the power cord and turn on the computer.

After your card is properly installed on your system, you can then configure your device using the Advantech Navigator Program that has already been installed on your system during driver setup. A complete device installation procedure should include device setup, configuration, and testing. The following sections will guide you through the setup, configuration, and testing of your device.

## 2.3 Signal Connection and Pin Assignment

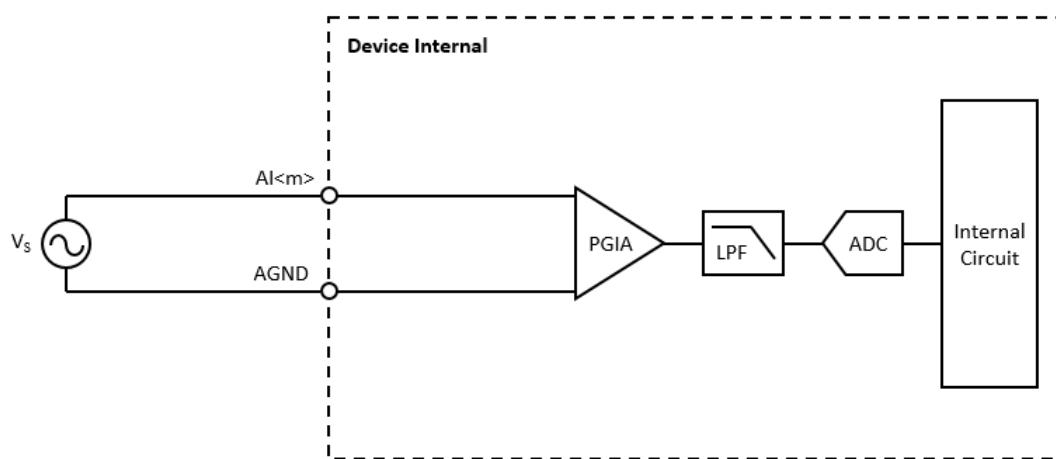

### 2.3.1 Analog Input Connection

An analog input channel measures the voltage ( $V_S$ ) of the external source. When a voltage source is being measured, the voltage difference between  $AI$  and  $GND$  is being measured. The voltage is then amplified or attenuated by a programmable gain instrumentation amplifier (PGIA), conditioned by a low-pass filter (LPF), and sampled and converted into a digital form of data by an analog-to-digital converter (ADC). The ADC of every channel samples the signal at the same time, and this architecture is thus called simultaneous sampling analog input.

The analog input signal connection and internal functional block diagram is shown in Figure 2.1.

Figure 2.1 Analog input signal connection

### 2.3.2 Digital Trigger Input Connection

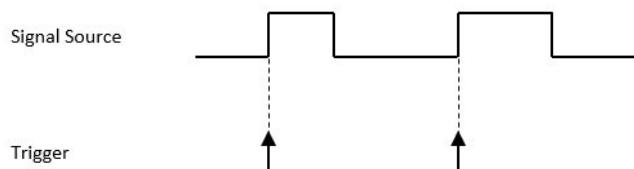

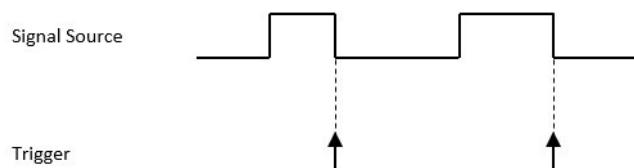

A digital trigger can be configured as rising edge active or falling edge active, as shown in Figures 2.2 and 2.3, respectively. Figure 2.4 shows the signal connection of the digital trigger.

Figure 2.2 Rising edge active digital trigger

Figure 2.3 Falling edge active digital trigger

**Figure 2.4 Signal connection of the digital trigger**

### 2.3.3 Pin Assignment

**Figure 2.5 Pin Assignment for PCIE-1842/PCIE-1842L**

**Table 2.1: List of Pin Assignment**

| Pin Name | Description                                                                                       |

|----------|---------------------------------------------------------------------------------------------------|

| AI0      | Analog input 0 terminal.                                                                          |

| AI1      | Analog input 1 terminal.                                                                          |

| AI2      | Analog input 2 terminal.                                                                          |

| AI3      | Analog input 3 terminal.                                                                          |

| AI4      | Analog input 4 terminal.                                                                          |

| AI5      | Analog input 5 terminal.                                                                          |

| AI6      | Analog input 6 terminal.                                                                          |

| AI7      | Analog input 7 terminal.                                                                          |

| AGND     | Ground terminals for analog signals                                                               |

| DTRG0    | Digital Trigger. The pin is the digital input, which is used to start or stop a data acquisition. |

| DGND     | Ground terminals for digital signals.                                                             |

## 2.4 Field Wiring Considerations

When measuring a signal using the device, noise in the environment might significantly affect the performance of the measurement if some cautions are not taken. Follow these recommendations to avoid degradation of the resulting measurement.

- Make signal lines as short as possible.

- Use shielded, twisted-pair cables.

- Keep signal lines away from noisy environments, high-voltage/current cables, or equipment which generates large electromagnetic interference, such as power lines, motors, breakers, or welding equipment.

- Route signal lines at right angles to noise generating cables.

- Use differential input configuration to reduce common-mode noise.

- For externally powered modules, use separate power sources for modules and other noise generating equipment.

## 2.5 Board ID Configuration

The Board ID information can be viewed in Advantech Navigator. The SW1 on the board sets the number. Table 2.2 shows the switch position and corresponding numbering.

**Table 2.2: SW1 position for Board ID**

| Board ID | Switch Position |      |      |      |

|----------|-----------------|------|------|------|

|          | 1               | 2    | 3    | 4    |

| 0*       | UP              | UP   | UP   | UP   |

| 1        | UP              | UP   | UP   | DOWN |

| 2        | UP              | UP   | DOWN | UP   |

| 3        | UP              | UP   | DOWN | DOWN |

| 4        | UP              | DOWN | UP   | UP   |

| 5        | UP              | DOWN | UP   | DOWN |

| 6        | UP              | DOWN | DOWN | UP   |

| 7        | UP              | DOWN | DOWN | DOWN |

|    |      |      |      |      |

|----|------|------|------|------|

| 8  | DOWN | UP   | UP   | UP   |

| 9  | DOWN | UP   | UP   | DOWN |

| 10 | DOWN | UP   | DOWN | UP   |

| 11 | DOWN | UP   | DOWN | DOWN |

| 12 | DOWN | DOWN | UP   | UP   |

| 13 | DOWN | DOWN | UP   | DOWN |

| 14 | DOWN | DOWN | DOWN | UP   |

| 15 | DOWN | DOWN | DOWN | DOWN |

\* Default setting.

## 2.6 Analog Input Configuration (JP1 - JP8)

**Table 2.3: Analog Input Configuration (JP1 - JP8)**

| Jumper Setting                                                                      | Description      |

|-------------------------------------------------------------------------------------|------------------|

|  | 50 $\Omega$ .    |

|  | 1 M $\Omega$ . * |

\* Default setting.

# Chapter 3

## Function Details

## 3.1 Analog Input

This chapter describes all the functions that the PCIE-1842/PCIE-1842L provides and how they work.

The following sections describe the analog input acquisition mechanism.

### 3.1.1 Instant Analog Input Acquisition

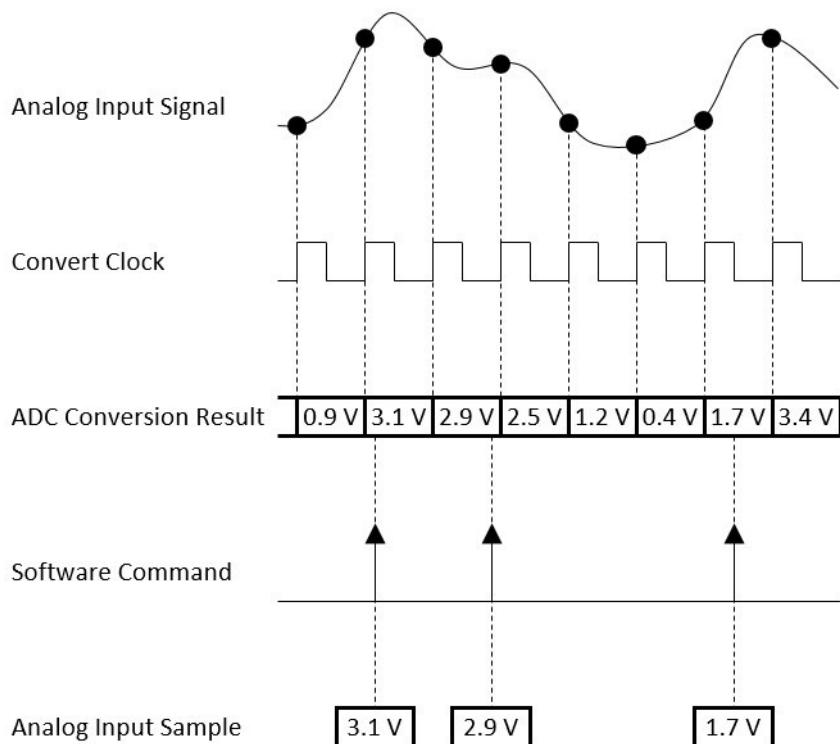

With instant analog input acquisition, the software controls the sample timing. The analog-to-digital converter (ADC) is continuously converting the analog input signal within its maximum allowable conversion rate. Each time the software sends a “read instant analog input sample” command, the most recent conversion result is sampled as shown in Figure 3.1.

Figure 3.1 Instant analog input acquisition

### 3.1.2 Buffered Analog Input Acquisition

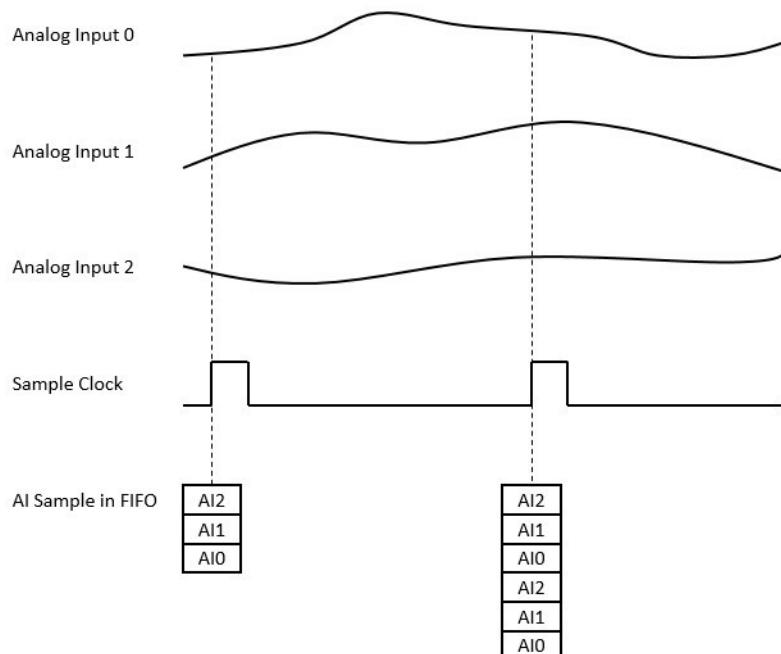

With buffered acquisition, a hardware signal called sample clock controls the rate and time of acquisition. The ADCs of all buffered acquisition enabled channels simultaneously begin to convert the analog input voltage at each rising edge of the sample clock. Figure 3.2 shows an example of analog input buffered acquisition where AI0, AI1, and AI2 are enabled.

**Figure 3.2 Buffered (hardware-timed) analog input acquisition**

The sample clock can be generated internally on the device or be provided externally. Refer to the device specifications for supported sample clock sources and the maximum allowable frequency of the sample clock.

The acquired samples are first accumulated in the onboard first-in-first-out (FIFO) memory of the device, and then moved to the buffer in the PC by a direct memory access (DMA) engine. A buffer is a block of memory in the PC for temporarily storing the data to be transferred to the application memory. Because the data is moved in large blocks instead of one point at a time, buffered acquisition typically allows much higher transfer rates. Buffered acquisition is also called hardware-timed acquisition.

The advantages of buffered acquisition over instant acquisition include:

- The sample rate can be much higher.

- The time of a sample is deterministic.

- Hardware triggers can be used.

### 3.1.3 Analog Input Low-Pass Filter

The low-pass filter removes high frequency noise of the input signal and the noise that is added by the high common-mode voltage amplifier. It can also act as an anti-aliasing filter which avoids alias generation due to ADC conversion.

## 3.2 Trigger Signal

The trigger can come from one of various signal sources. If the signal source is of a digital type (logic high or low), it is called a digital trigger. On the other hand, if the signal source is of an analog type (voltage level), it is called an analog trigger.

### 3.2.1 Digital Trigger

A digital trigger can be configured as rising edge active or falling edge active, as shown in Figures 3.3 and 3.4, respectively.

Figure 3.3 Rising edge active digital trigger

Figure 3.4 Falling edge active digital trigger

### 3.2.2 Analog Trigger

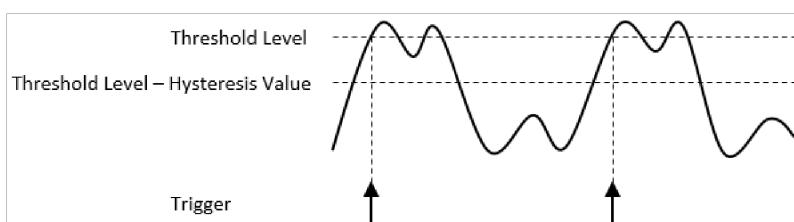

In addition to active edge, the user can configure the threshold level and the hysteresis value for an analog trigger. The threshold level specifies the analog input voltage level where the trigger occurs. The hysteresis value prevents unwanted triggers due to noisy signals.

A rising edge active analog trigger occurs when the signal crosses the threshold level from below. And another trigger occurs only if the signal has crossed the voltage specified by the threshold level minus the hysteresis value from above before it crosses the threshold level from below again. This is shown in Figure 3.5.

Figure 3.5 Rising edge active analog trigger

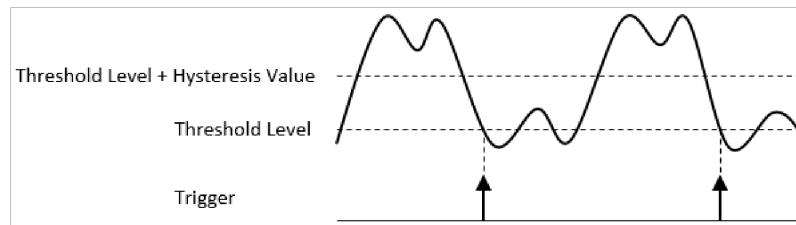

A falling edge active analog trigger occurs when the signal crosses the threshold level from above. And another trigger occurs only if the signal has crossed the voltage specified by the threshold level plus the hysteresis value from below before it crosses the threshold level from above again. This is shown in Figure 3.6.

Figure 3.6 Falling edge active analog trigger

### 3.3 Synchronization

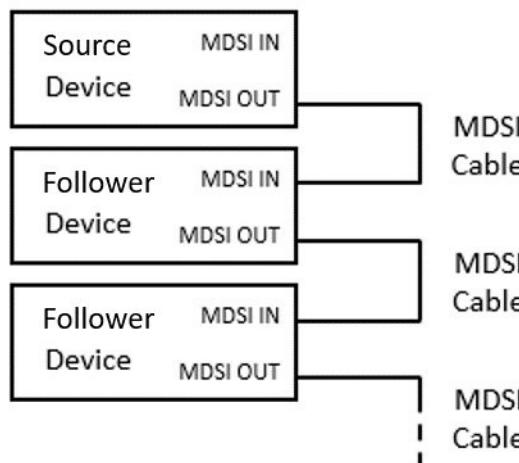

To synchronize the acquisition of multiple devices, the required timing signals must be wired correctly. All devices must use the same sample clock for the equivalent sample rate and be triggered at the same time. One of the devices is selected as the source device, and the others as follower devices. The source device sends the required timing signals to all the follower devices for synchronized acquisition.

The timing signals can be wired externally through cables, or internally by the Multi-Device Synchronization Interface (MDSI) cables.

#### 3.3.1 Synchronization via MDSI Cables

To use MDSI cables for synchronization, connect each cable from the MDSI OUT of one device to the MDSI IN of the next device as shown in Figure 3.7.

Figure 3.7 Synchronize multiple devices through MDSI cables

“Convert Clock Source” and “Trigger Source” configurations for the source can be selected as required. However, for the followers, these configurations must be selected according to Table 3.1.

**Table 3.1: Software configuration for synchronization by using an MDSI cable**

| Card                 | Source                                                         | Follower                             |

|----------------------|----------------------------------------------------------------|--------------------------------------|

| Convert Clock Source | Internal Clock                                                 | External Digital Clock from MDSI pin |

| Trigger Source       | None<br>One of the AI channels<br>External Digital Trigger 0/1 | MDSI Trigger 0/1                     |

After all configurations are done, start all the followers before the source. This ensures all the followers are ready when the source sends synchronization signals.

## 3.4 Configuration for Buffered Analog Input Acquisition

According to software configurations, buffered analog input acquisition can be classified into two types:

- One-buffered analog input acquisition

- Streaming analog input acquisition

### 3.4.1 One-Buffered Analog Input Acquisition

For one-buffered acquisition, only a specified number of samples is acquired. The starting or stopping of acquisition can be controlled by a software command or a hardware signal. Three types of acquisitions can be achieved: post-trigger acquisition, pre-trigger acquisition, and about-trigger acquisition.

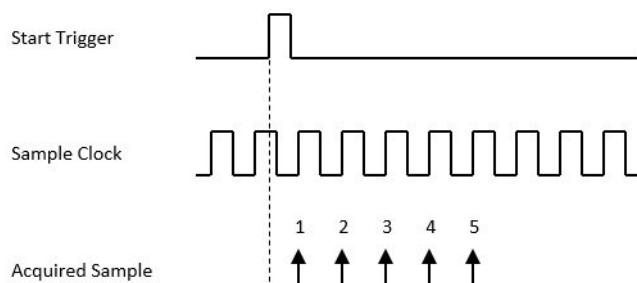

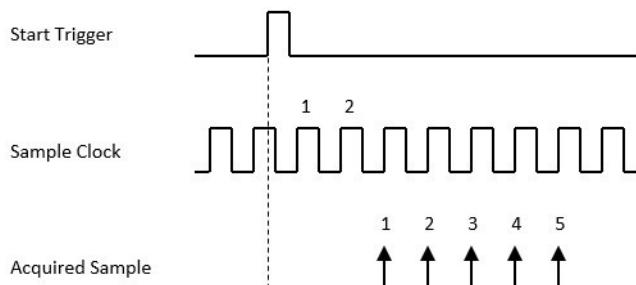

#### 3.4.1.1 Post-Trigger acquisition

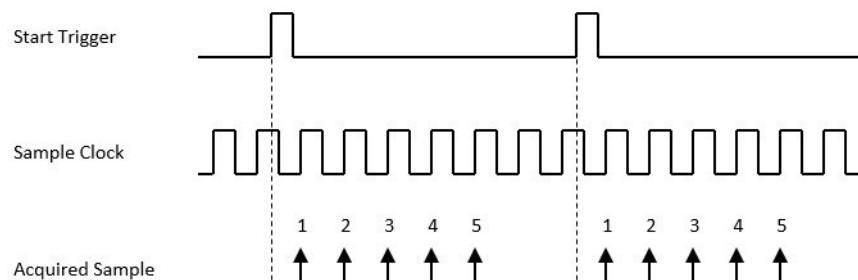

A post-trigger acquisition acquires a specified number of samples after the start trigger. The acquisition starts when a start trigger is received and automatically stops when the specified number of samples is acquired. An example of 5-sample post-trigger acquisition is shown in Figure 3.8.

**Figure 3.8 Post-trigger acquisition**

The start trigger can be a software command or a hardware signal. If a hardware signal is used as the start trigger, the start of acquisition can be delayed for a specified number of sample clock cycles after a start trigger is received. Figure 3.9 shows an example of a 2-sample delay post-trigger acquisition. Refer to the device specifications for possible signal sources.

**Figure 3.9 Post-trigger acquisition with delay**

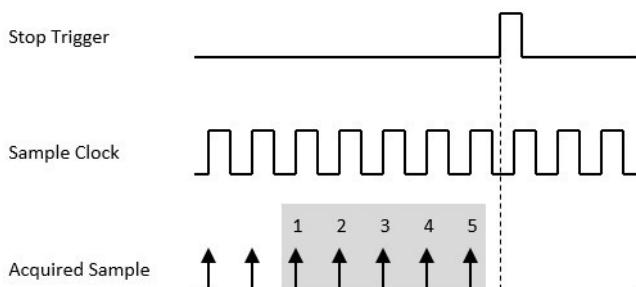

#### 3.4.1.2 Pre-trigger acquisition

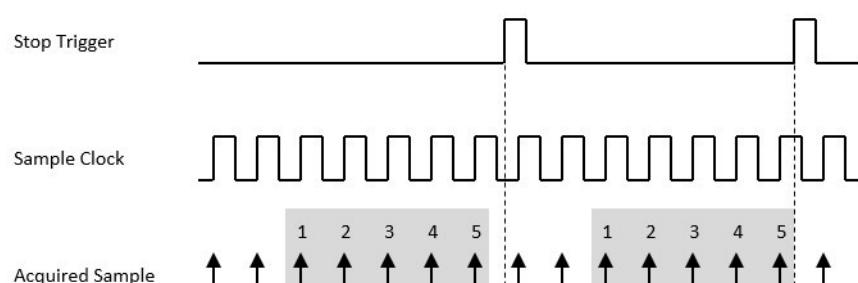

A pre-trigger acquisition acquires a specified number of samples before the stop trigger. The acquisition is started by a software command and stops when a hardware stop trigger is received. Figure 3.10 shows an example of a 5-sample pre-trigger acquisition. Only the samples in the shaded area are returned.

**Figure 3.10 Pre-trigger acquisition**

The stop trigger can only be a hardware signal. Refer to the device specifications for possible signal sources.

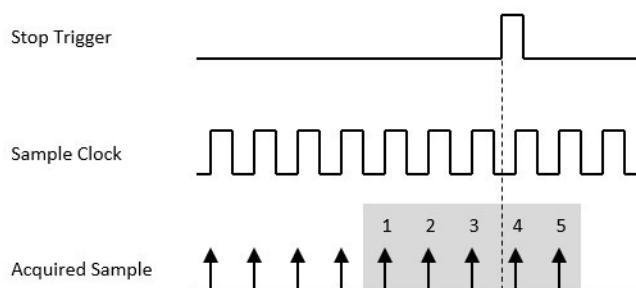

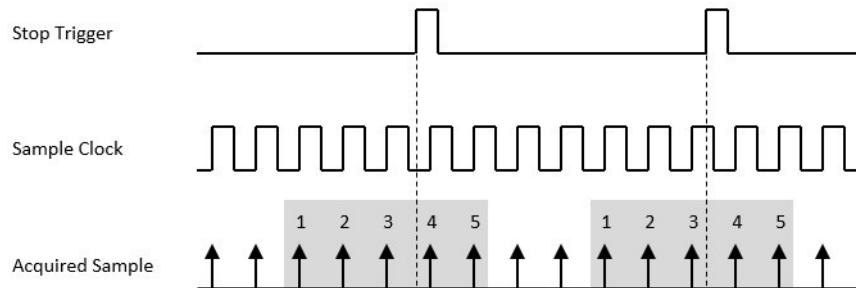

#### 3.4.1.3 About-trigger acquisition

An about-trigger acquisition is the same as a pre-trigger acquisition except that the time when the acquisition stops can be delayed by a specified number of sample clock cycles. Figure 3.11 shows an example of a 5-sample about-trigger acquisition with 2 cycles of stop delay. Only the samples in the shaded area are returned.

**Figure 3.11 About-trigger acquisition**

The stop trigger can only be a hardware signal. Refer to the device specifications for possible signal sources.

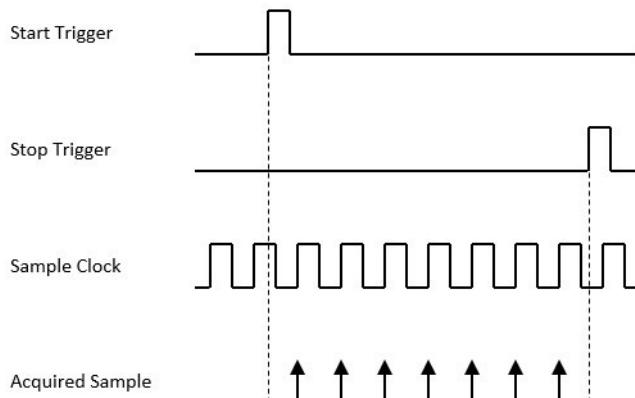

### 3.4.2 Streaming Analog Input Acquisition

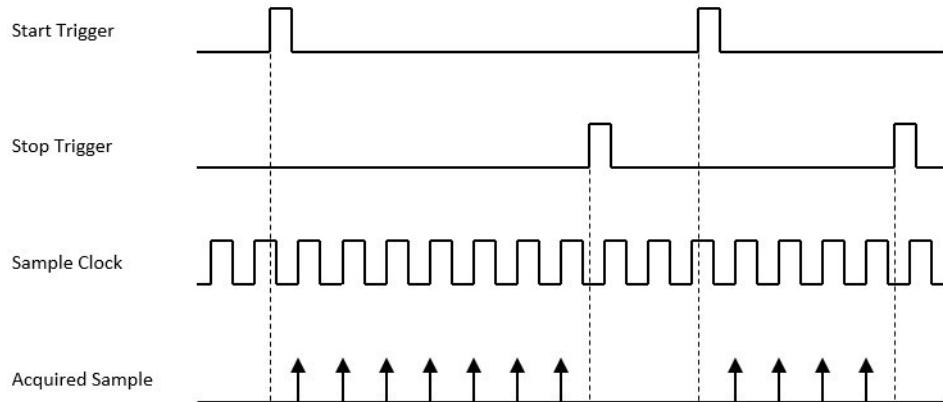

For a streaming acquisition, the number of samples to be acquired is set to infinite. The acquisition starts when a start trigger is received and continues until a stop trigger is received as shown in Figure 3.12.

Figure 3.12 Streaming acquisition

Both the start trigger and the stop trigger can come from a software command or a hardware signal. If a hardware signal is used, the start (for the start trigger) or the stop (for the stop trigger) of the acquisition can also be delayed. Refer to the device specifications for possible signal sources.

### 3.4.3 Re-Triggerable Analog Input Acquisition

The acquisition can be re-triggerable. When re-trigger is enabled, after the acquisition stops, it restarts whenever the required trigger is received, and reconfiguration of the acquisition is not required.

Figures 3.13 to 3.16 show examples of re-trigger acquisition for post-trigger, pre-trigger, about-trigger, and streaming acquisitions, respectively. In a post-trigger acquisition, a start trigger is ignored while the acquisition is in progress. In an about-trigger acquisition, a stop trigger is ignored while the acquisition is being stopped.

Figure 3.13 Post-trigger acquisition with re-trigger

Figure 3.14 Pre-trigger acquisition with re-trigger

Figure 3.15 About-trigger acquisition with re-trigger

Figure 3.16 Streaming acquisition with re-trigger

### 3.5 Analog Input Calibration

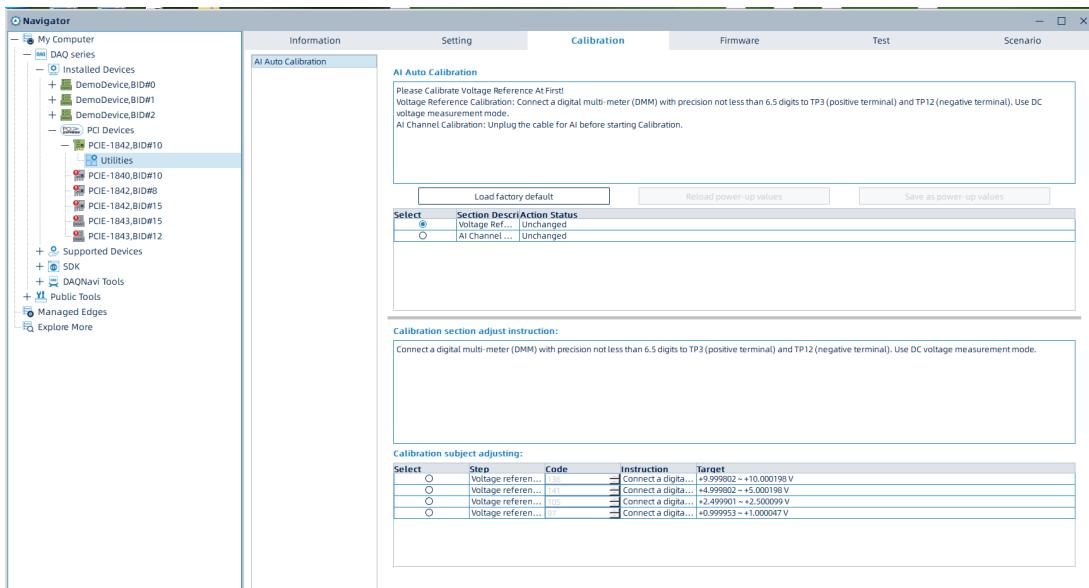

The Navigator of Advantech DAQNavi provides the calibration utility to calibrate the analog input and analog output circuitry of the device. Figure 3.17 shows the interface of the calibration utility. Follow the instructions shown to calibrate the device. For a multi-function device, which contains both analog input and analog output functions, analog input calibration must be performed before analog output calibration.

Figure 3.17 Calibration utility

---

When any of the calibration parameters are changed, the user can save the change by clicking the “Save as power-up values” button, or can reload power-up values by clicking the “Reload power-up values” button. The status of the calibration parameters is shown in the “Action Status” column. If required, the user can also load factory default calibration parameters by clicking the “Load factory default” button.

# Appendix A

## Specifications

## A.1 Analog Input

- **Channels**

- PCIE-1842: 8 single-ended

- PCIE-1842L: 4 single-ended

- **Analog-to-digital converter (ADC) resolution:** 14-bit

- **Input coupling:** DC

- **Input range:**  $\pm 10\text{ V}$ ,  $\pm 5\text{ V}$ ,  $\pm 2.5\text{ V}$ , or  $\pm 1\text{ V}$ , software configurable per channel

- **Maximum input voltage:**  $\pm 10\text{ V}$

- **Over-voltage protection:**  $\pm 15\text{ V}$

- **Input impedance:**  $50\text{ }\Omega$  or  $1\text{ M}\Omega$ , configured by on-board jumper per channel

- **Absolute accuracy**

- Operating temperature within  $\pm 5^\circ\text{C}$  of last auto-calibration temperature

| Accuracy |                   |                  |                    |                  |

|----------|-------------------|------------------|--------------------|------------------|

| Range    | $\pm 10\text{ V}$ | $\pm 5\text{ V}$ | $\pm 2.5\text{ V}$ | $\pm 1\text{ V}$ |

| Accuracy | $\pm 0.1\%$       | $\pm 0.1\%$      | $\pm 0.1\%$        | $\pm 0.2\%$      |

- Over full operating temperature range.

| Accuracy |                   |                  |                    |                  |

|----------|-------------------|------------------|--------------------|------------------|

| Range    | $\pm 10\text{ V}$ | $\pm 5\text{ V}$ | $\pm 2.5\text{ V}$ | $\pm 1\text{ V}$ |

| Accuracy | $\pm 0.5\%$       | $\pm 0.5\%$      | $\pm 0.5\%$        | $\pm 1\%$        |

- **Acquisition type:** Instant or buffered, software configurable

- **Buffered acquisition**

- Enabled channel combination: Each channel can be enabled/disabled independently by software

- Sample clock rate: 10 MHz max., for all channels, simultaneous sampling, software configurable

- Channel architecture: Simultaneous sampling

- Sample clock source: Internal

- Allowable internal sample clock rate:  $10\text{ MHz}/n$ , where  $n$  is an integer larger than 0, software configurable

- Internal data buffer (FIFO) size: 65,536 samples

- **Calibration:** Automatic

## A.2 Analog Input Characteristics

### ■ DC performance

**Table A.1: Idle Channel Noise**

| Range  | 100 kS/s      |                             | 1 MS/s        |                             | 10 MS/s       |                             |

|--------|---------------|-----------------------------|---------------|-----------------------------|---------------|-----------------------------|

|        | Noise (µVRMS) | Effective Resolution (bits) | Noise (µVRMS) | Effective Resolution (bits) | Noise (µVRMS) | Effective Resolution (bits) |

| ±10 V  | 911           | 14.00                       | 900           | 14.00                       | 902           | 14.00                       |

| ±5 V   | 455           | 14.00                       | 459           | 14.00                       | 453           | 14.00                       |

| ±2.5 V | 234           | 14.00                       | 234           | 14.00                       | 232           | 14.00                       |

| ±1 V   | 96            | 14.00                       | 96            | 14.00                       | 96            | 14.00                       |

### ■ AC performance

**Table A.2: Signal-to-Noise Ratio (SNR, 1 kHz Input Tone, -1 dBFS Amplitude)**

| Range  | 100 kS/s | 1 MS/s   | 10 MS/s  |

|--------|----------|----------|----------|

| ±10 V  | 76.75 dB | 76.93 dB | 77.29 dB |

| ±5 V   | 76.81 dB | 76.16 dB | 77.22 dB |

| ±2.5 V | 75.53 dB | 76.88 dB | 76.59 dB |

| ±1 V   | 72.71 dB | 72.97 dB | 74.07 dB |

**Table A.3: Total Harmonic Distortion (THD, 1 kHz Input Tone, -1 dBFS Amplitude)**

| Range  | 100 kS/s  | 1 MS/s    | 10 MS/s   |

|--------|-----------|-----------|-----------|

| ±10 V  | -85.14 dB | -85.42 dB | -91.16 dB |

| ±5 V   | -85.59 dB | -85.13 dB | -90.32 dB |

| ±2.5 V | -84.89 dB | -85.70 dB | -90.09 dB |

| ±1 V   | -85.12 dB | -85.60 dB | -90.04 dB |

**Table A.4: Total Harmonic Distortion Plus Noise (THD+N, 1 kHz Input Tone, -1 dBFS Amplitude)**

| Range  | 100 kS/s  | 1 MS/s    | 10 MS/s   |

|--------|-----------|-----------|-----------|

| ±10 V  | -76.16 dB | -76.36 dB | -77.13 dB |

| ±5 V   | -76.12 dB | -75.64 dB | -77.09 dB |

| ±2.5 V | -75.01 dB | -76.34 dB | -76.47 dB |

| ±1 V   | -72.47 dB | -72.74 dB | -73.97 dB |

**Table A.5: Spurious-Free Dynamic Range (SFDR, 1 kHz Input Tone, -1 dBFS Amplitude)**

| Range         | 100 kS/s | 1 MS/s   | 10 MS/s  |

|---------------|----------|----------|----------|

| <b>±10 V</b>  | 86.57 dB | 86.51 dB | 89.16 dB |

| <b>±5 V</b>   | 86.75 dB | 86.59 dB | 88.74 dB |

| <b>±2.5 V</b> | 86.35 dB | 86.84 dB | 88.27 dB |

| <b>±1 V</b>   | 86.57 dB | 87.04 dB | 88.77 dB |

**Table A.6: Effective Number of Bits (ENOB, 1 kHz Input Tone, -1 dBFS Amplitude)**

| Range         | 100 kS/s   | 1 MS/s     | 10 MS/s    |

|---------------|------------|------------|------------|

| <b>±10 V</b>  | 12.35 bits | 12.39 bits | 12.52 bits |

| <b>±5 V</b>   | 12.37 bits | 12.27 bits | 12.51 bits |

| <b>±2.5 V</b> | 12.17 bits | 12.39 bits | 12.41 bits |

| <b>±1 V</b>   | 11.74 bits | 11.79 bits | 11.99 bits |

**Table A.7: Signal to Noise and Distortion (SINAD, 1 kHz Input Tone, -1 dBFS Amplitude)**

| Range         | 100 kS/s | 1 MS/s   | 10 MS/s  |

|---------------|----------|----------|----------|

| <b>±10 V</b>  | 76.16 dB | 76.36 dB | 77.13 dB |

| <b>±5 V</b>   | 76.27 dB | 75.64 dB | 77.09 dB |

| <b>±2.5 V</b> | 75.06 dB | 76.34 dB | 76.47 dB |

| <b>±1 V</b>   | 72.47 dB | 72.74 dB | 73.97 dB |

**Table A.8: Crosstalk (1 kHz Input Tone, input amplitude is -1 dBFS)**

| Range         | 100 kS/s  | 1 MS/s    | 10 MS/s   |

|---------------|-----------|-----------|-----------|

| <b>±10 V</b>  | -69.96 dB | -68.34 dB | -69.96 dB |

| <b>±5 V</b>   | -69.96 dB | -69.96 dB | -69.96 dB |

| <b>±2.5 V</b> | -69.95 dB | -69.95 dB | -69.95 dB |

| <b>±1 V</b>   | -69.94 dB | -69.94 dB | -69.94 dB |

**Table A.9: Crosstalk (100 kHz Input Tone, input amplitude is -1 dBFS)**

| Range         | 1 MS/s    | 10 MS/s   |

|---------------|-----------|-----------|

| <b>±10 V</b>  | -68.38 dB | -69.96 dB |

| <b>±5 V</b>   | -69.96 dB | -69.96 dB |

| <b>±2.5 V</b> | -69.95 dB | -69.95 dB |

| <b>±1 V</b>   | -69.94 dB | -69.94 dB |

## A.3 Trigger

- **Trigger action:** Start, delay to start, stop, or delay to stop

- **Trigger delay range:** 0 ~ 16,777,215 samples

- **Sample number:** 0 ~ 16,777,215 samples

### A.3.1 Analog Trigger

- **Source:** One of the analog input channels, software configurable

- **Input range:** Full scale of analog input range

- **Resolution:** 14-bit

- **Hysteresis:** 1/256 of analog input range, software configurable

- **Accuracy:**  $\pm 0.1\%$  of full-scale range max.

- **Polarity:** Rising edge or falling edge, software configurable

- **Minimum width:** 1/(sample clock rate)

### A.3.2 Digital Trigger

- **Source:** 1 external pin

- **Input logic level:**

- Logic high: 2.0 V min.

- Logic low: 0.8 V max.

- **Working voltage:** -0.25 V ~ 5.25 V

- **Polarity:** Rising edge or falling edge, software configurable

- **Input protection voltage:** -0.5 V ~ 6.5 V

- **Pull-up resistor:** 10 kΩ

- **Minimum width:** 100 ns

## A.4 Multi-Device Synchronization Interface (MDSI)

- **MDSI:** Yes, connected by 10-pin flat cable

## A.5 General

- **Power consumption**

- PCIE-1842

- +3.3 V: 620 mA typ./660 mA max.

- +12 V: 290 mA typ./300 mA max.

- PCIE-1842L

- +3.3 V: 620 mA typ./660 mA max.

- +12 V: 160 mA typ./170 mA max.

- **Dimensions:** 167 x 111 x 18 mm<sup>3</sup> (6.57 x 4.37 x 0.7 in.<sup>3</sup>)

- **Weight:**

- PCIE-1842: 161g

- PCIE-1842L: 130g

- **Operating temperature:** 0 °C to 60 °C (32 °F to 140 °F)

- **Storage temperature:** -20 °C to 70 °C (-4 °F to 158 °F)

- **Operating humidity:** 10% to 90% RH, non-condensing

- **Storage humidity:** 5% to 95% RH, non-condensing

## A.6 Function Block

Figure A.1 Function block of PCIE-1842/1842L

## Appendix A Specifications

*Enabling an Intelligent Planet*

**[www.advantech.com](http://www.advantech.com)**

**Please verify specifications before quoting. This guide is intended for reference purposes only.**

**All product specifications are subject to change without notice.**

**No part of this publication may be reproduced in any form or by any means, such as electronically, by photocopying, recording, or otherwise, without prior written permission from the publisher.**

**All brand and product names are trademarks or registered trademarks of their respective companies.**

**© Advantech Co., Ltd. 2025**