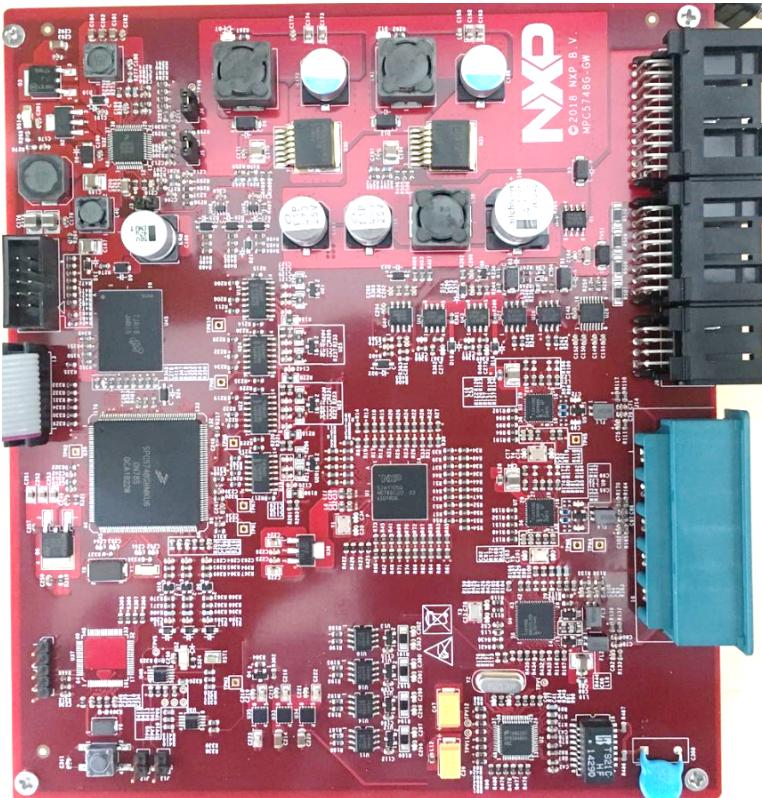

MPC5748G-GW-RDB

# EXAMPLE CODES USER GUIDE (ECUG)

Ultra-Reliable MCUs for Industrial and Automotive Applications

# SUMMARY

- 1. Hands-on - CAN

- 2. Hands-on - CAN\_FD

- 3. Hands-on - ENET0+SPI

- 4. Hands-on - ENET1

- 5. Hands-on - UART

- 6. Hands-on - LIN

# 01.

## Hands-on – CAN

# Hands-on – CAN: Objective

- Features of FlexCAN module on MPC5748G

- How to set a pin as output/input with SDK

- How to configure the port of CAN

- How to modify an existing SDK project with S32DS to suit this board

- Use CAN0~CAN7 to send CAN message

- Use CAN0~CAN7 to receive CAN message

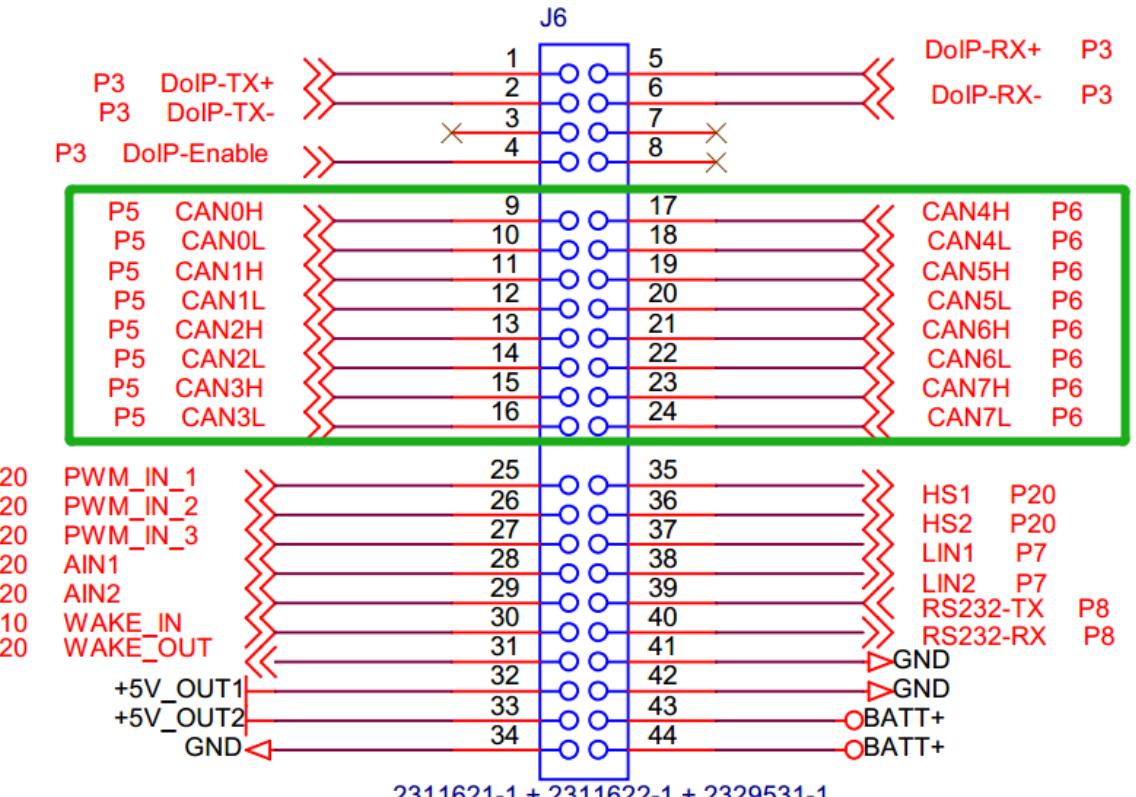

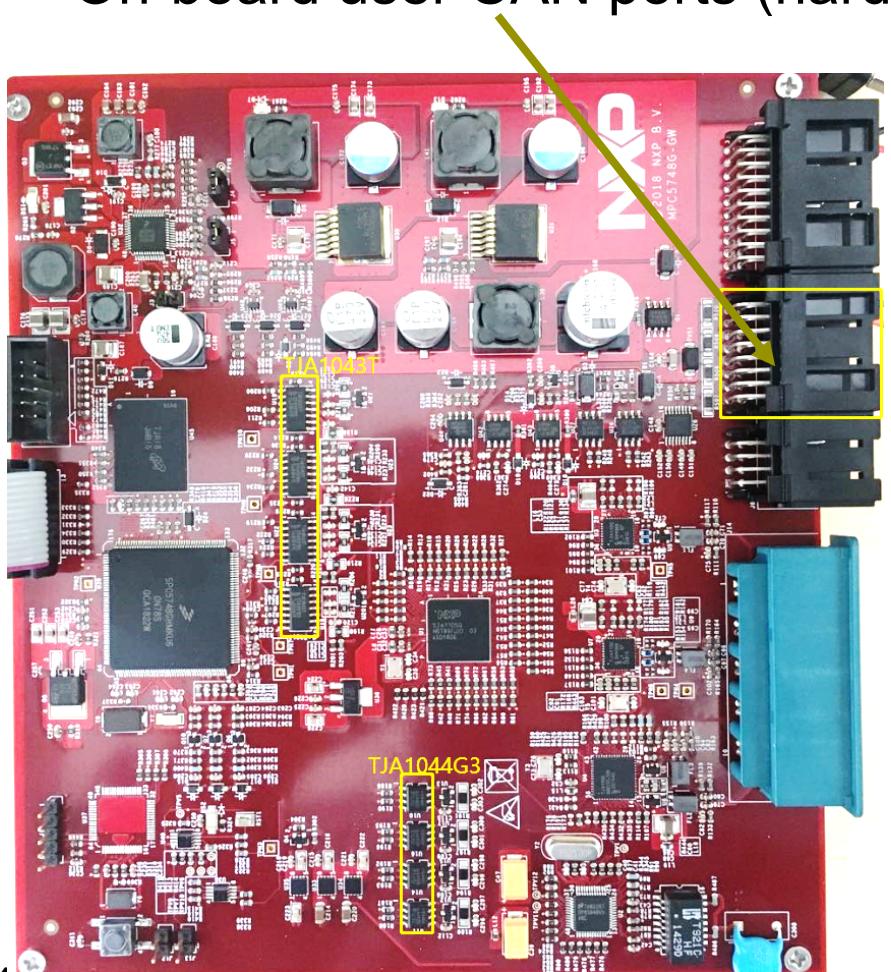

# Hands-on – CAN: Resources

- Resources to be used:

- On-board user CAN ports (hardwired to GPIOs)

# Hands-on – CAN: Theory

- Full implementation of the CAN FD & CAN 2.0 B

- data field bitrate up to 8Mbps

- Flexible mailboxes (0/8/16/32/64 bytes data length)

- Listen-Only mode capability

- Programmable Loop-Back mode supporting self-test operation

- Programmable transmission priority scheme

- Independence from the transmission medium

- CRC status for transmitted message

- Full featured Rx FIFO with storage capacity for 6 frames

- DMA request for Rx FIFO

- Programmable clock source to the CAN Protocol Interface, either bus clock or crystal oscillator

- 100% backward compatibility with previous FlexCAN version

- 8 FlexCAN instances

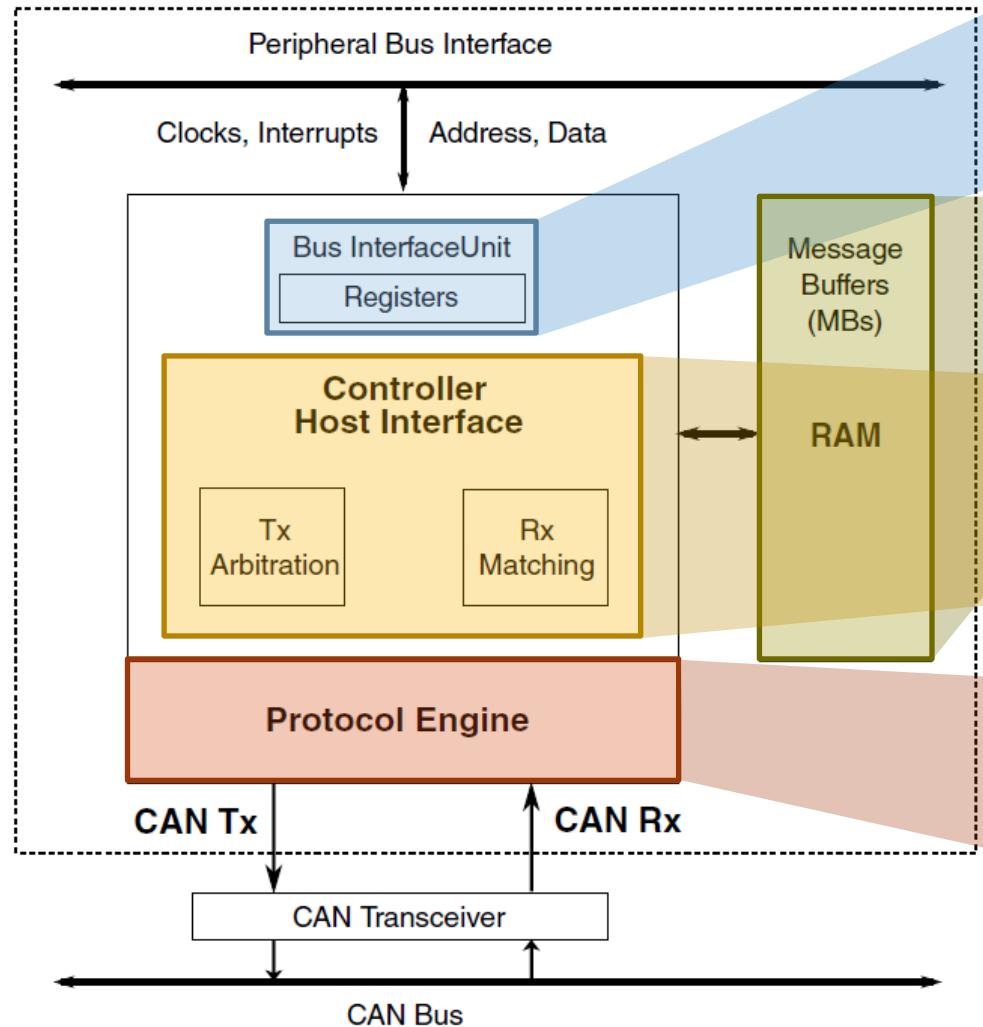

# Hands-on – CAN: Theory

Access to and from the internal interface bus (clocks, address and data buses, interrupts, DMA and test signals)

Embedded RAM dedicated to the FlexCAN

Message buffer selection for reception and transmission (arbitration and ID matching algorithms)

Serial communication on the CAN bus (RAM access requests for rx and tx frames, rx messages validation, error handling)

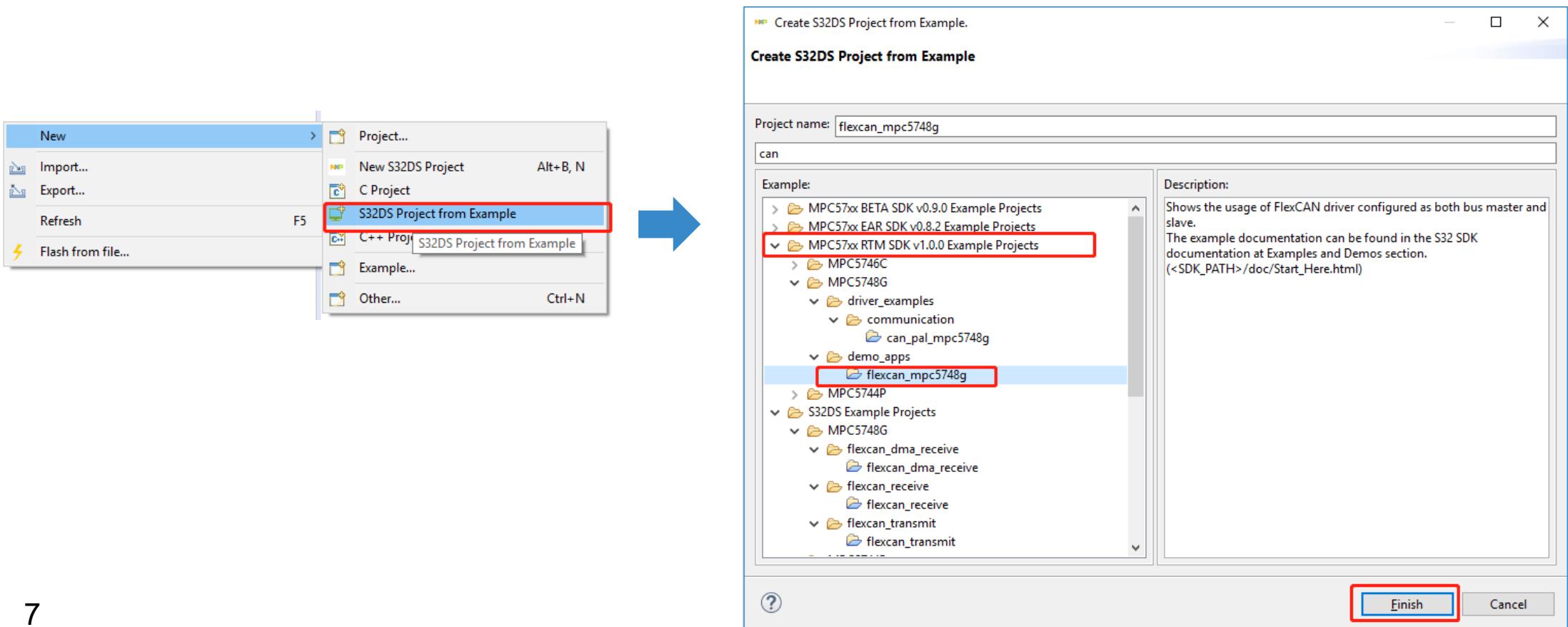

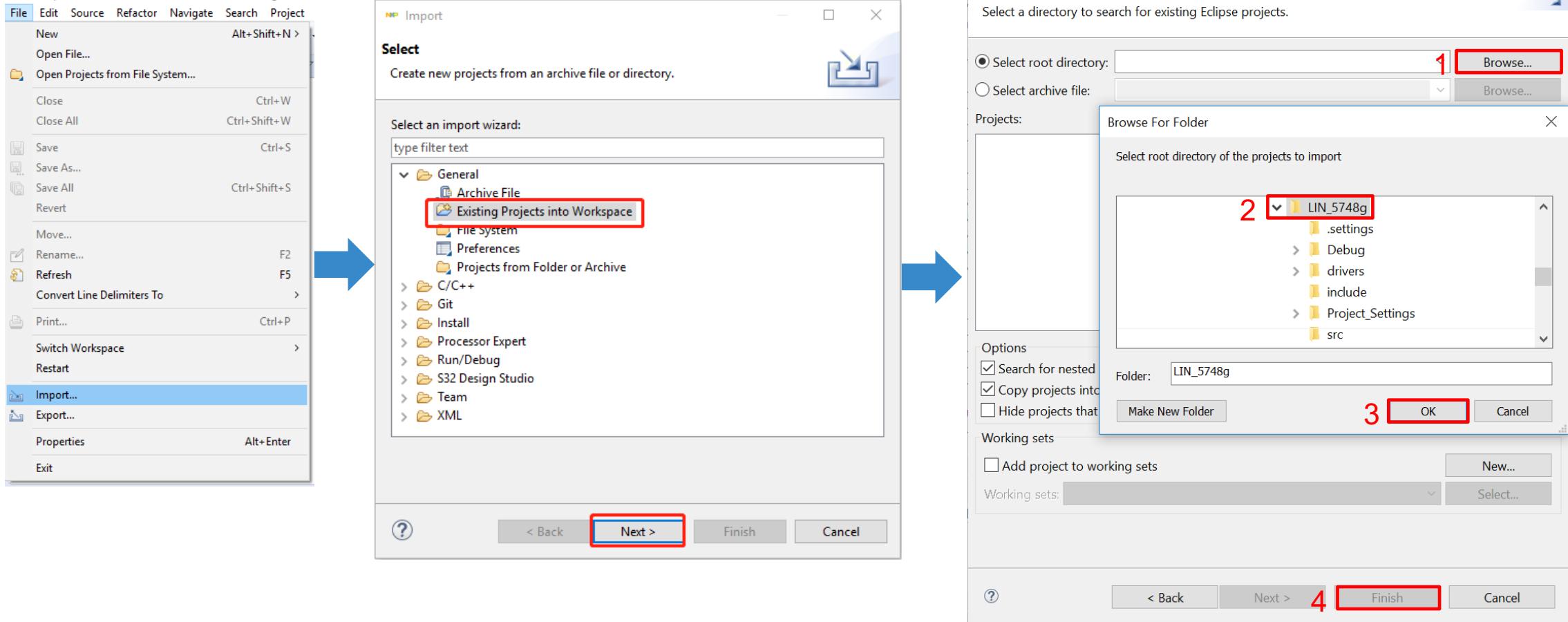

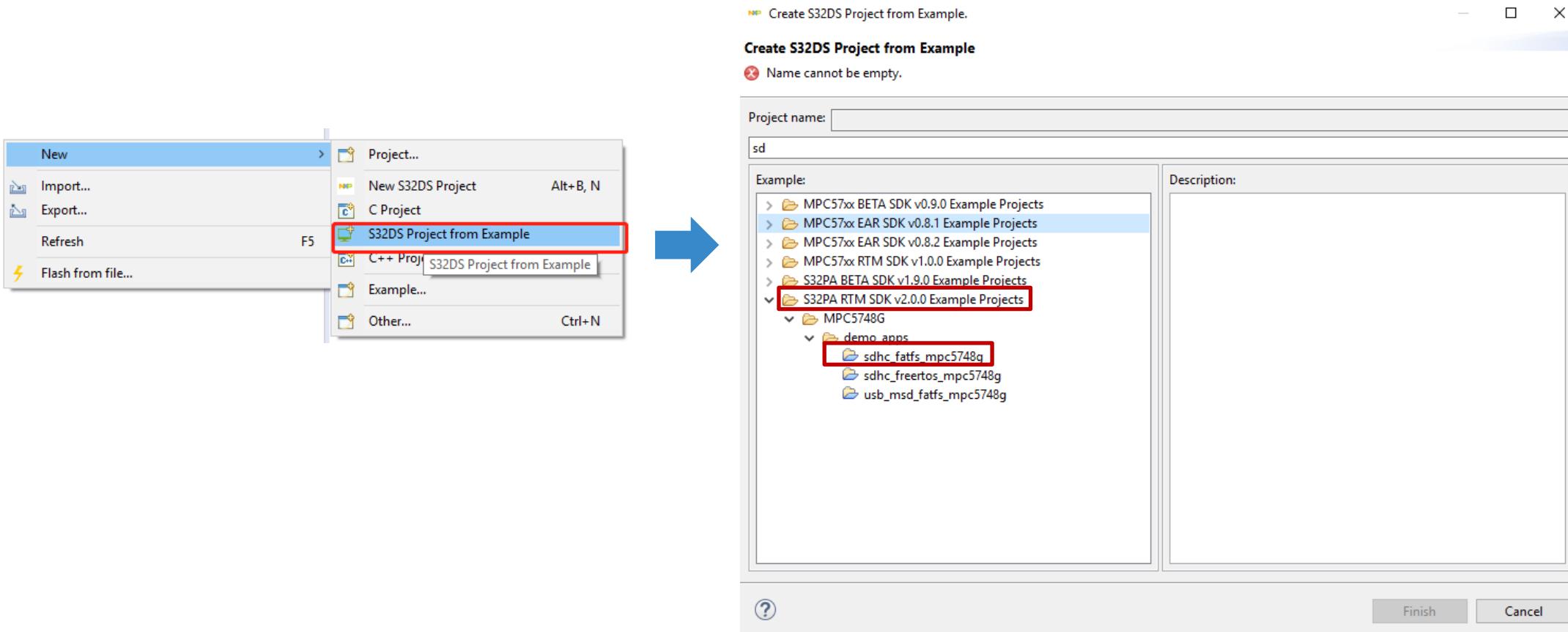

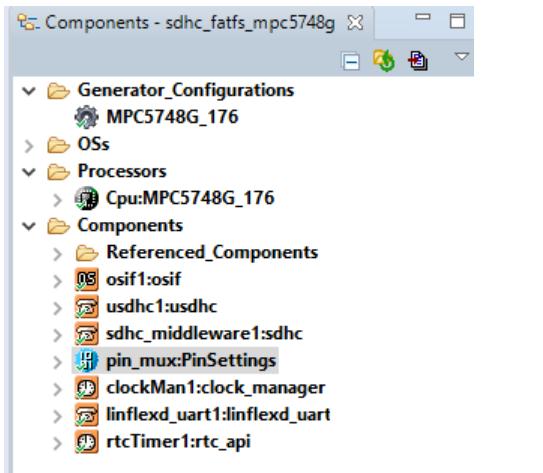

# Hands-on – CAN: Import Existing Project

- Create S32DS project from Example:

- File->New->New S32DS Project from Example

- Select: **flexcan\_mpc5748g** from **MPC57xxRTM SDK v1.0.0 Example Projects**

# Hands-on – CAN: Modify

- The example of flexcan\_mpc5748g project is suit to DEVKIT

- How to modify?

DEVKIT

1. Peripheral Power Supply

2. CAN Phy enablement

3. The Ports of CAN

4. CAN configuration

5. Application code of the main.c

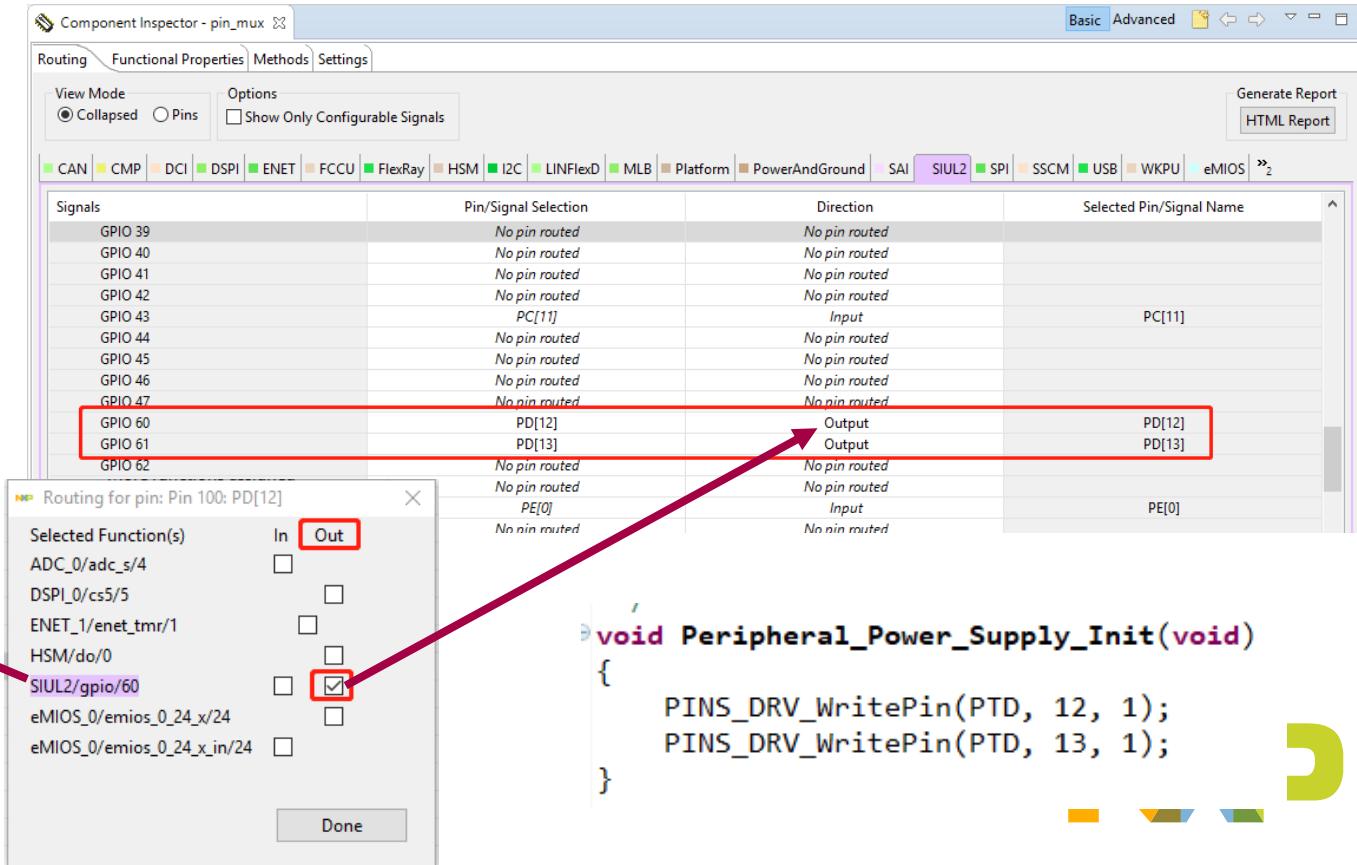

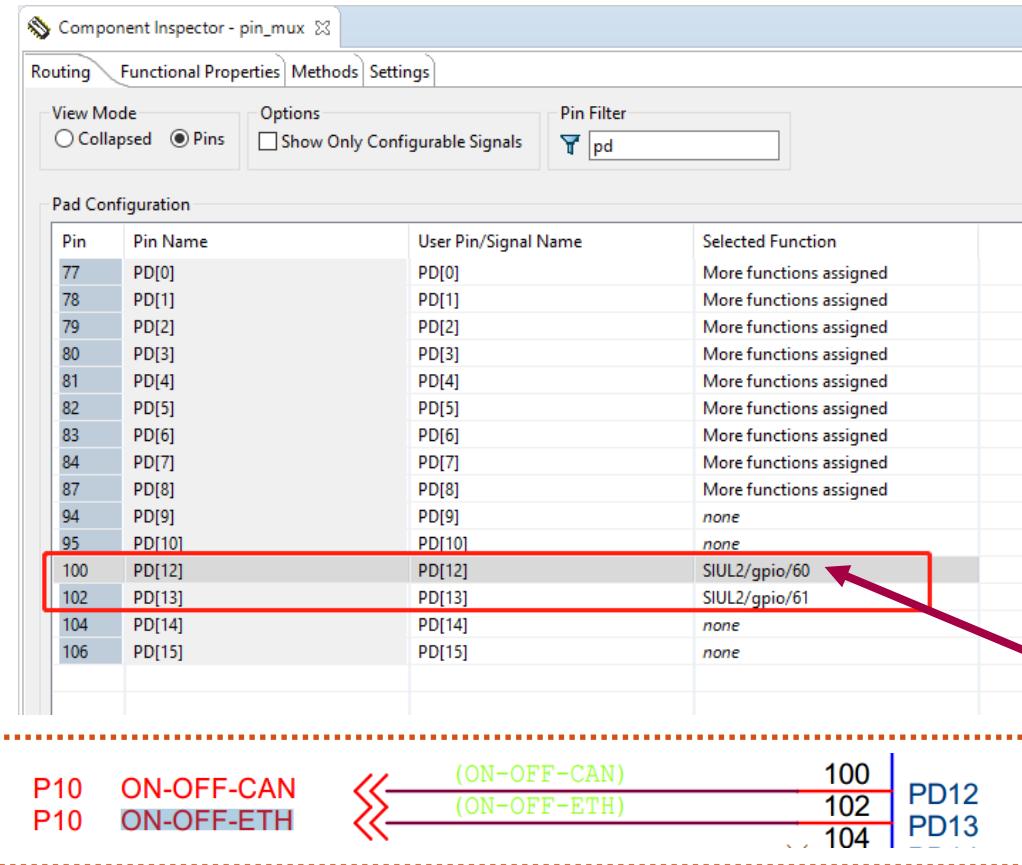

# Hands-on – CAN: Modify-Peripheral Power Supply

- Enable the peripheral power supply

- Open ‘pin\_mux’ component in ‘Component Inspector’ to configure pin routing

- SIUL2 tab -> GPIO 60 (61) > select the pin (one option) + direction output

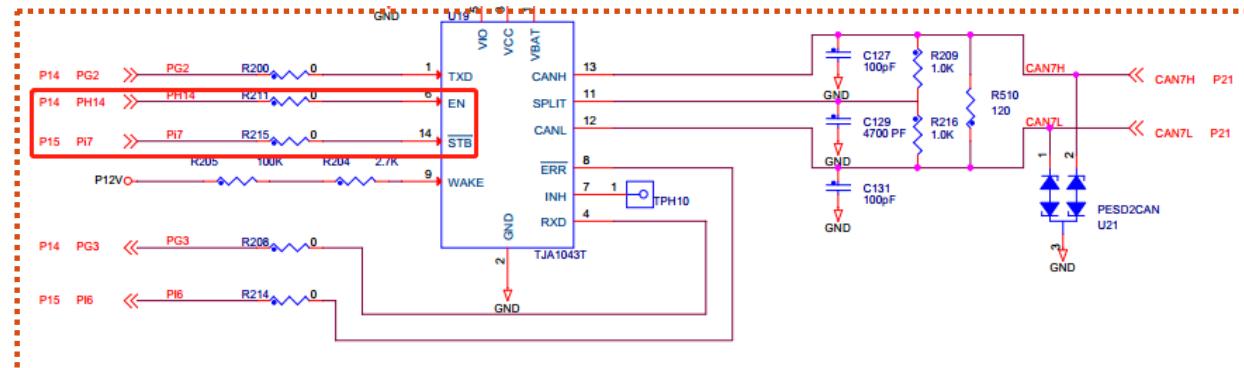

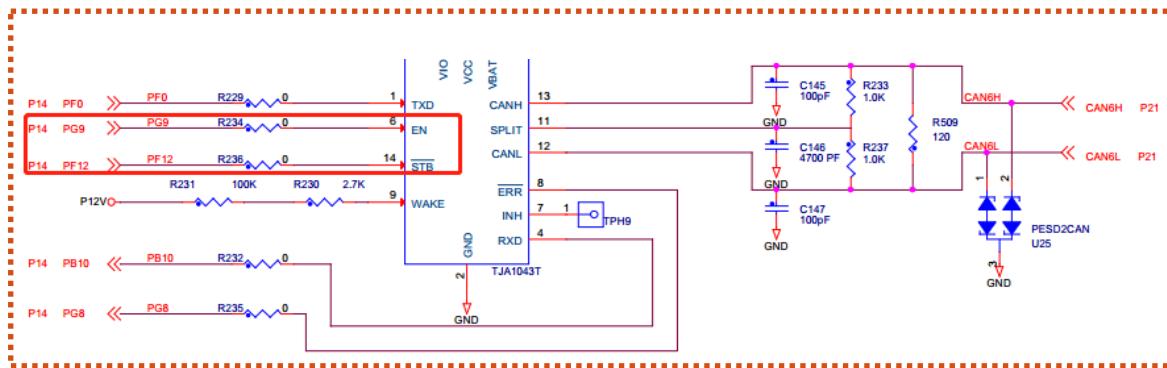

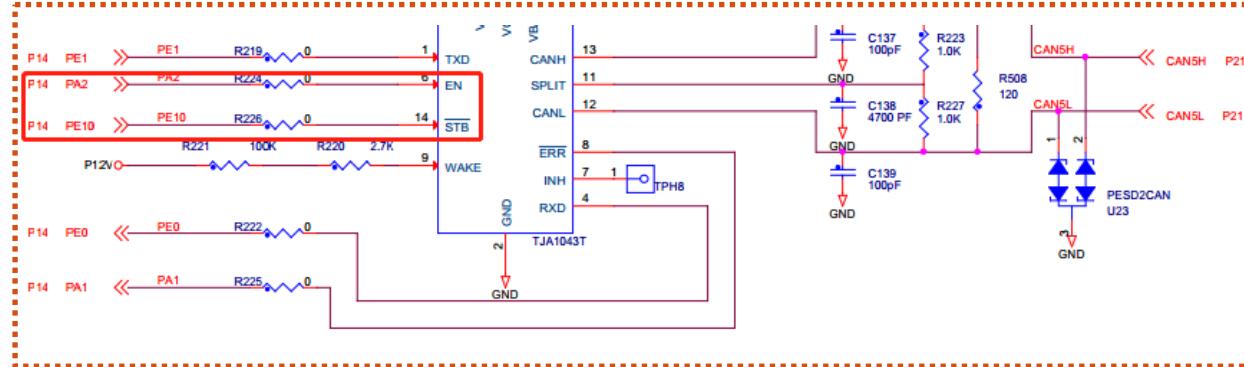

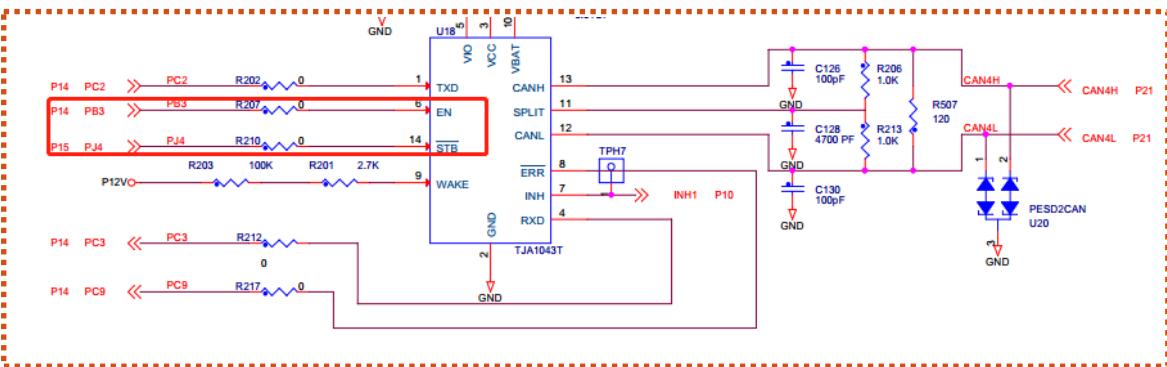

# Hands-on – CAN: Modify-CAN Phy Enablement

- Configure the CAN4~7 Phy(TJA1043T) GPIO

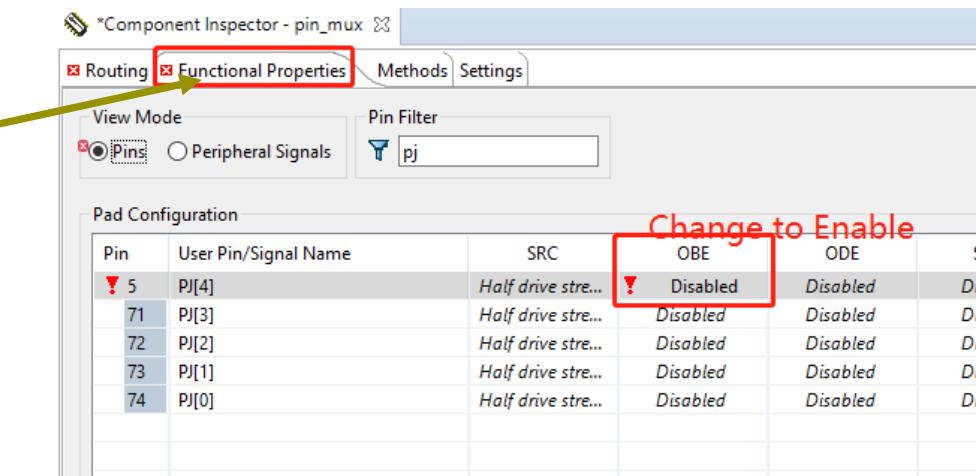

# Hands-on – CAN: Modify-CAN Phy Enablement

- The configuration method is similar to the slides on the previous page

| CAN Phy  | port   | routing        | direction | Note               |

|----------|--------|----------------|-----------|--------------------|

| CAN4 EN  | PB[3]  | SIUL2/gpio/19  | Out       |                    |

| CAN4 STB | PJ[4]  | SIUL2/gpio/148 | Out       | There is a problem |

| CAN5 EN  | PA[2]  | SIUL2/gpio/2   | Out       |                    |

| CAN5 STB | PE[10] | SIUL2/gpio/74  | Out       |                    |

| CAN6 EN  | PG[9]  | SIUL2/gpio/105 | Out       |                    |

| CAN6 STB | PF[12] | SIUL2/gpio/92  | Out       |                    |

| CAN7 EN  | PH[14] | SIUL2/gpio/126 | Out       |                    |

| CAN7 STB | PI[7]  | SIUL2/gpio/135 | Out       |                    |

Note: The default configuration of PJ[4] is input, we need to change the OBE to Enabled mode enable output.

```

void CAN_TJA1043T_Enable(void)

{

PINS_DRV_WritePin(PTB, 3, 1); /* Initialize high CAN4 EN */

PINS_DRV_WritePin(PTA, 2, 1); /* Initialize high CAN5 EN */

PINS_DRV_WritePin(PTG, 9, 1); /* Initialize high CAN6 EN */

PINS_DRV_WritePin(PTH, 14, 1); /* Initialize high CAN7 EN */

PINS_DRV_WritePin(PTJ, 4, 1); /* Initialize high CAN4 STB */

PINS_DRV_WritePin(PTE, 10, 1); /* Initialize high CAN5 STB */

PINS_DRV_WritePin(PTF, 12, 1); /* Initialize high CAN6 STB */

PINS_DRV_WritePin(PTI, 7, 1); /* Initialize high CAN7 STB */

}

```

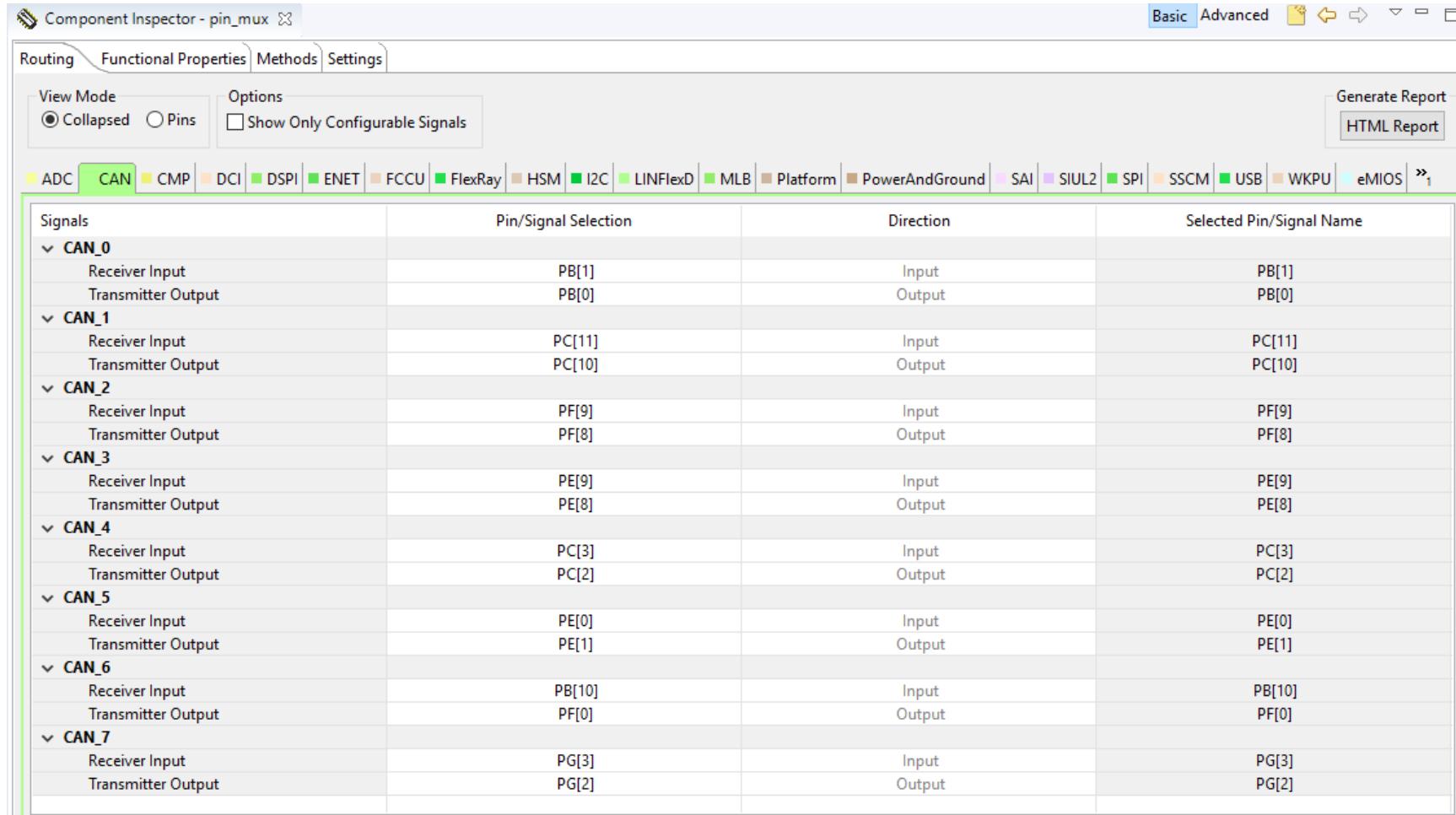

# Hands-on – CAN: Modify- Ports of CAN

- In ‘pin\_mux’ component → Routing(Collapsed)– select ‘CAN’

- Configuration the ports according to the schematic.

The screenshot shows the 'Component Inspector - pin\_mux' window with the 'Routing' tab selected. The 'View Mode' is set to 'Collapsed'. The 'Signals' section lists eight CAN ports (CAN\_0 to CAN\_7) with their receiver and transmitter pins mapped to specific pins on the chip. The 'Pin/Signal Selection' column shows the physical pins (e.g., PB[1], PC[11], PF[9], PE[9], etc.) and the 'Direction' column indicates whether they are 'Input' or 'Output'. The 'Selected Pin/Signal Name' column shows the final names assigned to these pins.

| Signals            | Pin/Signal Selection | Direction | Selected Pin/Signal Name |

|--------------------|----------------------|-----------|--------------------------|

| CAN_0              |                      |           |                          |

| Receiver Input     | PB[1]                | Input     | PB[1]                    |

| Transmitter Output | PB[0]                | Output    | PB[0]                    |

| CAN_1              |                      |           |                          |

| Receiver Input     | PC[11]               | Input     | PC[11]                   |

| Transmitter Output | PC[10]               | Output    | PC[10]                   |

| CAN_2              |                      |           |                          |

| Receiver Input     | PF[9]                | Input     | PF[9]                    |

| Transmitter Output | PF[8]                | Output    | PF[8]                    |

| CAN_3              |                      |           |                          |

| Receiver Input     | PE[9]                | Input     | PE[9]                    |

| Transmitter Output | PE[8]                | Output    | PE[8]                    |

| CAN_4              |                      |           |                          |

| Receiver Input     | PC[3]                | Input     | PC[3]                    |

| Transmitter Output | PC[2]                | Output    | PC[2]                    |

| CAN_5              |                      |           |                          |

| Receiver Input     | PE[0]                | Input     | PE[0]                    |

| Transmitter Output | PE[1]                | Output    | PE[1]                    |

| CAN_6              |                      |           |                          |

| Receiver Input     | PB[10]               | Input     | PB[10]                   |

| Transmitter Output | PF[0]                | Output    | PF[0]                    |

| CAN_7              |                      |           |                          |

| Receiver Input     | PG[3]                | Input     | PG[3]                    |

| Transmitter Output | PG[2]                | Output    | PG[2]                    |

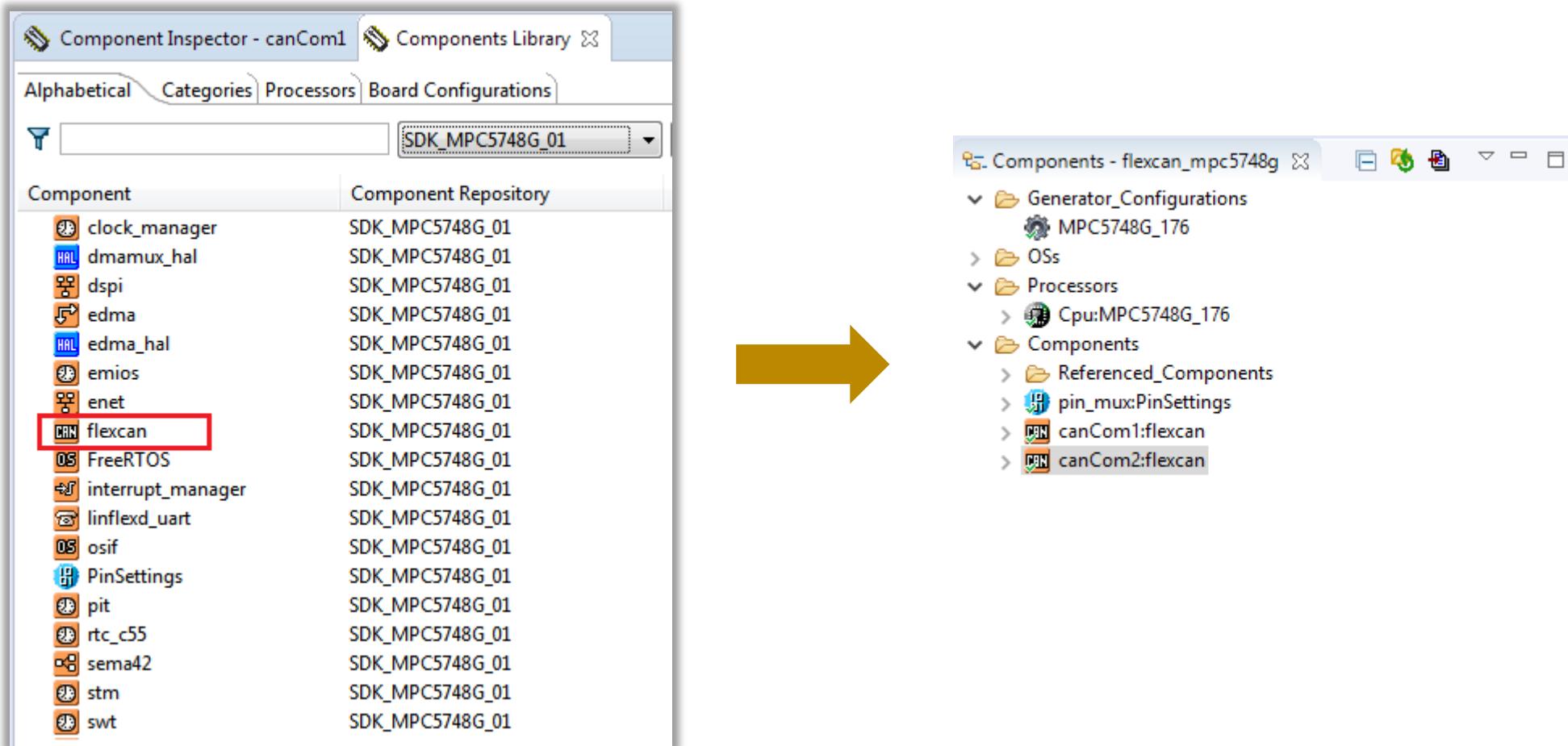

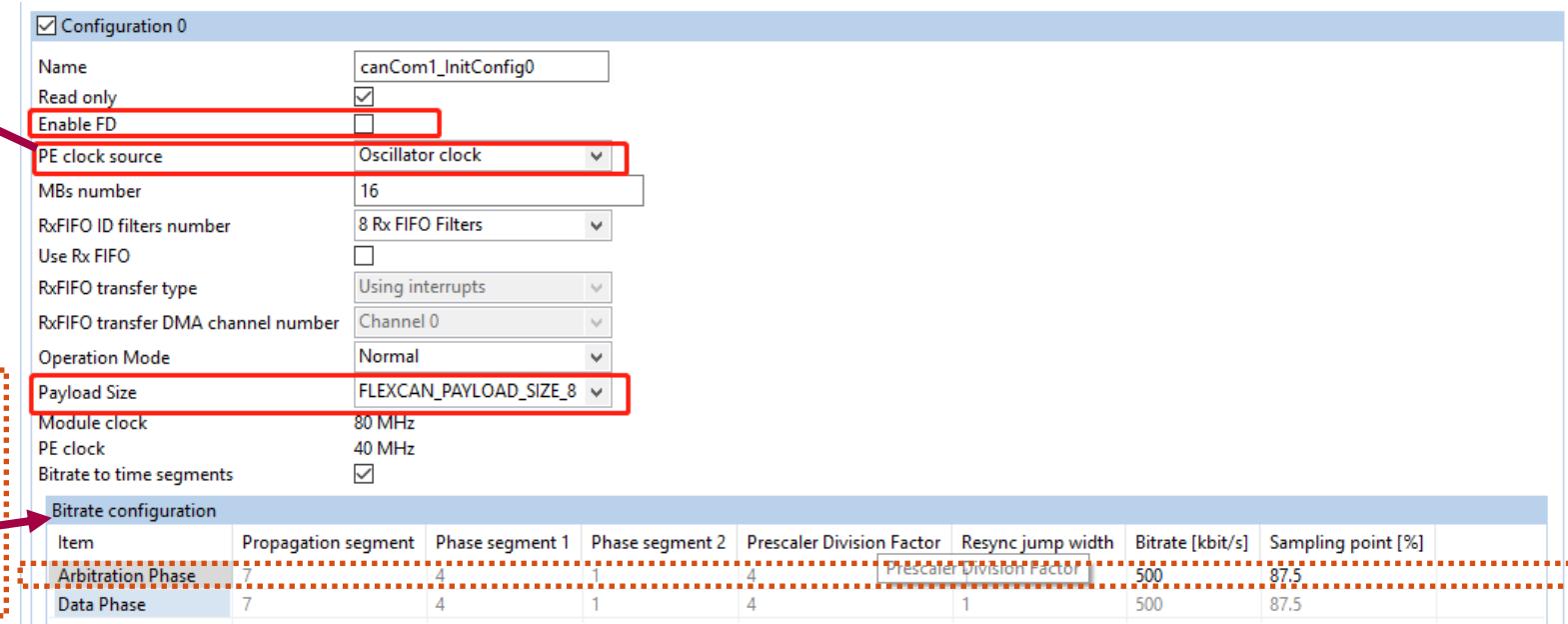

# Hands-on – CAN: Modify- CAN configuration

- From ‘Components Library’ view, double-click ‘flexcan’ component to add it the project

# Hands-on – CAN: Modify- CAN configuration

- No need to change default configuration for CAN:

- standard CAN (no FD), minimum payload, 500 kbps

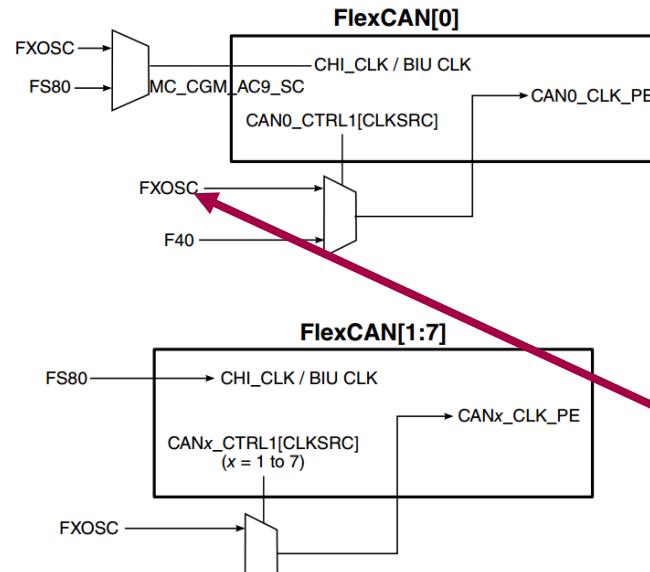

NOTE: The multiplexers for all FlexCAN modules are located outside of the module, but are controlled by registers inside the FlexCAN modules.

Equation:

PE clock(40MHz)=

((propagation segment+1)+(segment1+1)+(segment2+1)+1)

\*(Prescaler Division +1)\*(Bitrate)

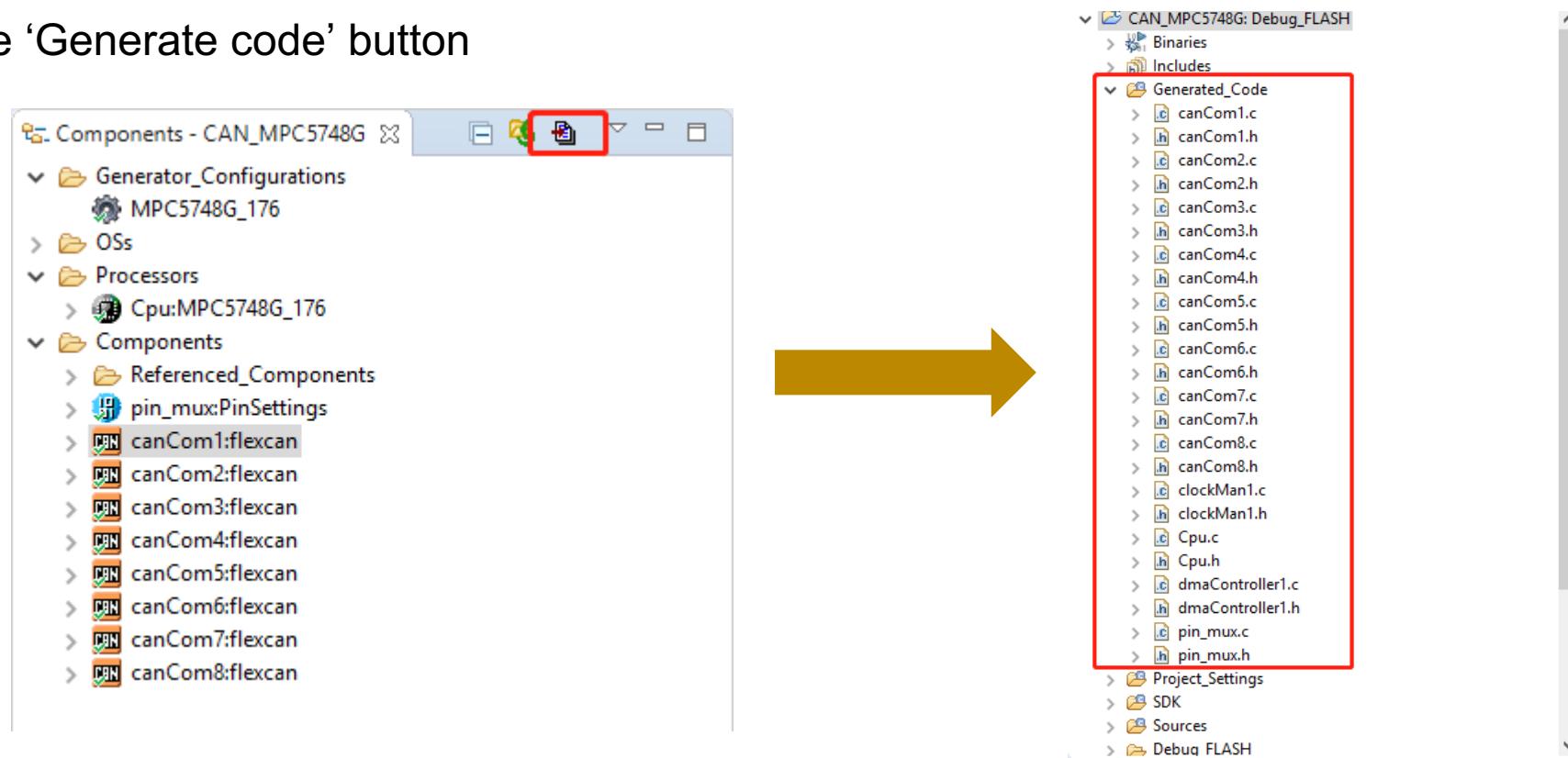

# Hands-on – CAN: Modify- CAN configuration

- After all the CAN configurations are complete, the components window should be like this

-Hit the ‘Generate code’ button

# Hands-on – CAN: Application Code

- Open the main.c file in text editor view

You can refer to the sample project (**can\_mpc5748g**) we provided to modify the main.c file. You can also replace it directly.

## Note:

The sending and receiving function of this project is realized separately, which needs to be controlled by macros.

```

/* Use this define to specify if the application use to send or receive CAN message */

#define CAN_SEND

//#define CAN_RECEIVE

```

# Hands-on – CAN: Application Code

## (1) Peripheral Power Supply:

```

185 int main(void)

186 {

187     uint32_t count = 0;

188     uint8_t Tx_Buffer[8] = {0};

189     uint8_t TxNumber = 0;

190     /** Processor Expert internal initialization. DON'T REMOVE THIS CODE!!

191     #ifdef PEX_RTOS_INIT

192         PEX_RTOS_INIT();           /* Initialization of the selected RTOS */

193     #endif

194     /** End of Processor Expert internal initialization.

195

196     /* Do the initializations required for this application */

197     BoardInit();

198     Peripheral_Power_Supply_Init();

199     CAN_TJA1043T_Enable();

```

```

150 /*

151  * Peripheral Power Supply

152  */

153 void Peripheral_Power_Supply_Init(void)

154 {

155     PINS_DRV_WritePin(PTD, 12, 1);

156     PINS_DRV_WritePin(PTD, 13, 1);

157 }

```

# Hands-on – CAN: Application Code

## (2) CAN4~CAN7 `S Phy (TJA1043T) Enable:

```

185 int main(void)

186 {

187     uint32_t count = 0;

188     uint8_t Tx_Buffer[8] = {0};

189     uint8_t TxNumber = 0;

190     /** Processor Expert internal initialization. DON'T REMOVE THIS CODE!

191     #ifdef PEX_RTOS_INIT

192         PEX_RTOS_INIT(); /* Initialization of the selected

193     #endif

194     /** End of Processor Expert internal initialization.

195

196     /* Do the initializations required for this application */

197     BoardInit();

198     Peripheral_Power_Supply_Init();

199     CAN_TJA1043T_Enable();

```

```

159 void CAN_TJA1043T_Enable(void)

160 {

161     PINS_DRV_WritePin(PTB, 3, 1); /* Initialize high CAN4 EN */

162     PINS_DRV_WritePin(PTA, 2, 1); /* Initialize high CAN5 EN */

163     PINS_DRV_WritePin(PTG, 9, 1); /* Initialize high CAN6 EN */

164     PINS_DRV_WritePin(PTH, 14, 1); /* Initialize high CAN7 EN */

165

166     PINS_DRV_WritePin(PTJ, 4, 1); /* Initialize high CAN4 STB */

167     PINS_DRV_WritePin(PTE, 10, 1); /* Initialize high CAN5 STB */

168     PINS_DRV_WritePin(PTF, 12, 1); /* Initialize high CAN6 STB */

169     PINS_DRV_WritePin(PTI, 7, 1); /* Initialize high CAN7 STB */

170 }

```

# Hands-on – CAN: Application Code

## (3) Sending data via CAN:

### Note:

When testing , we need to connect the port of CAN which need tested, otherwise it will wait for the completion of sending.

Eg. Testing CAN3

```

#ifdef CAN_SEND

void SendCANData(uint32_t mailbox, uint32_t messageId, uint8_t * data, uint32_t len)

{

/* Set information about the data to be sent

* - 1 byte in length

* - Standard message ID

* - Bit rate switch enabled to use a different bitrate for the data segment

* - Flexible data rate enabled

* - Use zeros for FD padding

*/

flexcan_data_info_t dataInfo =

{

.data_length = len,

.msg_id_type = FLEXCAN_MSG_ID_STD,

.enable_brs = true,

.fd_enable = true,

.fd_padding = 0U

};

/* Execute send non-blocking */

// while(FLEXCAN_DRV_Send(INST_CANCOM1, mailbox, &dataInfo, messageId, data) == STATUS_BUSY); /*CAN0*/

// while(FLEXCAN_DRV_Send(INST_CANCOM2, mailbox, &dataInfo, messageId, data) == STATUS_BUSY); /*CAN1*/

// while(FLEXCAN_DRV_Send(INST_CANCOM3, mailbox, &dataInfo, messageId, data) == STATUS_BUSY); /*CAN2*/

while(FLEXCAN_DRV_Send(INST_CANCOM4, mailbox, &dataInfo, messageId, data) == STATUS_BUSY); /*CAN3*/

// while(FLEXCAN_DRV_Send(INST_CANCOM5, mailbox, &dataInfo, messageId, data) == STATUS_BUSY); /*CAN4*/

// while(FLEXCAN_DRV_Send(INST_CANCOM6, mailbox, &dataInfo, messageId, data) == STATUS_BUSY); /*CAN5*/

// while(FLEXCAN_DRV_Send(INST_CANCOM7, mailbox, &dataInfo, messageId, data) == STATUS_BUSY); /*CAN6*/

// while(FLEXCAN_DRV_Send(INST_CANCOM8, mailbox, &dataInfo, messageId, data) == STATUS_BUSY); /*CAN7*/

}

#endif

```

# Hands-on – CAN: Application Code

## (4) Receiving data via CAN:

### Note:

Unlike CAN sending, you can test the receive on any port.

```

#ifdef CAN_RECEIVE

/* Define receive buffer */

flexcan_msghuff_t recvBuff;

/* Start receiving data in RX_MAILBOX. */

FLEXCAN_DRV_Receive(INST_CANCOM1, RX_MAILBOX, &recvBuff);

FLEXCAN_DRV_Receive(INST_CANCOM2, RX_MAILBOX, &recvBuff);

FLEXCAN_DRV_Receive(INST_CANCOM3, RX_MAILBOX, &recvBuff);

FLEXCAN_DRV_Receive(INST_CANCOM4, RX_MAILBOX, &recvBuff);

FLEXCAN_DRV_Receive(INST_CANCOM5, RX_MAILBOX, &recvBuff);

FLEXCAN_DRV_Receive(INST_CANCOM6, RX_MAILBOX, &recvBuff);

FLEXCAN_DRV_Receive(INST_CANCOM7, RX_MAILBOX, &recvBuff);

FLEXCAN_DRV_Receive(INST_CANCOM8, RX_MAILBOX, &recvBuff);

/* Wait until the previous FlexCAN receive is completed */

while((FLEXCAN_DRV_GetTransferStatus(INST_CANCOM1, RX_MAILBOX) & \

FLEXCAN_DRV_GetTransferStatus(INST_CANCOM2, RX_MAILBOX) & \

FLEXCAN_DRV_GetTransferStatus(INST_CANCOM3, RX_MAILBOX) & \

FLEXCAN_DRV_GetTransferStatus(INST_CANCOM4, RX_MAILBOX) & \

FLEXCAN_DRV_GetTransferStatus(INST_CANCOM5, RX_MAILBOX) & \

FLEXCAN_DRV_GetTransferStatus(INST_CANCOM6, RX_MAILBOX) & \

FLEXCAN_DRV_GetTransferStatus(INST_CANCOM7, RX_MAILBOX) & \

FLEXCAN_DRV_GetTransferStatus(INST_CANCOM8, RX_MAILBOX) ) == STATUS_BUSY);

/* Check the received message ID and payload */

if(recvBuff.dataLen == 8)

{

count++;

}

#elif defined CAN_SEND

```

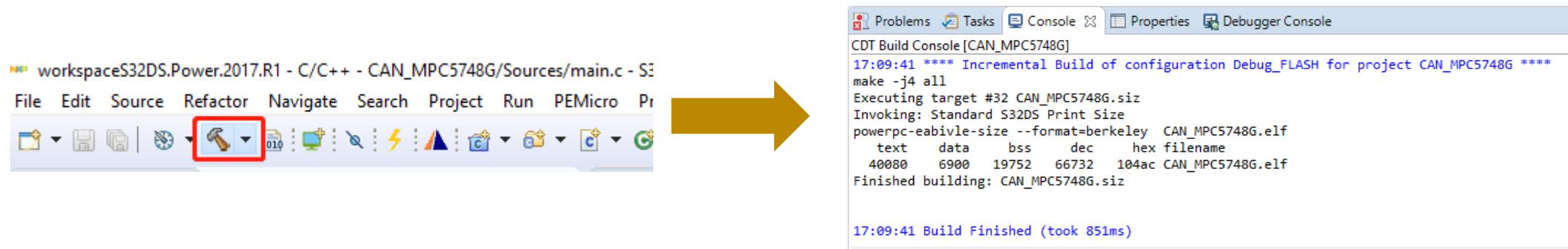

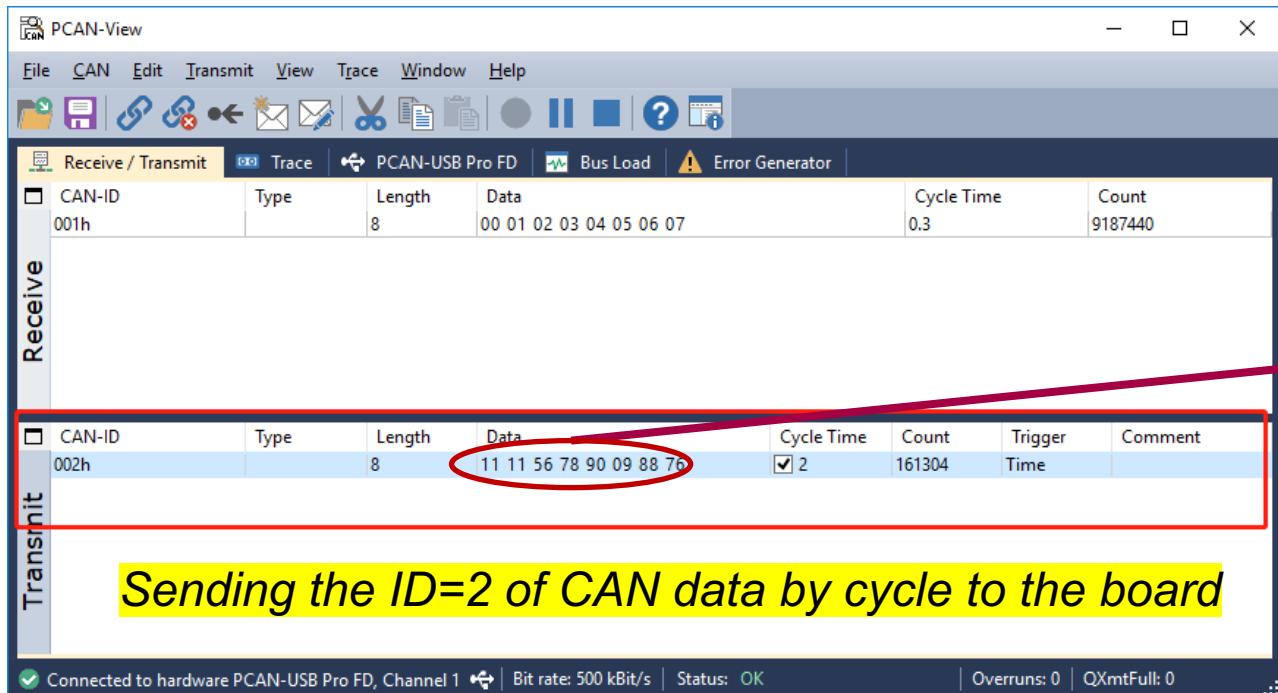

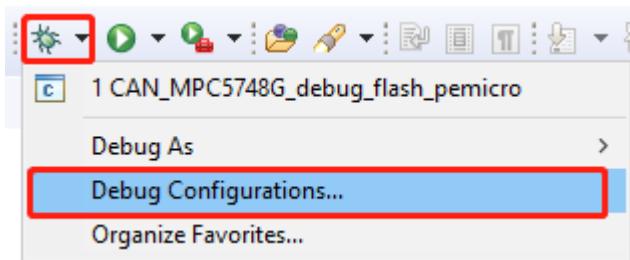

# Hands-on – CAN: Build and Debug

- Click the ‘build project’ button – make sure there are no compilation errors

- Select the correct debug configuration and interface to debug the application

# Hands-on – CAN: Build and Debug

- **TEST: Sending data via CAN:**

- 1) Open the macro of **CAN\_SEND**, commented out **CAN\_RECEIVE**.

- 2) Connect the sending port with PEAK(The test tools we use) through the wire.

- 3) Debug the application.

Code snippet (highlighted in red box):

```

#elif defined CAN_SEND

for(TxNumber=0; TxNumber<8; TxNumber++)

{

Tx_Buffer[TxNumber] = TxNumber;

}

```

*The data of CAN to be send*

Screenshot of the PCAN-View software interface. The 'Receive / Transmit' tab is selected. The 'Receive' table shows a single message entry:

| CAN-ID | Type | Length | Data                    | Cycle Time | Count   |

|--------|------|--------|-------------------------|------------|---------|

| 001h   |      | 8      | 00 01 02 03 04 05 06 07 | 0.3        | 8934553 |

*Receiving the data from CANx port of the board*

The 'Transmit' table is empty.

Bottom status bar: Connected to hardware PCAN-USB Pro FD, Channel 1 | Bit rate: 500 kBit/s | Status: OK | Overruns: 0 | QXmtFull: 0

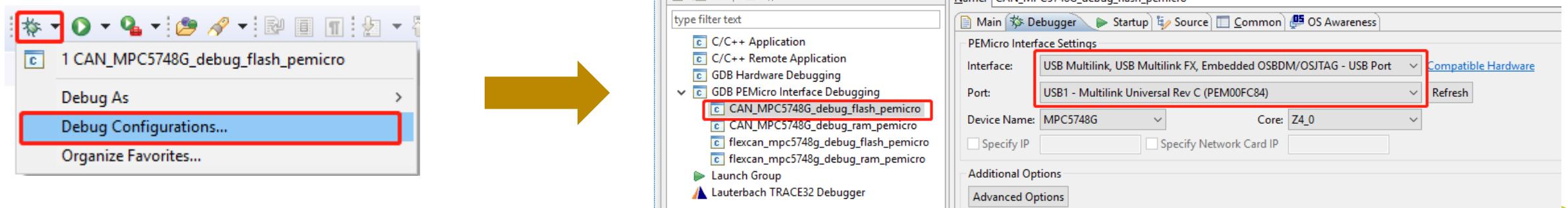

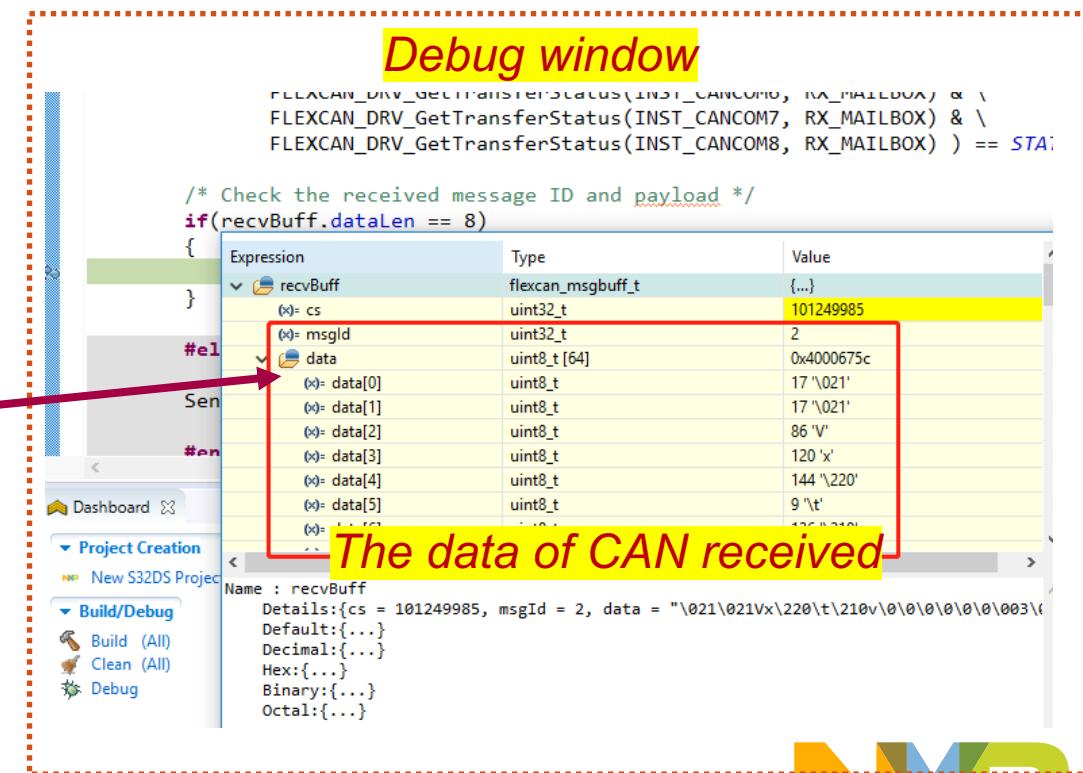

# Hands-on – CAN: Build and Debug

- **TEST: Receiving data via CAN :**

- 1) Open the macro of **CAN\_RECEIVE**, commented out **CAN\_SEND**

- 2) Connect the receiving port with PEAK(The test tools we use) through the wire.

- 3) Debug the application.

# 02.

## Hands-on – CAN\_FD

# Hands-on – CAN\_FD: Objective

- CAN\_FD is configured similarly to CAN.

- This section will be modified based on the previous section(**Hands-on-CAN**).

- Modify the CAN configurations.

- Modify the application code of main.c

- Please refer to section 1 if there is anything unclear

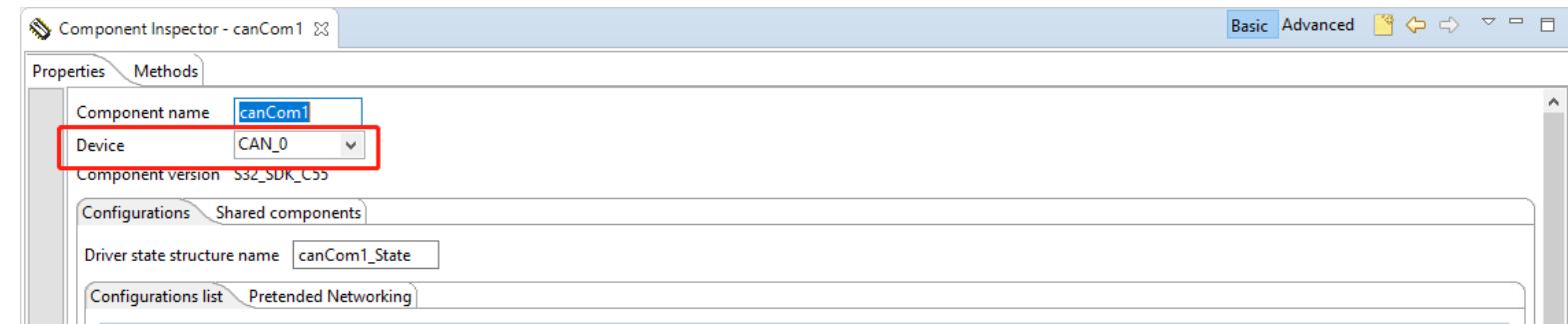

# Hands-on – CAN\_FD: Modify- CAN\_FD configuration

- Need to change default configuration for CAN\_FD:

- standard CAN\_FD, **maximum payload**, **Arbitration Phase**: 500 kbps, **Data Phase**: 2000kbps.

The image shows two windows from a software development environment. The top window is titled 'Component Inspector - canCom1' and displays configuration settings for a component named 'canCom1'. The 'Device' dropdown is set to 'CAN\_0'. The 'Configuration 0' tab is selected, showing fields like 'Name' (canCom1\_InitConfig0), 'Enable FD' (checked), 'PE clock source' (Oscillator clock), 'MBs number' (7), 'Payload Size' (FLEXCAN\_PAYLOAD\_SIZE\_64), and a 'Bitrate configuration' table. The bottom window is titled 'Components - CAN\_FD\_MPC5748G' and lists various components under 'Components', including 'canCom1:flexcan', which is highlighted with a red box. A red arrow points from the 'canCom1:flexcan' entry in the component list to the 'Enable FD' checkbox in the Component Inspector. A dashed red box encloses the 'Equation' and its formula.

**Equation:**

PE clock(40MHz)=

((propagation segment+1)+(segment1+1)+(segment2+1)+1)

\*(Prescaler Division +1)\*(Bitrate)

| Item              | Propagation segment | Phase segment 1 | Phase segment 2 | Prescaler Division Factor | Resync jump width | Bitrate [kbit/s] | Sampling point [%] |

|-------------------|---------------------|-----------------|-----------------|---------------------------|-------------------|------------------|--------------------|

| Arbitration Phase | 7                   | 4               | 1               | 4                         | 1                 | 500              | 87.5               |

| Data Phase        | 15                  | 1               | 1               | 0                         | 1                 | 2000             | 90                 |

# Hands-on – CAN\_FD: Modify - Application Code

## (1) Sending data via CAN:

```

184 */

185 int main(void)

186 {

187     uint32_t count = 0;

188     uint8_t Tx_Buffer[64] = {0};

189     uint8_t TxNumber = 0;

190     /* ... */

#elif defined CAN_SEND

191     for(TxNumber=0; TxNumber<64; TxNumber++)

192     {

193         Tx_Buffer[TxNumber] = TxNumber;

194     }

flexcan_data_info_t TXdataInfo =

195 {

196     .data_length = 64U,

197     .msg_id_type = FLEXCAN_MSG_ID_STD,

198     .enable_brs = true,

199     .fd_enable = true,

200     .fd_padding = 0U

201 };

```

64Bytes of data to be send

(Data: from 0 to 63)

The length of the data to be

send, the max length is 64

# Hands-on – CAN\_FD: Modify - Application Code

## (2) Receiving data via CAN:

```

215  #ifdef CAN_RECEIVE

216  /* Set information about the data to be received

217  * - 1 byte in length

218  * - Standard message ID

219  * - Bit rate switch enabled to use a different bitrate for the data segment

220  * - Flexible data rate enabled

221  * - Use zeros for FD padding

222  */

223  flexcan_data_info_t RXdataInfo =

224  {

225      .data_length = 64U, .data_length = 64U,

226      .msg_id_type = FLEXCAN_MSG_ID_STD,

227      .enable_brs = true,

228      .fd_enable = true,

229      .fd_padding = 0U

230  };

```

The length of the data to be receive, the max length is 64

```

296  /* Check the received message payload */

297  if(recvBuff.dataLen == 64) if(recvBuff.dataLen == 64)

298  {

299      count++;

300  }

```

For debug

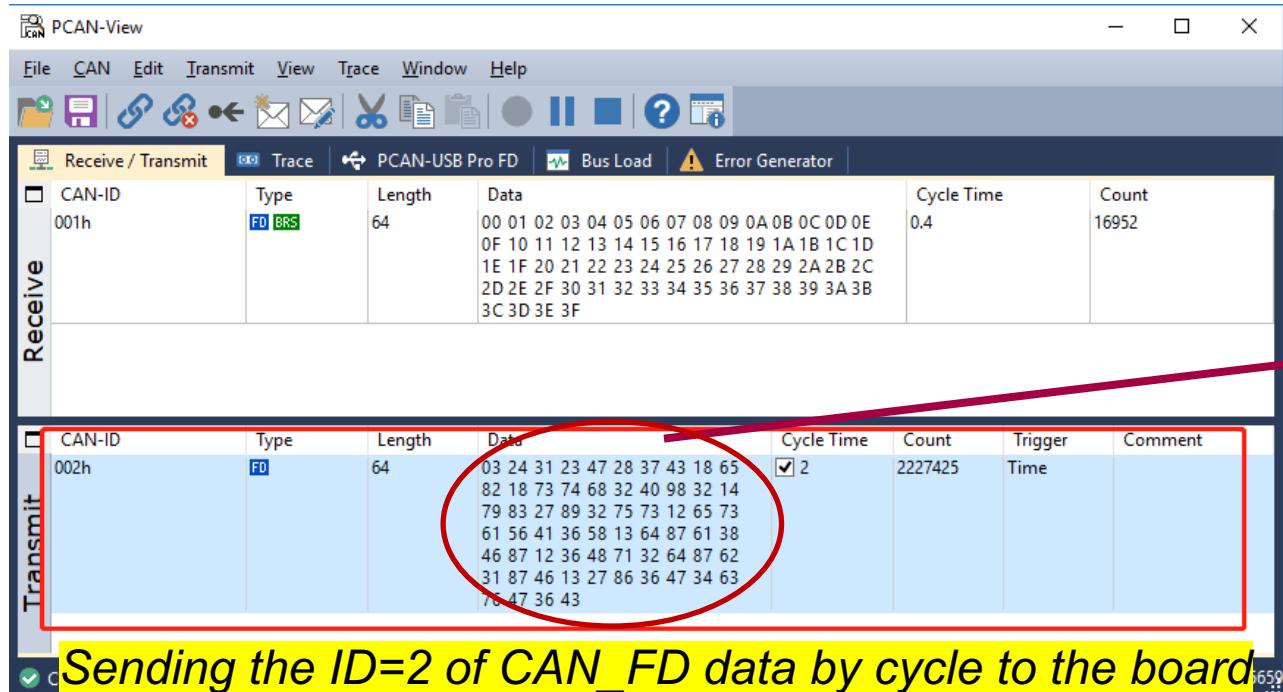

# Hands-on – CAN\_FD: Build and Debug

- TEST: Sending data via CAN\_FD:

- 1) Open the macro of CAN\_SEND, commented out CAN\_RECEIVE.

- 2) Connect the sending port with PEAK(The test tools we use) through the wire.

- 3) Debug the application.

`for(TxNumber=0; TxNumber<64; TxNumber++)

{

Tx_Buffer[TxNumber] = TxNumber;

}`

*The data of CAN to be send*

**PCAN-View**

Receive / Transmit   Trace   PCAN-USB Pro FD   Bus Load   Error Generator

| CAN-ID | Type   | Length | Data                                                                                                                                                                                                        | Cycle Time | Count |

|--------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|

| 001h   | FD BRS | 64     | 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E<br>0F 10 11 12 13 14 15 16 17 18 19 1A 1B 1C 1D<br>1E 1F 20 21 22 23 24 25 26 27 28 29 2A 2B 2C<br>2D 2E 2F 30 31 32 33 34 35 36 37 38 39 3A 3B<br>3C 3D 3E 3F | 0.4        | 16952 |

*Receiving the data from CANx port of the board*

| CAN-ID | Type | Length | Data                                                                                                                                                                                                              | Cycle Time | Count   | Trigger | Comment |

|--------|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|---------|---------|

| 002h   | FD   | 64     | 03 24 31 23 47 28 37 43 18 65<br>82 18 73 74 68 32 40 98 32 14<br>79 83 27 89 32 75 73 12 65 73<br>61 56 41 36 58 13 64 87 61 38<br>46 87 12 36 48 71 32 64 87 62<br>31 87 46 13 27 86 36 47 34 63<br>76 47 36 43 | 2          | 2226138 | Time    |         |

Connected to hardware PCAN-USB Pro FD, Channel 1   Bit rate: 500 kBit/s / 2 MBit/s   Status: OK   Overruns: 0   QXmtFull: 5659

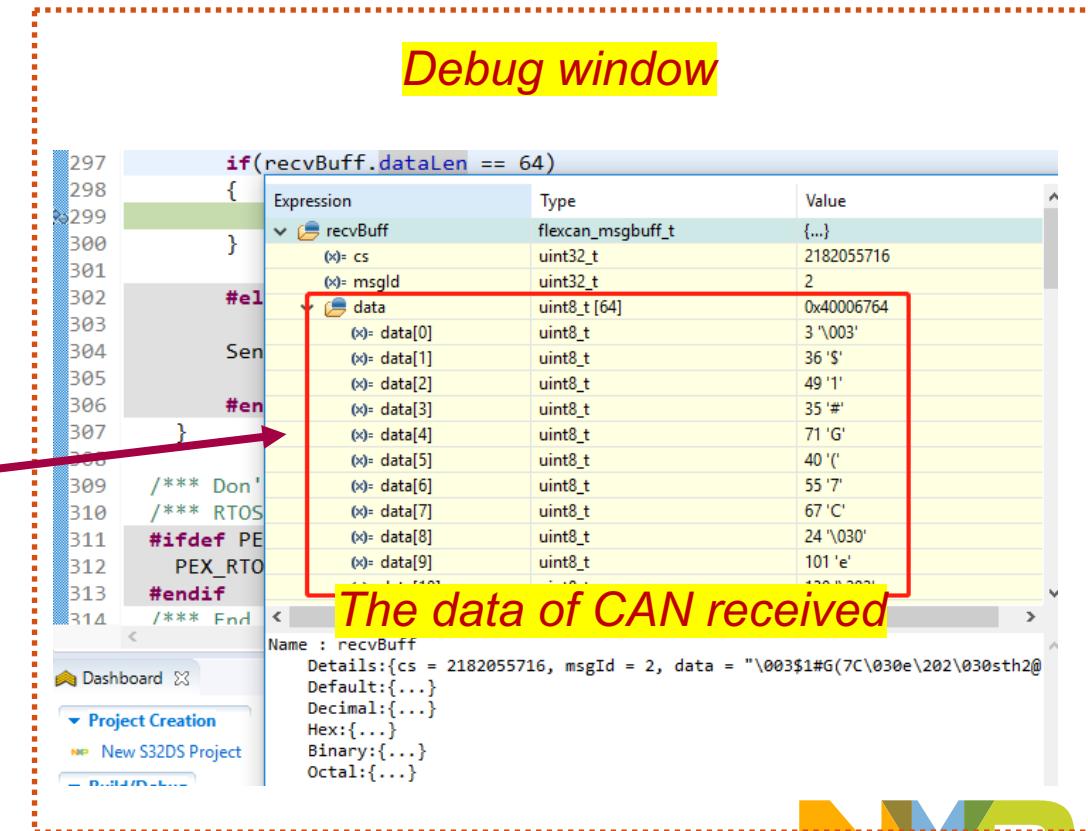

# Hands-on –CAN\_FD: Build and Debug

- **TEST: Receiving data via CAN :**

- 1) Open the macro of **CAN\_RECEIVE**, commented out **CAN\_SEND**

- 2) Connect the receiving port with PEAK(The test tools we use) through the wire.

- 3) Debug the application.

# 03.

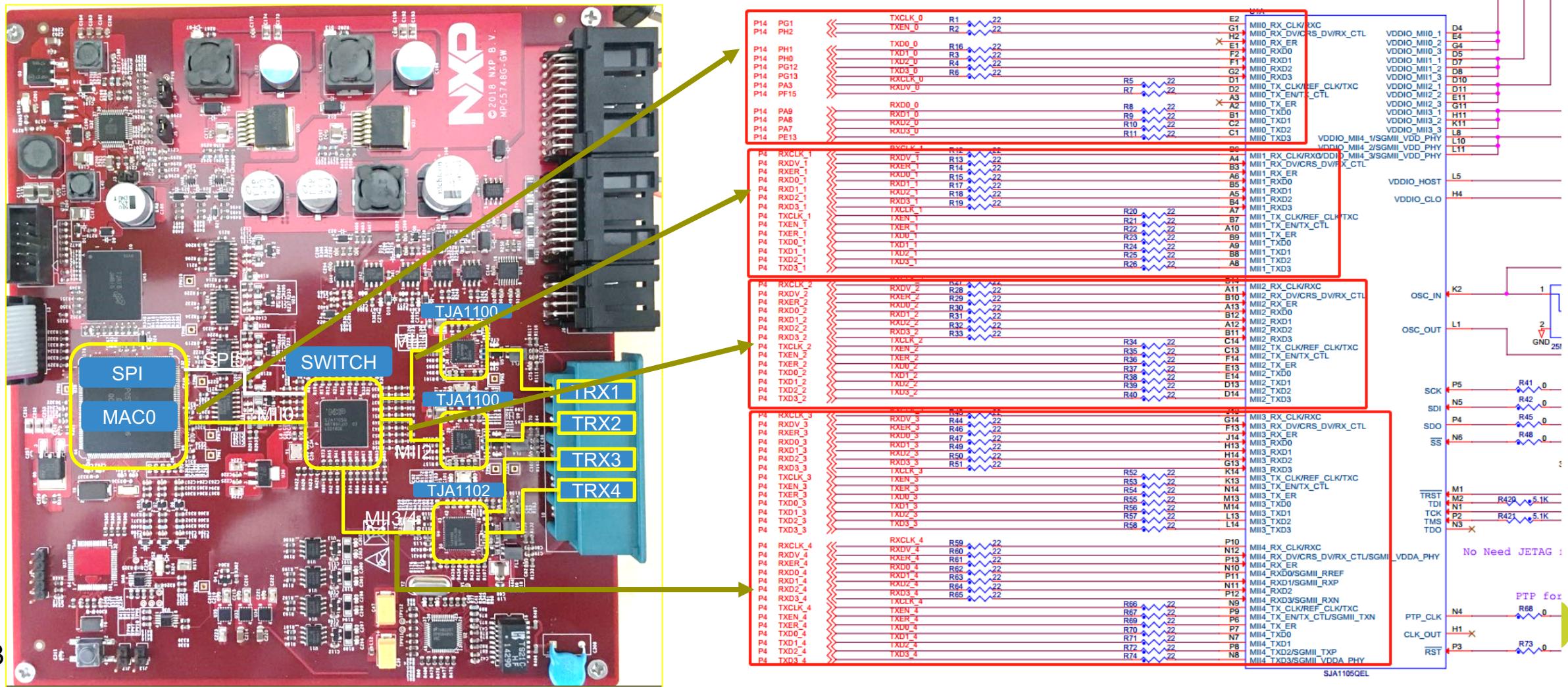

## Hands-on – ENET0+SPI

# Hands-on – ENET0: Objective

- Features of ENET0 module on MPC5748G

- How to set a pin as output/input with SDK

- How to configure the port of ENET0

- How to configure the SPI module to communicate with Switch(SJA1105)

- How to modify an existing SDK project with S32DS to suit this board

- Use CAN0~CAN7 to send CAN message

# Hands-on – ENET0: Resources

- Resources to be used:

- on-board user ENET ports

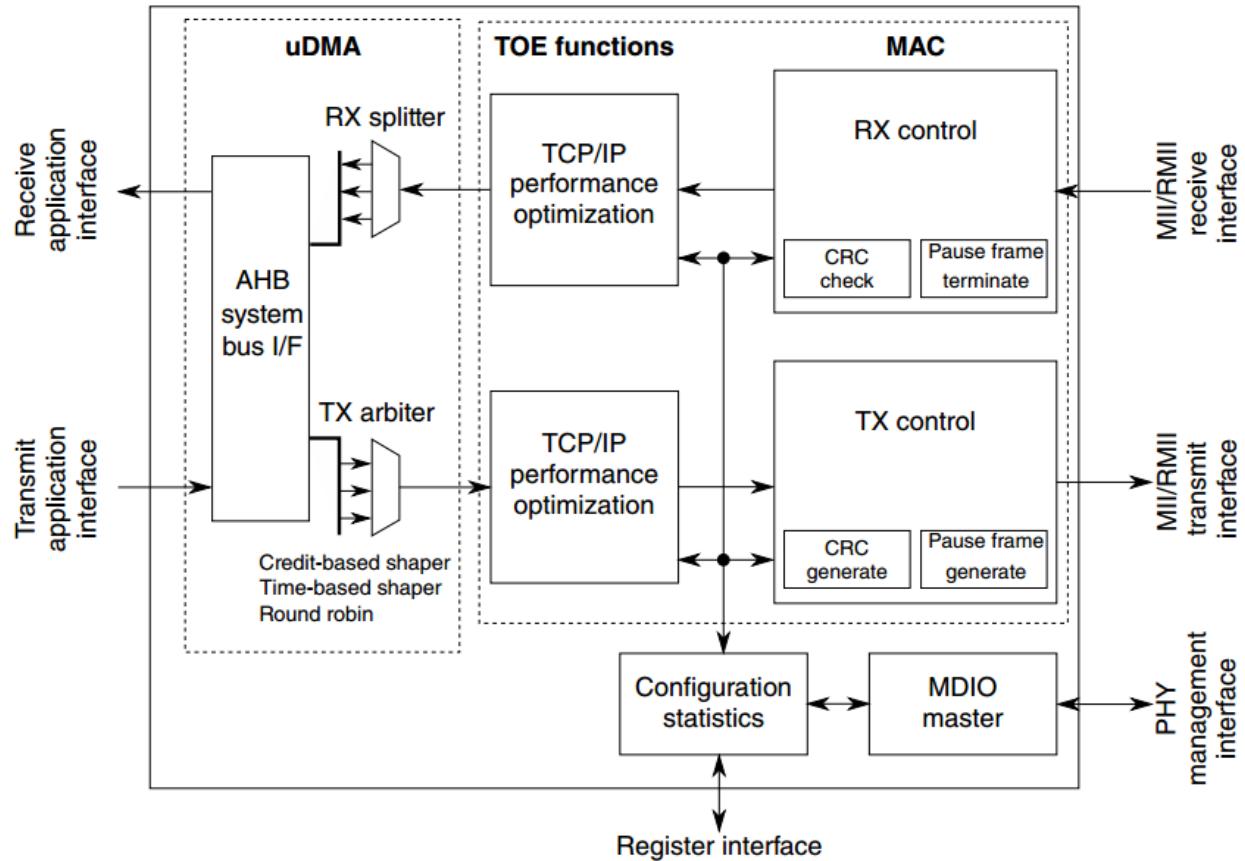

# Hands-on – ENET0: ENET-Theory

- The core implements a dual-speed 10/100-Mbit/s Ethernet MAC compliant with the IEEE802.3-2002 standard. The MAC layer provides compatibility with half- or fullduplex 10/100-Mbit/s Ethernet LANs.

- The MAC operation is fully programmable and can be used in Network Interface Card(NIC), bridging, or switching applications. The core implements the remote network monitoring (RMON) counters according to IETF RFC 2819.

- The programmable Ethernet MAC with IEEE 1588 integrates a standard IEEE 802.3 Ethernet MAC with a time-stamping module. The IEEE 1588 standard provides accurate clock synchronization for distributed control nodes for industrial automation applications.

# Hands-on – ENET0: SPI-Theory

- Full-duplex, three-wire synchronous transfers

- Master mode

- Slave mode

- Data streaming operation in Slave mode with continuous slave selection

- Buffered transmit operation using the transmit first in first out (TX FIFO) with depth of 4 entries

- Support for 8/16-bit accesses to the PUSH TX FIFO Register Data Field

- Buffered receive operation using the receive FIFO (RX FIFO) with depth of 4 entries

- Asynchronous clocking scheme for Register and Protocol Interfaces

- TX and RX FIFOs can be disabled individually for low-latency updates to SPI queues

- Visibility into TX and RX FIFOs for ease of debugging

- 6 peripheral chip selects (PCSes), expandable to 64 with external demultiplexer

- Deglitching support for up to 32 peripheral chip selects (PCSes) with external demultiplexer

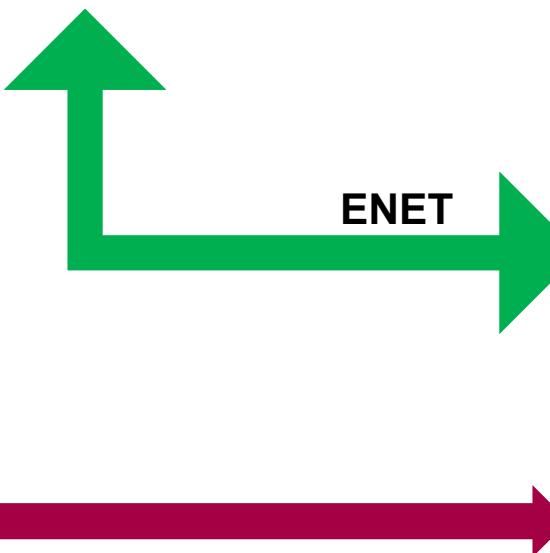

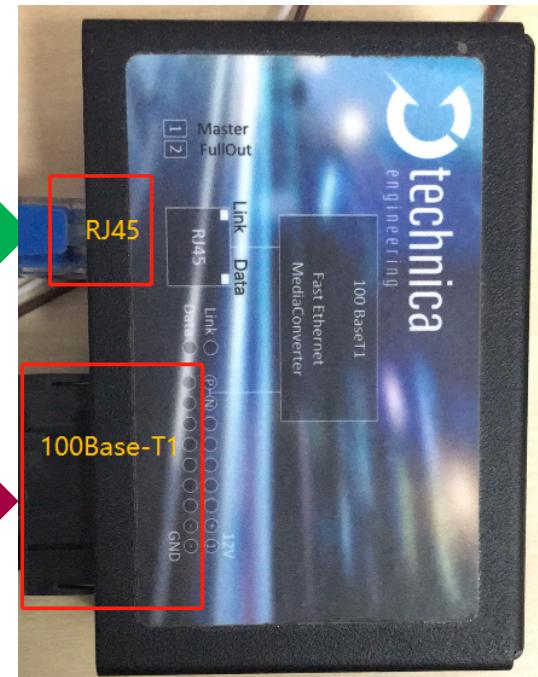

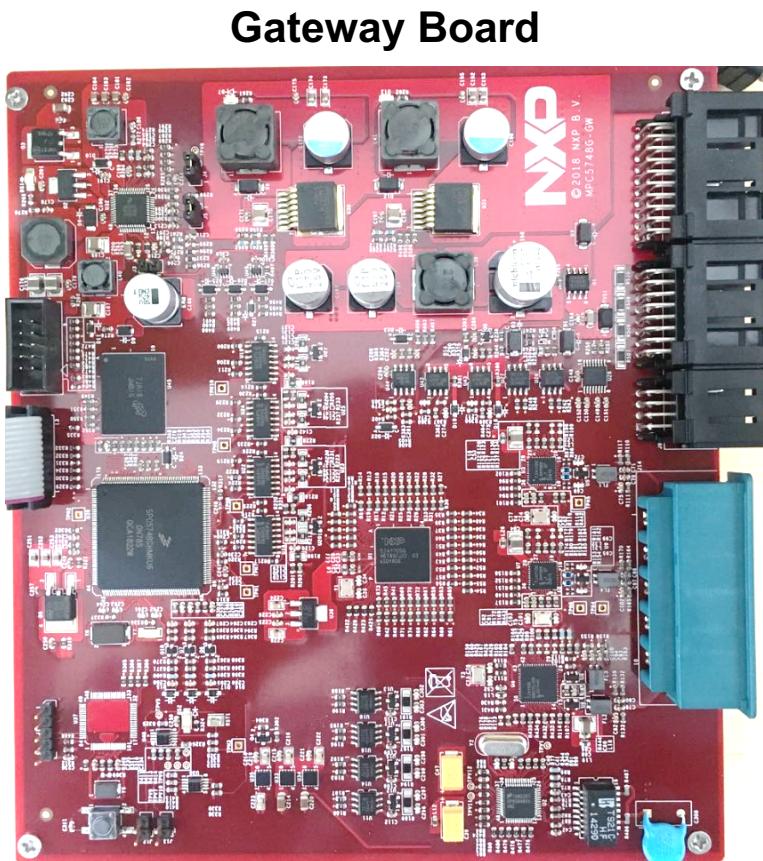

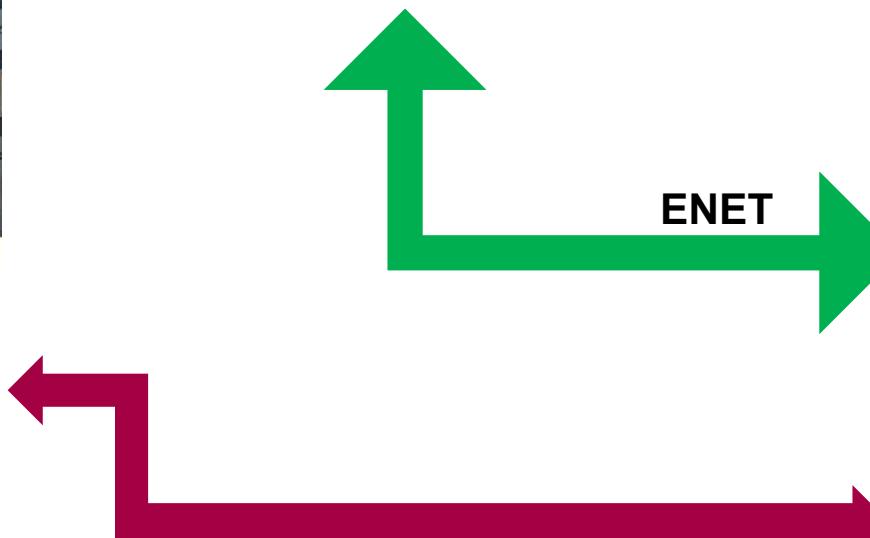

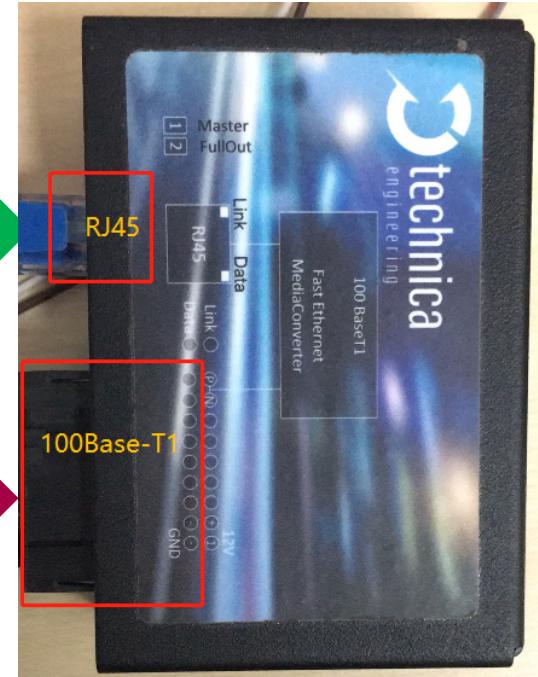

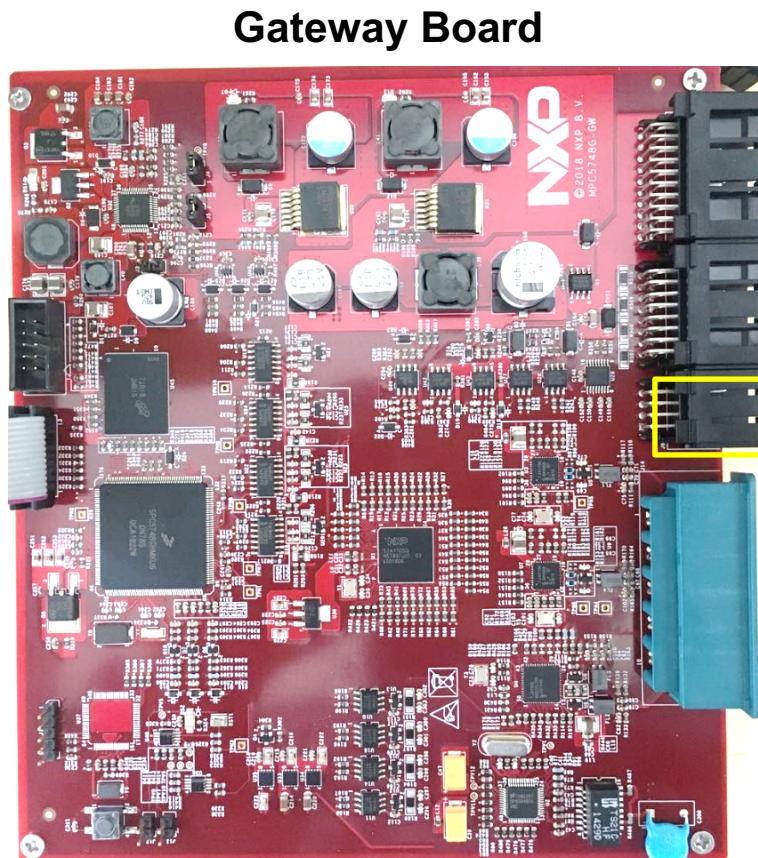

# Hands-on – ENET0: Lab Preview

Gateway Board

PC terminal

```

C:\>ping 192.168.1.19

Pinging 192.168.1.19 with 32 bytes of data:

Reply from 192.168.1.19: bytes=32 time=6ms TTL=255

Reply from 192.168.1.19: bytes=32 time=4ms TTL=255

Reply from 192.168.1.19: bytes=32 time=3ms TTL=255

Reply from 192.168.1.19: bytes=32 time=3ms TTL=255

```

MediaConverter\_TJA1100

RJ45 <----> 100BASE-T1

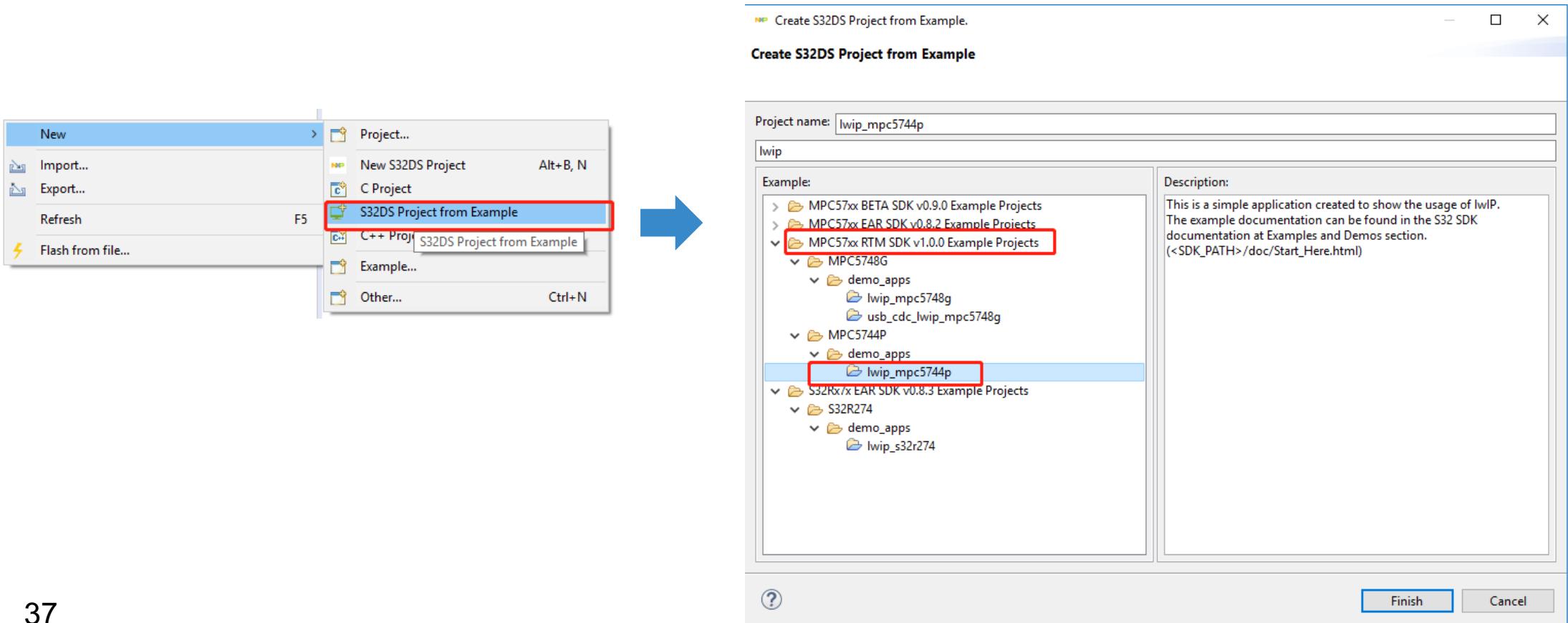

# Hands-on – ENET0: Import Example Project

- Import ‘enet\_ping’ example provided with the SDK:

- File->New->New S32DS Project from Example

- Select: **lwip\_mpc5748g** from **MPC57xxRTM SDK v1.0.0 Example Projects**

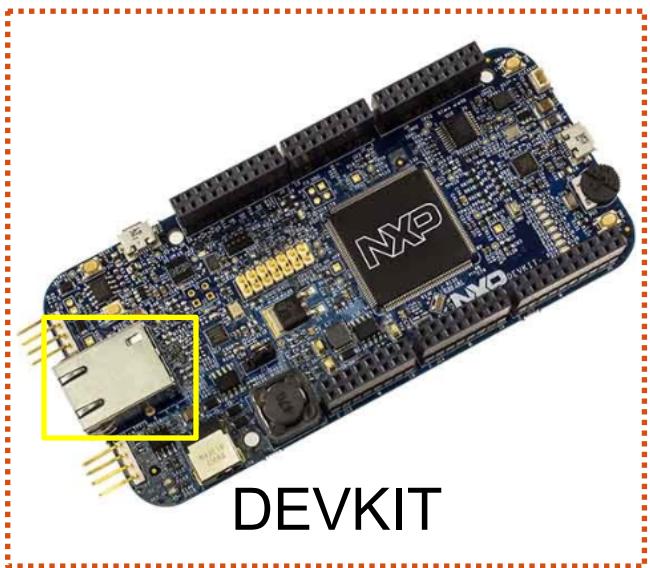

# Hands-on – ENET0: Modify

- The example of flexcan\_mpc5748g project is suit to DEVKIT

- How to modify?

1. Peripheral Power Supply

2. SWITCH configuration(Through SPI)

3. ENET configuration

4. Lwip middleware configuration

5. Application code

# Hands-on – ENET0: Modify-Peripheral Power Supply

- Enable the peripheral power supply

- Open ‘pin\_mux’ component in ‘Component Inspector’ to configure pin routing

- SIUL2 tab -> GPIO 60 (61) > select the pin (one option) + direction output

Component Inspector - pin\_mux

Routing Functional Properties Methods Settings

View Mode: Collapsed (selected) Pins Show Only Configurable Signals:  pd

Pad Configuration

| Pin | Pin Name | User Pin/Signal Name | Selected Function       |

|-----|----------|----------------------|-------------------------|

| 77  | PD[0]    | PD[0]                | More functions assigned |

| 78  | PD[1]    | PD[1]                | More functions assigned |

| 79  | PD[2]    | PD[2]                | More functions assigned |

| 80  | PD[3]    | PD[3]                | More functions assigned |

| 81  | PD[4]    | PD[4]                | More functions assigned |

| 82  | PD[5]    | PD[5]                | More functions assigned |

| 83  | PD[6]    | PD[6]                | More functions assigned |

| 84  | PD[7]    | PD[7]                | More functions assigned |

| 87  | PD[8]    | PD[8]                | More functions assigned |

| 94  | PD[9]    | PD[9]                | none                    |

| 95  | PD[10]   | PD[10]               | none                    |

| 100 | PD[12]   | PD[12]               | SIUL2/gpio/60           |

| 102 | PD[13]   | PD[13]               | SIUL2/gpio/61           |

| 104 | PD[14]   | PD[14]               | none                    |

| 106 | PD[15]   | PD[15]               | none                    |

**P10 ON-OFF-CAN** (ON-OFF-CAN) (ON-OFF-ETH) 100 102 104 PD12 PD13

Component Inspector - pin\_mux

Basic Advanced

View Mode: Collapsed (selected) Pins Show Only Configurable Signals:

Signals

| Pin/Signal Selection | Direction     | Selected Pin/Signal Name |

|----------------------|---------------|--------------------------|

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| PC[11]               | Input         | PC[11]                   |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| PD[12]               | Output        | PD[12]                   |

| PD[13]               | Output        | PD[13]                   |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| PE[0]                | Input         | PE[0]                    |

| No pin routed        | No pin routed |                          |

Routing for pin: Pin 100: PD[12]

Selected Function(s):

| In                       | Out                                 |

|--------------------------|-------------------------------------|

| <input type="checkbox"/> | <input type="checkbox"/>            |

| <input type="checkbox"/> | <input type="checkbox"/>            |

| <input type="checkbox"/> | <input type="checkbox"/>            |

| <input type="checkbox"/> | <input checked="" type="checkbox"/> |

| <input type="checkbox"/> | <input type="checkbox"/>            |

| <input type="checkbox"/> | <input type="checkbox"/>            |

| <input type="checkbox"/> | <input type="checkbox"/>            |

SIUL2/gpio/60

Done

```

void Peripheral_Power_Supply_Init(void)

{

PINS_DRV_WritePin(PTD, 12, 1);

PINS_DRV_WritePin(PTD, 13, 1);

}

```

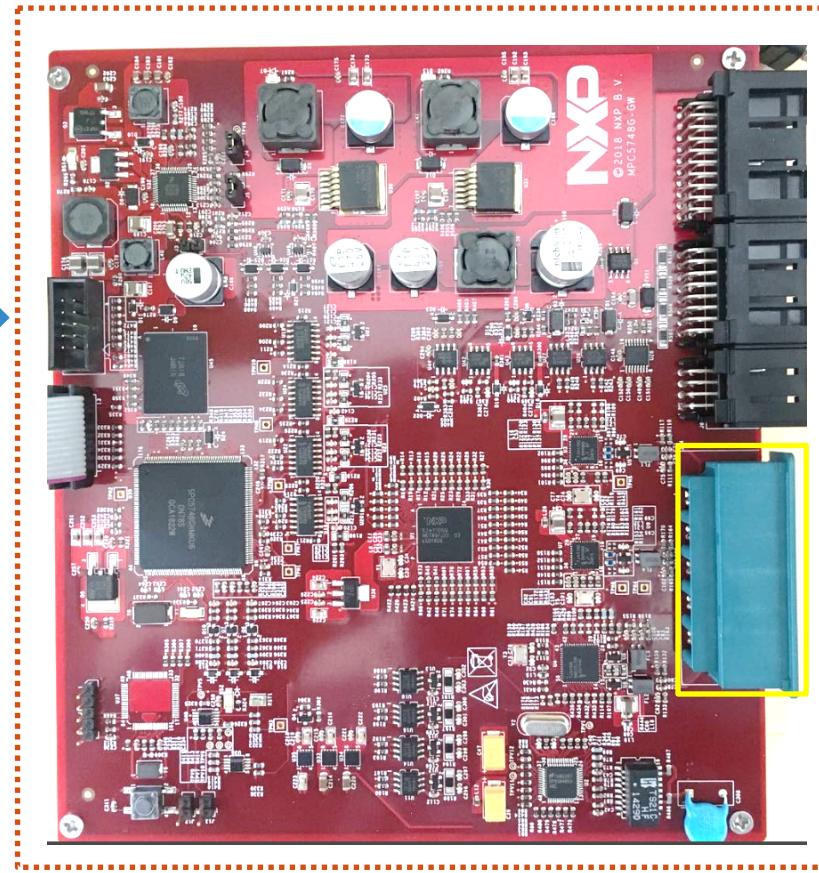

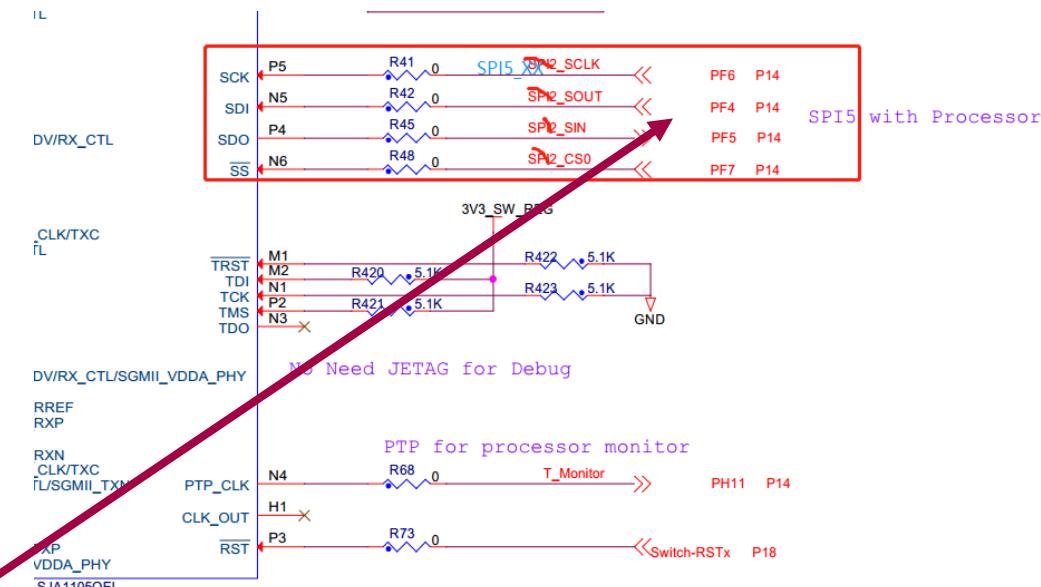

# Hands-on – ENET0: SWITCH configuration

## (1) Add spi\_pal component

- From 'Components Library' view, double-click 'spi\_pal' component to add it the project

# Hands-on – ENET0: SWITCH configuration

## (2) The port of SPI configuration

- In ‘pin\_mux’ component → Routing(Collapsed)– select ‘SPI’

- Configuration the ports according to the schematic.

\*Component Inspector - pin\_mux

Basic Advanced

Routing Functional Properties Methods Settings

View Mode: Collapsed Pins Show Only Configurable Signals

Signals

|                      | Pin/Signal Selection | Direction     | Selected Pin/Signal Name                                                                                                                                                                              |

|----------------------|----------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip Select Output 1 | No pin routed        | Output        |                                                                                                                                                                                                       |

| Chip Select Output 2 | No pin routed        | Output        |                                                                                                                                                                                                       |

| Serial Clock Output  | No pin routed        | No pin routed |                                                                                                                                                                                                       |

| Serial Data Input    | No pin routed        | Input         |                                                                                                                                                                                                       |

| Serial Data Output   | No pin routed        | Output        |                                                                                                                                                                                                       |

| Slave Select Input   | No pin routed        | Input         |                                                                                                                                                                                                       |

| <b>SPI_3</b>         |                      |               |                                                                                                                                                                                                       |

| Chip Select Output 0 | No pin routed        | Output        |                                                                                                                                                                                                       |

| Chip Select Output 1 | No pin routed        | Output        |                                                                                                                                                                                                       |

| Serial Clock Output  | No pin routed        | No pin routed |                                                                                                                                                                                                       |

| Serial Data Input    |                      |               | Automatic enabled - there is no user requirement for configuration. The value was selected automatically based on register configuration specified by other properties or based on after reset value. |

| Serial Data Output   |                      |               |                                                                                                                                                                                                       |

| Slave Select Input   | Serial Data Input    |               |                                                                                                                                                                                                       |

| <b>SPI_4</b>         |                      |               |                                                                                                                                                                                                       |

| Chip Select Output 0 | No pin routed        | Output        |                                                                                                                                                                                                       |

| Serial Clock Output  | No pin routed        | No pin routed |                                                                                                                                                                                                       |

| Serial Data Input    | No pin routed        | Input         |                                                                                                                                                                                                       |

| Serial Data Output   | No pin routed        | Output        |                                                                                                                                                                                                       |

| Slave Select Input   | No pin routed        | Input         |                                                                                                                                                                                                       |

| <b>SPI_5</b>         |                      |               |                                                                                                                                                                                                       |

| Chip Select Output 0 | PF[7]                | Output        | PF[7]                                                                                                                                                                                                 |

| Serial Clock Output  | PF[6]                | Output        | PF[6]                                                                                                                                                                                                 |

| Serial Data Input    | PF[5]                | Input         | PF[5]                                                                                                                                                                                                 |

| Serial Data Output   | PF[4]                | Output        | PF[4]                                                                                                                                                                                                 |

| Slave Select Input   | No pin routed        | Input         |                                                                                                                                                                                                       |

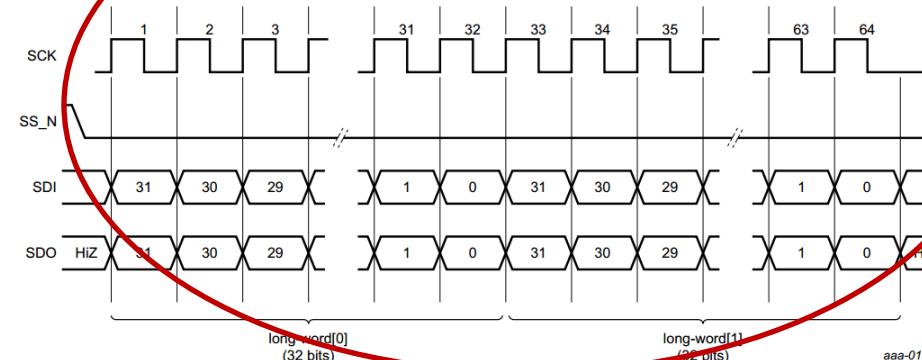

# Hands-on – ENET0: SWITCH configuration

## (3) SPI component configuration

Component Inspector - spi1

Basic Advanced

Properties Methods

Component name: spi1

Device: SPI\_5 (highlighted with a red box)

Component version: S32K144\_SDK01

SPI configuration read-only:

Master configurations Slave configurations Shared components

Master main configuration

| # | Configuration                       | Name               | Baud rate | SS | SS polarity | Bit order | Bits/frame | Phase               | Clock polarity | Transfer type | RX DMA channel |

|---|-------------------------------------|--------------------|-----------|----|-------------|-----------|------------|---------------------|----------------|---------------|----------------|

| 0 | <input checked="" type="checkbox"/> | spi1_MasterConfig0 | 1000000   | 0  | Active low  | MSB first | 8          | Read on second edge | Active high    | Interrupts    | No DMA         |

### 6.3 SPI interface

The SJA1105 provides an SPI bus slave as the host control interface. The host can control/configure the SJA1105 by accessing the configuration address space and the programming address space.

This interface acts as a slave in a synchronous serial data link that conforms with the SPI standard as defined in the SPI Block Guide from Motorola ([Ref. 7](#)). The interface operates in SPI Transfer mode 1 (CPOL = 0, CPHA = 1).

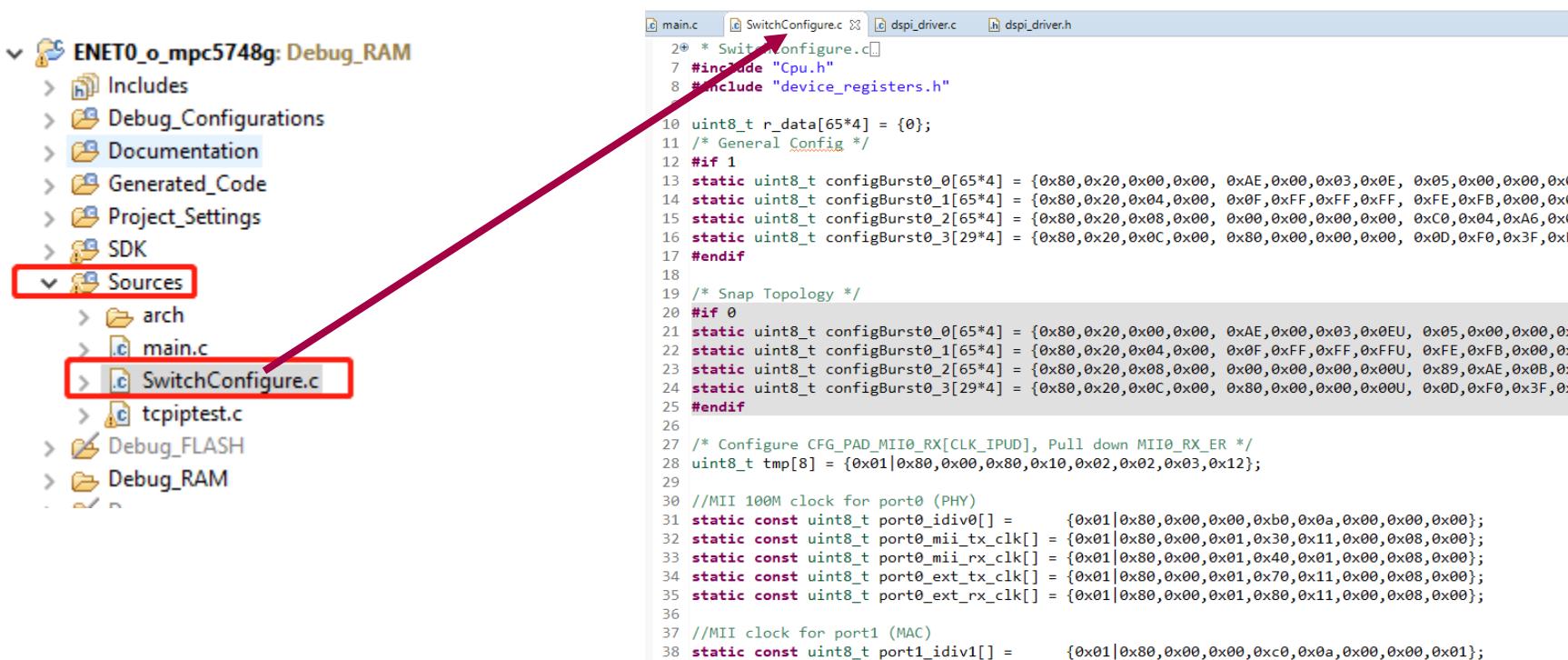

# Hands-on – ENET0: SWITCH configuration

## (4) Configure SWITCH`s data structure

- We have a tool for configuring SWITCH called *sja1105\_tools* (The version of this tool will be updated aperiodically, please contact FAE to get the latest version of the tool).

- You can refer to the sample demo(The project of *ENET0\_MPC5748G*) we provided. And copy the *SwitchConfigure.c* file to your project without any modification.

The image shows a software development environment with a project tree on the left and a code editor on the right. The project tree is for 'ENET0\_o\_mpc5748g: Debug\_RAM' and includes 'Includes', 'Debug\_Configurations', 'Documentation', 'Generated\_Code', 'Project\_Settings', 'SDK', and 'Sources'. The 'Sources' folder is expanded, showing files like 'main.c', 'SwitchConfigure.c' (which is highlighted with a red box), and 'tcpiptest.c'. A red arrow points from the 'Sources' folder in the project tree to the 'SwitchConfigure.c' file in the code editor. The code editor shows the content of the 'SwitchConfigure.c' file, which includes header includes, a configuration section for 'configBurst0', and a section for 'configBurst0\_3'. The code is written in C and uses hex values for memory addresses and configurations.

```

2 * SwitchConfigure.c

3 #include "Cpu.h"

4 #include "device_registers.h"

5

6 uint8_t r_data[65*4] = {0};

7 /* General Config */

8 #if 1

9     static uint8_t configBurst0_0[65*4] = {0x80,0x20,0x00,0x00, 0xAE,0x00,0x03,0x0E, 0x05,0x00,0x00,0x00,0x0

10     static uint8_t configBurst0_1[65*4] = {0x80,0x20,0x04,0x00, 0x0F,0xFF,0xFF,0xFF, 0xFE,0xFB,0x00,0x0

11     static uint8_t configBurst0_2[65*4] = {0x80,0x20,0x08,0x00, 0x00,0x00,0x00,0x00, 0xC0,0x04,0xA6,0x0

12     static uint8_t configBurst0_3[29*4] = {0x80,0x20,0x0C,0x00, 0x80,0x00,0x00,0x00, 0x0D,0xF0,0x3F,0xF

13 #endif

14

15 /* Snap Topology */

16 #if 0

17     static uint8_t configBurst0_0[65*4] = {0x80,0x20,0x00,0x00, 0xAE,0x00,0x03,0x0EU, 0x05,0x00,0x00,0x0

18     static uint8_t configBurst0_1[65*4] = {0x80,0x20,0x04,0x00, 0x0F,0xFF,0xFF,0xFFU, 0xFE,0xFB,0x00,0x0

19     static uint8_t configBurst0_2[65*4] = {0x80,0x20,0x08,0x00, 0x00,0x00,0x00,0x00U, 0x89,0xAE,0x0B,0x0

20     static uint8_t configBurst0_3[29*4] = {0x80,0x20,0x0C,0x00, 0x80,0x00,0x00,0x00U, 0x0D,0xF0,0x3F,0x0

21 #endif

22

23 /* Configure CFG_PAD_MII0_RX[CLK_IPUD], Pull down MII0_RX_ER */

24 uint8_t tmp[8] = {0x01|0x80,0x00,0x80,0x10,0x02,0x02,0x03,0x12};

25

26 //MII 100M clock for port0 (PHY)

27 static const uint8_t port0_idiv0[] = {0x01|0x80,0x00,0x00,0xb0,0xa0,0x00,0x00,0x00};

28 static const uint8_t port0_mii_tx_clk[] = {0x01|0x80,0x00,0x01,0x30,0x11,0x00,0x08,0x00};

29 static const uint8_t port0_mii_rx_clk[] = {0x01|0x80,0x00,0x01,0x40,0x01,0x00,0x08,0x00};

30 static const uint8_t port0_ext_tx_clk[] = {0x01|0x80,0x00,0x01,0x70,0x11,0x00,0x08,0x00};

31 static const uint8_t port0_ext_rx_clk[] = {0x01|0x80,0x00,0x01,0x80,0x11,0x00,0x08,0x00};

32

33 //MII clock for port1 (MAC)

34 static const uint8_t port1_idiv1[] = {0x01|0x80,0x00,0x00,0xc0,0xa0,0x00,0x00,0x01};

```

# Hands-on – ENET0: ENET configuration

- In ‘pin\_mux’ component → Routing(Collapsed) – select ‘ENET’

- Configuration the ports according to the schematic.

Component Inspector - pin\_mux

Basic Advanced

Routing Functional Properties Methods Settings

View Mode: Collapsed (selected), Pins, Show Only Configurable Signals

Legend: ADC, CAN, CMP, DCI, DSP, ENET, FCCU, FlexRay, HSM, I2C, LINFlexD, MLB, Platform, PowerAndGround, SAI, SIUL2, SPI, SSCM, USB, WKPL

ENET signals table:

| Signals                                 | Pin/Signal Selection | Direction    | Selected Pin/Signal |

|-----------------------------------------|----------------------|--------------|---------------------|

| ENET0                                   | No pin routed        | Input_Output |                     |

| ENET Timer 0                            | No pin routed        | Input_Output |                     |

| ENET Timer 1                            | PA[10]               | Input        | PA[10]              |

| ENET0 Collision                         | PE[12]               | Input        | PE[12]              |

| ENET0 Carrier Sense                     | PA[3]                | Input        | PA[3]               |

| ENET0 MII Receive Clock                 | PA[7]                | Input        | PA[7]               |

| ENET MII Receive Data 2                 | PE[13]               | Input        | PE[13]              |

| ENET MII Receive Data 3                 | PG[12]               | Output       | PG[12]              |

| ENET MII Transmit Data 2                | PG[13]               | Output       | PG[13]              |

| ENET MII Transmit Data 3                | PH[3]                | Output       | PH[3]               |

| ENET0 MII Transmit Error                | PG[0]                | Output       | PG[0]               |

| ENET0 RMII Management Data Clock        | PF[14]               | Input_Output | PF[14]              |

| ENET0 RMII Management Data Input/Output | PA[9]                | Input        | PA[9]               |

| ENET0 RMII Receive Data 0               | PA[8]                | Input        | PA[8]               |

| ENET0 RMII Receive Data 1               | PF[15]               | Input        | PF[15]              |

| ENET0 RMII Receive Data Valid           | PA[11]               | Input        | PA[11]              |

| ENET0 RMII Receive Error                | PG[1]                | Input        | PG[1]               |

| ENET0 RMII Transmit Clock               | PH[1]                | Output       | PH[1]               |

| ENET0 RMII Transmit Data 0              | PH[0]                | Output       | PH[0]               |

| ENET0 RMII Transmit Data 1              | PH[2]                | Output       | PH[2]               |

| ENET0 RMII Transmit Enable              |                      |              |                     |

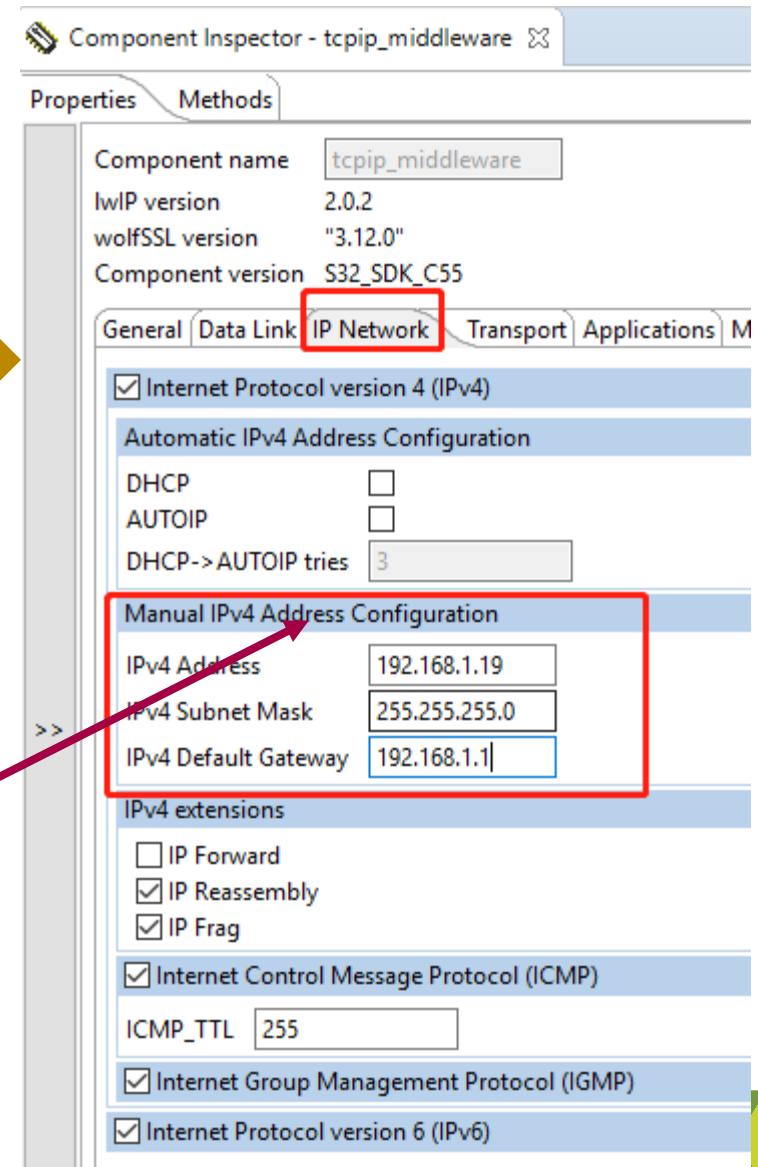

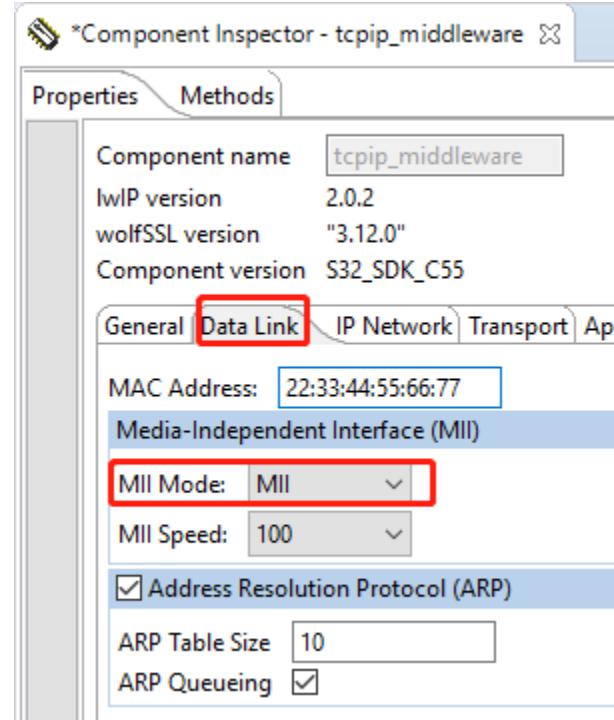

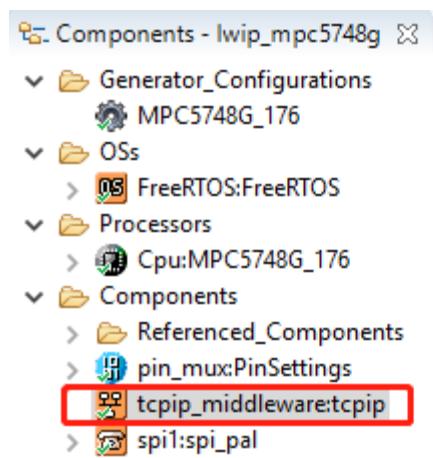

# Hands-on – ENET0: lwip middleware configuration

Define it by yourself

# Hands-on – ENET0: Application Code

## (1) Peripheral Power Supply:

- {Project Name} -> Source -> **main.c**

```

41 int main(void)

42 {

43

44     /** Processor Expert internal initialization. DON'T REMOVE THIS CODE!!!

45     #ifdef PEX_RTOS_INIT

46         PEX_RTOS_INIT();                                /* Initialization of the selected RT

47     #endif

48     /** End of Processor Expert internal initialization.

49

50     /* Write your code here */

51     /* Initialize and configure clocks

52     *      - see clock manager component for details

53     */

54

55     CLOCK_SYS_Init(g_clockManConfigsArr, CLOCK_MANAGER_CONFIG_CNT, g_clockMan

56     CLOCK_SYS_UpdateConfiguration(0U, CLOCK_MANAGER_POLICY AGREEMENT);

57

58     /* Initialize pins

59     *      - See PinSettings component for more info

60     */

61     PINS_DRV_Init(NUM_OF_CONFIGURED_PINS, g_pin_mux_InitConfigArr);

62

63     Peripheral_Power_Supply_Init();                    // Call to Peripheral Power Supply Init function

64

65     start_example();

66 }

```

```

150 /*

151  * Peripheral Power Supply

152  */

153 void Peripheral_Power_Supply_Init(void)

154 {

155     PINS_DRV_WritePin(PTD, 12, 1);

156     PINS_DRV_WritePin(PTD, 13, 1);

157 }

```

# Hands-on – ENET0: Application Code

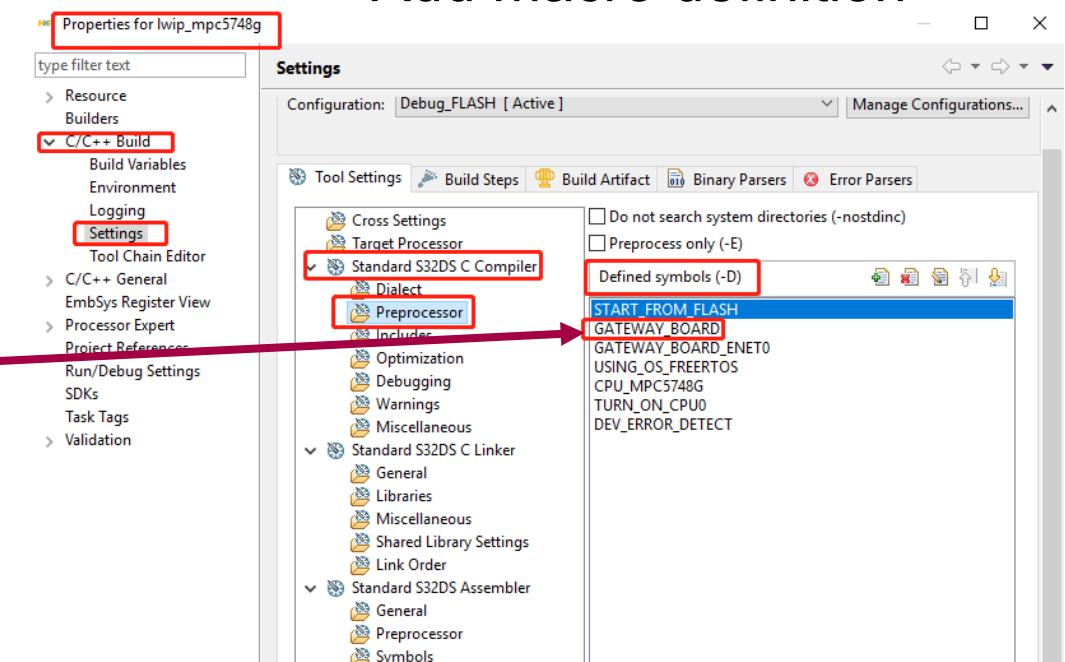

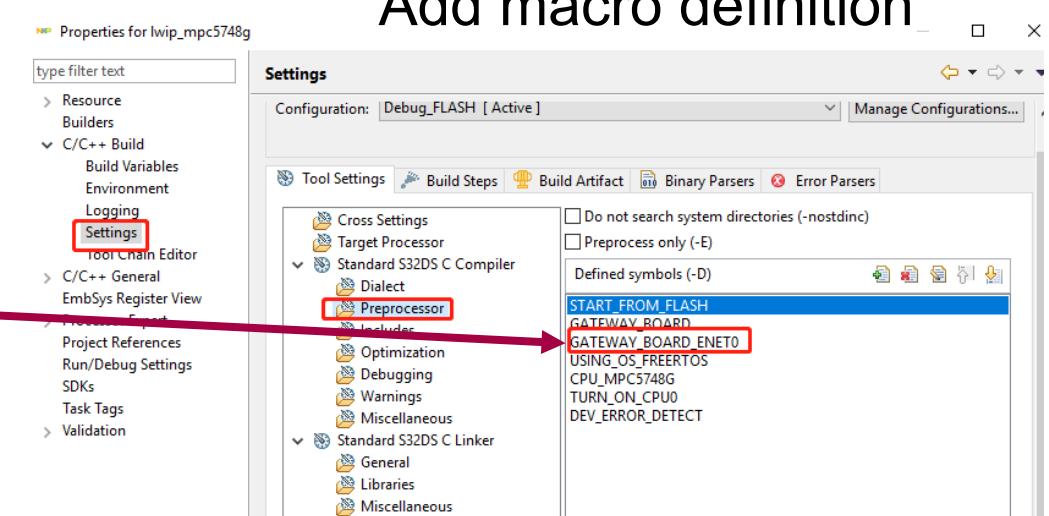

## (2) Modify the configuration of SPI to adaptation SJA1105:

- {Project Name} -> SDK -> platform -> pal -> spi -> src -> **spi\_pal.c**

### Note:

If you have a patched after update the SDK, you can ignore this modification

```

284 #if (defined(SPI_OVER_DSPI))

285 if ((instance->instType == SPI_INST_TYPE_SPI) || (instance->instType ==

286 {

287     uint32_t inst = GetDspiIndex(instance);

288

289     dspi_master_config_t dspiConfig;

290     dspiConfig.bitsPerSec = config->baudRate;

291     dspiConfig.bitcount = config->frameSize;

292     dspiConfig.clkPhase = (dsPIC_clock_phase_t)config->clockPhase;

293     dspiConfig.clkPolarity = (dsPIC_polarity_t)config->clockPolarity;

294     dspiConfig.isClkContinuous = false;

295

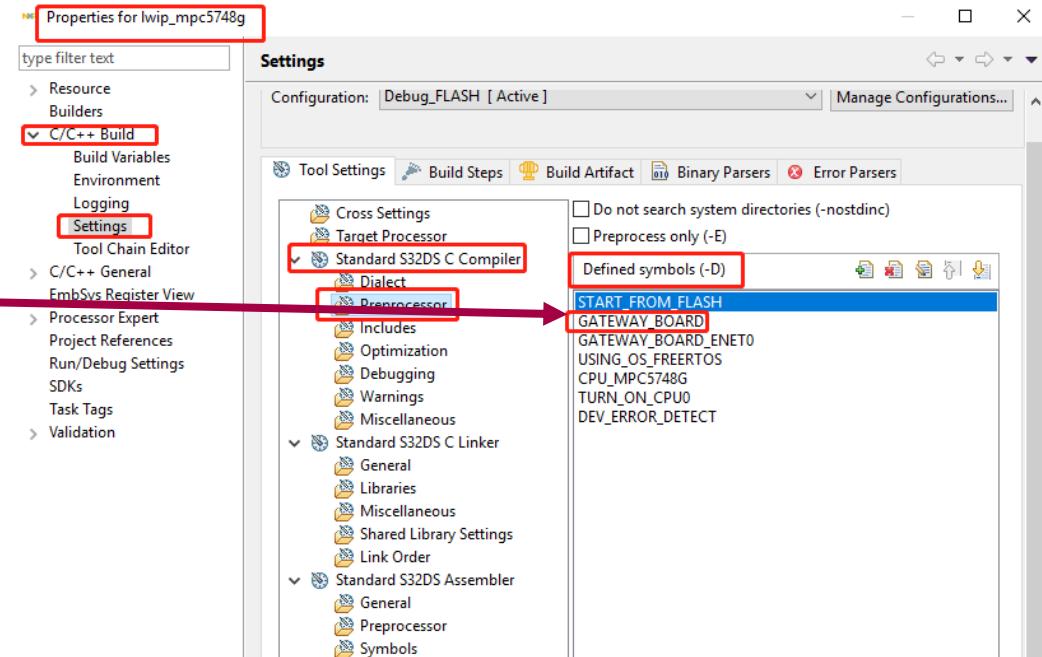

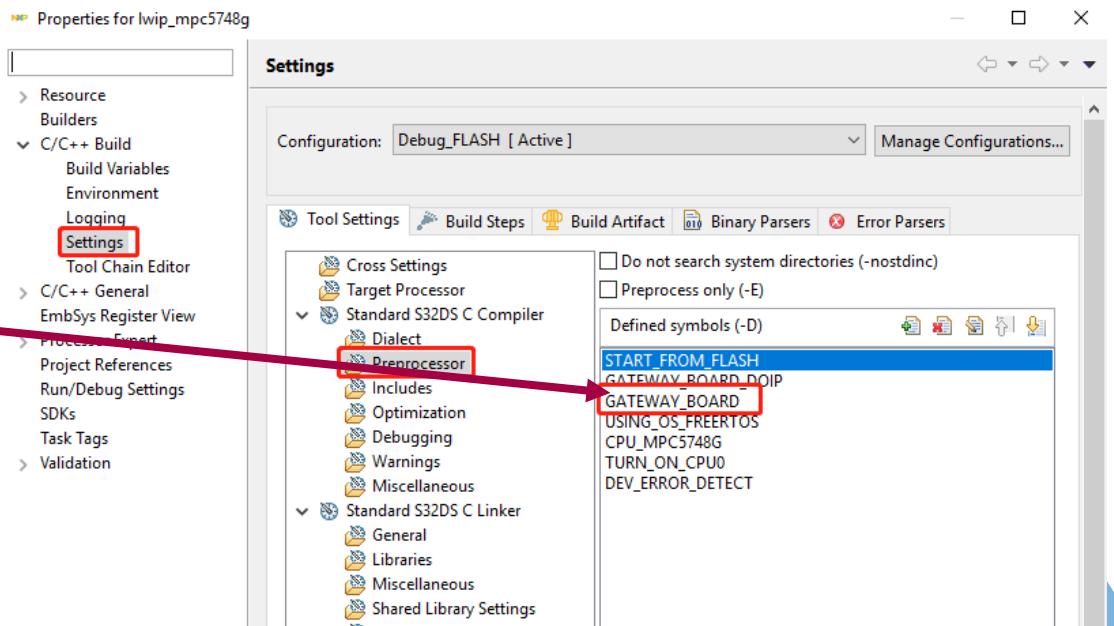

296     #ifdef GATEWAY_BOARD

297         dspiConfig.continuousPCS = true;

298     #else

299         dspiConfig.continuousPCS = false;

300     #endif

301

302     dspiConfig.lsbFirst = config->bitOrder;

```

### Explanation:

The default configuration of SPI's CS pin cannot be maintained until the delivery is completed when the send function (**SPI\_MasterTransferBlocking()**) is called. In order to match the SWITCH, you need to configure the **dspiConfig.continuousPCS = true**

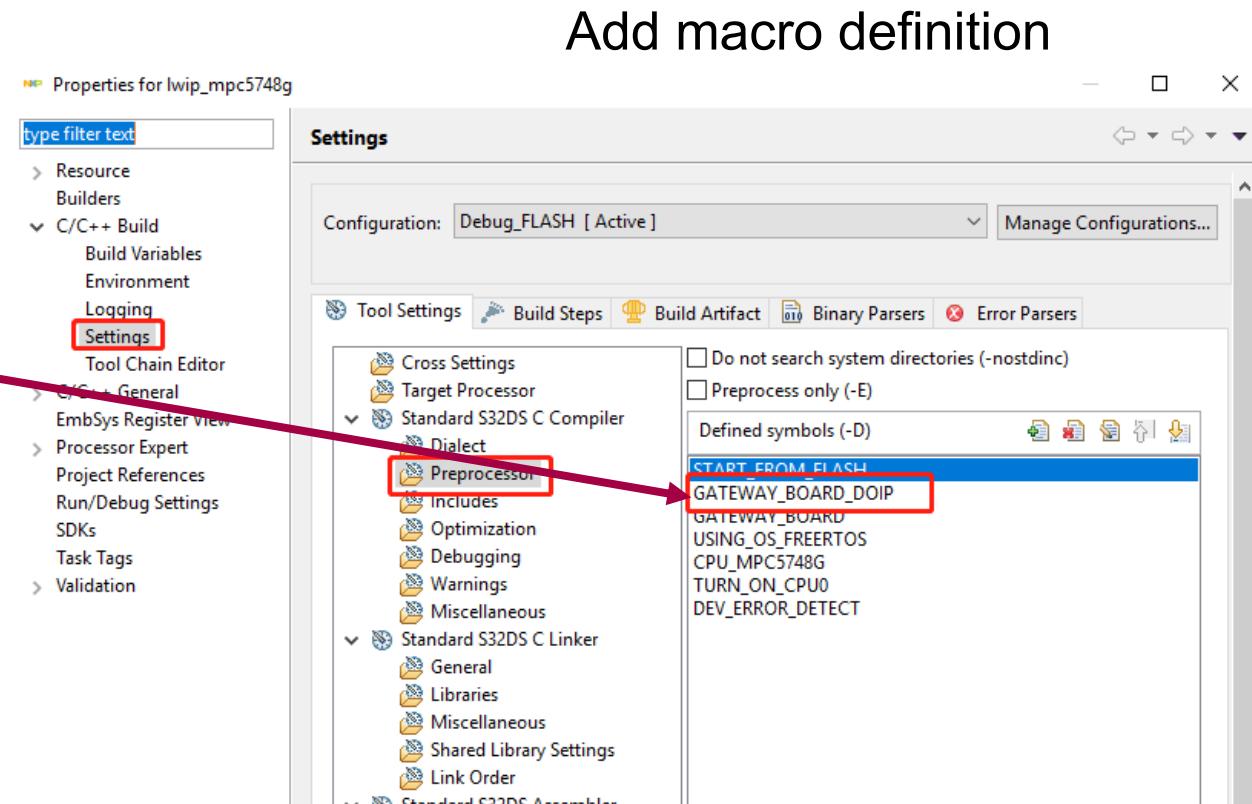

# Hands-on – ENET0: Application Code

## (3) Add the initialization function of the SWITCH:

- {Project Name} -> SDK -> middleware -> tcpip -> tcpip\_stack -> demo -> **test.c**

```

509 static void mainLoopTask(void* pvParameters)

510 {

511     (void)pvParameters;

512

513     /* initialize lwIP stack, network interfaces and applications */

514 #if !NO_SYS

515     err_t err;

516     sys_sem_t init_sem;

517

518 #ifdef GATEWAY_BOARD_ENET0

519     SWITCH_Init_Config();

520 #endif

521

522     err = sys_sem_new(&init_sem, 0);

523     LWIP_ASSERT("failed to create init_sem", err == (err_t)ERR_OK);

524     LWIP_UNUSED_ARG(err);

525     /* main init/func init /.../ * init code */

```

# Hands-on – ENET0: Application Code

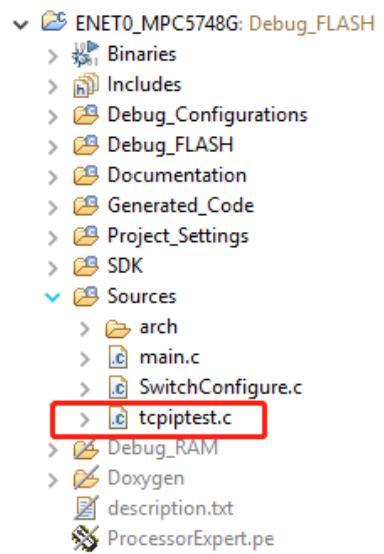

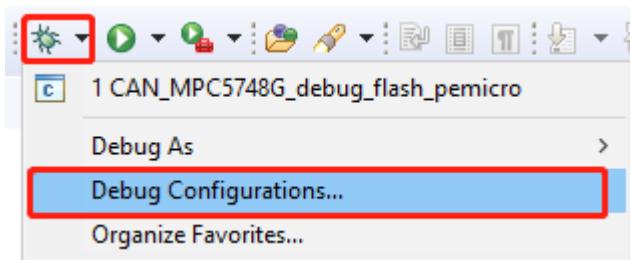

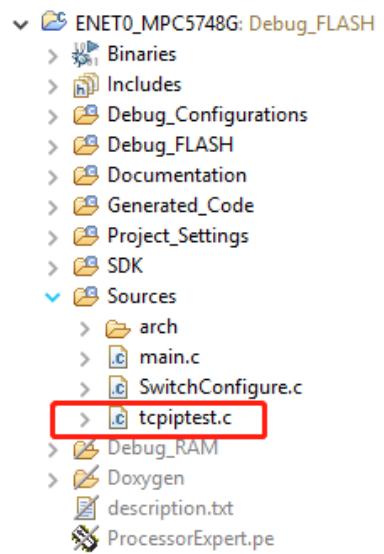

## (4) Add client application for lwip\_tcp

- You can refer to the sample demo(The project of *ENET0\_MPC5748G*) we provided. And copy the *tcpipitest.c* file to your project without any modification.

- Add client application call function under the **test.c** file

- {Project Name} -> SDK -> middleware -> tcpip -> tcpip\_stack -> demo -> **test.c**

```

391 /* This function initializes applications

392  * Implements apps_init_Activity

393  */

394 static void

395 apps_init(void)

396 {

397 #ifdef GATEWAY_BOARD

398     tcpipitest_init();

399 #endif

400

401 #if LWIP_DNS_APP && LWIP_DNS

402     /* wait until the netif is up (for dhcp, autoip or p

403     * ose timeout(5000, dns_donestart, NULL);

```

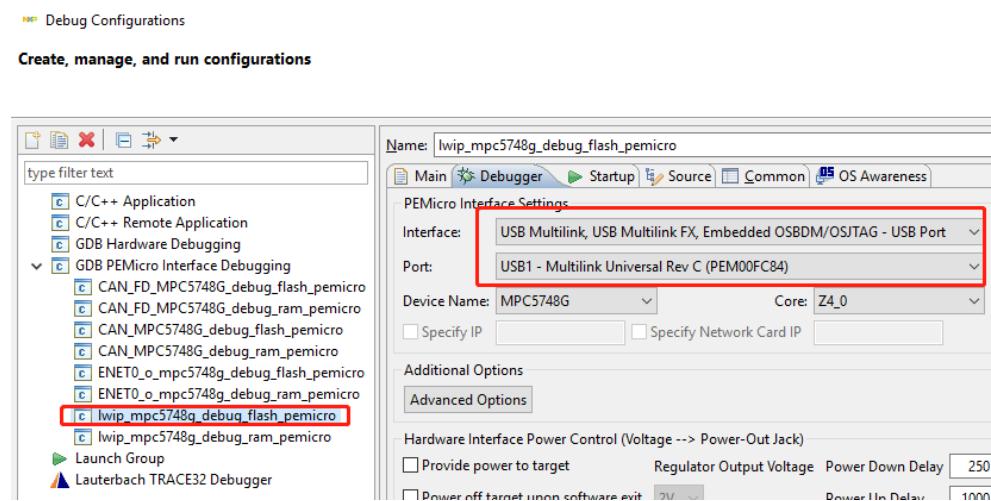

# Hands-on – ENET0: Build and Debug

- Click the ‘build project’ button – make sure there are no compilation errors

```

Problems Tasks Console Properties Debugger Console Call Hierarchy

CDT Build Console [lwip_mpc5748g]

11:03:34 **** Incremental Build of configuration Debug_FLASH for project lwip_mpc5748g ***

make -j4 all

Executing target #150 lwip_mpc5748g.siz

Invoking: Standard S32DS Print Size

powerpc-eabivle-size --format=berkeley lwip_mpc5748g.elf

text      data      bss      dec      hex filename

133274     8164   104836  246274  3c202 lwip_mpc5748g.elf

Finished building: lwip_mpc5748g.siz

11:03:37 Build Finished (took 3s.545ms)

```

- Select the correct debug configuration and interface to debug the application

# Hands-on – ENET0: Build and Debug

TEST: Ping the board from PC:

PC terminal

```

C:\>ping 192.168.1.19

Pinging 192.168.1.19 with 32 bytes of data:

Reply from 192.168.1.19: bytes=32 time=6ms TTL=255

Reply from 192.168.1.19: bytes=32 time=4ms TTL=255

Reply from 192.168.1.19: bytes=32 time=3ms TTL=255

Reply from 192.168.1.19: bytes=32 time=3ms TTL=255

```

MediaConverter\_TJA1100

RJ45 <----> 100BASE-T1

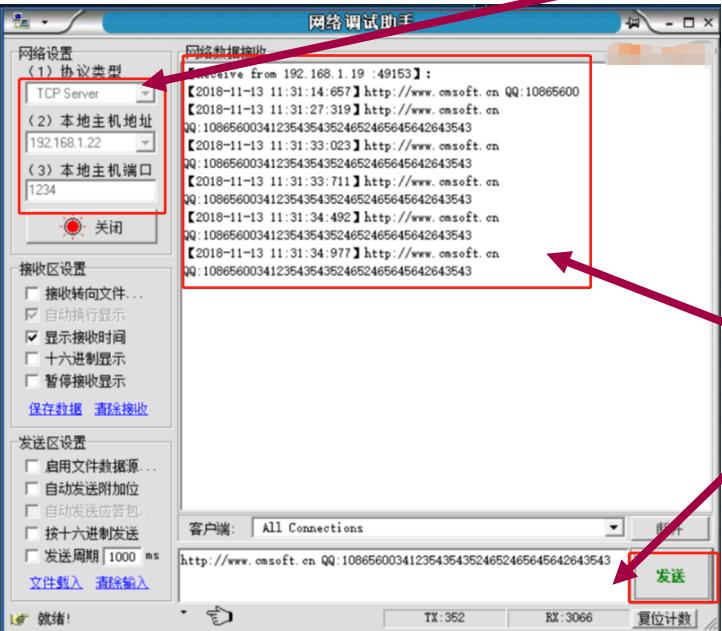

# Hands-on – ENET0: Build and Debug

TEST: LWIP\_tcp Client:

Gateway Board

Port1~port4

```

34     memset(&server_addr, 0, sizeof(server_addr));

35     server_addr.sin_family = AF_INET;

36     server_addr.sin_addr.s_addr = inet_addr("192.168.1.22");

37     server_addr.sin_port = PP htons(PORT);

38     server_addr.sin_len = sizeof(server_addr);

39

40     ret = lwip_connect(socket_fd, (struct sockaddr*)&server_addr, sizeof(struct sockaddr));

41     if(ret != ERR_OK)

42     {

43         while(1);

44     }

45

46     for(;;)

47     {

48         ret = lwip_read(socket_fd, ReceiveBuff, sizeof(ReceiveBuff));

49         if(ret == -1)

50         {

51             lwip_close(socket_fd);

52             break;

53         }

54

55         ret = lwip_send(socket_fd, ReceiveBuff, sizeof(ReceiveBuff)-1, 0);

56         if(ret < 0)

57         {

58             lwip_close(socket_fd);

59             break;

60         }

61     }

62 }

```

MediaConverter\_TJA1100

RJ45 <----> 100BASE-T1

TCP

Server ip:192.168.1.22

Port :1234

# 04.

## Hands-on – ENET1

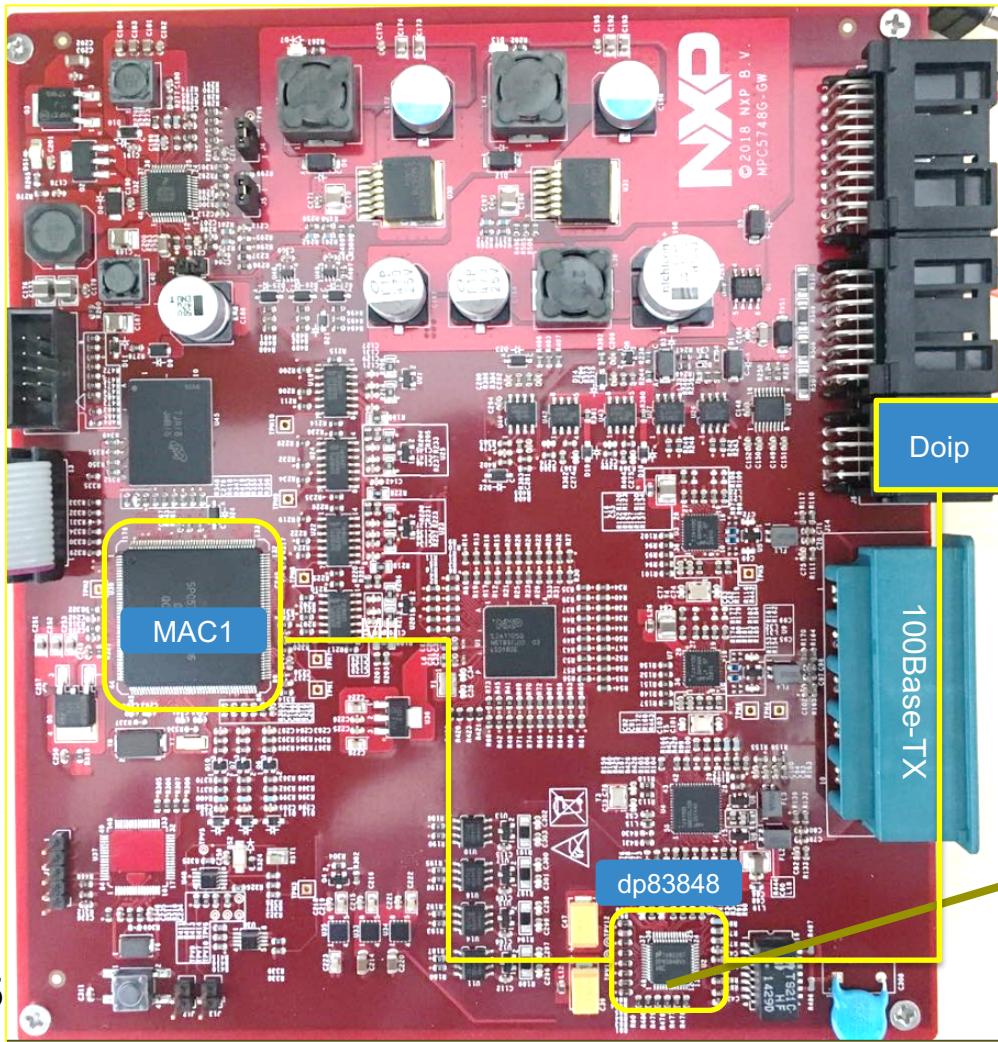

# Hands-on – ENET1: Objective

- ENET1 is configured similarly to ENET0.

- Unlike the previous section, the Phy(DP83848) for MCA1 directly connected.

- Please refer to section 3 if there is anything unclear

# Hands-on – ENET1: Resources

- Resources to be used:

- on-board user ENET1 ports

# Hands-on – ENET1: Modify-Peripheral Power Supply

- Enable the peripheral power supply

- Open ‘pin\_mux’ component in ‘Component Inspector’ to configure pin routing

- SIUL2 tab -> GPIO 60 (61) > select the pin (one option) + direction output

Component Inspector - pin\_mux

Routing Functional Properties Methods Settings

View Mode: Collapsed (selected) Pins Show Only Configurable Signals:  pd

Pad Configuration

| Pin | Pin Name | User Pin/Signal Name | Selected Function       |

|-----|----------|----------------------|-------------------------|

| 77  | PD[0]    | PD[0]                | More functions assigned |

| 78  | PD[1]    | PD[1]                | More functions assigned |

| 79  | PD[2]    | PD[2]                | More functions assigned |

| 80  | PD[3]    | PD[3]                | More functions assigned |

| 81  | PD[4]    | PD[4]                | More functions assigned |

| 82  | PD[5]    | PD[5]                | More functions assigned |

| 83  | PD[6]    | PD[6]                | More functions assigned |

| 84  | PD[7]    | PD[7]                | More functions assigned |

| 87  | PD[8]    | PD[8]                | More functions assigned |

| 94  | PD[9]    | PD[9]                | none                    |

| 95  | PD[10]   | PD[10]               | none                    |

| 100 | PD[12]   | PD[12]               | SIUL2/gpio/60           |

| 102 | PD[13]   | PD[13]               | SIUL2/gpio/61           |

| 104 | PD[14]   | PD[14]               | none                    |

| 106 | PD[15]   | PD[15]               | none                    |

**P10 ON-OFF-CAN** (ON-OFF-CAN) (ON-OFF-ETH) 100 102 104 PD12 PD13

Component Inspector - pin\_mux

Basic Advanced

View Mode: Collapsed (selected) Pins Show Only Configurable Signals:

Signals

| Pin/Signal Selection | Direction     | Selected Pin/Signal Name |

|----------------------|---------------|--------------------------|

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| PC[11]               | Input         | PC[11]                   |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| PD[12]               | Output        | PD[12]                   |

| PD[13]               | Output        | PD[13]                   |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| PE[0]                | Input         | PE[0]                    |

| No pin routed        | No pin routed |                          |

Routing for pin: Pin 100: PD[12]

Selected Function(s):

| In                       | Out                                 |

|--------------------------|-------------------------------------|

| <input type="checkbox"/> | <input type="checkbox"/>            |

| <input type="checkbox"/> | <input type="checkbox"/>            |

| <input type="checkbox"/> | <input type="checkbox"/>            |

| <input type="checkbox"/> | <input checked="" type="checkbox"/> |

| <input type="checkbox"/> | <input type="checkbox"/>            |

| <input type="checkbox"/> | <input type="checkbox"/>            |

| <input type="checkbox"/> | <input type="checkbox"/>            |

Done

```

32 void Peripheral_Power_Supply_Init(void)

33 {

34     PINS_DRV_WritePin(PTB, 12, 0); //DoIP_Power enable

35

36     PINS_DRV_WritePin(PTD, 12, 1);

37     PINS_DRV_WritePin(PTD, 13, 1);

38 }

```

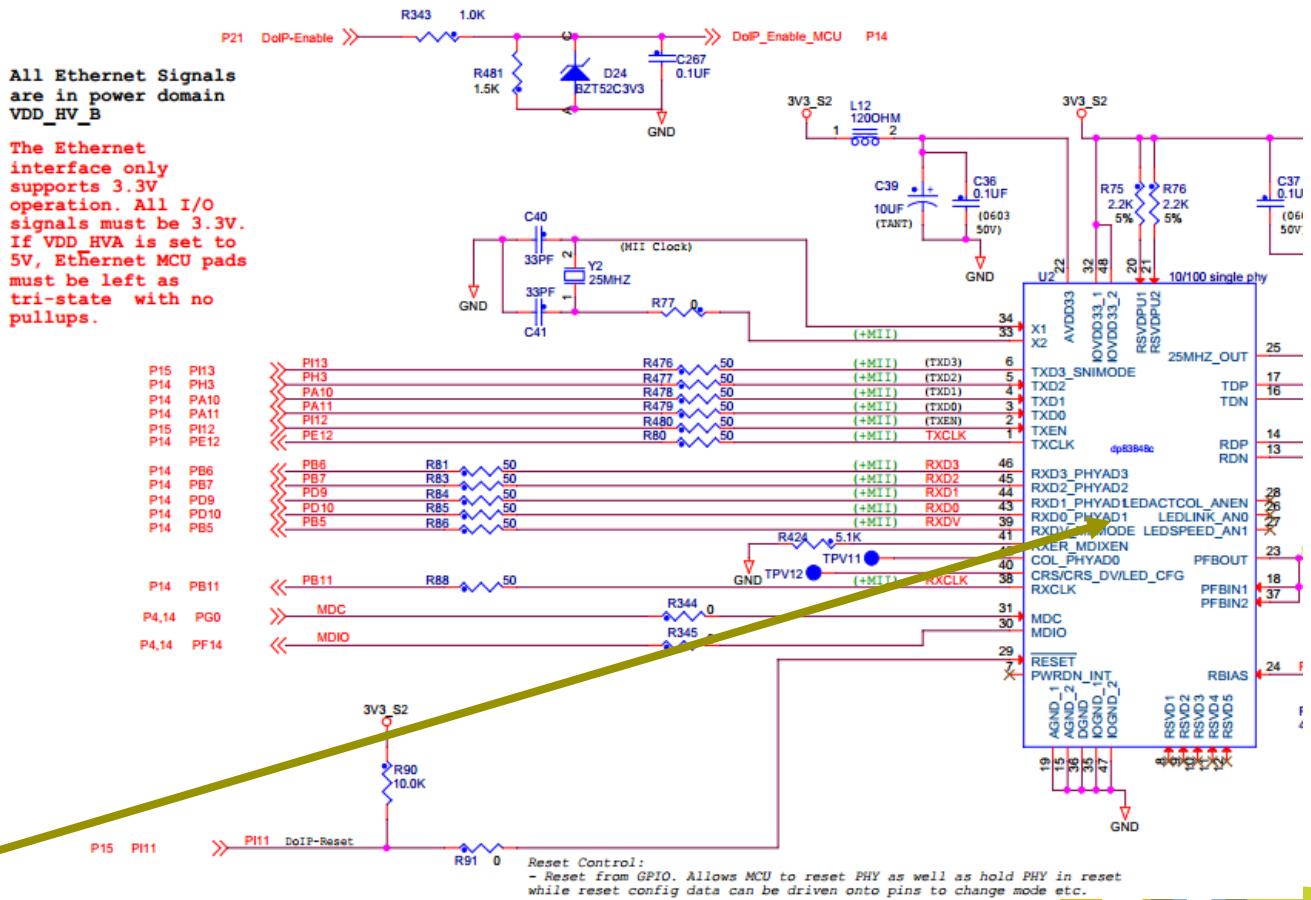

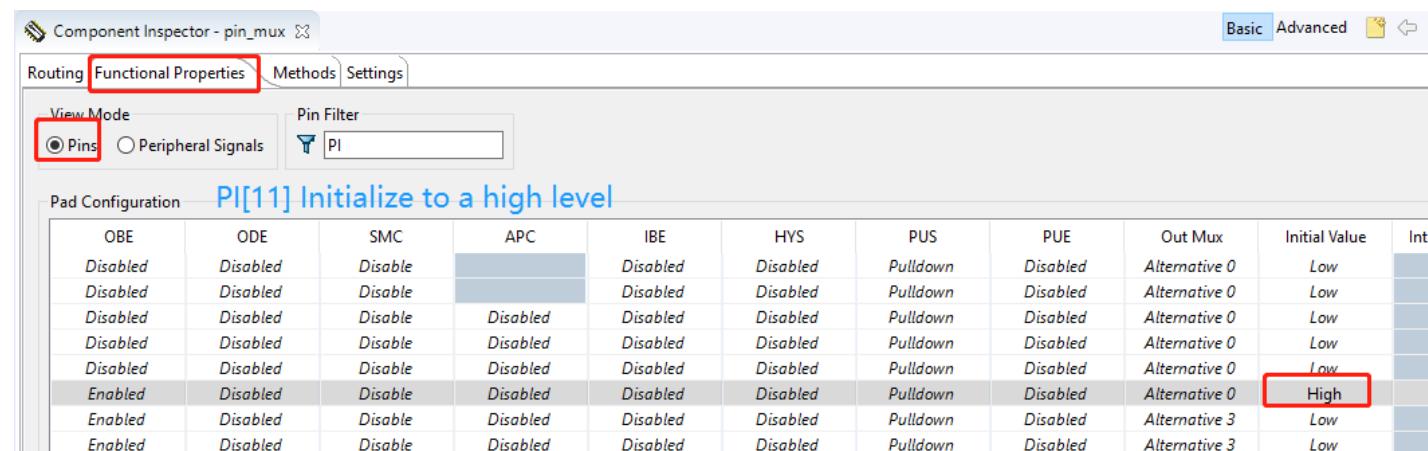

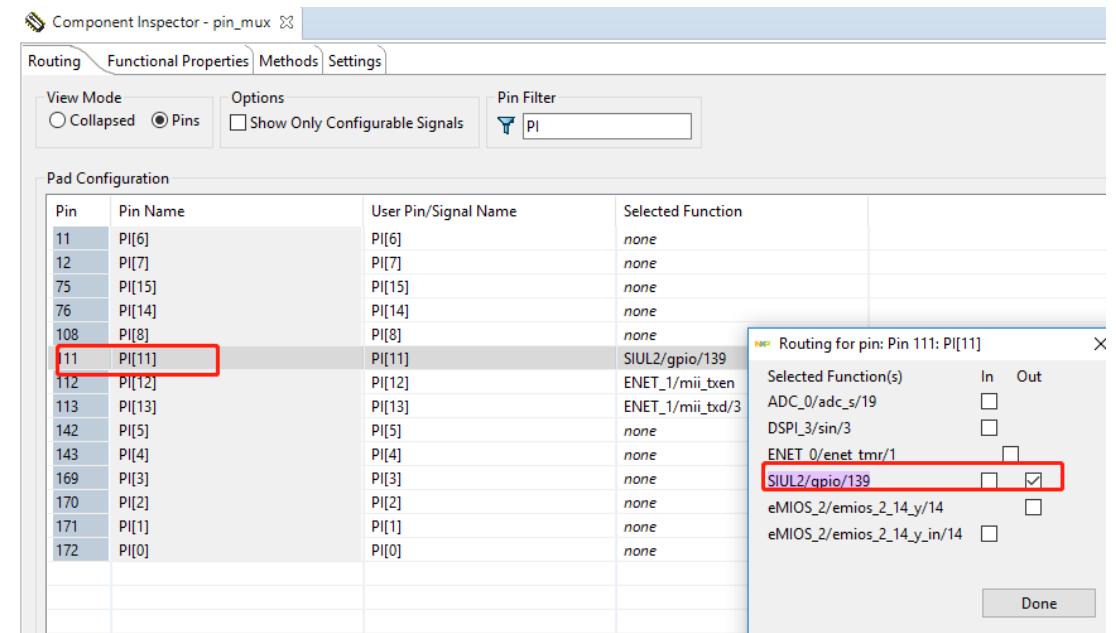

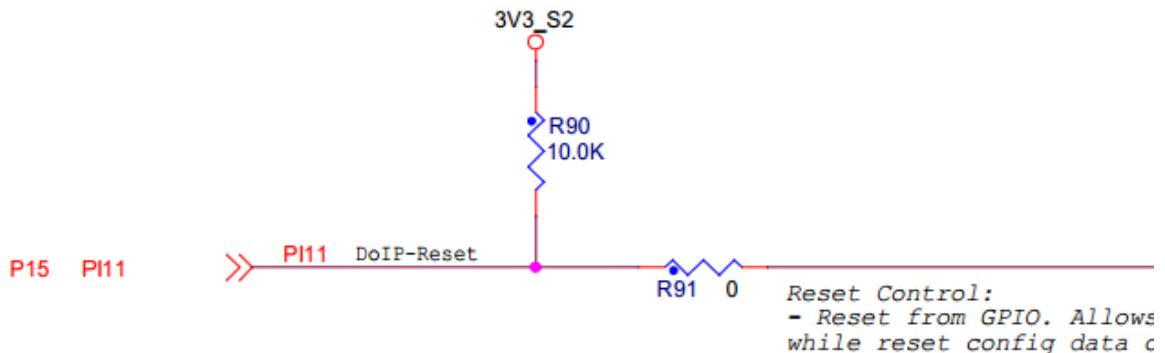

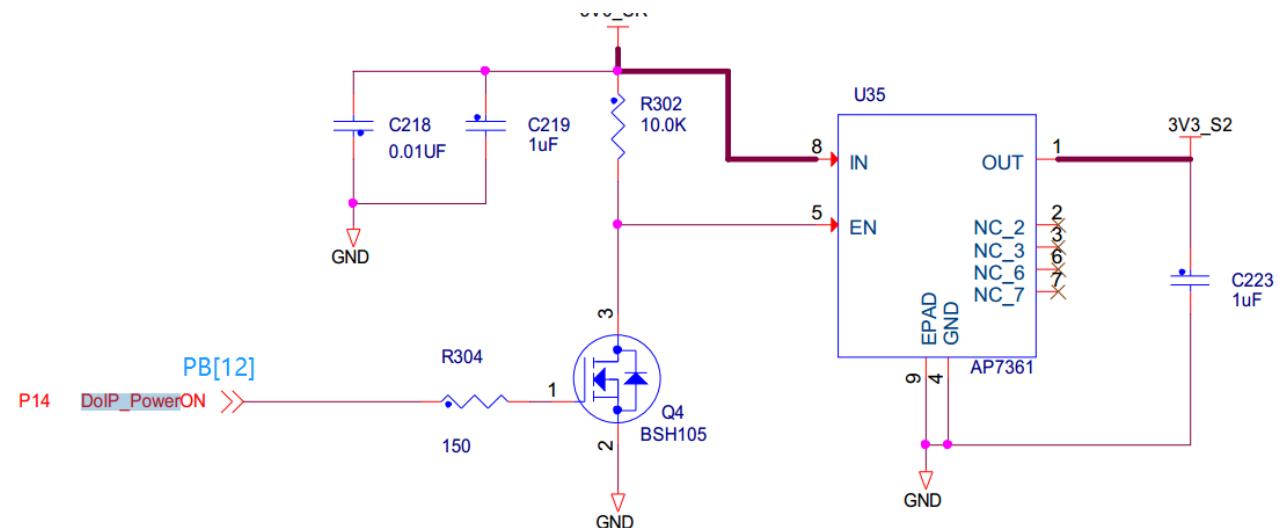

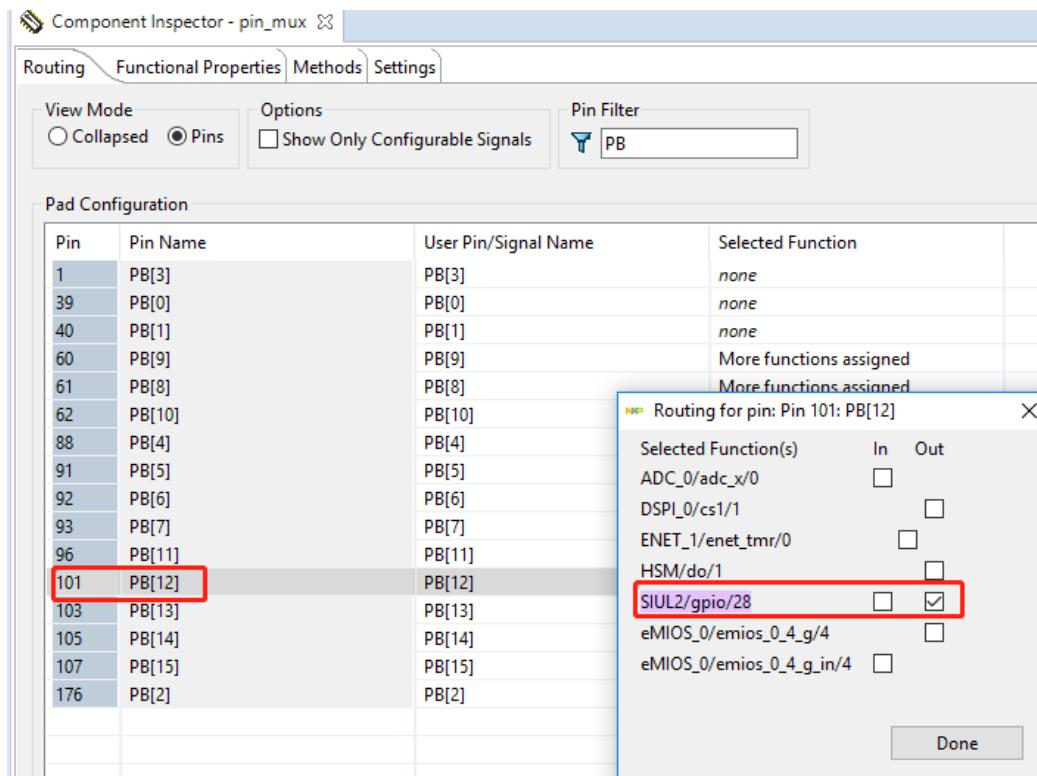

# Hands-on – ENET1: DP83848 configuration

- Initialize the DoIP-Reset pin

- Initialize to high level

# Hands-on – ENET1: DP83848 configuration

- Enable the DoIP Phy's Power

```

--

32 void Peripheral_Power_Supply_Init(void)

33 {

34     PINS_DRV_WritePin(PTB, 12, 0); //DoIP_Power enable

35

36     PINS_DRV_WritePin(PTD, 12, 1);

37     PINS_DRV_WritePin(PTD, 13, 1);

38 }

```

# Hands-on – ENET1: ENET configuration

- In ‘pin\_mux’ component → Routing(Collapsed) – select ‘ENET’

- Configuration the ports according to the schematic.

Routing   Functional Properties   Methods   Settings

View Mode: Collapsed   Options: Show Only Configurable Signals   Generate Report: HTML Report

ADC   CAN   CMP   DCI   DSPI   ENET   FCCU   FlexRay   HSM   I2C   LINFlexD   MLB   Platform   PowerAndGround   SAI   SIUL2   SPI   SSCM   USB   WKPU   eMIOS   uSDHC

| Signals                                 | Pin/Signal Selection | Direction    | Selected Pin/Signal Name |

|-----------------------------------------|----------------------|--------------|--------------------------|

| ENET MII Receive Data 2                 | No pin routed        | Input        |                          |

| ENET MII Receive Data 3                 | No pin routed        | Input        |                          |

| ENET MII Transmit Data 2                | No pin routed        | Output       |                          |

| ENET MII Transmit Data 3                | No pin routed        | Output       |                          |

| ENET0 MII Transmit Error                | No pin routed        | Output       |                          |

| ENET0 RMII Management Data Clock        | PG[0]                | Output       | PG[0]                    |

| ENET0 RMII Management Data Input/Output | PF[14]               | Input_Output | PF[14]                   |

| ENET0 RMII Receive Data 0               | No pin routed        | Input        |                          |

| ENET0 RMII Receive Data 1               | No pin routed        | Input        |                          |

| ENET0 RMII Receive Data Valid           | No pin routed        | Input        |                          |

| ENET0 RMII Receive Error                | No pin routed        | Input        |                          |

| ENET0 RMII Transmit Clock               | PG[1]                | Input        | PG[1]                    |

| ENET0 RMII Transmit Data 0              | No pin routed        | Output       |                          |

| ENET0 RMII Transmit Data 1              | No pin routed        | Output       |                          |

| ENET0 RMII Transmit Enable              | No pin routed        | Output       |                          |

| ENET1                                   |                      |              |                          |

| ENET Timer 0                            | No pin routed        | Input_Output |                          |

| ENET Timer 1                            | No pin routed        | Input_Output |                          |

| ENET1 MII Receive Clock                 | PB[11]               | Input        | PB[11]                   |

| ENET1 MII Receive Data 0                | PD[10]               | Input        | PD[10]                   |

| ENET1 MII Receive Data 1                | PD[9]                | Input        | PD[9]                    |

| ENET1 MII Receive Data 2                | PB[7]                | Input        | PB[7]                    |

| ENET1 MII Receive Data 3                | PB[6]                | Input        | PB[6]                    |

| ENET1 MII Receive Data Valid            | PB[5]                | Input        | PB[5]                    |

| ENET1 MII Transmit Clock                | PE[12]               | Input        | PE[12]                   |

| ENET1 MII Transmit Data 0               | PA[11]               | Output       | PA[11]                   |

| ENET1 MII Transmit Data 1               | PA[10]               | Output       | PA[10]                   |

| ENET1 MII Transmit Data 2               | PH[3]                | Output       | PH[3]                    |

| ENET1 MII Transmit Data 3               | PI[13]               | Output       | PI[13]                   |

| ENET1 MII Transmit Enable               | PI[12]               | Output       | PI[12]                   |

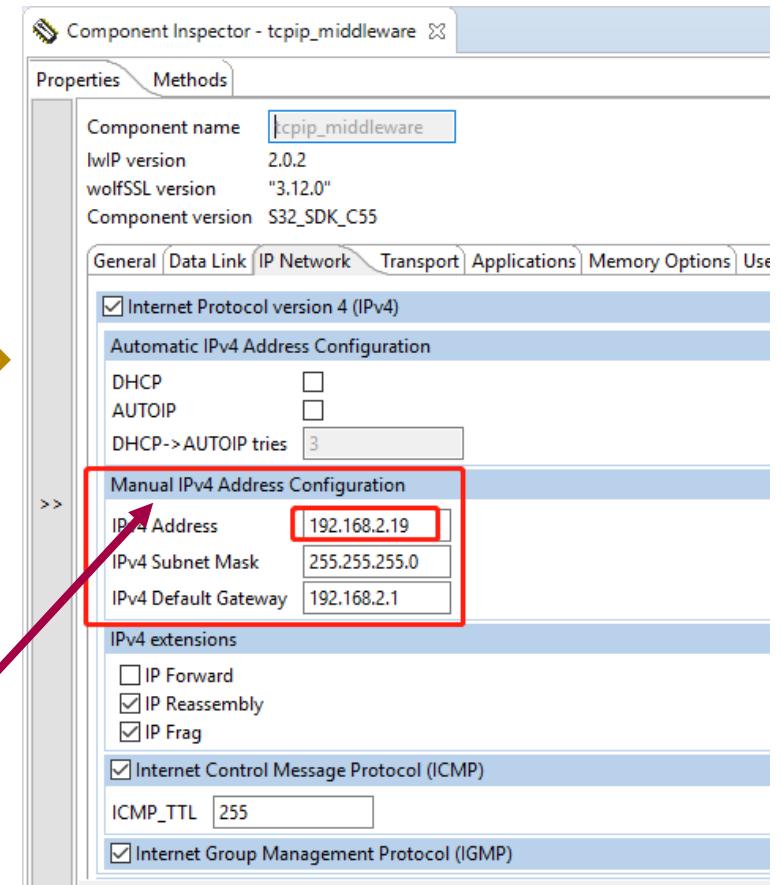

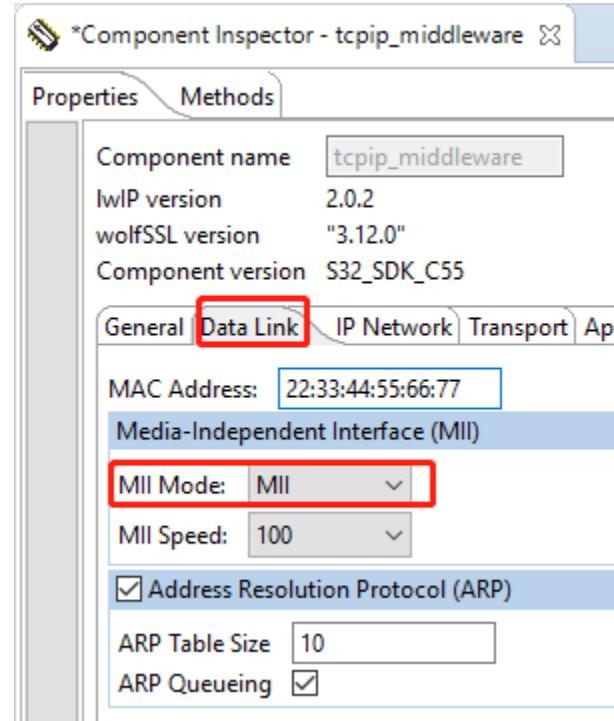

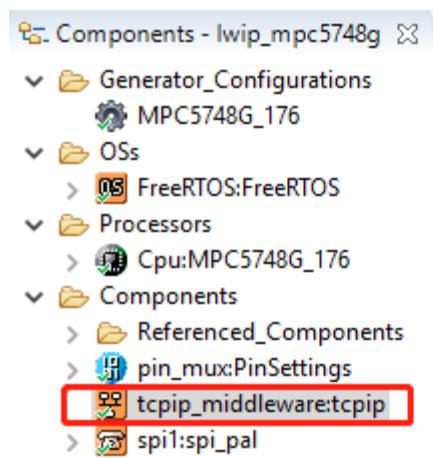

# Hands-on – ENET1: lwip middleware configuration

Define it by yourself

# Hands-on – ENET1: Application Code

## (1) Peripheral Power Supply:

- {Project Name} -> Source -> **main.c**

```

10 int main(void)

11 {

12

13     /** Processor Expert internal initialization. DON'T REMOVE THIS CODE!!!

14     #ifdef PEX_RTOS_INIT

15         PEX_RTOS_INIT();                         /* Initialization of the selected R

16     #endif

17

18     /** End of Processor Expert internal initialization.

19

20     /* Write your code here */

21     /* Initialize and configure clocks

22     *      - see clock manager component for details

23     */

24

25     CLOCK_SYS_Init(g_clockManConfigsArr, CLOCK_MANAGER_CONFIG_CNT, g_clockMa

26     CLOCK_SYS_UpdateConfiguration(0U, CLOCK_MANAGER_POLICY AGREEMENT);

27

28     /* Initialize pins

29     *      - See PinSettings component for more info

30     */

31     PINS_DRV_Init(NUM_OF_CONFIGURED_PINS, g_pin_max_InitConfigArr);

32     Enet1IOConfigure();

33

34     Peripheral_Power_Supply_Init();

35

36     start_example();

37

38 }

```

```

32 void Peripheral_Power_Supply_Init(void)

33 {

34     PINS_DRV_WritePin(PTB, 12, 0); //DoIP_Power enable

35

36     PINS_DRV_WritePin(PTD, 12, 1);

37     PINS_DRV_WritePin(PTD, 13, 1);

38 }

```

# Hands-on – ENET1: Application Code

## (2) Fix a problem that exists in our SDK

- {Project Name} -> SDK -> middleware -> tcpip -> tcpip\_stack -> ports -> netif -> enetif -> **enetif.h**

### Note:

If you have a patched after update the SDK, you can ignore this modification

```

55

56 #ifndef ENETIF_H

57 #define ENETIF_H

58

59 #include "lwip/err.h"

60

61 /*! @brief The ENET instance that you want to work on */

62 #ifdef GATEWAY_BOARD_DOIP

63 #define ENET_INSTANCE 1

64 #else

65 #define ENET_INSTANCE 0

66 #endif

67

68 #define ENET_QUEUE 0

69

70 /*! @brief Media-Independent Interface (MII) default setting */

```

### Explanation:

The SDK only implements the configuration for MAC0, and the code shown above needs to be added to support MAC1

# Hands-on – ENET1: Application Code

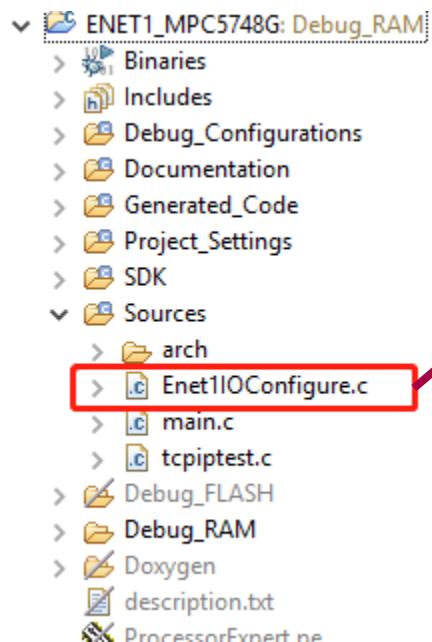

## (3) Fix a problem that exists in our PE

**CASE:** There is a problem with the generated code for ENET1's GPIO configuration.

You can refer to the sample demo(The project of *ENET1\_MPC5748G*) we provided. And copy the *Enet1IOConfigure.c* file to your project without any modification.

```

Enet1IOConfigure.c

...

7

8 #define RXD0_MSCR (*(volatile unsigned int *) 0xFFFFC0328UL)

9 #define RXD0_IMCR (*(volatile unsigned int *) 0xFFFFC1174UL)

10

11 #define RXD1_MSCR (*(volatile unsigned int *) 0xFFFFC0324UL)

12 #define RXD1_IMCR (*(volatile unsigned int *) 0xFFFFC1178UL)

13

14 #define RXD2_MSCR (*(volatile unsigned int *) 0xFFFFC029CUL)

15 #define RXD2_IMCR (*(volatile unsigned int *) 0xFFFFC117CUL)

16

17 #define RXD3_MSCR (*(volatile unsigned int *) 0xFFFFC0298UL)

18 #define RXD3_IMCR (*(volatile unsigned int *) 0xFFFFC1180UL)

19

20 #define RX_CLK_MSCR (*(volatile unsigned int *) 0xFFFFC02ACUL)

21 #define RX_CLK_IMCR (*(volatile unsigned int *) 0xFFFFC116CUL)

22

23 #define RX_DV_MSCR (*(volatile unsigned int *) 0xFFFFC0294UL)

24 #define RX_DV_IMCR (*(volatile unsigned int *) 0xFFFFC1184UL)

25

26 #define TX_CLK_MSCR (*(volatile unsigned int *) 0xFFFFC0370UL)

27 #define TX_CLK_IMCR (*(volatile unsigned int *) 0xFFFFC1170UL)

28

29 #define MDIO_MSCR (*(volatile unsigned int *) 0xFFFFC03B8UL)

30 #define MDIO_IMCR (*(volatile unsigned int *) 0xFFFFC1148UL)

31

32 #define MDC_MSCR (*(volatile unsigned int *) 0xFFFFC03C0UL)

```

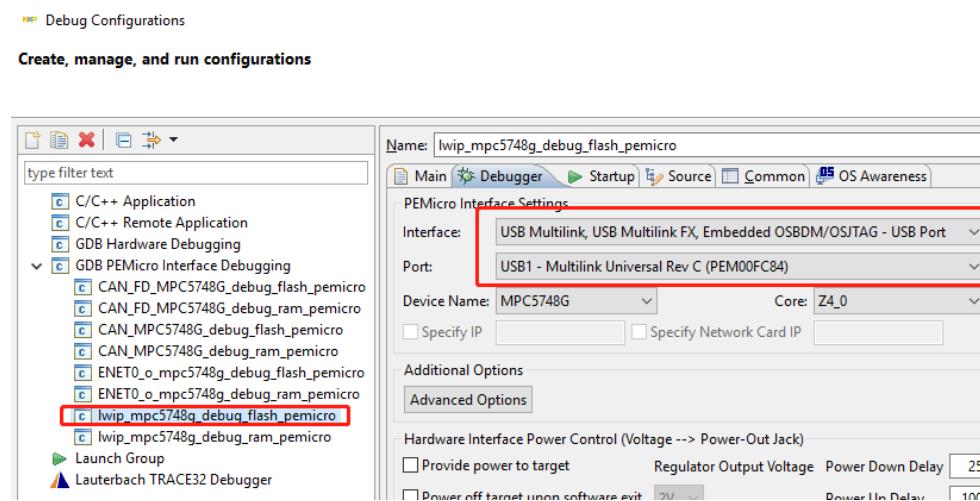

# Hands-on – ENET1: Application Code

## (4) Add client application for lwip\_tcp

- You can refer to the sample demo(The project of *ENET0\_MPC5748G*) we provided. And copy the *tcpipitest.c* file to your project without any modification.

- Add client application call function under the **test.c** file

- {Project Name} -> SDK -> middleware -> tcpip -> tcpip\_stack -> demo -> **test.c**

```

391 /* This function initializes applications

392  * Implements apps_init_Activity

393  */

394 static void

395 apps_init(void)

396 {

397 #ifdef GATEWAY_BOARD

398     tcpipitest_init();

399 #endif

400

401 #if LWIP_DNS_APP && LWIP_DNS

402     /* wait until the netif is up (for dhcp, autoip or p

403     * ose_timeout(5000, dns_donestart, NULL);

```

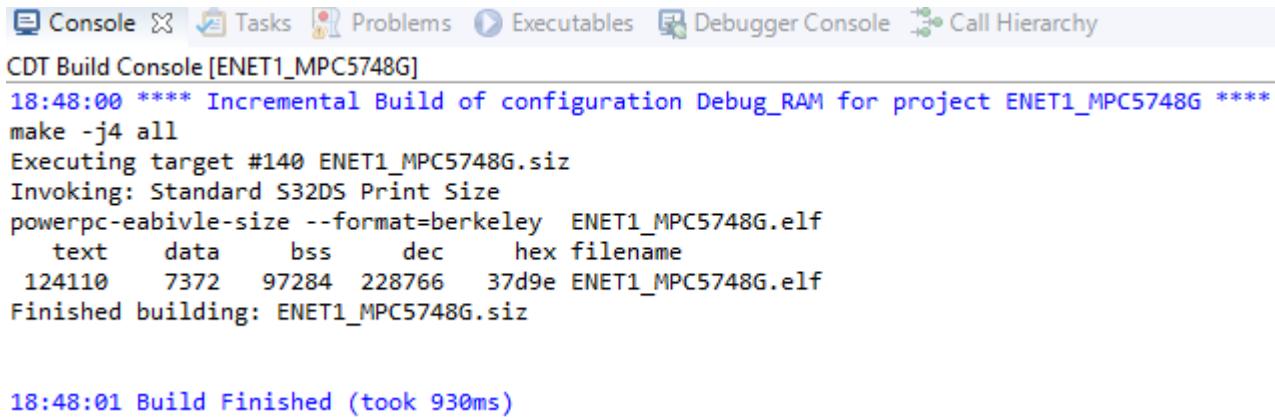

# Hands-on – ENET1: Build and Debug

- Click the ‘build project’ button – make sure there are no compilation errors

```

CDT Build Console [ENET1_MPC5748G]

18:48:00 **** Incremental Build of configuration Debug_RAM for project ENET1_MPC5748G ****

make -j4 all

Executing target #140 ENET1_MPC5748G.siz

Invoking: Standard S32DS Print Size

powerpc-eabivle-size --format=berkeley ENET1_MPC5748G.elf

text  data  bss  dec  hex filename

124110  7372  97284 228766  37d9e ENET1_MPC5748G.elf

Finished building: ENET1_MPC5748G.siz

18:48:01 Build Finished (took 930ms)

```

- Select the correct debug configuration and interface to debug the application

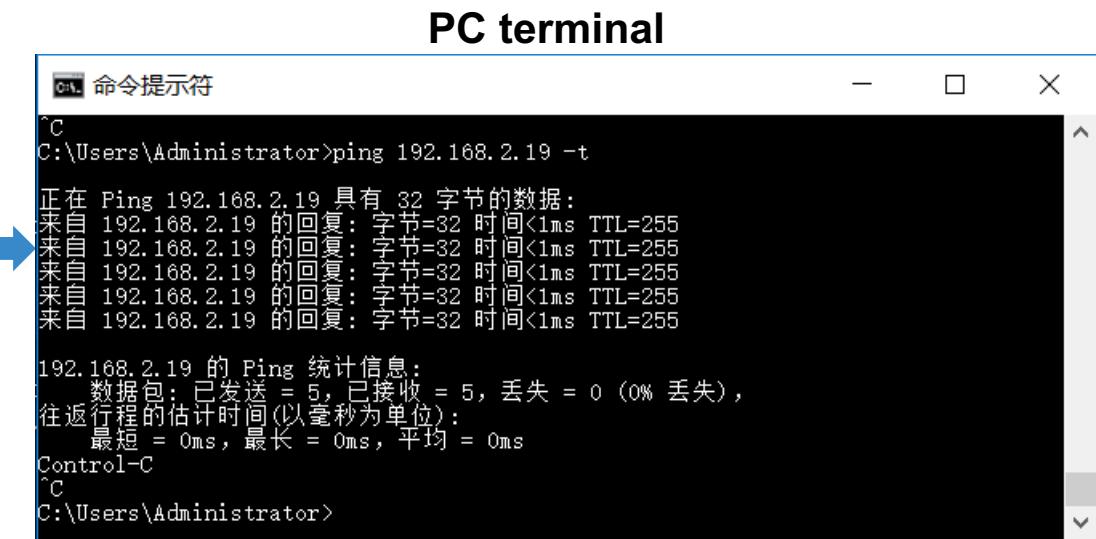

# Hands-on – ENET1: Build and Debug

TEST: Ping the board from PC:

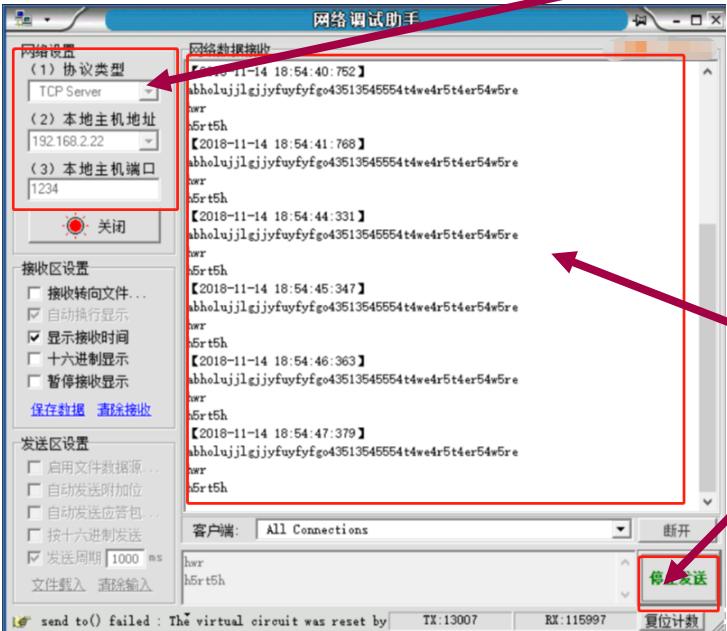

# Hands-on – ENET1: Build and Debug

TEST: LWIP\_tcp Client:

Gateway Board

```

34     memset(&server_addr, 0, sizeof(server_addr));

35     server_addr.sin_family = AF_INET;

36     server_addr.sin_addr.s_addr = inet_addr("192.168.2.22");

37     server_addr.sin_port = PP htons(PORT);

38     server_addr.sin_len = sizeof(server_addr);

39

40     ret= lwip_connect(socket_fd, (struct sockaddr*)&server_addr, sizeof(struct sockaddr));

41     if(ret != ERR_OK)

42     {

43         vTaskDelete(NULL);

44     }

45

46     for( ; );

47     {

48         ret = lwip_read(socket_fd, ReceiveBuff, sizeof(ReceiveBuff));

49         if(ret == -1)

50         {

51             lwip_close(socket_fd);

52             break;

53         }

54

55         ret = lwip_send(socket_fd, ReceiveBuff, sizeof(ReceiveBuff)-1, 0);

56         if(ret < 0)

57         {

58             lwip_close(socket_fd);

59             break;

60     }

```

TCP

Server ip:192.168.2.22

Port :1234

# 05.

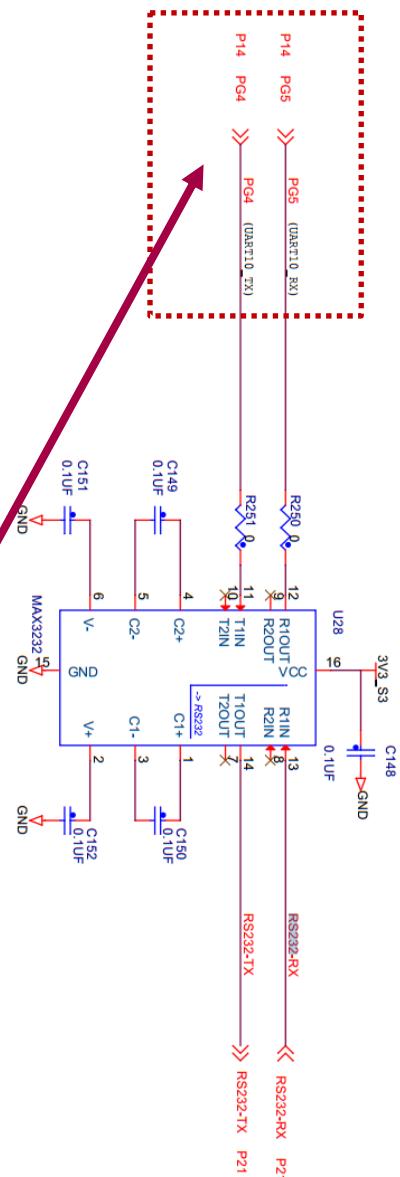

## Hands-on – UART

# Hands-on – UART: Objective

- Features of UART module on MPC5748G

- How to set a pin as output/input with SDK

- How to configure the port of UART

- How to modify an existing SDK project with S32DS to suit this board

# Hands-on – UART: Theory

- Full-duplex communication

- Separate clock for baud rate calculation

- The relationship “ $(2/3) * \text{LIN\_CLK} > \text{PBRIDGE}_{\text{Ex}}\text{\_CLK} > 1/3 * \text{LIN\_CLK}$ ” should be maintained.

- 15/16/7/8 bits data, parity

- 1/2/3 stop bits

- 12-bit + parity reception

- 4-byte buffer for reception, 4-byte buffer for transmission

- 12-bit counter for timeout management

- The maximum baud rate achievable is  $\text{LIN\_CLK}/4$  Mbit/s.

- For bit rate  $\leq \text{LIN\_CLK}/16$  Mbit/s

- Sixteen times oversampling

- 3:1 majority voting

- For  $\text{LIN\_CLK}/16$  Mbit/s  $<$  bit rate  $\leq \text{LIN\_CLK}/8$  Mbit/s

- Reduced over sampling programmable by the user

- 3:1 majority voting for reduced over sampling of 8

- For  $\text{LIN\_CLK}/8$  Mbit/s  $<$  bit rate  $\leq \text{LIN\_CLK}/4$  Mbit/s

- Reduced over sampling programmable by the user

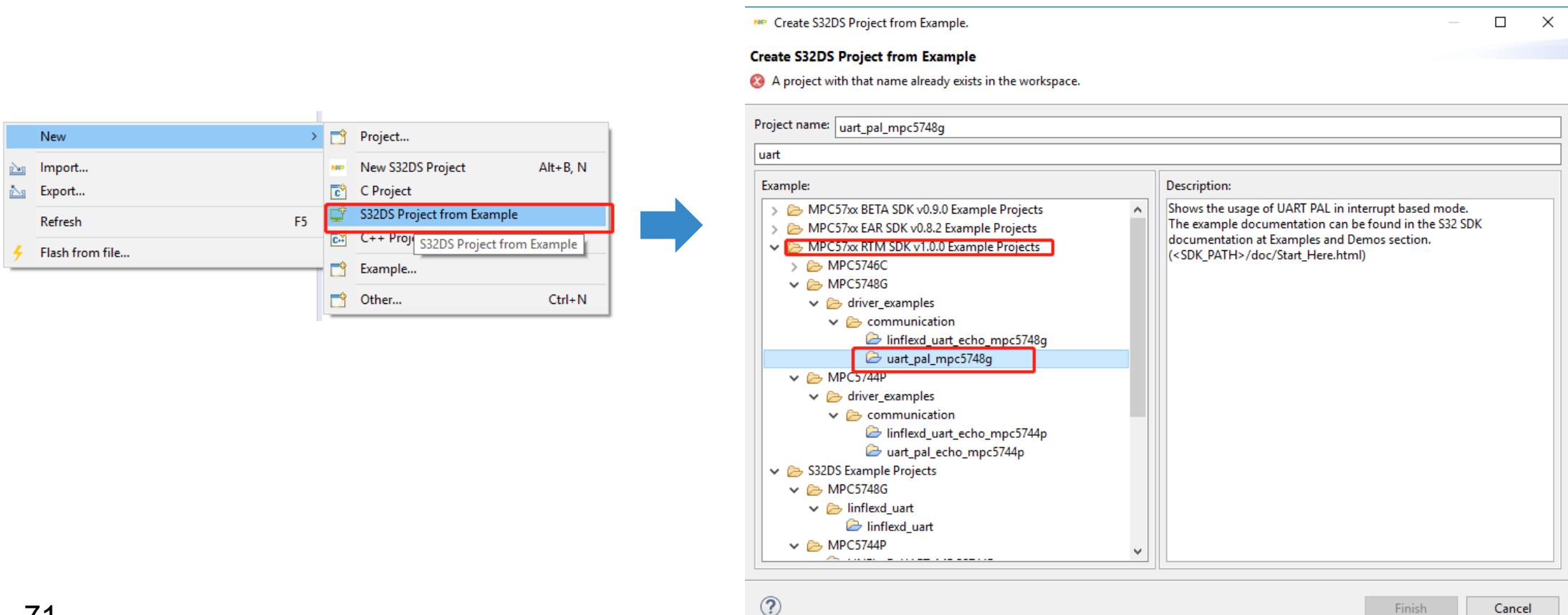

# Hands-on – UART: Import Example Project

- Import ‘uart’ example provided with the SDK:

- File->New->New S32DS Project from Example

- Select: **uart\_pal\_mpc5748g** from **MPC57xxRTM SDK v1.0.0 Example Projects**

# Hands-on – UART: Modify-Peripheral Power Supply

- Enable the peripheral power supply

- Open ‘pin\_mux’ component in ‘Component Inspector’ to configure pin routing

- SIUL2 tab -> GPIO 60 (61) > select the pin (one option) + direction output

Component Inspector - pin\_mux

Routing Functional Properties Methods Settings

View Mode: Collapsed (selected) Pins Show Only Configurable Signals:  pd

Pad Configuration

| Pin | Pin Name | User Pin/Signal Name | Selected Function       |

|-----|----------|----------------------|-------------------------|

| 77  | PD[0]    | PD[0]                | More functions assigned |

| 78  | PD[1]    | PD[1]                | More functions assigned |

| 79  | PD[2]    | PD[2]                | More functions assigned |

| 80  | PD[3]    | PD[3]                | More functions assigned |

| 81  | PD[4]    | PD[4]                | More functions assigned |

| 82  | PD[5]    | PD[5]                | More functions assigned |

| 83  | PD[6]    | PD[6]                | More functions assigned |

| 84  | PD[7]    | PD[7]                | More functions assigned |

| 87  | PD[8]    | PD[8]                | More functions assigned |

| 94  | PD[9]    | PD[9]                | none                    |

| 95  | PD[10]   | PD[10]               | none                    |

| 100 | PD[12]   | PD[12]               | SIUL2/gpio/60           |

| 102 | PD[13]   | PD[13]               | SIUL2/gpio/61           |

| 104 | PD[14]   | PD[14]               | none                    |

| 106 | PD[15]   | PD[15]               | none                    |

**P10 ON-OFF-CAN** (ON-OFF-CAN) (ON-OFF-ETH) 100 102 104 PD12 PD13

Component Inspector - pin\_mux

Basic Advanced

View Mode: Collapsed (selected) Pins Show Only Configurable Signals:

Signals

| Pin/Signal Selection | Direction     | Selected Pin/Signal Name |

|----------------------|---------------|--------------------------|

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| PC[11]               | Input         | PC[11]                   |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| GPIO 60              | PD[12]        | PD[12]                   |

| GPIO 61              | PD[13]        | PD[13]                   |

| No pin routed        | No pin routed |                          |

| No pin routed        | No pin routed |                          |

| PE[0]                | Input         | PE[0]                    |

| No pin routed        | No pin routed |                          |

Routing for pin: Pin 100: PD[12]

Selected Function(s):

| In                       | Out                                 |

|--------------------------|-------------------------------------|

| <input type="checkbox"/> | <input checked="" type="checkbox"/> |

| <input type="checkbox"/> | <input type="checkbox"/>            |

| <input type="checkbox"/> | <input type="checkbox"/>            |

| <input type="checkbox"/> | <input type="checkbox"/>            |

| <input type="checkbox"/> | <input checked="" type="checkbox"/> |

| <input type="checkbox"/> | <input type="checkbox"/>            |

| <input type="checkbox"/> | <input type="checkbox"/>            |

| <input type="checkbox"/> | <input type="checkbox"/>            |

SIUL2/gpio/60

Done

```

void Peripheral_Power_Supply_Init(void)

{

PINS_DRV_WritePin(PTD, 12, 1);

PINS_DRV_WritePin(PTD, 13, 1);

}

```

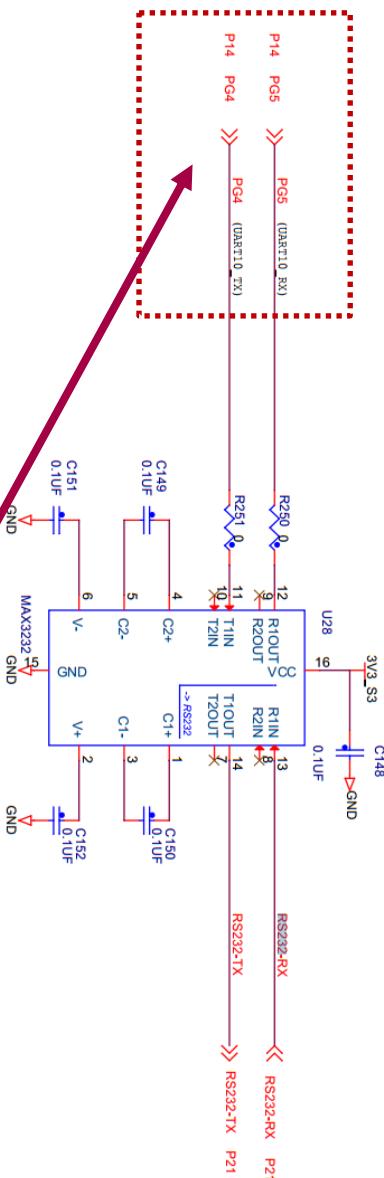

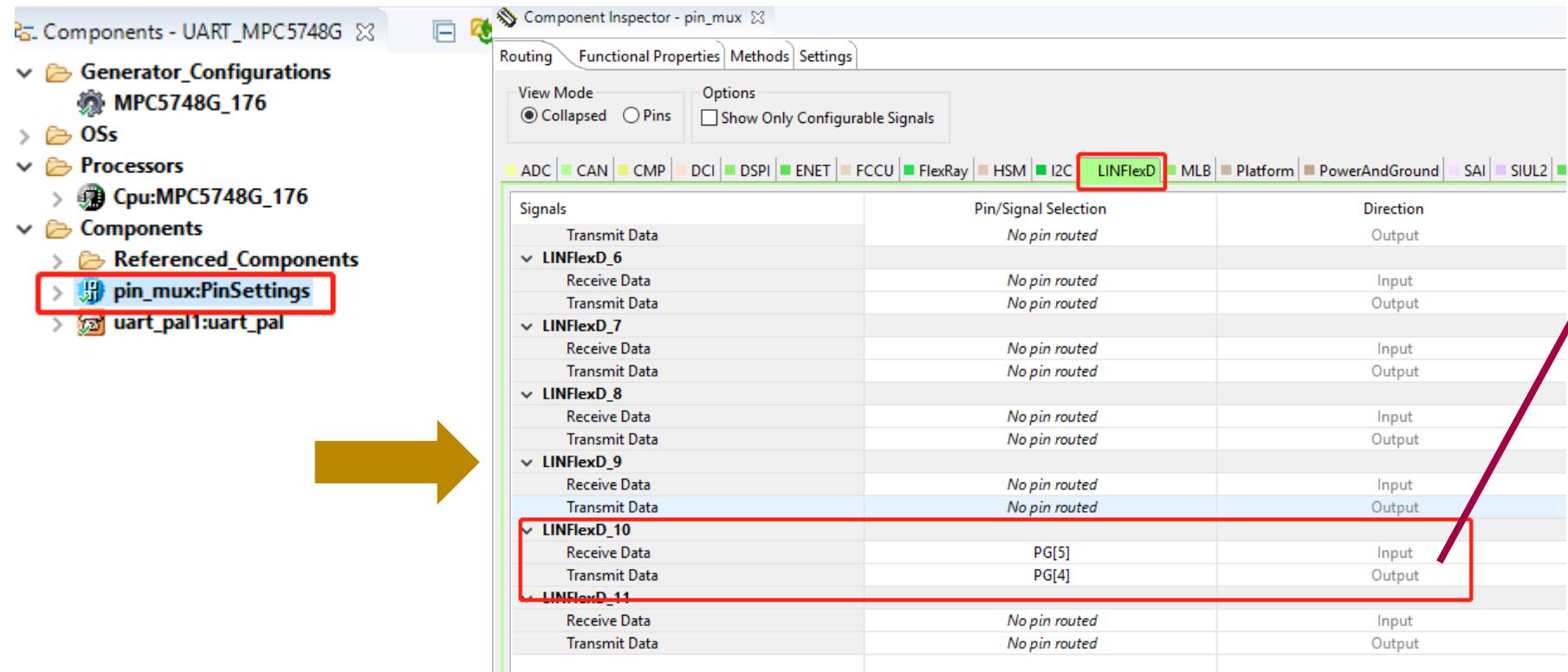

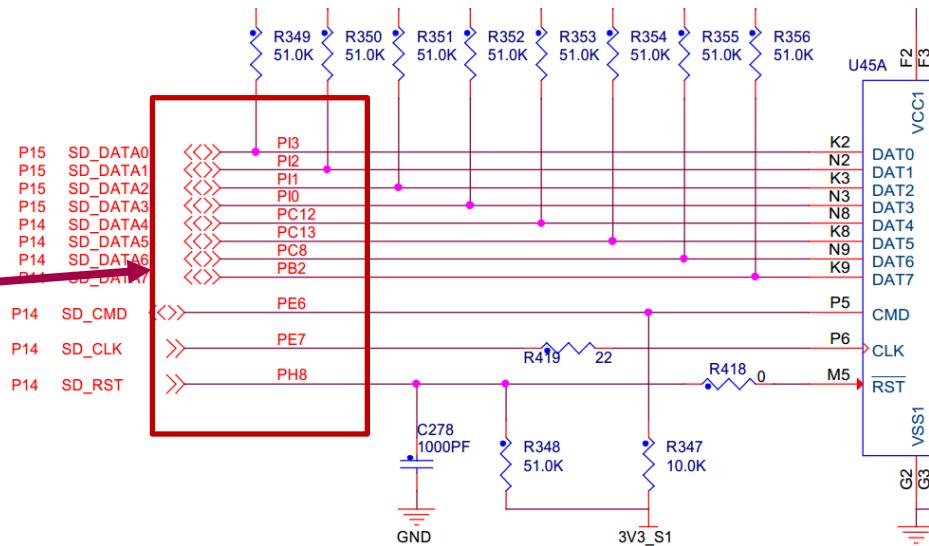

# Hands-on – UART: UART configuration

## (1) Configure the port of UART

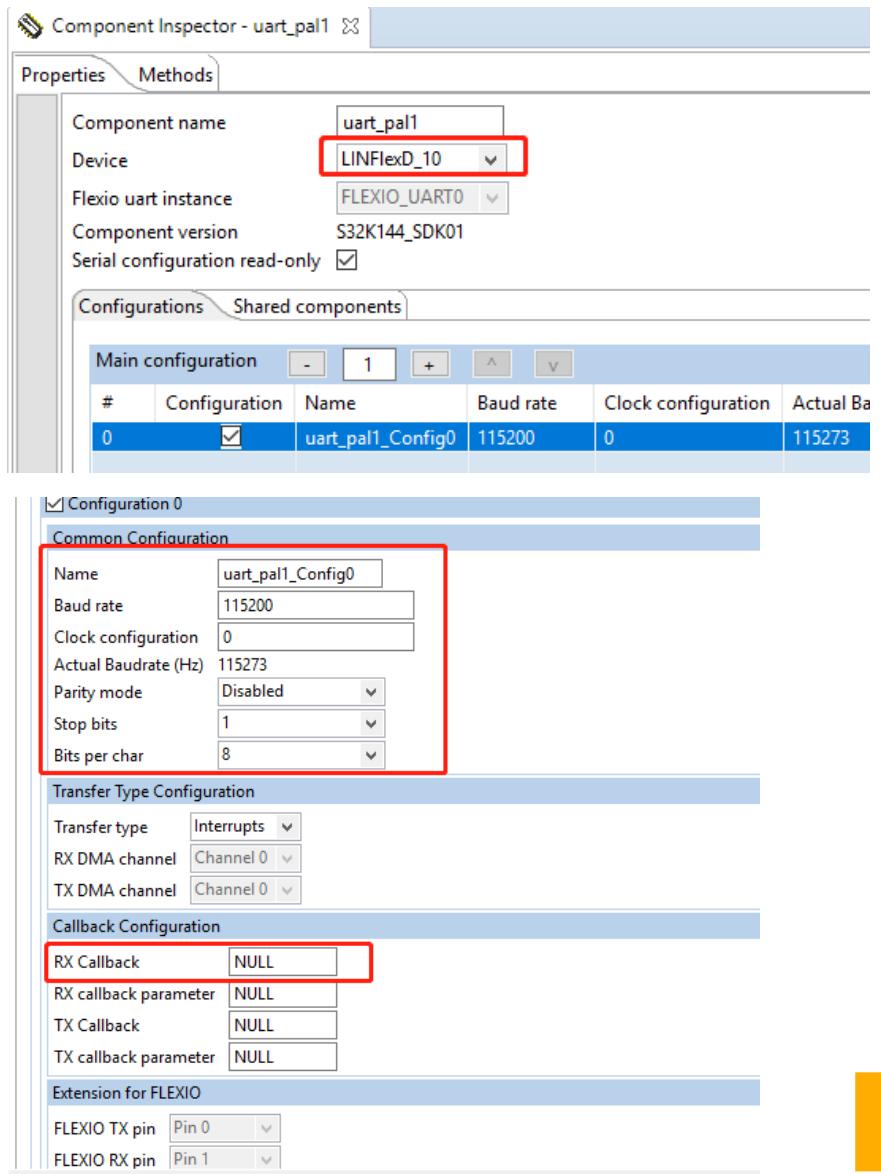

# Hands-on – UART: UART configuration

## (2) Configuration of UART properties

# Hands-on – UART: UART configuration

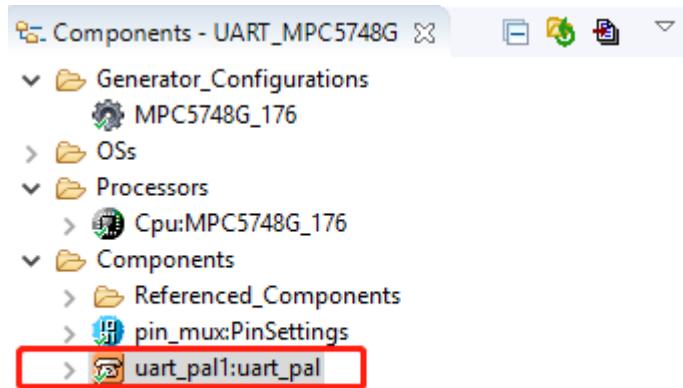

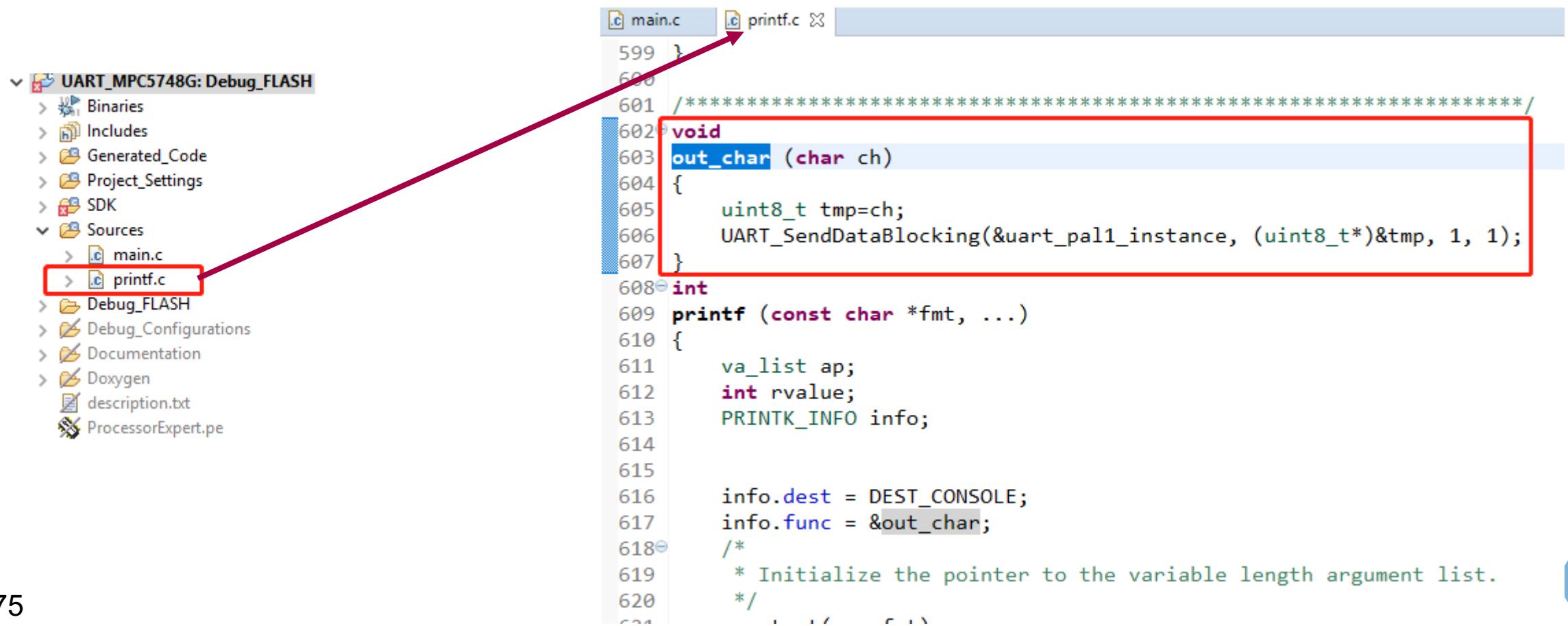

## (3) Port printf library functions

- You can refer to the sample demo(The project of *UART\_MPC5748G*) we provided. And copy the *printf.c* file to your project without any modification.

The screenshot shows a development environment with a project tree on the left and a code editor on the right.

**Project Tree:**

- UART\_MPC5748G: Debug\_FLASH

- Binaries

- Includes

- Generated\_Code

- Project\_Settings

- SDK

- Sources

- main.c

- printf.c

- Debug\_FLASH

- Debug\_Configurations

- Documentation

- Doxygen

- description.txt

- ProcessorExpert.pe

**Code Editor (printf.c):**

```

599 }

600

601 ****

602 void

603 out_char (char ch)

604 {

605     uint8_t tmp=ch;

606     UART_SendDataBlocking(&uart_pall1_instance, (uint8_t*)&tmp, 1, 1);

607 }

608 int

609 printf (const char *fmt, ...)

610 {

611     va_list ap;

612     int rvalue;

613     PRINTK_INFO info;

614

615

616     info.dest = DEST_CONSOLE;

617     info.func = &out_char;

618     /*

619      * Initialize the pointer to the variable length argument list.

620      */

621 }

```

A red box highlights the `out_char` function, and a red arrow points from the `printf.c` entry in the project tree to the same function in the code editor.

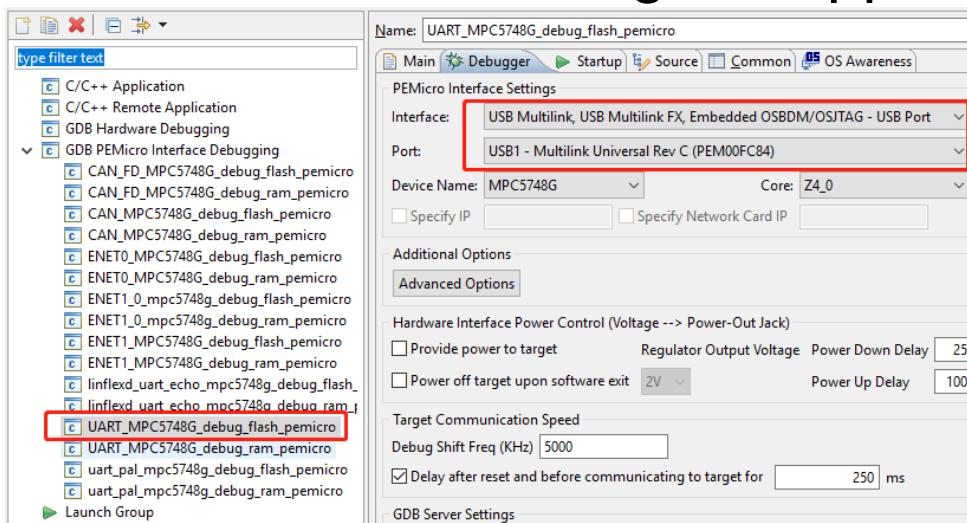

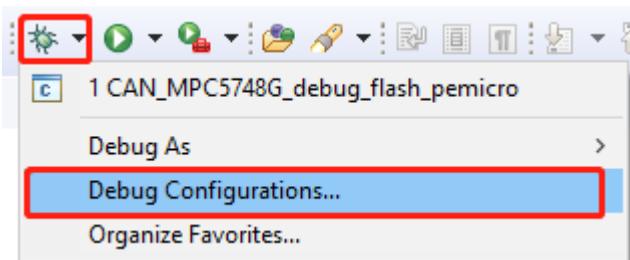

# Hands-on – UART: Build and Debug

- Click the ‘build project’ button – make sure there are no compilation errors

```

Problems Tasks Console Properties Debugger Console Call Hierarchy Search

CDT Build Console [UART_MPC5748G]

11:26:32 **** Incremental Build of configuration Debug_FLASH for project UART_MPC5748G ****

make -j4 all

Executing target #26 UART_MPC5748G.siz

Invoking: Standard S32DS Print Size

powerpc-eabivle-size --format=berkeley UART_MPC5748G.elf

text    data    bss    dec    hex filename

50396   20636   7392   78424  13258 UART_MPC5748G.elf

Finished building: UART_MPC5748G.siz

11:26:34 Build Finished (took 1s.539ms)

```

- Select the correct debug configuration and interface to debug the application

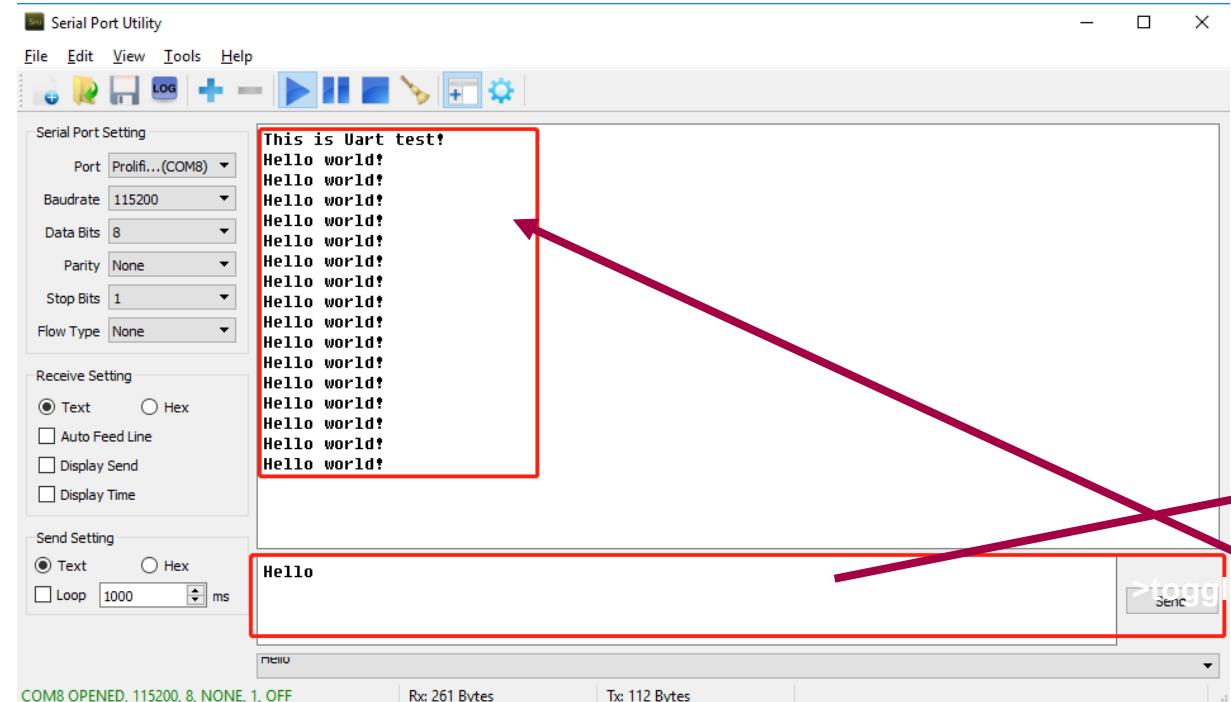

# Hands-on – UART: Build and Debug

## TEST: UART send and receive

### Main.c

```

95     g_clockManCallbacksArr, CLOCK_MANAGER_CALLBACK_CNI);

96     CLOCK_SYS_UpdateConfiguration(0U, CLOCK_MANAGER_POLICY_FORCIBLE);

97

98     /* Initialize pins */

99     PINS_DRV_Init(NUM_OF_CONFIGURED_PINS, g_pin_mux_InitConfigArr);

100

101    Peripheral_Power_Supply_Init();

102

103    /* Initialize UART PAL over LINFlexD */

104    UART_Init(&uart_pal1_instance, &uart_pal1_Config0);

105

106    /* Send the greeting message to console */

107    // UART_SendData(&uart_pal1_instance, (uint8_t*)msg, strlen(msg));

108    printf("This is Uart test!\n\r");

109

110    /* Infinite loop */

111    for( ; );

112    {

113        /* Get the message sent by user from the console, using blocking method, timeout 300 ms */

114        UART_ReceiveDataBlocking(&uart_pal1_instance, rxBuff, RX_MSG_LEN, 300U);

115

116        /* If the user typed "Hello", reply with the "Hello world!" message again */

117        if(strcmp((char*)rxBuff, "Hello") == 0)

118        {

119            // UART_SendDataBlocking(&uart_pal1_instance, (uint8_t*)msg, strlen(msg), 1000U);

120            printf("Hello world!\n\r");

121            /* Change the first character of the received buffer to avoid re-entering this branch,

122             * unless the user types "Hello" again */

123            rxBuff[0] = 0U;

```

# 06.

## Hands-on – LIN

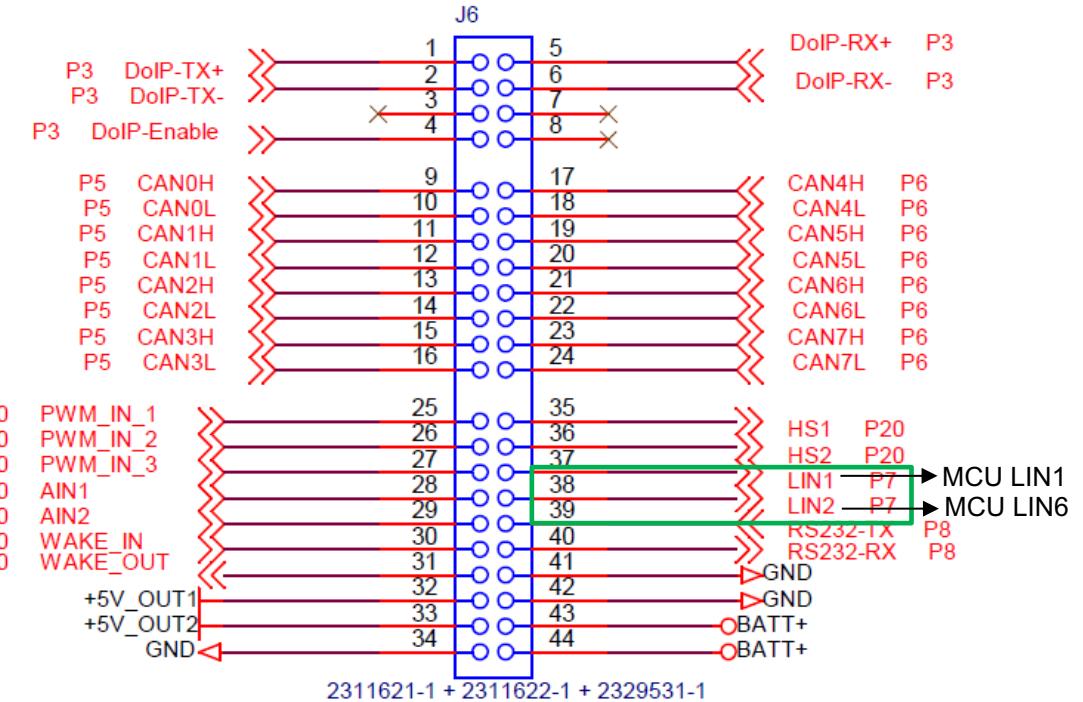

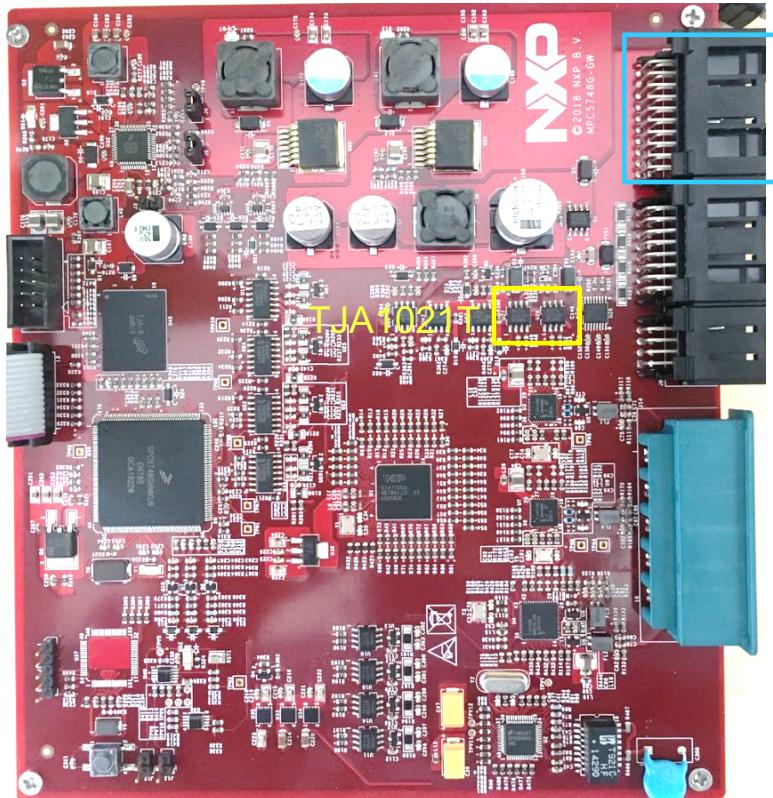

# Hands-on – LIN: Theory

- Supports LIN protocol version 1.3, 2.0, 2.1, and 2.2

- Bit rates up to 20 Kbit/s (LIN protocol)

- Master/Slave mode

- Classic and Enhanced Checksum calculation and check

- Single 8-byte buffer or FIFO for Transmission/Reception

- Timeout management

- Identifier filters

- DMA interface

- Supports a maximum of 16 possible identifiers

- Master mode with autonomous message handling

- Wakeup event on dominant bit detection

- True LIN field state machine

- Advanced LIN error detection

- Header, response, and frame timeout

- Slave mode