## 1. Features and Benefits

- Motor driver

- Driver for DC/BLDC/Stepper motor

- $R_{on}=0.8\Omega$  typ. for 1 half-bridge + shunt

- 2x NFET for each half-bridge

- on-chip charge-pump for top-NFETs

- $V_{ds}$  protection for all NFETs

- Microcontroller:

- MLX16-FX, application CPU

- MLX4, communication CPU

- 2x watch-dog

- +50 input interrupt controller

- Common purpose timer

- Memories split per CPU

- MLX16-FX memories:

- **64 kByte Flash with ECC**

- 10 kByte ROM

- **4 kByte RAM**

- 512 Byte EEPROM

- MLX4 memories:

- 6 kByte ROM

- 512 Byte RAM

- **Small QFN32,5x5 package**

- **Compatible with MLX81332 (32kB Flash)**

- **Automotive AEC-Q100 qualified**

- Periphery

- Configurable RC-clock 12..32 MHz

- 8x general purpose IO's, digital, analog, 1x high-voltage input, SPI, I2C-slave, UART

- 5x 16-bit motor PWM timers

- 2x 16-bit timers

- 10-bit ADC with < 6  $\mu$ s conversion time with multiple channels and different ADC references

- Differential current sense amplifier

- Temperature sensor, over-temperature detection

- Over-current detection, over-voltage and under-voltage protection

- Voltage regulators

- Internal voltage regulators, directly powered from 12V battery supply

- Operating voltage  $V_s$  = 5.5V to 20V

- Operation down to 3.5V with reduced analog characteristics, down to 3V without losing register content, down to 1.5V with intact RAM memory

- Low standby current consumption of typ 25 $\mu$ A (max 50  $\mu$ A) in sleep mode

- Wake-up possible via LIN, external pins or internal wake-up timer

- Bus interface

- LIN 2.x/SAE J2602 and ISO17987-4 compliant LIN slave

## 2. Application Examples

- Small Stepper/BLDC flap or valve, up to 1A per phase

- Small DC flap or valve, or single-coil fan, up to 1.4A

## 3. Ordering Information

| Order Code              | Temp. Range  | Package      | Delivery | Remark                     |

|-------------------------|--------------|--------------|----------|----------------------------|

| MLX81334 LLW-AMT-001-RE | -40 - 150 °C | QFN32_WF 5x5 | Reel     | DC/BLDC/Stepper with 8x IO |

Table 1 – Ordering information

## 4. Family Concept

|                                                            | MLX81330                                    | MLX81332                                          | MLX81334                                                |

|------------------------------------------------------------|---------------------------------------------|---------------------------------------------------|---------------------------------------------------------|

| MCU Memory                                                 | 32 KB Flash<br>+ 14 KB ROM                  | 32 KB Flash<br>+ 16 KB ROM                        | <b>64 KB Flash<br/>+ 16 KB ROM</b>                      |

| MCU EEPROM                                                 | 64x 8 Byte                                  | 64x 8 Byte                                        | <b>64x 8 Byte</b>                                       |

| MCU RAM                                                    | 2.5 KB                                      | 2.5 KB                                            | <b>4.5 KB</b>                                           |

| Driver                                                     | 4x Driver on-chip<br>typ. 3Ω Halfbridge     | 4x Driver on-chip<br>typ. 0.8Ω Halfbridge         | <b>4x Driver on-chip<br/>typ. 0.8Ω Halfbridge</b>       |

| IO pins (analog, digital)                                  | 3x LV + 1x HV/LV                            | 7x LV + 1x HV/LV                                  | <b>7x LV + 1x HV/LV</b>                                 |

| Motor current sense                                        | Low side,<br>On-chip                        | Low side,<br>On-chip                              | <b>Low side,<br/>On-chip</b>                            |

| Sensor interface (3V/5V supply)                            | analog, pwm, spi,<br>sent, I <sup>2</sup> C | analog, pwm, spi,<br>sent, I <sup>2</sup> C, uart | <b>analog, pwm, spi,<br/>sent, I<sup>2</sup>C, uart</b> |

| Sensorless support (hw + sw)                               | Yes                                         | Yes                                               | <b>Yes</b>                                              |

| LIN auto-address support (AA)                              | Yes                                         | Yes                                               | <b>Yes</b>                                              |

| Maximum IC Temperature<br>(with validated mission profile) | T <sub>j</sub> = 175°C                      | T <sub>j</sub> = 175°C                            | <b>T<sub>j</sub> = 175°C</b>                            |

| Package                                                    | QFN24, 4x4<br>SO8-ep                        | QFN24, 4x4<br>SO8-ep                              | <b>QFN32, 5x5</b>                                       |

Table 2 – Family Overview

## 5. Revision history

| Version | Date       | Description                        |

|---------|------------|------------------------------------|

| 1.0     | 15/11/2021 | Initial MLX81334 product abstract  |

| 2.0     | 03/04/2023 | Product abstract update for launch |

Table 3 – Revision history

## 6. Contents

|                                          |    |

|------------------------------------------|----|

| 1. Features and Benefits.....            | 1  |

| 2. Application Examples.....             | 1  |

| 3. Ordering Information .....            | 2  |

| 4. Family Concept.....                   | 2  |

| 5. Revision history .....                | 2  |

| 6. Contents.....                         | 3  |

| 7. IC Block diagram .....                | 4  |

| 8. Technical description.....            | 5  |

| 8.1. Package data QFN32.....             | 5  |

| 8.3. Package Pin-out .....               | 6  |

| 8.4. Package Marking .....               | 8  |

| 9. Typical application schematic .....   | 9  |

| 10. Electrical characteristics .....     | 10 |

| 10.1. Absolute maximum ratings .....     | 10 |

| 10.2. Operating range.....               | 11 |

| 10.3. Electrical specifications .....    | 12 |

| 10.3.1. Current consumption .....        | 12 |

| 10.3.2. Supply system .....              | 12 |

| 10.3.3. Clock generation .....           | 14 |

| 10.3.4. Motor driver module.....         | 15 |

| 10.3.5. VSM supply sensor.....           | 16 |

| 10.3.6. Over-temperature detection ..... | 16 |

| 10.3.7. ADC.....                         | 17 |

| 10.3.8. IO .....                         | 18 |

| 10.3.9. LIN.....                         | 19 |

| 11. Disclaimer.....                      | 22 |

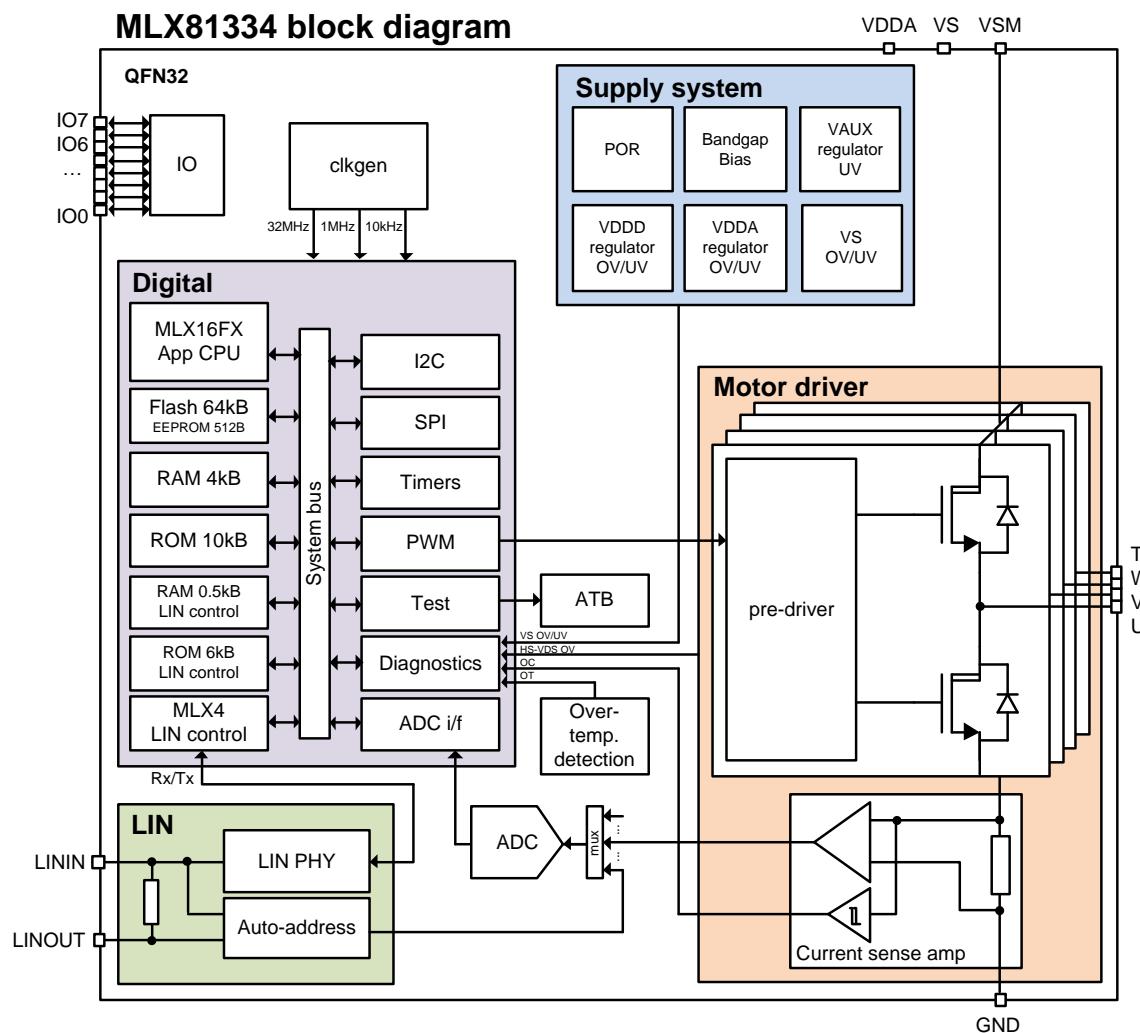

## 7. IC Block diagram

Figure 1 – IC Block diagram

## 8. Technical description

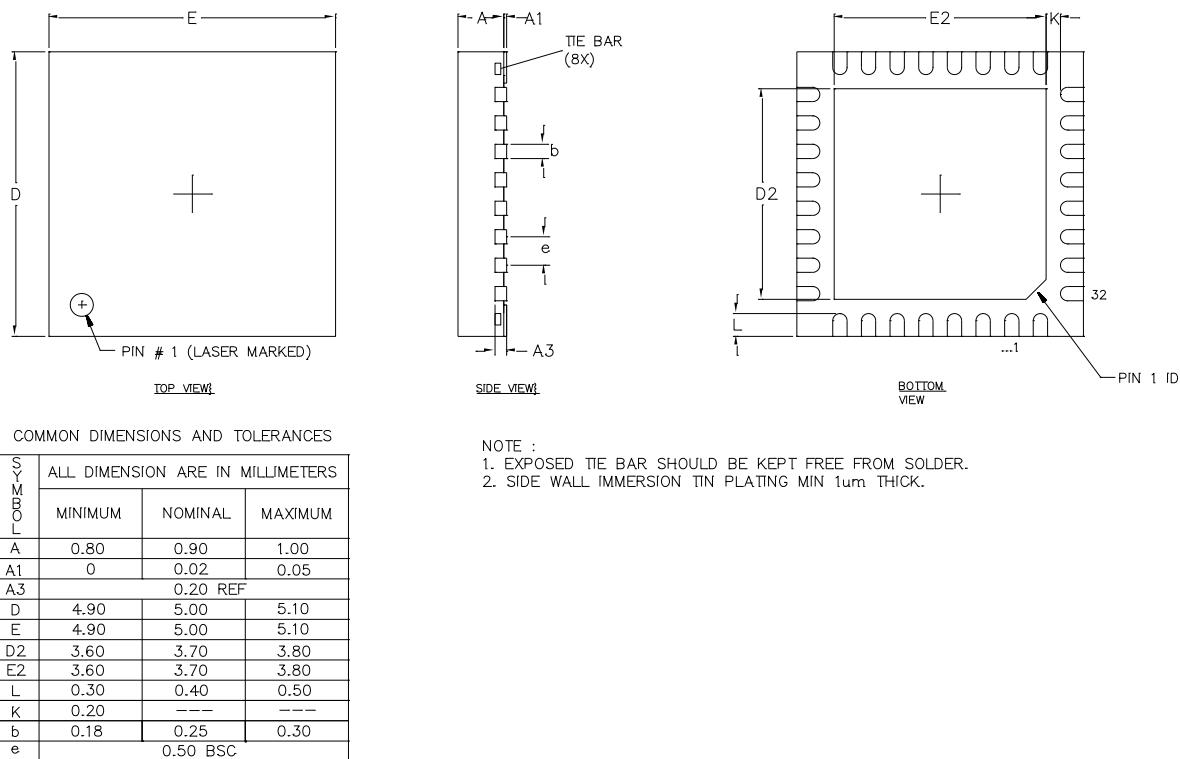

### 8.1. Package data QFN32

Figure 2 – Package data QFN32

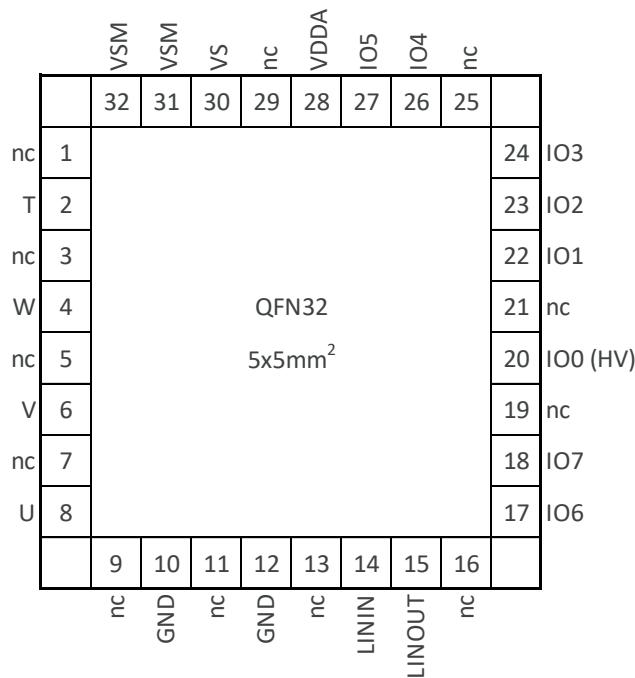

## 8.3. Package Pin-out

Figure 3 – Pin-out diagram QFN32

| #  | Pin name | Description         | Comment                    |

|----|----------|---------------------|----------------------------|

|    |          | <b>QFN32, 5x5mm</b> | <b>All pins accessible</b> |

| 1  | nc       |                     | <b>-0xx variant</b>        |

| 2  | T        | T-phase             |                            |

| 3  | nc       |                     |                            |

| 4  | W        | W-phase             |                            |

| 5  | nc       |                     |                            |

| 6  | V        | V-phase             |                            |

| 7  | nc       |                     |                            |

| 8  | U        | U-phase             |                            |

| 9  | nc       |                     |                            |

| 10 | GND      | Ground              |                            |

| 11 | nc       |                     |                            |

| 12 | GND      | Ground              |                            |

| 13 | nc       |                     |                            |

| #  | Pin name            | Description                        | Comment             |

|----|---------------------|------------------------------------|---------------------|

|    | <b>QFN32, 5x5mm</b> | <b>All pins accessible</b>         | <b>-0xx variant</b> |

| 14 | LIN-IN              | LIN input                          |                     |

| 15 | LIN-OUT             | LIN output (for auto-addressing)   |                     |

| 16 | nc                  |                                    |                     |

| 17 | IO6                 | LVIO + test input for development  |                     |

| 18 | IO7                 | LVIO + test output for development |                     |

| 19 | nc                  |                                    |                     |

| 20 | IO0                 | LVIO + HVI (high-voltage input)    |                     |

| 21 | nc                  |                                    |                     |

| 22 | IO1                 | LVIO                               |                     |

| 23 | IO2                 | LVIO                               |                     |

| 24 | IO3                 | LVIO                               |                     |

| 25 | nc                  |                                    |                     |

| 26 | IO4                 | LVIO                               |                     |

| 27 | IO5                 | LVIO                               |                     |

| 28 | VDDA                | 3.3V analog supply voltage         |                     |

| 29 | nc                  |                                    |                     |

| 30 | VS                  | Supply voltage for MCU             |                     |

| 31 | VSM                 | Supply voltage for motor driver    |                     |

| 32 | VSM                 | Supply voltage for motor driver    |                     |

Table 4 – Pin-out description for QFN32

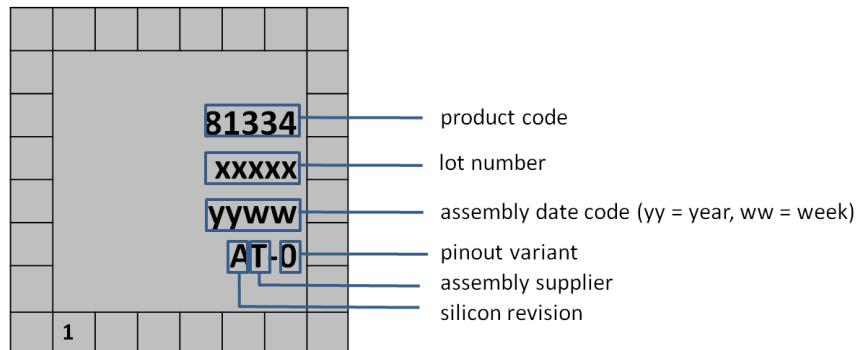

## 8.4. Package Marking

Figure 4 – Package Marking QFN32

## 9. Typical application schematic

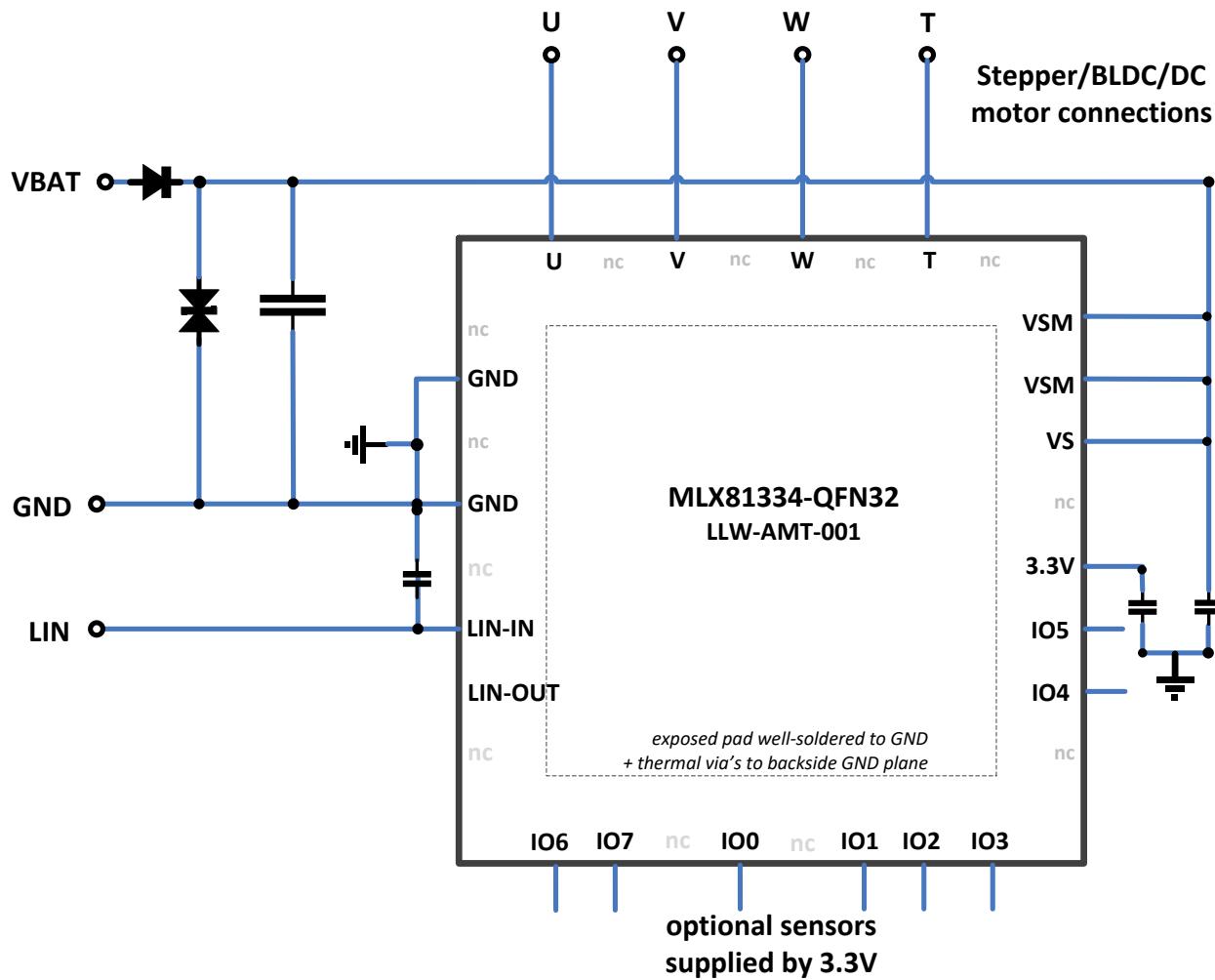

In the following schematic examples, external components are indicated that may be needed to protect the IC against EMC / ESD pulses. Depending on ECU conditioned power, overvoltage and reverse polarity discretes may not be needed. Capacitor discretes or capacitor values will depend on specific OEM ESD/EMC requirements

Figure 5 – Typical motor schematic with MLX81334 in QFN32

## 10. Electrical characteristics

### 10.1. Absolute maximum ratings

| Parameter                 | Symbol      | Min. | Typ. | Max.     | Unit | Condition                         |

|---------------------------|-------------|------|------|----------|------|-----------------------------------|

| Supply voltage            | VS, VSM     | -0.3 |      | 28       | V    |                                   |

| Supply voltage            | VS, VSM     | -0.3 |      | 40       | V    | t < 500ms                         |

| Supply voltage transient  | VS.tr1      | -100 |      |          | V    | ISO 7637-2 pulse 1 [1]            |

| Supply voltage transient  | VS.tr2      |      |      | 75       | V    | ISO 7637-2 pulse 2 [1]            |

| Supply voltage transient  | VS.tr3      | -150 |      | 100      | V    | ISO 7637-2 pulses 3a, 3b [1]      |

| Output voltage            | VDDA        | -0.3 |      | 5.5      | V    |                                   |

| LIN bus voltage           | VLIN        | -40  |      |          | V    | Referenced to VS                  |

| LIN bus voltage           | VLIN        |      |      | 40       | V    | Referenced to GND                 |

| LIN bus voltage transient | VLIN.tr1    | -30  |      |          | V    | ISO 7637-3 DCC slow – [2]         |

| LIN bus voltage transient | VLIN.tr2    |      |      | 30       | V    | ISO 7637-3 DCC slow + [2]         |

| LIN bus voltage transient | VLIN.tr3    | -150 |      | 100      | V    | ISO 7637-2 pulses 3a, 3b [2]      |

| Analog HV voltage         | VAN_HV      | -0.3 |      | VS+0.3   | V    | IO0 (HV input mode)<br>U, V, W, T |

| Analog LV voltage         | VAN_LV      | -0.3 |      | VDDA+0.3 | V    | IO0...7                           |

| Digital input voltage     | VIN_DIG     | -0.3 |      | VDDA+0.3 | V    | IO0...7                           |

| Digital output voltage    | VOUT_DIG    | -0.3 |      | VDDA+0.3 | V    | IO0...7                           |

| ESD HBM capability        | ESD_HBM     | -2   |      | 2        | kV   | All pins except LININ, LINOUT     |

| ESD HBM capability        | ESD_HBM_LIN | -6   |      | 6        | kV   | Pins LININ, LINOUT                |

| ESD CDM capability        | ESD_CDM     | -500 |      | 500      | V    | All pins                          |

| Junction temperature      | TJ          | -55  |      | 175      | °C   |                                   |

Table 5 – Absolute maximum ratings

[1] ISO 7637 test pulses are applied to VS via a reverse polarity diode and blocking capacitor.

[2] ISO 7637 test pulses are applied to LIN via a coupling capacitance of 1nF.

## 10.2. Operating range

| Parameter            | Symbol                           | Min. | Typ. | Max. | Unit | Condition                                  |

|----------------------|----------------------------------|------|------|------|------|--------------------------------------------|

| Supply voltage       | V <sub>S</sub> , V <sub>SM</sub> | 6.5  | 12   | 20   | V    | Driver full performance                    |

| Supply voltage       | V <sub>S</sub> , V <sub>SM</sub> | 5.5  |      | 6.5  | V    | Driver reduced performance [1]             |

| Supply voltage       | V <sub>S</sub>                   | 4    |      | 20   | V    | Analog full performance                    |

| Supply voltage       | V <sub>S</sub>                   | 3.5  |      | 4    | V    | Analog reduced performance [2]             |

| Supply voltage       | V <sub>S</sub>                   | 3    |      | 20   | V    | Digital functional                         |

| Supply voltage       | V <sub>S</sub>                   | 1.5  |      | 20   | V    | SRAM content valid                         |

| Junction temperature | T <sub>J</sub>                   | -40  |      | 175  | °C   | Limited time at T <sub>J</sub> =175 °C [3] |

*Table 6 – Operating range*

[1] Motor driver is functional at reduced performance (higher bridge resistance, reduced accuracy of current sense amplifier)

[2] 3.3V regulator is functional at reduced performance (lower current capability)

[3] Extended temperature range with T<sub>J</sub>=175 °C is only allowed for a limited time, customer's mission profile has to be agreed by Melexis as an obligatory part of the Part Submission Warrant (PSW).

## 10.3. Electrical specifications

### 10.3.1. Current consumption

| Parameter              | Symbol | Min. | Typ. | Max. | Unit | Condition |

|------------------------|--------|------|------|------|------|-----------|

| Normal working current | INOM   |      | 10   | 15   | mA   |           |

| Sleep mode current     | ISLEEP |      | 25   | 50   | µA   | VS=13V    |

| Stop mode current      | ISTOP  |      | 250  | 500  | µA   |           |

| Holding current        | IHOLD  |      | 5    | 7    | mA   |           |

Table 7 – Electrical specifications : current consumption

### 10.3.2. Supply system

#### 10.3.2.1. VDDA 3.3V regulator (5V option, external C: 0 ... 220nF)

| Parameter                               | Symbol      | Min. | Typ. | Max. | Unit | Condition                          |

|-----------------------------------------|-------------|------|------|------|------|------------------------------------|

| 3.3V analog supply voltage (default)    | VDDA        | 3.2  | 3.3  | 3.4  | V    | Bandgap and VDDA regulator trimmed |

| 3.3V current capability                 | IVDDA       | 20   |      |      | mA   | VS >= 4V                           |

| 3.3V external current capability        | IVDDA_EXT   | 0    |      | 15   | mA   | VS >= 4V                           |

| 3.3V under-voltage detection threshold  | VTH_UV_VDDA | 2.75 | 2.85 | 2.95 | V    | VDDA ramping down                  |

| 3.3V under-voltage detection hysteresis | VHY_UV_VDDA | 0.1  | 0.15 |      | V    |                                    |

#### 5V option (SWITCH\_VDDA\_TO\_5V=1)

|                                       |             |      |      |      |    |                                    |

|---------------------------------------|-------------|------|------|------|----|------------------------------------|

| 5V analog supply voltage (option)     | VDDA        | 4.85 | 5    | 5.15 | V  | Bandgap and VDDA regulator trimmed |

| 5V current capability                 | IVDDA       | 20   |      |      | mA | VS >= 6V                           |

| 5V external current capability        | IVDDA_EXT   | 0    |      | 15   | mA | VS >= 6V                           |

| 5V under-voltage detection threshold  | VTH_UV_VDDA | 3.95 | 4.1  | 4.25 | V  | VDDA ramping down                  |

| 5V under-voltage detection hysteresis | VHY_UV_VDDA | 0.1  | 0.15 |      | V  |                                    |

Table 8 – Electrical specifications : VDDA regulator

### 10.3.2.2. VDDD 1.8V regulator

| Parameter                   | Symbol | Min. | Typ.  | Max. | Unit | Condition                          |

|-----------------------------|--------|------|-------|------|------|------------------------------------|

| 1.8V digital supply voltage | VDDD   | 1.8  | 1.875 | 1.95 | V    | Bandgap and VDDD regulator trimmed |

| 1.8V current capability     | IVDDD  | 15   |       |      | mA   |                                    |

*Table 9 – Electrical specifications : VDDD regulator*

### 10.3.2.3. VS under-voltage and over-voltage detection

| Parameter                             | Symbol    | Min. | Typ. | Max. | Unit | Condition |

|---------------------------------------|-----------|------|------|------|------|-----------|

| VS under-voltage detection threshold  | VTH_UV_VS | 3.5  | 4    | 4.5  | V    | PRUV_VS=0 |

| VS under-voltage detection threshold  | VTH_UV_VS | 4.5  | 5    | 5.5  | V    | PRUV_VS=1 |

| VS under-voltage detection threshold  | VTH_UV_VS | 5.5  | 6    | 6.5  | V    | PRUV_VS=2 |

| VS under-voltage detection threshold  | VTH_UV_VS | 6.5  | 7    | 7.5  | V    | PRUV_VS=3 |

| VS under-voltage detection threshold  | VTH_UV_VS | 7.5  | 8    | 8.5  | V    | PRUV_VS=4 |

| VS under-voltage detection threshold  | VTH_UV_VS | 8.5  | 9    | 9.5  | V    | PRUV_VS=5 |

| VS under-voltage detection hysteresis | VHY_UV_VS | 0.1  | 0.5  | 1    | V    |           |

| VS over-voltage detection threshold   | VTH_OV_VS | 20   | 22   | 24   | V    | PROV_VS=0 |

| VS over-voltage detection threshold   | VTH_OV_VS | 22   | 24   | 26   | V    | PROV_VS=1 |

| VS over-voltage detection threshold   | VTH_OV_VS | 38   | 40   | 42   | V    | PROV_VS=2 |

| VS over-voltage detection hysteresis  | VHY_OV_VS | 1    | 2    | 3    | V    |           |

*Table 10 – Electrical specifications : VS over- and under-voltage detection*

### 10.3.2.4. Wake-up circuit

| Parameter                      | Symbol        | Min. | Typ.                | Max. | Unit | Condition           |

|--------------------------------|---------------|------|---------------------|------|------|---------------------|

| Wake-up filter time<br>IO pins | TFILT_W_U_IO  | 15   |                     | 80   | μs   |                     |

| Wake-up filter time<br>LIN pin | TFILT_W_U_LIN | 28   |                     | 125  | μs   |                     |

| Wake-up time<br>internal timer | TWU_INT       |      | n/a                 |      |      | WUI=00 (no wake-up) |

| Wake-up time<br>internal timer | TWU_INT       |      | 4096 /<br>FOSC_10K  |      |      | WUI=01 (~0.4 s)     |

| Wake-up time<br>internal timer | TWU_INT       |      | 8192 /<br>FOSC_10K  |      |      | WUI=10 (~0.8 s)     |

| Wake-up time<br>internal timer | TWU_INT       |      | 16384 /<br>FOSC_10K |      |      | WUI=11 (~1.6 s)     |

Table 11 – Electrical specifications : wake-up circuit

### 10.3.2.5. Bandgap

| Parameter                             | Symbol | Min. | Typ.  | Max. | Unit  | Condition |

|---------------------------------------|--------|------|-------|------|-------|-----------|

| Bandgap voltage                       | VBG    | 1.15 | 1.185 | 1.22 | V     | Trimmed   |

| Bandgap voltage<br>temperature coeff. | TC_VBG |      |       | 180  | ppm/K |           |

Table 12 – Electrical specifications : bandgap

### 10.3.3. Clock generation

| Parameter                     | Symbol     | Min.  | Typ. | Max. | Unit | Condition                                                              |

|-------------------------------|------------|-------|------|------|------|------------------------------------------------------------------------|

| Frequency 1MHz<br>oscillator  | FOSC_1M    | -5%   | 1    | +5%  | MHz  | Trimmed                                                                |

| Frequency 32MHz<br>oscillator | FOSC_32M   | -5%   | 32   | +5%  | MHz  | Trimmed                                                                |

| Frequency 10kHz<br>oscillator | FOSC_10K   | 5     | 10   | 20   | kHz  |                                                                        |

| Timing accuracy               | TIMING_ACC | -1.5% |      | 1.5% | %    | Timing accuracy after sw correction<br>using EEPROM calibration values |

Table 13 – Electrical specifications : clock generation

## 10.3.4. Motor driver module

### 10.3.4.1. Charge Pump clock

| Parameter                   | Symbol  | Min. | Typ. | Max. | Unit | Condition         |

|-----------------------------|---------|------|------|------|------|-------------------|

| Charge pump clock frequency | FOSC_CP | 51   | 60   | 69   | MHz  | Trimmed           |

| Charge pump clock frequency | FOSC_CP | 71   | 82   | 93   | MHz  | Trimmed (default) |

Table 14 – Electrical specifications : driver clock

### 10.3.4.2. Output stage

| Parameter                             | Symbol                | Min. | Typ. | Max. | Unit             | Condition                                                                  |

|---------------------------------------|-----------------------|------|------|------|------------------|----------------------------------------------------------------------------|

| Half-bridge phase current             | IHB                   |      |      | 1.0  | A <sub>pk</sub>  | During normal operation                                                    |

| Half-bridge phase current             | IHB                   |      |      | 0.7  | A <sub>rms</sub> | During normal operation                                                    |

| Half-bridge phase boost current       | IHB                   |      |      | 1.3  | A                | < 1s, ambient temperature -40°C...85°C [1]                                 |

| 2x half-bridge phase boost current    | IHB                   |      |      | 1.8  | A                | < 1s, ambient temperature -40°C...85°C, 2 phases in parallel [1]           |

| Half-bridge resistance                | RHB                   |      | 0.8  | 1.6  | Ω                | TopFET + BottomFet + Shunt                                                 |

| Duty cycle range of PWM output        | DC_OUT                | 2    |      | 98   | %                | For switching PWM (0% or 100% can be set as well)<br>PWM frequency = 20kHz |

| Duty cycle of PWM output              | DC_OUT                | 1    |      | 3    | %                | PWM duty cycle setting = 2%<br>PWM frequency = 20kHz                       |

| Duty cycle of PWM output              | DC_OUT                | 97   |      | 99   | %                | PWM duty cycle setting = 98%<br>PWM frequency = 20kHz                      |

| FET over-current detection threshold  | ITH_DS_H <sub>S</sub> | 1.6  | 2.2  | 2.8  | A                |                                                                            |

| FET over-current detection hysteresis | IHY_DS                |      | 0.1  |      | A                |                                                                            |

Table 15 – Electrical specifications : output stage

[1] Time between boost cycles is 2x boost time

### 10.3.4.3. Current sense amplifier

| Parameter                                 | Symbol     | Min.  | Typ. | Max.  | Unit | Condition                                           |

|-------------------------------------------|------------|-------|------|-------|------|-----------------------------------------------------|

| Sense resistor                            | RCS        |       | 0.1  | 0.2   | Ω    |                                                     |

| Input range                               | ICS        | -2    |      | 2     | A    | Current sensing range                               |

| Input range                               | ICS        |       |      | 4     | A    | High-end range extension for over-current detection |

| Over-current detection threshold          | ITH_OC     | -2    |      | 4     | A    | Adjustable through 8bit DAC [1]                     |

| Over-current detection threshold accuracy | ITH_OC     | -10   |      | 10    | %    | OCD threshold = 2A                                  |

| Over-current settling time                | TSET_TH_OC |       |      | 10    | μs   | Settling time after adjustment                      |

| Gain                                      | GCS        | 0.38  | 0.4  | 0.42  | V/A  | Trimmed and calibrated                              |

| Offset                                    | VCSO       | 1.215 | 1.25 | 1.285 | V    | Trimmed and calibrated                              |

*Table 16 – Electrical specifications : current sense amplifier*

[1] 8bit signed DAC, step size = 23.4mA, value for code 0x00 = 800mA

### 10.3.5. VSM supply sensor

| Parameter                         | Symbol | Min. | Typ. | Max. | Unit | Condition             |

|-----------------------------------|--------|------|------|------|------|-----------------------|

| Voltage range for ADC measurement |        |      |      | 28   | V    | Measurement of VSM/21 |

| VSM filter cut-off frequency      |        |      |      | 4    | kHz  |                       |

*Table 17 – Electrical specifications : VSM supply sensor*

### 10.3.6. Over-temperature detection

| Parameter      | Symbol | Min. | Typ. | Max. | Unit | Condition                |

|----------------|--------|------|------|------|------|--------------------------|

| OTD threshold  | TTH_OT | 175  | 185  | 195  | °C   | Temperature ramping up   |

| OTD threshold  | TTH_OT | 150  | 160  | 170  | °C   | Temperature ramping down |

| OTD hysteresis | THY_OT | 10   | 25   |      | °C   |                          |

*Table 18 – Electrical specifications : over-temperature detection*

### 10.3.7. ADC

| Parameter                                               | Symbol  | Min.  | Typ. | Max.  | Unit | Condition                                                |

|---------------------------------------------------------|---------|-------|------|-------|------|----------------------------------------------------------|

| Reference voltage                                       | VREFADC |       | VDDA |       | V    |                                                          |

| Reference voltage                                       | VREFADC | 2.45  | 2.5  | 2.55  | V    | Trimmed and calibrated                                   |

| Reference voltage                                       | VREFADC | 1.47  | 1.5  | 1.53  | V    | Trimmed and calibrated                                   |

| Reference voltage                                       | VREFADC | 0.735 | 0.75 | 0.765 | V    | Trimmed and calibrated                                   |

| Resolution                                              |         |       | 10   |       | bit  |                                                          |

| Conversion time                                         | TCONV   |       |      | 6     | μs   |                                                          |

| DNL                                                     |         | -1    |      | 1     | LSB  |                                                          |

| INL                                                     |         | -3    |      | 3     | LSB  |                                                          |

| ADC LV channel<br>(with 1/1.36 divider)<br>accuracy [1] |         | -45   |      | 45    | mV   | 0V – 3.3V input, calibrated acc.<br>calibration document |

| ADC HV channel<br>(with 1/21 divider)<br>accuracy       |         | -0.30 |      | 0.30  | V    | <5V input, calibrated acc.<br>calibration document       |

| ADC HV channel<br>(with 1/21 divider)<br>accuracy       |         | -0.60 |      | 0.60  | V    | <20V input, calibrated acc.<br>calibration document      |

| ADC VSMF channel<br>(with 1/21 divider)<br>accuracy     |         | -0.20 |      | 0.20  | V    | <5V input, calibrated acc.<br>calibration document       |

| ADC VSMF channel<br>(with 1/21 divider)<br>accuracy     |         | -0.30 |      | 0.30  | V    | <20V input, calibrated acc.<br>calibration document      |

| ADC temperature<br>channel accuracy                     |         | -10   |      | 10    | °C   | Calibrated acc. calibration<br>document                  |

| ADC channel select                                      |         | 0     |      | 25    |      | See datasheet                                            |

Table 19 – Electrical specifications : ADC

[1] VS >= 4.7V for IO0 ADC LV channel

### 10.3.8. IO

| Parameter                                            | Symbol | Min.        | Typ. | Max. | Unit | Condition                                                       |

|------------------------------------------------------|--------|-------------|------|------|------|-----------------------------------------------------------------|

| Input threshold level L → H                          |        |             |      | 2.4  | V    |                                                                 |

| Input threshold level H → L                          |        | 1           |      |      | V    | [1]                                                             |

| Input hysteresis                                     |        | 0.1         |      |      | V    |                                                                 |

| Output voltage L, IO1...7                            |        |             |      | 0.4  | V    | ILOAD = 2mA                                                     |

| Output voltage L, IO0                                |        |             |      | 0.5  | V    | ILOAD = 2mA                                                     |

| Output voltage H, IO1...7                            |        | VDDA - 0.4V |      |      | V    | ILOAD = 2mA                                                     |

| Output voltage H, IO0                                |        | VDDA - 0.5V |      |      | V    | ILOAD = 2mA, VS > 5.5V                                          |

| Input voltage range for high-voltage ADC measurement |        | 0           |      | 28   | V    | IO0<br>Measurement of IO0/21                                    |

| Input voltage range for low-voltage ADC measurement  |        | 0           |      | VDDA | V    | IO0...7<br>Measurement of IOx/1.36                              |

| I2C SDA hold time (vs SCL)                           |        | 0           | 35   | 70   | ns   | IO0 pin, SDAFILT_IO=00, setting for Fast-mode Plus              |

| I2C SDA hold time (vs SCL)                           |        | 180         | 260  | 340  | ns   | IO0 pin, SDAFILT_IO=01                                          |

| I2C SDA hold time (vs SCL)                           |        | 240         | 330  | 420  | ns   | IO0 pin, SDAFILT_IO=10                                          |

| I2C SDA hold time (vs SCL)                           |        | 360         | 500  | 640  | ns   | IO0 pin, SDAFILT_IO=11, setting for Standard-mode and Fast-mode |

Table 20 – Electrical specifications : IO

[1] If IO0 is used as a global pin, then a series resistor of min. 800Ω / max. 10kΩ needs to be applied.

## 10.3.9. LIN

### 10.3.9.1. LIN transceiver - static

| Parameter                                                 | Symbol       | Min.     | Typ.   | Max.     | Unit | Condition                                                                 |

|-----------------------------------------------------------|--------------|----------|--------|----------|------|---------------------------------------------------------------------------|

| Transmitter internal capacitance [1]                      | CLIN         |          | 30     | 40       | pF   | Response on 14V pulse via 1K                                              |

| Bus short circuit current                                 | IBUS_LIM     | 40       | 100    | 200      | mA   | VLIN = VS = 27V, VTxD = 0V                                                |

| Pull up resistance bus, untrimmed                         | RSLAVE       | 20       | 35     | 60       | kΩ   | VDISTERM = 0                                                              |

| Pull up current bus, sleep mode                           | ISLAVE_SLEEP | -50      | -20    | -5       | µA   | VLIN = 0V,<br>VSBY = VAUX, VEN = 0                                        |

| Dominant input leakage current including pull up resistor | IBUS_PAS_dom | -600     |        |          | µA   | VLIN = 0V, VS = 12V,<br>VTxD = VDDD, VDISTERM = 0<br>VEN = VDDD, VSBY = 0 |

| Recessive input leakage current                           | IBUS_PAS_rec |          | 0.25   | 1        | µA   | VEN = VDDD, VSBY = 0,<br>VTxD = VDDD, VLIN > VS                           |

| Bus reverse current loss of battery [2]                   | IBUS_NO_BAT  |          | 0.25   | 1        | µA   | VS = 0V,<br>0V < VLIN < 27V                                               |

| Bus current during loss of ground [2]                     | IBUS_NO_GND  | -100     |        | 1        | µA   | VS = VGND = 12V,<br>0 < VLIN < 27V                                        |

| Transmitter dominant output voltage [2]                   | VolBUS       | 0        |        | 0.2×VS   | V    | Rload = 500Ω                                                              |

| Transmitter recessive output voltage [2]                  | VohBUS       | 0.8×VS   |        | 1×VS     | V    | VEN = VDDD, VSBY = 0,<br>VTxD = VDDD<br>or sleep mode                     |

| Receiver dominant voltage                                 | VBUSdom      |          |        | 0.4×VS   | V    |                                                                           |

| Receiver recessive voltage                                | VBUSrec      | 0.6×VS   |        |          | V    |                                                                           |

| Center point of receiver threshold                        | VBUS_CNT     | 0.475×VS | 0.5×VS | 0.525×VS | V    | VBUS_cnt = (Vth_dom+Vth_rec)/2                                            |

| Receiver hysteresis                                       | VHYS         |          |        | 0.175×VS | V    | VHYS = (Vth_rec - Vth_dom)                                                |

Table 21 – Electrical specifications : LIN transceiver – static

[1] No production test, guaranteed by design and qualification

[2] In accordance to SAE J2602

## 10.3.9.2. LIN transceiver – dynamic

| Parameter                                      | Symbol  | Min.  | Typ.  | Max. | Unit  | Condition                                           |

|------------------------------------------------|---------|-------|-------|------|-------|-----------------------------------------------------|

| Propagation delay receiver [1]                 | trx_pdf |       |       | 6    | μs    | CRxD = 25pF, falling edge                           |

| Propagation delay receiver [1]                 | trx_pdr |       |       | 6    | μs    | CRxD = 25pF, rising edge                            |

| Propagation delay receiver symmetry            | trx_sym | -2    |       | 2    | μs    | Calculate $\text{trx\_pdf} - \text{trx\_pdr}$       |

| Receiver debounce time [2]                     | trx_deb | 0.5   |       | 4    | μs    | LIN rising & falling edge                           |

| LIN duty cycle 1 [2] [3] [5]                   | D1      | 0.396 |       |      |       | 20kbps operation, normal mode<br>Vs = 7 to 18V      |

| LIN duty cycle 2 [2] [3] [5]                   | D2      |       | 0.581 |      |       | 20kbps operation, normal mode<br>Vs = 7 to 18V      |

| LIN duty cycle 3 [2] [3] [5]                   | D3      | 0.417 |       |      |       | 10.4kbs operation, low speed mode<br>Vs = 7 to 18V  |

| LIN duty cycle 4 [2] [3] [5]                   | D4      |       | 0.590 |      |       | 10.4kbs operation, low speed mode<br>Vs = 7 to 18V  |

| tREC(MAX) – tDOM(MIN) [4] [5]                  | Δt3     |       |       | 15.9 | μs    | 10.4kbs operation, low speed mode                   |

| tDOM(MAX) – tREC(MIN) [4] [5]                  | Δt4     |       | 17.28 | μs   |       | 10.4kbs operation, low speed mode                   |

| Slew rate on pin LIN normal mode, untrimmed    |         |       | 1.7   |      | V/ μs | dV/dt between duty cycle measurement points, Vs=12V |

| Slew rate on pin LIN low speed mode, untrimmed |         | 0.85  |       |      | V/ μs | dV/dt between duty cycle measurement points, Vs=12V |

| TxD dominant timeout [6]                       | txd_to  |       | 15    |      | ms    | Normal mode, vTxD = 0V                              |

Table 22 – Electrical specifications : LIN transceiver – dynamic

[1] This parameter is tested by applying a square wave signal to the LIN. The minimum slew rate for the LIN rising and falling edges is 50V/us

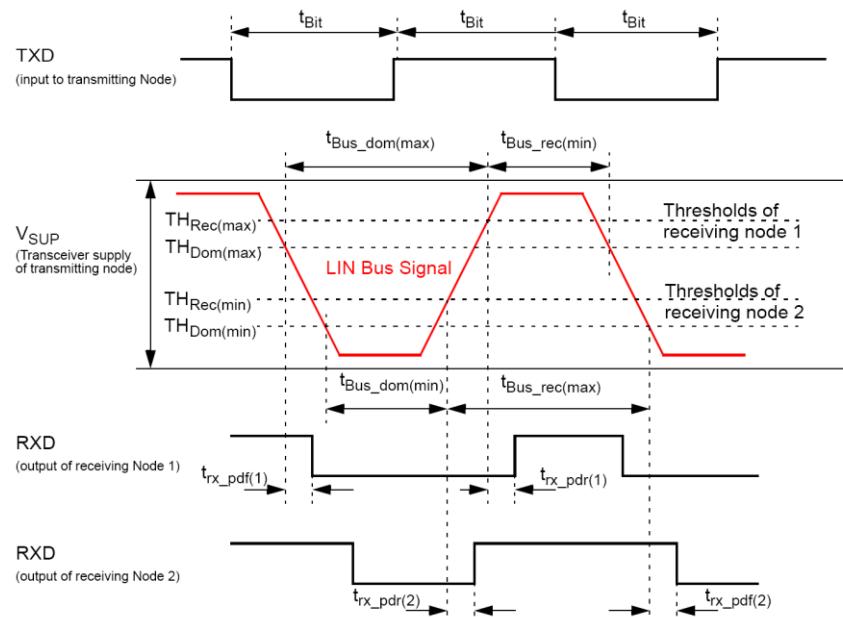

[2] See Figure 6

[3] Standard loads for duty cycle measurements are 1KΩ/1nF, 660Ω/6.8nF, 500Ω/10nF, internal master termination disabled

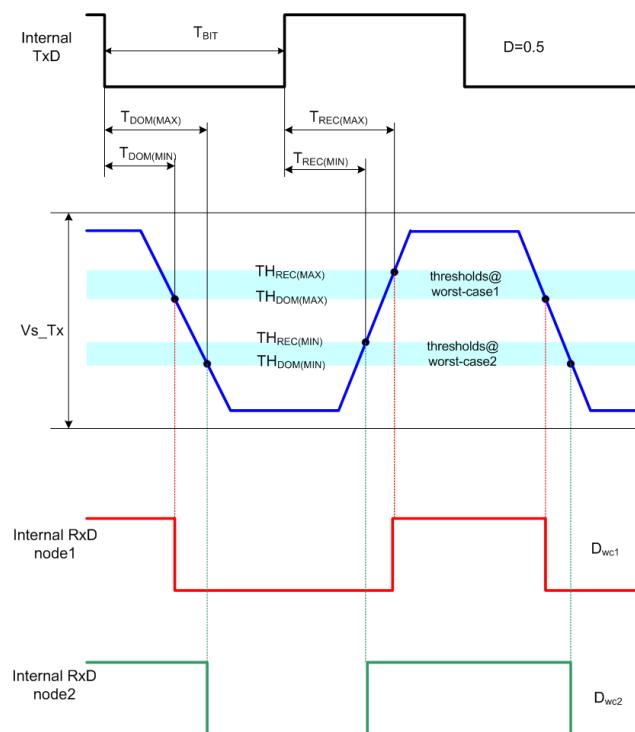

[4] In accordance to SAE J2602, see Figure 7

[5] For supply voltage ranges  $V_s=5.5\ldots 7V$  and  $V_s=18\ldots 27V$  parametric deviations are possible (target specification is w/o deviations &  $ppK>2.0$ )

[6] Parameter in relation to internal signal TxD

Figure 6 – LIN timing diagram (reference LIN2.1 specification)

Figure 7 – LIN timing diagram, relation between propagation delay and duty cycle (reference SAE J2602 specification)

## 11. Disclaimer

The content of this document is believed to be correct and accurate. However, the content of this document is furnished "as is" for informational use only and no representation, nor warranty is provided by Melexis about its accuracy, nor about the results of its implementation. Melexis assumes no responsibility or liability for any errors or inaccuracies that may appear in this document. Customer will follow the practices contained in this document under its sole responsibility. This documentation is in fact provided without warranty, term, or condition of any kind, either implied or expressed, including but not limited to warranties of merchantability, satisfactory quality, non-infringement, and fitness for purpose. Melexis, its employees and agents and its affiliates' and their employees and agents will not be responsible for any loss, however arising, from the use of, or reliance on this document. Notwithstanding the foregoing, contractual obligations expressly undertaken in writing by Melexis prevail over this disclaimer.

This document is subject to change without notice, and should not be construed as a commitment by Melexis. Therefore, before placing orders or prior to designing the product into a system, users or any third party should obtain the latest version of the relevant information.

Users or any third party must determine the suitability of the product described in this document for its application, including the level of reliability required and determine whether it is fit for a particular purpose.

This document as well as the product here described may be subject to export control regulations. Be aware that export might require a prior authorization from competent authorities. The product is not designed, authorized or warranted to be suitable in applications requiring extended temperature range and/or unusual environmental requirements. High reliability applications, such as medical life-support or life-sustaining equipment or avionics application are specifically excluded by Melexis. The product may not be used for the following applications subject to export control regulations: the development, production, processing, operation, maintenance, storage, recognition or proliferation of:

1. chemical, biological or nuclear weapons, or for the development, production, maintenance or storage of missiles for such weapons;

2. civil firearms, including spare parts or ammunition for such arms;

3. defense related products, or other material for military use or for law enforcement;

4. any applications that, alone or in combination with other goods, substances or organisms could cause serious harm to persons or goods and that can be used as a means of violence in an armed conflict or any similar violent situation.

No license nor any other right or interest is granted to any of Melexis' or third party's intellectual property rights.

If this document is marked "restricted" or with similar words, or if in any case the content of this document is to be reasonably understood as being confidential, the recipient of this document shall not communicate, nor disclose to any third party, any part of the document without Melexis' express written consent. The recipient shall take all necessary measures to apply and preserve the confidential character of the document. In particular, the recipient shall (i) hold document in confidence with at least the same degree of care by which it maintains the confidentiality of its own proprietary and confidential information, but no less than reasonable care; (ii) restrict the disclosure of the document solely to its employees for the purpose for which this document was received, on a strictly need to know basis and providing that such persons to whom the document is disclosed are bound by confidentiality terms substantially similar to those in this disclaimer; (iii) use the document only in connection with the purpose for which this document was received, and reproduce document only to the extent necessary for such purposes; (iv) not use the document for commercial purposes or to the detriment of Melexis or its customers. The confidentiality obligations set forth in this disclaimer will have indefinite duration and in any case they will be effective for no less than 10 years from the receipt of this document.

This disclaimer will be governed by and construed in accordance with Belgian law and any disputes relating to this disclaimer will be subject to the exclusive jurisdiction of the courts of Brussels, Belgium.

The invalidity or ineffectiveness of any of the provisions of this disclaimer does not affect the validity or effectiveness of the other provisions.

The previous versions of this document are repealed.

Melexis © - No part of this document may be reproduced without the prior written consent of Melexis. (2023)

IATF 16949 and ISO 14001 Certified