## Single Input Single Output Load Switch with Surge Protection

### Features

- 2.75V to 21.5V Operating Voltage Range

- 28V Abs. Max. Rating at VBUS and VOUT

- 9mΩ typ. On-Resistance from VBUS to VOUT

- 6A Continuous Current Rating

- ▶ 12A Pulse Current Rating (5ms)

- Over-Voltage Protection (OVP) at VBUS

- ▶ 12.4V (OVLO\_SEL = LOW)

- ▶ 21.9V (OVLO\_SEL = HIGH)

- Transient Voltage Suppression (TVS) at VBUS

- ▶ ±200V Surge Protection (IEC61000-4-5)

- ▶ ±8kV ESD Contact Discharge (IEC61000-4-2)

- ▶ ±15kV ESD Air Discharge (IEC61000-4-2)

- Over-Temperature Protection (OTP)

- OV\_FLAGB Open-Drain Output Flag

- VBUS detection LDO

- Active VBUS Discharge Control Input

- Active-Low Enable Logic Input

- -40°C to 85°C Operating Temperature Range

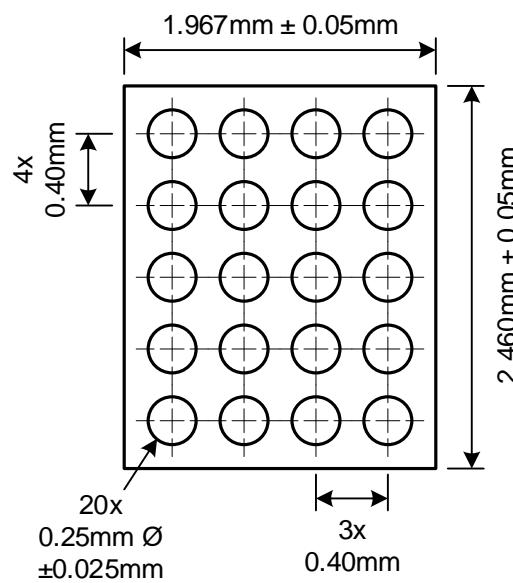

- 20-bump WLCSP 2.460 x 1.967mm (0.4mm pitch)

### Brief Description

KTS1652 is a low resistance, bi-directional high current load switch with over-voltage protection, over-temperature protection and integrated TVS. The integrated TVS at VBUS is rated up to IEC61000-4-5 ±200V Surge voltage and IEC61000-4-2 Level 4 Electrostatic Discharge, which protects the downstream components from abnormal input conditions.

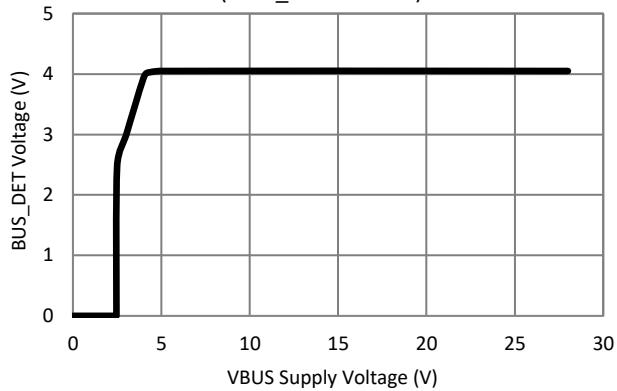

When VBUS is greater than  $V_{UVLO\_BUS}$ , the integrated LDO provides an “always ON” power source at BUS\_DET. BUS\_DET voltage is regulated to typically 4.0V, regardless of the status of ENB, so to power downstream components permitting operation without an installed battery.

KTS1652 is packaged in advanced, fully “green” compliant, 2.460 x 1.967mm, 20-bump Wafer-Level Chip-Scale Package (WLCSP).

### Applications

- Smartphones, Ultra-Books, Tablets

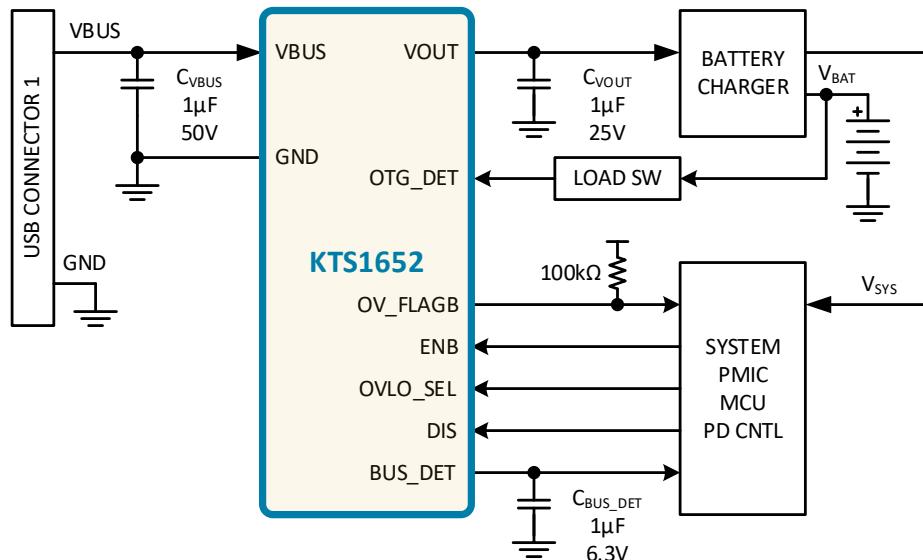

### Typical Application

### Ordering Information

| Part Number    | Marking <sup>1</sup> | Operating Temperature | Package    |

|----------------|----------------------|-----------------------|------------|

| KTS1652EIAC-TA | TFYWZNAAABB          | -40°C to +85°C        | WLCSP54-20 |

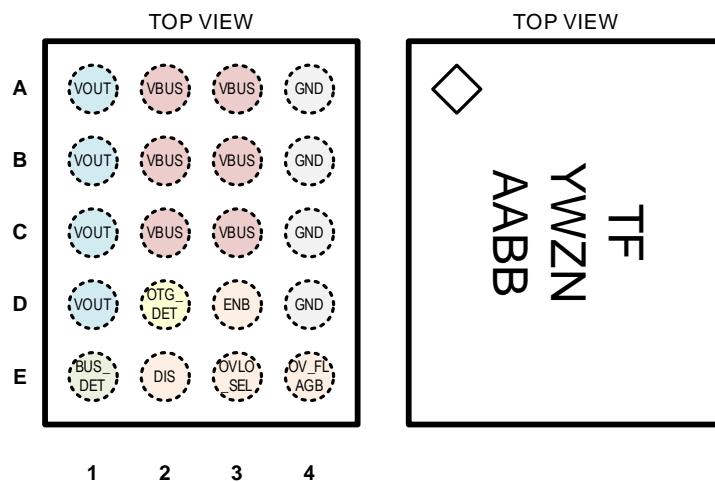

### Pinout Diagram

**WLCSP54-20**

20-bump 2.460mm x 1.967mm x 0.555mm

WLCSP Package, 0.4mm pitch

Top Mark: TF = Device ID, YW = Date Code, ZN = Assembly Code, AABB = Serial Number

1. TF = Device ID, YW = Date Code, ZN = Assembly Code and AABB = Serial Number.

### Pin Descriptions

| Pin #                     | Name     | Function                                                                                                                                                                                       |

|---------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A2, A3, B2, B3,<br>C2, C3 | VBUS     | Power Switch Input/Output and Device Power Supply.                                                                                                                                             |

| A1, B1, C1, D1            | VOUT     | Power Switch Input/Output.                                                                                                                                                                     |

| D2                        | OTG_DET  | Power Supply Input for charge pump circuit during startup in OTG mode.                                                                                                                         |

| E1                        | BUS_DET  | Always on LDO output powered by VBUS.                                                                                                                                                          |

| D3                        | ENB      | Active Low Enable signal for VBUS-VOUT path. An internal 1MΩ pull-down resistor is integrated.                                                                                                 |

| E2                        | DIS      | Active High Enable signal for active discharge path at VBUS. An internal 1-MΩ pull-down resistor is integrated.                                                                                |

| E3                        | OVLO_SEL | Selection of OVLO threshold. An internal 1-MΩ pull-down resistor is integrated.<br>OVLO_SEL = LOW:<br>→ OVLO threshold = 12.4 V (typ.)<br>OVLO_SEL = HIGH:<br>→ OVLO threshold = 21.9 V (typ.) |

| E4                        | OV_FLAGB | Open-drain type output indicating an over-voltage state. An external pull-up resistor is required.                                                                                             |

| A1, B4, C4, D4            | GND      | Ground. Connect this pin to system ground.                                                                                                                                                     |

## Absolute Maximum Ratings<sup>2</sup>

| Symbol          | Description                                                                            | Value                  | Units |

|-----------------|----------------------------------------------------------------------------------------|------------------------|-------|

| $V_{VBUS}$      | $V_{VBUS}$ to GND (continuous)<br>$V_{VBUS}$ to GND (during IEC61000-4-5 surge event)  | -0.3 to 28<br>-5 to 36 | V     |

| $V_{VOUT}$      | $V_{VOUT}$ to GND                                                                      | -0.3 to 28             | V     |

| $V_{BUS\_DET}$  | $BUS\_DET$ to GND                                                                      | -0.3 to 6              | V     |

| $V_I$ and $V_O$ | $OV\_FLAGB$ , $DIS$ , $ENB$ , $OVLO\_SEL$ , $OTG\_DET$ to GND                          | -0.3 to 6              | V     |

| $I_{VBUS-VOUT}$ | Maximum Switch Current (continuous)<br>Peak Switch Current (duration is $P_d$ limited) | 6<br>12                | A     |

| $I_{BUS\_DET}$  | $BUS\_DET$ Maximum Switch Current (continuous)                                         | > 10                   | mA    |

| $T_J$           | Operating Temperature Range                                                            | -40 to 150             | °C    |

| $T_S$           | Storage Temperature Range                                                              | -65 to 150             | °C    |

| $T_{LEAD}$      | Maximum Soldering Temperature (at leads, 10 sec)                                       | 260                    | °C    |

## ESD and Surge Ratings<sup>3</sup>

| Symbol         | Description                                   | Value | Units |

|----------------|-----------------------------------------------|-------|-------|

| $V_{ESD\_HBM}$ | JEDEC JS-001-2017 Human Body Model (all pins) | ±2    | kV    |

| $V_{ESD\_CD}$  | IEC61000-4-2 Contact Discharge ( $V_{VBUS}$ ) | ±8    | kV    |

| $V_{ESD\_AGD}$ | IEC61000-4-2 Air Gap Discharge ( $V_{VBUS}$ ) | ±15   | kV    |

| $V_{SURGE}$    | IEC61000-4-5 Surge ( $V_{VBUS}$ to GND)       | ±200  | V     |

## Thermal Capabilities<sup>4</sup>

| Symbol                | Description                                                     | Value | Units |

|-----------------------|-----------------------------------------------------------------|-------|-------|

| $\Theta_{JA}$         | Thermal Resistance – Junction to Ambient                        | 74    | °C/W  |

| $P_D$                 | Maximum Power Dissipation at 25°C ( $T_J = 125^\circ\text{C}$ ) | 1.35  | W     |

| $\Delta P_D/\Delta T$ | Derating Factor Above $T_A = 25^\circ\text{C}$                  | -13.5 | mW/°C |

(continued next page)

2. Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

3. ESD and Surge Ratings conform to JEDEC and IEC industry standards. Some pins may have higher performance. Surge ratings apply with chip enabled, disabled, or unpowered, unless otherwise noted.

4. Junction to Ambient thermal resistance is highly dependent on PCB layout. Values are based on thermal properties of the device when soldered to an EV board.

**Recommended Operating Conditions**

| Symbol         | Description                         | Value         | Units        |

|----------------|-------------------------------------|---------------|--------------|

| $V_{BUS}$      | VBUS Supply Voltage                 | 2.75 to 21.5  | V            |

| $V_{OUT}$      | VOUT Output Voltage                 | 2.75 to 21.5  | V            |

| $V_{BUS\_DET}$ | BUS_DET Output Voltage              | 3 to 5.5      | V            |

| $V_I, V_O$     | Logic Input and Output Voltage      | 0 to 5.5      | V            |

| $C_{BUS}$      | Input Capacitance                   | 1 to 10<br>50 | $\mu F$<br>V |

| $C_{OUT}$      | Output Capacitance                  | 1 to 10<br>25 | $\mu F$<br>V |

| $C_{BUS\_DET}$ | Output Capacitance                  | 1<br>6.3      | $\mu F$<br>V |

| $T_A$          | Ambient Operating Temperature Range | -40 to 85     | °C           |

| $T_J$          | Die Operating Temperature Range     | -40 to 125    | °C           |

(continued next page)

## Electrical Characteristics<sup>5</sup>

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operating range of  $T_A = -40^\circ\text{C}$  to  $+85^\circ\text{C}$ ,  $V_{\text{BUS}} = 2.75\text{V}$  to  $21.5\text{V}$ . Typical values are specified at  $T_A = +25^\circ\text{C}$  with  $V_{\text{BUS}} = 5\text{V}$ ,  $I_{\text{BUS}} \leq 2\text{A}$ ,  $\text{ENB} = \text{DIS} = \text{LOW}$ ,  $\text{OVLO\_SEL} = \text{Low}$  and  $C_{\text{BUS}} = 1\mu\text{F}$ .

### VBUS Supply Specifications

| Symbol                 | Description                   | Conditions                                                       | Min                | Typ      | Max        | Units         |

|------------------------|-------------------------------|------------------------------------------------------------------|--------------------|----------|------------|---------------|

| $V_{\text{BUS}}$       | Input Voltage Operating Range |                                                                  | 2.75               |          | 21.5       | V             |

| $V_{\text{UVLO\_BUS}}$ | Under-Voltage Lockout         | $V_{\text{BUS}}$ rising threshold<br>Hysteresis                  | 2.25<br>150        | 2.5      | 2.75       | V<br>mV       |

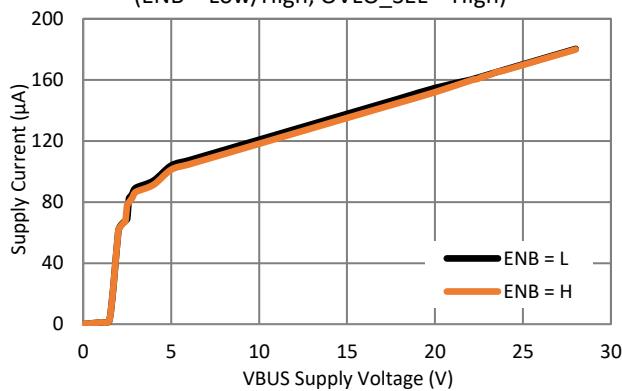

| $I_{\text{Q\_BUS}}$    | No-Load Supply Current        | $V_{\text{BUS}} = 5\text{V}$ ,<br>$V_{\text{OUT}} = \text{open}$ | ENB = L<br>ENB = H | 90<br>90 | 140<br>140 | $\mu\text{A}$ |

### VBUS to VOUT Switch Specifications

| Symbol                    | Description                                | Conditions                                                     | Min                                                                                            | Typ         | Max            | Units            |

|---------------------------|--------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------|----------------|------------------|

| $R_{\text{ON\_VOUT}}$     | Switch On-Resistance                       | $I_{\text{VOUT}} = 200\text{mA}$ ,<br>$T_A = 25^\circ\text{C}$ | $V_{\text{BUS}} = 5\text{V}$<br>$V_{\text{BUS}} = 12\text{V}$<br>$V_{\text{BUS}} = 21\text{V}$ | 9<br>9<br>9 | 12<br>12<br>12 | $\text{m}\Omega$ |

| $t_{\text{ON\_VOUT}}$     | Switch Turn-On Time <sup>6</sup>           | $RL = 100\ \Omega$ , $C_{\text{VOUT}} = 1\ \mu\text{F}$        |                                                                                                | 1           | 3              | ms               |

| $t_{\text{DOFF\_VOUT}}^7$ | Switch Turn-Off Response Time <sup>8</sup> | $RL = 100\ \Omega$ ,<br>$C_{\text{VOUT}} = 1\ \mu\text{F}$     | $\text{OVLO\_SEL} = \text{L}$<br>$\text{OVLO\_SEL} = \text{H}$                                 |             | 50<br>50       | ns               |

| $t_{\text{DEB\_VOUT}}$    | VBUS Debounce Time <sup>9</sup>            |                                                                |                                                                                                | 15          | 20             | ms               |

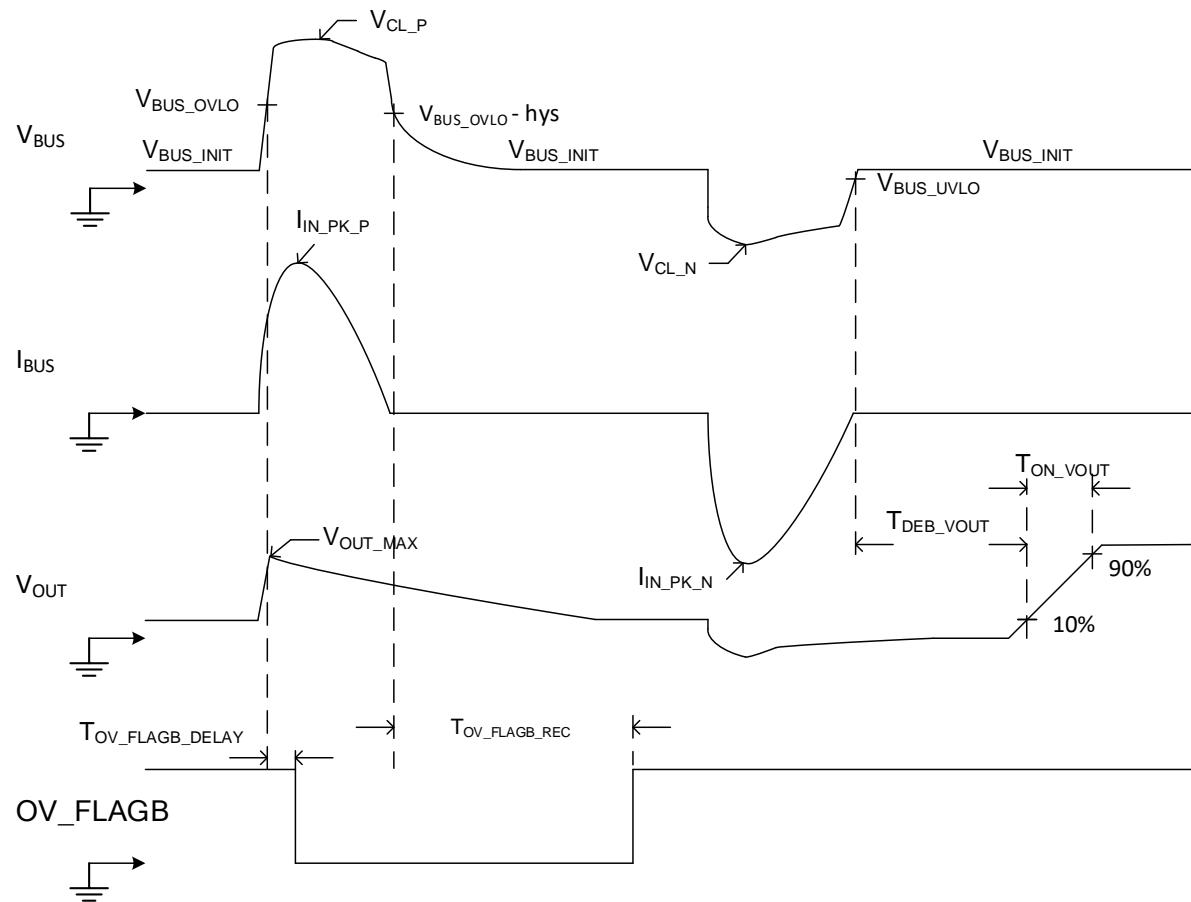

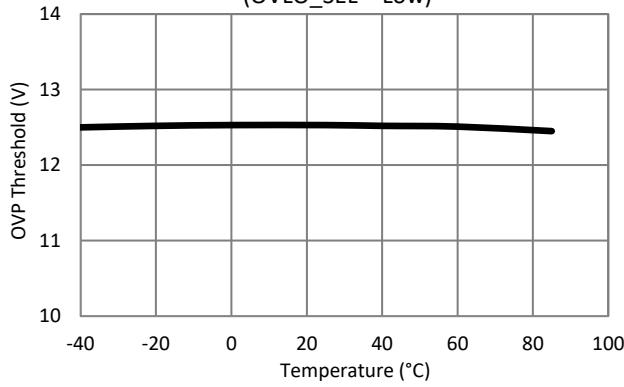

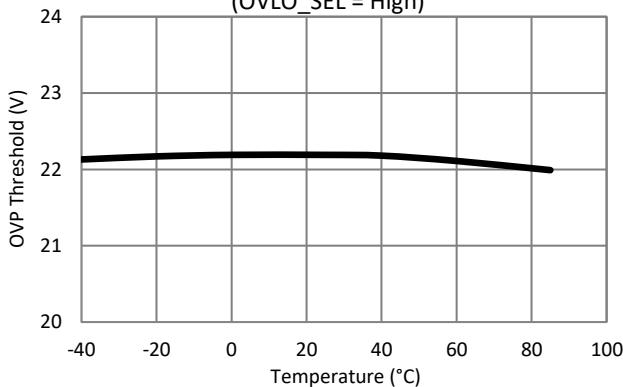

### Over-Voltage Protection (OVP) Specifications

| Symbol                  | Description                                      | Conditions                                                                                                                                               | Min                                                 | Typ        | Max          | Units         |   |

|-------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------|--------------|---------------|---|

| $V_{\text{BUS\_OVLO}}$  | Internal Over-Voltage Protection                 | $\text{OVLO\_SEL} = \text{L}$                                                                                                                            | $V_{\text{BUS}}$ rising<br>$V_{\text{BUS}}$ falling | 12.1       | 12.4         | 12.7          | V |

|                         |                                                  | $\text{OVLO\_SEL} = \text{H}$                                                                                                                            | $V_{\text{BUS}}$ rising<br>$V_{\text{BUS}}$ falling | 21.4       | 21.9<br>21.5 | 22.4          |   |

| $I_{\text{IN\_OVLO}}$   | OVLO Supply Current <sup>10</sup>                | $\text{OVLO\_SEL} = \text{L}$ , $V_{\text{BUS}} = 15\text{V}$<br>$\text{OVLO\_SEL} = \text{H}$ , $V_{\text{BUS}} = 23\text{V}$                           |                                                     | 120<br>160 | 160<br>180   | $\mu\text{A}$ |   |

| $V_{\text{OUT\_MAX}}^7$ | Maximum VOUT during positive surge <sup>11</sup> | $V_{\text{BUS}} = 11\text{V}$ , +200V Surge, $\text{OVLO\_SEL} = \text{L}$<br>$V_{\text{BUS}} = 21\text{V}$ , +200V Surge, $\text{OVLO\_SEL} = \text{H}$ |                                                     |            | 15<br>23     | V             |   |

5. Device is guaranteed to meet performance specifications over the  $-40^\circ\text{C}$  to  $+85^\circ\text{C}$  operating temperature range by design, characterization, and correlation with statistical process controls.

6.  $t_{\text{ON\_VOUT}}$  is time from the specified test condition and from  $V_{\text{VOUT}} = 10\% * V_{\text{VOUT}}$  until  $V_{\text{VOUT}} = 90\% * V_{\text{VOUT}}$ .

7. Guaranteed by design, characterization, and statistical process control methods; not production tested.

8.  $t_{\text{DOFF\_VOUT}}$  is time from  $V_{\text{BUS}} = V_{\text{BUS\_OVLO}}$  to VOUT stop rising. Measured when VBUS rises from 0V to 15V ( $\text{OVLO\_SEL} = \text{L}$ ) or from 0V to 25V ( $\text{OVLO\_SEL} = \text{H}$ ) at  $14\text{V}/\mu\text{s}$  Slew Rate.

9.  $t_{\text{DEB\_VOUT}}$  is time from  $V_{\text{BUS\_UVLO}} \leq V_{\text{BUS}} < V_{\text{BUS\_OVLO}}$  to  $V_{\text{VOUT}} = 0.1 \times V_{\text{VOUT}}$ .

10.  $I_{\text{IN\_OVLO}}$  is VBUS input current measured using the specified test condition, together with  $V_{\text{VOUT}} = \text{open}$  and  $\text{ENB} = \text{L}$ .

11.  $V_{\text{OUT\_MAX}}$  is measured using the specified test condition, together with  $\text{ENB} = \text{L}$ ,  $V_{\text{VOUT}} = \text{Open}$  and without any  $C_{\text{VOUT}}$ .

## Electrical Characteristics<sup>5</sup>

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operating range of  $T_A = -40^\circ\text{C}$  to  $+85^\circ\text{C}$ ,  $V_{\text{BUS}} = 2.75\text{V}$  to  $21.5\text{V}$ . Typical values are specified at  $T_A = +25^\circ\text{C}$  with  $V_{\text{BUS}} = 5\text{V}$ ,  $I_{\text{BUS}} \leq 2\text{A}$ ,  $\text{ENB} = \text{DIS} = \text{LOW}$ ,  $\text{OVLO\_SEL} = \text{Low}$  and  $C_{\text{BUS}} = 1\mu\text{F}$ .

### Active VBUS Discharge Specifications

| Symbol                      | Description                                 | Conditions                                                                                                                            | Min | Typ | Max | Units         |

|-----------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| $R_{\text{VBUS\_DIS}}$      | VBUS Discharge Resistance <sup>12</sup>     | $V_{\text{BUS}} = 5\text{V}$ , $\text{DIS} = 1.8\text{V}$                                                                             |     | 550 |     | $\Omega$      |

| $t_{\text{VBUS\_DIS\_ON}}$  | VBUS Discharge ON Delay Time <sup>13</sup>  | $V_{\text{OUT}} = 5\text{V}$ , $\text{DIS}$ pin from Low to High                                                                      |     | 200 |     | ns            |

| $t_{\text{VBUS\_DIS}}$      | VBUS Discharge Time <sup>14</sup>           | $V_{\text{OUT}} = 5\text{V}$ , $C_{\text{VBUS}} = C_{\text{OUT}} = 1\mu\text{F}$ , $\text{DIS}$ pin from $0\text{V}$ to $1.8\text{V}$ |     | 1.1 | 5   | ms            |

| $t_{\text{VBUS\_DIS\_OFF}}$ | VBUS Discharge OFF Delay Time <sup>15</sup> | $V_{\text{OUT}} = 5\text{V}$ , $\text{DIS}$ pin from High to Low                                                                      |     | 1   | 3   | $\mu\text{s}$ |

### OTG Mode (VOUT to VBUS) Specifications

| Symbol                      | Description                                | Conditions                                                                                                                                                                                                                                                               | Min          | Typ                       | Max                | Units            |

|-----------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------|--------------------|------------------|

| $V_{\text{OUT}}$            | Output Voltage Operating Range             |                                                                                                                                                                                                                                                                          | 2.75         |                           | 21.5               | V                |

| $V_{\text{OTG\_DET\_UVLO}}$ | OTG_DET Under-Voltage Lockout              | $V_{\text{OTG\_DET}}$ rising threshold<br>$V_{\text{OTG\_DET}}$ falling threshold                                                                                                                                                                                        | 2.80<br>2.80 | 2.95<br>2.80              | 3.10               | V                |

| $I_{\text{IN\_OTG\_DET}}$   | OTG_DET Input Supply Current <sup>16</sup> | $\text{OTG\_DET} = 2.5\text{ V}$ , $V_{\text{OUT}} = 0\text{ V}$<br>$\text{OTG\_DET} = 5\text{ V}$ , $V_{\text{OUT}} = 0\text{ V}$<br>$\text{OTG\_DET} = 4.5\text{ V}$ , $V_{\text{OUT}} = 5\text{ V}$<br>$\text{OTG\_DET} = 0\text{ V}$ , $V_{\text{OUT}} = 5\text{ V}$ |              | 0.2<br>50<br>0.4<br>< 0.1 | 1<br>120<br>1<br>1 | $\mu\text{A}$    |

| $R_{\text{ON\_OTG}}$        | Switch On-Resistance in OTG mode           | $V_{\text{OUT}} = 5\text{ V}$ , $I_{\text{BUS}} = -200\text{ mA}$ , $T_A = 25^\circ\text{C}$                                                                                                                                                                             |              | 9                         | 12                 | $\text{m}\Omega$ |

| $t_{\text{DON\_OTG}}$       | OTG_DET Startup Delay Time <sup>17</sup>   | $T_A = -40^\circ\text{C}$ to $85^\circ\text{C}$                                                                                                                                                                                                                          |              | 0.6                       | 1                  | ms               |

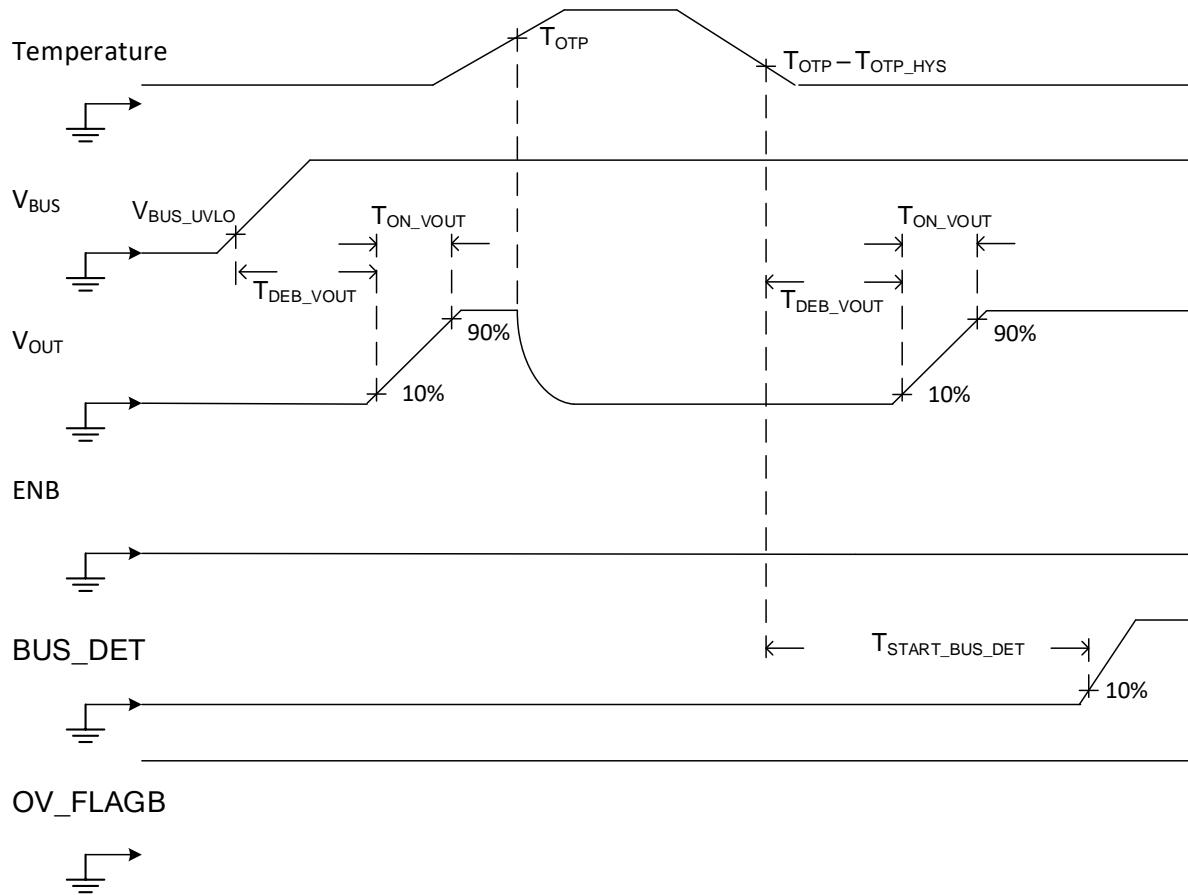

### BUS\_DET Specifications

| Symbol                       | Description                                      | Conditions                                                                                                                                | Min | Typ | Max | Units |

|------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| $V_{\text{BUS\_DET}}$        | BUS_DET Regulation Output Voltage                | $V_{\text{BUS}} = 5\text{V} / 21\text{V}$ ,<br>$I_{\text{BUS\_DET}} = 0\text{mA} / 10\text{mA}$ ,<br>$C_{\text{BUS\_DET}} = 1\mu\text{F}$ | 3.8 | 4.0 | 4.2 | V     |

| $t_{\text{START\_BUS\_DET}}$ | Soft-Start Current Limit Done Time <sup>18</sup> |                                                                                                                                           |     | 37  |     | ms    |

12.  $R_{\text{VBUS\_DIS}}$  can be higher than  $550\Omega$  when  $\text{DIS} < 1.8\text{V}$  or lower than  $550\Omega$  when  $\text{DIS} > 1.8\text{V}$ .

13.  $t_{\text{VBUS\_DIS\_ON}}$  is time from  $\text{DIS} = \text{L} \rightarrow \text{H}$  until Discharge path is ON ( $I_{\text{OUT}} = I_{\text{BUS}} + \text{Discharge current}$ ).

14.  $t_{\text{VBUS\_DIS}}$  is time from when VBUS first begins to fall until  $V_{\text{BUS}} = 10\% * V_{\text{OUT}}$ , once  $\text{DIS} = \text{ENB} = \text{LOW} \rightarrow \text{HIGH}$  and  $V_{\text{OUT}}$  source is removed at the same time.

15.  $t_{\text{VBUS\_DIS\_OFF}}$  is time from  $\text{DIS} = \text{H} \rightarrow \text{L}$  until Discharge path is OFF ( $I_{\text{OUT}} = I_{\text{BUS}}$ ).

16.  $I_{\text{IN\_OTG\_DET}}$  is OTG\_DET input current measured using specified test condition, together with  $\text{ENB} = \text{L}$ ,  $V_{\text{BUS}} = \text{Open}$ ,  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$ .

17.  $t_{\text{DON\_OTG}}$  is time from  $\text{OTG\_DET} \geq V_{\text{OTG\_DET\_UVLO}}$  to  $V_{\text{BUS}} = V_{\text{OUT}}$  (Charge Pump Output Enable).

18.  $t_{\text{START\_BUS\_DET}}$  is time from  $V_{\text{BUS}} \geq V_{\text{BUS\_UVLO}}$  to  $\text{BUS\_DET} = 10\%$  of target value.

## Electrical Characteristics<sup>5</sup>

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operating range of  $T_A = -40^\circ\text{C}$  to  $+85^\circ\text{C}$ ,  $V_{\text{BUS}} = 2.75\text{V}$  to  $21.5\text{V}$ . Typical values are specified at  $T_A = +25^\circ\text{C}$  with  $V_{\text{BUS}} = 5\text{V}$ ,  $I_{\text{BUS}} \leq 2\text{A}$ ,  $\text{ENB} = \text{DIS} = \text{LOW}$ ,  $\text{OVLO\_SEL} = \text{Low}$  and  $C_{\text{BUS}} = 1\mu\text{F}$ .

### Transient Voltage Suppression (TVS) Specifications

| Symbol                      | Description                      | Conditions                                                          | Min  | Typ | Max | Units |

|-----------------------------|----------------------------------|---------------------------------------------------------------------|------|-----|-----|-------|

| $V_{\text{RW\_P}}$          | Positive Reserve Working Voltage |                                                                     |      |     | 28  | V     |

| $V_{\text{BR\_P}}$          | Positive Breakdown Voltage       | $I_{\text{V}_{\text{BUS}}} = 1\text{mA}$ , $T_A = 25^\circ\text{C}$ | 30   | 32  | 34  | V     |

| $V_{\text{CL\_P}}^{19}$     | Positive Clamping Voltage        | +200V Surge                                                         |      |     | 40  | V     |

| $I_{\text{IN\_PK\_P}}^{19}$ | Positive Peak Surge Current      | +200V Surge                                                         |      |     | 100 | A     |

| $V_{\text{F\_TVS}}$         | Forward Voltage                  | $I_{\text{V}_{\text{BUS}}} = -10\text{mA}$                          | 0.2  | 0.6 | 0.8 | V     |

| $V_{\text{CL\_N}}^{19}$     | Negative Clamping Voltage        | -200V Surge                                                         | -6   |     |     | V     |

| $I_{\text{IN\_PK\_N}}^{19}$ | Negative Peak Surge Current      | -200V Surge                                                         | -100 |     |     | A     |

### Over-Temperature Protection (OTP) Specifications

| Symbol                | Description                             | Conditions                           | Min | Typ       | Max | Units    |

|-----------------------|-----------------------------------------|--------------------------------------|-----|-----------|-----|----------|

| $T_{\text{OTP}}^{19}$ | IC Junction Over-Temperature Protection | $T_J$ rising threshold<br>Hysteresis |     | 145<br>20 |     | °C<br>°C |

### Logic Pin Specifications (OV\_FLAGB, ENB, DIS, OVLO\_SEL)

| Symbol                        | Description                                   | Conditions                                                                      | Min       | Typ       | Max  | Units    |

|-------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------|-----------|-----------|------|----------|

| <b>OV_FLAGB</b>               |                                               |                                                                                 |           |           |      |          |

| $V_{\text{OV\_FLAGB\_OL}}$    | Output Logic Low                              | $V_{\text{IO}} = 1.2\text{V}/1.8\text{V}$ , $R_{\text{pu}} = 100\text{k}\Omega$ |           |           | 0.36 | V        |

| $t_{\text{OV\_FLAGB\_DELAY}}$ | OV_FLAGB Assertion Delay Time <sup>20</sup>   | $\text{ENB} = \text{H/L}$                                                       |           |           | 3    | μs       |

| $t_{\text{OV\_FLAGB\_REC}}$   | OV_FLAGB Recovery Debounce Time <sup>21</sup> | $\text{ENB} = \text{L}$<br>$\text{ENB} = \text{H}$                              | 16<br>100 | 20<br>140 |      | ms<br>μs |

| <b>ENB, DIS, OVLO_SEL</b>     |                                               |                                                                                 |           |           |      |          |

| $V_{\text{IH1}}$              | Input Logic High                              | $V_{\text{IO}} = 1.2\text{V}/1.8\text{V}$                                       | 0.84      |           |      | V        |

| $V_{\text{IL1}}$              | Input Logic Low                               | $V_{\text{IO}} = 1.2\text{V}/1.8\text{V}$                                       |           |           | 0.54 | V        |

| $R_{\text{I\_PD}}$            | Input Logic Pull-Down                         |                                                                                 |           | 1         |      | MΩ       |

<sup>19</sup> Guaranteed by design, characterization, and statistical process control methods; not production tested.

<sup>20</sup>.  $t_{\text{OV\_FLAGB\_DELAY}}$  is time from  $\text{V}_{\text{BUS}} \geq V_{\text{BUS\_OVLO}}$  to  $\text{OV\_FLAGB} = \text{L}$ . When  $\text{ENB} = \text{H}$ , Initial  $\text{V}_{\text{BUS}}$  voltage is expected to settle at  $\geq V_{\text{BUS\_UVLO}}$  and  $< V_{\text{BUS\_OVLO}}$  for a long time before the over-voltage event.

<sup>21</sup>.  $t_{\text{OV\_FLAGB\_REC}}$  is time from  $\text{V}_{\text{BUS}} \leq V_{\text{BUS\_OLVO}}$  to  $\text{OV\_FLAGB} = \text{H}$ . When  $\text{ENB} = \text{L}$ , OV\_FLAGB Recovery Debounce Time should always be longer than  $\text{V}_{\text{BUS}}$  debounce time + Switch Turn-on delay.

## Timing Diagrams

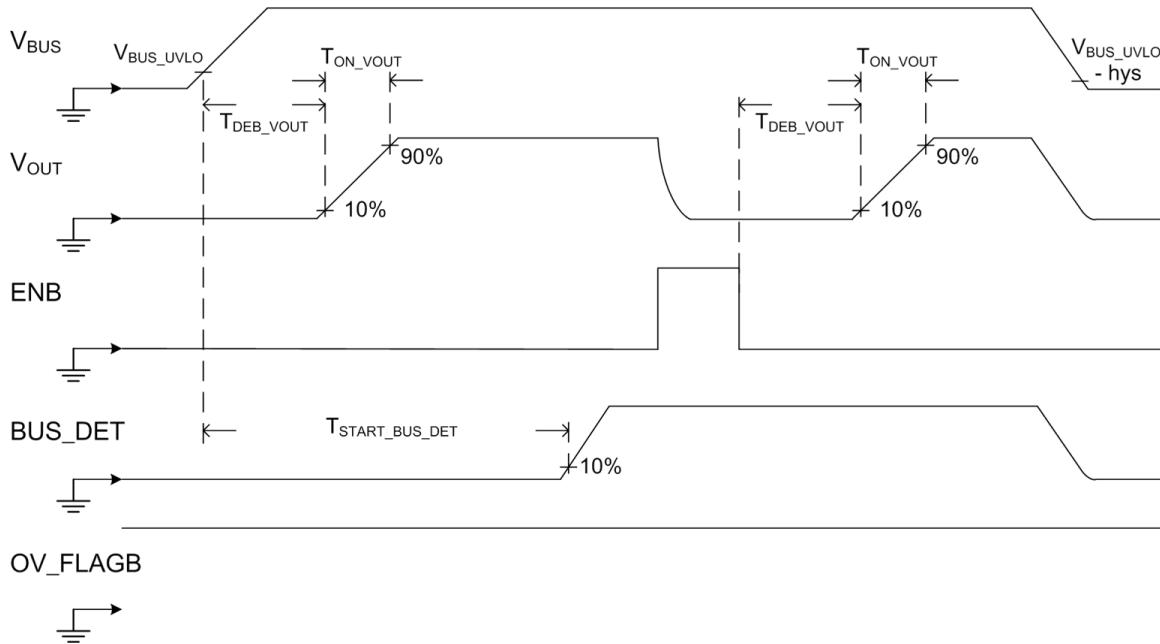

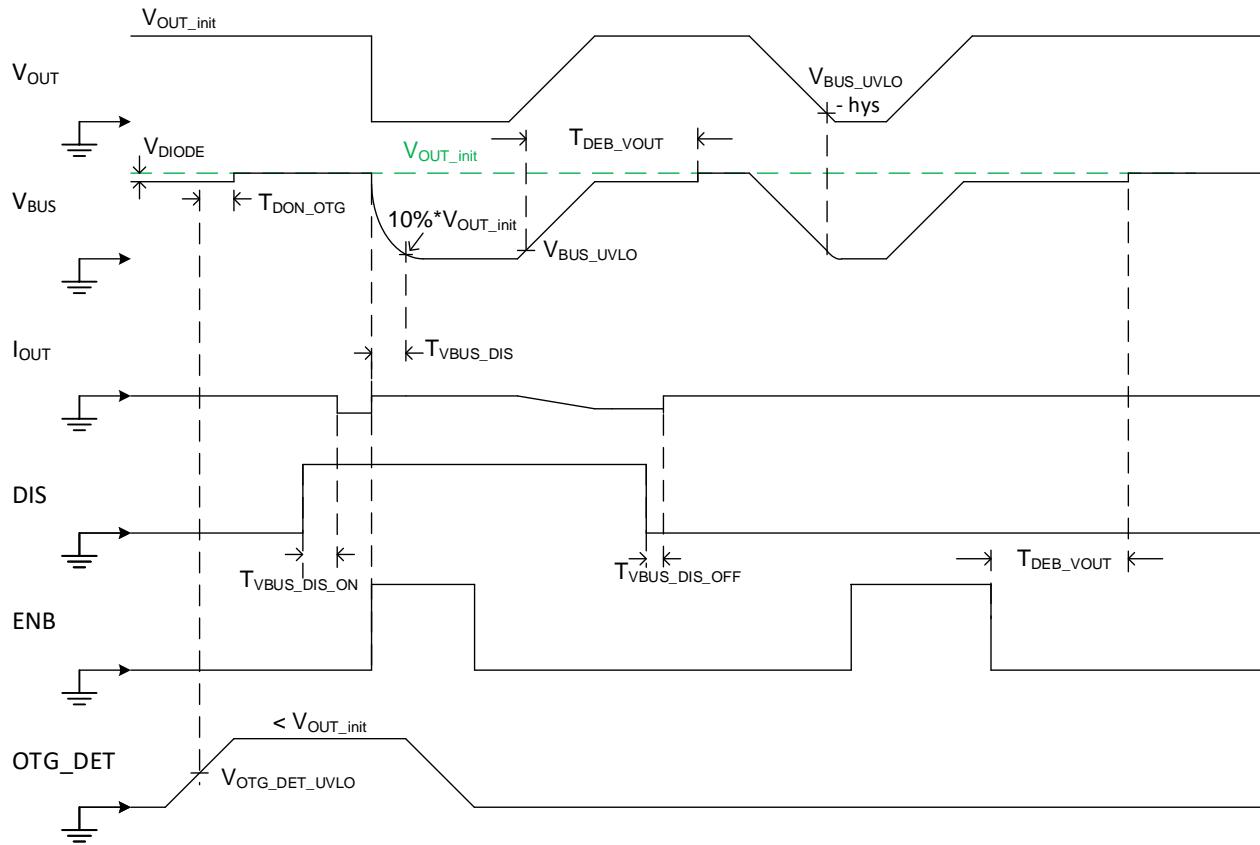

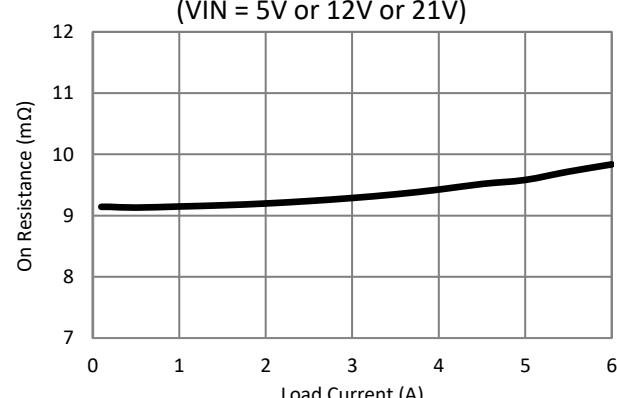

**Figure 1. VBUS Ramp-up, Ramp down and ENB Toggling**

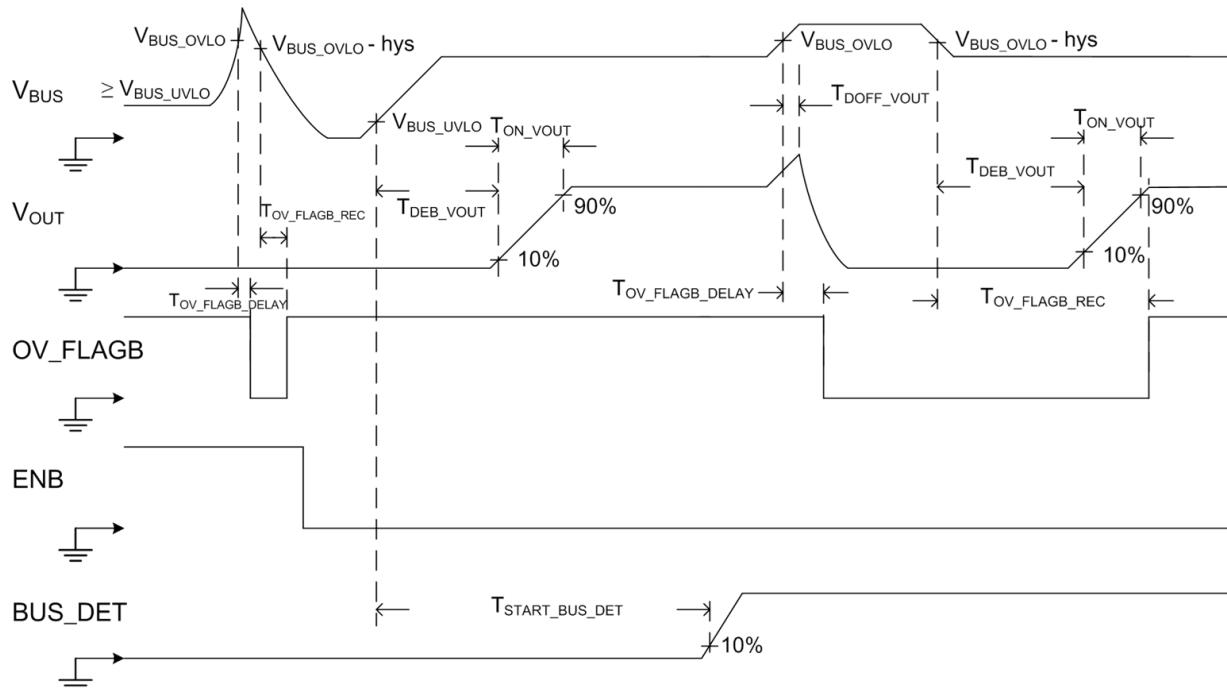

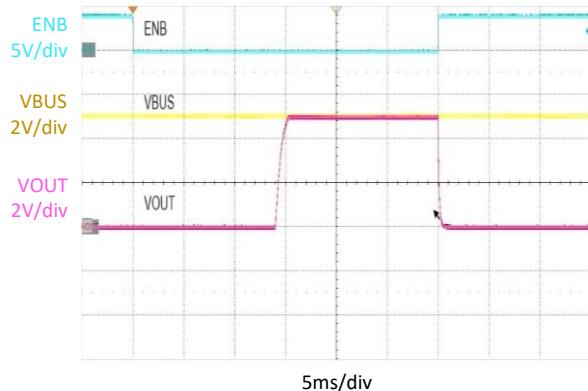

**Figure 2. Over Voltage Protection (OVP) Trigger and Recover**

## Timing Diagrams

**Figure 3. OTG Mode and VBUS Active Discharge**

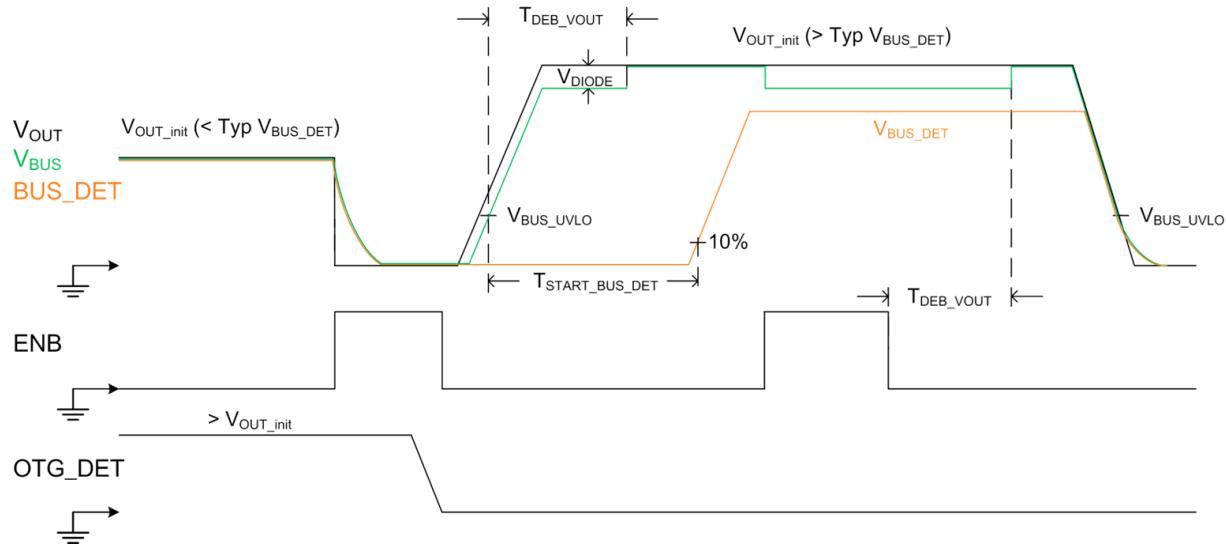

**Figure 4. OTG Mode and BUS\_DET**

## Timing Diagrams

**Figure 5. Over Temperature Protection (OTP)**

## Timing Diagrams

**Figure 6. VBUS Surge per IEC61000-4-5 Standard**

## Typical Characteristics

$V_{BUS} = 5V$ , ENB = GND, DIS = GND, OVLO\_SEL = GND,  $C_{VBUS} = 1\mu F$ ,  $C_{OUT} = 1\mu F$ , CBUS\_DET =  $1\mu F$  and  $T_A = +25^\circ C$  unless specified otherwise.

### No-Load Supply Current vs. VIN Voltage

(ENB = Low/High, OVLO\_SEL = High)

### BUS\_DET Regulation Voltage vs. VBUS Voltage

(IBUS\_DET = 10mA)

### OVP Threshold vs. Temperature

(OVLO\_SEL = Low)

### OVP Threshold vs. Temperature

(OVLO\_SEL = High)

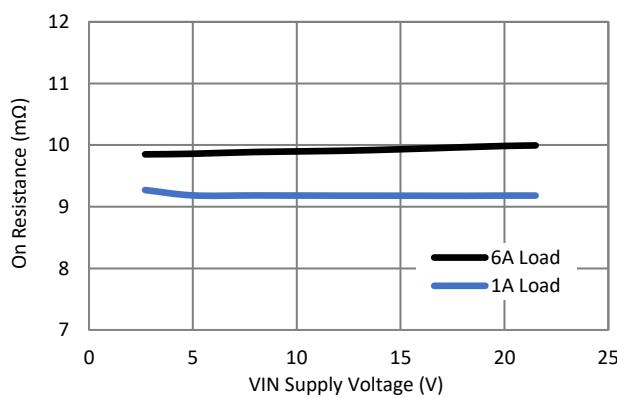

### Switch On-Resistance vs. VIN

### Switch On-Resistance vs. Load Current

(VIN = 5V or 12V or 21V)

## Typical Characteristics

$V_{BUS} = 5V$ ,  $ENB = GND$ ,  $DIS = GND$ ,  $OVLO\_SEL = GND$ ,  $C_{V_{BUS}} = 1\mu F$ ,  $C_{OUT} = 1\mu F$ ,  $CBUS\_DET = 1\mu F$  and  $T_A = +25^\circ C$  unless specified otherwise.

**Enable Turn-on, Turn-off Response**

(100Ω load)

**OVP Response with OV\_FLAGB and Recovery**

(100Ω load,  $V_{BUS}$  from 10V to 15V to 10V)

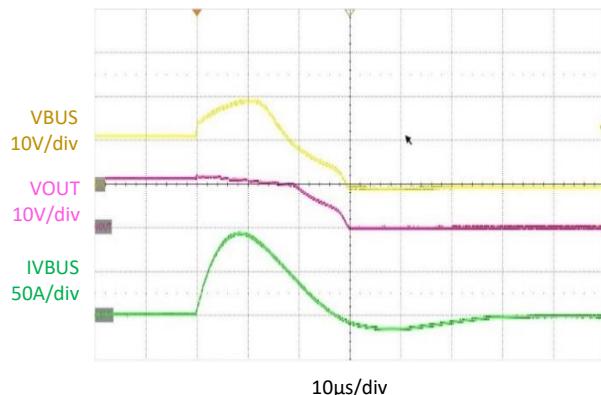

**Surge Transient Response**

( $V_{BUS} = 11VDC$ , +200V Surge,  $OVLO\_SEL = Low$ )

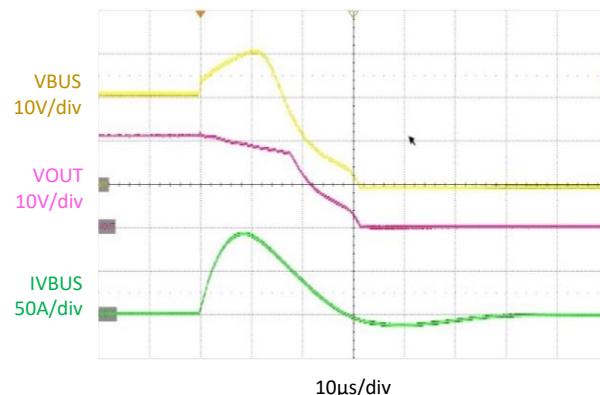

**Surge Transient Response**

( $V_{BUS} = 21VDC$ , +200V Surge,  $OVLO\_SEL = High$ )

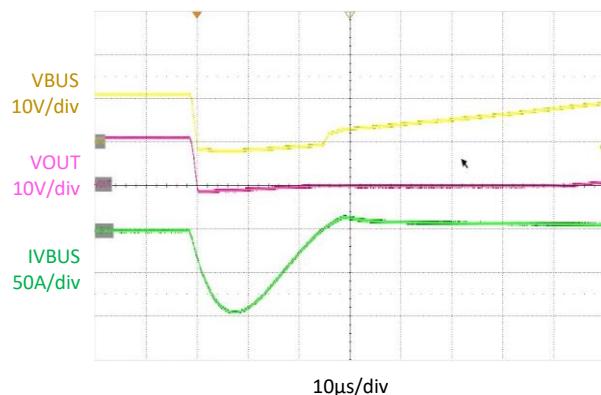

**Surge Transient Response**

( $V_{BUS} = 11VDC$ , -200V Surge,  $OVLO\_SEL = Low$ )

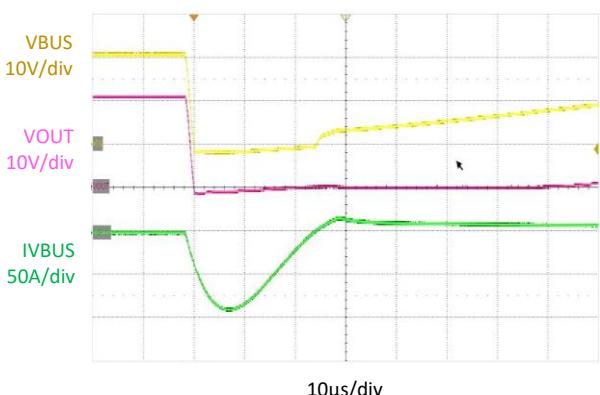

**Surge Transient Response**

( $V_{BUS} = 21VDC$ , -200V Surge,  $OVLO\_SEL = High$ )

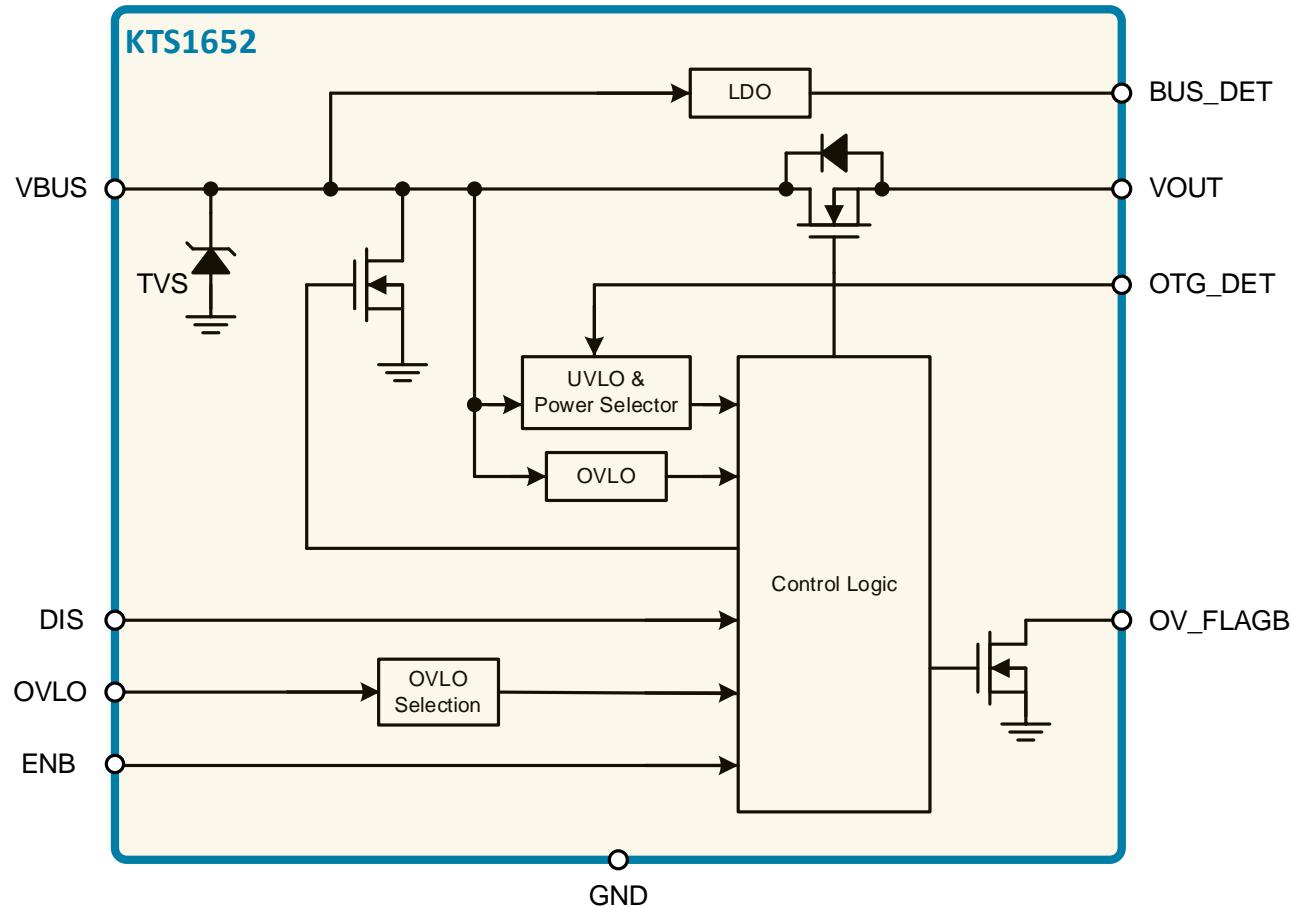

## Functional Block Diagram

**Figure 7. Functional Block Diagram**

## Functional Description

KTS1652 is a low resistance, bi-directional high current load switch with over-voltage protection, over-temperature protection and integrated TVS. The integrated TVS at VBUS is designed to protect against IEC61000-4-5  $\pm 200V$  Surge voltage and IEC61000-4-2 Level 4 Electrostatic Discharge, which safeguards the downstream components from abnormal input conditions.

The power switch connected VBUS to VOUT is a low resistance MOSFET switch, which is typically  $9m\Omega$ . It is intended to be used on VBUS in USB-C to protect against abnormal voltage and current conditions from a power source to a load. VBUS to VOUT is dedicated to sink current, up to 6A, from VBUS to system side; but can also source the same amount of current from system side to VBUS in OTG mode.

### Under-Voltage Lockout (UVLO)

When  $V_{BUS} < V_{UVLO\_BUS}$ , the power switch is disabled. Once  $V_{BUS}$  exceeds  $V_{UVLO\_BUS}$ , the power switch is controlled by the ENB pin and fault detection circuits.

## Over-Voltage Protection (OVP)

When VBUS input voltage is greater than  $V_{BUS\_OVLO}$ , the power switch is disabled. Once VBUS input source voltage drops below  $V_{BUS\_OVLO}$  - Hysteresis, and no other fault is detected, the power switch re-enables via debounce time and turn on time. The KTS1652 has 2 preset over-voltage thresholds, 12.4V or 21.9V; and these two thresholds can be selected by biasing OVLO\_SEL pin to either logic low or logic high.

## Transient Voltage Suppressor (TVS)

KTS1652 has a Transient Voltage Suppressor (TVS) connected from VBUS to GND, which is designed to protect against up to IEC61000-4-5  $\pm 200V$  Surge voltage and IEC61000-4-2 Level 4 Electrostatic Discharge. The internal TVS positive breakdown voltage is 32V (typ), and it is design guaranteed to clamp VBUS voltage at 40V or lower during  $+200V$  Surge. Since KTS1652 OVP response time is fast, VOUT is also design guaranteed not to exceed 15V with VBUS = 11V and  $V_{OVLO\_BUS} = 12.4V$ , or not to exceed 23V with VBUS = 21V and  $V_{OVLO\_BUS} = 21.9V$ , when  $+200V$  surge is applied at VBUS and VOUT is not loaded with any output capacitance or load. During  $-200V$  surge, TVS is forward biased and VBUS negative voltage is limited to  $-6V$  or higher. When testing surge on the bench, each surge voltage, either positive or negative, is tested 100 times, with 1 second relief time before the next surge pulse. VBUS I-V curve should not show any shift after the surge test, otherwise it is considered as failed.

## USB On-The-Go (OTG) Mode

KTS1652 can be powered up from VBUS or VOUT to enable operation in systems that support USB On-The-Go (OTG). There are two ways to enable OTG mode. One way is to set  $VOUT > V_{UVLO\_BUS} + V_{DIODE}$  ( $\sim 1V$ ), and then OTG mode should be ready after VBUS debounce time. The other way to enable OTG mode is by setting OTG\_DET pin voltage  $\geq V_{OTG\_DET\_UVLO}$ , and then VOUT to VBUS power switch should be fully turned on after OTG\_DET Startup Delay time for VOUT initial  $> V_{UVLO\_BUS}$  (2.75V). Since OTG startup delay time is much shorter than VBUS debounce time, the later method to turn on OTG mode is much quicker. In OTG mode, KTS1652 is powered from VOUT or OTG\_DET, whichever is higher, instead of VBUS; as a result, the input current at VBUS drops to  $1\mu A$  or less. VBUS should always equal to VOUT when ENB=L and power is switching from OTG\_DET to VOUT, or vice versa. Switch On-Resistance in OTG mode is the same as normal mode (VBUS to VOUT), which is typically  $9m\Omega$ , and it can also support up to 6A current to be delivered from VOUT to VBUS.

## BUS\_DET

When VBUS is greater than  $V_{UVLO\_BUS}$ , the integrated LDO provides an “always ON” power source at BUS\_DET. BUS\_DET voltage is regulated to 4.0V typically, regardless of the status of ENB input, so to power downstream components permitting operation without an installed battery. The BUS\_DET LDO supplies up to 10mA of output current. BUS\_DET should always be coupled with  $1\mu F$  at least; otherwise, its voltage can overshoot beyond its absolute maximum rating during fast VBUS voltage transient event, such as Surge event.

## Over-Temperature Protection (OTP)

When device junction temperature exceeds  $145^\circ C$ , the OTP circuit disables VBUS to VOUT switch. Once the device junction temperature decreases below  $125^\circ C$ , and no other fault is detected, the power switch returns to its previous state via debounce time and switch turn on time.

## VBUS Input Discharge

For USB Power Delivery (PD), KTS1652 features an active discharge for the VBUS node. When DIS is set to logic high, the internal  $550\Omega$  connected from VBUS to GND is enabled and discharges VBUS from as high as 20V to below 0.8V within 650ms, with sufficient margin for any excess capacitance on VBUS due to the compliance test equipment. Enabling active discharge with a constant voltage at VBUS can cause continuous excessive power dissipation, which should be avoided at all costs.

## **OV\_FLAGB Output Flag**

The OV\_FLAGB output is an active-low, open-drain output that requires an external pull-up resistor. The pull up resistor value is recommended to be 10 KΩ to 200 KΩ. When there is no over voltage fault and the power switch is ON, the OV\_FLAGB flag is high impedance to indicate no fault condition is detected. Whenever over voltage fault ( $V_{BUS} \geq V_{OVLO\_BUS}$ ) at VBUS triggers OVP, OV\_FLAGB pin actively pulls to GND after  $T_{OV\_FLAGB\_DELAY}$ . Once VBUS recovers back to  $V_{OVLO\_BUS}$  - hysteresis, OV\_FLAGB automatically returns back to high impedance after Recovery Debounce Time ( $T_{OV\_FLAGB\_REC}$ ). OV\_FLAGB Recovery debounce time is short (100us) when KTS1652 is not enabled (ENB = H) and VBUS is initially settled at  $\geq V_{BUS\_UVLO}$  and  $< V_{BUS\_OVLO}$  for a long time before the over-voltage event; but it is extended to 20ms (typ) when KTS1652 is already enabled (ENB = L) before OVP event, so to assure OV\_FLAGB will be reset to high impedance only after VOUT is fully recovered.

## **ENB Enable Control**

The ENB is an active-low input with an internal 1MΩ pull-down resistor. ENB = H disables the power switch, but it is not intended to reduce input supply current. ENB = L enables the protection circuits and the power switch. A 15ms debounce time deploys before device turns on.

**Table 1. BUS\_DET and OV\_FLAGB Truth Table**

| <b>VBUS</b>                                  | <b>OTP</b> | <b>ENB</b> | <b>BUS_DET</b> | <b>OV_FLAGB</b> |

|----------------------------------------------|------------|------------|----------------|-----------------|

| $V_{BUS} < V_{BUS\_UVLO}$                    | X          | X          | OFF            | HI-Z            |

| $V_{BUS\_UVLO} \leq V_{BUS} < V_{BUS\_OVLO}$ | 0          | X          | ON             | HI-Z            |

|                                              | 1          | X          | OFF            | HI-Z            |

| $V_{BUS} \geq V_{BUS\_OVLO}$                 | 0          | X          | ON             | LOW             |

|                                              | 1          | X          | OFF            | HI-Z            |

X = Don't Care

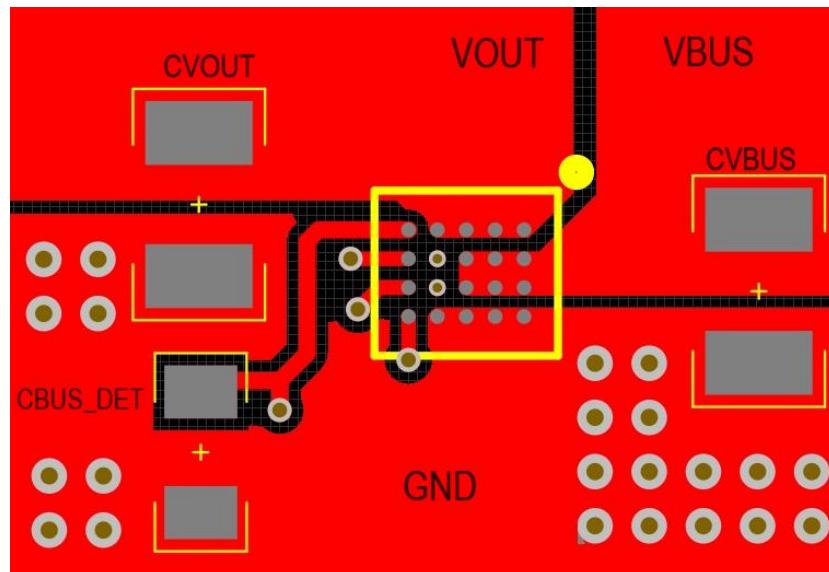

## PCB Layout Guidelines

Optimized trace routing and placement are important to assure KTS1652 protection features. The following guidelines are recommended for best system performance:

1. KTS1652 IC package should be placed as close as possible to the USB Type-C connector to maximize ESD, surge and OVP protection for the system.

2. For the printed circuit board, a good thermal design is recommended to support 6A fully loaded current. VBUS, VOUT and GND should have a reasonable size of copper pour, so that it can be used as a thermal dissipating interface. Additional thermal vias can also help to conduct the heat to the other side of PCB, with additional copper plate.

3. Place the input bypass capacitors and output decoupling capacitor as close to VBUS, VOUT and BUS\_DET as possible. Connect the ground terminal of the capacitor to the ground plane using multiple vias.

4. Signal trace for OV\_FLAGB, ENB, OTG\_DET, OVLO\_SEL and DIS are low current traces.

Figure 8. Recommended PCB Layout

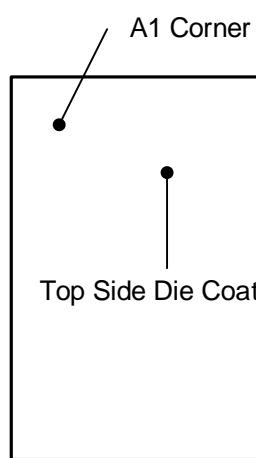

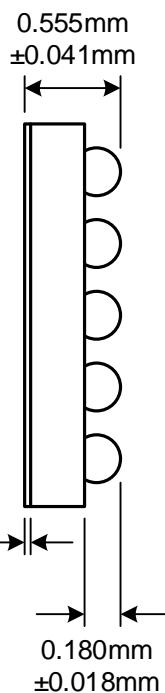

### Packaging Information

WLCSP54-20 (2.460mm x 1.967mm x 0.555mm)

Top View

Side View

Bottom View

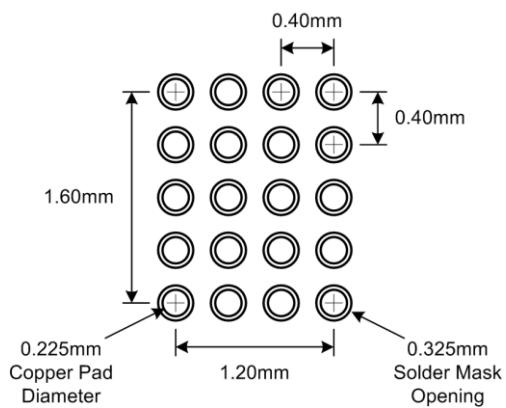

### Recommended Footprint (NSMD Pad Type)

Kinetic Technologies cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Kinetic Technologies product. No intellectual property or circuit patent licenses are implied. Kinetic Technologies reserves the right to change the circuitry and specifications without notice at any time.