# 256 Mb/512 Mb/1 Gb SEMPER™ Flash

**Quad SPI, 1.8 V/3.0 V**

## Features

- Infineon 45-nm MIRRORBIT™ technology that stores two data bits in each memory array cell

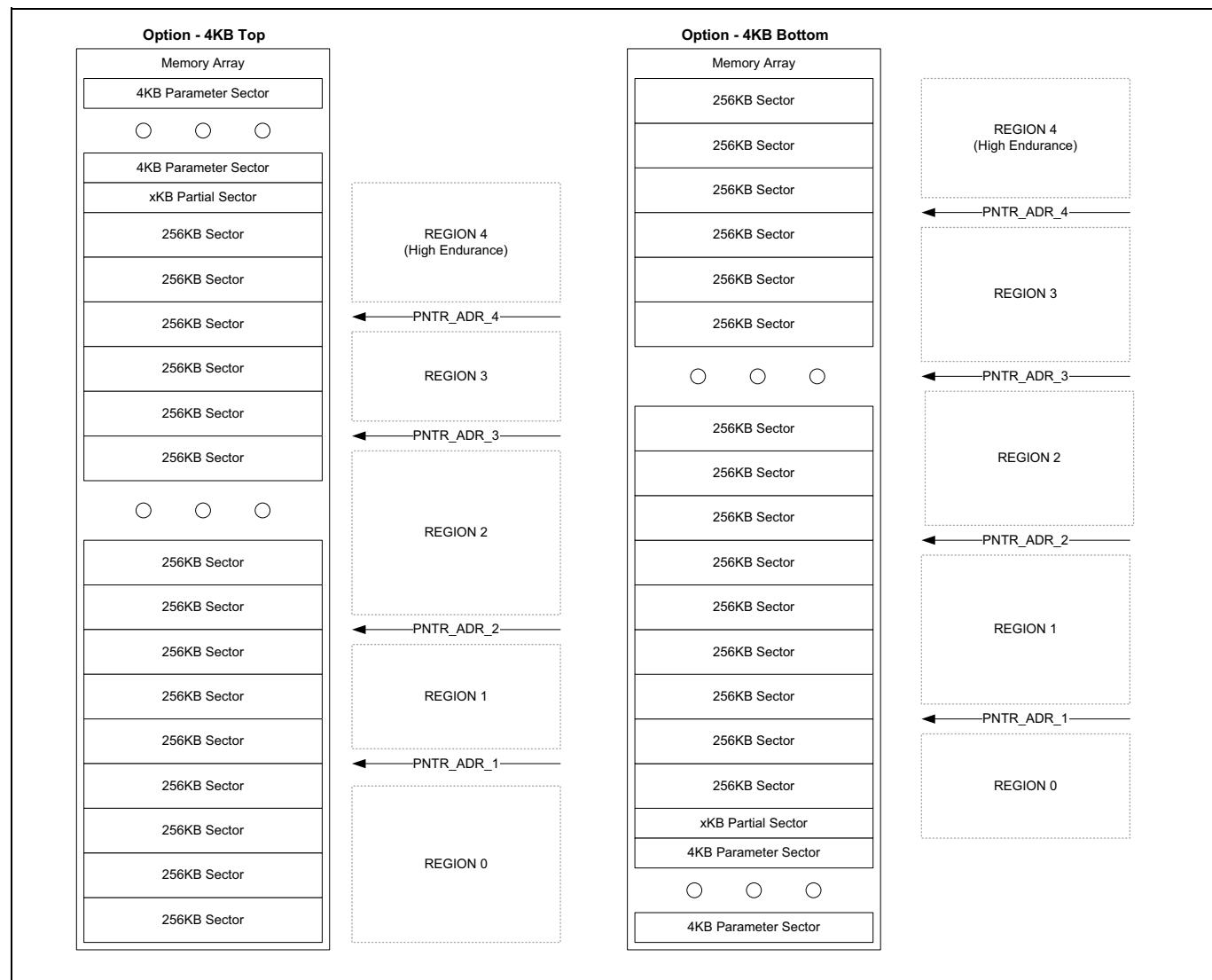

- Sector architecture options

- Uniform: Address space consists of all 256 KB sectors

- Hybrid Configuration 1: Address space consists of thirty-two 4 KB sectors grouped either on the top or the bottom while the remaining sectors are all 256 KB

- Hybrid Configuration 2: Address space consists of thirty-two 4 KB sectors equally split between top and bottom while the remaining sectors are all 256 KB

- Page programming buffer of 256 or 512 bytes

- OTP secure silicon array of 1024 bytes (32 × 32 bytes)

- Quad SPI

- Supports 1S-1S-4S, 1S-4S-4S, 1S-4D-4D, 4S-4S-4S, 4S-4D-4D protocols

- SDR option runs up to 83-MBps (166 MHz clock speed)

- DDR option runs up to 102-MBps (102 MHz clock speed)

- Dual SPI

- Supports 1S-2S-2S protocol

- SDR option runs up to 41.5-MBps (166 MHz clock speed)

- SPI

- Supports 1S-1S-1S protocol

- SDR option runs up to 21-MBps (166 MHz clock speed)

- Functional safety features

- Functional safety with the industry's first ISO26262 ASIL B compliant and ASIL D ready NOR Flash

- Infineon Endurance Flex architecture provides high-endurance and long retention partitions

- Data integrity CRC detects errors in memory array

- SafeBoot reports device initialization failures, detects configuration corruption, and provides recovery options

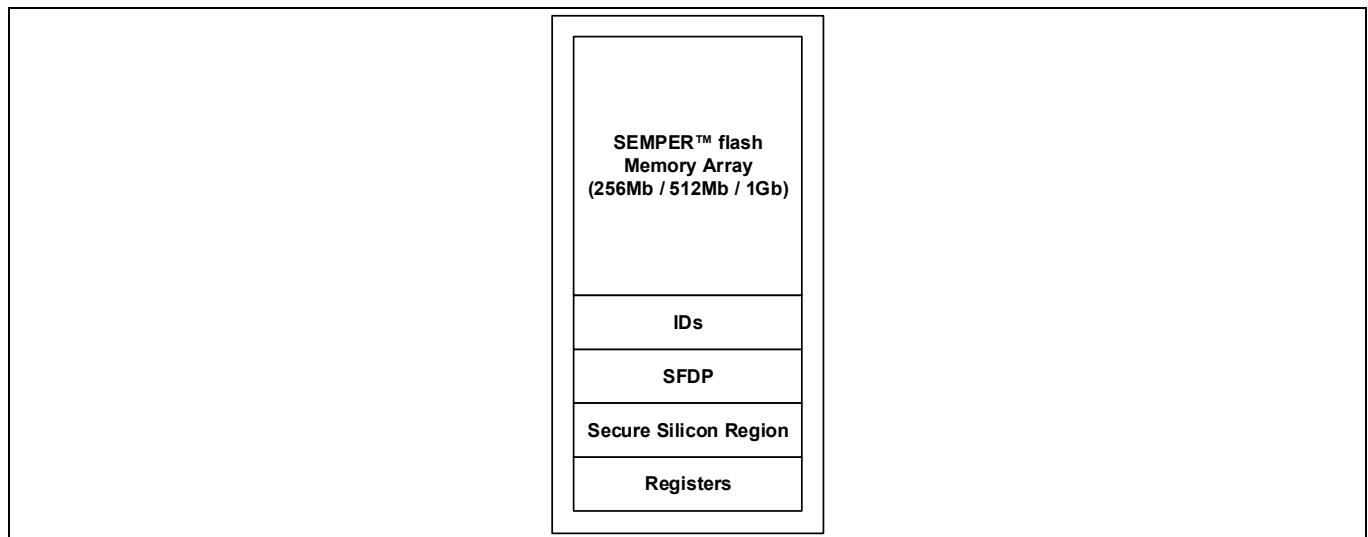

- Built-in error correcting code (ECC) corrects single-bit error and detects double-bit error (SECDED) on memory array data

- Sector erase status indicator for power loss during erase

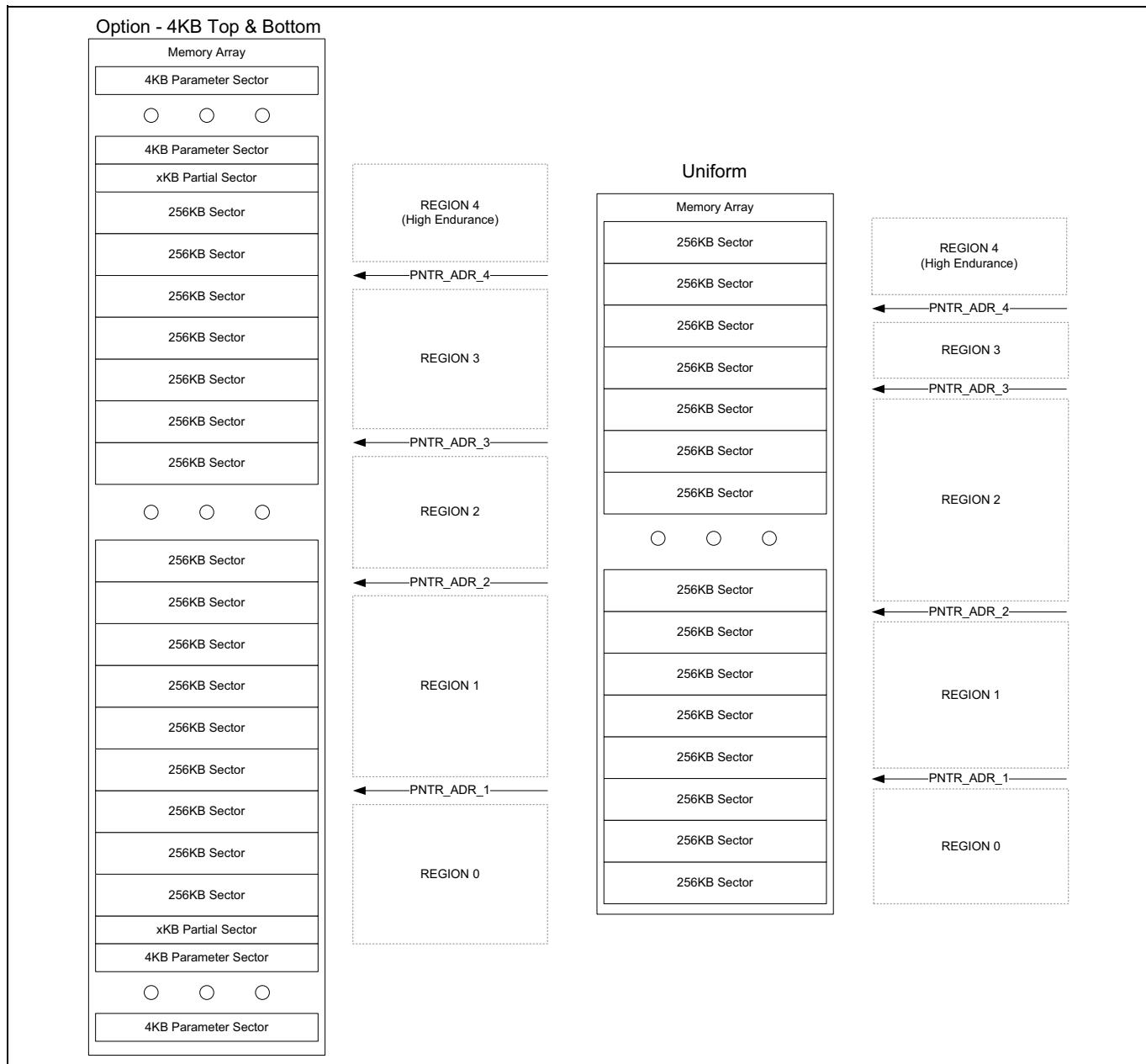

- Protection features

- Legacy block protection for memory array and device configuration

- Advanced sector protection for individual memory array sector based protection

- AutoBoot enables immediate access to the memory array following power-on

- Hardware reset through JEDEC Serial Flash Reset Signaling Protocol / individual RESET# pin / DQ3\_RESET# pin

- Serial flash discoverable parameters (SFDP) describing device functions and features

- Device identification, manufacturer identification, and unique identification

## Features

- Data Integrity

- 256Mb devices

- Minimum 640,000 program-erase cycles for the main array

- 512Mb devices

- Minimum 1,280,000 program-erase cycles for the main array

- 1Gb devices

- Minimum 2,560,000 program-erase cycles for the main array

- All devices

- Minimum 300,000 program-erase cycles for the 4KB sectors

- Minimum 25 years data retention

- Supply voltage

- 1.7 V to 2.0 V (HS-T)

- 2.7 V to 3.6 V (HL-T)

- Grade / temperature range

- Industrial (-40°C to +85°C)

- Industrial plus (-40°C to +105°C)

- Automotive AEC-Q100 grade 3 (-40°C to +85°C)

- Automotive AEC-Q100 grade 2 (-40°C to +105°C)

- Automotive AEC-Q100 grade 1 (-40°C to +125°C)

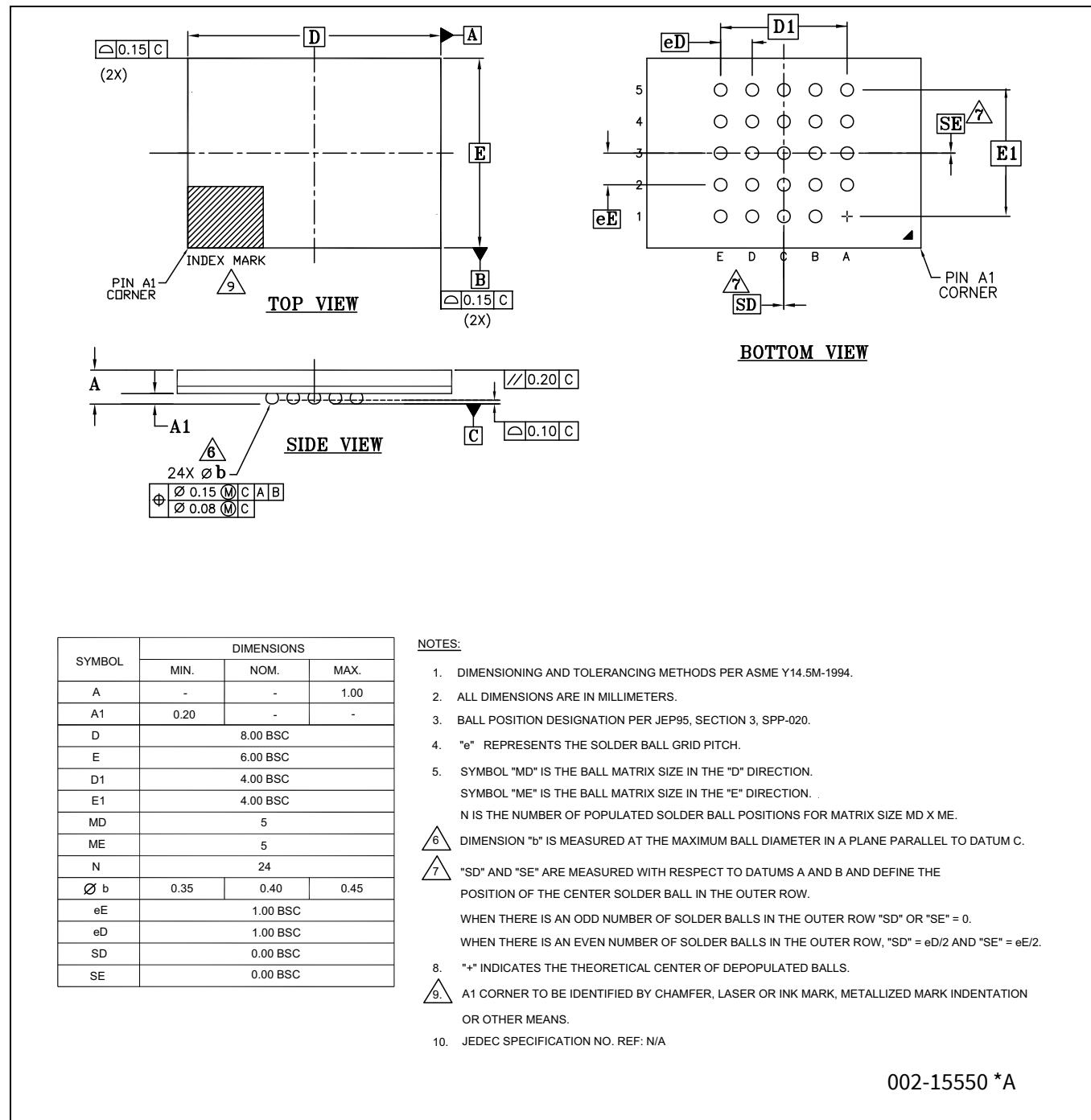

- Packages

- 256MB and 512MB

- 16-lead SOIC (300 mil) - SO3016

- 24-ball BGA 6 × 8 mm

- 16-lead SOIC (300 mil)

- 8-contact WSON 6 × 8 mm

- 1GB

- 16-lead SOIC (300 mil) - SO3016

- 24-ball BGA 8 × 8 mm

- 16-lead SOIC (300 mil)

Performance summary

## Performance summary

### Maximum read rates

| Transaction   | Initial access latency (Cycles) | Clock rate (MHz) | MBps  |

|---------------|---------------------------------|------------------|-------|

| SPI Read      | 0                               | 50               | 6.25  |

| SPI Fast Read | 9                               | 166              | 20.75 |

| Dual Read SDR | 7                               | 166              | 41.5  |

| Quad Read SDR | 10                              | 166              | 83    |

| Quad Read DDR | 7                               | 102              | 102   |

### Typical program and erase rates

| Operation                                         | KBps      |

|---------------------------------------------------|-----------|

| 256B page programming (4KB sector / 256KB sector) | 595 / 533 |

| 512B page programming (4KB sector / 256KB sector) | 753 / 898 |

| 256KB sector erase                                | 331       |

| 4KB sector erase                                  | 95        |

### Typical current consumption

| Operation              | Current (mA) |

|------------------------|--------------|

| SDR Read 50 MHz        | 10           |

| SDR Read 166 MHz       | 53           |

| DDR Read 102 MHz       | 50           |

| Program                | 50           |

| Erase                  | 50           |

| Standby (HS-T)         | 0.011        |

| Standby (HL-T)         | 0.014        |

| Deep power down (HS-T) | 0.0013       |

| Deep power down (HL-T) | 0.0022       |

Data integrity

## Data integrity

### Program / erase (PE) endurance - High endurance (256 KB sectors)

| Sectors in partition            | Minimum PE cycles | Minimum retention time | Unit  |

|---------------------------------|-------------------|------------------------|-------|

| 512 (Default for 1GB devices)   | 2,560,000         | 2                      | Years |

| 508                             | 2,540,000         |                        |       |

| 504                             | 2,520,000         |                        |       |

| ...                             | ...               |                        |       |

| 256 (Default for 512MB devices) | 1,280,000         |                        |       |

| 252                             | 1,260,000         |                        |       |

| 128 (Default for 256MB devices) | 640,000           |                        |       |

| ...                             |                   |                        |       |

| 28                              | 140,000           |                        |       |

| 24                              | 120,000           |                        |       |

| 20                              | 100,000           |                        |       |

**Note** Minimum cycles is for entire high endurance partition.

### Program / erase endurance - Long retention partition (256 KB sectors)

| Minimum PE cycles | Minimum retention time | Unit  |

|-------------------|------------------------|-------|

| 500               | 25                     | Years |

**Note** Minimum cycles is for each sector.

### Program / erase endurance 4 KB sector and nonvolatile register array

| Flash memory type                                                                                                        | Minimum cycles                                                                                                                                                    | Unit      | Minimum retention time | Unit  |

|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------|-------|

| Program/Erase cycles per 4KB sector                                                                                      | 500                                                                                                                                                               | PE cycles | 25                     | Years |

|                                                                                                                          | 300,000                                                                                                                                                           |           | 2                      |       |

|                                                                                                                          | <b>Note</b> It is required to restrict the power loss events to 300 times per sector during program or erase operation to achieve the mentioned endurance cycles. |           |                        |       |

| Program/Erase cycles per persistent protection bits (PPB) array or nonvolatile register array                            | 500                                                                                                                                                               |           | 25                     |       |

| <b>Note</b> Each write transaction to a nonvolatile register causes a PE cycle on the entire nonvolatile register array. |                                                                                                                                                                   |           |                        |       |

## Table of contents

|                                                                                                            |           |

|------------------------------------------------------------------------------------------------------------|-----------|

| <b>Features .....</b>                                                                                      | <b>1</b>  |

| <b>Performance summary .....</b>                                                                           | <b>3</b>  |

| <b>Data integrity.....</b>                                                                                 | <b>4</b>  |

| <b>Table of contents .....</b>                                                                             | <b>5</b>  |

| <b>1 Pinout and signal description.....</b>                                                                | <b>8</b>  |

| <b>2 Interface overview .....</b>                                                                          | <b>10</b> |

| 2.1 General description .....                                                                              | 10        |

| 2.2 Signal protocols .....                                                                                 | 12        |

| 2.2.1 SEMPER™ Flash with Quad SPI clock modes .....                                                        | 12        |

| 2.3 Transaction protocol .....                                                                             | 13        |

| 2.3.1 Serial peripheral interface (SPI, 1S-1S-1S) .....                                                    | 15        |

| 2.3.2 Dual IO SPI (DIO, 1S-2S-2S).....                                                                     | 17        |

| 2.3.3 QUAD output read SPI (QOR, 1S-1S-4S).....                                                            | 18        |

| 2.3.4 QUAD IO SPI (QIO, 1S-4S-4S, 1S-4D-4D).....                                                           | 18        |

| 2.3.5 Quad peripheral interface (QPI, 4S-4S-4S and 4S-4D-4D).....                                          | 20        |

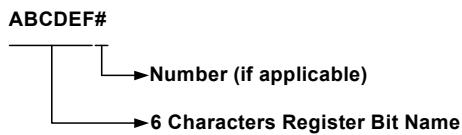

| 2.4 Register naming convention .....                                                                       | 23        |

| 2.5 Transaction naming convention .....                                                                    | 23        |

| <b>3 Address space maps .....</b>                                                                          | <b>24</b> |

| 3.1 SEMPER™ Flash memory array .....                                                                       | 24        |

| 3.2 ID address space .....                                                                                 | 26        |

| 3.3 JEDEC JESD216 serial flash discoverable parameters (SFDP) space .....                                  | 26        |

| 3.4 SSR address space .....                                                                                | 26        |

| 3.5 Registers .....                                                                                        | 27        |

| <b>4 Features.....</b>                                                                                     | <b>29</b> |

| 4.1 Error detection and correction.....                                                                    | 29        |

| 4.1.1 ECC error reporting.....                                                                             | 30        |

| 4.1.2 ECC related registers and transactions.....                                                          | 32        |

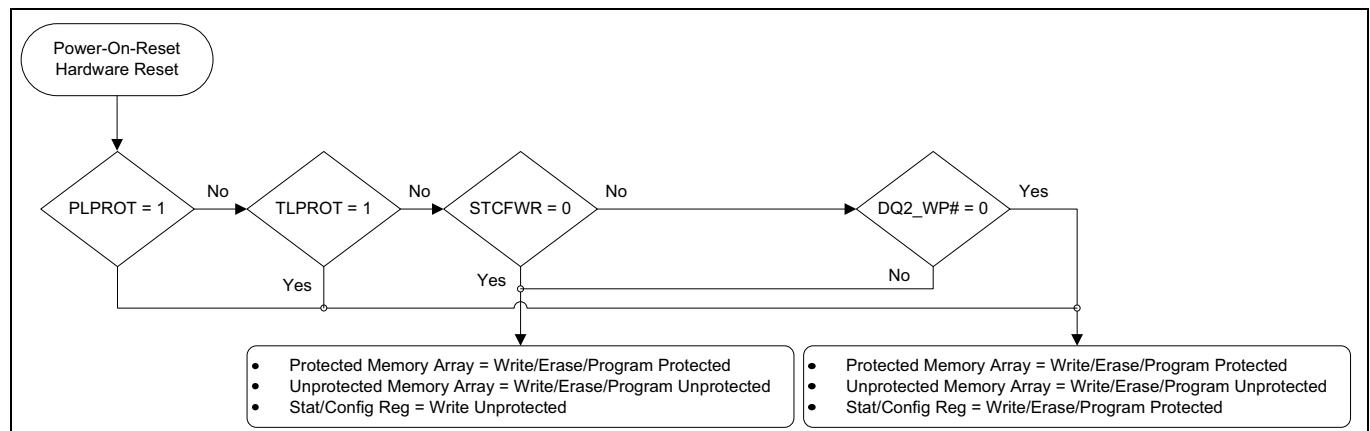

| 4.2 Infineon Endurance Flex architecture (wear leveling) .....                                             | 32        |

| 4.2.1 Configuration 1: Maximum endurance - Single high endurance region .....                              | 35        |

| 4.2.2 Configuration 2: Two region selection - One long retention region and one high endurance region..... | 35        |

| 4.2.3 Infineon Endurance Flex architecture related registers and transaction .....                         | 36        |

| 4.3 Data integrity CRC .....                                                                               | 36        |

| 4.3.1 Data integrity check related registers and transactions .....                                        | 36        |

| 4.4 Data protection schemes .....                                                                          | 37        |

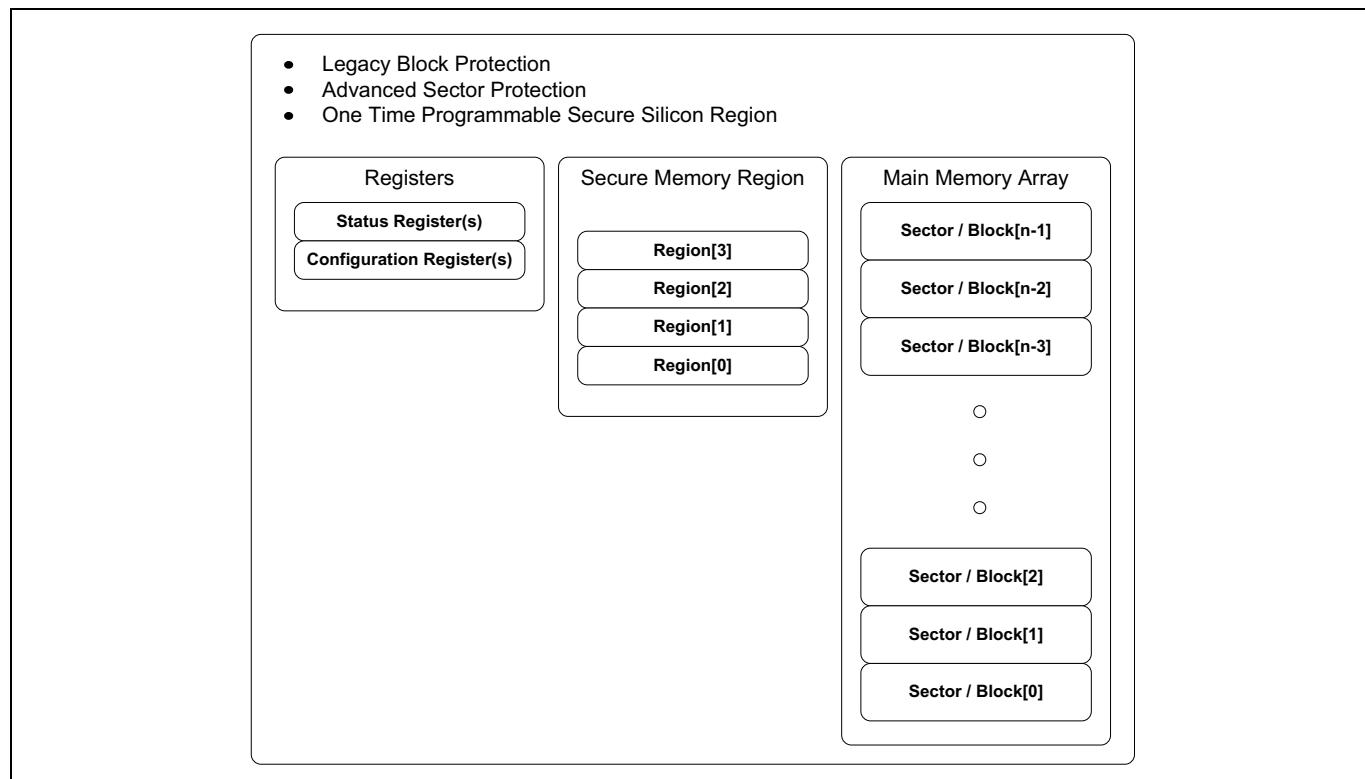

| 4.4.1 Legacy block protection (LBP) .....                                                                  | 37        |

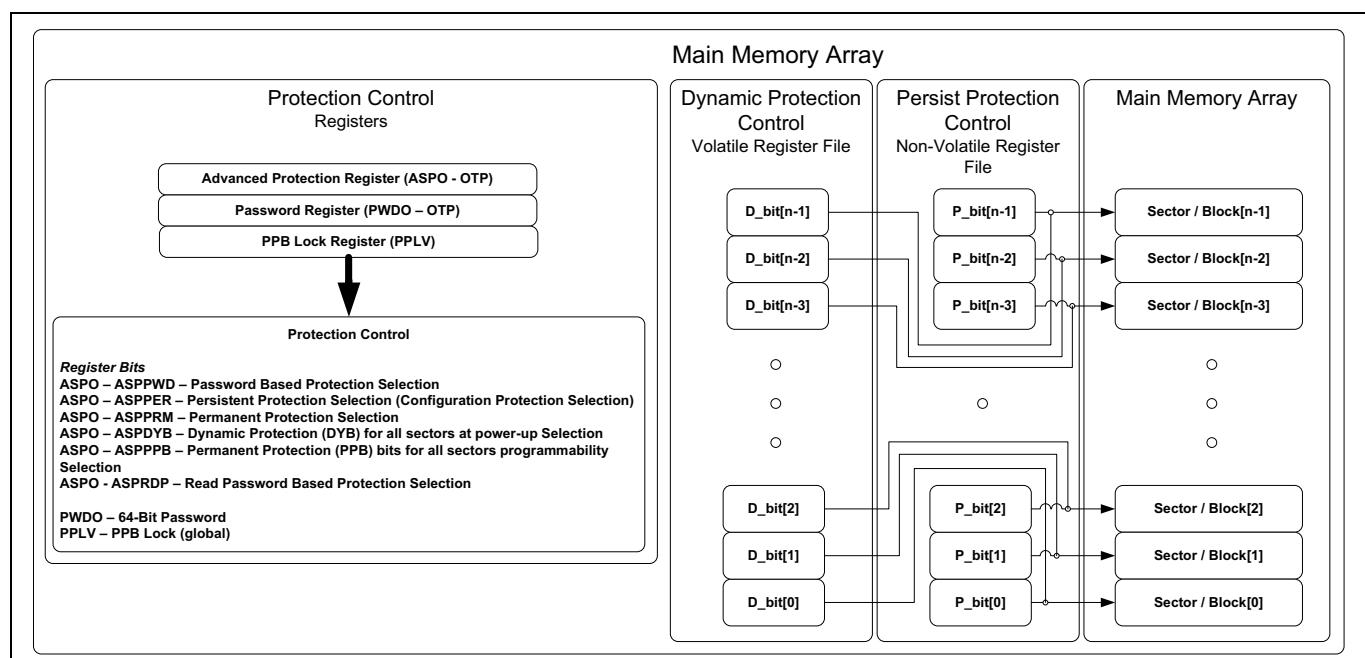

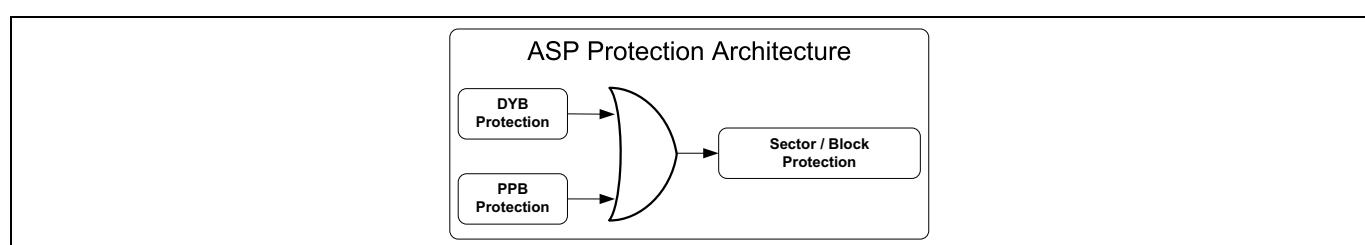

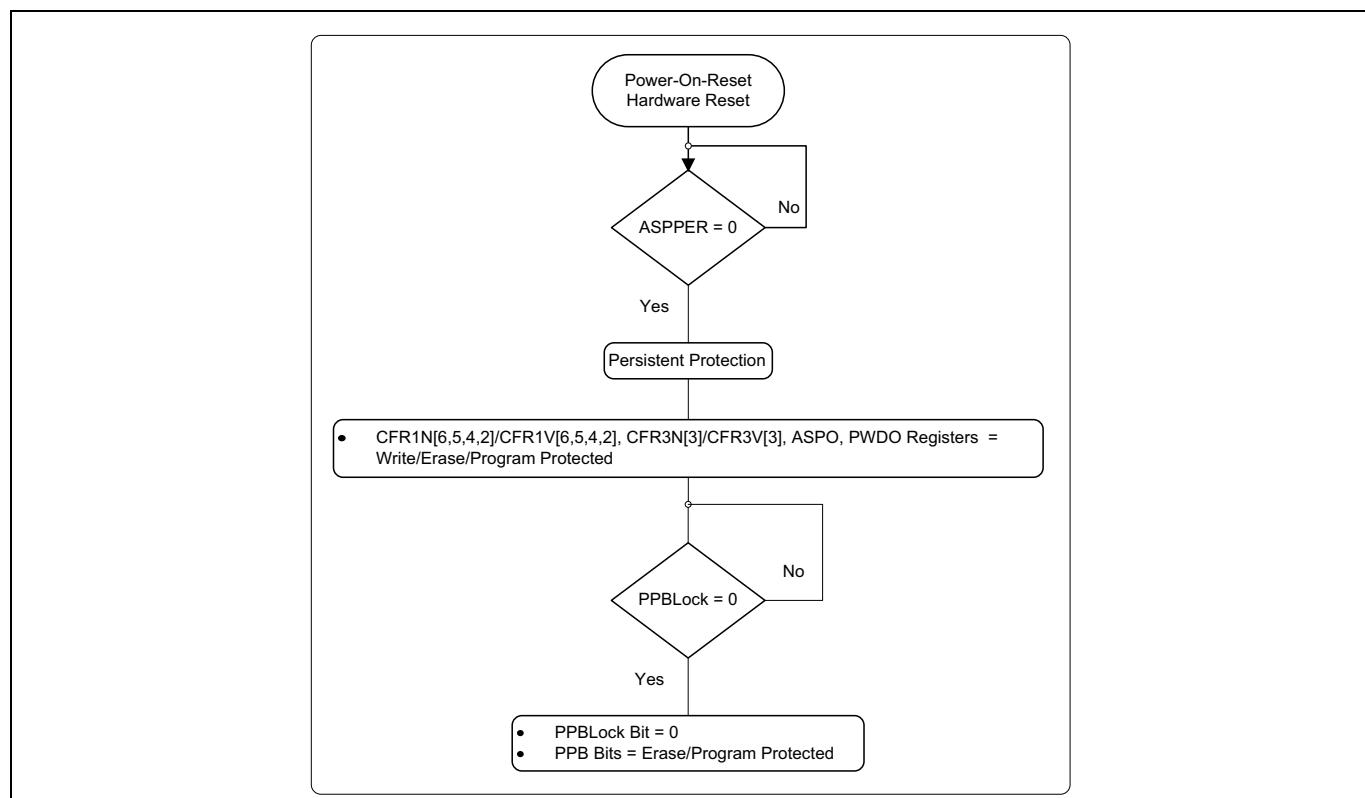

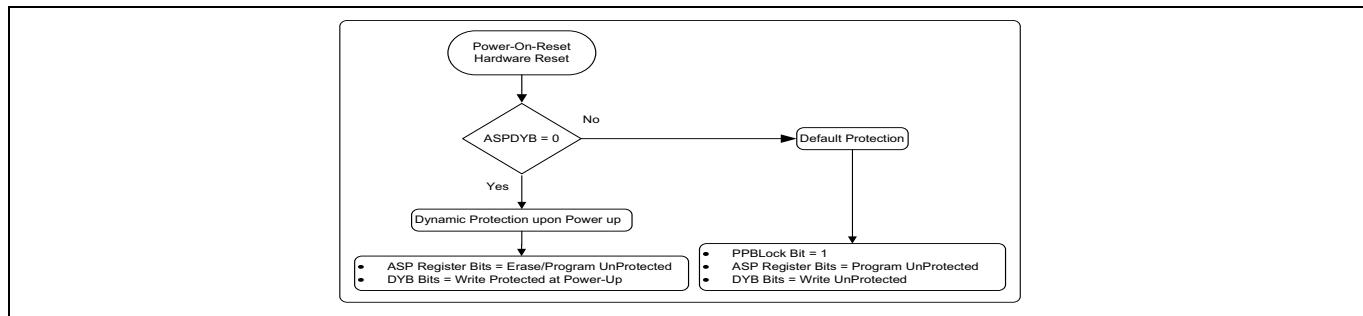

| 4.4.2 Advanced sector protection (ASP) .....                                                               | 40        |

| 4.4.3 Secure silicon region (SSR).....                                                                     | 46        |

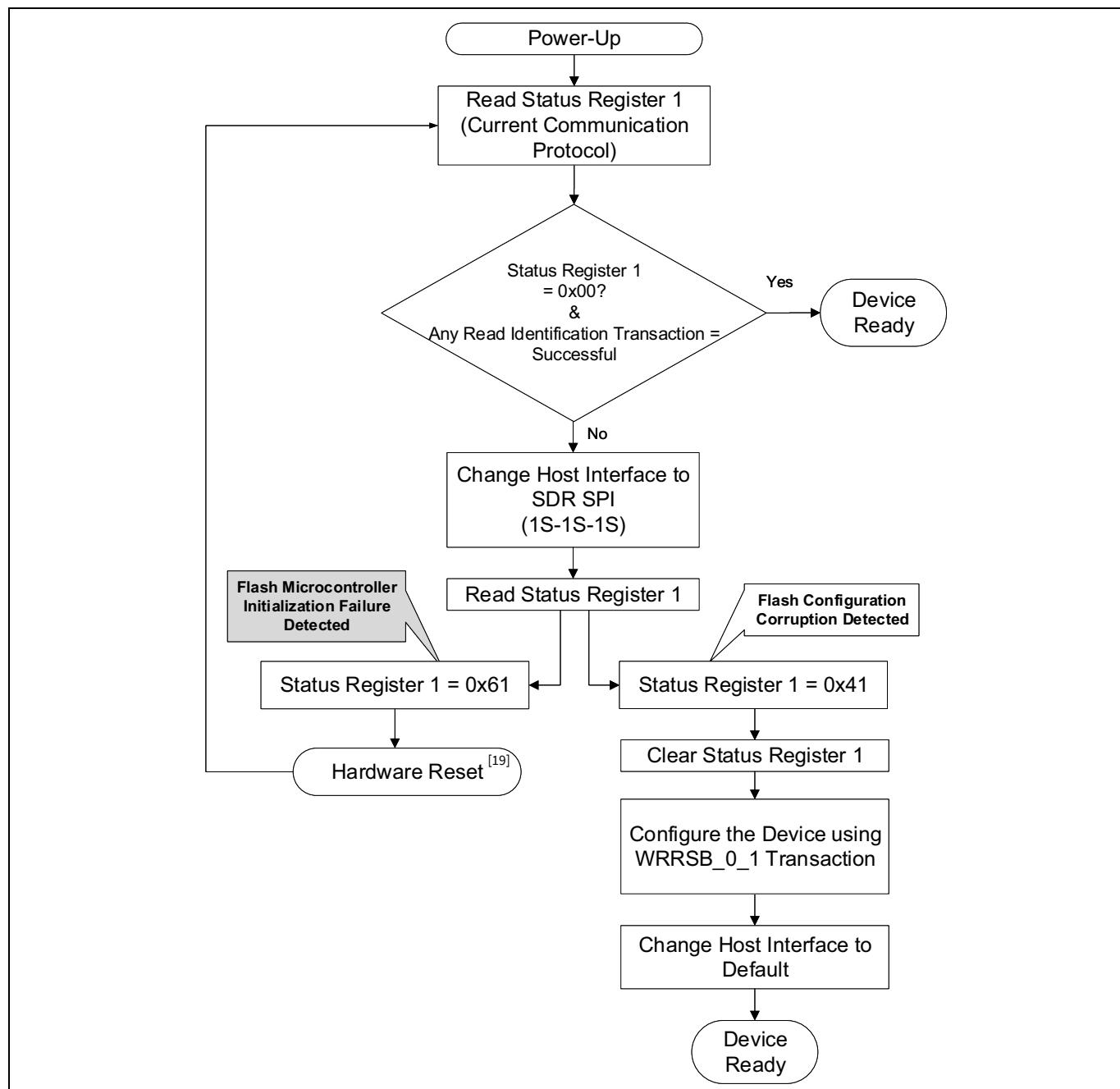

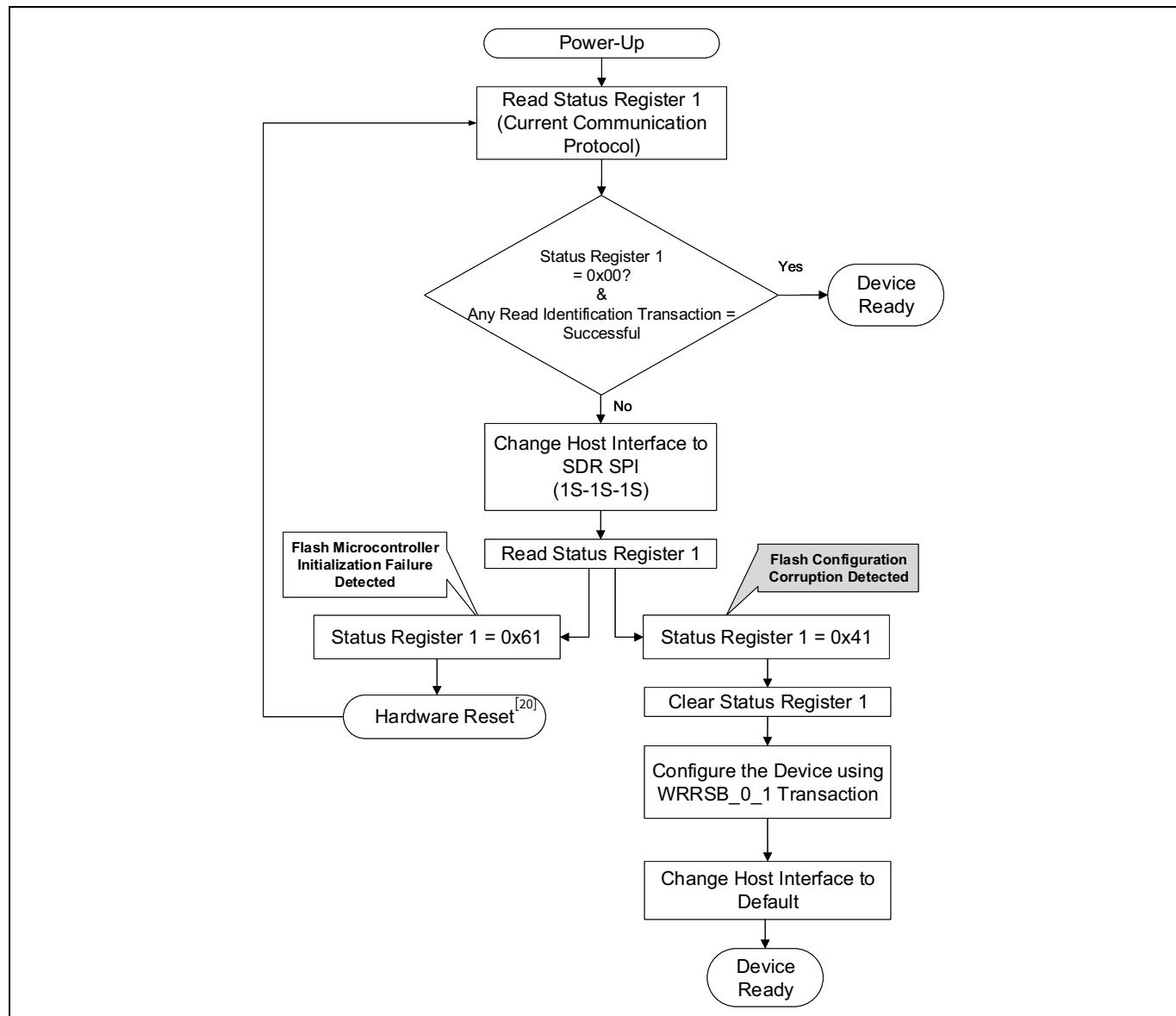

| 4.5 SafeBoot .....                                                                                         | 47        |

| 4.5.1 Microcontroller initialization failure detection .....                                               | 47        |

| 4.5.2 Configuration corruption detection.....                                                              | 49        |

| 4.6 AutoBoot .....                                                                                         | 51        |

| 4.6.1 AutoBoot related registers and transactions .....                                                    | 51        |

| 4.7 Read .....                                                                                             | 52        |

| 4.7.1 Read Identification transactions.....                                                                | 52        |

| 4.7.2 Read Memory Array transactions .....                                                                 | 53        |

| 4.7.3 Read registers transactions.....                                                                     | 55        |

| 4.7.4 Data learning pattern (DLP).....                                                                     | 56        |

| 4.8 Write .....                                                                                            | 57        |

| 4.8.1 Write Enable transaction .....                                                                       | 57        |

| 4.8.2 Write Enable for volatile registers .....                                                            | 57        |

| 4.8.3 Write Disable transaction .....                                                                      | 57        |

Table of contents

|                                                                         |           |

|-------------------------------------------------------------------------|-----------|

| 4.8.4 Clear Program and Erase Failure Flags transaction .....           | 57        |

| 4.8.5 Clear ECC Status Register transaction .....                       | 57        |

| 4.8.6 Write Registers transactions.....                                 | 58        |

| 4.8.7 Write Any Register transaction .....                              | 58        |

| 4.8.8 Write PPB Lock Bit .....                                          | 58        |

| 4.8.9 Enter 4 Byte Address Mode.....                                    | 59        |

| 4.8.10 Exit 4 Byte Address Mode.....                                    | 59        |

| 4.8.11 Write transactions related registers and transactions.....       | 59        |

| 4.9 Program.....                                                        | 60        |

| 4.9.1 Program granularity .....                                         | 60        |

| 4.9.2 Page programming .....                                            | 60        |

| 4.9.3 Program Page transaction.....                                     | 60        |

| 4.9.4 Program Secure Silicon Region transaction.....                    | 61        |

| 4.9.5 Program Persistent Protect Bit (PPB) .....                        | 61        |

| 4.9.6 Program related registers and transactions.....                   | 61        |

| 4.10 Erase .....                                                        | 62        |

| 4.10.1 Erase 4KB Sector transaction .....                               | 62        |

| 4.10.2 Erase 256 KB Sector transaction .....                            | 62        |

| 4.10.3 Erase Chip transaction.....                                      | 62        |

| 4.10.4 Erase Persistent Protection Bit (PPB) transaction .....          | 62        |

| 4.10.5 Erase status and count .....                                     | 63        |

| 4.10.6 Erase related registers and transaction .....                    | 63        |

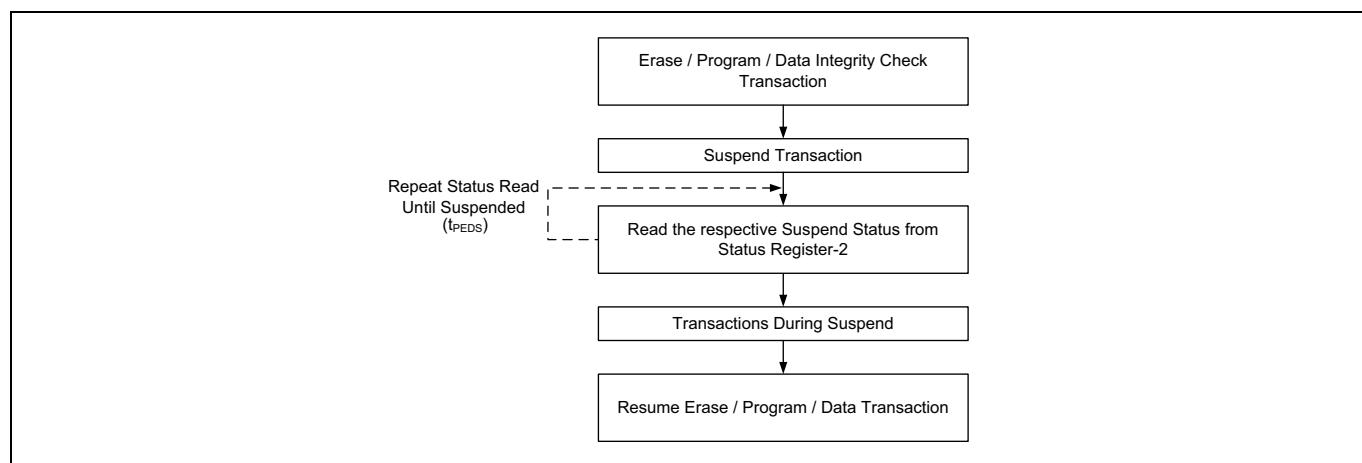

| 4.11 Suspend and resume embedded operation.....                         | 64        |

| 4.11.1 Erase, program, or data integrity check suspend .....            | 64        |

| 4.11.2 Erase, Program, or Data Integrity Check Resume .....             | 66        |

| 4.11.3 Suspend and resume related registers and transactions .....      | 66        |

| 4.12 Reset .....                                                        | 67        |

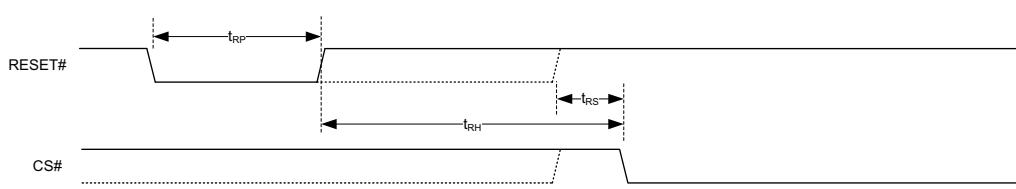

| 4.12.1 Hardware reset (using RESET# input pin and DQ3_RESET# pin) ..... | 67        |

| 4.12.2 Power-on reset (POR) .....                                       | 69        |

| 4.12.3 JEDEC serial flash reset signaling protocol .....                | 70        |

| 4.12.4 Software reset .....                                             | 71        |

| 4.12.5 Reset behavior .....                                             | 72        |

| 4.13 Power modes .....                                                  | 73        |

| 4.13.1 Active power and standby power modes .....                       | 73        |

| 4.13.2 Deep power down (DPD) mode .....                                 | 73        |

| 4.14 Power up and power down .....                                      | 75        |

| 4.14.1 Power up .....                                                   | 75        |

| 4.14.2 Power down .....                                                 | 75        |

| <b>5 Registers.....</b>                                                 | <b>76</b> |

| 5.1 Register naming convention .....                                    | 76        |

| 5.2 Status Register 1 (STR1x).....                                      | 77        |

| 5.3 Status Register 2 (STR2x).....                                      | 79        |

| 5.4 Configuration Register 1 (CFR1x) .....                              | 80        |

| 5.5 Configuration Register 2 (CFR2x) .....                              | 82        |

| 5.6 Configuration Register 3 (CFR3x) .....                              | 84        |

| 5.7 Configuration Register 4 (CFR4x) .....                              | 86        |

| 5.8 Memory Array Data Integrity Check CRC Register (DCRV).....          | 87        |

| 5.9 ECC Status Register (ECSV).....                                     | 88        |

| 5.10 ECC Address Trap Register (EATV).....                              | 88        |

| 5.11 ECC Error Detection Counter Register (ECTV) .....                  | 89        |

| 5.12 Advanced Sector Protection Register (ASPO).....                    | 89        |

| 5.13 ASP Password Register (PWDO) .....                                 | 90        |

| 5.14 ASP PPB Lock Register (PPLV) .....                                 | 91        |

Table of contents

|                                                                           |            |

|---------------------------------------------------------------------------|------------|

| 5.15 ASP PPB Access Register (PPAV) .....                                 | 91         |

| 5.16 ASP Dynamic Block Access Register (DYAV) .....                       | 91         |

| 5.17 Data Learning Register (DLPx) .....                                  | 92         |

| 5.18 AutoBoot Register (ATBN) .....                                       | 93         |

| 5.19 Sector Erase Count Register (SECV) .....                             | 93         |

| 5.20 Infineon Endurance Flex Architecture Selection Register (EFXX) ..... | 94         |

| <b>6 Transaction table.....</b>                                           | <b>97</b>  |

| 6.1 1-1-1 transaction table .....                                         | 97         |

| 6.2 1-2-2 transaction table .....                                         | 102        |

| 6.3 1-1-4 transaction table .....                                         | 102        |

| 6.4 1-4-4 transaction table .....                                         | 103        |

| 6.5 4-4-4 transaction table .....                                         | 104        |

| <b>7 Electrical characteristics .....</b>                                 | <b>110</b> |

| 7.1 Absolute maximum ratings[32-34].....                                  | 110        |

| 7.2 Operating range .....                                                 | 110        |

| 7.2.1 Power supply voltages.....                                          | 110        |

| 7.2.2 Temperature ranges .....                                            | 110        |

| 7.3 Thermal resistance .....                                              | 111        |

| 7.4 Capacitance characteristics .....                                     | 111        |

| 7.5 Latchup characteristics .....                                         | 111        |

| 7.6 DC characteristics .....                                              | 112        |

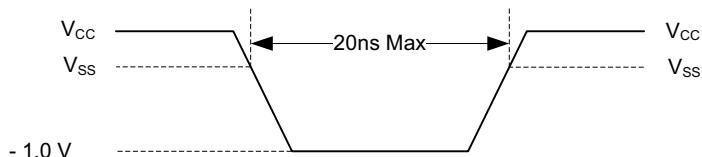

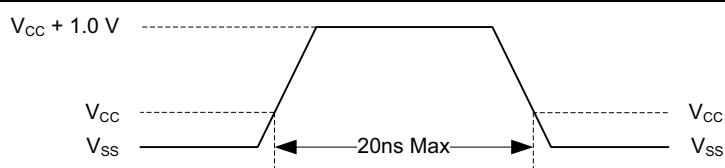

| 7.6.1 Input signal overshoot.....                                         | 112        |

| 7.6.2 DC characteristics (all temperature ranges).....                    | 113        |

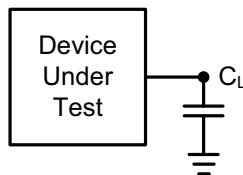

| 7.7 AC test conditions .....                                              | 115        |

| <b>8 Timing characteristics.....</b>                                      | <b>116</b> |

| 8.1 Timing waveforms .....                                                | 120        |

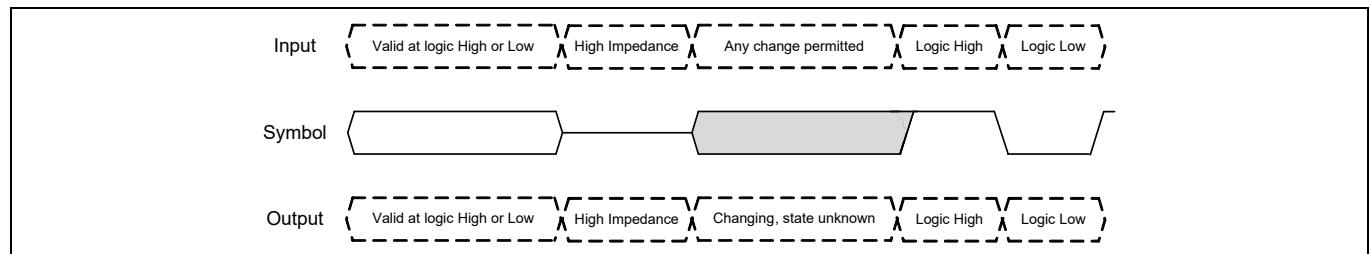

| 8.1.1 Key to timing waveform .....                                        | 120        |

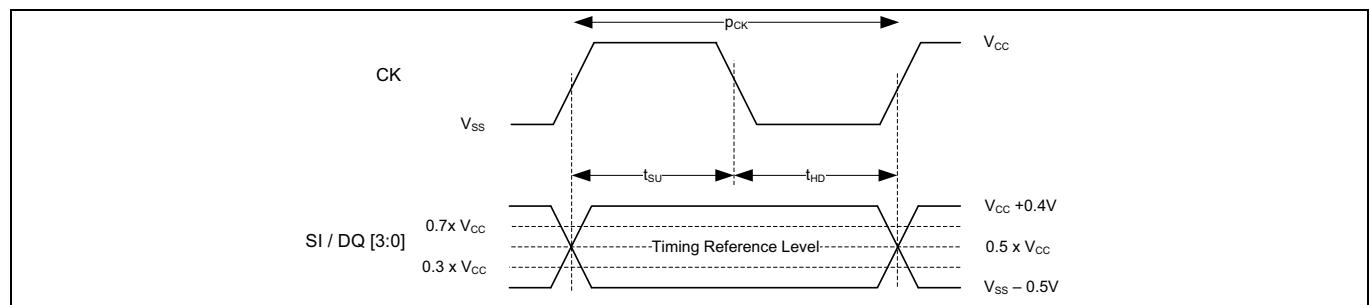

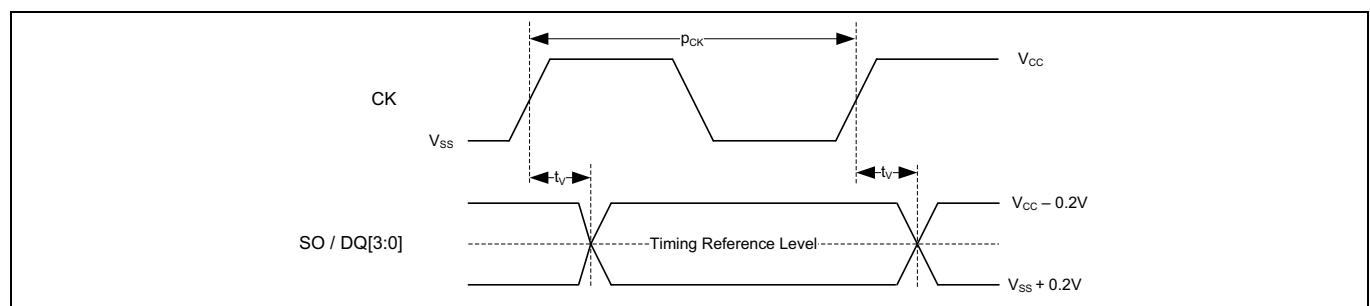

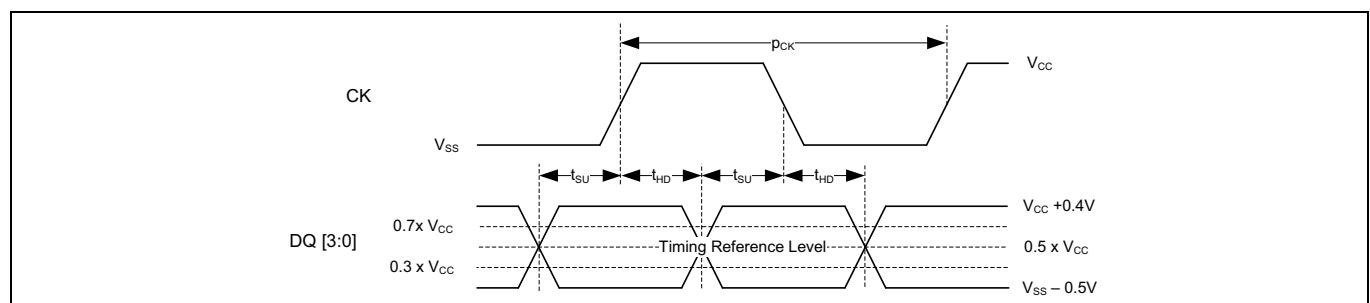

| 8.1.2 Timing reference levels.....                                        | 120        |

| 8.1.3 Clock timing .....                                                  | 121        |

| 8.1.4 Input / output timing .....                                         | 121        |

| <b>9 Device identification .....</b>                                      | <b>123</b> |

| 9.1 JEDEC SDFP Rev D.....                                                 | 123        |

| 9.1.1 JEDEC SDFP Rev D header table .....                                 | 123        |

| 9.1.2 JEDEC SDFP Rev D parameter table.....                               | 124        |

| 9.2 Manufacturer and Device ID .....                                      | 135        |

| 9.3 Unique Device ID .....                                                | 135        |

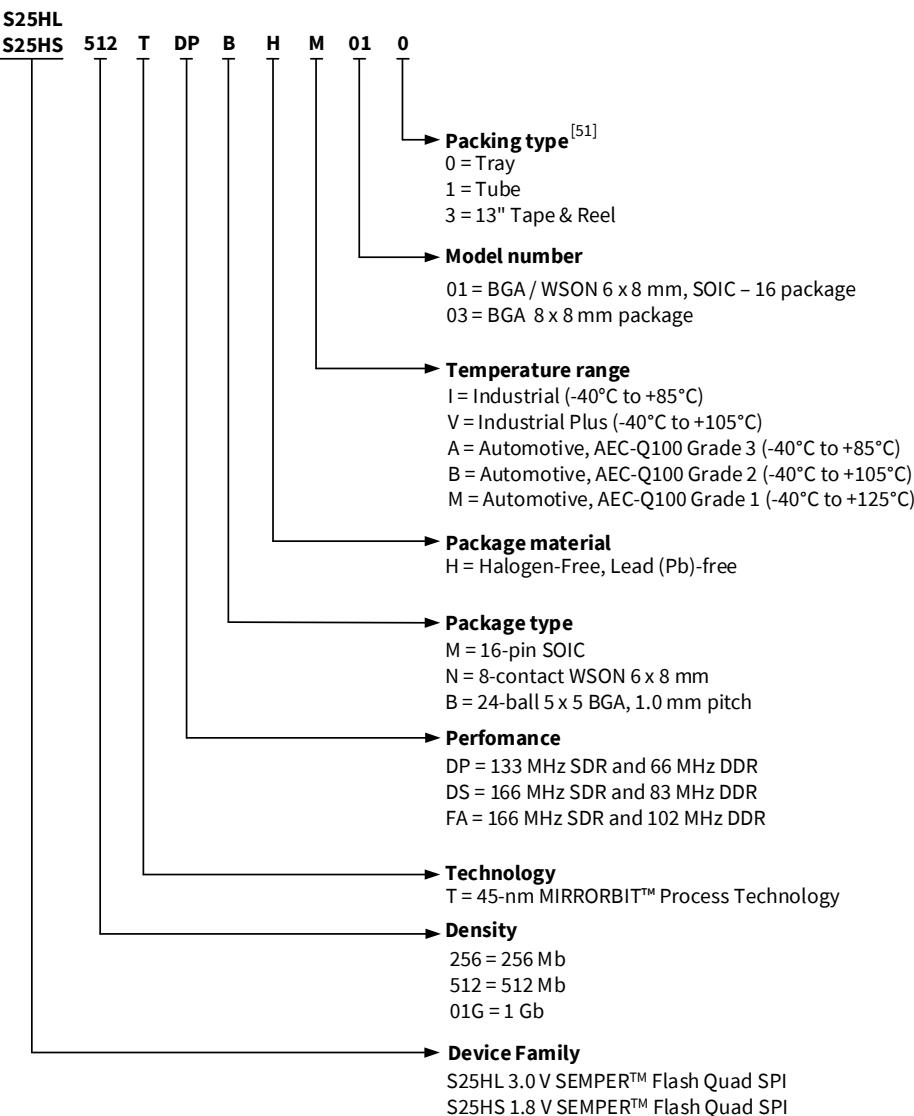

| <b>10 Package diagrams .....</b>                                          | <b>136</b> |

| <b>11 Ordering information .....</b>                                      | <b>140</b> |

| 11.1 Valid combinations — standard grade.....                             | 141        |

| 11.2 Valid combinations — automotive grade / AEC-Q100.....                | 142        |

| <b>Revision history .....</b>                                             | <b>144</b> |

Pinout and signal description

## 1 Pinout and signal description

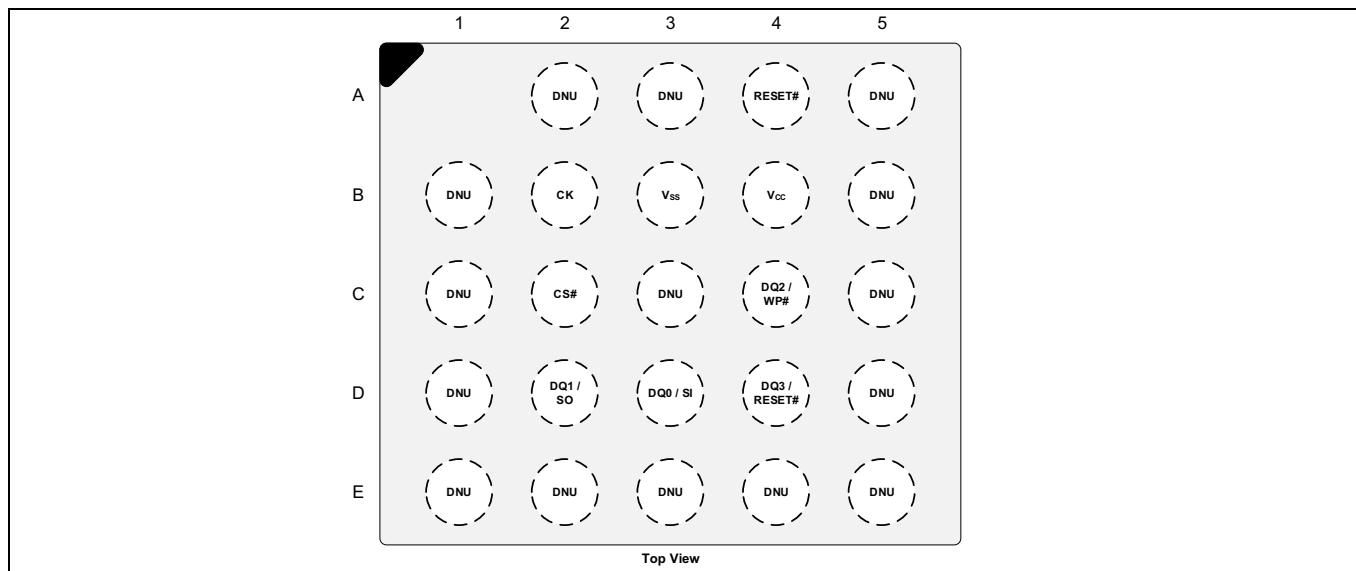

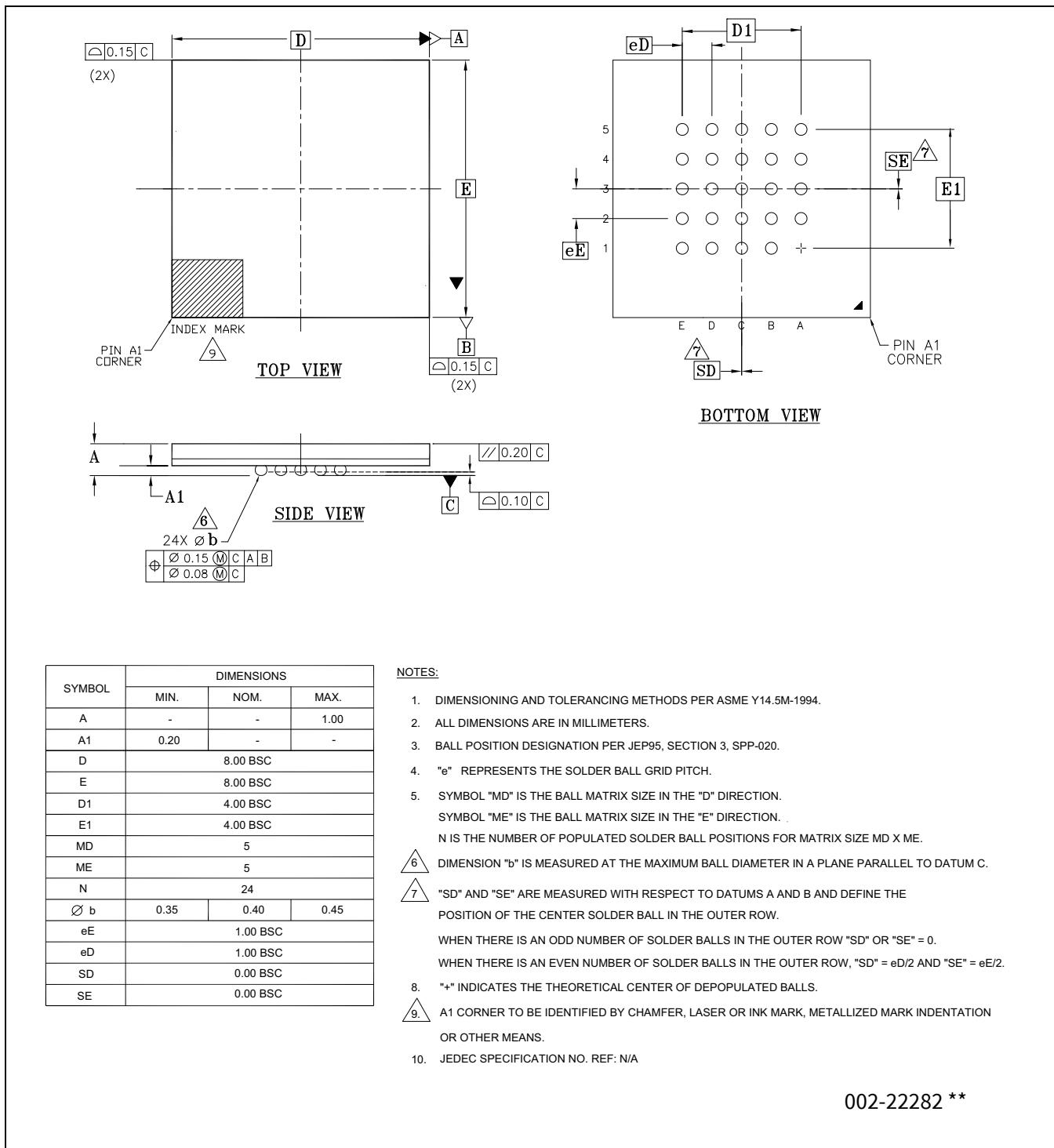

Figure 1 24-ball BGA pinout configuration<sup>[1]</sup>

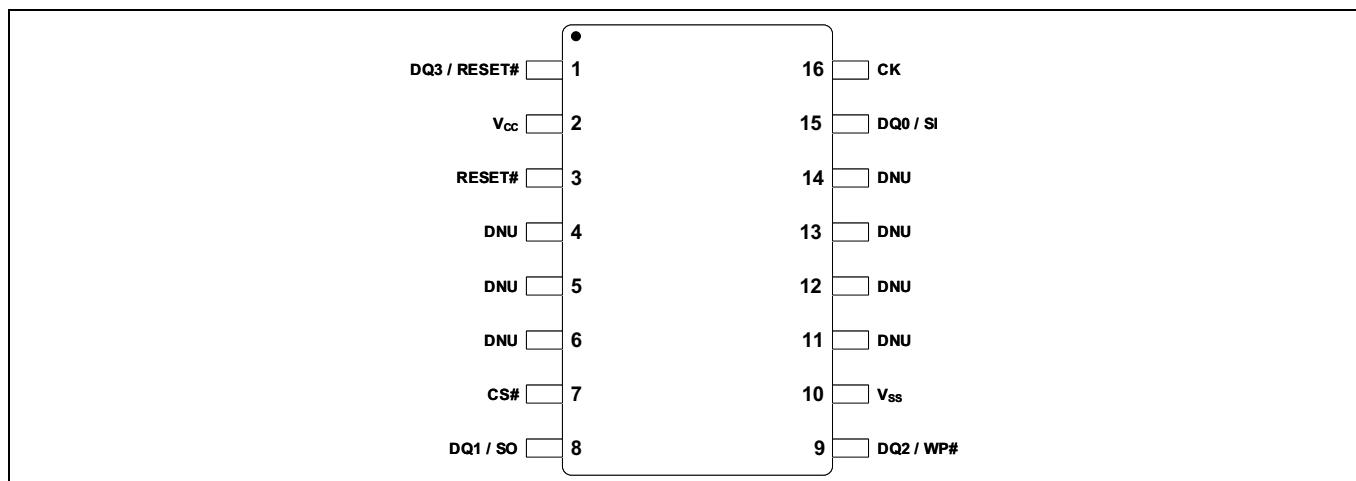

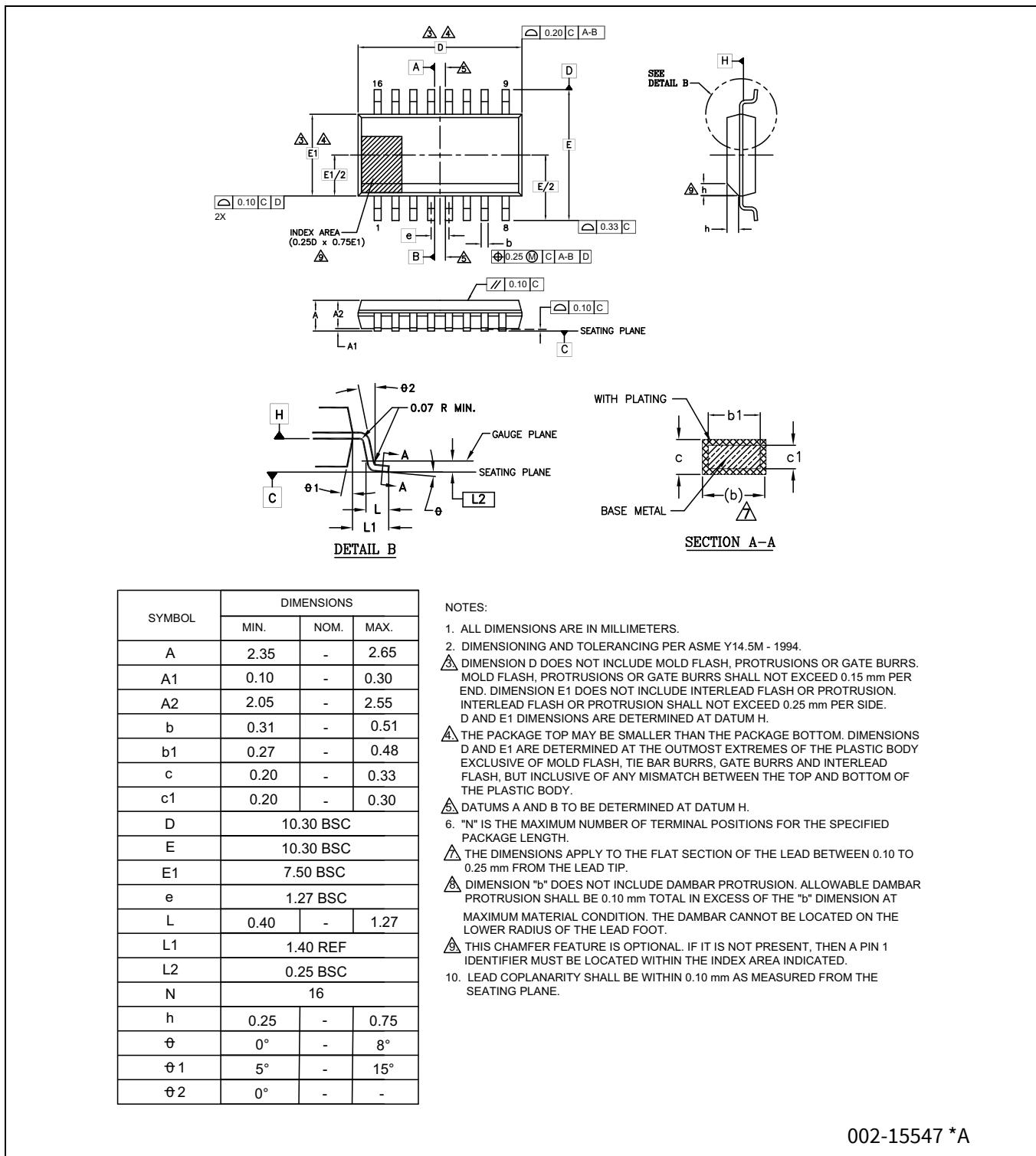

Figure 2 16-lead SOIC package (SO316), top view

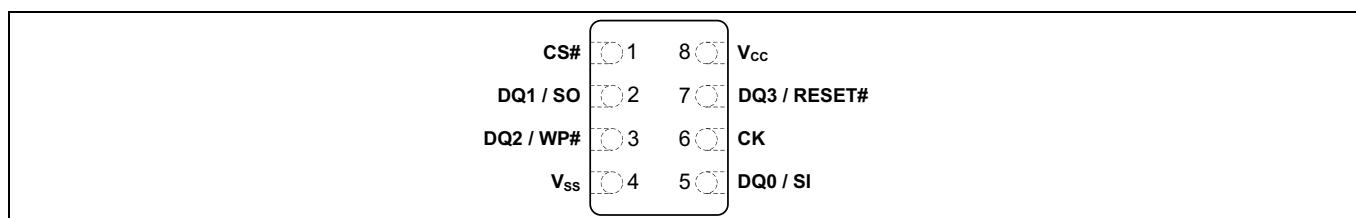

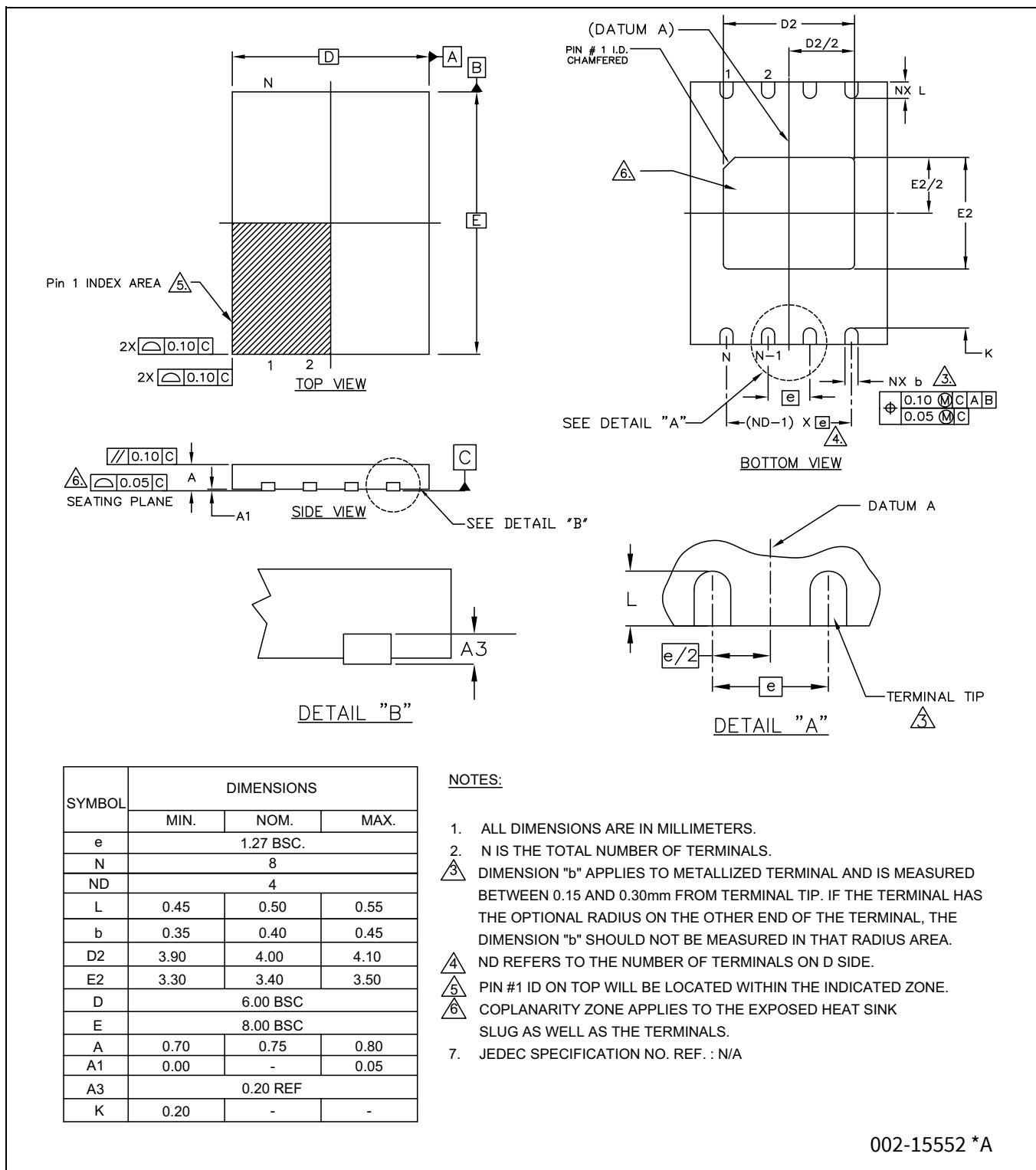

Figure 3 8-connector package (WSON 6 x 8), top view

### Note

1. Flash memory devices in BGA packages can be damaged if exposed to ultrasonic cleaning methods. The package, data integrity, or both may be compromised if the package body is exposed to temperatures above 150°C for prolonged periods of time.

**Table 1** Signal description

| Symbol          | Type                           | Mandatory / optional | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|--------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS#             | Input                          | Mandatory            | <b>Chip Select (CS#).</b> All bus transactions are initiated with a HIGH to LOW transition on CS# and terminated with a LOW to HIGH transition on CS#. Driving CS# LOW enables the device, placing it in the active mode. When CS# is driven HIGH, the device enters standby mode, unless an internal embedded operation is in progress. All other input pins are ignored and the output pins are put in high impedance state. On parts where the pin configuration offers a dedicated RESET# pin, it remains active when CS# is HIGH. |

| CK              |                                |                      | <b>Clock (CK).</b> Clock provides the timing of the serial interface. Transactions are latched on the rising edge of the clock. In SDR protocol, command, address and data inputs are latched on the rising edge of the clock, while data is output on the falling edge of the clock. In DDR protocol, command, address and data inputs are latched on both edges of the clock, and data is output on both edges of the clock.                                                                                                         |

| DQ0 / SI        |                                |                      | Serial Input (SI) for single SPI protocol<br><b>DQ0 Input/Output</b> for Dual or Quad SPI protocol                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DQ1 / SO        |                                |                      | Serial Output (SO) for single SPI protocol<br><b>DQ1 Input/Output</b> for Dual or Quad SPI protocol                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DQ2 / WP#       |                                |                      | Write Protect (WP#) for single and dual SPI protocol<br><b>DQ2 Input/Output</b> for Quad SPI protocol<br>The signal has an internal pull-up resistor and can be left unconnected in the host system if not used for Quad transactions or write protection. If write protection is enabled, the host system is required to drive WP# HIGH or LOW during write register transactions.                                                                                                                                                    |

| DQ3 / RESET#    | Input/Output<br>(weak Pull-up) | Optional             | <b>RESET#</b> for single and dual SPI protocol. This signal can be configured as RESET# when CS# is HIGH or Quad SPI protocol is disabled.<br><b>DQ3 Input/Output</b> for Quad SPI protocol<br>The signal has an internal pull-up resistor and can be left unconnected in the host system if not used for Quad SPI transactions or RESET#                                                                                                                                                                                              |

| RESET#          |                                |                      | <b>Hardware Reset (RESET#).</b> When LOW, the device will self initialize and return to the array read state. DQ[3:0] are placed into the high impedance state when RESET# is LOW. RESET# includes a weak pull-up, meaning, if RESET# is left unconnected it will be pulled up to the HIGH state on its own.                                                                                                                                                                                                                           |

| V <sub>CC</sub> | Power Supply                   | Mandatory            | Core Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>SS</sub> | Ground Supply                  |                      | Core Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DNU             | -                              | -                    | Do Not Use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## 2 Interface overview

### 2.1 General description

The Infineon SEMPER™ Flash with Quad SPI family of products are high-speed CMOS, MIRRORBIT™ NOR Flash devices. SEMPER™ Flash is designed for Functional Safety with development according to ISO 26262 standard to achieve ASIL-B compliance and ASIL-D readiness.

SEMPER™ Flash with Quad SPI devices support traditional SPI single bit serial input and output, optional two bit (Dual I/O or DIO) as well as four bit wide Quad I/O (QIO) and Quad Peripheral Interface (QPI) protocols. In addition, there are DDR read transactions for QIO and QPI that transfer address and read data on both edges of the clock.

Read operations from the device are burst oriented. Read transactions can be configured to use either a wrapped or linear burst. Wrapped bursts read from a single page whereas linear bursts can read the whole memory array.

The erased state of each memory bit is a logic 1. Programming changes a logic 1 (HIGH) to a logic 0 (LOW). Only an erase operation can change a memory bit from a 0 to a 1. An erase operation must be performed on a complete sector (4 KBs or 256 KBs).

SEMPER™ Flash provides a flexible sector architecture. The address space can be configured as either a uniform 256 KB sector array, or a hybrid configuration 1 where thirty-two 4 KB sectors are either grouped at the top or at the bottom while the remaining sectors are all 256 KB, or a hybrid configuration 2 where the thirty-two 4 KB sectors are equally split between the top and the bottom while the remaining sectors are all 256 KB.

The Page Programming Buffer used during a single programming operation is configurable to either 256 bytes or 512 bytes. The 512 byte option provides the highest programming throughput.

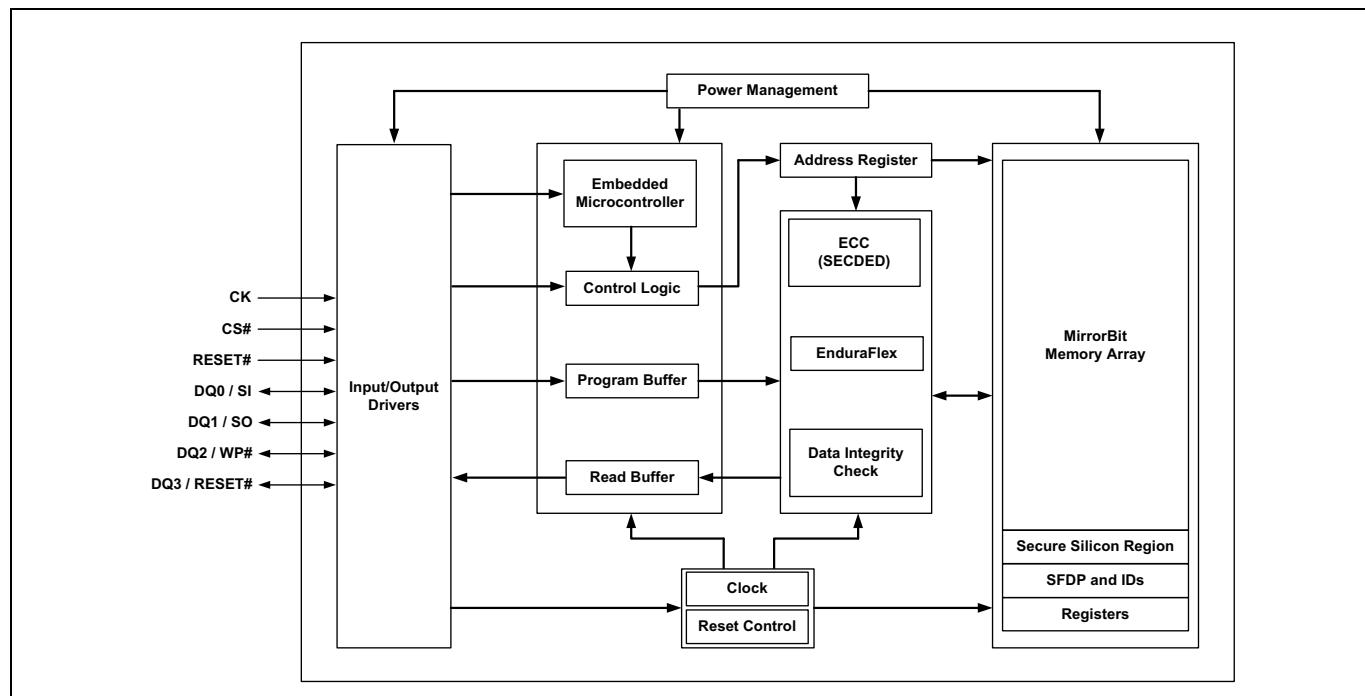

**Figure 4 Logic block diagram**

The SEMPER™ Flash with Quad SPI family consists of multiple densities with, 1.8 V and 3.0 V core and I/O voltage options.

## Interface overview

The device control logic is subdivided into two parallel operating sections: the Host Interface Controller (HIC) and the Embedded Algorithm Controller (EAC). The HIC monitors signal levels on the device inputs and drives outputs as needed to complete read, program, and write data transfers with the host system. The HIC delivers data from the currently entered address map on read transfers; places write transfer address and data information into the EAC command memory, and notifies the EAC of power transition, and write transfers. The EAC interrogates the command memory, after a program or write transfer, for legal command sequences and performs the related Embedded Algorithms.

Changing the nonvolatile data in the memory array requires a sequence of operations that are part of Embedded Algorithms (EA). The algorithms are managed entirely by the internal EAC. The main algorithms perform programming and erase of the main flash array data. The host system writes command codes to the flash device. The EAC receives the command, performs all the necessary steps to complete the transaction, and provides status information during the progress of an EA.

Executing code directly from flash memory is often called Execute-In-Place (XIP). By using XIP with SEMPER™ Flash devices at the higher clock rates with Quad or DDR Quad SPI transactions, the data transfer rate can match or exceed traditional parallel or asynchronous NOR Flash memories while reducing signal count dramatically.

Infineon Endurance Flex architecture provides system designers the ability to customize the NOR Flash endurance and retention for their specific application. The host defines partitions for high endurance or long retention, providing up to 1+ million cycles or 25 years of data retention.

The SEMPER™ Flash with Quad SPI device supports error detection and correction by generating an embedded Hamming error correction code during memory array programming. This ECC code is then used for single-bit and double-bit error detection and single-bit correction during read.

The SEMPER™ Flash with Quad SPI device has built-in diagnostic features providing the host system with the device status.

- Program and Erase Operation: Reporting of program or erase success, failure and suspend status

- Error Detection and Correction: 1-bit and/or 2-bit error status with address trapping and error count

- Data Integrity Check: Error detection over memory array contents

- SafeBoot: Reporting of proper flash device initialization and configuration corruption recovery

- Sector Erase Status: Reporting of erase success or failure status per sector

- Sector Erase Counter: Counts the number of erase cycles per sector

## 2.2 Signal protocols

### 2.2.1 SEMPER™ Flash with Quad SPI clock modes

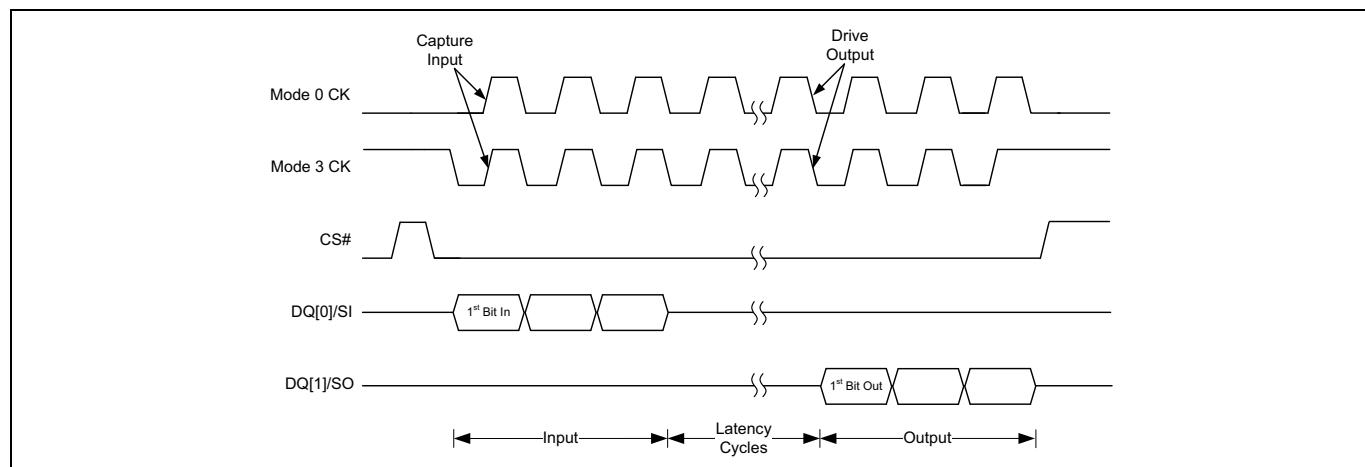

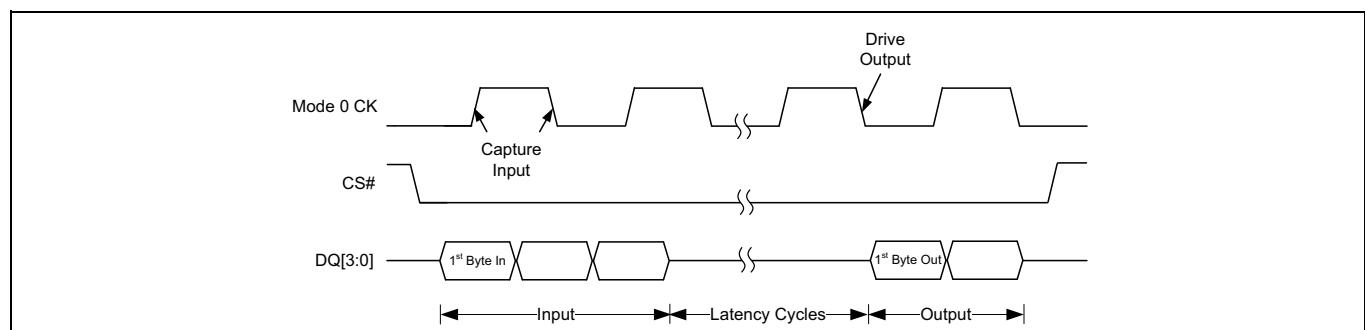

The SEMPER™ Flash with Quad SPI device can be driven by an embedded microcontroller (bus master) in either of the following two clocking modes:

- **Mode 0** with Clock Polarity LOW at the fall of CS# and staying LOW until it goes HIGH at capture input.

- **Mode 3** with Clock Polarity HIGH at the fall of CS# then going LOW to HIGH at capture input.

For these two modes, data is latched into the device on the rising edge of the CK signal in SDR protocol and both edges of the CK signal in DDR protocol. The output data is available on the falling edge of the CK clock signal. For DDR protocol, Mode 3 is not supported.

The difference between the two modes is the clock polarity when the bus master is in Standby mode and not transferring any data.

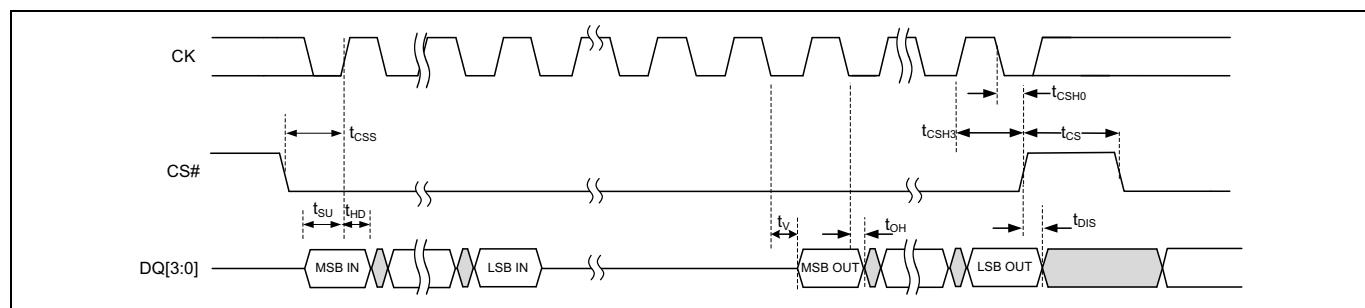

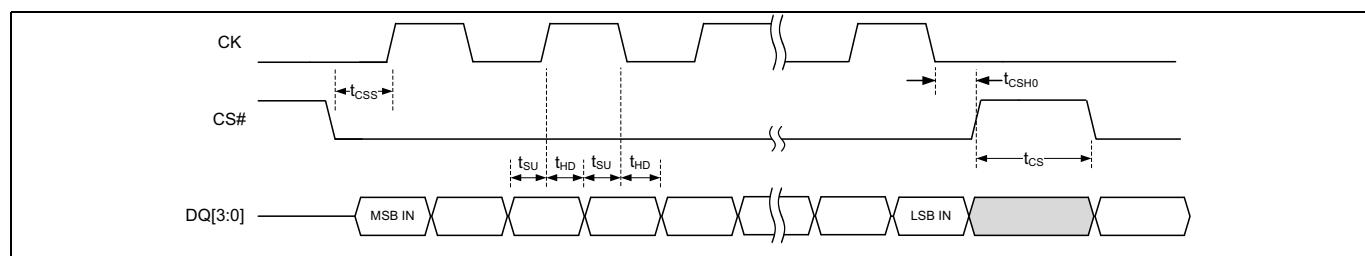

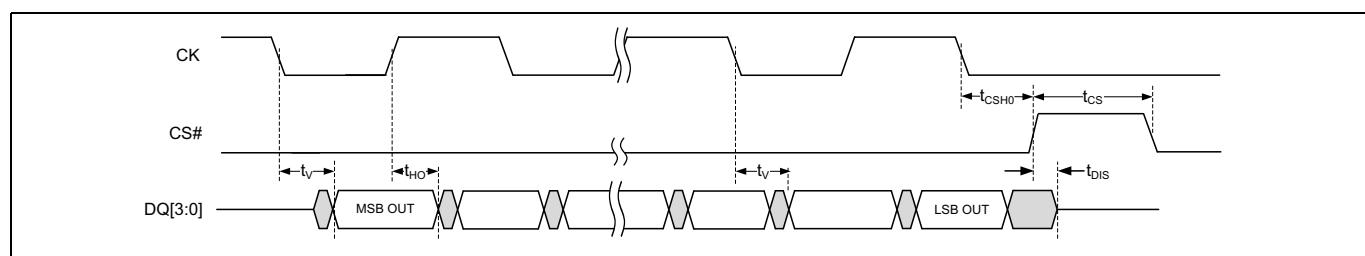

**Figure 5** SPI SDR mode support

**Figure 6** SPI DDR mode support

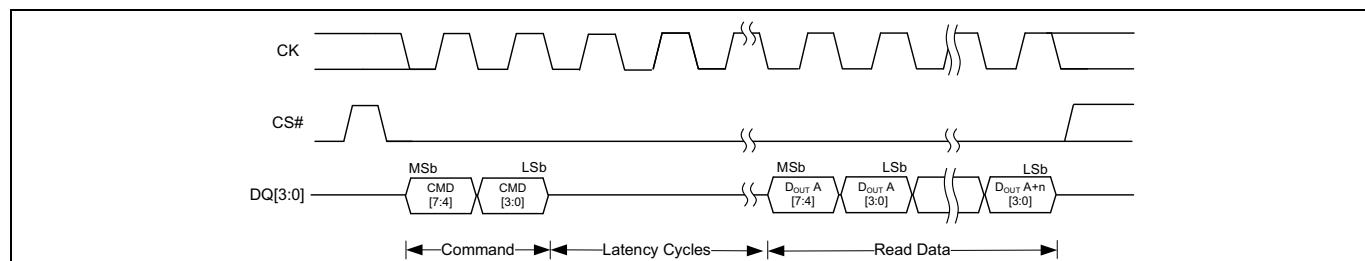

## 2.3 Transaction protocol

### Transaction

- During the time that CS# is active (LOW) the clock signal (CK) is toggled while command information is first transferred on the data (DQ) signals followed by address and data from the host to the flash device. The clock continues to toggle during the transfer of read data from the flash device to the host or write data from the host to the flash device. When the host has transferred the desired amount of data, the host drives the CS# inactive (HIGH). The period during which CS# is active is called a transaction on the bus.

- While CS# is inactive, the CK is not required to toggle.

- The command transfer occurs at the beginning of every transaction. The address, latency cycles, and data transfer phases are optional and their presence depends on the protocol mode or command transferred.

### Transaction capture

- CK marks the transfer of each bit or group of bits between the host and memory. Command, address and write data bits transfer occurs on CK rising edge in SDR transactions, or on every CK edge, in DDR transactions.

**Note:** All attempts to read the flash memory array during a program or erase (embedded operations) are ignored. The embedded operation will continue to execute without any effect. A very limited set of commands are accepted during an embedded operation. These are discussed in “[Suspend and resume embedded operation](#)” on page 64.

### Protocol terminology

- The number of DQ signals used during the transaction, depends on the current protocol mode or command transferred. The latency cycles do not use the DQ signals for information transfer. The protocol mode options are described by the data rate and the DQ width (number of DQ signals) used during the command, address, and data phases in the following format:

WR-WR-WR, where:

- The first WR is the command bit width and rate.

- The second WR is the address bit width and rate.

- The third WR is the data bit width and rate.

- The bit width value may be 1, 2 or 4. R has a value of S for SDR or D for DDR. SDR has the same transfer value during the rising and falling edge of a clock cycle. DDR can have different transfer values during the rising and falling edges of each clock.

- Examples:

- 1S-1S-1S means that the command is 1 bit wide SDR, the address is 1 bit wide SDR, and the data is one bit wide SDR.

- 4S-4D-4D means that the command is 4 bits wide SDR, address, and data transfers are 4 bits wide DDR.

### Protocols definition

- Protocol Modes defined for the SEMPER™ Flash with Quad SPI:

- 1S-1S-1S: One DQ signal used during command transfer, address transfer, and data transfer. All phases are SDR.

- 1S-2S-2S: One DQ signal used during command transfer, two DQ signals used during address transfer, and data transfer. All phases are SDR.

- 1S-1S-4S: One DQ signal used during command and address transfer, four DQ signals used during data transfer. All phases are SDR.

- 1S-4S-4S: One DQ signal used during command transfer, four DQ signals used during address transfer, and data transfer. All phases are SDR.

- 1S-4D-4D: One DQ signal used during command transfer at SDR, four DQ signals used during address and data transfer at DDR.

## Interface overview

- 4S-4S-4S: Four DQ signals used during command transfer, address transfer, and data transfer. All phases are SDR.

- 4S-4D-4D: Four DQ signals used during command transfer at SDR, four DQ signals used during address and data transfer at DDR.

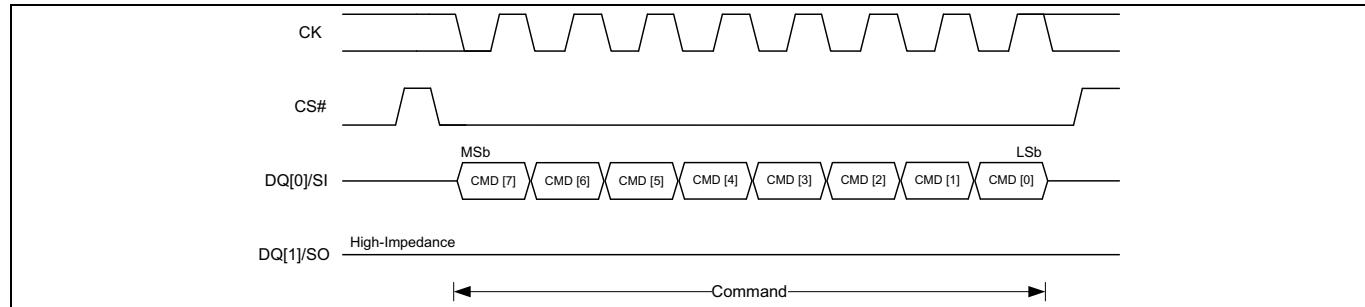

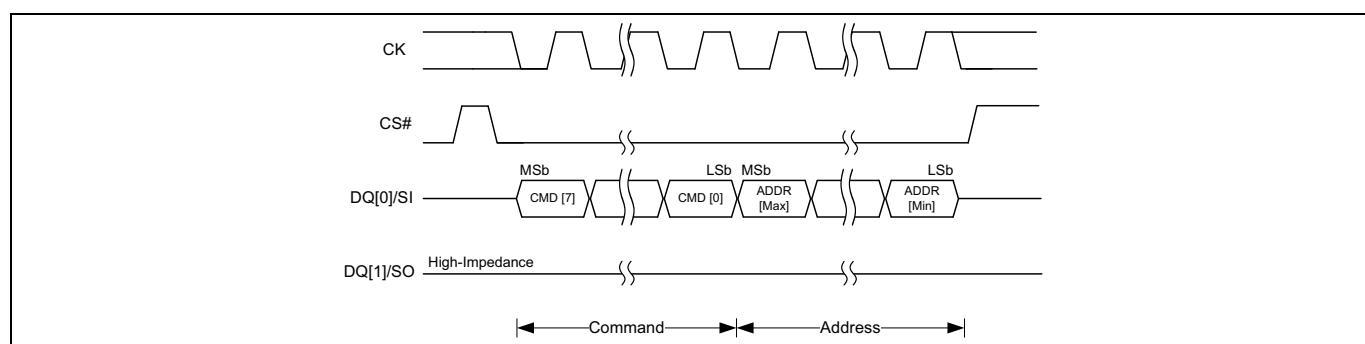

- Each transaction begins with an 8-bit (1-byte) command. The command selects the type of information transfer or device operation to be performed.

- All protocols supports 3 or 4-byte addressing.

### **1S-1S-1S protocol (single input/output, SIO)**

- The 1S-1S-1S mode is the preferred default protocol following Power-on-Reset (POR), but flash devices can be configured to reset into the Quad mode.

- This protocol uses DQ[0]/SI to transfer information from host to flash device and DQ[1]/SO to transfer information from flash device to host. On each DQ, information is placed on the DQ line in Most Significant bit (MSb) to Least Significant bit (LSb) order within each byte. Sequential address bytes are transferred in highest order to lowest order sequence. Sequential data bytes are transferred in lowest address to highest address order.

- In 1S-1S-1S, DQ[3:2] are not used for data transfer period. DQ[2] can be used as a WP# and DQ[3] can be used as a RESET# input. Otherwise, the DQ[3:2] signals will be high impedance.

### **1S-2S-2S protocol (dual input/output, DIO)**

- This protocol uses DQ[1:0] signals. The 8-bit command placed on the DQ[0] in MSb to LSb order. The LSb of address byte is placed on DQ[0] with next order bit on DQ[1] signal and so on. Sequential address bytes are transferred in highest order to lowest order sequence. Sequential data bytes in SDR are transferred in lowest address to highest address order.

- In 1S-2S-2S, DQ[3:2] are not used for data transfer period. DQ[2] can be used as a WP# and DQ[3] can be used as a RESET# input. Otherwise, the DQ[3:2] signals will be high impedance.

### **1S-1S-4S protocol (quad output read, QOR)**

- This protocol uses DQ[3:0] signals. The 8-bit command and address placed on the DQ[0] in MSb to LSb order. Sequential data bytes in SDR are transferred in lowest address to highest address order.

### **1S-4S-4S and 1S-4D-4D protocol (quad input/output, QIO)**

- This protocol uses DQ[3:0] signals. The 8-bit command placed on the DQ[0] in MSb to LSb order. The LSb of address byte is placed on DQ[0] with each higher order bit on the successively higher numbered DQ signals. Sequential address bytes are transferred in highest order to lowest order sequence. Sequential data bytes in SDR are transferred in lowest address to highest address order. Sequential data bytes in DDR are transferred only in byte pairs (words) where the byte order depends on the order in which the bytes are written or programmed in that protocol mode. Sequential data bytes are transferred in lowest address to highest address order.

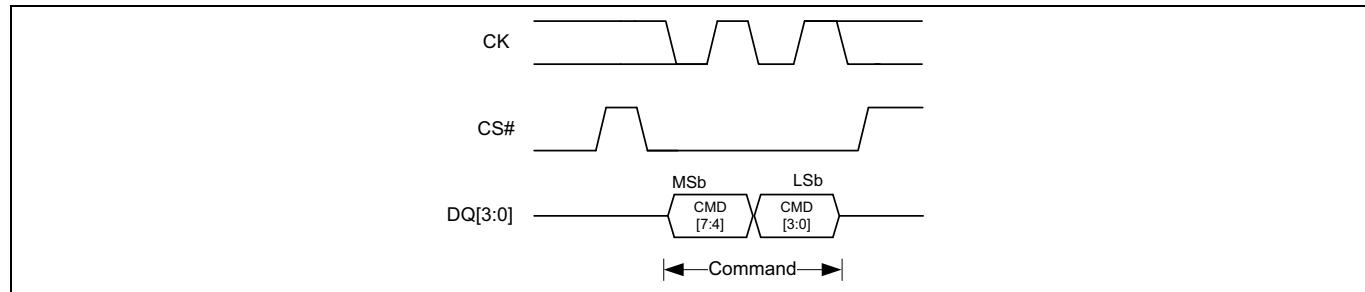

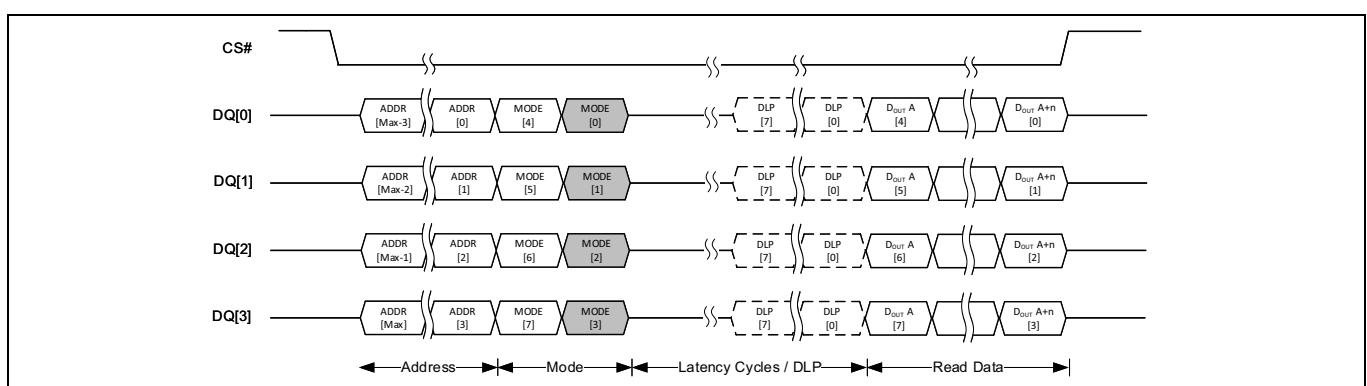

### **4S-4S-4S and 4S-4D-4D protocol (quad peripheral interface, QPI)**

- This protocol uses DQ[3:0] signals. The LSb of each byte is placed on DQ[0] with each higher order bit on the successively higher numbered DQ signals. Sequential address bytes are transferred in highest order to lowest order sequence. Sequential data bytes in SDR are transferred in lowest address to highest address order. Sequential data bytes in DDR are transferred only in byte pairs (words) where the byte order depends on the order in which the bytes are written or programmed in that protocol mode. Sequential data bytes are transferred in lowest address to highest address order. **“Serial peripheral interface (SPI, 1S-1S-1S)”** on page 15 through **“Quad peripheral interface (QPI, 4S-4S-4S and 4S-4D-4D)”** on page 20 show all transaction formats by protocol mode.

Interface overview

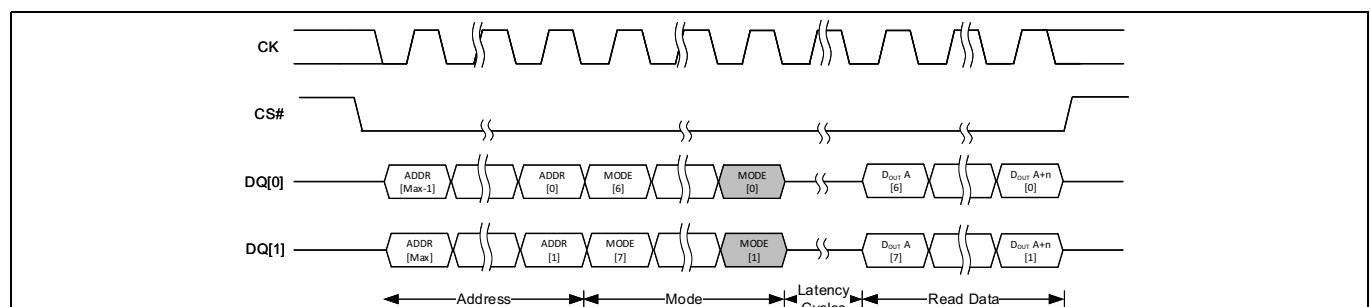

### 2.3.1 Serial peripheral interface (SPI, 1S-1S-1S)

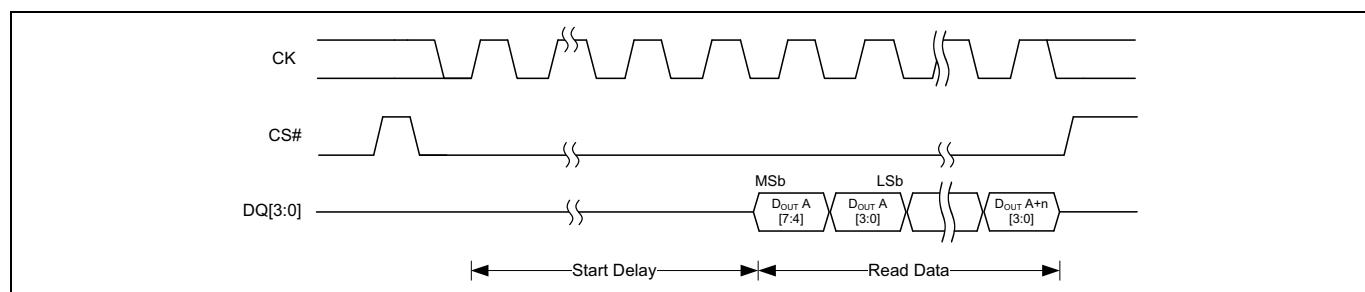

**Figure 7** SPI transaction with command input

**Figure 8** SPI transaction with command and address input

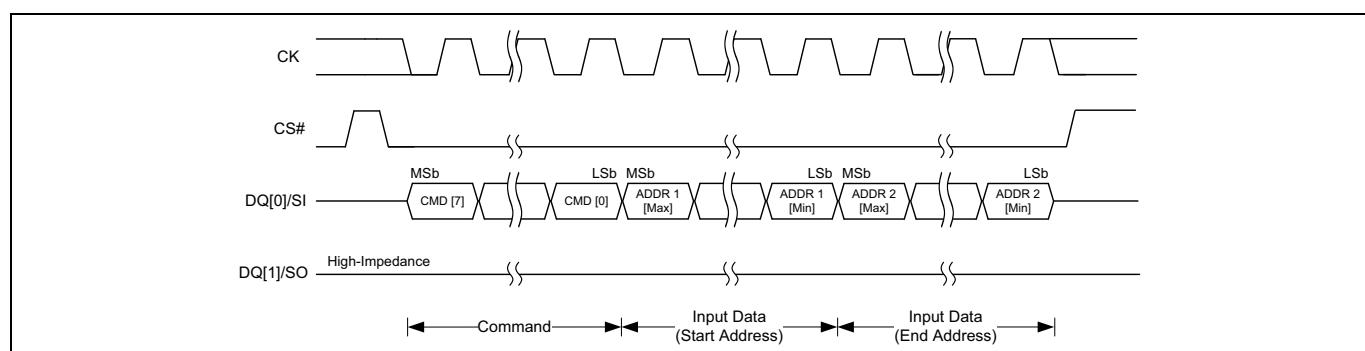

**Figure 9** SPI transaction with command and two input addresses

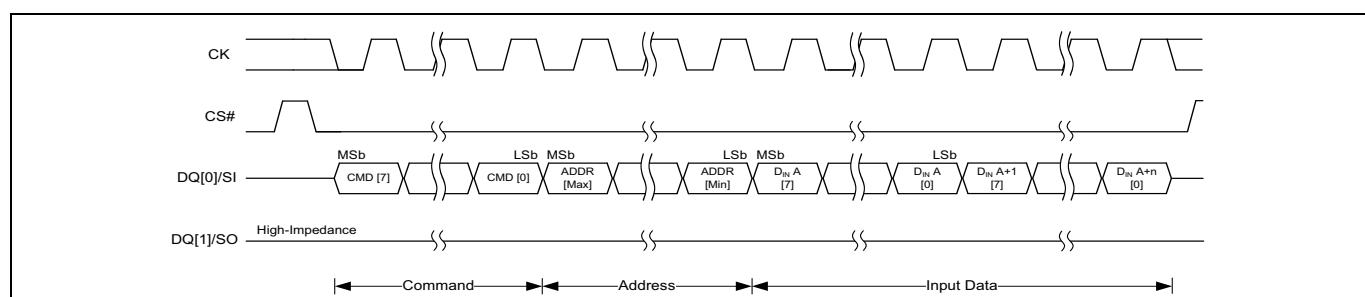

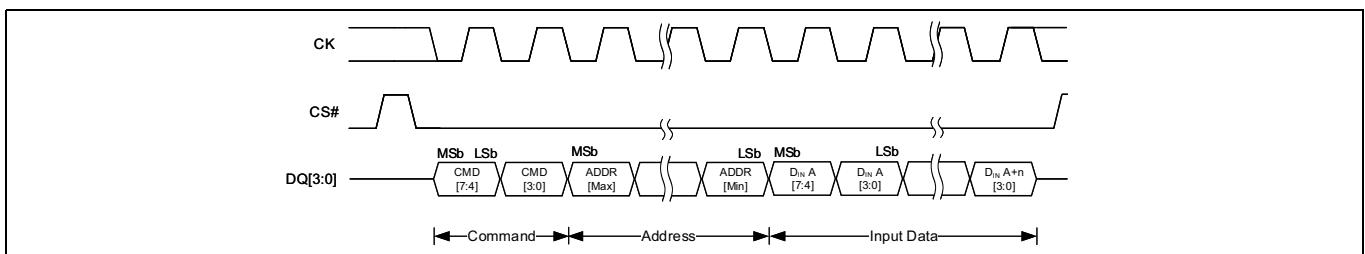

**Figure 10** SPI program transaction with command, address, and data input

Interface overview

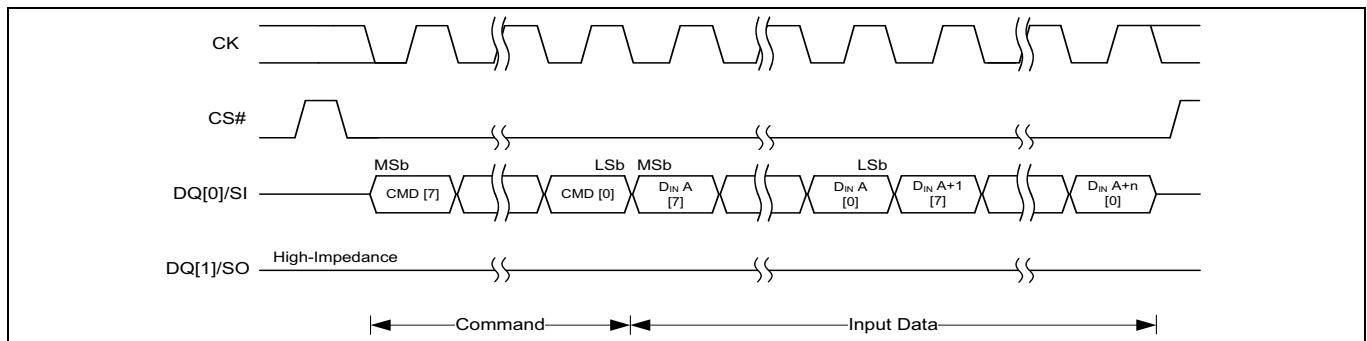

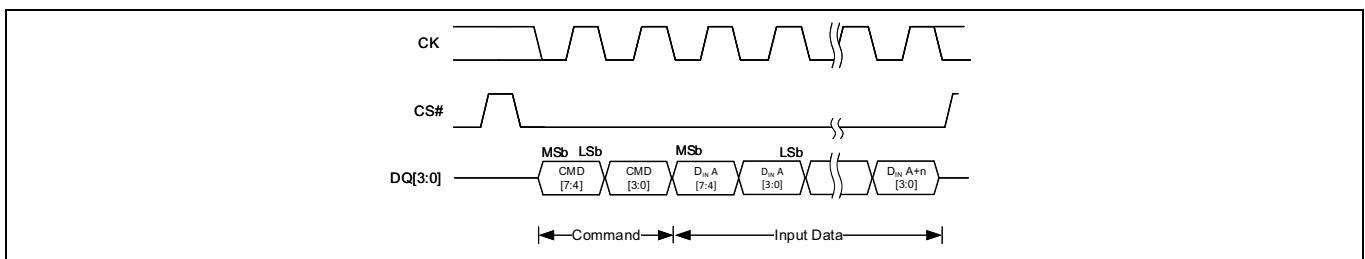

Figure 11 SPI program transaction with command and data input

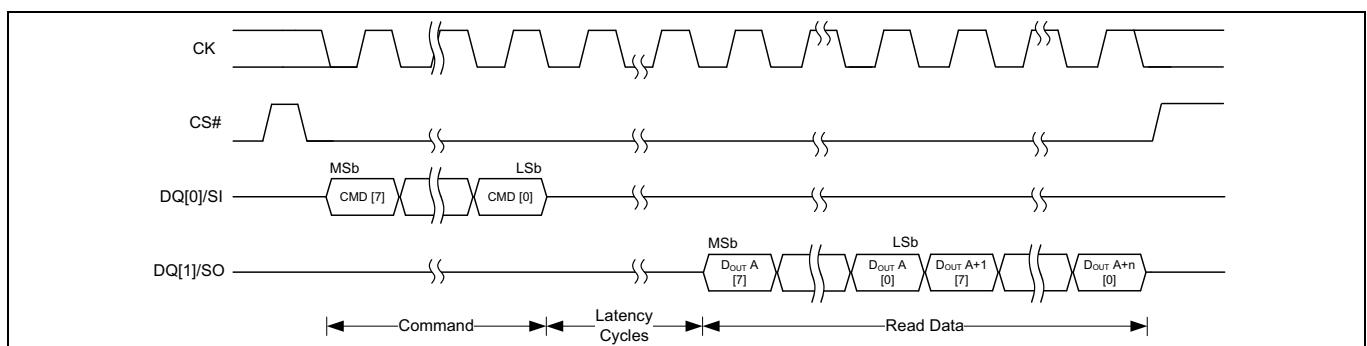

Figure 12 SPI read transaction with command input (output latency)<sup>[2, 3]</sup>

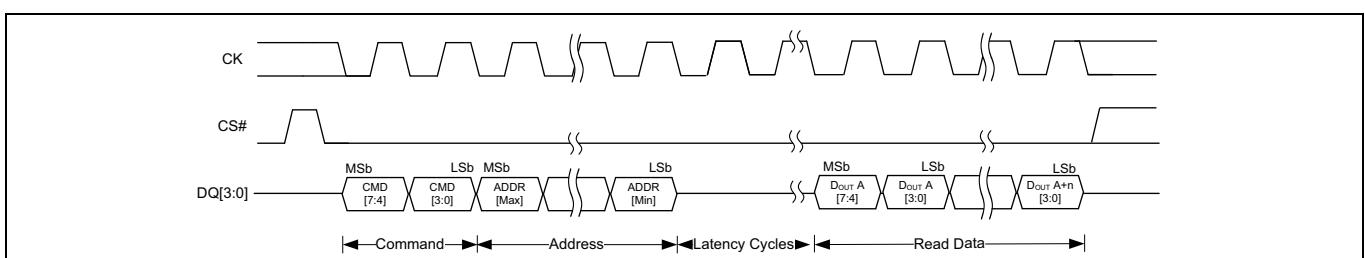

Figure 13 SPI read transaction with command and address input (output latency)<sup>[4]</sup>

**Notes**

2. In case of Status Register 1 and 2, Read Byte data out is the updated status.

3. In case of Data Learning Pattern Read, each byte outputs the DLP.

4. In case of RDAY2\_4\_0 transaction, the host must provide the mode bits.

Interface overview

**Figure 14 SPI read transaction with command and address input (no output latency)**

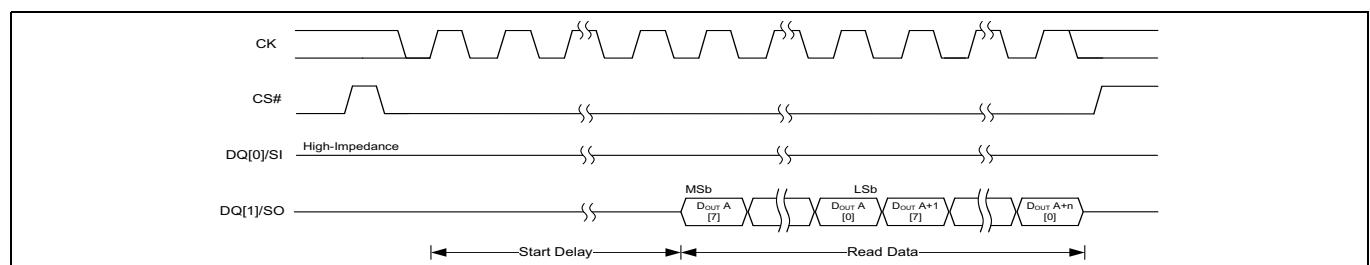

**Figure 15 SPI transaction with output data sequence (AutoBoot)**

### 2.3.2 Dual IO SPI (DIO, 1S-2S-2S)

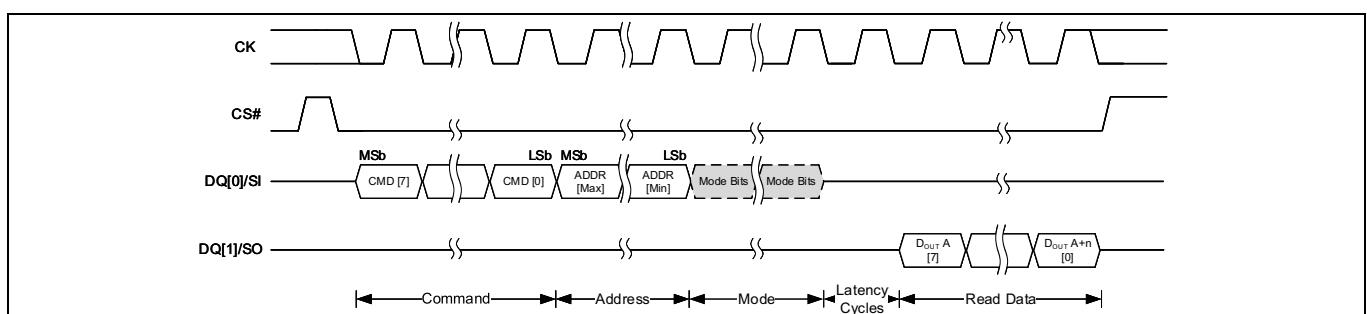

**Figure 16 DIO read transaction with command, address, and mode input (output latency)**

**Figure 17 DIO continuous read transaction with address and mode input (output latency)**

Interface overview

### 2.3.3 QUAD output read SPI (QOR, 1S-1S-4S)

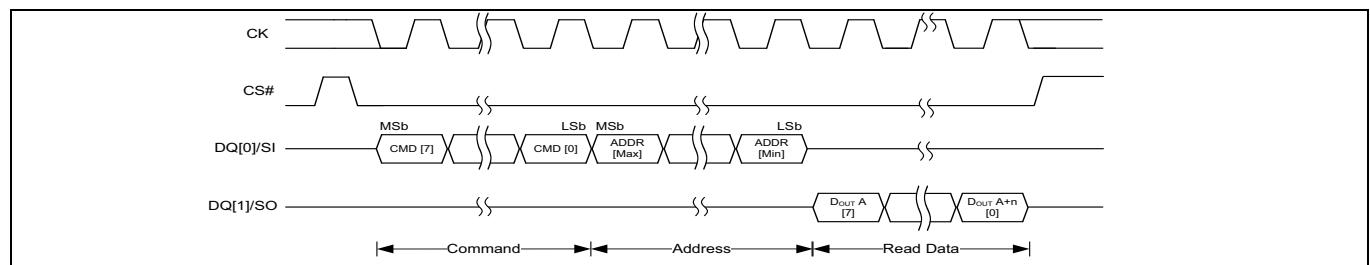

Figure 18 QOR SDR read transaction with command, address, and mode input (output latency)

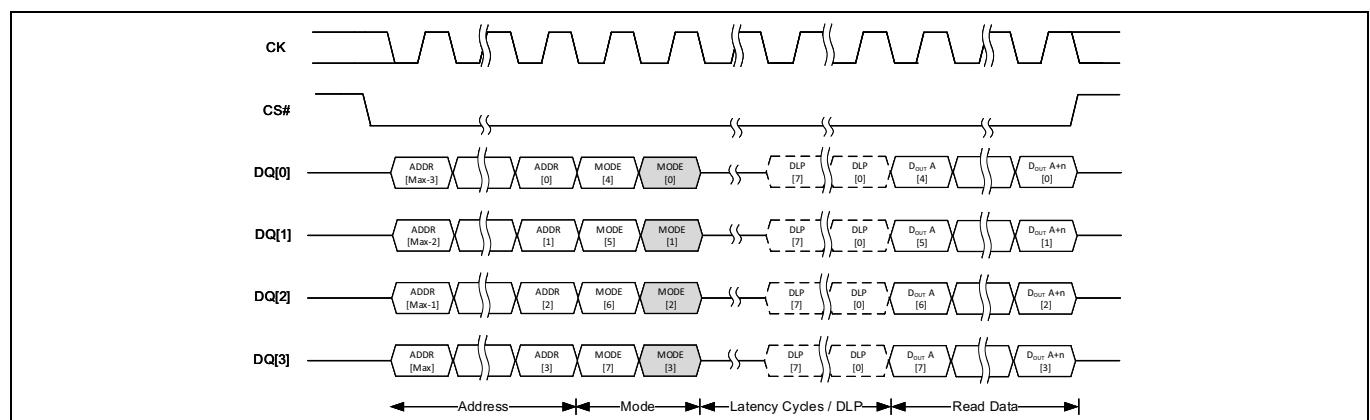

### 2.3.4 QUAD IO SPI (QIO, 1S-4S-4S, 1S-4D-4D)

Figure 19 QIO SDR read transaction with command, address, and mode input (output latency)<sup>[5]</sup>

Figure 20 QIO SDR continuous read transaction with address and mode input (output latency)<sup>[5]</sup>

#### Note

5. The gray bits data is don't care.

## Interface overview

Figure 21 QIO DDR read transaction with command, address, and mode input (output latency)

Figure 22 QIO DDR continuous read transaction with address and mode input (output latency)

Figure 23 Quad ID read transaction with command input (output latency)

Interface overview

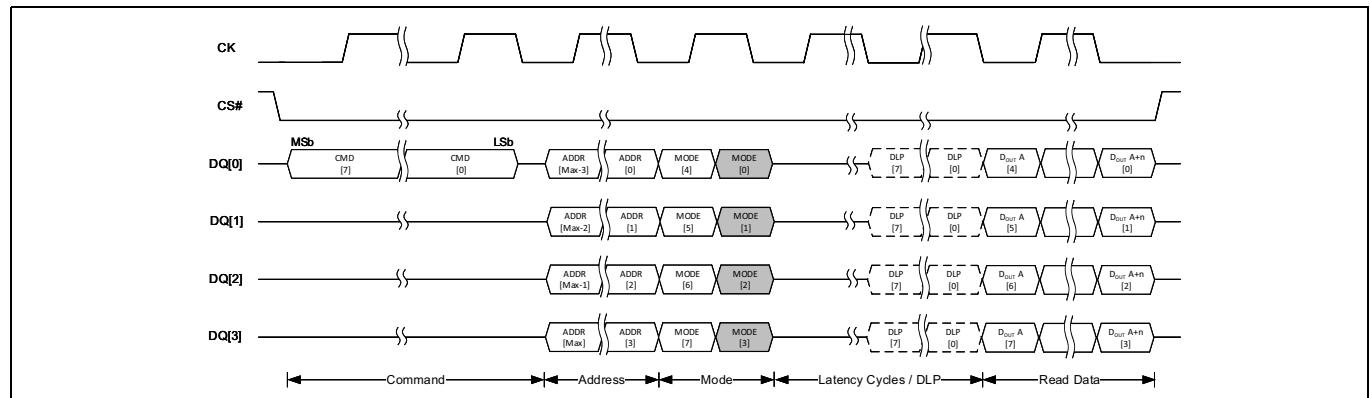

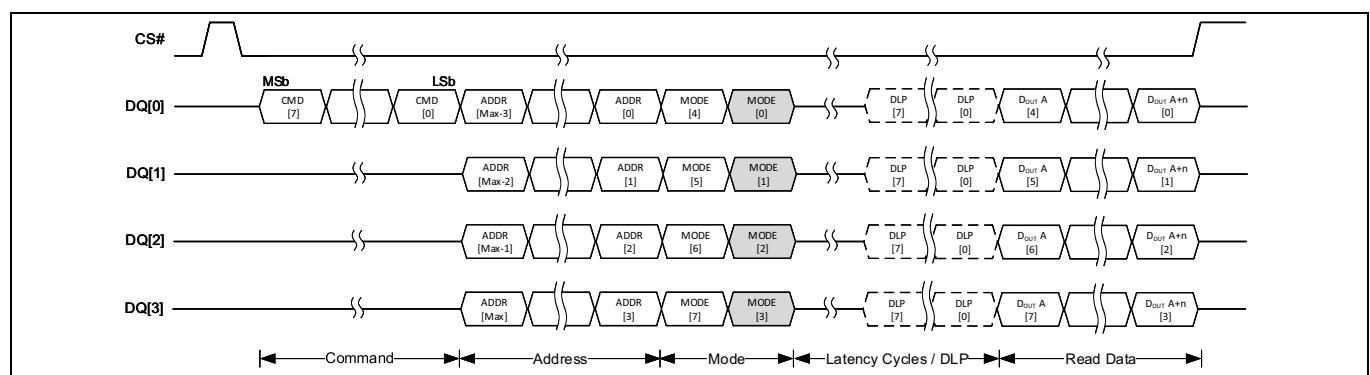

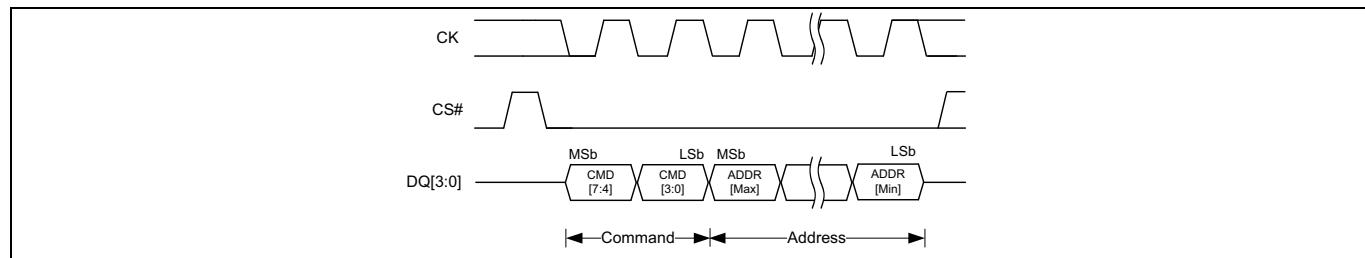

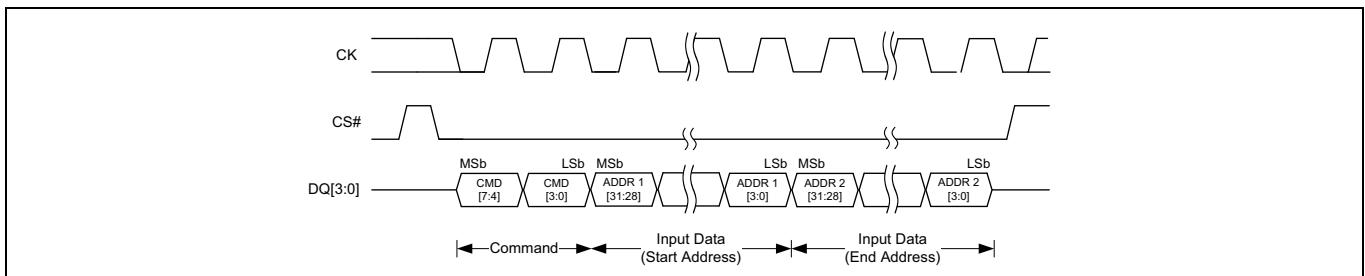

### 2.3.5 Quad peripheral interface (QPI, 4S-4S-4S and 4S-4D-4D)

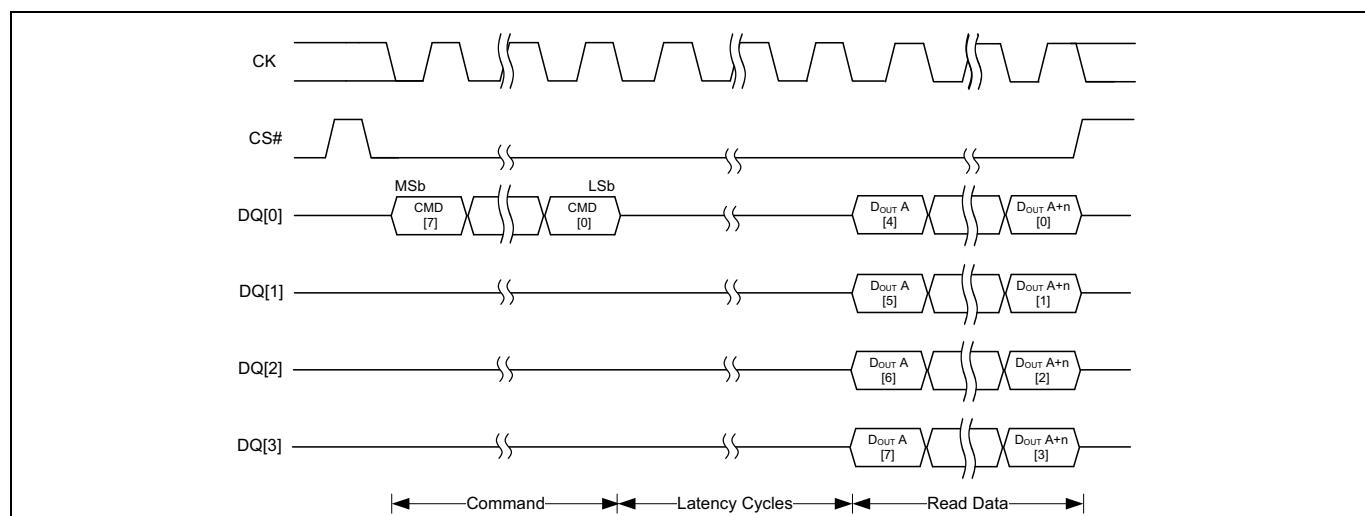

**Figure 24** QPI SDR transaction with command input

**Figure 25** QPI transaction with output data sequence (AutoBoot)

**Figure 26** QPI SDR transaction with command and address input

**Figure 27** QPI SDR read transaction with command input (output latency)

Interface overview

**Figure 28 QPI SDR transaction with command and two addresses input**

**Figure 29 QPI SDR transaction with command and data input**

**Figure 30 QPI SDR program transaction with command, address, and data input**

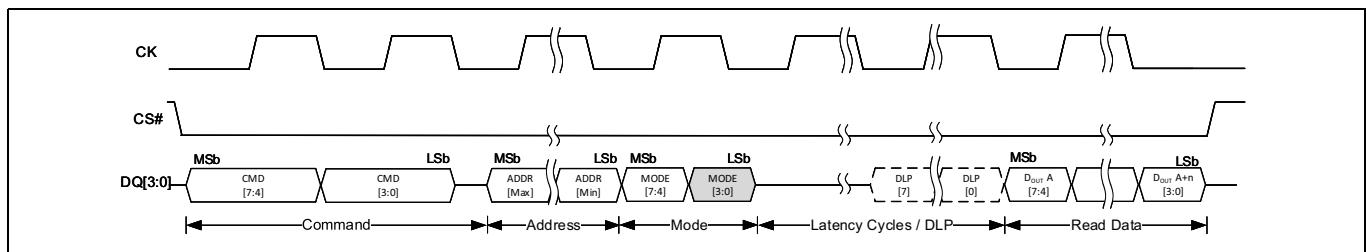

**Figure 31 QPI SDR read transaction with command and address input (output latency)**

Interface overview

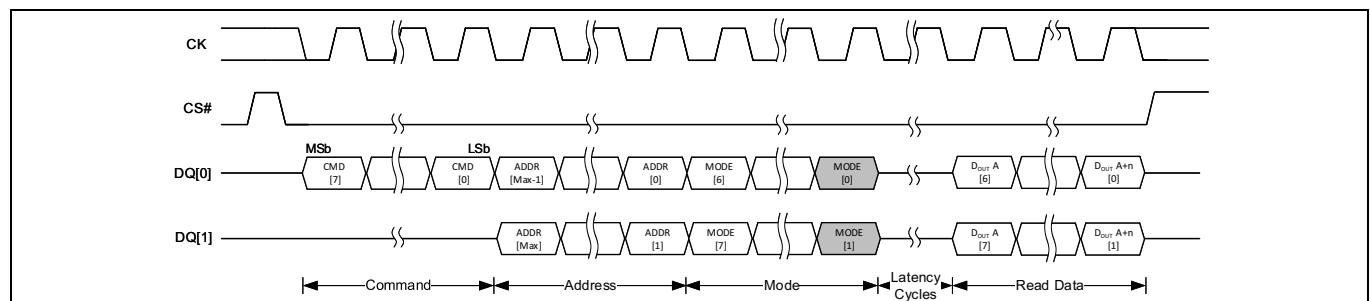

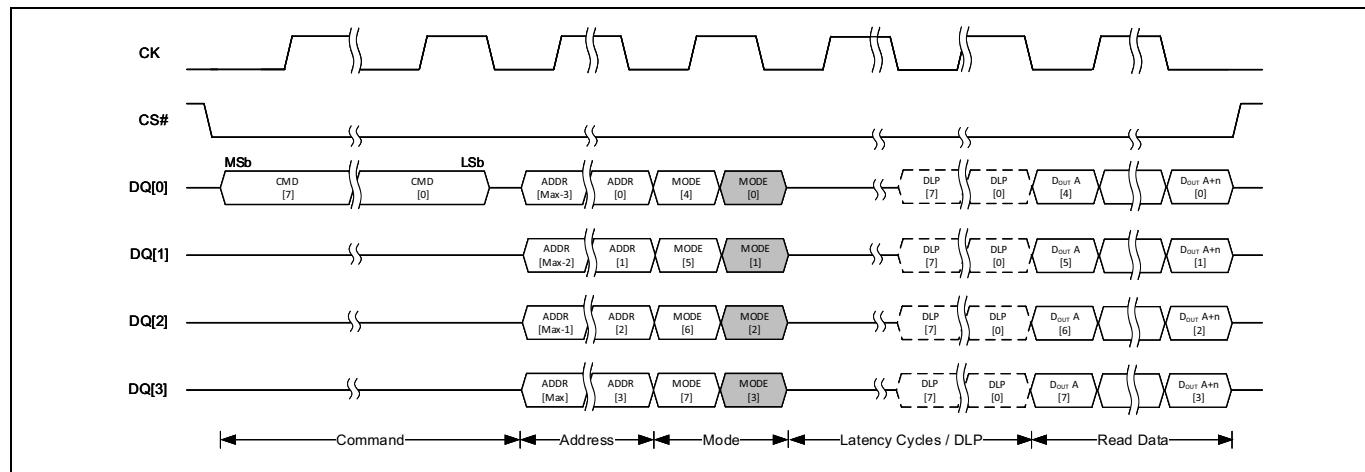

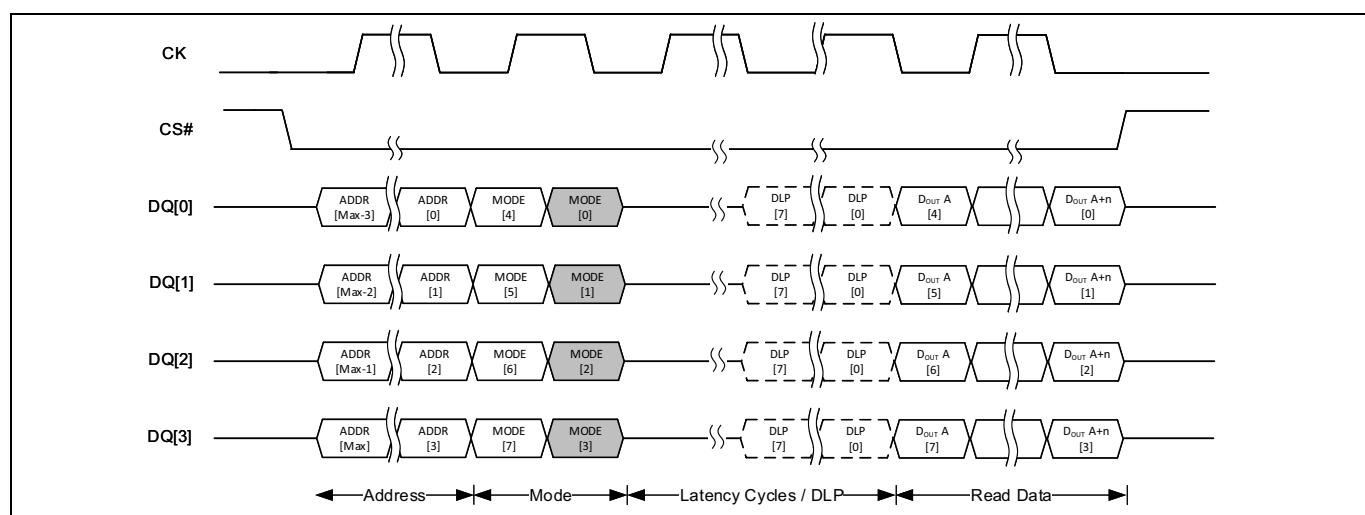

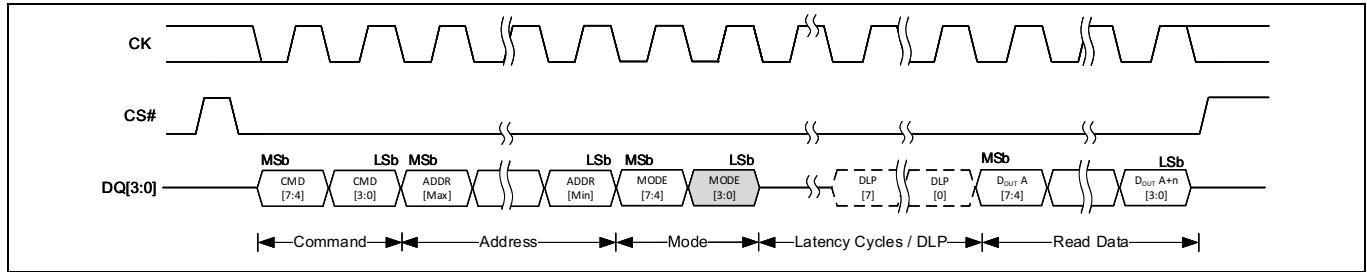

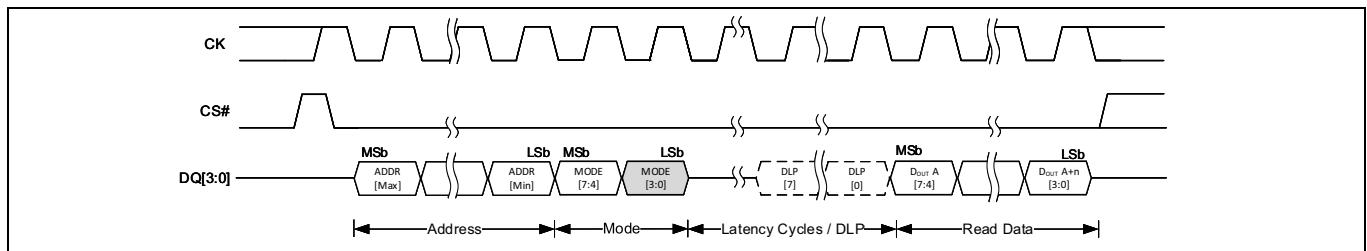

Figure 32 QPI SDR read transaction with command, address, and mode input (output latency)<sup>[6]</sup>

Figure 33 QPI SDR continuous read transaction with address and mode input (output latency)<sup>[6]</sup>

Figure 34 QPI DDR read transaction with command, address, and mode input (output latency)<sup>[6]</sup>

Figure 35 QPI DDR continuous read transaction with address and mode input (output latency)<sup>[6]</sup>

### Note

6. The gray bits data is don't care.

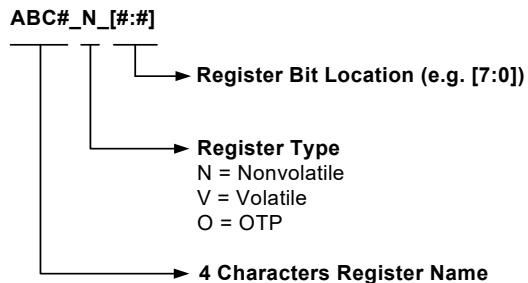

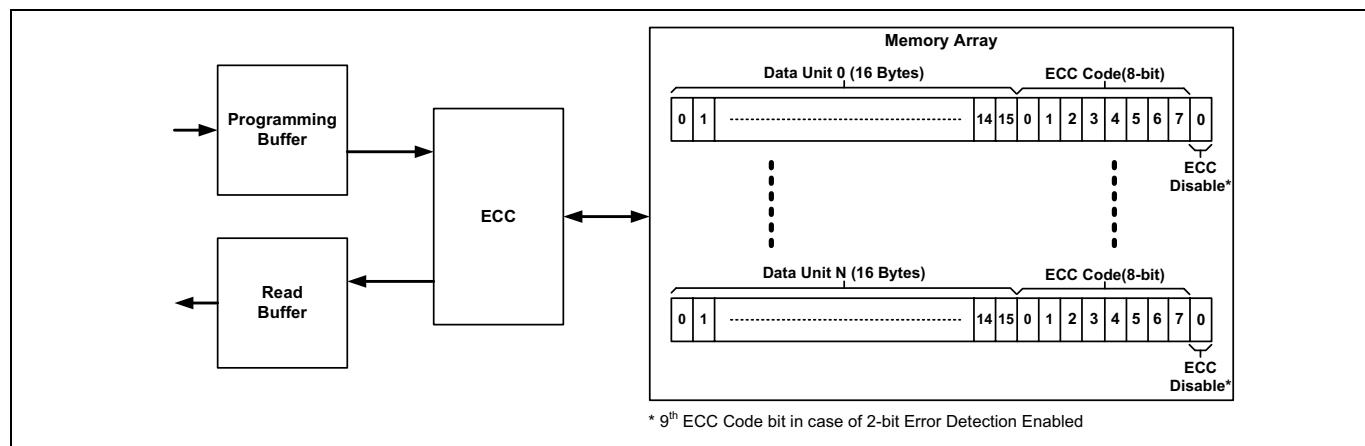

## 2.4 Register naming convention

**Figure 36 Register naming convention**

**Figure 37 Register bit naming convention**

## 2.5 Transaction naming convention

**Figure 38 Transaction naming convention**

Address space maps

### 3 Address space maps

The HL-T/HS-T family supports 24-bit as well as 32-bit (4-Byte) addresses, to enable 256 Mb or 512 Mb or 1 Gb density devices. 4-Byte addresses allow direct addressing of up to 4 GB (32 Gb) address space. The address byte option can be changed by writing the respective configuration registers OR there are separate transactions also available to enter (EN4BA\_0\_0) and exit (EX4BA\_0\_0) the 4-byte address mode.

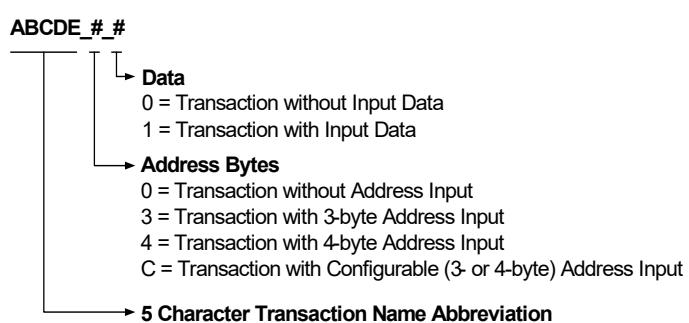

Besides flash memory array, HL-T/HS-T family includes separate address spaces for Manufacturer ID, Device ID, Unique ID, Serial Flash Discoverable Parameters (SFDP), Secure Silicon Region (SSR), and Registers.

**Figure 39** HL-T/HS-T address space map overview

#### 3.1 SEMPER™ Flash memory array

The main flash array is divided into units called physical sectors.

The HL-T/HS-T family sector architecture supports the following options:

- 256 Mb, 512 Mb, 1 Gb supports 256 KB Uniform sector options

- 256 Mb, 512 Mb, 1 Gb Hybrid sector options

- Physical set of thirty-two 4 KB sectors and one 128 KB sector at the top or bottom of address space with all remaining sectors of 256 KB

- Physical set of sixteen 4 KB sectors and one 192 KB sector at both the top and bottom of the address space with all remaining sectors of 256 KB

The combination of the sector architecture selection bits in Configuration Register-1 and Configuration Register-3 support the different sector architecture options of the HL-T/HS-T family. See “[Registers](#)” on page 76 for more information.

**Table 2** 256 KB uniform sector address map<sup>[7]</sup>

| Sector size (KB) | S25HL01GT and S25HS01GT |              |                                                                    | S25HL512T and S25HS512T |              |                                                                    | S25HL256T and S25HS256T |              |                                                                    |

|------------------|-------------------------|--------------|--------------------------------------------------------------------|-------------------------|--------------|--------------------------------------------------------------------|-------------------------|--------------|--------------------------------------------------------------------|

|                  | Sector count            | Sector range | Byte address range (sector starting address–sector ending address) | Sector count            | Sector range | Byte address range (sector starting address–sector ending address) | Sector count            | Sector range | Byte address range (sector starting address–Sector ending address) |

| 256              | 512                     | SA00         | 0000000h–0003FFFFh                                                 | 256                     | SA00         | 0000000h–0003FFFFh                                                 | 128                     | SA00         | 0000000h–0003FFFFh                                                 |

|                  |                         | :            | :                                                                  |                         | :            | :                                                                  |                         | :            | :                                                                  |

|                  |                         | SA511        | 07FC0000h–07FFFFFFh                                                |                         | SA255        | 03FC0000h–03FFFFFFh                                                |                         | SA127        | 01FC0000h–01FFFFFFh                                                |

**Note**

7. Configuration: CFR3N[3]=1.

Address space maps

**Table 3 Bottom hybrid configuration 1 thirty-two 4 KB sectors and 256 KB uniform sectors address map<sup>[8]</sup>**

| Sector size (KB) | S25HL01GT and S25HS01GT |              |                                                                     | S25HL512T and S25HS512T |              |                                                                     | S25HL256T and S25HS 256T |              |                                                                     |

|------------------|-------------------------|--------------|---------------------------------------------------------------------|-------------------------|--------------|---------------------------------------------------------------------|--------------------------|--------------|---------------------------------------------------------------------|

|                  | Sector count            | Sector range | Byte address range (sector starting address -sector ending address) | Sector count            | Sector range | Byte address range (sector starting address -sector ending address) | Sector count             | Sector range | Byte address range (sector starting address -sector ending address) |

| 4                | 32                      | SA00         | 00000000h-00000FFFh                                                 | 32                      | SA00         | 00000000h-00000FFFh                                                 | 32                       | SA00         | 00000000h-00000FFFh                                                 |

|                  |                         | :            | :                                                                   |                         | :            | :                                                                   |                          | :            | :                                                                   |

|                  |                         | SA31         | 0001F000h-0001FFFFh                                                 |                         | SA31         | 0001F000h-0001FFFFh                                                 |                          | SA31         | 0001F000h-0001FFFFh                                                 |

| 128              | 1                       | SA32         | 00020000h-0003FFFFh                                                 | 1                       | SA32         | 00020000h-0003FFFFh                                                 | 1                        | SA32         | 00020000h-0003FFFFh                                                 |

| 256              | 511                     | SA33         | 00040000h-0007FFFFh                                                 | 255                     | SA33         | 00040000h-0007FFFFh                                                 | 127                      | SA33         | 00040000h-0007FFFFh                                                 |

|                  |                         | :            | :                                                                   |                         | :            | :                                                                   |                          | :            | :                                                                   |

|                  |                         | SA543        | 07FC0000h-07FFFFFFh                                                 |                         | SA287        | 03FC0000h-03FFFFFFh                                                 |                          | SA159        | 01FC0000h-01FFFFFFh                                                 |

**Note**

8. Configuration: CFR3N[3] = 0, CFR1N[6] = 0, CFR1N[2] = 0.

**Table 4 Top hybrid configuration 1 thirty-two 4 KB sectors and 256 KB uniform sectors address map<sup>[9]</sup>**

| Sector size (KB) | S25HL01GT and S25HS01GT |              |                                                                     | S25HL512T and S25HS512T |              |                                                                     | S25HL256T and S25HS256T |              |                                                                     |

|------------------|-------------------------|--------------|---------------------------------------------------------------------|-------------------------|--------------|---------------------------------------------------------------------|-------------------------|--------------|---------------------------------------------------------------------|

|                  | Sector count            | Sector range | Byte address range (sector starting address -sector ending address) | Sector count            | Sector range | Byte address range (sector starting address -sector ending address) | Sector count            | Sector range | Byte address range (sector starting address -sector ending address) |

| 256              | 511                     | SA00         | 00000000h-0003FFFFh                                                 | 255                     | SA00         | 00000000h-0003FFFFh                                                 | 127                     | SA00         | 00000000h-0003FFFFh                                                 |

|                  |                         | :            | :                                                                   |                         | :            | :                                                                   |                         | :            | :                                                                   |

|                  |                         | SA510        | 07F80000h-07FBFFFFh                                                 |                         | SA254        | 03F80000h-03FBFFFFh                                                 |                         | SA126        | 01F80000h-01FBFFFFh                                                 |

| 128              | 1                       | SA511        | 07FC0000h-07FDFFFFh                                                 | 1                       | SA255        | 03FC0000h-03FDFFFFh                                                 | 1                       | SA127        | 01FC0000h-01FDFFFFh                                                 |

| 4                | 32                      | SA512        | 07FE0000h-07FE0FFFh                                                 | 32                      | SA256        | 03FE0000h-03FE0FFFh                                                 | 32                      | SA128        | 01FE0000h-01FE0FFFh                                                 |

|                  |                         | :            | :                                                                   |                         | :            | :                                                                   |                         | :            | :                                                                   |

|                  |                         | SA543        | 07FFF000h-07FFFFFFh                                                 |                         | SA287        | 03FFF000h-03FFFFFFh                                                 |                         | SA159        | 01FFF000h-01FFFFFFh                                                 |

**Note**

9. Configuration: CFR3N[3] = 0, CFR1N[6] = 0, CFR1N[2] = 1.

**Table 5 Hybrid configuration 2 bottom sixteen and top sixteen 4 KB sectors address map<sup>[10]</sup>**

| Sector size (KB) | S25HL01GT and S25HS01GT |              |                                                                     | S25HL512T and S25HS512T |              |                                                                     | S25HL256T and S25HS256T |              |                                                                     |

|------------------|-------------------------|--------------|---------------------------------------------------------------------|-------------------------|--------------|---------------------------------------------------------------------|-------------------------|--------------|---------------------------------------------------------------------|

|                  | Sector count            | Sector range | Byte address range (sector starting address -sector ending address) | Sector count            | Sector range | Byte address range (sector starting address -sector ending address) | Sector count            | Sector range | Byte address range (sector starting address -sector ending address) |

| 4                | 16                      | SA00         | 00000000h-00000FFFh                                                 | 16                      | SA00         | 00000000h-00000FFFh                                                 | 16                      | SA00         | 00000000h-00000FFFh                                                 |

|                  |                         | :            | :                                                                   |                         | :            | :                                                                   |                         | :            | :                                                                   |

|                  |                         | SA15         | 0000F000h-0000FFFFh                                                 |                         | SA15         | 0000F000h-0000FFFFh                                                 |                         | SA15         | 0000F000h-0000FFFFh                                                 |

| 192              | 1                       | SA16         | 00010000h-0003FFFFh                                                 | 1                       | SA16         | 00010000h-0003FFFFh                                                 | 1                       | SA16         | 00010000h-0003FFFFh                                                 |

| 256              | 510                     | SA17         | 00040000h-0007FFFFh                                                 | 254                     | SA17         | 00040000h-0007FFFFh                                                 | 126                     | SA17         | 00040000h-0007FFFFh                                                 |

|                  |                         | :            | :                                                                   |                         | :            | :                                                                   |                         | :            | :                                                                   |

|                  |                         | SA526        | 07F80000h-07FBFFFFh                                                 |                         | SA270        | 03F80000h-03FBFFFFh                                                 |                         | SA142        | 01F80000h-01FBFFFFh                                                 |

| 192              | 1                       | SA527        | 07FC0000h-07FEFFFFh                                                 | 1                       | SA271        | 03FC0000h-03FEFFFFh                                                 | 1                       | SA143        | 01FC0000h-01FEFFFFh                                                 |

| 4                | 16                      | SA528        | 07FF0000h-07FF0FFFh                                                 | 16                      | SA272        | 03FF0000h-03FF0FFFh                                                 | 16                      | SA144        | 01FF0000h-01FF0FFFh                                                 |

|                  |                         | :            | :                                                                   |                         | :            | :                                                                   |                         | :            | :                                                                   |

|                  |                         | SA543        | 07FFF000h-07FFFFFFh                                                 |                         | SA287        | 03FFF000h-03FFFFFFh                                                 |                         | SA159        | 01FFF000h-01FFFFFFh                                                 |

**Note**

10. Configuration: CFR3N[3] = 0, CFR1N[6] = 1.

These are condensed tables that use a couple of sectors as references. There are address ranges that are not explicitly listed. All 4 KB sectors have the pattern xxxx000h-xxxxFFFFh. All 256 KB sectors have the pattern xxx0000h-xxx3FFFFh, xxx40000h-xxx7FFFFh, xx80000h-xxxCFFFFh, or xxD0000h-xxxFFFFh.

Address space maps

### 3.2 ID address space

This particular region of the memory is assigned to manufacturer, device, and unique identification:

- The manufacturer identification is assigned by JEDEC (see [Table 89](#)).

- The device identification is assigned by Infineon (see [Table 89](#)).

- A 64-bit unique number is located in 8 bytes of the Unique Device ID address space. This Unique ID can be used as a software readable serial number that is unique for each device (see [Table 90](#)).

There is no address space defined for these IDs as they can be read by providing the respective transactions only. The transactions do not need the address to read these IDs. The data in this address space is read-only data.

### 3.3 JEDEC JESD216 serial flash discoverable parameters (SFDP) space

The SFDP standard provides a consistent method of describing the functional and feature capabilities of this serial flash device in a standard set of internal parameter tables. These parameter tables can be interrogated by host system software to enable adjustments needed to accommodate divergent features. The SFDP address space has a header starting at address zero that identifies the SFDP data structure and provides a pointer to each parameter. The SFDP address space is programmed by Infineon and read-only for the host system (see [Table 85](#) through [Table 88](#)).

**Table 6 SFDP overview address map**

| Byte address | Description                                                                              |

|--------------|------------------------------------------------------------------------------------------|

| 0000h        | Location zero within JEDEC JESD216D SFDP space - start of SFDP header                    |

| „„           | Remainder of SFDP header followed by undefined space                                     |

| 0100h        | Start of SFDP parameter tables The SFDP parameter table data starting at 0100h           |

| ...          | Remainder of SFDP parameter tables followed by either more parameters or undefined space |

### 3.4 SSR address space

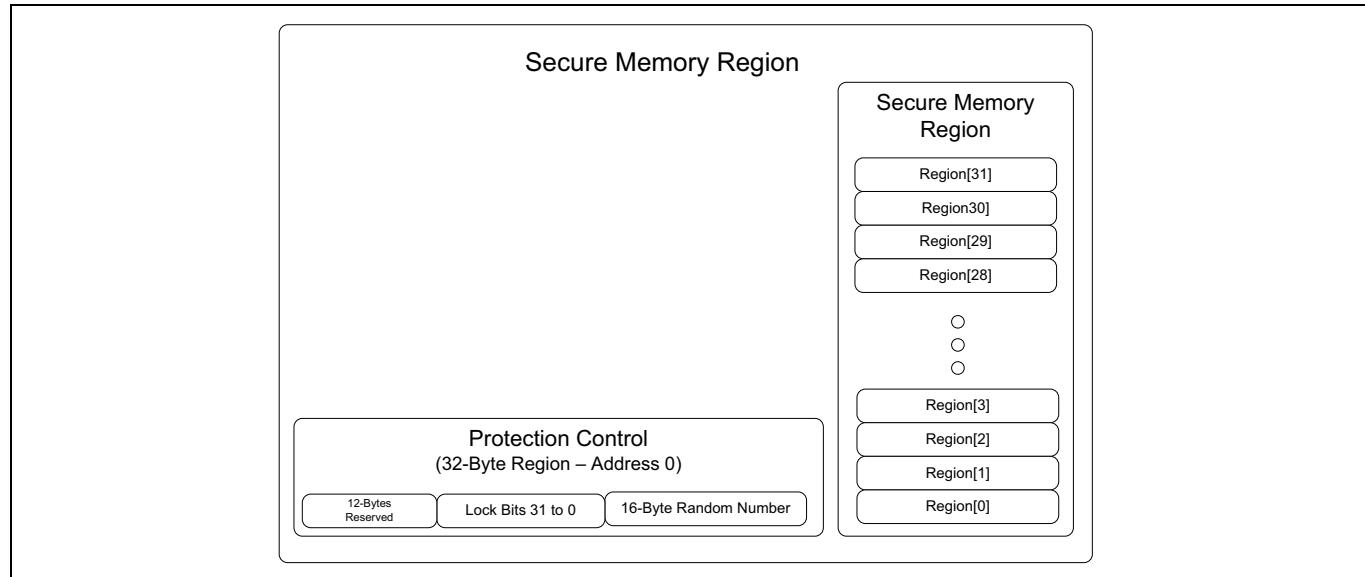

Each HS/L-T family memory device has a 1024-byte Secure Silicon Region which is OTP address space. This address space is separate from the main flash array. The SSR area is divided into 32 individually lockable, 32-byte aligned and length regions.

In the 32-byte region starting at address zero:

- The 16 lowest bytes contain a 128-bit random number. The random number cannot be written to, erased or programmed and any attempts will return an PRGERR flag.

- The next four bytes are used to provide one bit per secure region (32 bits in total) to permanently protect once set to “0” from writing, erasing or programming.

- All other bytes are reserved.

The remaining regions are erased when shipped from Infineon, and are available for programming of additional permanent data.

**Table 7 SSR address map**

| Region    | Byte address range | Contents                                                                                                                                              | Initial delivery state            |

|-----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Region 0  | 000h               | LSB of Infineon Programmed Random Number                                                                                                              | Infineon Programmed Random Number |

|           | ...                | ...                                                                                                                                                   |                                   |

|           | 00Fh               | MSB of Infineon Programmed Random Number                                                                                                              |                                   |

|           | 010h to 013h       | Region Locking Bits<br>Byte 10h [bit 0] locks region 0 from programming when = 0<br>...<br>Byte 13h [bit 7] locks region 31 from programming when = 0 | All Bytes = FFh                   |

|           | 014h to 01Fh       | Reserved for future use (RFU)                                                                                                                         | All Bytes = FFh                   |

| Region 1  | 020h to 03Fh       | Available for User Programming                                                                                                                        | All Bytes = FFh                   |

| Region 2  | 040h to 05Fh       | Available for User Programming                                                                                                                        | All Bytes = FFh                   |

| ...       | ...                | Available for User Programming                                                                                                                        | All Bytes = FFh                   |

| Region 31 | 3E0h to 3FFh       | Available for User Programming                                                                                                                        | All Bytes = FFh                   |

Address space maps

### 3.5 Registers

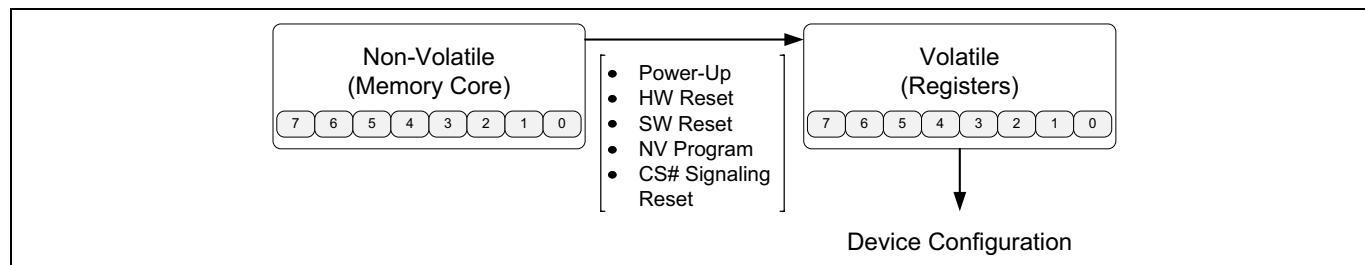

Registers are small groups of memory cells used to configure how the HS/L-T family memory device operates, or to report the status of device operations. The registers are accessed by specific commands and addresses.

**Table 8** shows the address map for every available register in this flash memory device.

**Table 8 Register address map**

| Function                             | Register type                                                    | Register name          | Volatile component address (hex) | Nonvolatile component address (hex) |

|--------------------------------------|------------------------------------------------------------------|------------------------|----------------------------------|-------------------------------------|

| Device Status                        | Status Register 1                                                | STR1N[7:0], STR1V[7:0] | 0x00800000                       | 0x00000000                          |

|                                      | Status Register 2                                                | STR2V[7:0]             | 0x00800001                       | N/A                                 |

| Device Configuration                 | Configuration Register 1                                         | CFR1N[7:0], CFR1V[7:0] | 0x00800002                       | 0x00000002                          |

|                                      | Configuration Register 2                                         | CFR2N[7:0], CFR2V[7:0] | 0x00800003                       | 0x00000003                          |

|                                      | Configuration Register 3                                         | CFR3N[7:0], CFR3V[7:0] | 0x00800004                       | 0x00000004                          |

|                                      | Configuration Register 4                                         | CFR4N[7:0], CFR4V[7:0] | 0x00800005                       | 0x00000005                          |

| Infineon Endurance Flex architecture | Infineon Endurance Flex architecture Selection Register 0 [1:0]  | EFX0O[1:0]             | N/A                              | 0x00000050                          |

|                                      | Infineon Endurance Flex architecture Selection Register 1 [7:0]  | EFX1O[7:0]             |                                  | 0x00000052                          |

|                                      | Infineon Endurance Flex architecture Selection Register 1 [10:8] | EFX1O[10:8]            |                                  | 0x00000053                          |

|                                      | Infineon Endurance Flex architecture Selection Register 2 [7:0]  | EFX2O[7:0]             |                                  | 0x00000054                          |

|                                      | Infineon Endurance Flex architecture Selection Register 2 [10:8] | EFX2O[10:8]            |                                  | 0x00000055                          |

|                                      | Infineon Endurance Flex architecture Selection Register 3 [7:0]  | EFX3O[7:0]             |                                  | 0x00000056                          |

|                                      | Infineon Endurance Flex architecture Selection Register 3 [10:8] | EFX3O[10:8]            |                                  | 0x00000057                          |

|                                      | Infineon Endurance Flex architecture Selection Register 4 [7:0]  | EFX4O[7:0]             |                                  | 0x00000058                          |

|                                      | Infineon Endurance Flex architecture Selection Register 4 [10:8] | EFX4O[10:8]            |                                  | 0x00000059                          |

|                                      |                                                                  |                        |                                  |                                     |

| Error Correction                     | ECC Status Register                                              | ESCV[7:0]              | 0x00800089                       | N/A                                 |

|                                      | ECC Error Detection Count Register [7:0]                         | ECTV[7:0]              | 0x0080008A                       |                                     |

|                                      | ECC Error Detection Count Register [15:8]                        | ECTV[15:8]             | 0x0080008B                       |                                     |

|                                      | ECC Address Trap Register [7:0]                                  | EATV[7:0]              | 0x0080008E                       |                                     |

|                                      | ECC Address Trap Register [15:8]                                 | EATV[15:8]             | 0x0080008F                       |                                     |

|                                      | ECC Address Trap Register [23:16]                                | EATV[23:16]            | 0x00800040                       |                                     |

|                                      | ECC Address Trap Register [31:24]                                | EATV[31:24]            | 0x00800041                       |                                     |

| AutoBoot                             | AutoBoot Register [7:0]                                          | ATBN[7:0]              | N/A                              | 0x00000042                          |

|                                      | AutoBoot Register [15:8]                                         | ATBN[15:8]             |                                  | 0x00000043                          |

|                                      | AutoBoot Register [23:16]                                        | ATBN[23:16]            |                                  | 0x00000044                          |

|                                      | AutoBoot Register [31:24]                                        | ATBN[31:24]            |                                  | 0x00000045                          |

| Data Learning                        | Data Learning Register [7:0]                                     | DLPN[7:0], DLPV[7:0]   | 0x00800010                       | 0x00000010                          |

| Erase Count                          | Sector Erase Count Register [7:0]                                | SECV[7:0]              | 0x00800091                       | N/A                                 |

|                                      | Sector Erase Count Register [15:8]                               | SECV[15:8]             | 0x00800092                       |                                     |

|                                      | Sector Erase Count Register [23:16]                              | SECV[23:16]            | 0x00800093                       |                                     |

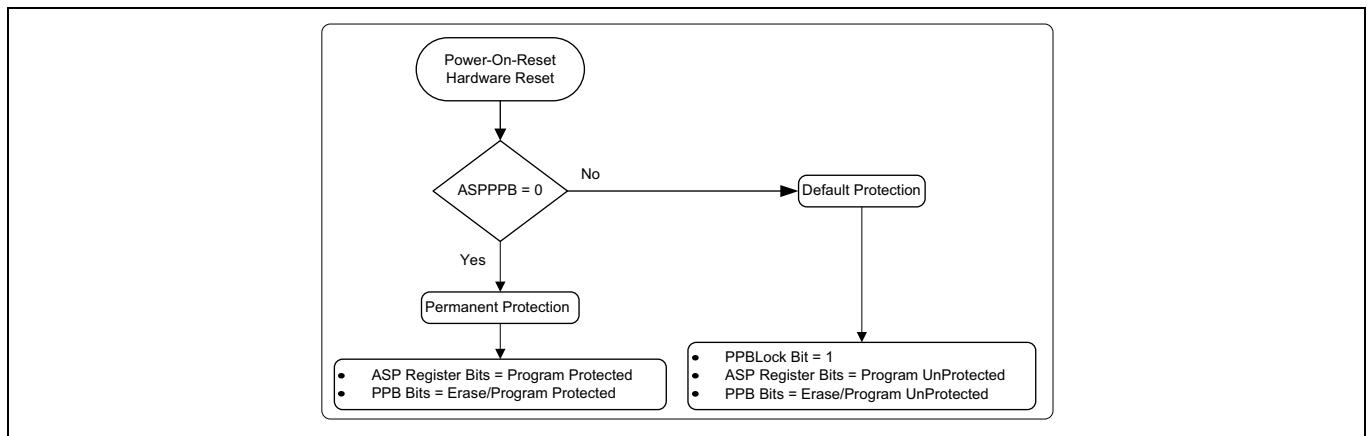

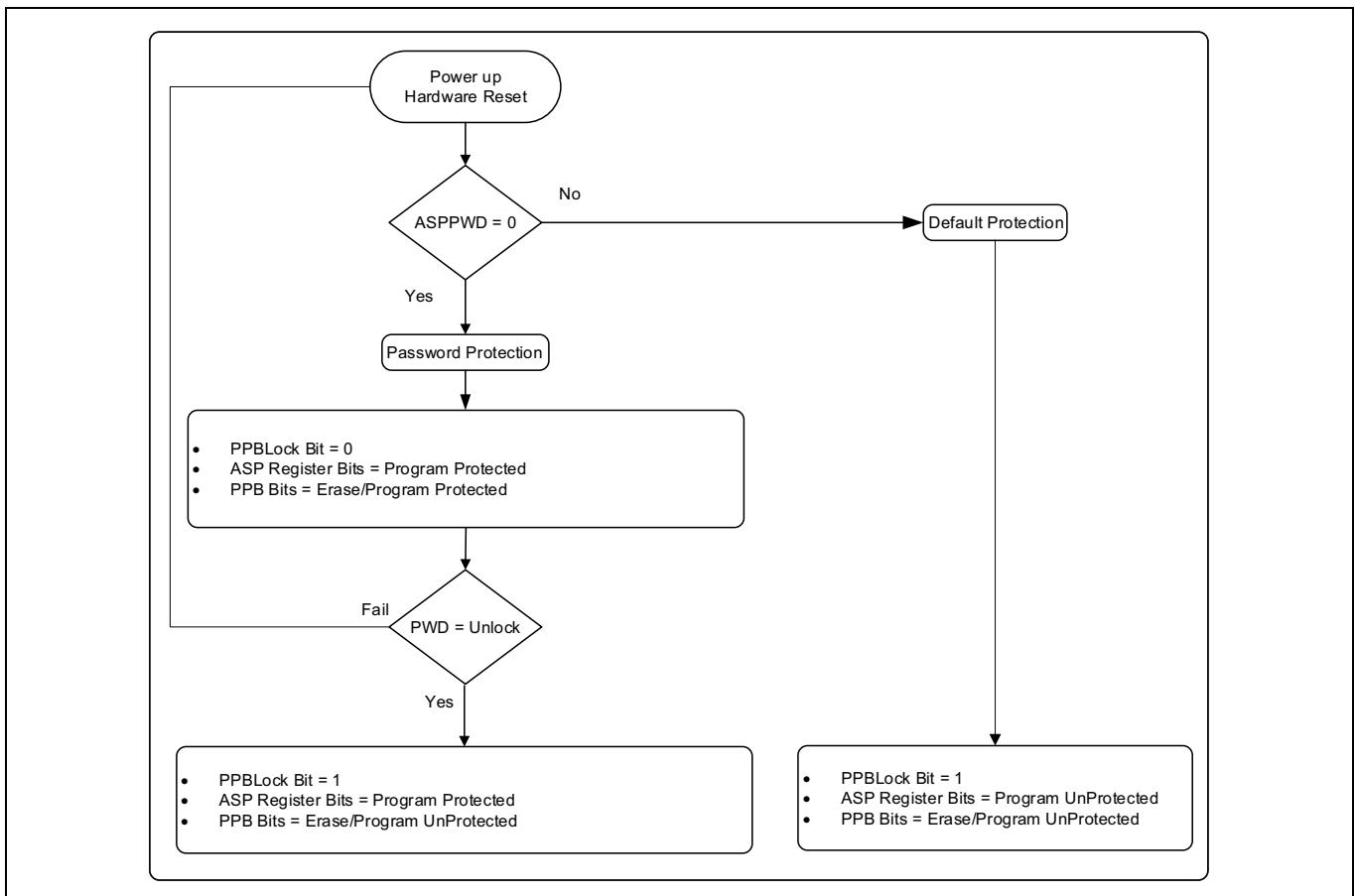

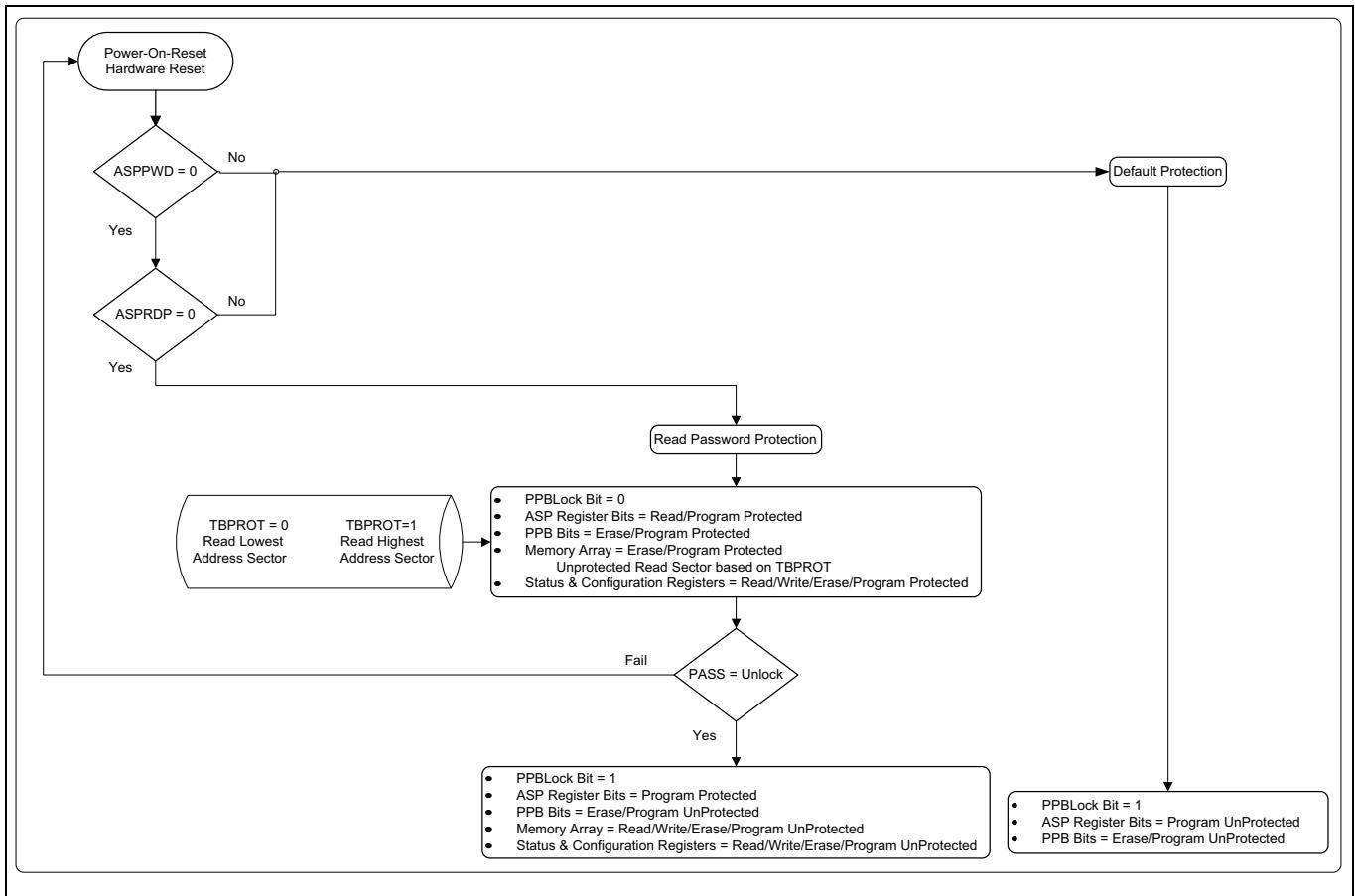

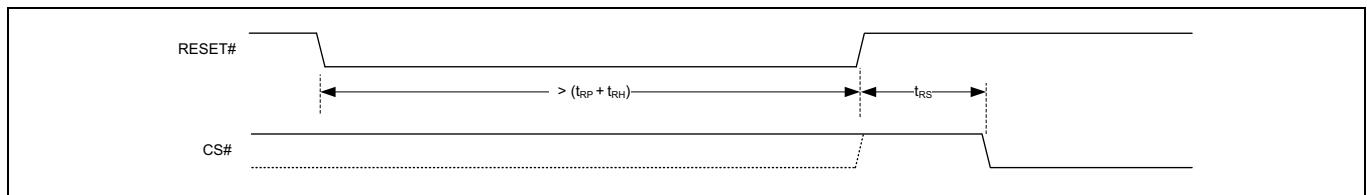

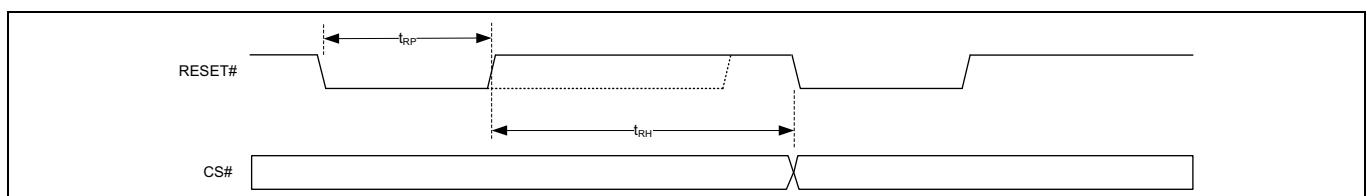

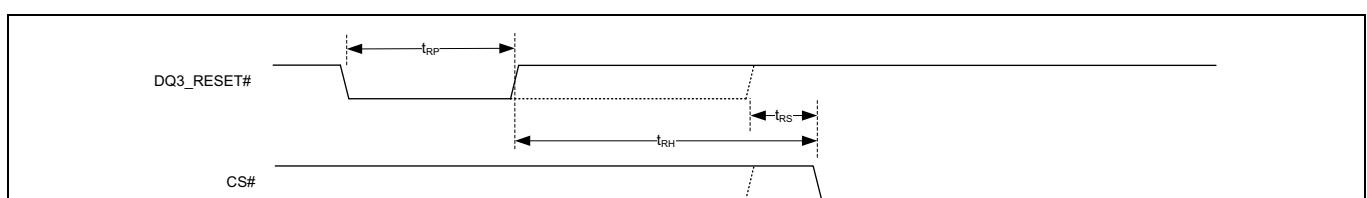

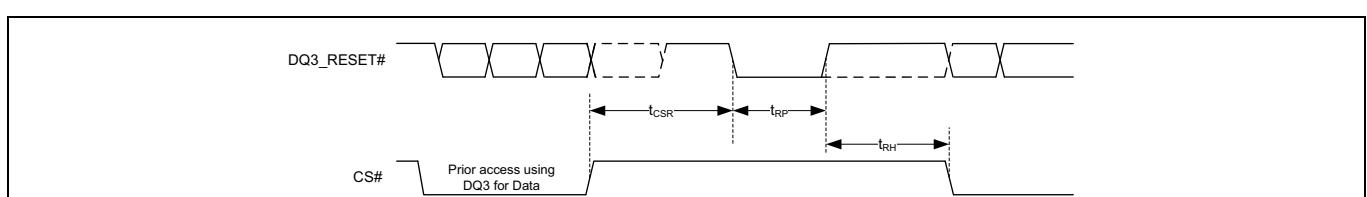

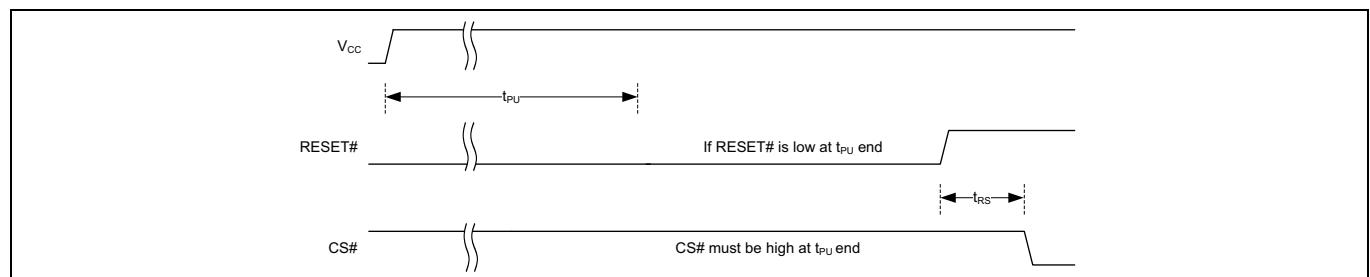

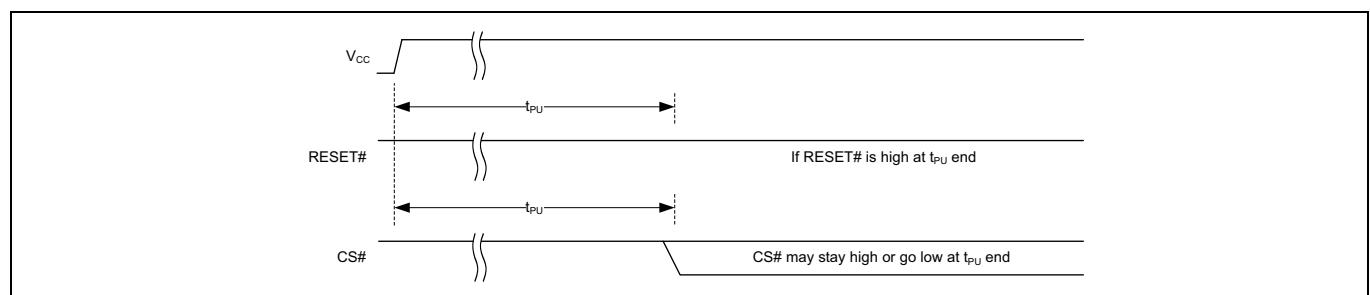

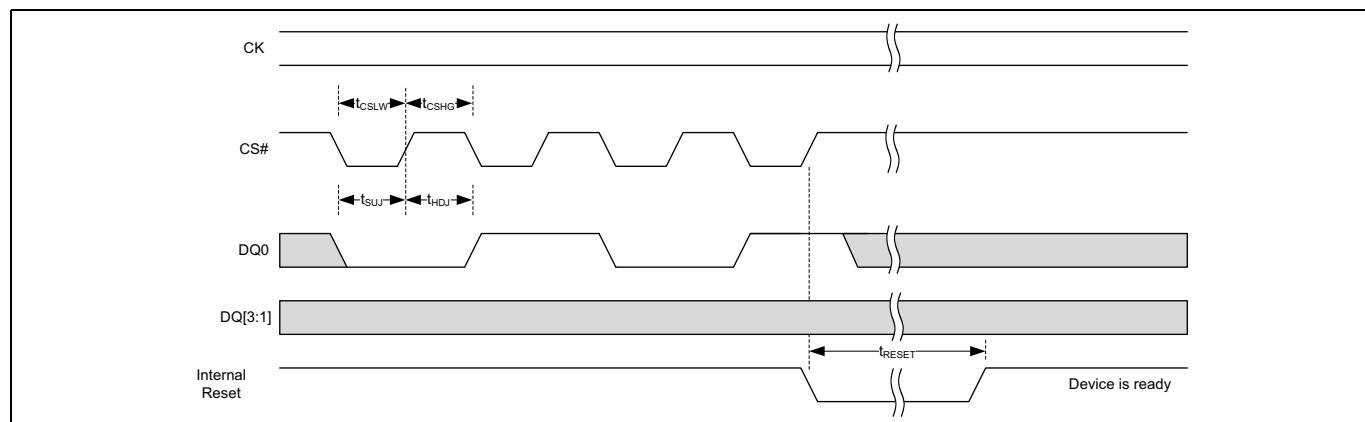

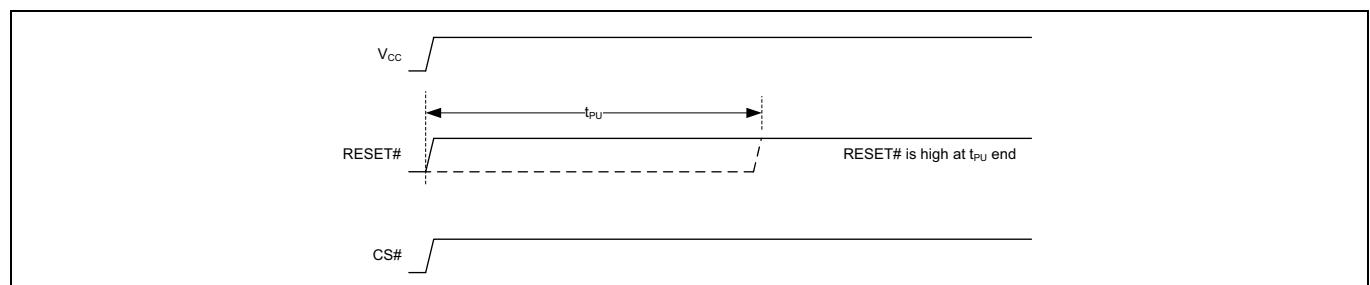

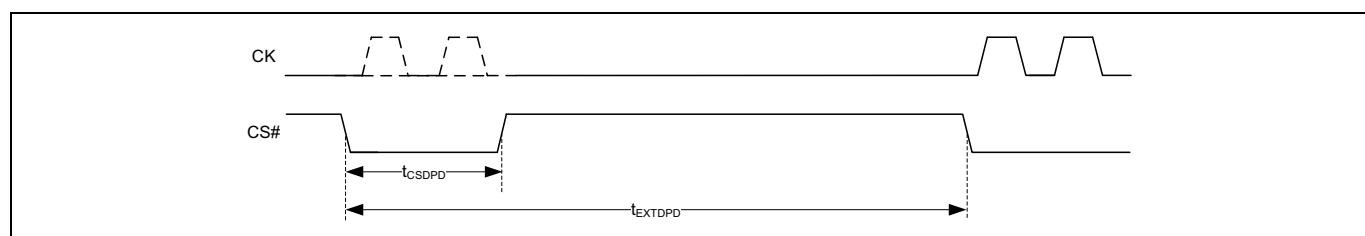

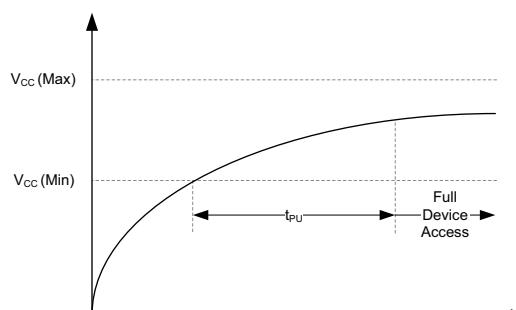

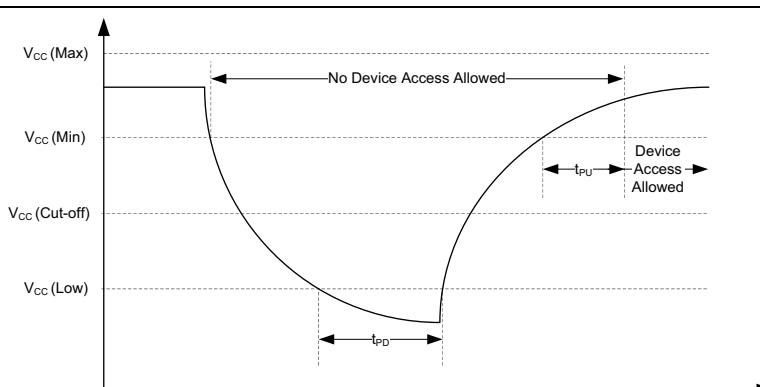

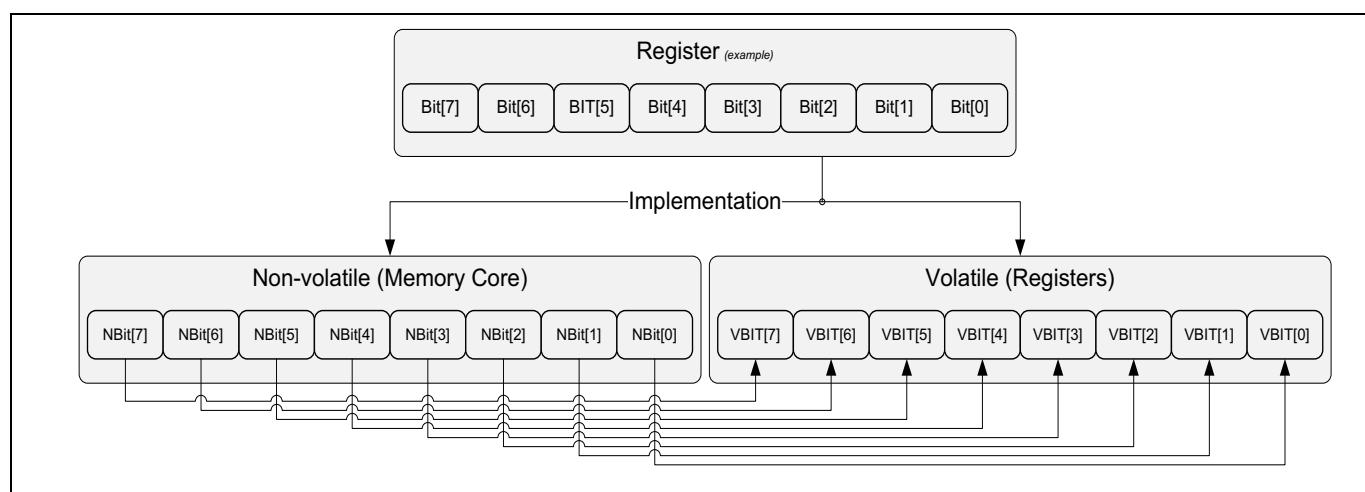

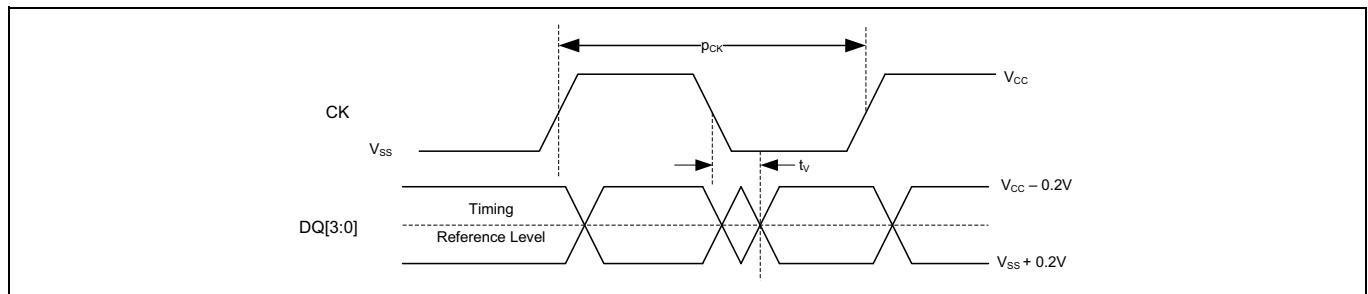

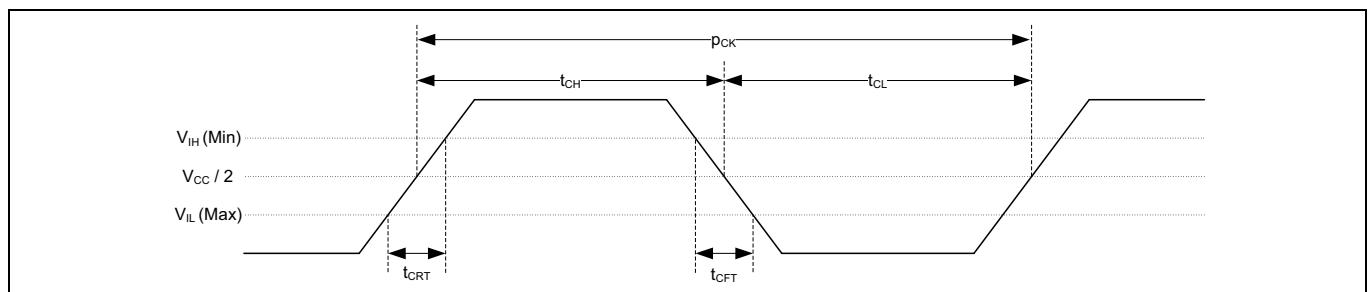

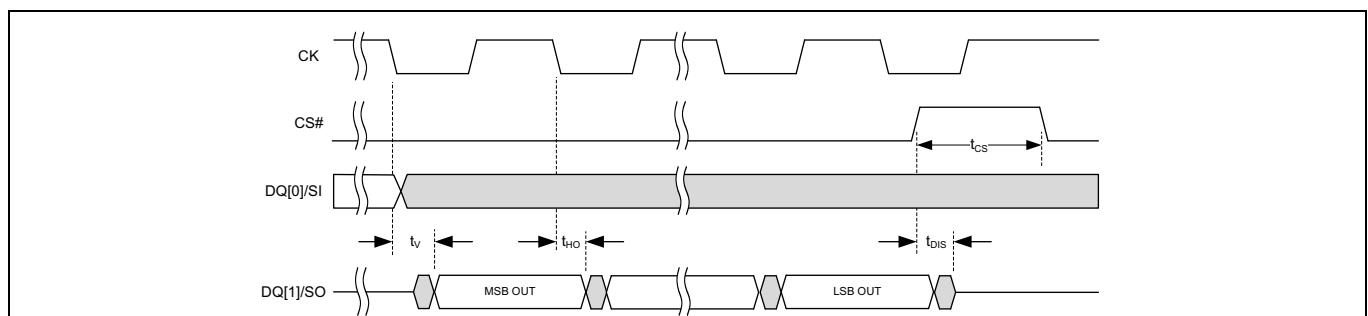

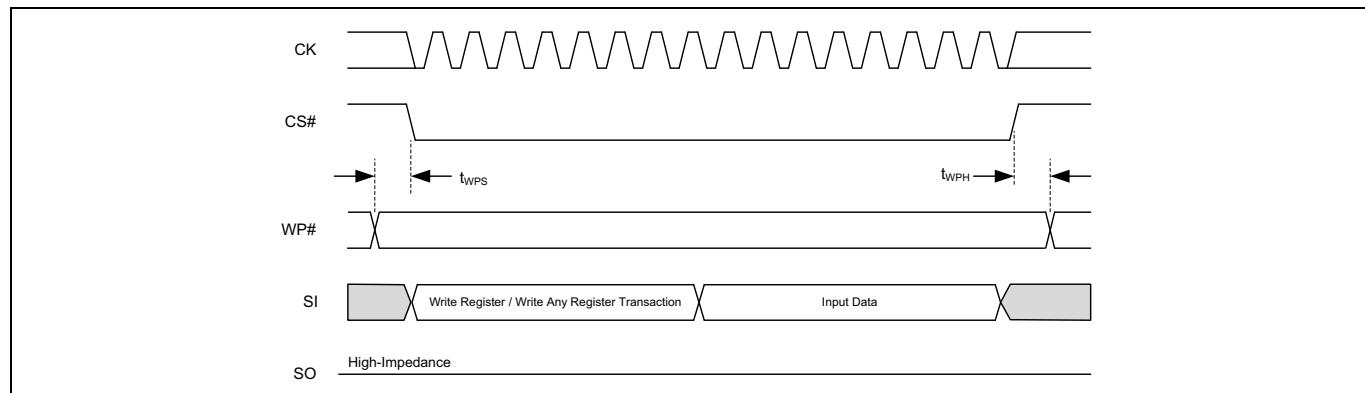

| Data Integrity Check                 | Data Integrity Check CRC Register [7:0]                          | DCRV[7:0]              | 0x00800095                       | N/A                                 |