# Getting started with 2ED2410-EM

## Application note

### About this document

#### Scope and purpose

This application note shows users how to simply design-in Infineon EiceDRIVER™ APD 2ED2410-EM.

It shows how to set-up external components based on practical considerations, using datasheet parameters and provides tips on how to use this unique gate driver flexibility.

#### Intended audience

This document is intended for all electrical and electronic engineers who need to replace relay and fuses by an effective and simple way to make a reliable and self-protected solid-state switch based on MOSFET and a shunt resistor.

**Note:** *Values shown in this application note are measured under lab conditions and will vary for different cooling conditions and setups.*

**Note:** *In this document, [PRQ-xxx] numbers refer to 2ED2410-EM datasheet parameters.*

|                                                                    |           |

|--------------------------------------------------------------------|-----------|

| <b>About this document.....</b>                                    | <b>1</b>  |

| <b>1 Basic functions and mandatory external components .....</b>   | <b>3</b>  |

| 1.1 Sizing $L$ and $R_{RS}$ .....                                  | 3         |

| 1.2 Sizing $C_{BC}$ .....                                          | 5         |

| 1.3 Computing boost converter frequency .....                      | 6         |

| 1.4 Sizing $R_{GATE}$ .....                                        | 7         |

| 1.4.1 Example in application .....                                 | 8         |

| 1.5 Reverse battery behaviour.....                                 | 9         |

| 1.5.1 Common drain in reverse battery.....                         | 10        |

| 1.5.2 Common source in reverse battery .....                       | 11        |

| <b>2 What to do with non-used pins? .....</b>                      | <b>12</b> |

| <b>3 Enhanced functions and optional external components .....</b> | <b>14</b> |

| 3.1 Simple pre-charge circuit.....                                 | 14        |

| 3.2 IDLE as default mode (undervoltage auto-restart) .....         | 15        |

| <b>4 Amplifiers set-up.....</b>                                    | <b>17</b> |

| 4.1 Current sense set-up .....                                     | 17        |

| 4.2 Temperature sense set-up .....                                 | 18        |

| 4.2.1 TMPA target curve calculation example.....                   | 19        |

| <b>5 PCB layout recommendations.....</b>                           | <b>20</b> |

| 5.1 SW, BC and RS pin routing .....                                | 20        |

| 5.2 VS node routing .....                                          | 21        |

| 5.3 Amplifiers routing.....                                        | 21        |

| 5.4 GND pin .....                                                  | 22        |

| <b>6 External parts for driver protection.....</b>                 | <b>23</b> |

| 6.1 Protecting the VS node.....                                    | 23        |

| 6.2 ISO7637 transient pulses and DPI protections.....              | 23        |

| 6.3 ESD components and layout recommendation.....                  | 24        |

| <b>7 Quiescent current example .....</b>                           | <b>25</b> |

| 7.1 SLEEP mode.....                                                | 25        |

| 7.2 IDLE mode.....                                                 | 26        |

| 7.3 ON/SAFESTATE mode .....                                        | 28        |

| <b>Revision history.....</b>                                       | <b>30</b> |

## 1 Basic functions and mandatory external components

This chapter describes the minimal and necessary components to operate the 2ED2410-EM.

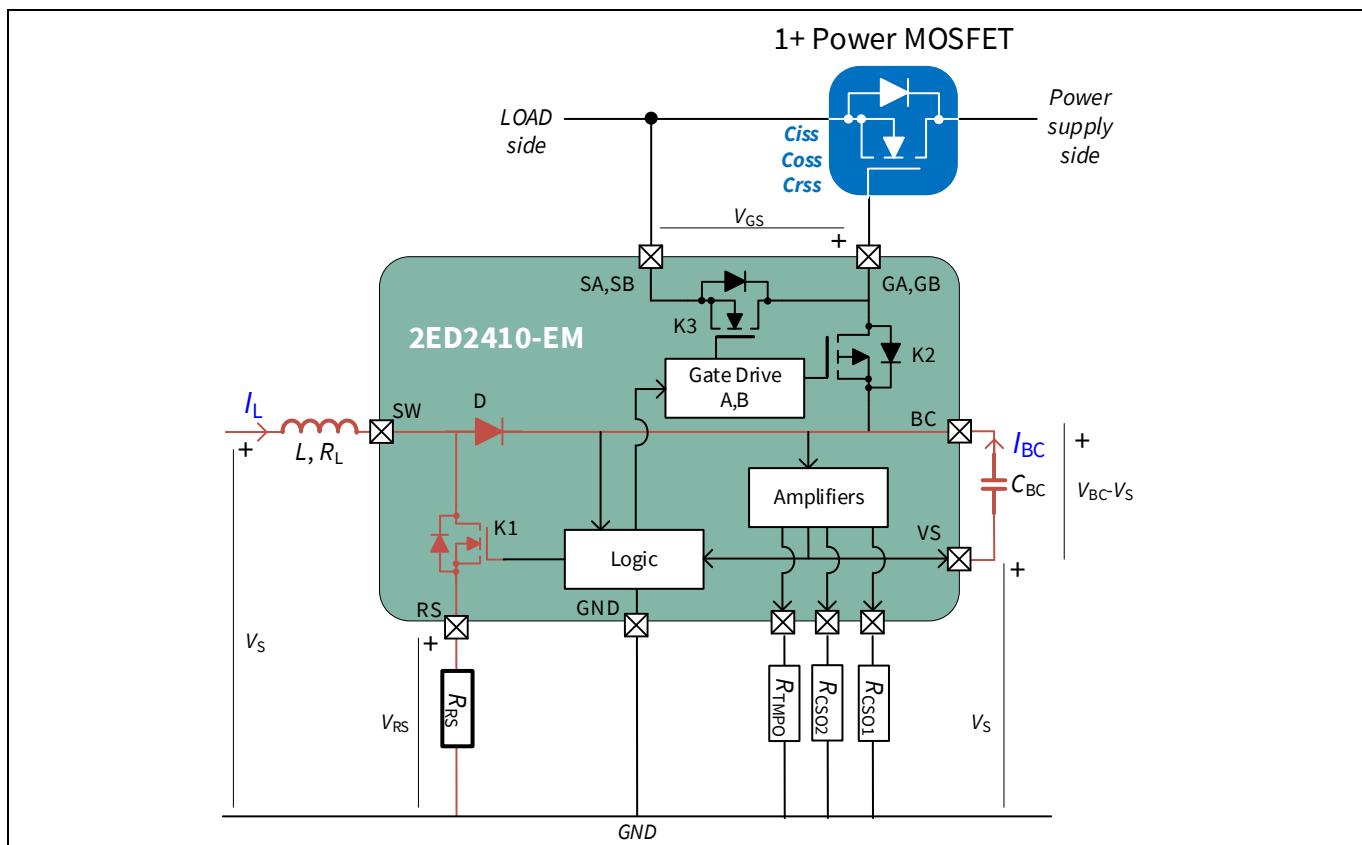

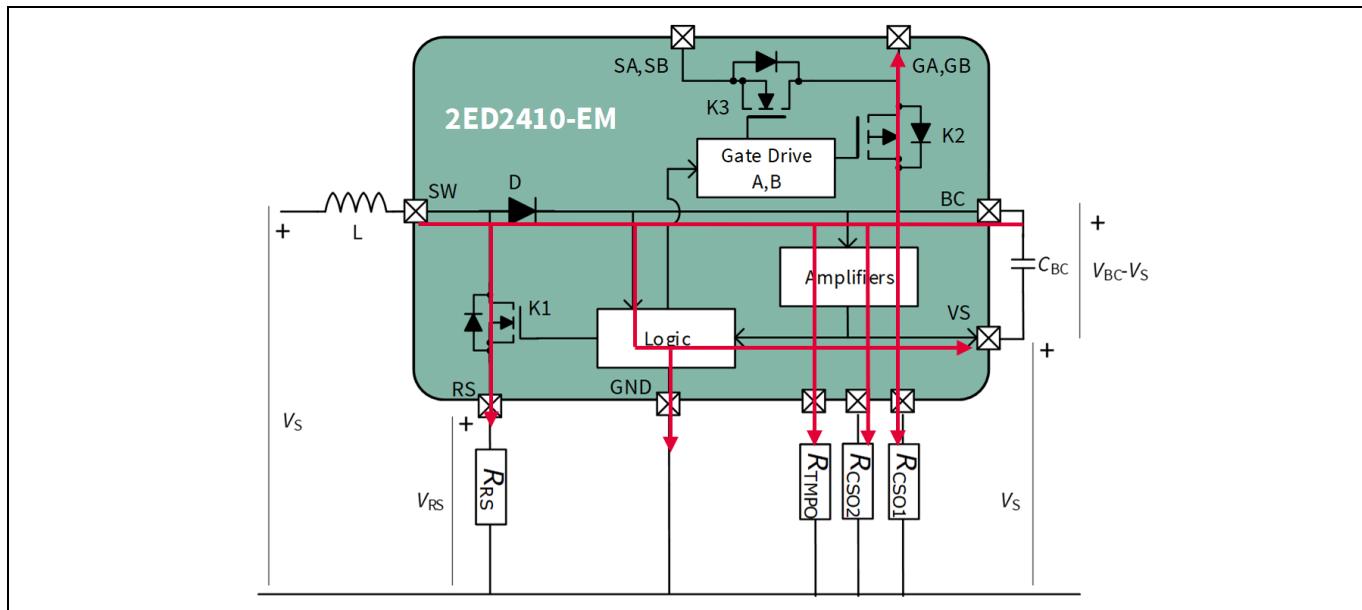

2ED2410-EM is a high-side gate driver and therefore needs a power supply that elevates voltage above battery voltage in order to drive the MOSFETs. A boost converter supply is chosen in order to have improved efficiency compared to a charge pump, and therefore, pulls less current from the car's battery. The diode (D) and switching element (K1) are implemented inside the chip and the inductor ( $L$ ), output capacitor ( $C_{BC}$ ) and resistor for current peak sense ( $R_{RS}$ ) have to be added externally.

**Figure 1** 2ED2410-EM Boost converter supply concept with currents and voltages definition

### 1.1 Sizing $L$ and $R_{RS}$

The boost converter is designed for very small duty cycle (<1 %), open loop and current peak control operation in discontinuous conduction mode.

Therefore, the most important parameter to observe is the  $I_L = I_{peak}$  limitation in the switching element (K1, refer to figure 1), defined by maximum of parameter  $I_{SW}$  [PRQ-16]. This condition  $I_L < I_{SW}$  must be true at all temperatures over the application voltage range.

The current in the inductor is limited by the  $V_{RS(TH)}$  comparator, inside the driver (see figure 26 in datasheet), which monitors the voltage across  $R_{RS}$ . Due to the delay in the loop ( $t_{D(OFF)K1}$  [PRQ-155]), the inductor current exceeds the threshold set by:  $V_{RS(TH)}$  [PRQ-147].

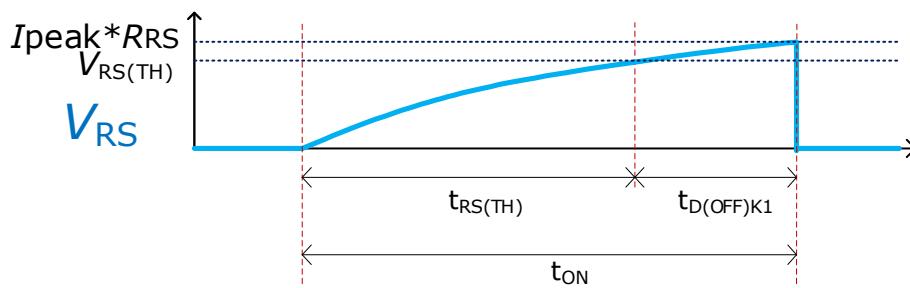

**Figure 2** Switching waveform of boost converter,  $V_{RS}$  voltage

The current waveform in the inductor is not linear, but exponential because the sum of the resistor of K1, of the parasitic inductor of  $L$  ( $R_L$ ) and  $R_{RS}$  are not negligible in the K1 short activation timeframe.

Therefore, the time to reach  $t_{RS(TH)}$  is computed by:

$$(1) \quad t_{RS(TH)} = -\frac{L}{R_{DS(ON)K1} + R_{RS} + R_L} \times \ln(1 - V_{RS(TH)}) \times \frac{R_{DS(ON)K1} + R_{RS} + R_L}{R_{RS} \times V_S}$$

Referring to figure 2:

$$(2) \quad t_{ON} = t_{RS(TH)} + t_{D(OFF)K1}$$

Ideally  $R_{RS}$  should be as low as possible: a high  $R_{RS}$  resistor would lower output current capability and boost converter operating frequency could be in the audible range. By design of the  $I_{peak}$  detection loop, a minimum is given in the datasheet  $R_{RS(MIN)}=10 \Omega$  (PRQ-138). Additionally, the computed power must be sustained by the resistor  $R_{RS}$  across the whole application range, meaning  $I_{peak}$  has to be computed for 18 V if the operating range expected in the application is 8-18 V, for example.

$$(3) \quad P_{RRS} \geq I_{peak(V_{S(MAX})})^2 \times R_{RS}$$

Therefore, from datasheet equation (17), having chosen  $R_{RS}$  value, the  $I_{peak}$  can be computed with the available inductor. As there are three unknowns in the equation, there is no simple way to compute the minimum inductor that can be used. It has to be ensured that  $I_{peak}$  parameter is not violated over the application  $V_S$  range given the characteristics of the inductor used.

Therefore, the  $I_{peak}$  current can be solved by:

$$(4) \quad I_{peak} = \frac{V_S}{R_{DS(ON)K1} + R_{RS} + R_L} \times \left( 1 - e^{-t_{ON} \times \frac{R_{DS(ON)K1} + R_{RS} + R_L}{L}} \right)$$

The automated calculation can be found in the workbook “Getting started with 2ED2410-EM, tab “boost converter sizing”.

Typically, an inductor between 100  $\mu$ H and 470  $\mu$ H can be selected with  $R_{RS(MIN)}$ . Where a 100  $\mu$ H can be cost-optimized compared to a 470  $\mu$ H inductor, while a 470  $\mu$ H inductor improves the efficiency and therefore will optimize the current consumption from the battery. Also, choosing an inductor with a small parasitic series resistance  $R_L$ , will increase the boost converter efficiency and reduce the current drawn from the battery (See chap. 7 Quiescent current example for detailed quiescent current calculation).

To sum up: the choice of the inductor is driven by the  $I_{peak}$  and its optimization by three parameters: the parasitic resistance of the coil, current consumption of the driver in the application and application target cost.

## 1.2 Sizing $C_{BC}$

The  $C_{BC}$  capacitor is the output capacitor of the boost converter, normally used to filter the output on regular boost converters. Here, it is also used as a charge buffer for the external MOSFETs parasitic  $C_{iss}$  at turn-on: during turn-on, the charges are transferred from  $C_{BC}$  to the external MOSFET  $C_{iss}$ . This allows 2ED2410-EM to drive many MOSFETs in parallel, up 100 nF equivalent  $C_{GS}$  per gate driver output. Therefore, it has to be ensured that during turn-on, the  $C_{BC}$  capacitor's voltage does not drop below the boost converter gate UVLO limit. The range between gate UVLO [PRQ-140] and regulating output voltage of the boost converter  $V_{BC(TH)}$  [PRQ-139] above battery voltage, is called  $V_{BC(RG)}$  [PRQ-141].

Assuming the charge is conserved between tank capacitor  $C_{BC}$  and the total MOSFET  $C_{iss}$ , using  $Q=C*V$ ,

$$(5) \quad C_{BC} * \Delta V_{BC} = C_{iss(TOT)} * V_{BC(TH)}$$

Therefore, knowing that the minimum  $\Delta V_{BC}$  we have to sustain with  $C_{BC}$ , is  $V_{BC(RG)MIN}$  (min of  $V_{BC(RG)}$ );

$$(6) \quad C_{BC(MIN)} = \frac{C_{iss(TOT)} * V_{BC(TH)MAX}}{V_{BC(RG)MIN}}$$

As an example, using eight IAUT300N08S5N012 (four in parallel on each gate output), the computed  $C_{BC(MIN)}$  is given by:

$$(7) \quad C_{BC(MIN)} = \frac{8 * 1.625 * 10^{-8}}{1.9} = 0.96 \mu F$$

Therefore, a suitable capacitor for this application could be a 1  $\mu F$  capacitor. Considering a 30 % shift of capacitor value over lifetime as well as 20 % ceramic capacitor accuracy, here we should use a 2.2  $\mu F$  capacitor for  $C_{BC}$ .

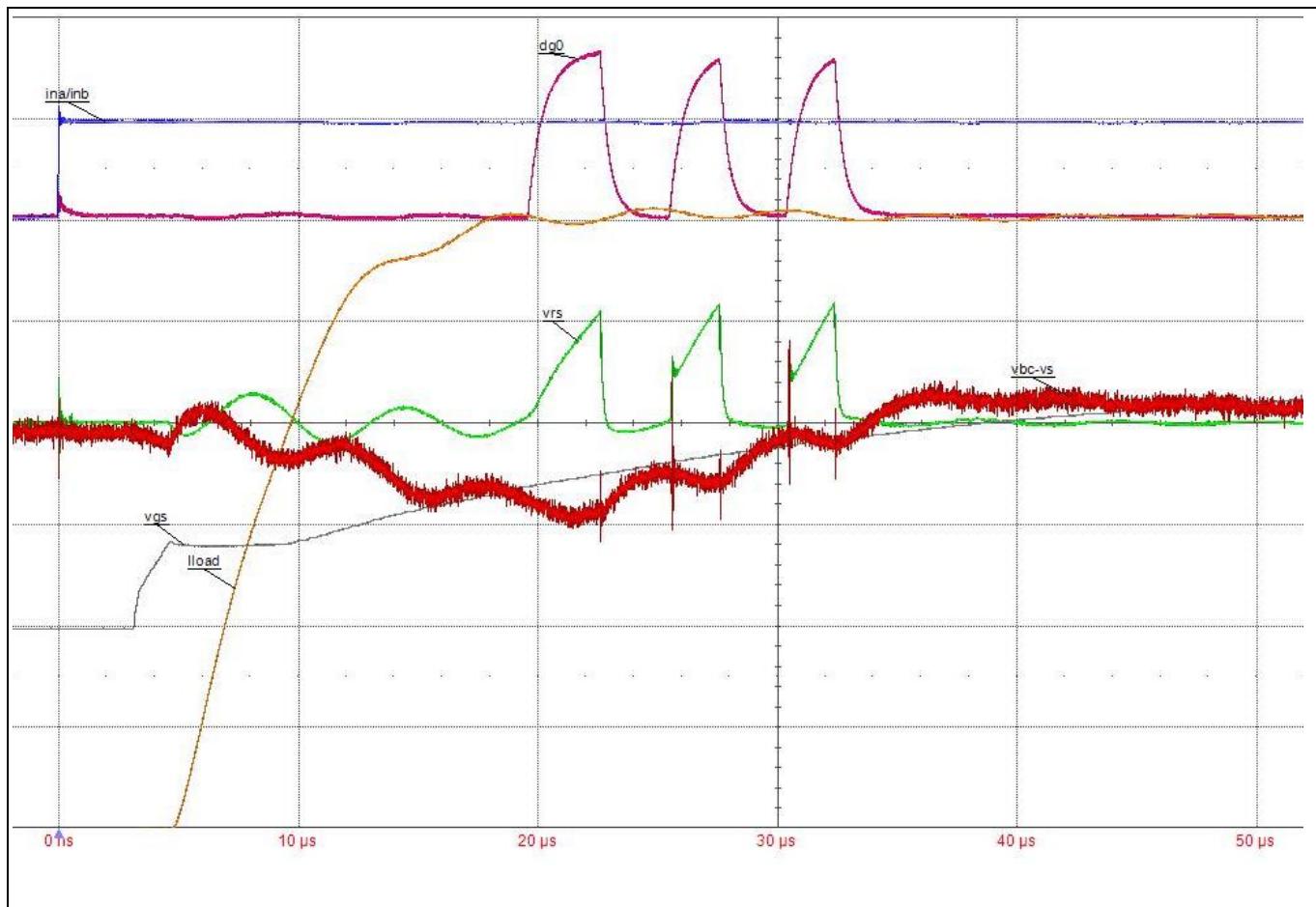

A regular turn-on is shown in figure 3. When the MOSFETs are turned-on the charges are taken from  $C_{BC}$  and the boost converter needs to pump again to compensate the charged transferred to the MOSFET, hence the activation of RS (green). The activation is monitored by DG0 pin (pink) in ON mode.

**Figure 3** Switching waveform from IDLE to ON [blue: INx; green:  $V_{RS}$ ; red:  $V_{BC-VS}$  (AC mode) (boost converter output); pink: DG0; grey: gate-source on MOSFET; orange: LOAD current]

## 1.3 Computing boost converter frequency

Figure 1 shows the gates are supplied directly out of the gate driver through the PMOS of a push-pull (PMOS K2, see figure 1). Therefore, in ON mode, the output of the boost converter is directly connected to the MOSFET gate through K2. Consequently, monitoring the boost frequency monitors the health of the gate source junction. Any leakage or short connection in the power MOSFET can be detected by a much higher frequency in boost converter operation compared to normal.

The activation frequency depends on the boost converter current  $I_{BC}$ . The current seen by the boost converter is given in the datasheet, depending on the mode the driver is in [ $I_{BC(IDLE)}$ , PRQ-144;  $I_{BC(ON)}$ , PRQ-145;  $I_{BC(SAFESTATE)}$ , PRQ-146].

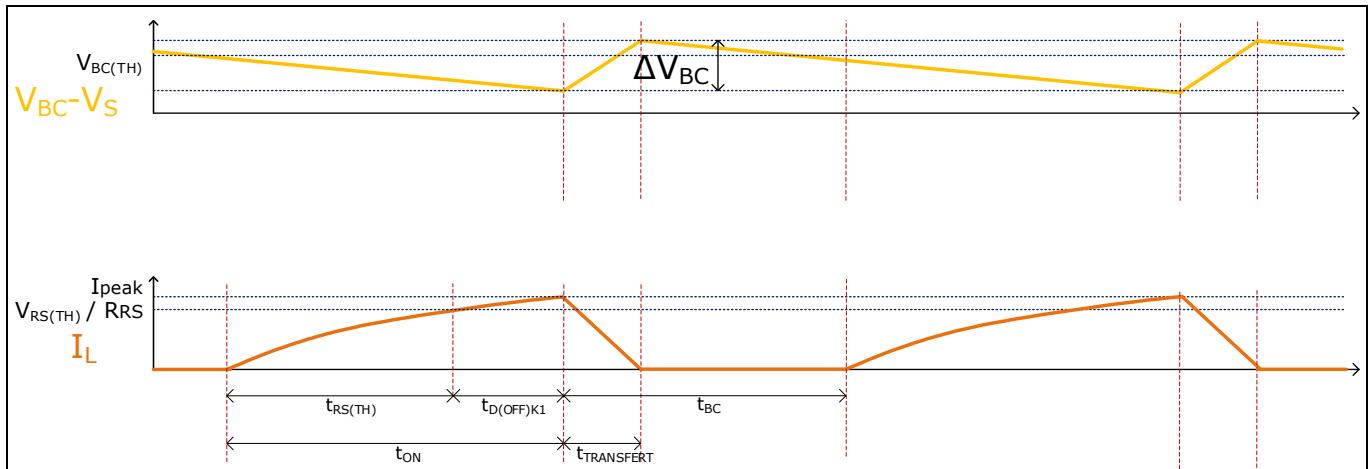

Assuming no leakage losses in  $C_{BC}$  capacitor, the charges going out  $C_{BC}$  with an  $I_{BC}$  current over the period  $T$  of the boost converter is equivalent to the charges received from the inductor over that same period of time. Therefore, assuming the amount of charges stays the same in and out  $C_{BC}$ , the time and current to transfer from  $L$  to  $C_{BC}$ , using  $Q=I*t$ ,  $T$  can be computed easily:

$$(8) \quad T = \frac{t_{transfert} * \frac{I_{peak}}{2}}{I_{BC}}$$

With

$$(9) \quad t_{transfert} = L * \frac{I_{peak}}{(V_{BC(TH)} + V_{FBC})}$$

Equation (9) uses  $V = L * \frac{di}{dt}$  approximation where  $V_{FBC}$  is the integrated boost converter diode (PRQ-148) and adds up to the boost converter output voltage.

**Figure 4** Boost converter theoretical waveform in discontinuous conduction mode (not to scale)

Note that  $I_{BC}$  varies with application temperature and therefore boost frequency varies with temperature.

The DG0 frequency can be simply monitored on pin DG0 in ON mode.

The automated calculations for expected boost converter frequency can be found in the excel workbook "Getting started with 2ED2410-EM, tab "boost converter sizing".

## 1.4 Sizing $R_{GATE}$

In power distribution applications, power availability is a critical topic. Our driver connects the gate of external MOSFET to the boost converter output, and therefore if a gate source degradation occurs in one MOSFET, it could trigger gate UVLO protection. But it also gives the opportunity to identify such a failure by sizing  $R_{GATE}$  properly without turning-off the switch.

$R_{GATE}$  can be sized so it limits the current to the maximum boost converter output current. As a result, the boost converter frequency will operate with greater frequency and can be easily monitored on pin DG0 in ON mode.

Since the boost converter frequency can be monitored by a microcontroller, it allows the car central computer unit to make power management decision in case of gate-source short detection on one MOSFET (e.g. turn-off some non-essential load to reduce power losses through the remaining MOSFET).

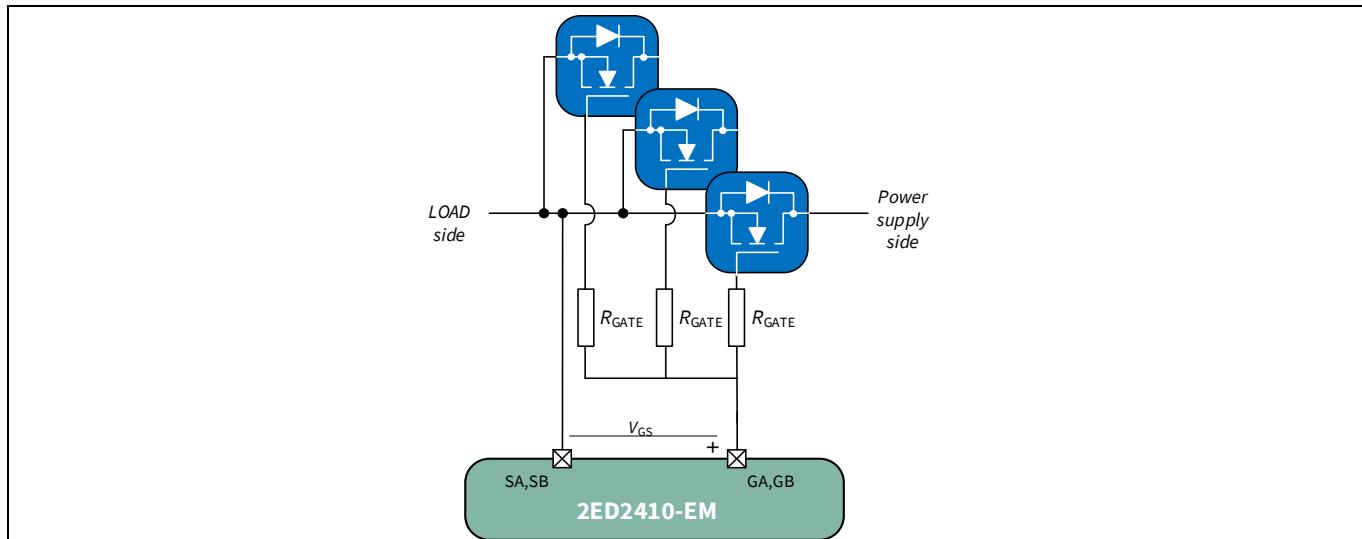

**Figure 5** Schematic of principle to identify  $R_{GATE}$  in the application

The max current which can be delivered by the boost converter is computed by:

$$(10) \quad I_{BC(MAX),disc.} = \frac{\Delta I_{peak} * t_{transfert}}{2 * (t_{ON(K1)} + t_{BC})}$$

This gives a minimum value for  $R_{GATE}$  according to:

$$(11) \quad R_{GATE(MIN)} = \frac{V_{BC(TH)}}{I_{BC(MAX)}}$$

The automated calculation can be found in the workbook “Getting started with 2ED2410-EM, tab “boost converter sizing.

#### 1.4.1 Example in application

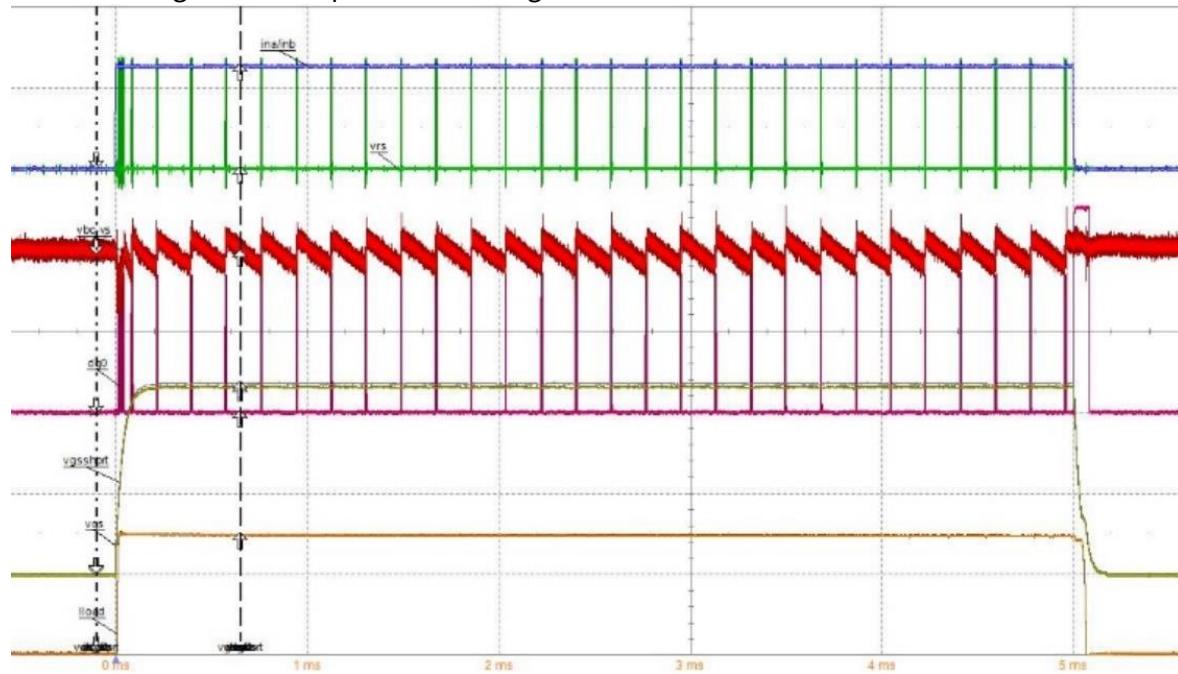

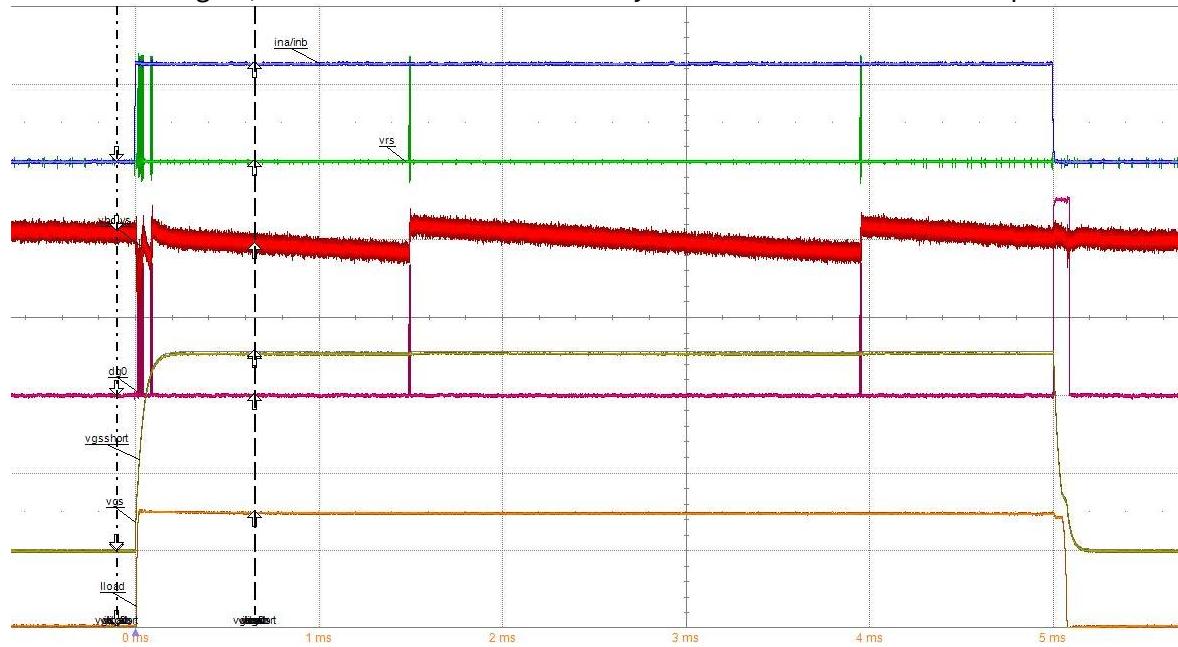

This figure shows an example  $R_{GATE}$  designed to sustain gate-source short and shows the effects on the gate driver signals. It uses 12 V demoboard with ES samples.

It is clear that the boost converter frequency is increased in case of gate-source short and proper RGATE value. As a result, the driver does not enter SAFESTATE but keeps the switch operating.

With shorted gate and adapted resistor so gate UVLO is avoided and the switch is maintained ON

With no shorted gate, normal boost converter activity can be monitored out of DG0 pin in ON mode

**Figure 6**  $R_{GATE}$  to prevent UVLO when gate-source short: with and without failure [blue: INx; green:  $V_{RS}$ ; red:  $V_{BC}-V_S$  (boost converter output); pink: DG0; yellow: gate-source on MOSFET; orange: LOAD current]

## 1.5 Reverse battery behaviour

Here is described the behaviour of the driver when reverse battery is applied. Two case are examined, common drain and common source MOSFET configuration.

*Note: for a third case, single high-side MOSFET control, there are no protection: no turn-on mechanism of the MOSFET in reverse battery is implemented. Therefore, if reverse battery occurs in this configuration, MOSFET destruction may occur because of power dissipated with the inverse current in the MOSFET body diode.*

#### 1.5.1 Common drain in reverse battery

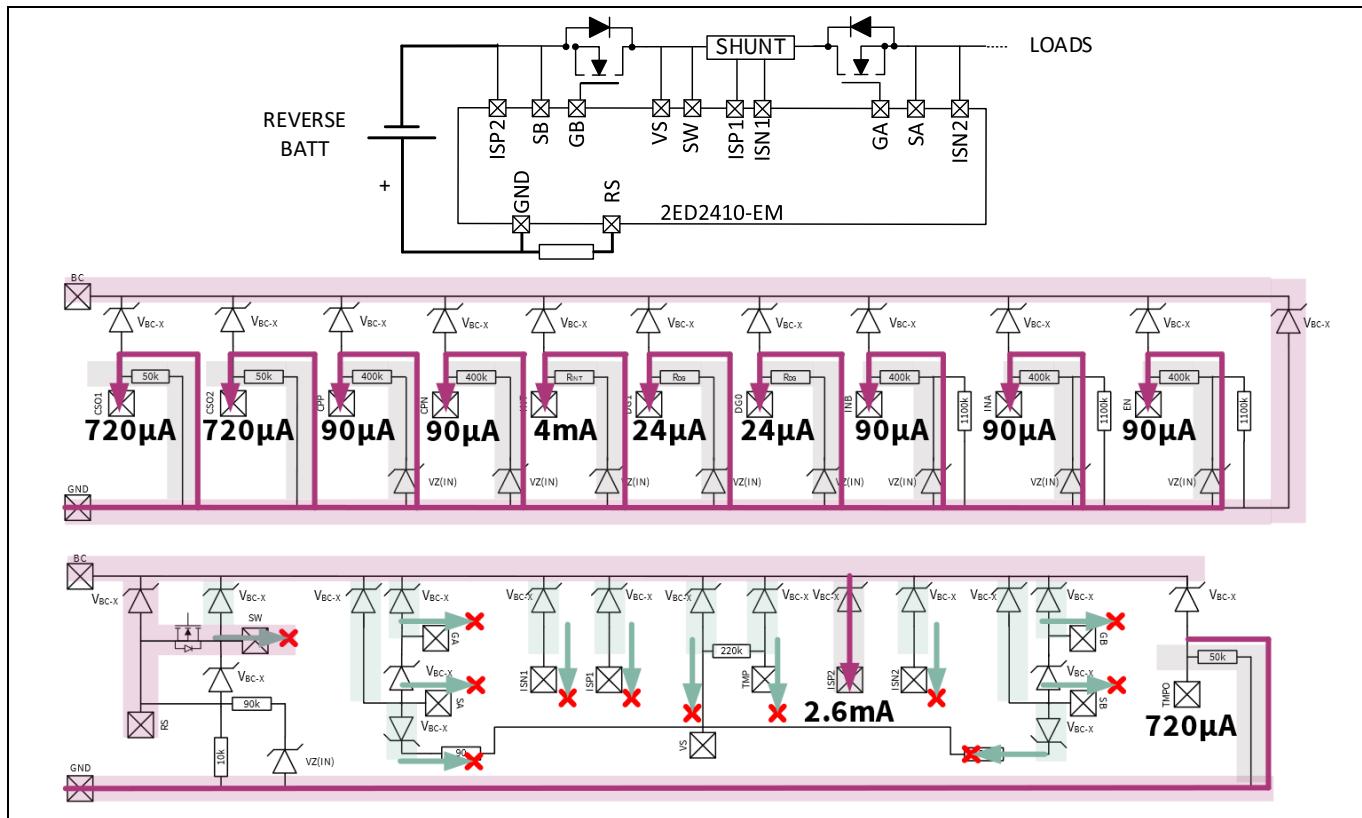

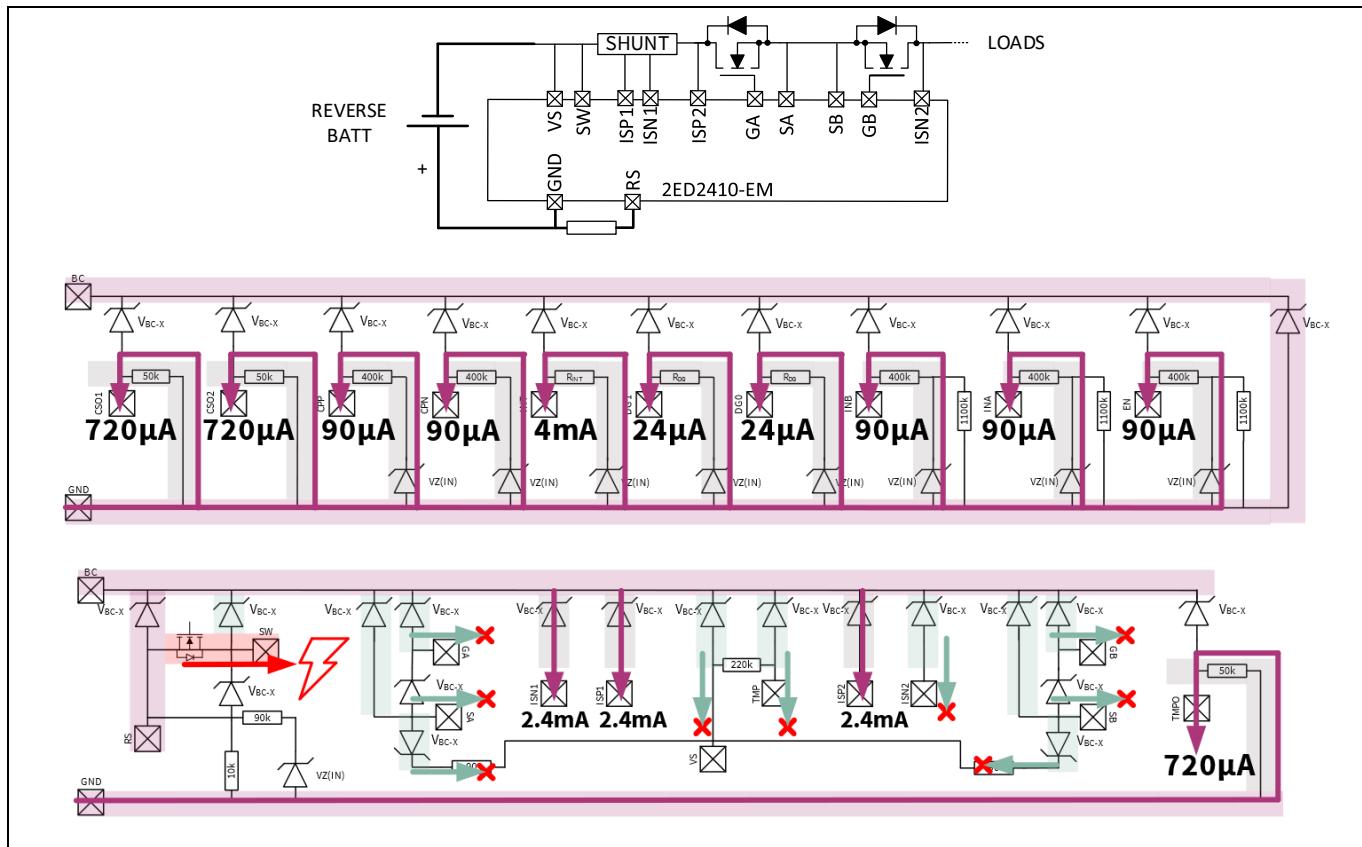

The following figure 8 describes the current leaking through the driver, in reverse battery @-36V, in common drain configuration. Refer to diodes diagram in datasheet for the original diodes diagram.

**Figure 7** 2ED2410-EM diodes diagram with typical leakages @-36V in common drain configuration

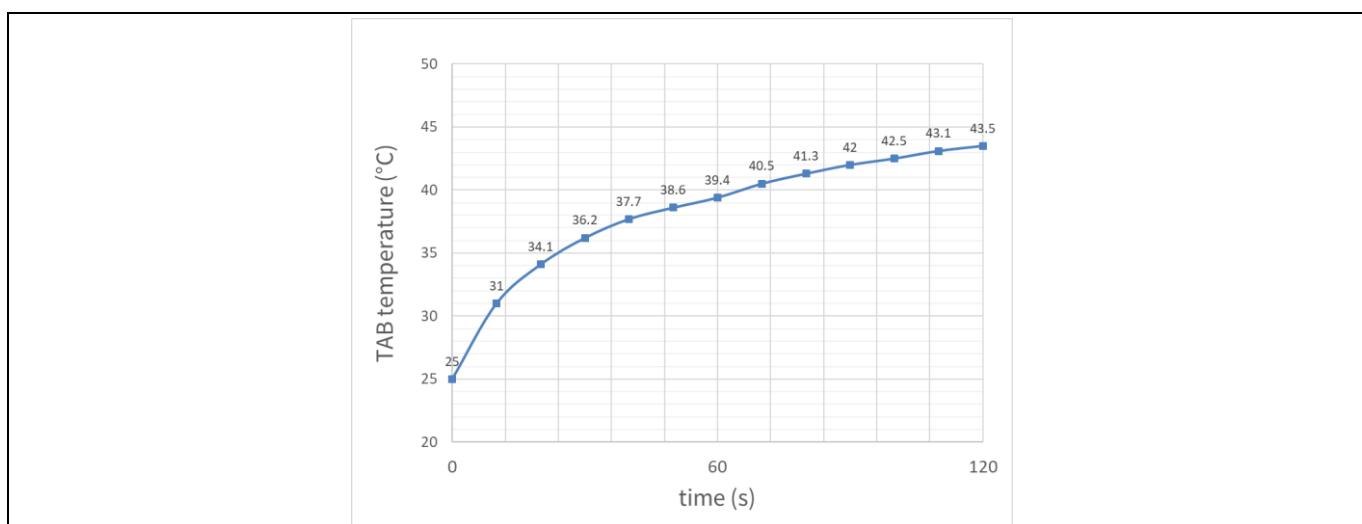

Due to the common drain structure, there is no current flowing back from load to battery. A 2-min test was conducted with reverse battery @-58V, see figure 9.

**Figure 8** Driver TAB temperature under -58 V reverse battery

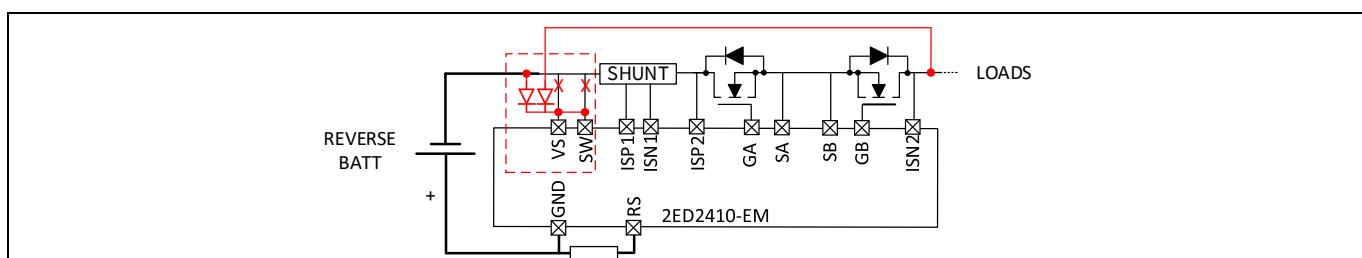

#### 1.5.2 Common source in reverse battery

The following figure 10 describes the current leaking through the driver, in reverse battery @-36V, in common source configuration. Refer to diodes diagram in datasheet for the original diodes diagram.

Due to the common source structure, current is flowing back from GND to battery mainly through RS to SW, the current being limited only by  $R_{RS}$  resistor. As a result, K1 MOSFET is likely to be destroyed because of the power dissipated in its body diode.

Figure 9 2ED2410-EM diodes diagram with typical leakages @-36V in common drain configuration

A diode must be used on VS and SW in order to prevent inverse current during reverse battery.

- This diode needs to have a rating sufficient to handle 200 mA, as per 2ED2410-EM driver datasheet [PRQ-16]. Ideally the voltage drop across this diode is as small as possible (e.g. 0.3 V Schottky diode) so VS pin voltage is as close as possible from ISP<sub>X</sub> pins voltage. The breakdown should be able to handle the expected worst case of reverse battery voltage.

- This diode can be an “OR” diode (e.g. BAT54C) to handle full bi-directional switch operation with common source configuration

Figure 10 Handling reverse battery and bi-directional switch with common source configuration

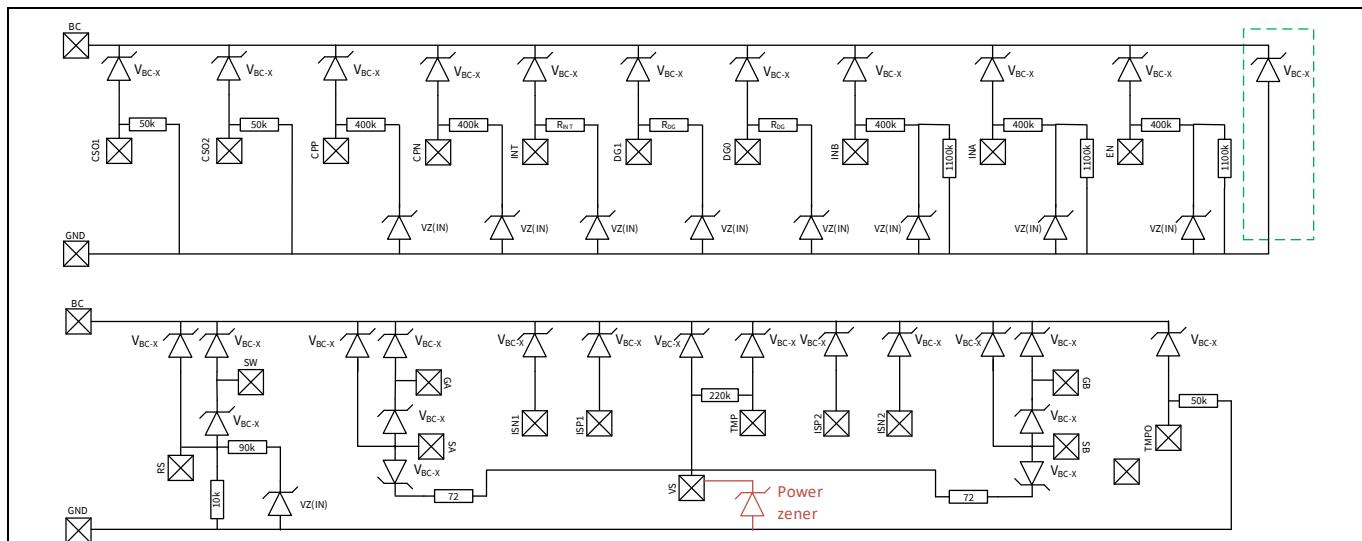

## 2 What to do with non-used pins?

2ED2410-EM has a lot of features and possibilities. After setting up the basics for driver operation, all functions may not be needed. Therefore, the non-used features can be disabled to save some current consumption or simplify routing on PCB. Disabling the non-used feature, the proper way, also ensures correct driver operation. The table below shows how to connect the pins in order to disable the corresponding features.

**Table 1 Connection of non-used pins**

| Pin # | Pin name | Pin type | How to connect pin to disable corresponding function                                                                                                                                                                                          |

|-------|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | CSO1     | I/O      | GND (FLOAT can trigger random latch on CSO1 internal comparator)                                                                                                                                                                              |

| 2     | CSO2     | O        | GND                                                                                                                                                                                                                                           |

| 3     | CPP      | I        | GND (FLOAT can trigger random latch CPP)                                                                                                                                                                                                      |

| 4     | CPN      | I        | EN (VS induces 'large' current consumption. GND can trigger random latch)                                                                                                                                                                     |

| 5     | INT      | O        | FLOAT                                                                                                                                                                                                                                         |

| 6     | DG1      | O        | FLOAT                                                                                                                                                                                                                                         |

| 7     | DG0      | O        | FLOAT                                                                                                                                                                                                                                         |

| 8     | INB      | I        | GND (FLOAT potential IBC increase, DPI sensitivity increased if SB GB floating, no IDLE mode)                                                                                                                                                 |

| 9     | INA      | I        | GND (FLOAT potential IBC increase, DPI sensitivity increased if SA GA floating, no IDLE mode)                                                                                                                                                 |

| 10    | EN       | I        | 5V (@GND driver will always remain in SLEEP mode. EN can also be connected to VS with 100k+diode so driver is by default in IDLE mode as long as a power supply is connected > Vzener+Vrev_diode is present on VS pin. diode: cathode on VS.) |

| 11    | GND      | I/O      | GND (never leave open: can randomly activate boost converter, IC destruction))                                                                                                                                                                |

| 12    | RS       | O        | FLOAT (when using external supply directly on BC, RS connection to GND could cause IC destruction)                                                                                                                                            |

| 13    | SW       | I        | FLOAT (in case of boost supply converter disconnection and driver external supply directly on BC)                                                                                                                                             |

| 14    | SA       | O        | FLOAT (if GA not used)                                                                                                                                                                                                                        |

| 15    | GA       | I/O      | FLOAT                                                                                                                                                                                                                                         |

| 16    | ISN1     | I        | GND/VS                                                                                                                                                                                                                                        |

| 17    | ISP1     | I        | VS/GND                                                                                                                                                                                                                                        |

| 18    | VS       | I/O      | VS (FLOAT: BC is not regulated, external MOSFET gate destruction expected).                                                                                                                                                                   |

| 19    | TMP      | I        | FLOAT                                                                                                                                                                                                                                         |

| 20    | ISP2     | I        | GND/VS                                                                                                                                                                                                                                        |

| 21    | ISN2     | I        | VS/GND                                                                                                                                                                                                                                        |

# Getting started with 2ED2410-EM

## Application note

### What to do with non-used pins?

| Pin # | Pin name | Pin type | How to connect pin to disable corresponding function                                                     |

|-------|----------|----------|----------------------------------------------------------------------------------------------------------|

| 22    | GB       | I/O      | FLOAT                                                                                                    |

| 23    | SB       | O        | FLOAT (if GB not used)                                                                                   |

| 24    | TMPO     | O        | FLOAT or GND                                                                                             |

| TAB   | BC       | O        | Boost capacitor $C_{BC}$ or external supply (see datasheet for $V_{BC}-V_s$ functional range [PRQ-339]). |

## 3 Enhanced functions and optional external components

**Attention:** *The electrical diagrams in this chapter are circuit propositions that need optimization and verification by the customer in the real application. The objective is to show the possibilities offered by the 2ED2410-EM driver. Other circuits may achieve the same goals.*

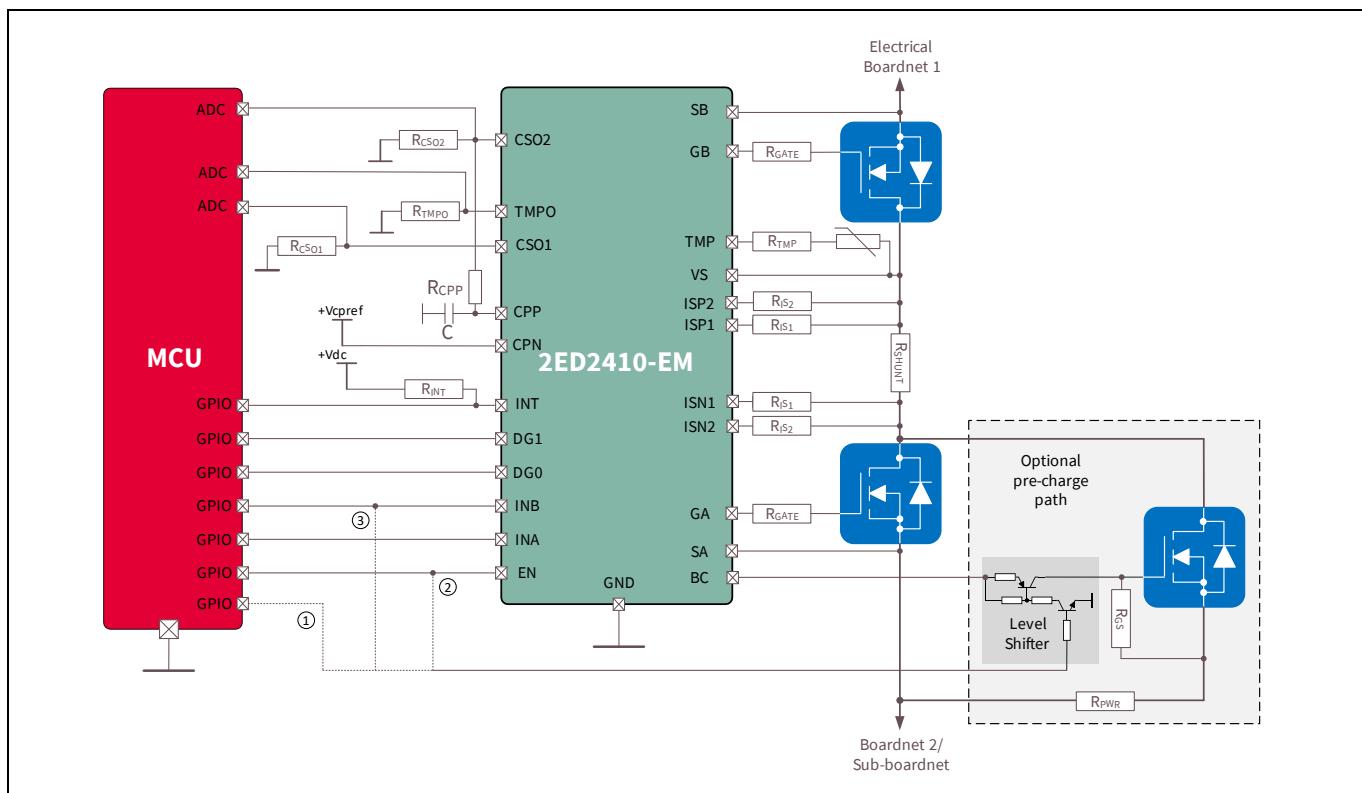

### 3.1 Simple pre-charge circuit

In this paragraph, a simple circuit and its control options are discussed. The goal is to enable pre-charging of board net circuit capacitances while making the best out of the 2ED2410-EM driver.

2ED2410-EM driver uses a boost converter as a supply (see chap. 1), and therefore this supply can be re-used with a level shifter to drive a by-pass circuit with a current limiting, power resistor, to charge capacitances with a constant current that will not trigger 2ED2410-EM protections.

Three options are proposed for operating the pre-charge circuit and described in the example of power supply protection switch (PSP) below. More are possible and this list aims to give an outlook on the possibilities with 2ED2410-EM driver.

1. First option uses another GPIO from the controller to drive the pre-charge on demand.

2. Second option ties the pre-charge circuit to EN pin, as soon as the driver enters IDLE mode, pre-charge will be enabled as well. Therefore, depending on EN pin type of connection (see chap 3.2), pre-charge could be enabled without microcontroller. It also has the advantage to save one GPIO.

In IDLE mode, it is possible to monitor the pre-charge status with DG0. DG0 monitors if SA node voltage is within  $V_{DS\_DIAG(TH)}$  range from VS voltage (see datasheet, chap. 7.1).

3. Third option sets the driver in ON mode. It also saves one GPIO compared to option 1. It has the advantage to set B MOSFET on, so there is no power dissipation in the body diode of MOSFET B compared to option 2. Additionally, protections from the driver are operational (including I-t wire protection) and measurements such as current sense can be used to check the pre-charge operation.

*Note: PSP in below example features I-t wire protection, common drain configuration, MOSFET tab temperature measurement. Many MOSFET can be used in parallel on each gate output thanks to strong gate drive (datasheet, chap. 4.3).*

**Figure 11 Power supply protection (PSP) switch example, with pre-charge circuit and its different control options**

*Note: Infineon enhanced BSS83P PMOS and 2N7002 NMOS can replace PNP and NPN in the level shifter.*

*Note: Gate-source resistor is needed for the pre-charge MOSFET to maintain it off when PNP (or PMOS) is open.*

*Gate-source resistors are not needed for power MOSFET in the main current path because the driver pulls down gate-source by default as long as a VS voltage is present.*

## 3.2 IDLE as default mode (undervoltage auto-restart)

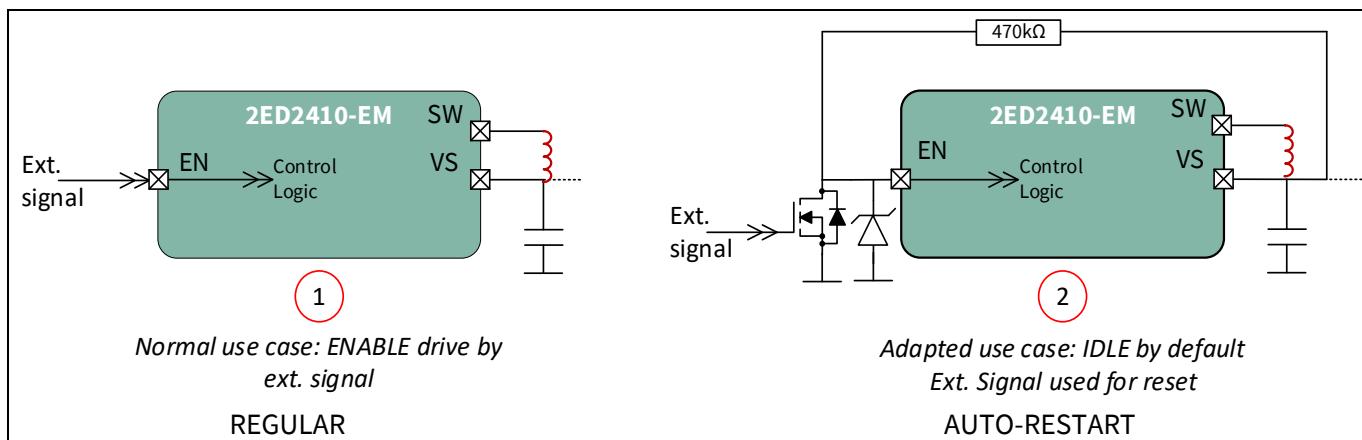

In automotive power distribution, it can be mandatory for the switch to auto-restart by itself in case of micro-cuts on the power supply. A simple way to do so with 2ED2410-EM is to link the EN pin to VS though a very high-ohmic resistor and use a zener between EN and GND to fix the EN pin voltage to any custom value that suits the application. As a result, the driver is in IDLE mode by default.

In order for the driver to be reset externally, a simple small signal NMOS can be used to pull-down EN pin voltage.

**Figure 12 Schematic from datasheet, improved. Regular and UV auto-restart configuration**

In case of undervoltage, if  $VS < 0.7V$ , EN will reset if it goes to SAFESTATE. In configuration 2, the driver will go to SAFESTATE because of  $C_{BC}$  discharge (when VS is close to 0 V, the boost converter cannot maintain  $C_{BC}$  charged.  $C_{BC}$  discharges and as a result the driver would enter SAFESTATE because of gate UVLO (see datasheet).

*Note: If the expected voltage drop, on VS, is  $\geq 3$  V, there is no need for the auto-restart configuration, because the driver will keep operating in ON mode normally. Only the current sense amplifiers outputs would be affected by desaturation, and as a result a lower short-circuit limit during the drop (see datasheet chap. 8.1, Figure 23 & 24).*

The auto-restart and regular 2ED2410-EM configurations were tested against well-known ISO16750-2-4.6.2 standard reset behaviour at 0 V voltage drop.

The two tables below show the functional status expected from the ISO16750 and the actual status observed during the test in each configuration.

**Table 2 ISO16750-2 results in regular configuration (3.3 μF capacitor between VS and GND)**

| t1                                            | Functional status expected | Functional status observed |

|-----------------------------------------------|----------------------------|----------------------------|

| $>10 \mu s$ to $100 \mu s$ - int = $10 \mu s$ | A                          | A                          |

| $100 \mu s$ to $1 ms$ - int = $100 \mu s$     | C                          | D                          |

| $1 ms$ to $10 ms$ - int = $1 ms$              | C                          | D                          |

| $10 ms$ to $100 ms$ - int = $10 ms$           | C                          | D                          |

| $100 ms$ to $2 s$ - int = $100 ms$            | C                          | D                          |

**Table 3 ISO16750-2 results in auto-restart configuration (3.3 μF capacitor between VS and GND)**

| t1                                            | Functional status expected | Functional status observed |

|-----------------------------------------------|----------------------------|----------------------------|

| $>10 \mu s$ to $100 \mu s$ - int = $10 \mu s$ | A                          | A                          |

| $100 \mu s$ to $1 ms$ - int = $100 \mu s$     | C                          | C                          |

| $1 ms$ to $10 ms$ - int = $1 ms$              | C                          | C                          |

| $10 ms$ to $100 ms$ - int = $10 ms$           | C                          | C                          |

| $100 ms$ to $2 s$ - int = $100 ms$            | C                          | C                          |

## 4 Amplifiers set-up

Note: *Wire protection is not covered in this application note and is described in a separate application note.*

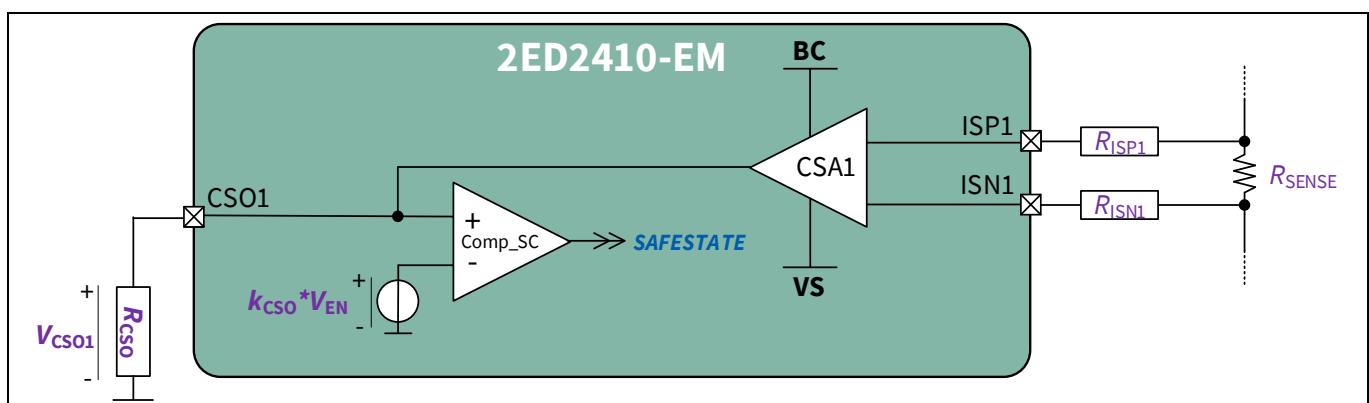

### 4.1 Current sense set-up

This chapter details calculation on how to set-up a correct short-circuit limit. The sensing element, here a shunt resistor, is assumed already chosen by the customer (based on application thermal requirements). The EN pin voltage is either fixed by the low voltage power supply or the microcontroller. To set-up the correct protection threshold and consistent current reading,  $R_{ISP}$ ,  $R_{ISN}$  and  $R_{CSO}$  need to be determined according the customer target.

Figure 13 Overview of bi-directional current sense amplifier CSA1

Note: CSA2 is identical, but does not feature comparator on output for protection

Target: set a short circuit protection at  $I_{SC}=200$  A, with shunt resistor  $R_{SENSE}=200 \mu\Omega$ ,  $V_{EN} = 3.3$  V

Calculation steps:

- Compute the voltage drop across the sensing element at the desired short-circuit limit:

$V_{SENSE(SC=200A)} = R_{SENSE} * I_{SC} = 200 * 2e-4 = 40 \text{ mV}$

- Compute the threshold detection voltage of CSO1 comparator that needs to be matched by  $V_{SENSE(SC=200A)}$ :

$V_{CSO(TH)} = k_{CSO(TH)} * V_{EN} = 0.74 * 3.3 = 2.44 \text{ V}$

- Compute the gain needed for matching  $V_{SENSE(SC=200A)}$  and  $V_{CSO(TH)}$ :

$G_{CSO} = V_{CSO(TH)} / V_{SENSE} = 2.44 \text{ V} / 0.04 \text{ V} = 61 \text{ V/V}$

- Once the gain is computed, resistors setting the gain need to be selected. For example, amplifier output resistor  $R_{CSO}$  is chosen typical at 20 k $\Omega$  [PRQ-326]

- Therefore, the amplifier inputs resistors can be computed by:

$R_{ISP/ISN} = R_{CSO} / G_{CSO} = 20000 / 61 = 327 \Omega$

Using the couple of values  $\{R_{CSO}, R_{ISP/ISN}\} = \{20 \text{ k}\Omega; 327 \Omega\}$  with a  $R_{SENSE}=200 \mu\Omega$  shunt will provide a turn-off managed by 2ED2410-EM enabled at  $V_{EN} = 3.3$  V when the current reaches 200 A.

The automated calculations can be found in the workbook, tab “CSA set-up”.

Note: The current sense amplifier CSA2 does not feature an internal comparator on its output for protection.

Therefore, the gain can be set freely according to customer needs. The gain of amplifier CSA2 does not need to be equal to the gain of amplifier CSA1.

## 4.2 Temperature sense set-up

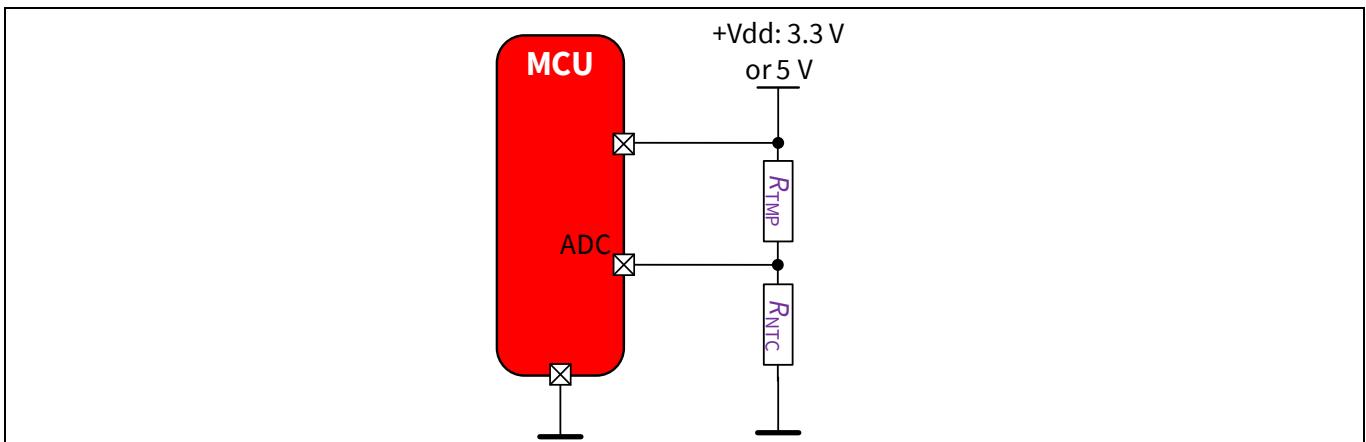

The main drawback of the "standard solution", is that it needs to use Vdd of microcontroller.

Figure 14 Basic temperature sense circuit

Therefore, it is complicated to route on layout the NTC (or another thermistor used) to the MOSFET TAB and back to the microcontroller. Also, this basic circuit draws additional consumption permanently (as long as Vdd is still ON), meaning, it would need additional components to control it with a small NPN or NMOS to activate or deactivate it (and therefore an additional  $\mu$ C GPIO used).

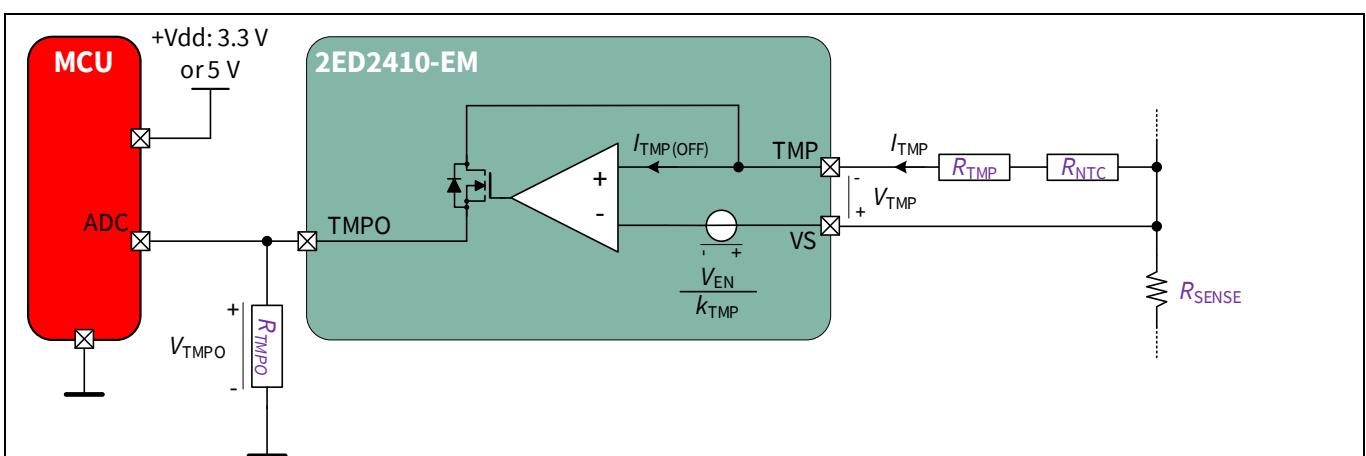

The purpose of 2ED2410-EM's temperature amplifier is to sense switch temperature (= MOSFET TAB temperature). The advantage from 2ED2410-EM solution is that the Vdd is replaced by the battery line voltage and therefore the thermistor (PTC or NTC) is in the upper position. Therefore, it is very easy to route the layout of the thermistor close to MOSFET TAB (See chapter 5.2 for routing example).

Figure 15 Overview of temperature amplifier sense TMPA

Other advantages are the following:

- The output of TMPA amplifier is independent of battery voltage, and varies according to the resistors' settings. Not the case with basic temperature sensing circuit shown in Fig. 10.

- The consumption of TMPA amplifier itself is low. Also, this additional self-consumption current is not present in IDLE or SLEEP mode, because the amplifier is not activated in those modes.

- The output can be linearized easily using  $R_{\text{TMP}}$  resistor. Therefore, temperature can be sensed accurately over a wide range (e.g. from 0 °C to 150 °C). It can be easily verified with demoboard and a temperature sensor.

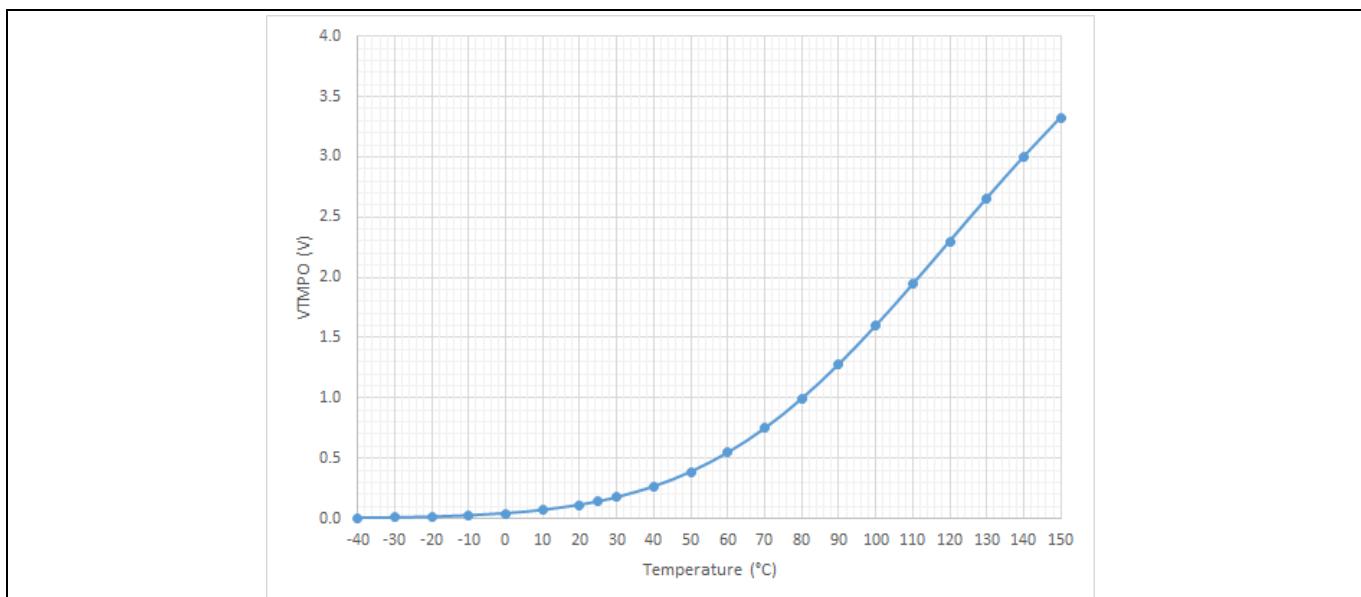

#### 4.2.1 TMPA target curve calculation example

TMPA is an amplifier of current. The current  $I_{\text{TMP}}$  is conserved through the temperature amplifier, which, by neglecting  $I_{\text{TMP(OFF)}}$ , can be written by:

$$(12) \quad I_{\text{TMP}} = \frac{V_{\text{TMP}}}{(R_{\text{NTC}} + R_{\text{TMP}})} = \frac{V_{\text{TMPO}}}{R_{\text{TMPO}}}$$

In equation (10),  $R_{\text{NTC}}$  is the thermistor (in this case an NTC thermistor) resistance which varies with the temperature, and  $R_{\text{TMP}}$  is a normal resistor used to linearize the thermistor behaviour with respect to temperature, positioned as per figure 11. Therefore,  $V_{\text{TMPO}}$  can be written as:

$$(13) \quad V_{\text{TMPO}} = \frac{V_{\text{TMP}} \times R_{\text{TMPO}}}{(R_{\text{NTC}} + R_{\text{TMP}})}$$

By replacing  $V_{\text{TMP}}$  from  $k_{\text{TMP}}$  [PRQ-187] datasheet equation (11), in equation (11) here, also considering the input offset of TMPA [PRQ-186], it gives:

$$(14) \quad V_{\text{TMPO}} = \left( \frac{V_{\text{EN}}}{k_{\text{TMP}}} + V_{\text{TMP(OFFSET)}} \right) \times \frac{R_{\text{TMPO}}}{(R_{\text{NTC}} + R_{\text{TMP}})}$$

Computed for different temperature values, it allows to trace  $V_{\text{TMPO}}(V) = f(T(\text{°C}))$ , depending on the law used to describe the temperature variation of the thermistor.

Example in figure 12 below, with  $V_{\text{EN}} = 3.3 \text{ V}$ , and automotive qualified 47 kΩ NTC and  $R_{\text{TMP}} = 1.2 \text{ kΩ}$ , the equation (13) below was used to compute  $R_{\text{NTC}} = f(T(\text{°C}))$ , where  $T$  and  $T(25 \text{ °C})$  are expressed in Kelvin:

$$(15) \quad R_{\text{NTC}} = R_{(T=25\text{°C})} \times e^{\beta \times \left( \frac{1}{T} - \frac{1}{T(25\text{°C})} \right)}$$

Figure 16 Example of curve  $V_{\text{TMPO}}(V) = f(T(\text{°C}))$

## 5 PCB layout recommendations

**Attention:** *The PCB traces examples in this chapter are proposed layout solutions and are not mandatory. Those propositions are standard and final implementation depends on customer layer stack and must be verified by the customer in the real application. Other layouts may achieve the same goals.*

### 5.1 SW, BC and RS pin routing

In this sub-chapter is given a non-exhaustive list of advices in order to route properly the 2ED2410-EM amplifiers on the PCB.

- SW is the main supply of the driver (input of boost converter, see datasheet chap. 9). The maximum current peak is 200mA (driver max. ratings, see datasheet chap 3 PRQ-16), therefore standard trace length on standard thickness is enough (35µm, 0.254mm/10mil) for power dissipation considerations. However, in order to optimize boost converter efficiency, parasitic resistance of the trace must be kept to minimum.

*Note: The SW pin must be routed separately from current senses and temperature senses strips, because the pulses in the range of hundreds of mA would highly disturb current sense reading and may cause unintended SAFESTATE trigger in some situations. Only VS could be routed together from the main power line.*

**Table 4 SW pin routing**

| Optimization      | Power/Thermal reasons                                                            | Parasitic resistance                                                                                      | Parasitic capacitance                                                             |

|-------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Width             | According to PRQ-16, 2ED2410-EM datasheet. Standard width trace is generally ok. | Augment width based on PCB thickness. Ideally, $(R_L + R_{TRACE}) < 3\Omega$                              | Reduce width based on distance between top layer strip and embedded plane         |

| Inductance choice | No specific adjustment.                                                          | Choose an inductor with a parasitic resistor as small as possible. Ideally, $(R_L + R_{TRACE}) < 3\Omega$ | As close as possible from SW pin (<10 mm) to limit parasitic capacitance (<10 pF) |

- For BC tab,  $C_{BC}$  capacitor should be placed as close as possible from driver tab, ideally <10mm, to minimize stray inductance. Connection to VS must be direct with no cap to GND in between.

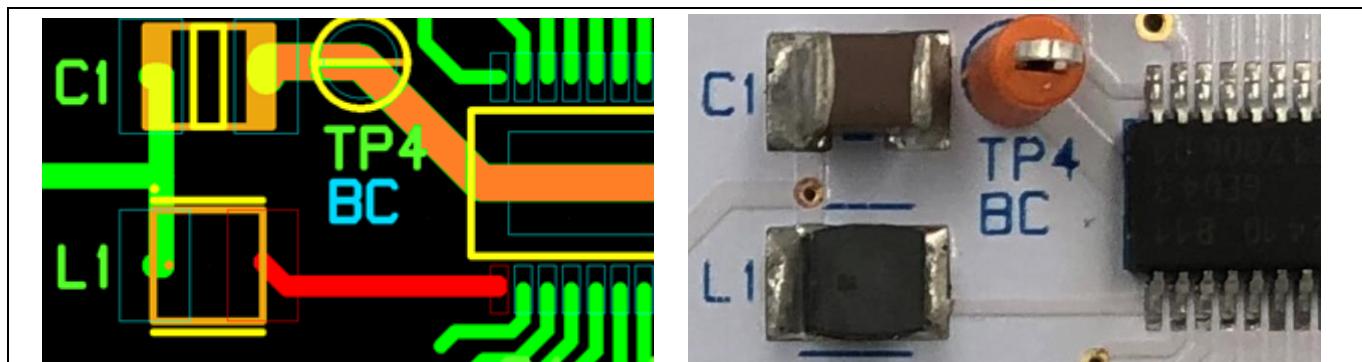

**Figure 17 SW pin correct routing example (red) with VLS3015CX-101M-H and  $C_{BC}$  routing (orange)**

### PCB layout recommendations

- RS pin is the output of the boost converter. Therefore, connection to GND through the RS resistor should be also as short as possible (see 5.4, same recommendation than GND pin after RS resistor).

## 5.2 VS node routing

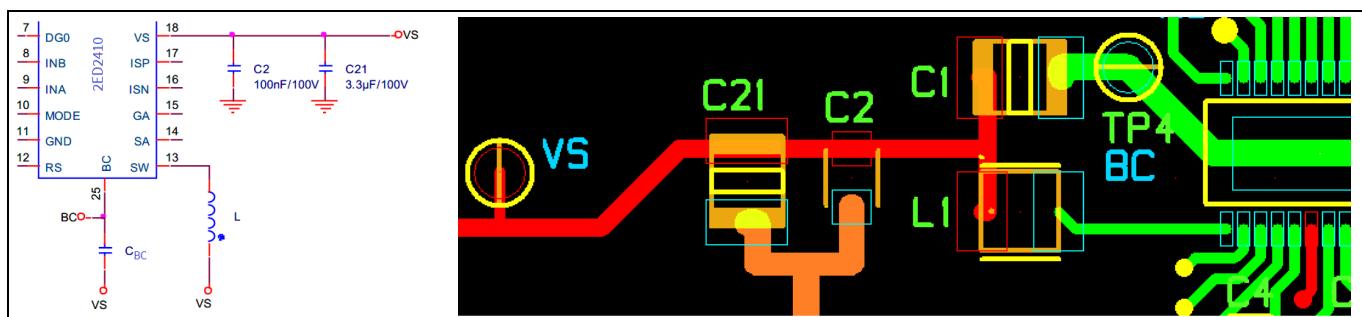

For protection purposes (ESD, ISO7637 transient disturbances), it may be needed to use capacitors and/or a zener diode on the VS pin depending on the conditions (see chapter 6.1 protecting the VS node).

However, it has to be noted that in order to supply the amplifiers correctly, the  $V_{BC}-V_S$  voltage must be kept stable [PRQ-339]. Therefore, any filtering on the VS pin should also apply to BC capacitor and L connection to VS node.

**Figure 18 VS pin schematic and correct routing example (red) with filtering caps and GND (orange)**

Because amplifiers are supplied between BC and VS, one of the two inputs of the amplifier has to be ideally placed on the VS node for better amplifier performance.

## 5.3 Amplifiers routing

In this sub-chapter is given a non-exhaustive list of advices in order to route properly the 2ED2410-EM amplifiers on the PCB.

- Amplifiers are supplied between BC and VS. See datasheet chapter 7.2 for details. Therefore, it is not advised to use capacitors between the amplifiers input pins and GND.

- Output amplifier resistor  $R_{CSOx}$  [PRQ-326] and amplifier gain  $G$  [PRQ-317] parameters must be respected in the application.

- Input and output amplifiers resistors are advised at 1% accuracy or better and ideally close to the device.

- Ideally the two input traces should be routed together. The parasitic resistance of the traces must not influence the desired gain in the application. Straight lines are advised to avoid any antenna/loop effects.

- To optimize the noise on current reading, the input amplifiers resistors  $R_{ISPx/Nx}$  have to be minimal, as parasitic noise increases with resistance.

- Even if  $R_{ISPx}$  or  $R_{ISNx}$  is electrically on the same node as VS and L1 connection, they must be routed separately to avoid interference from VS and SW pin current, that could create a parasitic voltage drop across  $R_{ISPx}$  or  $R_{ISNx}$  (R6 or R7 in the diagram below) and therefore perturbate amplifier operation.

**Figure 19 Example of amplifier correct routing from shunt resistor (red) and from input resistance to pins (orange)**

*Note: Vias do not impact accuracy are their internal resistance is negligible.*

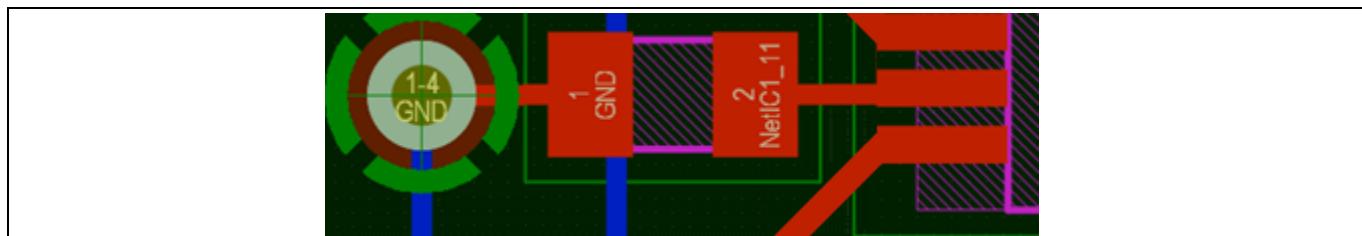

## 5.4 GND pin

The GND pin trace should be as short as possible to a GND plane or to the GND connector. If a GND plane is used, located below the driver, it is good practice to separate signal GND from power GND (for example if a freewheeling diode is used on PCB where the 2ED2410-EM is located).

A small, optional, resistor (see chap. 6.3) could be used on the GND pin to increase ESD module robustness or BCI robustness in case of failures, or for safety reasons (see 2ED2410-EM Safety Application Note). In this case, again, the path should be as shorter as possible.

**Figure 20 Example of GND correct routing with the optional additional resistor and connection to GND plane with standard via (green)**

## 6 External parts for driver protection

### 6.1 Protecting the VS node

The 2ED2410-EM diode diagram shows us that the zener diode between BC and GND is the critical path that should be protected against overvoltage in order to preserve the driver integrity.

- Due to the boost converter between BC and VS, the VS node has to be protected against spikes greater than  $V_{BC-GND} - V_{BC(TH)MAX}$ , giving 75 V-14 V=61 V.

Figure 21 Diode diagram with BC-GND highlighted (green) and optional power diode (red)

- 1-5 W power zener is advised, when using MOSFET with a breakdown voltage equal or greater than 60 V. For example, this protection diode is not needed when using 40 V MOSFET, because the breakdown voltage of a 40 V MOSFET is below 61V.

### 6.2 ISO7637 transient pulses and DPI protections

*Note: This section does not give a list of mandatory components that must be used in the application. It gives a list of possible solutions that can improve 2ED2410-EM behaviour during EMC tests.*

Table 5

| Pin connection      | Purpose            | Counter-measure        | PCB layout recommendation                                        |

|---------------------|--------------------|------------------------|------------------------------------------------------------------|

| VS-GND              | ISO7637 pulse 3b   | $C_{VS} = 3.3 \mu F$   | According chapter 5.2.<br>Zener in chap.6.1 can replace $C_{VS}$ |

| SA-GND and SB-GND   | DPI/BCI robustness | $C_{SX} = 10 nF$       | Between MOSFET source and GND plane (power).                     |

| ISPx-BC and ISNx-BC | DPI robustness     | $C_{ISXX-BC} = 1 nF$   | As close as possible from driver for shortest path to BC.        |

| VS-SA or VS-SB      | BCI robustness     | $C_{VS-SX} = 1-100 nF$ | Snubber capacitor across MOSFET drain-source                     |

*Note: Details of 2ED2410-EM EMC tests can be delivered on-demand.*

## 6.3 ESD components and layout recommendation

*Note: This section does not give a list of mandatory components that must be used in the application. It gives a list of possible solutions that can fix a behaviour, based on experiments and experience of the Infineon application and design team with gate drivers.*

For ESD automotive qualification, at device level, there are no additional components used. The bare driver passed the qualification HBM AEC-Q100 as per specified in the datasheet [PRQ-130].

For ESD module level ESD tests, options are available if the driver in typical application does not comply with customer end test at module level:

**Table 6**

| Pin connection | Purpose                                        | Counter-measure             | PCB layout recommendation                                                                                   |

|----------------|------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------|

| GND            | Improve BC-GND zener diode robustness          | $R_{GND} = 50-100 \Omega$   | PCB trace as short as possible (to limit stray inductance) to GND PCB plane (analog). See chap. 5.4.        |

| VS-GND         | Improve module ESD robustness, dV/dt filtering | $C_{VS} = 1-470 \text{ nF}$ | PCB trace as short as possible (to limit stray inductance) to GND PCB plane (power). See cap C2 in fig. 15. |

## 7 Quiescent current example

This chapter shows the formulas how to compute quiescent current and shows real-life examples of consumption in 4 operating modes of the 2ED2410-EM driver.

- Power supply of driver is a boost DC/DC converter with integrated diode and switch (K1 MOSFET, see fig. 1)

- The quiescent current of 2ED2410-EM is then related to the efficiency of the boost converter and to the battery voltage

- The efficiency depends on the boost converter external components

For this reason, quiescent current is measured from the battery line rather than the ground connection of the device.

- Due to the variety of choices of external components, Infineon cannot commit on a specific quiescent current value from battery

- Infineon can only commit to the driver consumption itself, measured on pins BC and VS in production test and characterisation (see datasheet chap. 4.5 for the current consumption parameters).

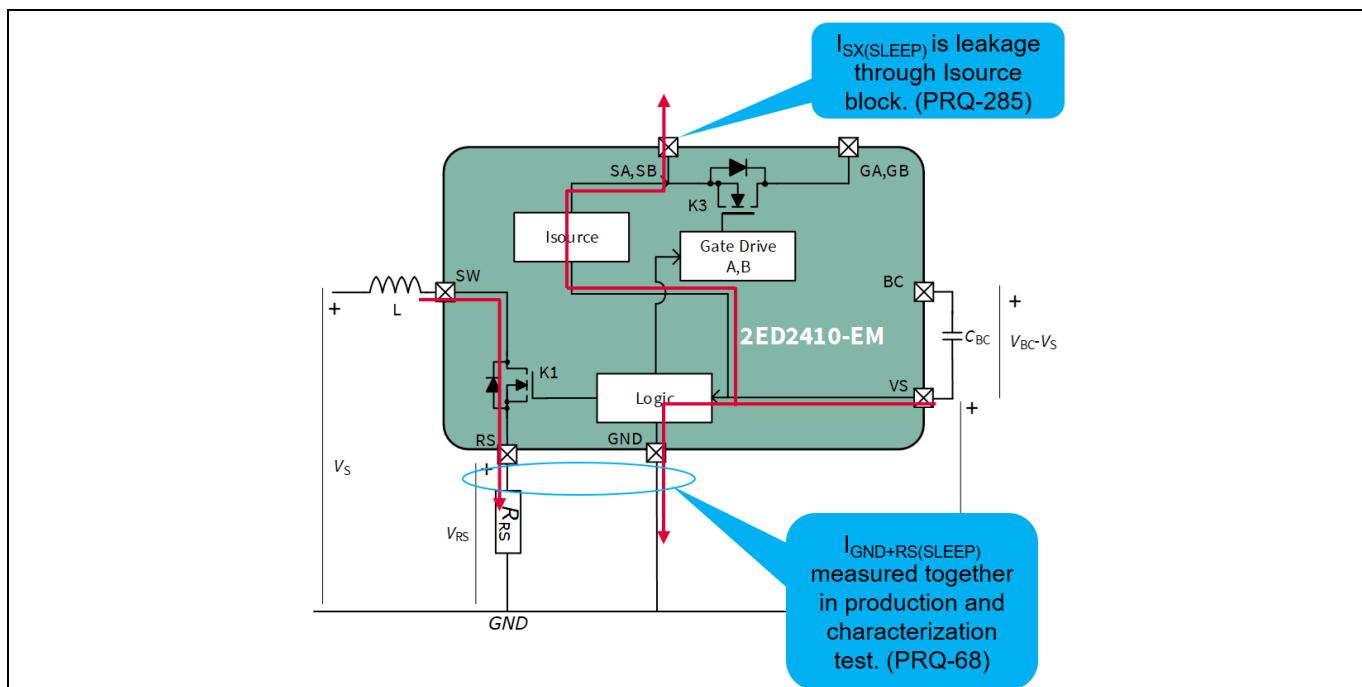

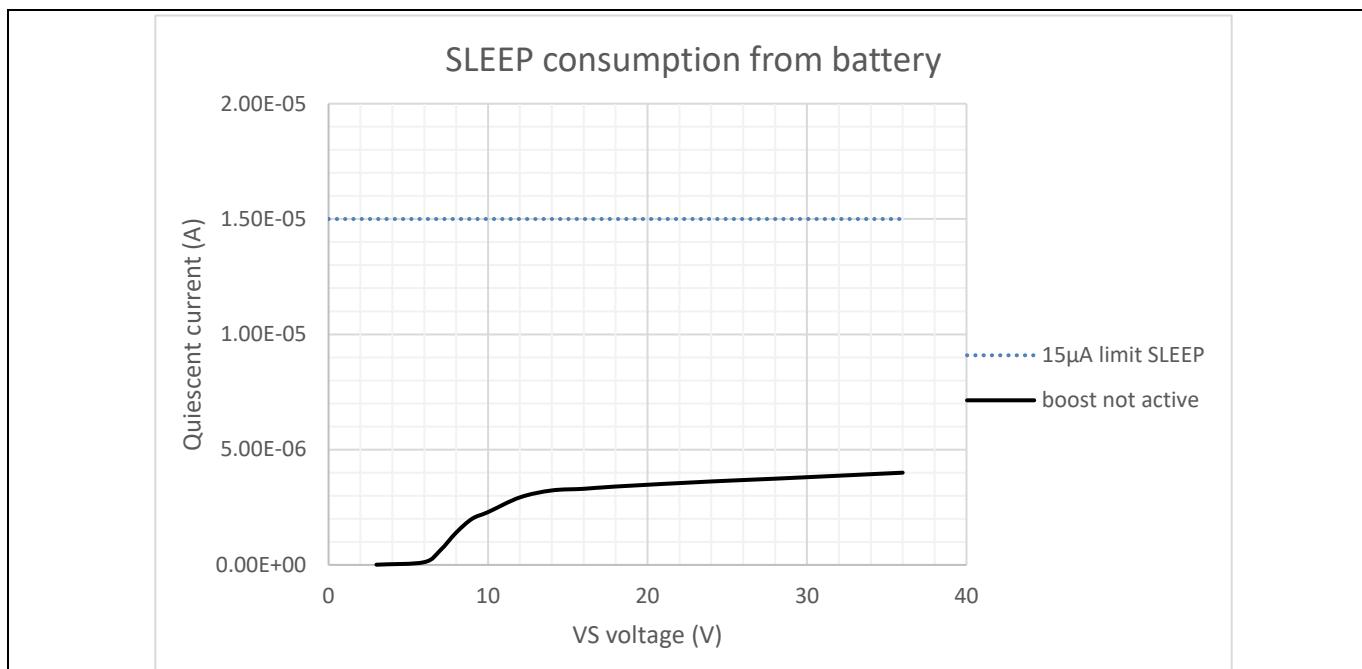

### 7.1 SLEEP mode

In SLEEP mode, the boost converter is not active. The quiescent current can be measured on GND+RS pin plus the source SA or SB pin depending on connection in application.

$$(16) \quad I_{q(SLEEP)} = I_{GND+RS(SLEEP)} + I_{SA(SLEEP)}^1 + I_{SB(SLEEP)}^1$$

1) To be considered only if SA or SB is below VS voltage

Figure 22 Current paths in SLEEP mode

**Figure 23 Quiescent current measurement of 2ED2140-EM in SLEEP mode @25°C (boost converter not active)**

## 7.2 IDLE mode

In IDLE mode, the boost converter is active. However, amplifiers and comparators, main contributors to current consumption, are not active. External MOSFETs are OFF.

(11) is the general efficiency equation applied to our boost converter:

$$(17) \quad \eta = \frac{P_{OUT}}{P_{IN}} = \frac{I_{BC} \cdot V_{BC}}{I_{SW} \cdot V_S}$$

The current drawn from the battery in IDLE is the sum of the current pulled by the boost input (SW) and VS pin.

$$(18) \quad I_{q(IDLE)} = I_{BAT} = I_{SW} + I_{VS(IDLE)}$$

Combining (11) and (12) gives:

$$(19) \quad I_{q(IDLE)} = \frac{I_{BC(IDLE)} \cdot V_{BC}}{\eta \cdot V_S} + I_{VS(IDLE)}$$

There is no easy way to compute efficiency; therefore, a tool will be provided at product release; in the meantime, excel calculation workbook can be used for estimation.

**Figure 24** Current paths in IDLE mode

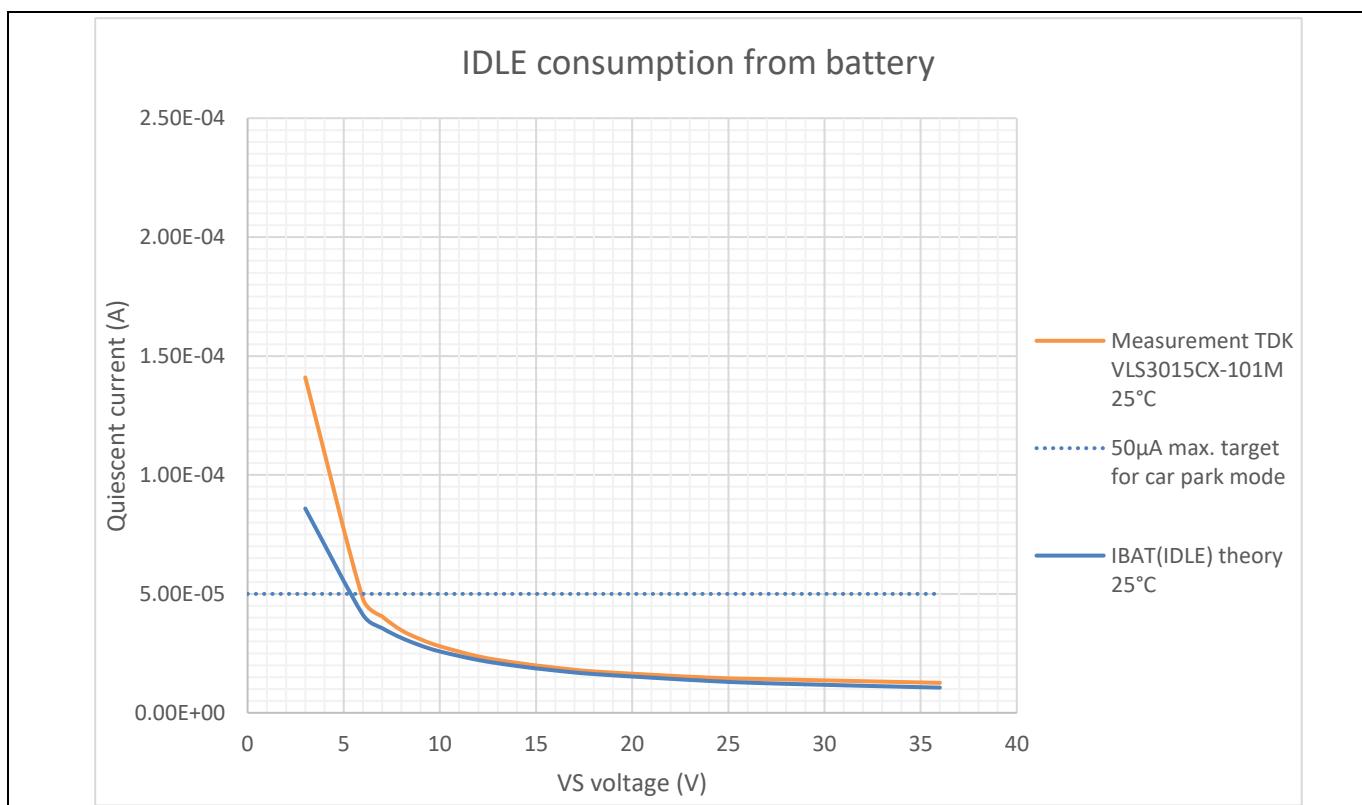

The below graph shows the correlation between theoretical calculation and measurement from evaluation board. It is measured in open load to avoid interference of the  $I_{SOURCE}$  function (see datasheet chap. 6).

**Figure 25** Quiescent current of 2ED2410-EM in IDLE mode @25°C, open load, using TDK VLS3015CX-101M and  $R_{RS}=10\ \Omega$

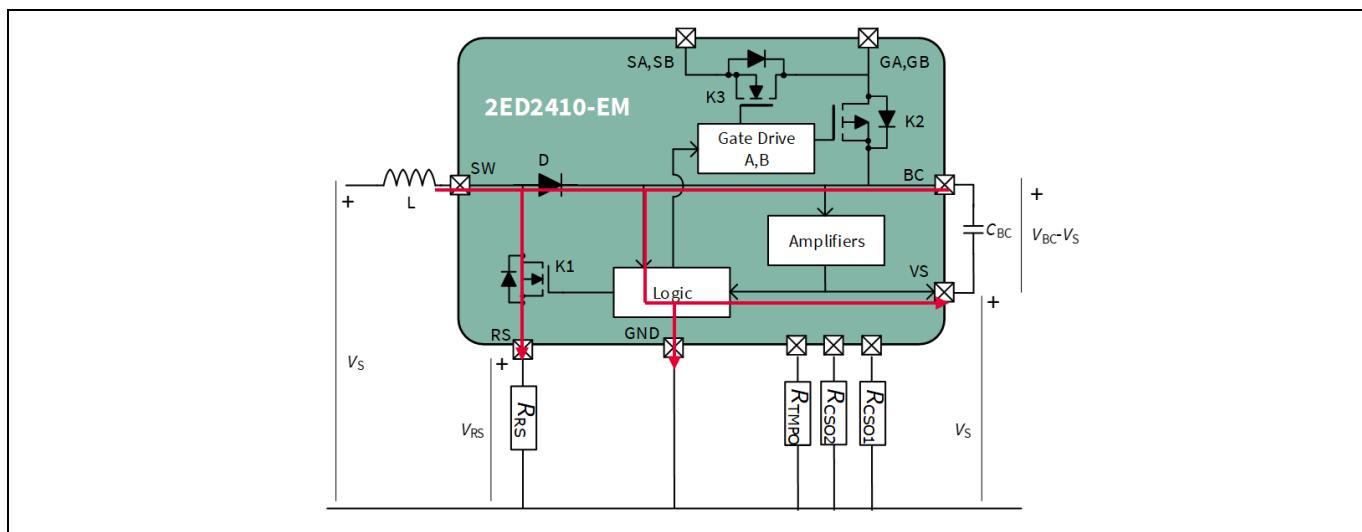

## 7.3 ON/SAFESTATE mode

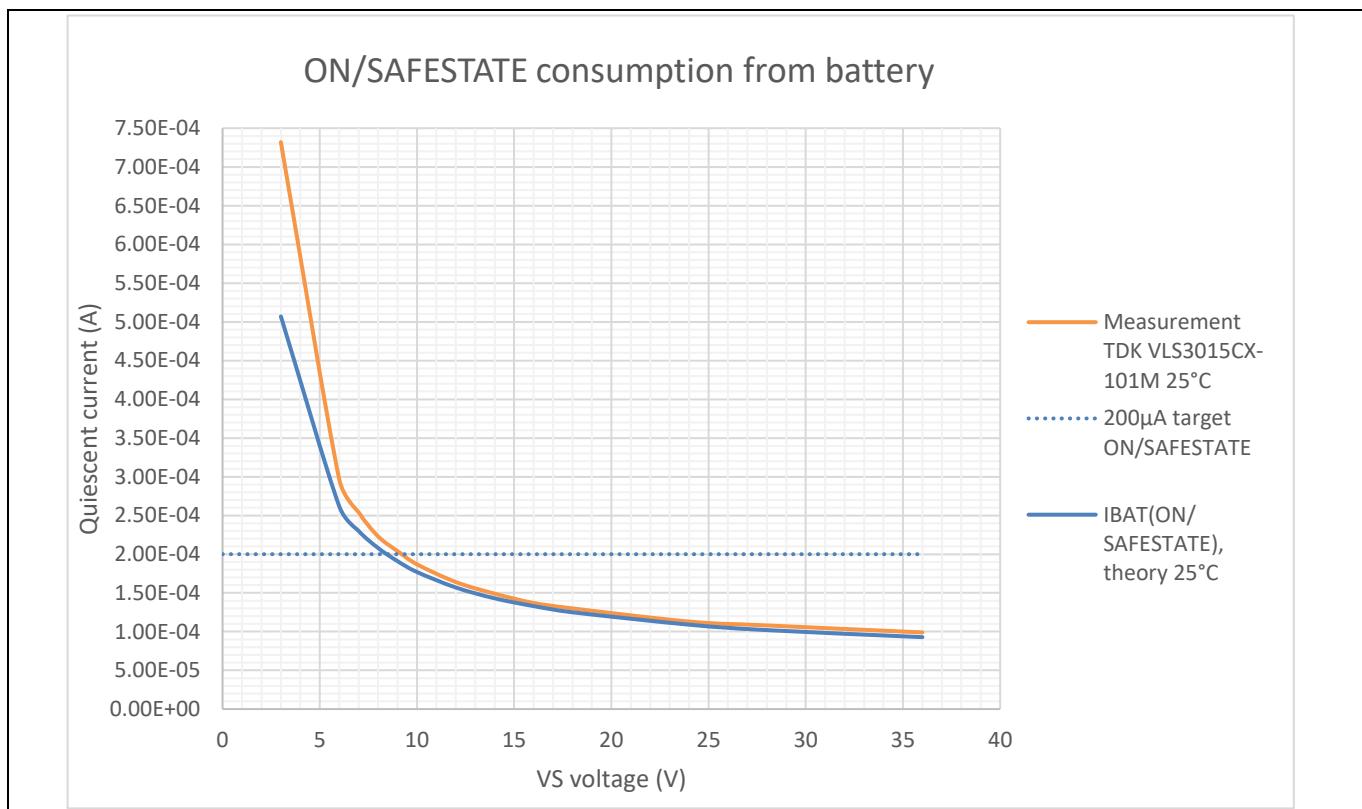

In ON and SAFESTATE mode, the boost converter is active. External MOSFET are turned-on. Amplifiers, main contributors to current consumption, are also active. Additionally, current going through the amplifiers has to be added, including current sense amplifiers 1 and 2, and temperature amplifier (unless the amplifier is disabled, see datasheet chap. 7.2 and 7.3).

Therefore, the current needed by the driver from the battery is:

$$(20) \quad I_{q(ON)} = I_{BAT} = \bar{I}_{SW} + I_{CSA1}^{1)} + I_{CSA2}^{1)} + I_{TMPA}^{2)} + I_{VS(ON)}$$

1) to be considered only if amplifier is active and current flowing through sense

2) to be considered only if temperature amplifier is active

Where:

$$(21) \quad I_{CSAx} = \frac{V_{CSOx}}{R_{CSOx}}$$

$$(22) \quad I_{TMPA} = \frac{V_{ENABLE}}{k_{TMP} * (R_{NTC} + R_{TMP})}$$

Combining (11), (15) and (16) in (14) gives:

$$(23) \quad I_{q(ON)} = \frac{I_{BC(ON)} * V_{BC}}{\eta * V_S} + I_{VS(ON)} + \frac{V_{SENSE1}}{R_{IS1}} + \frac{V_{SENSE2}}{R_{IS2}} + \frac{V_{ENABLE}}{k_{TMP} * (R_{NTC} + R_{TMP})}$$

There is no easy way to compute efficiency; therefore, a tool will be provided at product release; in the meantime, excel calculation workbook can be used for estimation.

Figure 26 Current paths in ON/SAFESTATE mode

The below graph shows the correlation between theoretical calculation and measurement from evaluation board, in open load so no current is flowing through the sense element.

**Figure 27 Quiescent current of 2ED2410-EM in ON and SAFESTATE modes @25°C, open load, using TDK VLS3015CX-101M-H and  $R_{RS}=10\ \Omega$**

**Revision history**

| <b>Document version</b> | <b>Date of release</b> | <b>Description of changes</b> |

|-------------------------|------------------------|-------------------------------|

| 1.0                     | 18/03/2022             | First release                 |

|                         |                        |                               |

|                         |                        |                               |

## Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

**Edition 2022-03-18**

**Published by**

**Infineon Technologies AG**

**81726 Munich, Germany**

**© 2022 Infineon Technologies AG.

All Rights Reserved.**

**Do you have a question about this

document?**

**Email:** [erratum@infineon.com](mailto:erratum@infineon.com)

**Document reference

Z8F80192434**

## IMPORTANT NOTICE

The information contained in this application note is given as a hint for the implementation of the product only and shall in no event be regarded as a description or warranty of a certain functionality, condition or quality of the product. Before implementation of the product, the recipient of this application note must verify any function and other technical information given herein in the real application. Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of non-infringement of intellectual property rights of any third party) with respect to any and all information given in this application note.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office ([www.infineon.com](http://www.infineon.com)).

## WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.