## Implementing IEEE 1588-2008 with LAN7430

*Author: Parthiv Pandya

Microchip Technology Inc.*

### INTRODUCTION

This application note describes an implementation of IEEE 1588 Precision Time Protocol (PTP) using LAN7430 PCIe to Ethernet bridge. The LAN7430 device has an integrated 10/100/1000 Mbps Ethernet PHY, PCIe PHY and MAC that supports IEEE 1588-2008. The Ethernet PHY supports timestamping of outgoing and incoming Ethernet frames using hardware that provides precise timings. For this application note, PTP was tested on the EVB-LAN7430 Rev B evaluation board and Linux PTP software stack. This application note provides only a basic overview of the IEEE1588-2008 standard. The user is encouraged to review the official IEEE 1588-2008 documentation from the IEEE organization.

### Sections

This document includes the following topics:

- [IEEE 1588-2008 Overview on page 2](#)

- [IEEE 1588-2008 with LAN7430 on page 4](#)

- [Demonstration Setup on page 6](#)

- [Steps to Demonstrate PTP on page 7](#)

- [Results on page 8](#)

- [Conclusion on page 9](#)

### References

The following documents should be referenced when using this application note. See your Microchip representative for availability.

- *LAN7430 Data Sheet*

- *IEEE-1588-2008 Official Standard*

- *ptp4l (Precision Time Protocol for Linux) Manual*

## IEEE 1588-2008 OVERVIEW

The IEEE 1588 protocol is used for synchronization within a distributed network. The standard provides accuracy of nanoseconds. The protocol autocorrects the latency in the network. Due to the high accuracy requirement, it is advised to perform all the necessary tasks of this standard in the hardware domain rather than in software.

The standard is highly suitable for industrial, telecommunication, smart power grid, and financial applications. For example, in an industrial environment when one task is required to start within finite time of another task, the use of IEEE1588-2008 PTP ensures determinism.

This is a master-slave protocol where a main clock (grandmaster clock) acts as the master and another clock in a node acts as the slave. To synchronize timing, the standard uses following messages between the master and the slave:

- Announce

- Timestamped messages

- Sync

- Delay\_Req

- Pdelay\_Req

- Pdelay\_Resp

- General Messages

- Follow\_Up

- Delay\_Resp

- Pdelay\_Resp\_Follow\_Up

- Management

- Signaling

The time difference between the master clock and the slave clock is a combination of the clock offset and message transmission delay. Hence, correcting the clock skew is done in two phases: offset correction and delay correction.

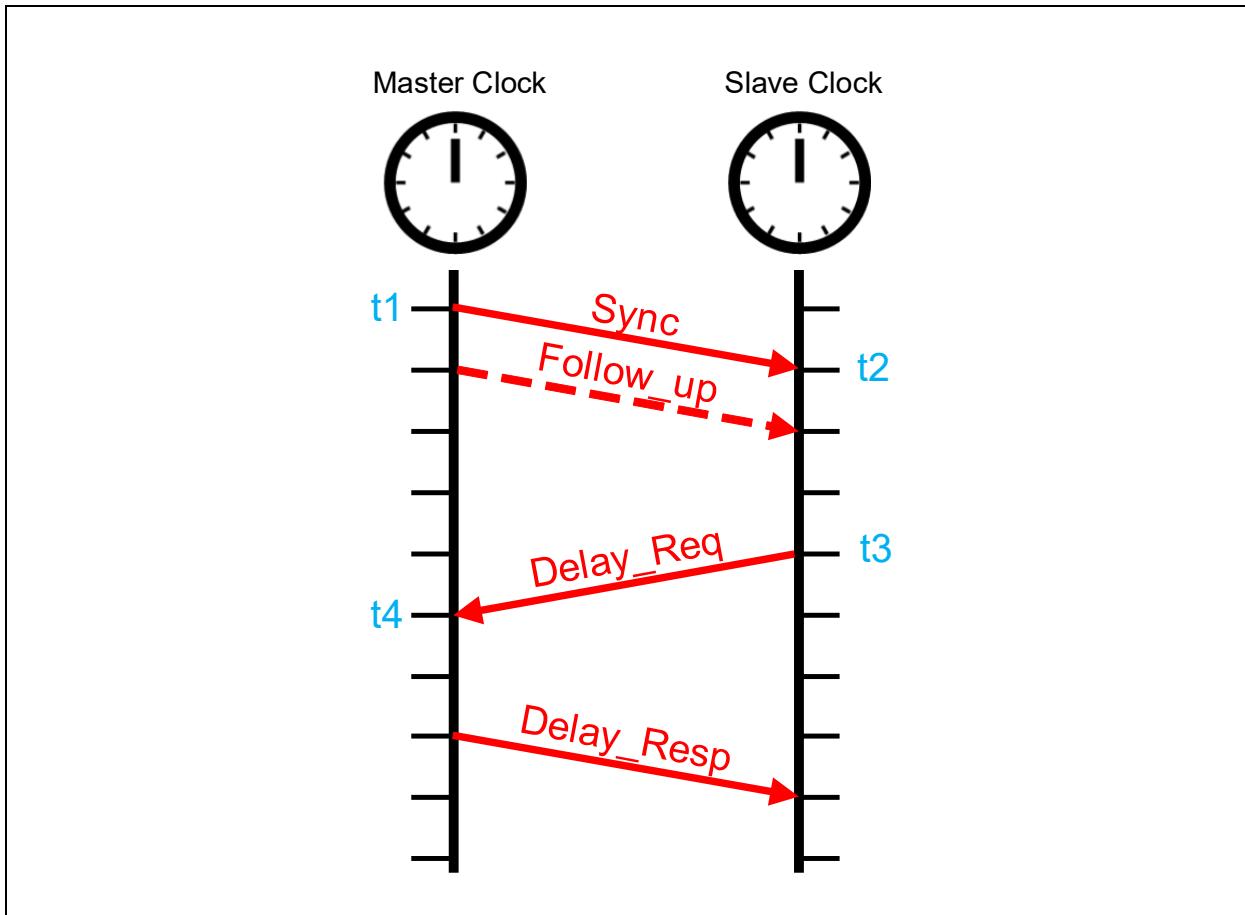

The master clock initiates offset correction using sync and follow-up messages. When the master sends a sync message, the slave uses its local clock to timestamp the arrival of the sync message and compares it to the actual sync transmission timestamp in the follow-up message of the master clock. The difference between the two timestamps represents the offset of the slave plus the message transmission delay. The slave clock then adjusts the local clock by this difference at point A.

To correct for the message transmission delay, the slave uses a second set of sync and follow-up messages with its corrected clock to calculate the master-to-slave delay at point B. The second set of messages is necessary to account for variations in network delays.

The slave then timestamps the sending of a delay request message. The master clock timestamps the arrival of the delay request message. It then sends a delay response message with the delay request arrival timestamp at point C. The difference between the timestamps is the slave-to-master delay. The slave averages the two directional delays and then adjusts the clock by the delay to synchronize the two clocks. Because the master and slave clocks drift independently, periodically repeating offset correction and delay correction keeps the clocks synchronized.

Figure 1 shows the PTP clock synchronization steps. The offset and the path delay can be calculated using [Equation 1](#) and [Equation 2](#), respectively.

**FIGURE 1: PTP CLOCK SYNCHRONIZATION**

**EQUATION 1: MEAN PATH DELAY**

$$\text{PathDelay} = \frac{(t_2 - t_1) + (t_4 - t_3)}{2}$$

**EQUATION 2: OFFSET**

$$\text{Offset} = \frac{(t_2 - t_1) - (t_4 - t_3)}{2}$$

## IEEE 1588-2008 WITH LAN7430

The device provides hardware support for the IEEE 1588-2008 (v2) Precision Time Protocol (PTP), allowing clock synchronization with remote Ethernet devices, packet timestamping, and time driven event generation.

The device may function as a master or a slave clock per the IEEE 1588-2008 Specification. End-to-end and peer-to-peer link delay mechanisms are supported in the same way as one-step and two-step operations.

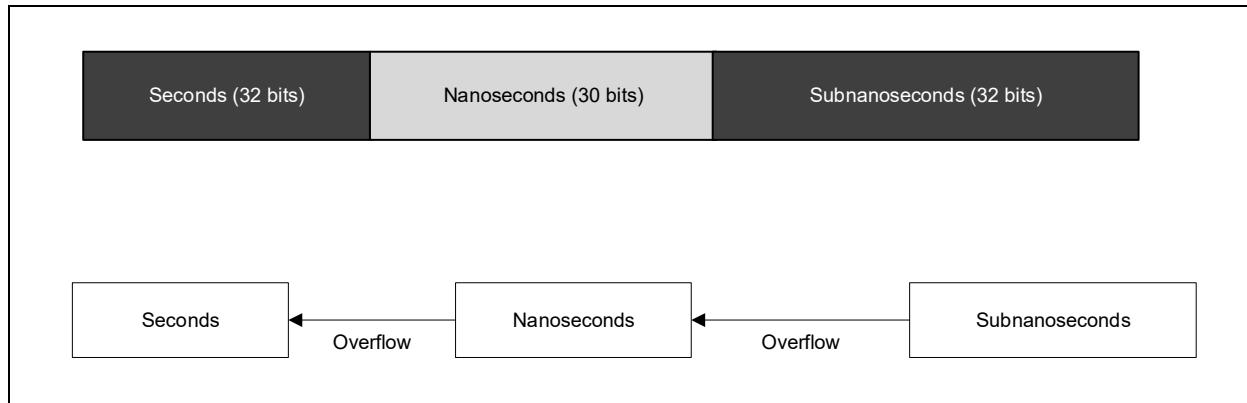

The 1588 Clock of the LAN7430 device consists of a 32-bit wide seconds portion, a 30-bit wide nanoseconds counter, and a 32-bit subnanosecond counter. Running at a nominal reference frequency of 125 MHz, the nanoseconds portion is normally incremented by a value of 8 every reference clock period. Upon reaching or exceeding its maximum value of  $10^9$ , the nanoseconds portion rolls over to or past zero and the seconds portion is incremented.

The System Time Clock (STC) of the device is a readable and writable high-precision counter that is used to keep the PTP time. The counter resolution is 2-32 ns.

STC either works as master clock or is synchronized to a master clock to provide the time for PTP-related functions.

This clock can be read or written through the CPU interface, and it is constructed with three counters: 32-bit counter for the second units, 30-bit counter for the nanosecond units, and 32-bit counter for the subnanosecond units.

[Figure 2](#) shows a block diagram of the internal 1588 clock.

**FIGURE 2: LAN7430 1588 CLOCK**

For the LAN7430 device, the system clock can be set by writing directly to the clock registers. This can be used to correct for any gross errors in the slave clock or when the system is first powering up.

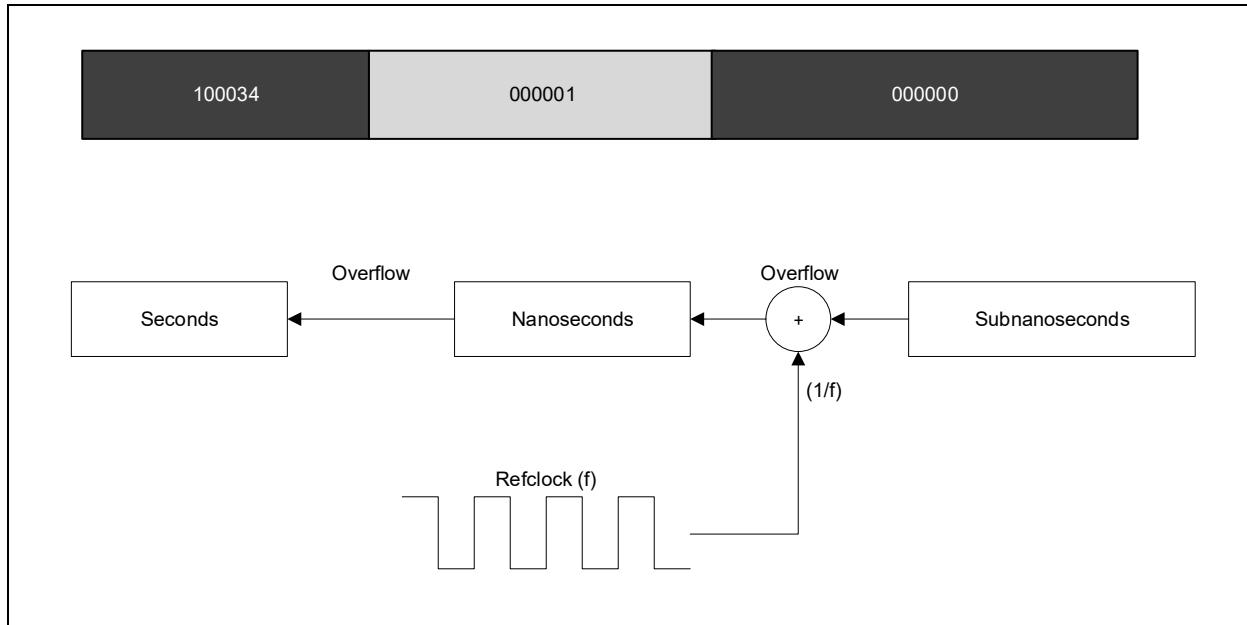

As shown in [Figure 3](#), the system clock is maintained by the Refclock of the target device. Every time a clock edge is detected, it increments the nanosecond counter by the value of the period of the clock. A more accurate Refclock yields a more accurate system clock.

**FIGURE 3: LAN7430 1588 CLOCK SETUP**

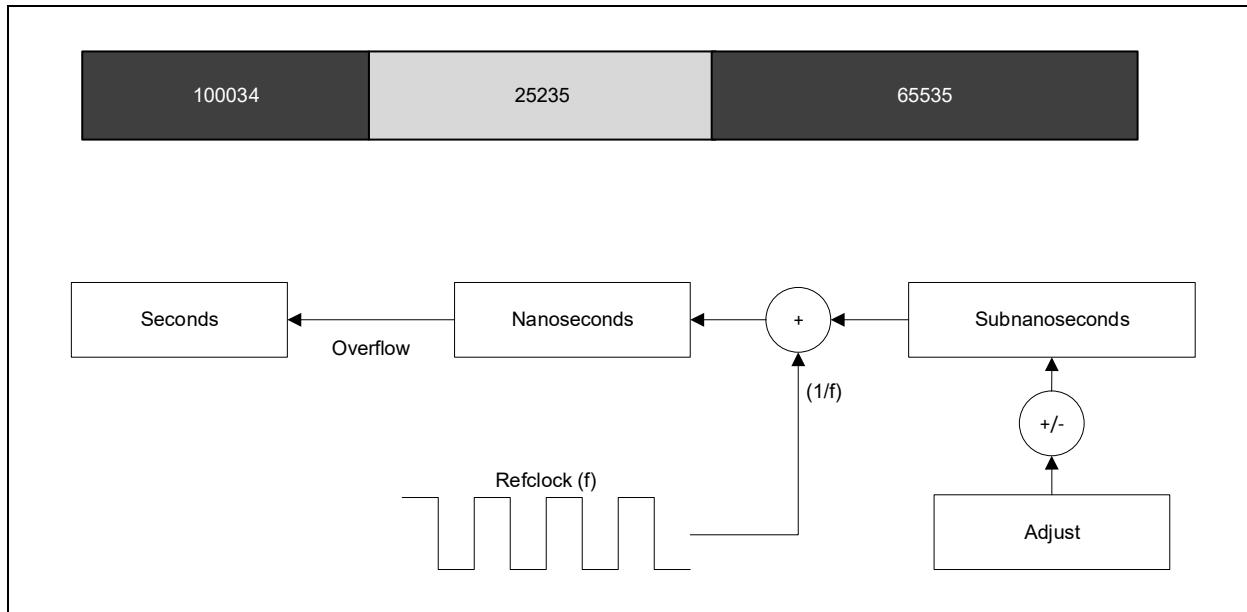

The system clock can also be adjusted to fine tune the clock based on the offset and delay calculated by the messages. [Figure 4](#) shows the block diagram.

**FIGURE 4: LAN7430 1588 CLOCK ADJUSTMENT**

## DEMONSTRATION SETUP

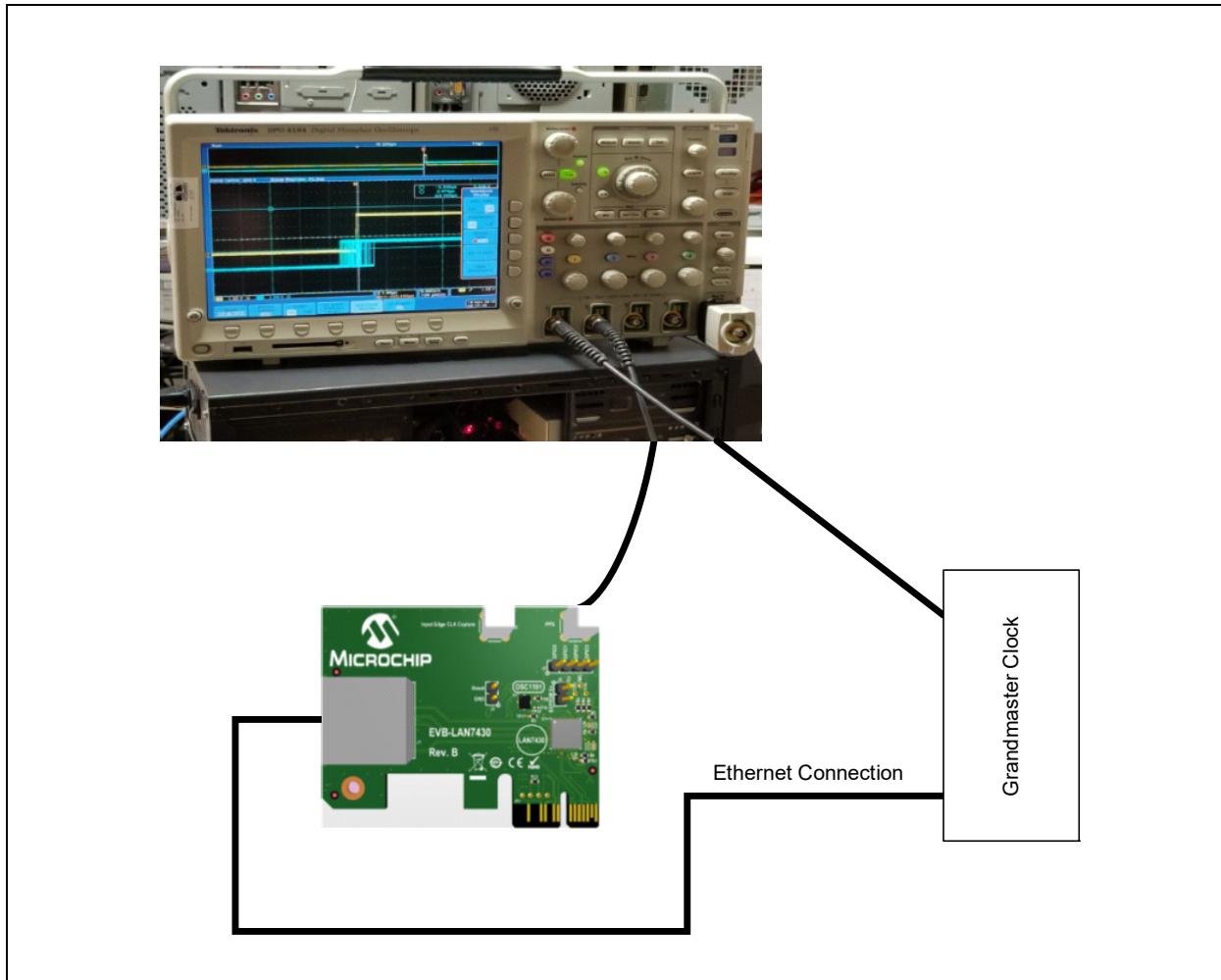

Figure 5 illustrates the setup using a GPS disciplined grandmaster clock. The grandmaster clock is connected to the EVB-LAN7430 board using an Ethernet cable. One connection of the grandmaster clock is connected to the oscilloscope, and one connection to the oscilloscope is from the EVB-LAN7430 EVB Pulse Per Second (PPS) connection.

**FIGURE 5: DEMONSTRATION SETUP**

---

## STEPS TO DEMONSTRATE PTP

The demonstration is performed on Linux operating system using PTP4L utility. The following steps are followed:

1. Open the PTP4L utility on Linux.

2. Confirm the setup as per [Demonstration Setup on page 6](#).

3. Set up a PTP configuration file, `ptp4l.conf`. A configuration file includes a few sections that configure several options for PTP. A section is labeled inside a bracket. For example, the following configuration file defines two sections (they are shown in brackets), `global` and `enp0s31f6`. The `global` section defines program options, clock options, and default port options, and the `enp0s31f6` section defines the PTP port.

```

[global]

verbose 1

time_stamping hardware

slaveOnly 0

priority1 128

priority2 128

logging_level 6

boundary_clock_jbod 0

twoStepFlag 0

```

```

[enp0s31f6]

delay_mechanism E2E

network_transport UDPv4

```

The `ptp4l.conf` file is saved in the `etc` directory (`/etc/ptp4l.conf`).

4. Run the configuration file as follows:

```

sudo ptp4l -f /etc/ptp4l.conf

```

## RESULTS

Figure 6 shows the output of the PTP demonstration. Results shows the offset and the path delay. It can be observed that after few seconds the LAN7430 tightly follows the GPS 1588 clock where the offset and the path delay are in single digit.

**FIGURE 6: LAN7430 PTP RESULTS**

```

validation1@validation1-z170X-UDS-TH:~/Documents/LAN7430_Driver/lan743x.0.7.1.180501/lan743x.0.7.1.180501/src$ sudo ptp41 -f /etc/ptp41.conf

ptp41[151.820]: selected /dev/ptp2 as PTP clock

ptp41[151.845]: port 1: INITIALIZING to LISTENING on INITIALIZE

ptp41[151.845]: port 0: INITIALIZING to LISTENING on INITIALIZE

ptp41[151.845]: port 1: link up

ptp41[152.433]: port 1: new foreign master 00b0ae.ffff.04e28f-3

ptp41[156.433]: selected best master clock 00b0ae.ffff.04e28f

ptp41[156.433]: port 1: LISTENING to UNCALIBRATED on RS_SLAVE

ptp41[158.370]: master offset 2894399134462 s0 freq +0 path delay 6007

ptp41[159.370]: master offset 2894399117758 s1 freq -16704 path delay 5519

ptp41[161.370]: master offset -6325 s2 freq -23029 path delay 4485

ptp41[161.379]: port 1: UNCALIBRATED to SLAVE on MASTER_CLOCK_SELECTED

ptp41[162.370]: master offset 533 s2 freq -18069 path delay 3451

ptp41[163.370]: master offset 1396 s2 freq -17049 path delay 3451

ptp41[164.370]: master offset 2893 s2 freq -15130 path delay 1792

ptp41[165.370]: master offset 816 s2 freq -16339 path delay 1792

ptp41[166.370]: master offset 1605 s2 freq -15305 path delay 133

ptp41[167.370]: master offset -677 s2 freq -17106 path delay 512

ptp41[168.370]: master offset -403 s2 freq -17035 path delay 133

ptp41[169.370]: master offset -564 s2 freq -17317 path delay 112

ptp41[170.370]: master offset -441 s2 freq -17363 path delay 89

ptp41[171.370]: master offset -217 s2 freq -17271 path delay 3

ptp41[172.370]: master offset -164 s2 freq -17283 path delay 5

ptp41[173.370]: master offset -105 s2 freq -17274 path delay 5

ptp41[174.370]: master offset -42 s2 freq -17242 path delay -10

ptp41[175.370]: master offset -24 s2 freq -17237 path delay -10

ptp41[176.370]: master offset -12 s2 freq -17232 path delay -10

ptp41[177.370]: master offset -14 s2 freq -17230 path delay -10

ptp41[178.370]: master offset -9 s2 freq -17237 path delay -10

ptp41[179.370]: master offset -15 s2 freq -17245 path delay 0

ptp41[180.370]: master offset -8 s2 freq -17243 path delay 5

ptp41[181.370]: master offset 2 s2 freq -17235 path delay 5

ptp41[182.370]: master offset -4 s2 freq -17241 path delay 6

ptp41[183.370]: master offset -4 s2 freq -17242 path delay 6

ptp41[184.370]: master offset -12 s2 freq -17251 path delay 6

ptp41[185.370]: master offset -1 s2 freq -17244 path delay 6

ptp41[186.370]: master offset -6 s2 freq -17249 path delay 6

ptp41[187.370]: master offset -7 s2 freq -17252 path delay 7

ptp41[188.370]: master offset -12 s2 freq -17259 path delay 7

ptp41[189.370]: master offset -3 s2 freq -17254 path delay 8

ptp41[190.370]: master offset -8 s2 freq -17259 path delay 9

ptp41[191.370]: master offset -13 s2 freq -17267 path delay 9

ptp41[192.370]: master offset -3 s2 freq -17261 path delay 9

ptp41[193.370]: master offset -8 s2 freq -17267 path delay 9

ptp41[194.370]: master offset -14 s2 freq -17275 path delay 9

ptp41[195.370]: master offset -3 s2 freq -17268 path delay 9

ptp41[196.370]: master offset -8 s2 freq -17274 path delay 9

ptp41[197.370]: master offset -6 s2 freq -17275 path delay 9

ptp41[198.370]: master offset -12 s2 freq -17282 path delay 9

ptp41[199.370]: master offset -2 s2 freq -17276 path delay 9

ptp41[200.370]: master offset -7 s2 freq -17282 path delay 9

ptp41[201.370]: master offset -6 s2 freq -17283 path delay 9

ptp41[202.370]: master offset -4 s2 freq -17282 path delay 9

ptp41[203.370]: master offset -3 s2 freq -17283 path delay 9

ptp41[204.370]: master offset -9 s2 freq -17290 path delay 9

ptp41[205.370]: master offset -7 s2 freq -17260 path delay 0

```

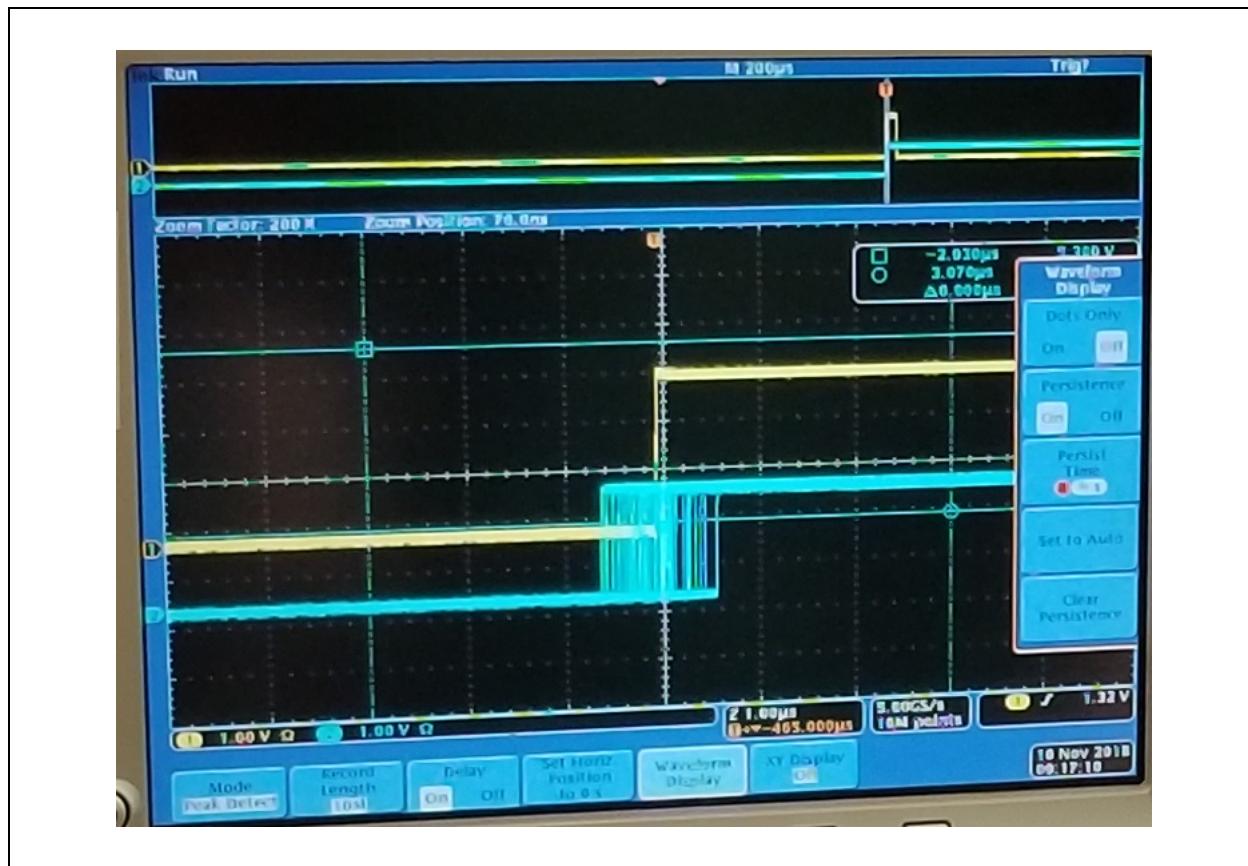

Figure 7 shows the oscilloscope captures of the offset and jitters of the PPS signal between master and the LAN7430 slave clock.

**FIGURE 7: JITTER COMPARISON OF LAN7430 SLAVE AND MASTER PPS OUTPUTS**

## CONCLUSION

The results show that the integrated IEEE 1588-2008 of the LAN7430 device is very precise, which is extremely useful in industrial and automotive applications.

## APPENDIX A: PTP4L COMMAND DESCRIPTION

TABLE A-1: PTP4L COMMAND DESCRIPTION

| Command             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [global]            | Sets the program options, clock options, and default port options.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| -f config           | Reads configuration from the specified file. No configuration file is read by default.                                                                                                                                                                                                                                                                                                                                                                                                                |

| verbose             | Prints messages to the standard output if enabled. The default is 0 (disabled).                                                                                                                                                                                                                                                                                                                                                                                                                       |

| time_stamping       | The time stamping method. The allowed values are hardware, software, and legacy. The default is hardware.                                                                                                                                                                                                                                                                                                                                                                                             |

| slaveOnly           | The local clock is a slave-only clock if enabled. This option is only for use with 1588 clocks and should not be enabled for 802.1AS clocks. The default is 0 (disabled).                                                                                                                                                                                                                                                                                                                             |

| priority1           | The priority1 attribute of the local clock. It is used in the best master selection algorithm, lower values take precedence. Must be in the range 0 to 255. The default is 128.                                                                                                                                                                                                                                                                                                                       |

| priority2           | The priority2 attribute of the local clock. It is used in the best master selection algorithm, lower values take precedence. Must be in the range 0 to 255. The default is 128.                                                                                                                                                                                                                                                                                                                       |

| logging_level       | The maximum logging level of messages that should be printed. The default is 6 (LOG_INFO).                                                                                                                                                                                                                                                                                                                                                                                                            |

| boundary_clock_jbod | When running as a boundary clock (that is, when more than one network interface is configured), ptpt4l performs a sanity check to make sure that all of the ports share the same hardware clock device. This option allows ptpt4l to work as a boundary clock using “just a bunch of devices” that are not synchronized to each other. For this mode, the collection of clocks must be synchronized by an external program, for example phc2sys(8) in an automatic mode. The default is 0 (disabled). |

| twoStepFlag         | Enables two-step mode for sync messages. One-step mode can be used only with hardware time stamping. The default is 1 (enabled).                                                                                                                                                                                                                                                                                                                                                                      |

| delay_mechanism     | Selects the delay mechanism. Possible values are E2E, P2P, and Auto. The default is E2E.                                                                                                                                                                                                                                                                                                                                                                                                              |

| network_transport   | Selects the network transport. Possible values are UDPv4, UDPv6, and L2. The default is UDPv4.                                                                                                                                                                                                                                                                                                                                                                                                        |

---

**APPENDIX B: APPLICATION NOTE REVISION HISTORY****TABLE B-1: REVISION HISTORY**

| Revision Level & Date     | Section/Figure/Entry | Correction |

|---------------------------|----------------------|------------|

| DS00002930A<br>(01-24-19) | Initial release      |            |

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at [www.microchip.com](http://www.microchip.com). This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** – Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- **General Technical Support** – Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- **Business of Microchip** – Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at [www.microchip.com](http://www.microchip.com). Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

**Technical support is available through the web site at: <http://microchip.com/support>**

---

**Note the following details of the code protection feature on Microchip devices:**

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

---

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. **MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE.** Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBloX, KeeLoq, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, memBrain, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQL, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2019, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-4082-6

---

**QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

= ISO/TS 16949 =**

*Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KeeLoq® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.*

# MICROCHIP

## Worldwide Sales and Service

### AMERICAS

**Corporate Office**

2355 West Chandler Blvd.

Chandler, AZ 85224-6199

Tel: 480-792-7200

Fax: 480-792-7277

Technical Support:

<http://www.microchip.com/support>

Web Address:

[www.microchip.com](http://www.microchip.com)

**Atlanta**

Duluth, GA

Tel: 678-957-9614

Fax: 678-957-1455

**Austin, TX**

Tel: 512-257-3370

**Boston**

Westborough, MA

Tel: 774-760-0087

Fax: 774-760-0088

**Chicago**

Itasca, IL

Tel: 630-285-0071

Fax: 630-285-0075

**Dallas**

Addison, TX

Tel: 972-818-7423

Fax: 972-818-2924

**Detroit**

Novi, MI

Tel: 248-848-4000

**Houston, TX**

Tel: 281-894-5983

**Indianapolis**

Noblesville, IN

Tel: 317-773-8323

Fax: 317-773-5453

Tel: 317-536-2380

**Los Angeles**

Mission Viejo, CA

Tel: 949-462-9523

Fax: 949-462-9608

Tel: 951-273-7800

**Raleigh, NC**

Tel: 919-844-7510

**New York, NY**

Tel: 631-435-6000

**San Jose, CA**

Tel: 408-735-9110

Tel: 408-436-4270

**Canada - Toronto**

Tel: 905-695-1980

Fax: 905-695-2078

### ASIA/PACIFIC

**Australia - Sydney**

Tel: 61-2-9868-6733

**China - Beijing**

Tel: 86-10-8569-7000

**China - Chengdu**

Tel: 86-28-8665-5511

**China - Chongqing**

Tel: 86-23-8980-9588

**China - Dongguan**

Tel: 86-769-8702-9880

**China - Guangzhou**

Tel: 86-20-8755-8029

**China - Hangzhou**

Tel: 86-571-8792-8115

**China - Hong Kong SAR**

Tel: 852-2943-5100

**China - Nanjing**

Tel: 86-25-8473-2460

**China - Qingdao**

Tel: 86-532-8502-7355

**China - Shanghai**

Tel: 86-21-3326-8000

**China - Shenyang**

Tel: 86-24-2334-2829

**China - Shenzhen**

Tel: 86-755-8864-2200

**China - Suzhou**

Tel: 86-186-6233-1526

**China - Wuhan**

Tel: 86-27-5980-5300

**China - Xian**

Tel: 86-29-8833-7252

**China - Xiamen**

Tel: 86-592-2388138

**China - Zhuhai**

Tel: 86-756-3210040

### ASIA/PACIFIC

**India - Bangalore**

Tel: 91-80-3090-4444

**India - New Delhi**

Tel: 91-11-4160-8631

**India - Pune**

Tel: 91-20-4121-0141

**Japan - Osaka**

Tel: 81-6-6152-7160

**Japan - Tokyo**

Tel: 81-3-6880- 3770

**Korea - Daegu**

Tel: 82-53-744-4301

**Korea - Seoul**

Tel: 82-2-554-7200

**Malaysia - Kuala Lumpur**

Tel: 60-3-7651-7906

**Malaysia - Penang**

Tel: 60-4-227-8870

**Philippines - Manila**

Tel: 63-2-634-9065

**Singapore**

Tel: 65-6334-8870

**Taiwan - Hsin Chu**

Tel: 886-3-577-8366

**Taiwan - Kaohsiung**

Tel: 886-7-213-7830

**Taiwan - Taipei**

Tel: 886-2-2508-8600

**Thailand - Bangkok**

Tel: 66-2-694-1351

**Vietnam - Ho Chi Minh**

Tel: 84-28-5448-2100

### EUROPE

**Austria - Wels**

Tel: 43-7242-2244-39

Fax: 43-7242-2244-393

**Denmark - Copenhagen**

Tel: 45-4450-2828

Fax: 45-4485-2829

**Finland - Espoo**

Tel: 358-9-4520-820

**France - Paris**

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

**Germany - Garching**

Tel: 49-8931-9700

**Germany - Haan**

Tel: 49-2129-3766400

**Germany - Heilbronn**

Tel: 49-7131-67-3636

**Germany - Karlsruhe**

Tel: 49-721-625370

**Germany - Munich**

Tel: 49-89-627-144-0

Fax: 49-89-627-144-44

**Germany - Rosenheim**

Tel: 49-8031-354-560

**Israel - Ra'anana**

Tel: 972-9-744-7705

**Italy - Milan**

Tel: 39-0331-742611

Fax: 39-0331-466781

**Italy - Padova**

Tel: 39-049-7625286

**Netherlands - Drunen**

Tel: 31-416-690399

Fax: 31-416-690340

**Norway - Trondheim**

Tel: 47-7288-4388

**Poland - Warsaw**

Tel: 48-22-3325737

**Romania - Bucharest**

Tel: 40-21-407-87-50

**Spain - Madrid**

Tel: 34-91-708-08-90

Fax: 34-91-708-08-91

**Sweden - Gothenberg**

Tel: 46-31-704-60-40

**Sweden - Stockholm**

Tel: 46-8-5090-4654

**UK - Wokingham**

Tel: 44-118-921-5800

Fax: 44-118-921-5820