# UM11733

## Hardware user manual for FRDM665CANFDEVB

Rev. 1 — 25 July 2022

User manual

### Document information

| Information | Content                                                                                                                                         |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | MC33665A, CAN FD, BMS gateway IC                                                                                                                |

| Abstract    | Hardware user manual for FRDM665CANFDEVB, which can support both CAN and CAN FD communication to microcontroller on battery control unit (BCU). |

## Revision history

| Rev | Date     | Description     |

|-----|----------|-----------------|

| 1   | 20220725 | initial version |

**IMPORTANT NOTICE****For engineering development or evaluation purposes only**

NXP provides the product under the following conditions:

This evaluation kit is for use of ENGINEERING DEVELOPMENT OR EVALUATION PURPOSES ONLY. It is provided as a sample IC pre-soldered to a printed-circuit board to make it easier to access inputs, outputs and supply terminals. This evaluation board may be used with any development system or other source of I/O signals by connecting it to the host MCU computer board via off-the-shelf cables. This evaluation board is not a Reference Design and is not intended to represent a final design recommendation for any particular application. Final device in an application heavily depends on proper printed-circuit board layout and heat sinking design as well as attention to supply filtering, transient suppression, and I/O signal quality.

The product provided may not be complete in terms of required design, marketing, and or manufacturing related protective considerations, including product safety measures typically found in the end device incorporating the product. Due to the open construction of the product, it is the responsibility of the user to take all appropriate precautions for electric discharge. In order to minimize risks associated with the customers' applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. For any safety concerns, contact NXP sales and technical support services.

## 1 Introduction

The NXP analog product development boards provide an easy-to-use platform for evaluating NXP products. The boards support a range of analog, mixed-signal, and power solutions. They incorporate monolithic integrated circuits and system-in-package devices that use proven high-volume technology. NXP products offer longer battery life, a smaller form factor, reduced component counts, lower cost, and improved performance in powering state-of-the-art systems.

## 2 Finding kit resources and information on the NXP web site

NXP Semiconductors provides online resources for this evaluation board and its supported device(s) on <http://www.nxp.com>.

The information page for the FRDM665CANFDEVB evaluation board is at <http://www.nxp.com/FRDM665CANFDEVB>. The information page provides overview information, documentation, software and tools, parametrics, ordering information and a Getting Started tab. The Getting Started tab provides quick-reference information applicable to using the FRDM665CANFDEVB evaluation board, including the downloadable assets referenced in this document.

## 3 Getting ready

Working with the FRDM665CANFDEVB evaluation board requires the kit contents, additional hardware, and a Windows PC workstation with installed software.

### 3.1 Kit contents

The FRDM665CANFDEVB kit includes:

- MC33665A CAN FD EVB, CAN or CAN FD to four transformer physical layer (TPL) interface EVB

- One TPL daisy chain cable; two-wire twisted-pair daisy chain interface cable

- One power cable, 4-pin socket

- Quick start guide

### 3.2 Additional hardware

In addition to the kit contents, the following hardware is necessary or beneficial:

- External dual power supply 8 V to 16 V/2 A (optional)

- EVBs of battery cell controller (BCC) devices from NXP

- 14-cell battery pack or a battery emulator, such as BATT-14CEMULATOR

## 4 Getting to know the hardware

### 4.1 Kit overview

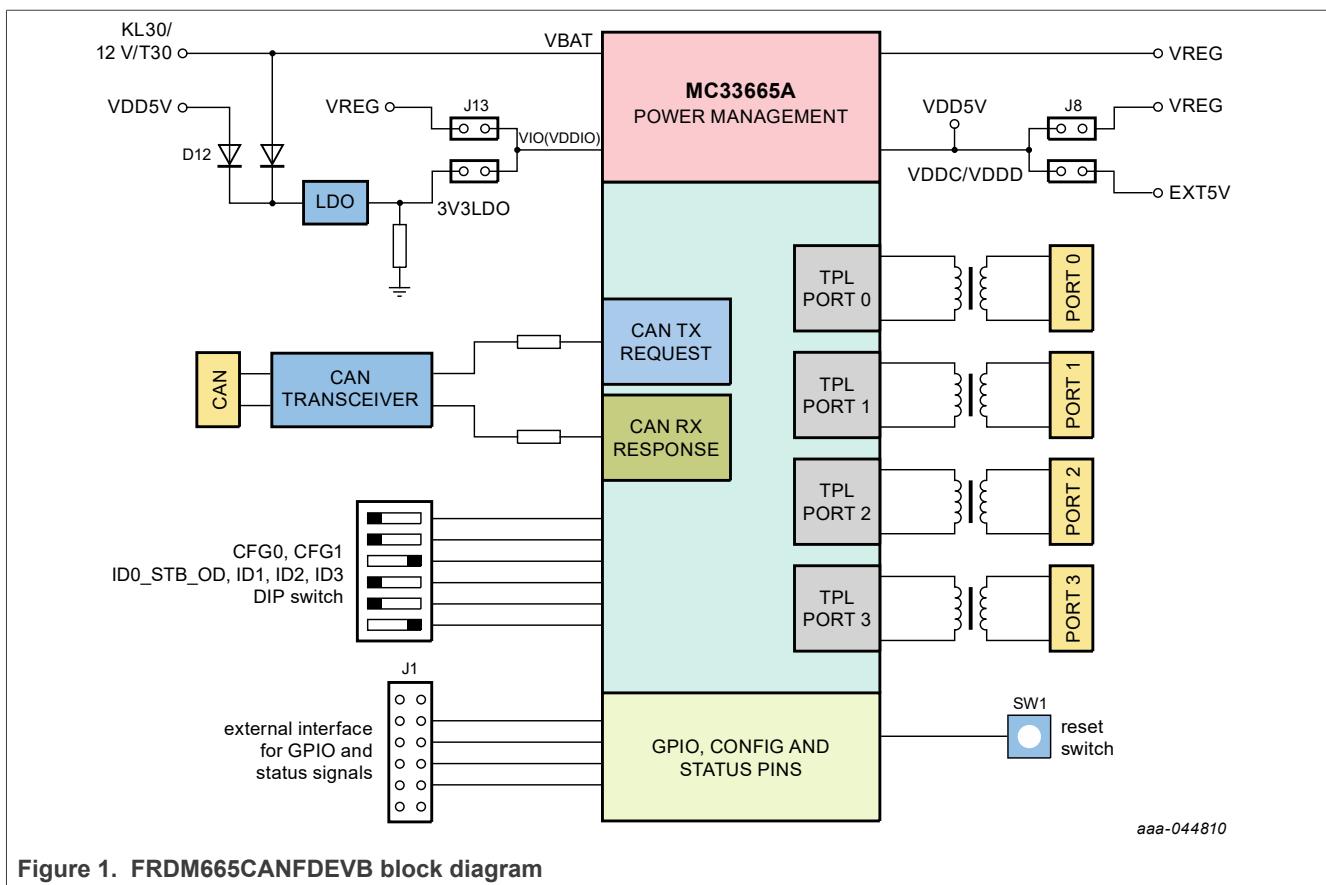

The FRDM665CANFDEVB serves as a hardware evaluation tool in support of the MC33665A device of NXP. The MC33665A is a gateway router that can route TPL messages from the microcontroller to four different TPL ports. It is designed for use in both automotive and industrial applications. The device can route both TPL2 and TPL3

messages. FRDM665CANFDEVB is an ideal board for rapid prototyping of MC33665A for CAN FD interface to MCU.

FRDM665CANFDEVB supports both classical CAN or CAN FD. Differential communication to daisy chain devices can be established with four different ports.

## 4.2 Board features

The main features of FRDM665CANFDEVB are:

- CAN and CAN FD

- Onboard transformer isolation for TPL communication to BCC devices

- Configurable VIO voltage

- Configurable VDD5V from internal and external supply

- DIP switch for configuring the arbitration baud rate and CAN ID of MC33665A

- Reset switch for the device and board

- LED display for the status of power

- Connectors for external interface to general-purpose input/output (GPIO) and I<sup>2</sup>C-bus

## 4.3 Block diagram

Figure 1. FRDM665CANFDEVB block diagram

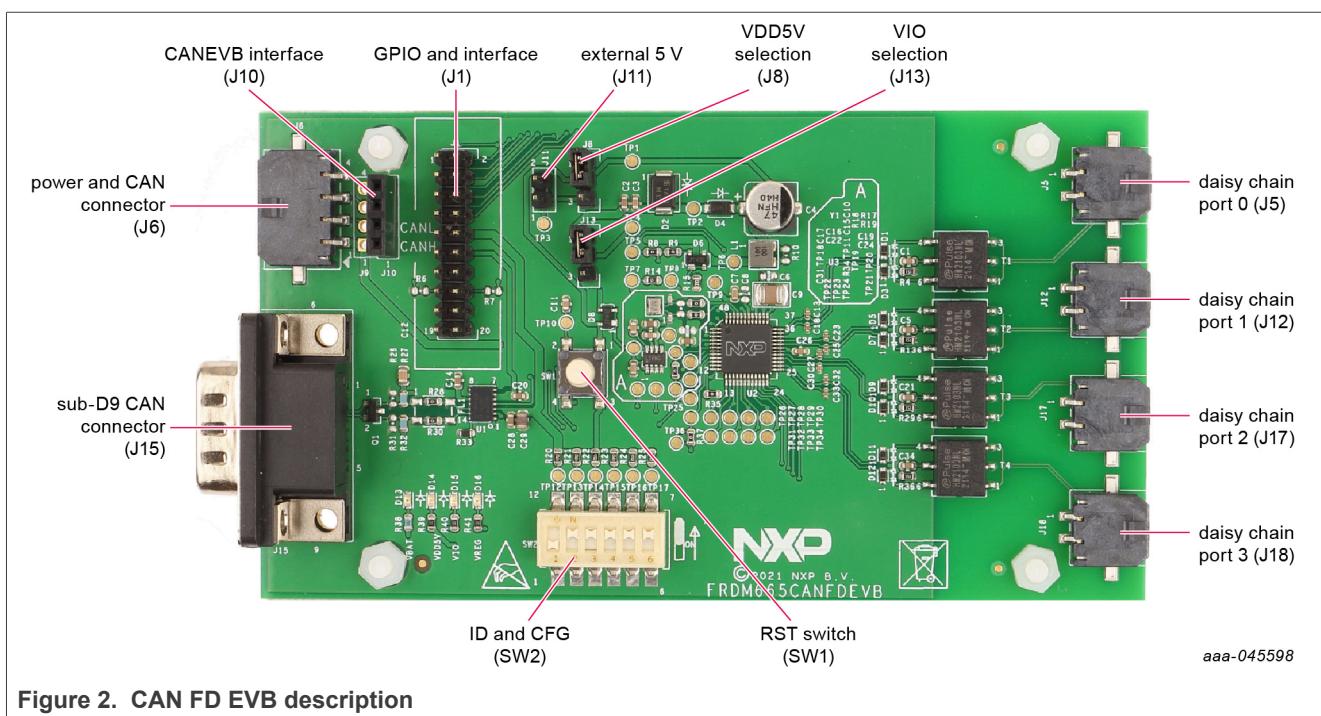

#### 4.4 Board description

The FRDM665CANFDEVB allows the user to prototype and test all functions of the MC33665A gateway router with CAN or CAN FD communication.

CAN or CAN FD communication can be established with MC33665A via sub-D9 connector. In addition to sub-D9 CAN connector, same signals of CANH and CANL are available in both power and CAN connector J6 and CANEVB interface J10. TJA1443 is the CAN transceiver used for FRDM665CANFDEVB.

12 V (> 5 W) DC power supply can be connected to J6. VDD5V selection and VIO selection have no influence in FRDM665CANFDEVB as there is a constant 12 V power supply and there is no direct microcontroller to select VIO. CAN ID can be selected by setting the position in DIP switch SW2. Take care to set the position of DIP switches (SW2) appropriately to configure ID and CAN arbitration baud rates to MC33665A.

External 5 V can be connected to bypass the VREG circuit of MC33665A. Take care in selecting the appropriate jumper J8 to power the VDD5V.

Connector J1 gives the option to access the GPIO and I<sup>2</sup>C pins of MC33665A.

Contact the NXP engineering team for using TPL autowake function in FRDM665CANFDEVB.

Figure 2. CAN FD EVB description

Power configuration of the board can be reflected by LEDs populated on board. LEDs glowing on board reflect the right power interface connected to FRDM665CANFDEVB.

Table 1. Power status LEDs

| LED         | VBAT 12 V | External 5 V |

|-------------|-----------|--------------|

| D13 - red   | X         | -            |

| D14 - green | X         | X            |

| D15 - green | X         | X            |

Table 1. Power status LEDs...continued

| LED       | VBAT 12 V | External 5 V |

|-----------|-----------|--------------|

| D16 - red | X         | -            |

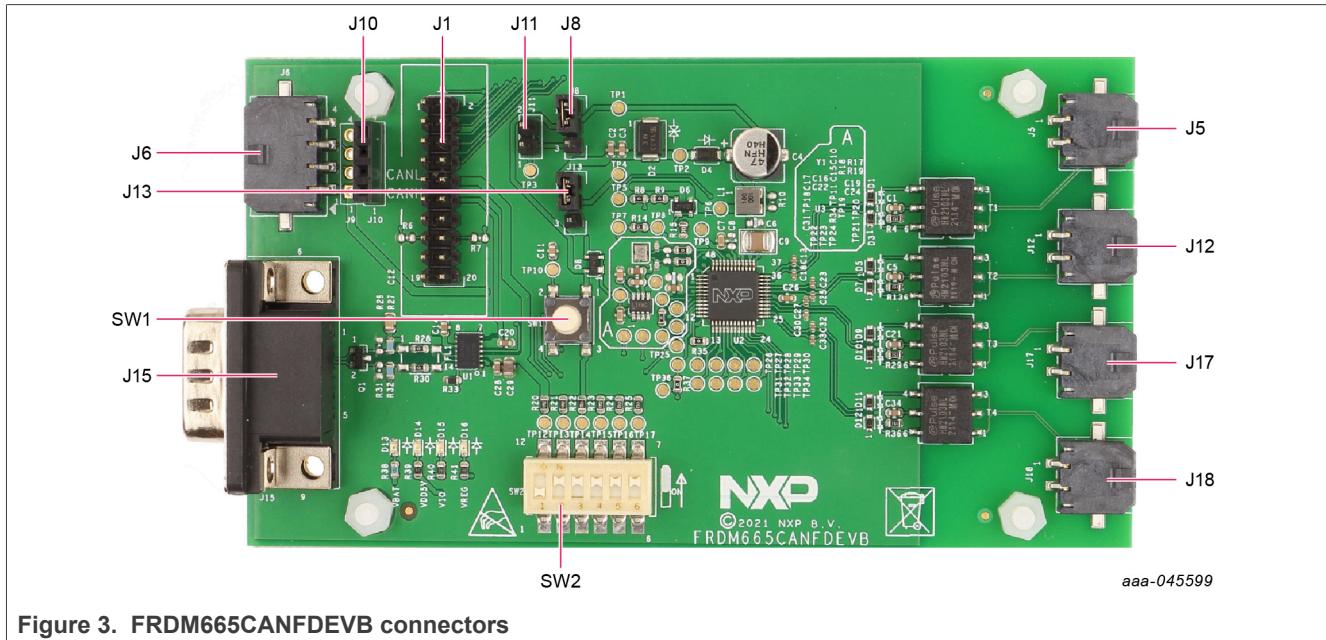

## 4.5 Connectors

FRDM665CANFDEV has multiple connectors for interfacing to MCU, internal GPIO, and external BCC devices.

Figure 3. FRDM665CANFDEV connectors

Pin configuration of connectors is shown in [Table 2](#) to [Table 8](#).

Table 2. Power and CAN connector - J6

| Pin number | Connection | Description                                         |

|------------|------------|-----------------------------------------------------|

| 1          | VBAT       | connection to 12 V                                  |

| 2          | CANH       | CANH interface for TJA1443                          |

| 3          | CANL       | CANL interface for TJA1443                          |

| 4          | GND        | ground connection for MC33665A and interface boards |

Table 3. CANEVB connector - J10

| Pin number | Connection | Description                                         |

|------------|------------|-----------------------------------------------------|

| 1          | CANH       | CANH interface for TJA1443                          |

| 2          | CANL       | CANL interface for TJA1443                          |

| 3          | GND        | ground connection for MC33665A and interface boards |

| 4          | -          | no connection                                       |

**Table 4. GPIO and interface - J1**

| Pin number | Connection | Description                                            |

|------------|------------|--------------------------------------------------------|

| 1          | GPIO0      | interface to GPIO0 or INT0 for MC33665A                |

| 2          | GPIO1      | interface to GPIO1 or INT1 for MC33665A                |

| 3          | GPIO2      | interface to GPIO2 or INT2 for MC33665A                |

| 4          | GPIO3      | interface to GPIO3 or INT3 for MC33665A                |

| 5          | GPIO4      | interface to GPIO4 or I <sup>2</sup> C-bus in MC33665A |

| 6          | GPIO5      | interface to GPIO5 or I <sup>2</sup> C-bus in MC33665A |

| 7          | GPIO6      | interface to GPIO6 or SYNC in MC33665A                 |

| 8          | GPIO7      | interface to GPIO7 or HOLD in MC33665A                 |

| 9          | VSS/GND    | ground                                                 |

| 10         | VDD5V      | 5 V supply line                                        |

| 11         | VSS/GND    | ground                                                 |

| 12         | VIO        | VIO interface for MC33665A                             |

| 13         | -          | not connected                                          |

| 14         | -          | not connected                                          |

| 15         | NC-CAN_TXD | populate R6 to connect CAN_TXD                         |

| 16         | NC-CAN_RXD | populate R7 to connect CAN_RXD                         |

| 17         | STB_N_OUT  | inverted standby signal from MC33665A                  |

| 18         | STB_OUT    | standby signal from MC33665A                           |

| 19         | RESET      | reset signal for MC33665A                              |

| 20         | VDD5V      | 5 V supply line                                        |

**Table 5. External 5 V - J11**

| Pin number | Connection | Description         |

|------------|------------|---------------------|

| 1          | EXT5V      | external 5 V supply |

| 2          | VSS/GND    | ground              |

**Table 6. VDD5V jumper - J8**

| Pin number | Connection  | Description                                                                                                                                     |

|------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-2        | VREG-VDD5V  | Connection from VREG generated by internal low dropout (LDO) connection to VDD5V for MC33665A and interface circuits. Note: Default connection. |

| 2-3        | EXT5V-VDD5V | External 5 V supply can be connected to VDD5V to MC33665A and interface circuits.                                                               |

**Table 7. VIO jumper - J13**

| Pin number | Connection | Description                                                                                                                        |

|------------|------------|------------------------------------------------------------------------------------------------------------------------------------|

| 1-2        | VREG-VIO   | connect VREG (5 V) generated by internal LDO of MC33665A to VDDIO/VIO of MC33665A and interface circuit. Note: Default connection. |

Table 7. VIO jumper - J13...continued

| Pin number | Connection | Description                                             |

|------------|------------|---------------------------------------------------------|

| 2-3        | 3V3LDO-VIO | connect constant 3.3 V generated by external LDO to VIO |

Table 8. Sub-D9 CAN connector - J15

| Pin number | Connection | Description                                         |

|------------|------------|-----------------------------------------------------|

| 2          | CANL       | CANL interface for TJA1443                          |

| 3          | VSS        | ground connection for MC33665A and interface boards |

| 7          | CANH       | CANH interface for TJA1443                          |

| Others     | -          | not connected                                       |

## 4.6 Schematic, board layout and bill of materials

The schematic, board layout and bill of materials for the FRDM665CANFDEV<sup>B</sup> evaluation board are available at <http://www.nxp.com/FRDM665CANFDEV>

## 5 Configuring the hardware

FRDM665CANFDEV<sup>B</sup> can be configured as stacked board to S32K344EVB.

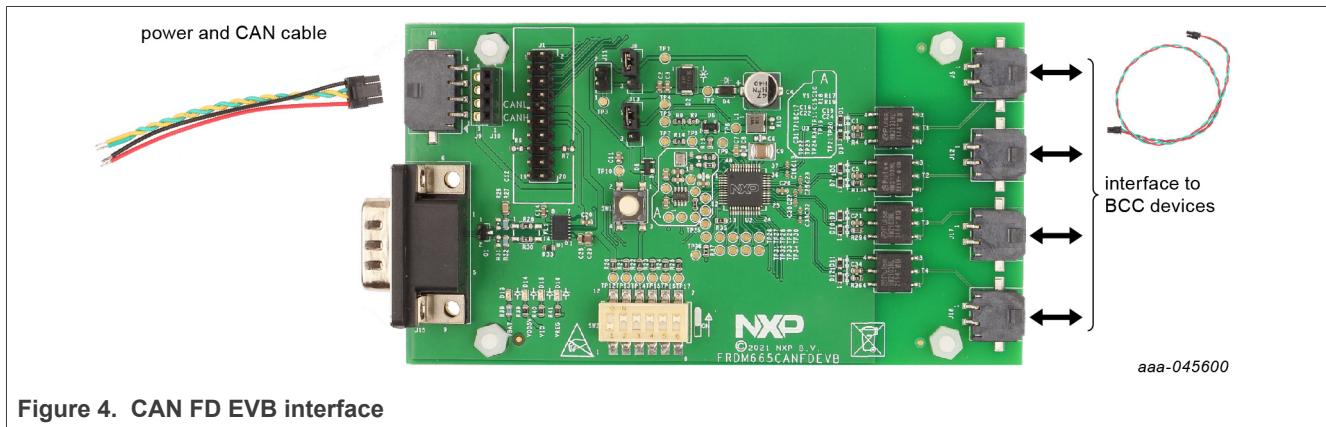

### 5.1 CAN FD interface

FRDM665CANFDEV<sup>B</sup> can be connected to a PC/laptop or other ECUs with power and CAN cable or connector. 12 V supply line can be used to power the FRDM665CANFDEV<sup>B</sup>, female sub-D9 connector can be interfaced to relevant CAN tool or ECU. SW2 can be used to configure the CAN ID for MC33665A. CFG pins can also be configured to set the arbitration speed for MC33665A. Press SW1 button (RST switch) after changing any settings on SW2 (ID and CFG). Ensure the settings on J8 for VDD5V and J13 for VIO selection are appropriate for power supplied to the board. CANEVB interface J10 can be used for direct interface with S32K344EVB for CAN or CAN FD.

Figure 4. CAN FD EVB interface

## 6 Available accessories

**Table 9. Accessories**

| Part number      | Description                                                               |

|------------------|---------------------------------------------------------------------------|

| FRDM33772CSPEVB  | evaluation board for MC33772C with SPI communication                      |

| RD33771CDSTEVB   | evaluation board for MC33771C BCC with isolated daisy chain communication |

| BATT-14EXTENDER  | battery emulator extender                                                 |

| BATT-14CEMULATOR | 14-cell battery pack to supply MC33771C EVBs                              |

| BATT-TPLCABLE20  | TPL, two-wire, twisted, 20 cm long cable                                  |

| BATT-TPLCABLE50  | TPL, two-wire, twisted, 50 cm long cable                                  |

| BATT-14CTCABLE25 | cell terminal (CT) cable, 14 cells, 25 cm long                            |

## 7 Legal information

### 7.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

### 7.2 Disclaimers

**Limited warranty and liability** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Terms and conditions of commercial sale** — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <http://www.nxp.com/profile/terms>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

**Security** — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately.

Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at [PSIRT@nxp.com](mailto:PSIRT@nxp.com)) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

### 7.3 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

**NXP** — wordmark and logo are trademarks of NXP B.V.

## Tables

|         |                                    |   |         |                                  |    |

|---------|------------------------------------|---|---------|----------------------------------|----|

| Tab. 1. | Power status LEDs .....            | 6 | Tab. 6. | VDD5V jumper - J8 .....          | 8  |

| Tab. 2. | Power and CAN connector - J6 ..... | 7 | Tab. 7. | VIO jumper - J13 .....           | 8  |

| Tab. 3. | CANEVB connector - J10 .....       | 7 | Tab. 8. | Sub-D9 CAN connector - J15 ..... | 9  |

| Tab. 4. | GPIO and interface - J1 .....      | 8 | Tab. 9. | Accessories .....                | 10 |

| Tab. 5. | External 5 V - J11 .....           | 8 |         |                                  |    |

## Figures

|         |                                    |   |         |                                 |   |

|---------|------------------------------------|---|---------|---------------------------------|---|

| Fig. 1. | FRDM665CANFDEV block diagram ..... | 5 | Fig. 3. | FRDM665CANFDEV connectors ..... | 7 |

| Fig. 2. | CAN FD EVB description .....       | 6 | Fig. 4. | CAN FD EVB interface .....      | 9 |

## Contents

---

|          |                                                                  |           |

|----------|------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                              | <b>4</b>  |

| <b>2</b> | <b>Finding kit resources and information on the NXP web site</b> | <b>4</b>  |

| <b>3</b> | <b>Getting ready</b>                                             | <b>4</b>  |

| 3.1      | Kit contents                                                     | 4         |

| 3.2      | Additional hardware                                              | 4         |

| <b>4</b> | <b>Getting to know the hardware</b>                              | <b>4</b>  |

| 4.1      | Kit overview                                                     | 4         |

| 4.2      | Board features                                                   | 5         |

| 4.3      | Block diagram                                                    | 5         |

| 4.4      | Board description                                                | 6         |

| 4.5      | Connectors                                                       | 7         |

| 4.6      | Schematic, board layout and bill of materials                    | 9         |

| <b>5</b> | <b>Configuring the hardware</b>                                  | <b>9</b>  |

| 5.1      | CAN FD interface                                                 | 9         |

| <b>6</b> | <b>Available accessories</b>                                     | <b>10</b> |

| <b>7</b> | <b>Legal information</b>                                         | <b>11</b> |

---

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

---