## Compact PMIC with Source Voltage Level Configuration for Single/ Dual PV Cells or Pulsed Source

### Features and Benefits

**Cold start from 250 mV input voltage and 5  $\mu$ W input power (typical)**

- Fast start-up from source.

**Constant input voltage regulation (0.12 V to 1.47 V)**

- Optimized for single/dual elements capacitive PV cell, intermittent and pulsed power sources.

**Selectable overdischarge and overcharge protection**

- Supports various types of rechargeable batteries (LiC, Li-ion, LiPo, Li-ceramic pouch, etc.).

**Ultra-low power idle mode**

- Stored energy is preserved when no source available.

**Shipping and shelf mode**

- Prevents energy drain from battery when no source available (**KEEP\_ALIVE** pin);

- Disables storage element charging (**DIS\_STO\_CH** pin).

**Configuration pins or I<sup>2</sup>C**

- Easy setup;

- Basic settings at startup with configuration pins;

- Advanced configuration with I<sup>2</sup>C (Fast Mode Plus).

**Average power monitoring**

- Easy estimation of the harvested power.

**Integrated thermistor conditioning circuit**

- Configurable battery thermal protection.

### Applications

Wearable Electronics

Remote Control

Smart Buildings

Keyboards

Electronic Shelf Labels

Indoor Sensors

### Description

The AEM0090x is a compact, fully integrated battery charger that harvests DC power to store energy in rechargeable batteries. It extends battery lifetime and removes the need for primary energy storage in a large range of applications.

Selecting the operating voltage allows the user to set a constant Maximum Power Point at which the AEM0090x operates, to charge a storage element, such as a Li-ion battery or a LiC. The boost converter operates with input voltages ranging from 120 mV to 1.47 V, making AEM0090x ideal for single or dual element PV cell.

The AEM0090x has a unique cold-start circuit capable of operation with input voltages as low as 250 mV and power as minimal as 5  $\mu$ W. The output voltages ranges from 2.8 V to 4.8 V, with configurable protection levels to prevent overcharging and overdischarging of the storage element. No external components are necessary to set these protection levels. Additionally, thermal monitoring safeguards the storage element, while an Average Power Monitoring system offers insights into the harvested energy for the application circuit.

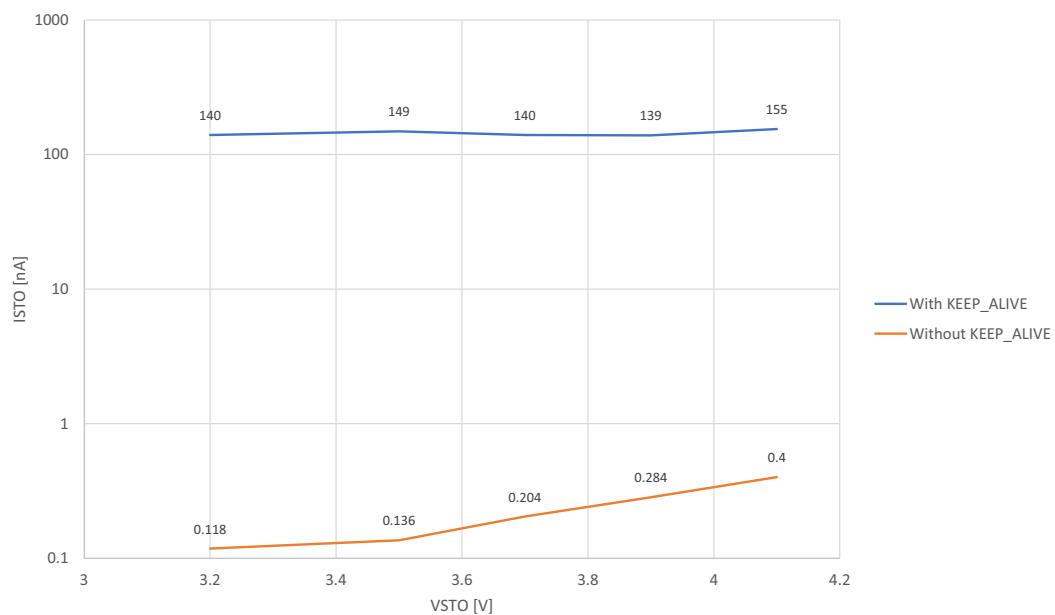

Thanks to the keep-alive feature, the AEM0090x internal circuit can stay powered by the storage element even in absence of a harvesting source. When keep-alive is disabled and no harvesting source is present, the AEM0090x turns off, preserving the energy of the storage element.

A shelf-mode can be obtained by disabling the keep-alive feature, preventing the battery to be drained during device storage. Furthermore, enabling the **DIS\_STO\_CH** feature creates a shipping mode by preventing battery charging.

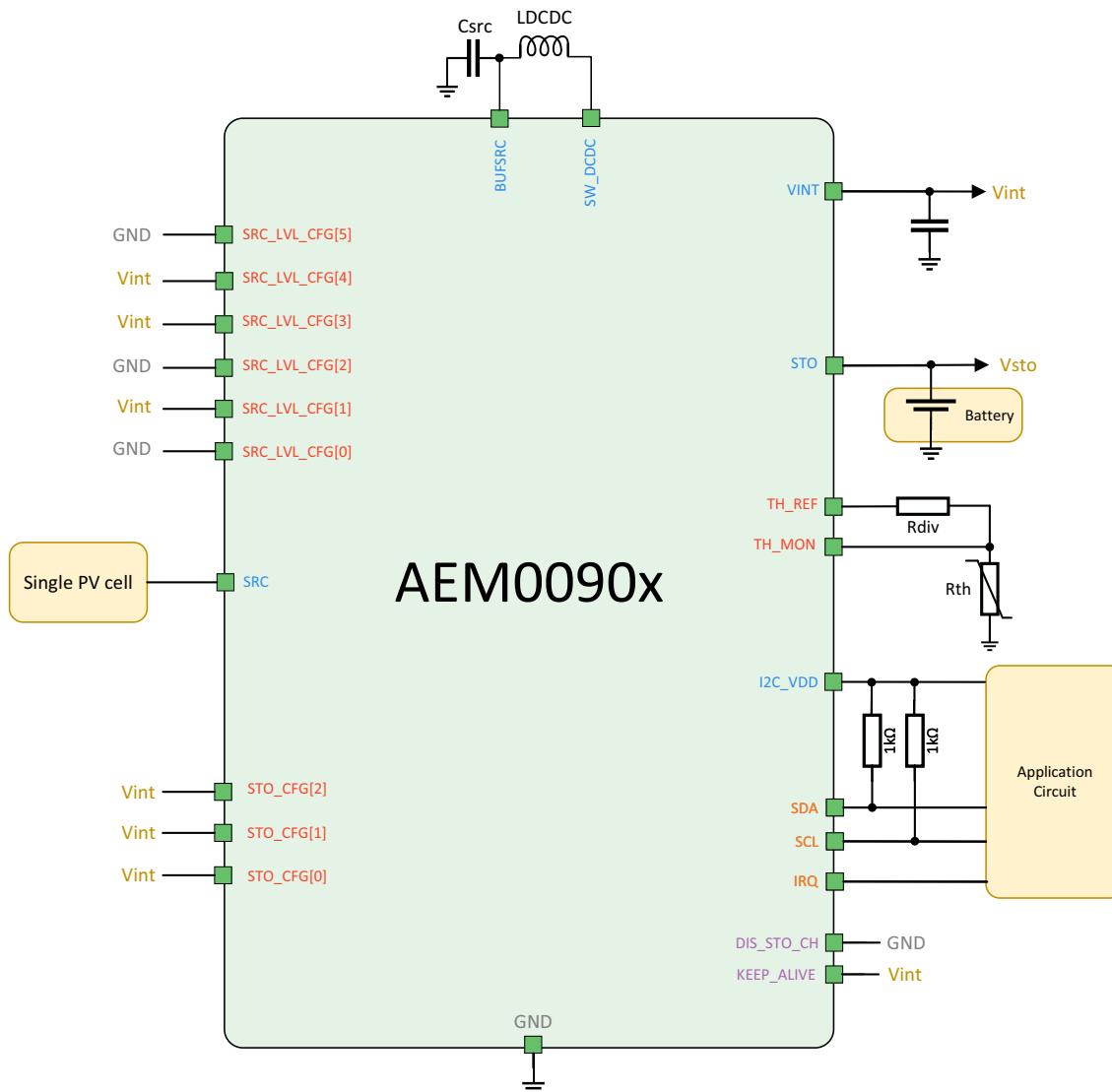

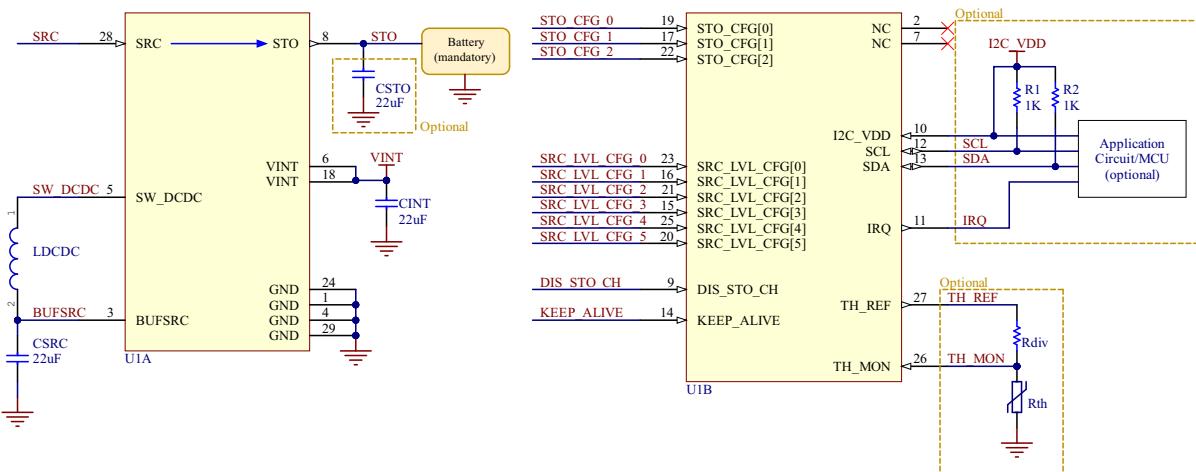

The AEM00900 application schematic is featuring small PCB size (51 mm<sup>2</sup>) and a global lower bill of material. The AEM00901 application schematic allows higher performance with a PCB area penalty as low as 6 mm<sup>2</sup>, enabling small size and low cost implementation for single/dual element PV or pulsed sources versus other DCDC based solutions.

### Device Information

| Part Number     | Package    | Body size |

|-----------------|------------|-----------|

| 10AEM00900C0000 | QFN 28-pin | 4x4mm     |

| 10AEM00901C0000 |            |           |

### Evaluation Board

| Part number    |

|----------------|

| 2AAEM00900C001 |

| 2AAEM00901C001 |

## Table of Contents

|                                                                   |    |

|-------------------------------------------------------------------|----|

| <b>1. Introduction</b>                                            | 6  |

| <b>2. Pin Configuration and Functions</b>                         | 7  |

| <b>3. Absolute Maximum Ratings</b>                                | 9  |

| <b>4. Thermal Resistance</b>                                      | 9  |

| <b>5. Material</b>                                                | 9  |

| 5.1. RoHS Compliance .....                                        | 9  |

| 5.2. REACH Compliance .....                                       | 9  |

| <b>6. Typical Electrical Characteristics at 25 °C</b>             | 10 |

| <b>7. Recommended Operation Conditions</b>                        | 11 |

| <b>8. Functional Block Diagram</b>                                | 12 |

| <b>9. Theory of Operation</b>                                     | 13 |

| 9.1. Boost Converter .....                                        | 13 |

| 9.2. Source Voltage Regulation .....                              | 13 |

| 9.3. Thermal Monitoring .....                                     | 13 |

| 9.4. Average Power Monitoring .....                               | 14 |

| 9.5. Automatic High Power Mode (AEM00900 only) .....              | 14 |

| 9.6. Keep-alive .....                                             | 14 |

| 9.7. IRQ Pin .....                                                | 14 |

| 9.8. State Description .....                                      | 15 |

| 9.8.1. Reset State .....                                          | 15 |

| 9.8.2. Sense STO State .....                                      | 15 |

| 9.8.3. Supply State .....                                         | 15 |

| 9.8.4. Sleep State .....                                          | 15 |

| <b>10. System Configuration</b>                                   | 16 |

| 10.1. Configuration Pins and I <sup>2</sup> C .....               | 16 |

| 10.1.1. Configuration Pins .....                                  | 16 |

| 10.1.2. Configuration by I <sup>2</sup> C .....                   | 16 |

| 10.2. Source Level Configuration .....                            | 17 |

| 10.3. Storage Element Thresholds Configuration .....              | 17 |

| 10.4. Disable Storage Element Charging .....                      | 18 |

| 10.5. I <sup>2</sup> C Serial Interface Protocol .....            | 19 |

| 10.6. Registers Map .....                                         | 21 |

| 10.7. Registers Configurations .....                              | 23 |

| 10.7.1. Version Register (VERSION) .....                          | 23 |

| 10.7.2. Source Voltage Regulation Register (SRCREGU) .....        | 23 |

| 10.7.3. Storage Element Threshold Registers (VOVDIS, VOVCH) ..... | 25 |

| 10.7.4. Temperature Register (TEMPCOLD, TEMPHOT) .....            | 25 |

| 10.7.5. Power Register (PWR) .....                                | 26 |

| 10.7.6. Sleep Register (SLEEP) .....                              | 27 |

| 10.7.7. Storage Element Acquisition Rate Register (STOMON) .....  | 28 |

| 10.7.8. Average Power Monitoring Control Register (APM) .....     | 28 |

| 10.7.9. IRQ Enable Register (IRQEN) .....                         | 29 |

| 10.7.10. I <sup>2</sup> C Control (CTRL) .....                    | 30 |

|                                                                             |           |

|-----------------------------------------------------------------------------|-----------|

| 10.7.11. IRQ Flag Register (IRQFLG) .....                                   | 30        |

| 10.7.12. Status Register (STATUS) .....                                     | 31        |

| 10.7.13. Average Power Monitoring Data Registers (APM) .....                | 32        |

| 10.7.14. Temperature Data Register (TEMP) .....                             | 32        |

| 10.7.15. Battery Voltage Register (STO) .....                               | 33        |

| Table 27: .....                                                             | 33        |

| 10.8. External Components .....                                             | 34        |

| 10.8.1. Storage Element .....                                               | 34        |

| 10.8.2. External Inductor Information .....                                 | 34        |

| 10.8.3. External Capacitors Information .....                               | 34        |

| 10.8.4. Optional External Components for Thermal Monitoring .....           | 34        |

| 10.8.5. Optional Pull-up Resistors for the I <sup>2</sup> C Interface ..... | 34        |

| <b>11. Typical Application Circuits</b>                                     | <b>35</b> |

| 11.1. Example Circuit 1 .....                                               | 35        |

| 11.2. Example Circuit 2 .....                                               | 36        |

| <b>12. Circuit Behavior</b>                                                 | <b>37</b> |

| <b>13. Performance Data</b>                                                 | <b>40</b> |

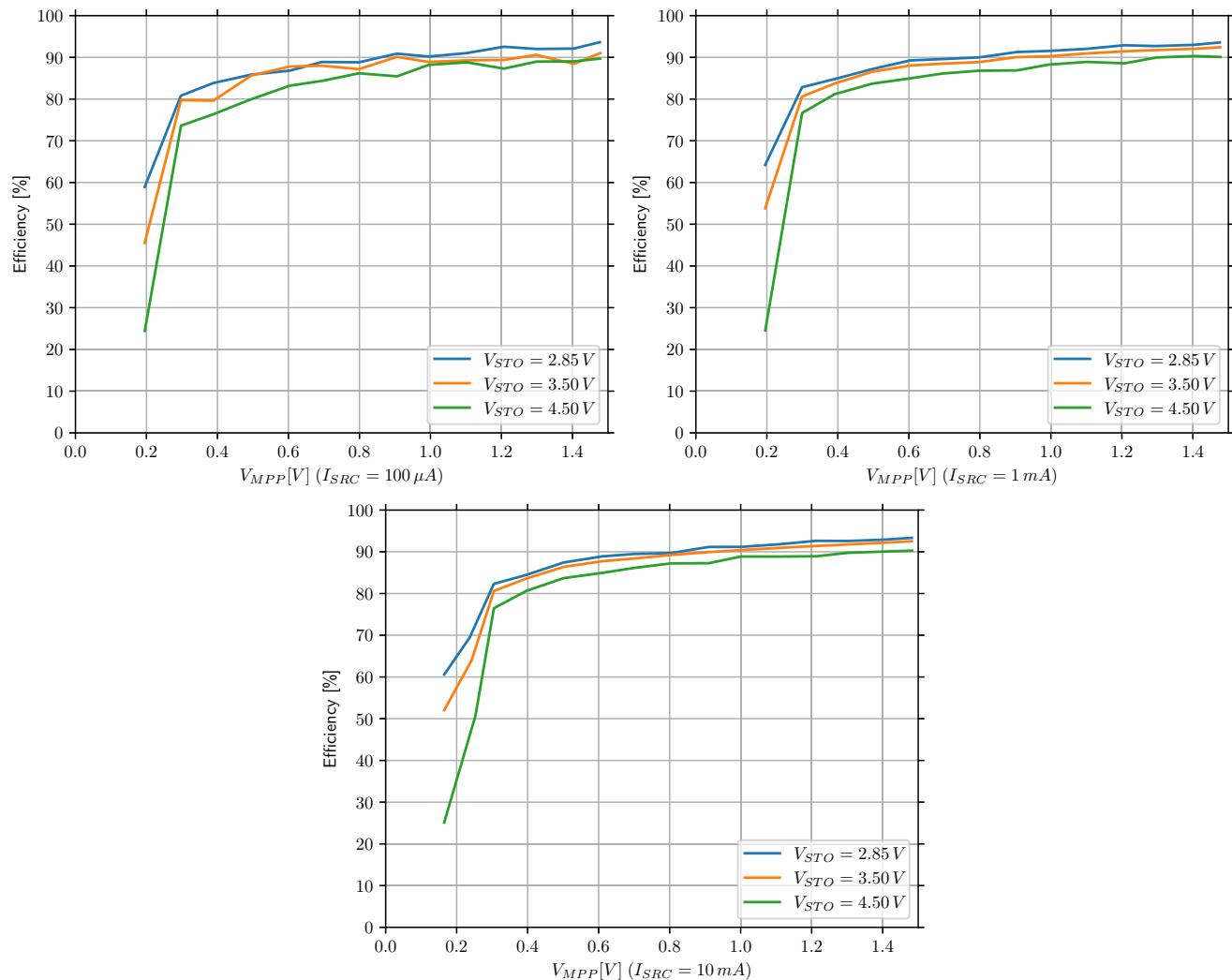

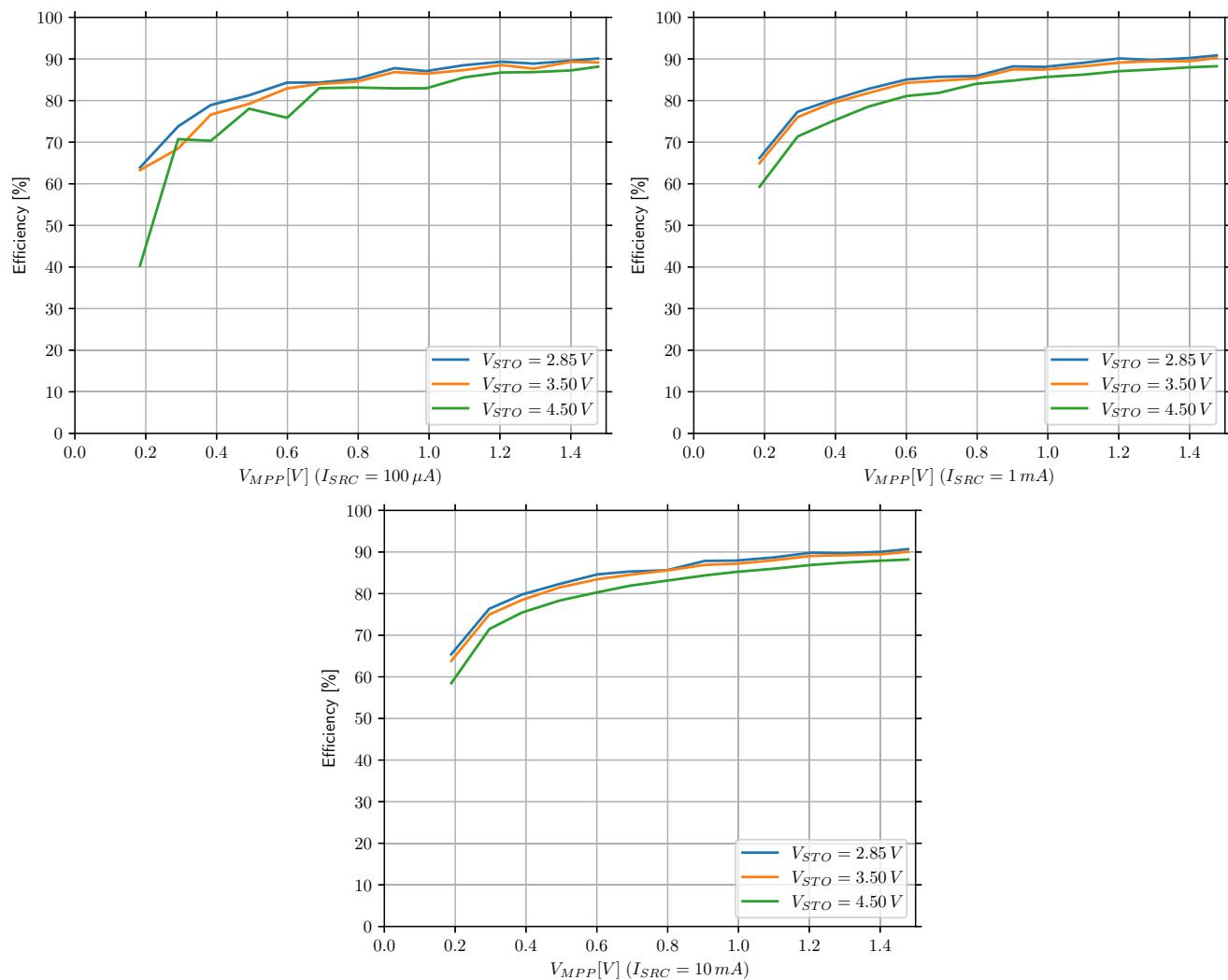

| 13.1. DCDC Conversion Efficiency .....                                      | 40        |

| 13.2. Quiescent Current .....                                               | 42        |

| <b>14. Package Information</b>                                              | <b>43</b> |

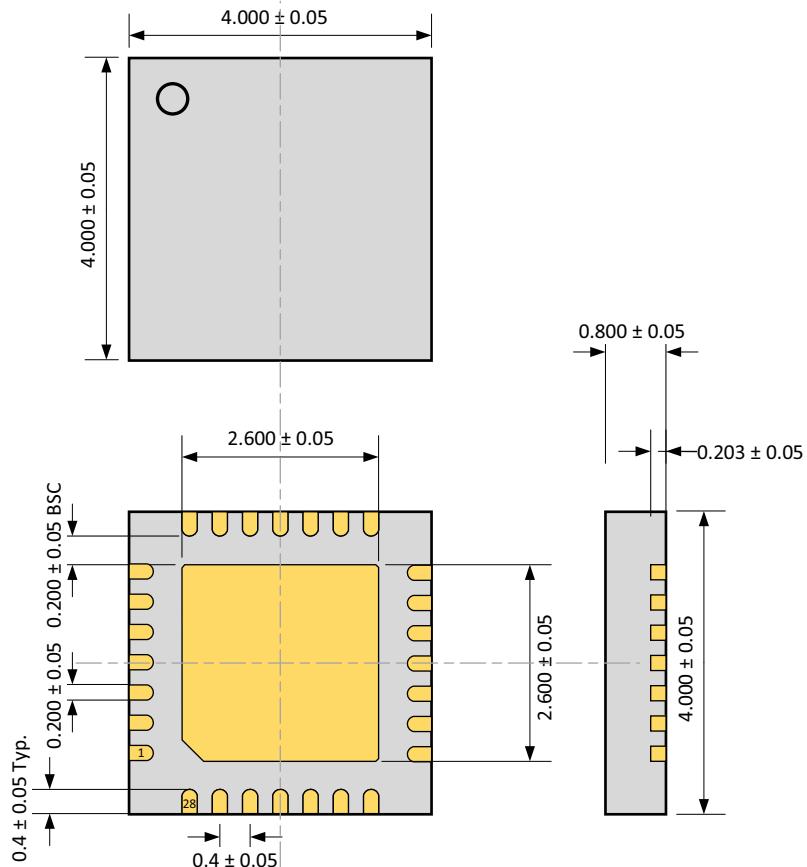

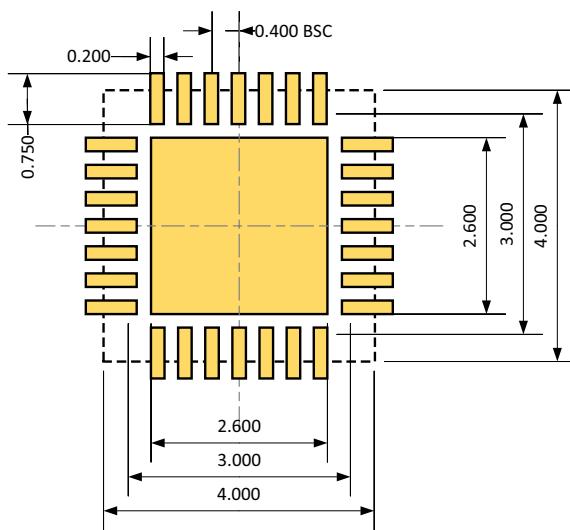

| 14.1. Plastic Quad Flatpack no-lead (QFN28 4x4mm) .....                     | 43        |

| 14.2. QFN28 Board Layout .....                                              | 43        |

| <b>15. Minimum BOM</b>                                                      | <b>44</b> |

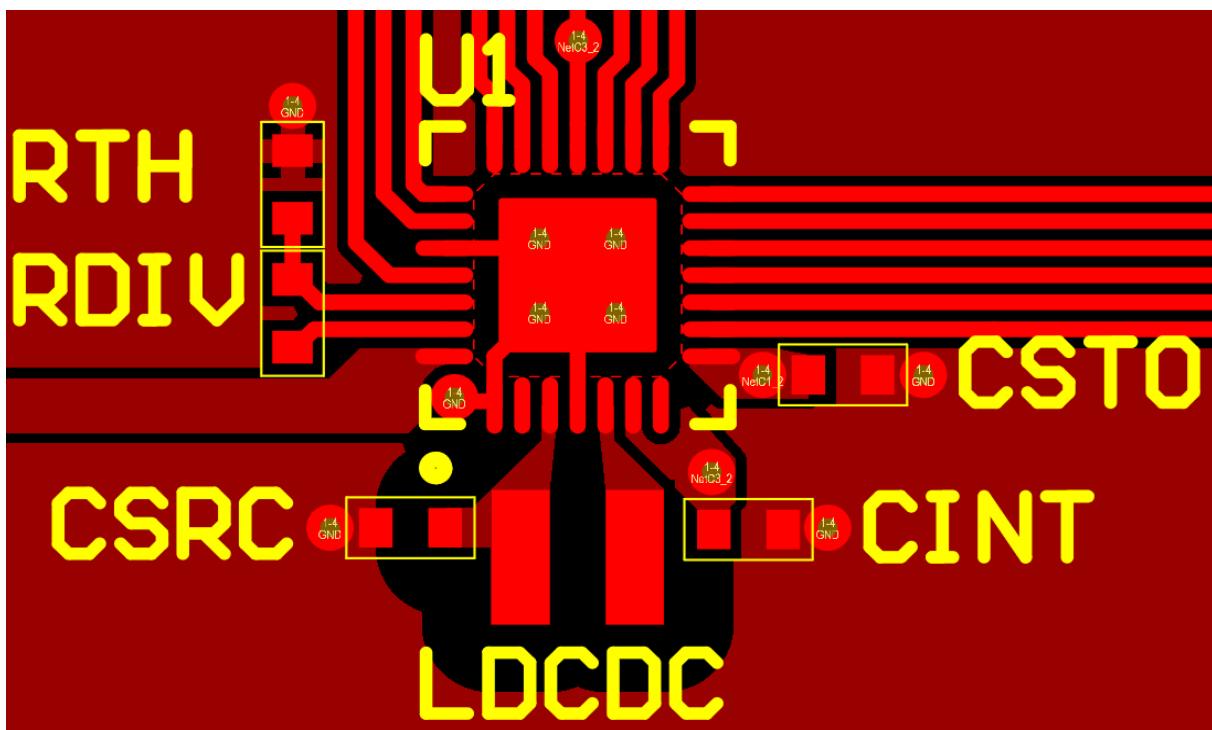

| <b>16. Layout</b>                                                           | <b>45</b> |

| <b>17. Glossary</b>                                                         | <b>47</b> |

| <b>18. Revision History</b>                                                 | <b>48</b> |

## List of Figures

|                                                                                        |    |

|----------------------------------------------------------------------------------------|----|

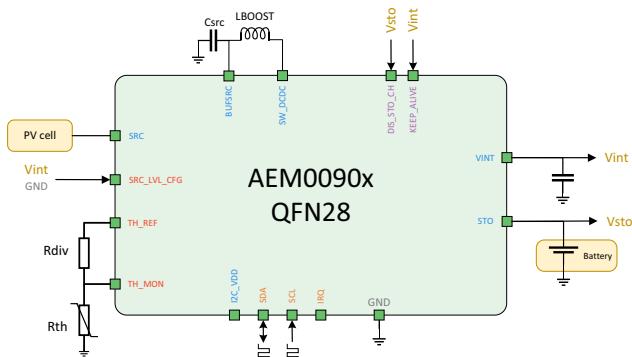

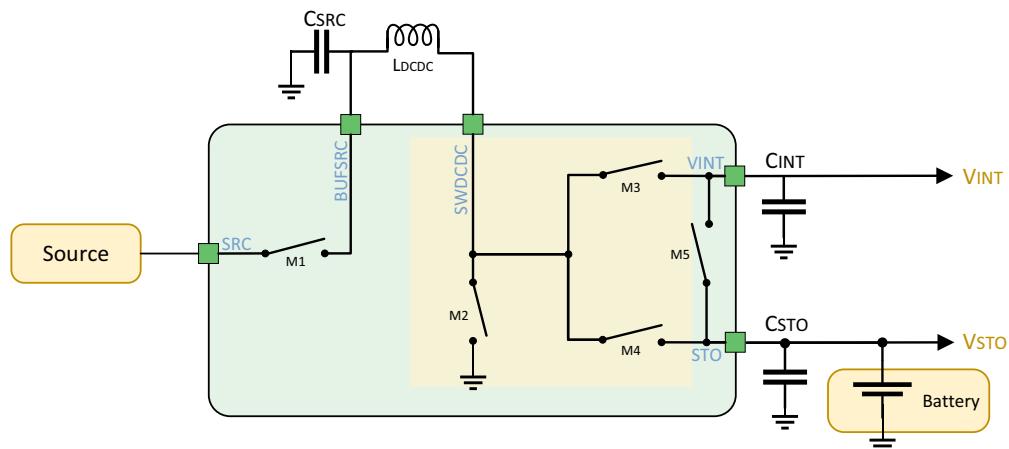

| Figure 1: Simplified schematic view .....                                              | 6  |

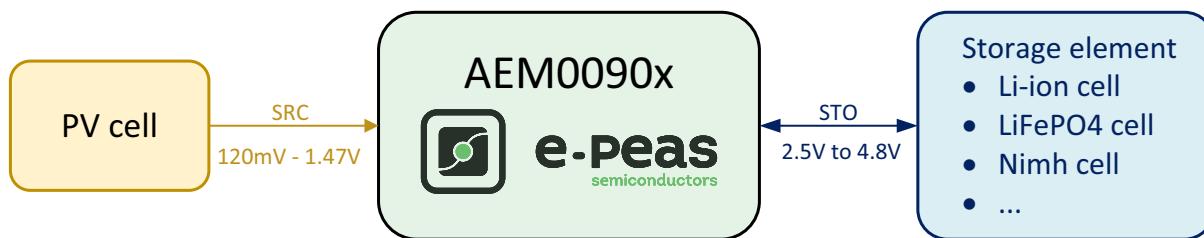

| Figure 2: Pinout diagram QFN28 .....                                                   | 7  |

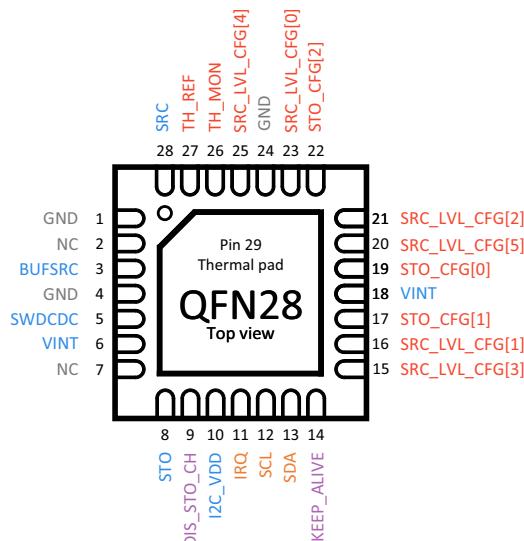

| Figure 3: Functional block diagram .....                                               | 12 |

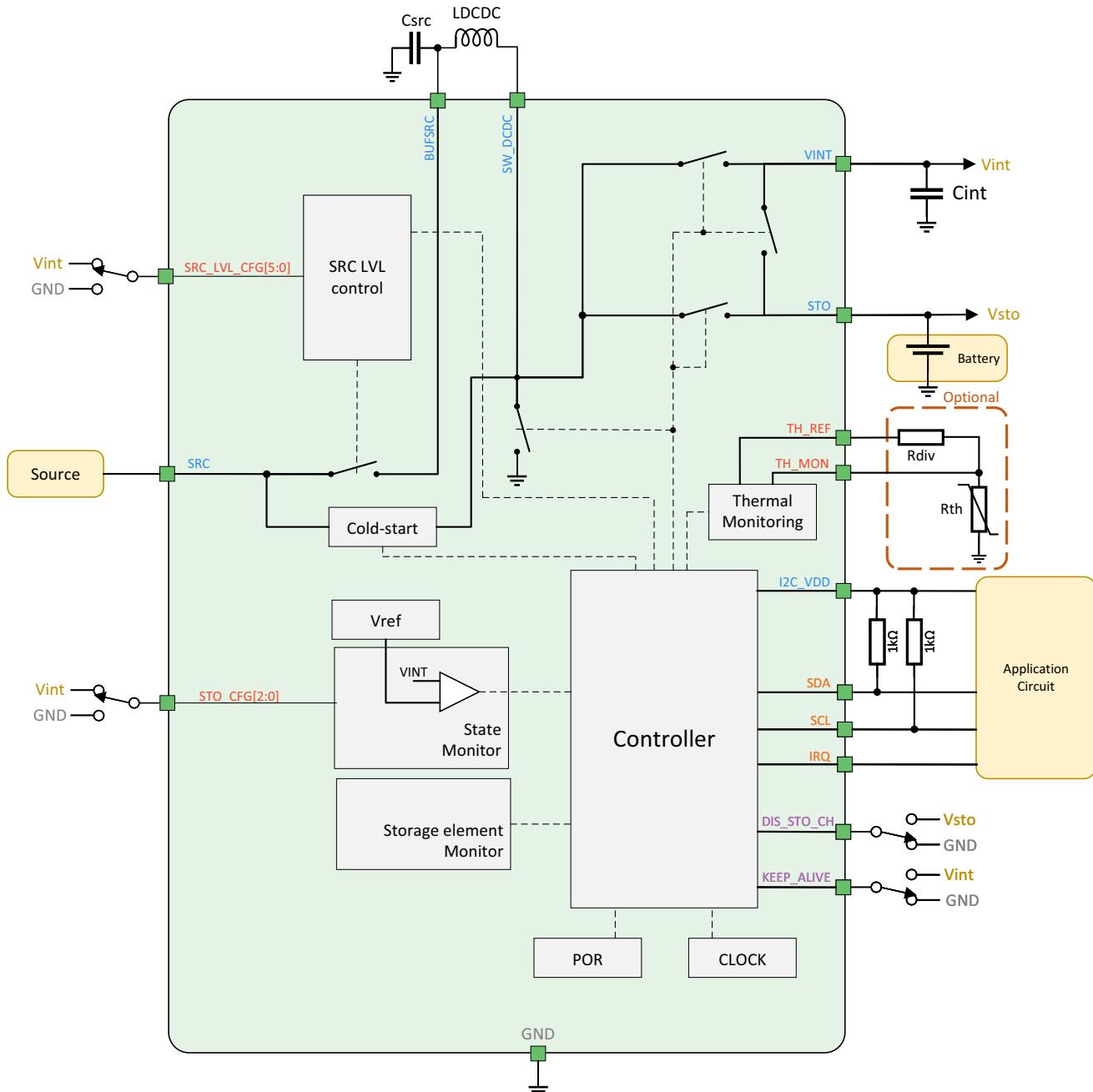

| Figure 4: Simplified schematic view of the AEM0090x .....                              | 13 |

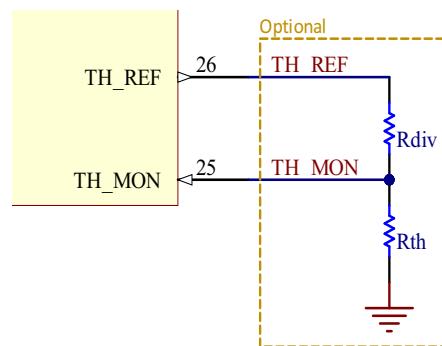

| Figure 5: TH_REF and TH_MON connections .....                                          | 13 |

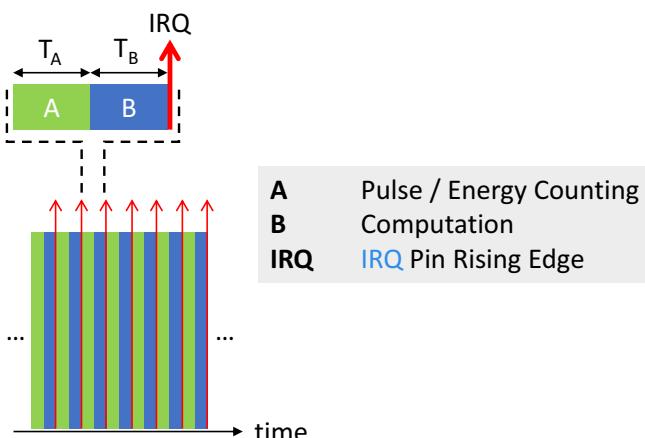

| Figure 6: Average Power Monitoring description .....                                   | 14 |

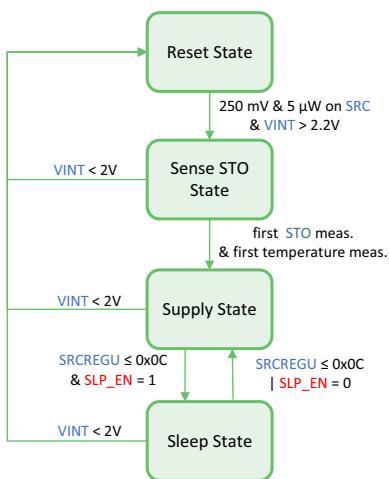

| Figure 7: Diagram of the AEM0090x state machine .....                                  | 15 |

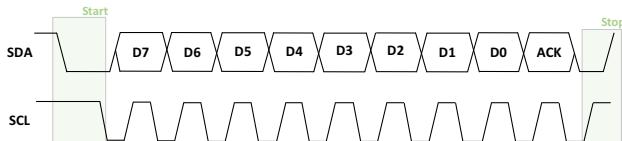

| Figure 8: I <sup>2</sup> C transmission frame .....                                    | 19 |

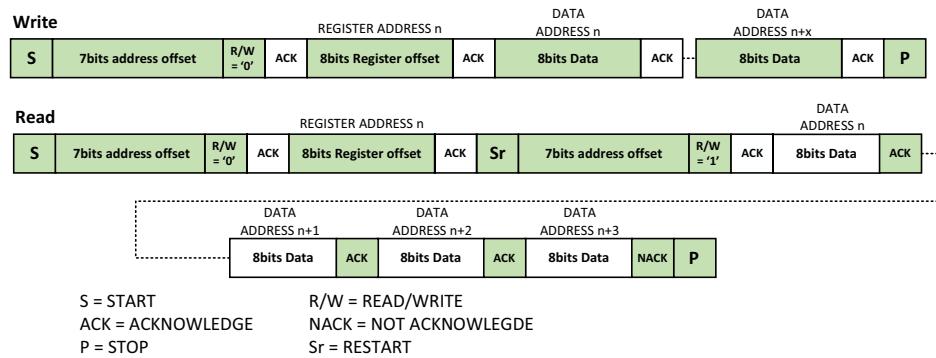

| Figure 9: Read and write transmission .....                                            | 20 |

| Figure 10: Typical application circuit 1 .....                                         | 35 |

| Figure 11: Typical application circuit 2 .....                                         | 36 |

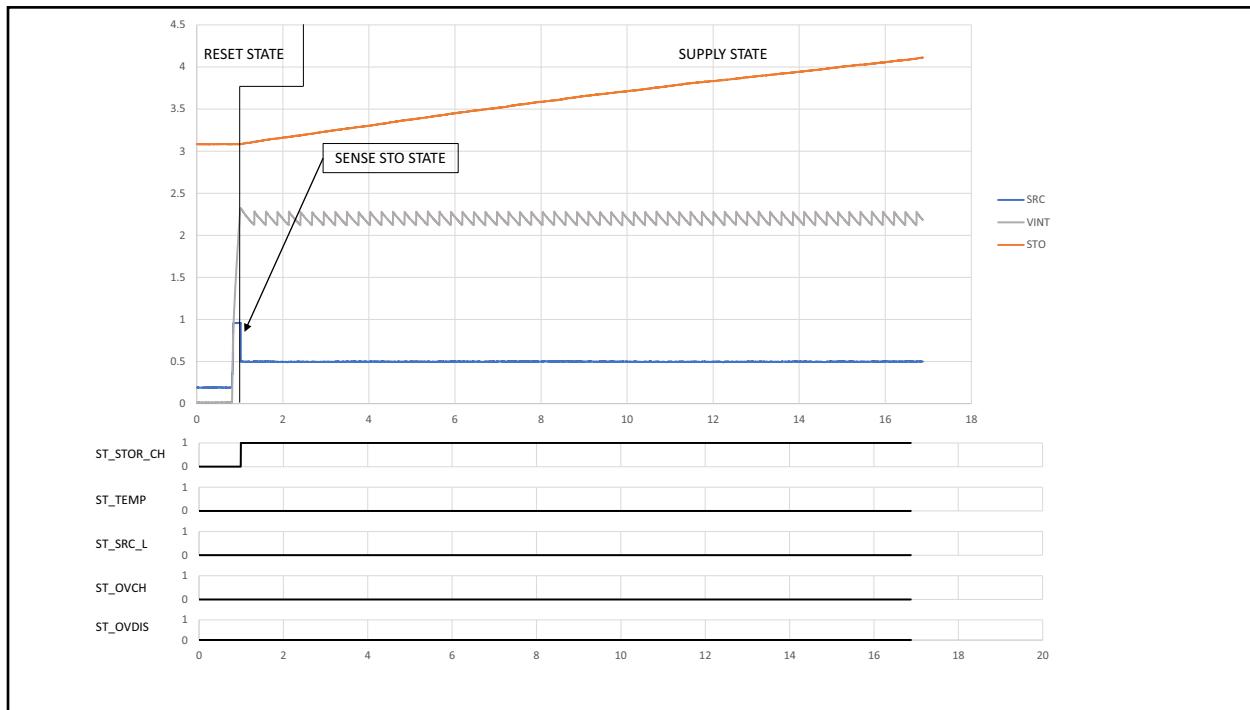

| Figure 12: Start-up State .....                                                        | 37 |

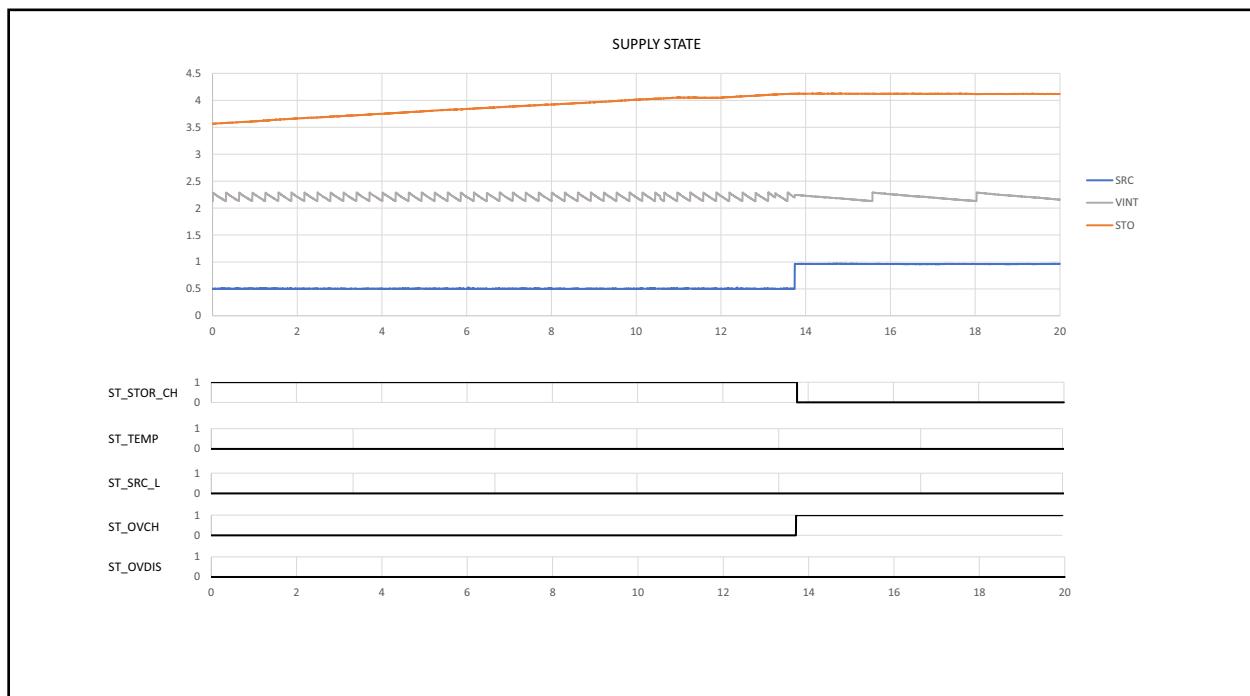

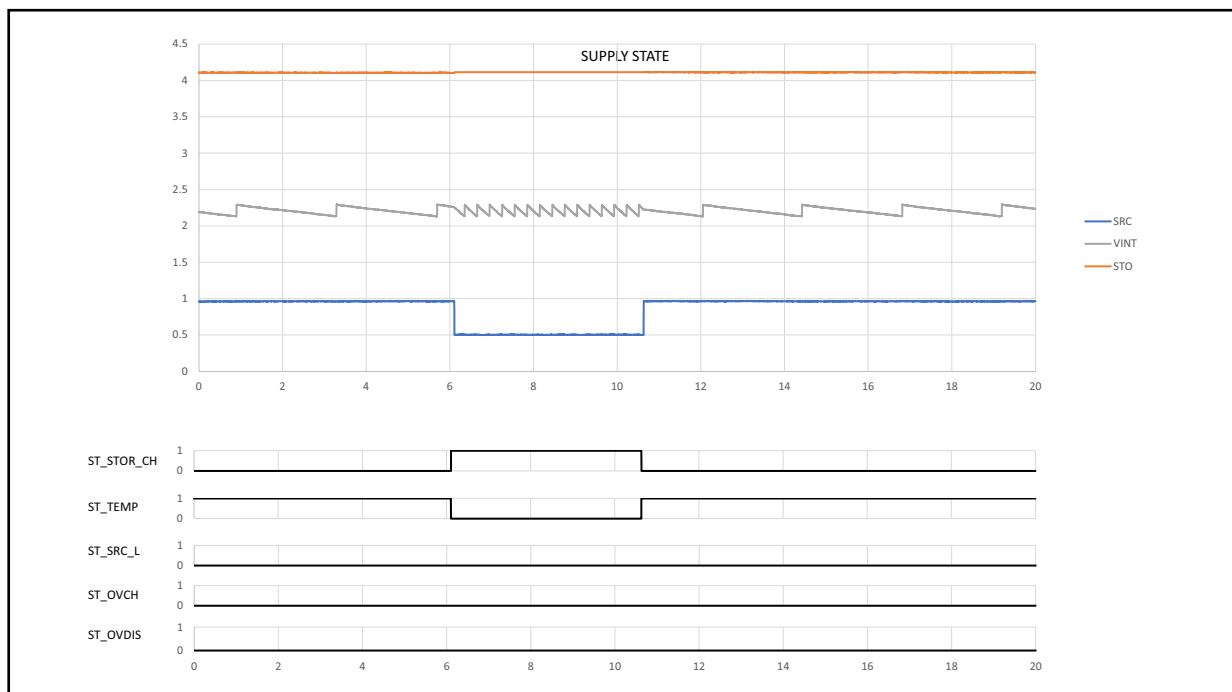

| Figure 13: Supply State .....                                                          | 37 |

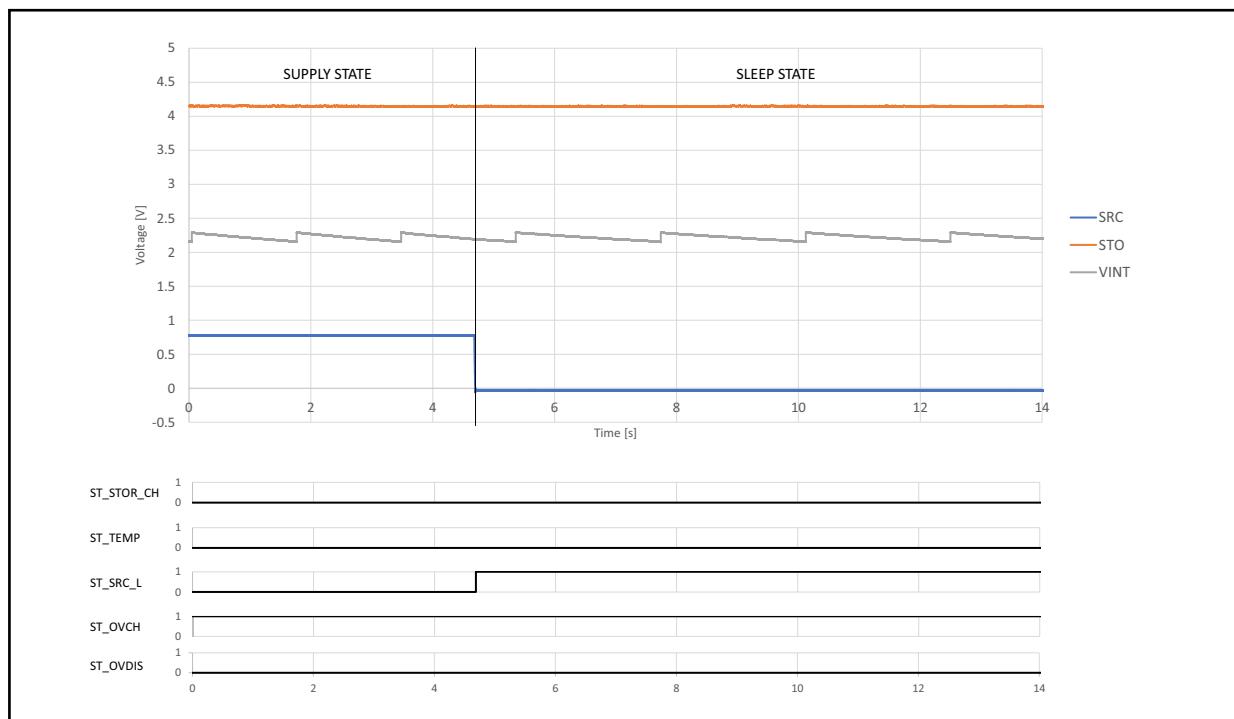

| Figure 14: Behavior with the Keep Alive mode and without the source .....              | 38 |

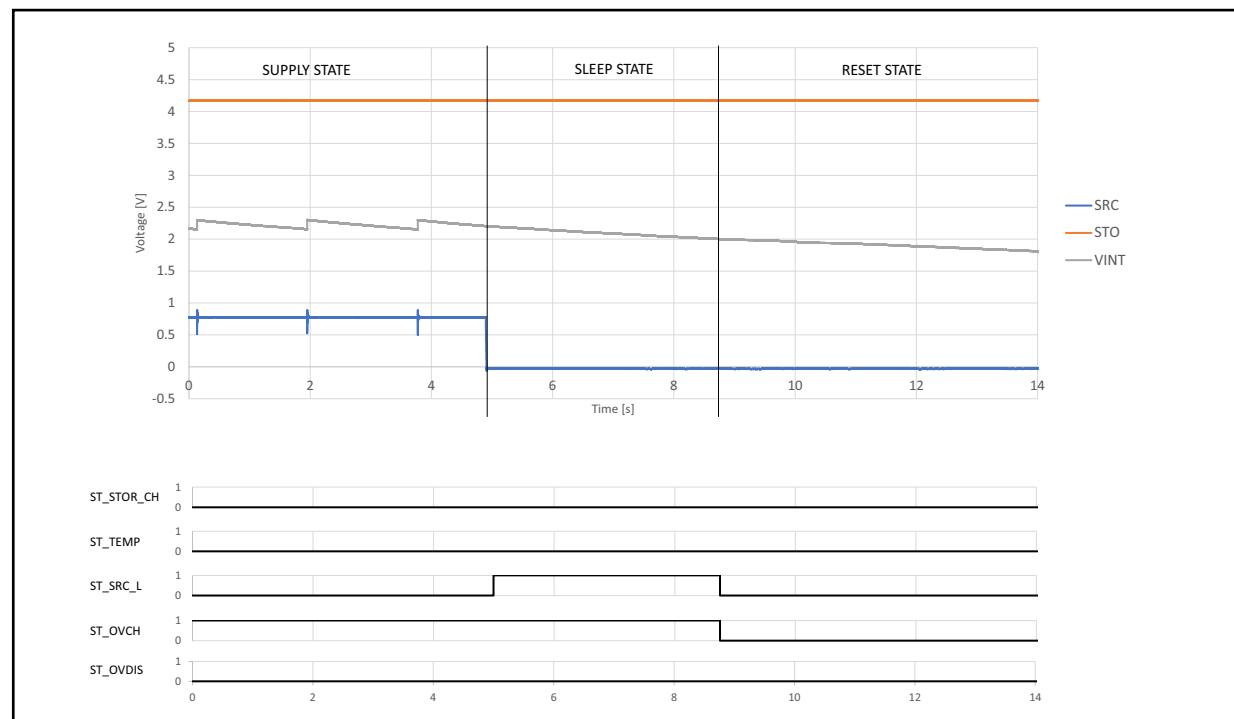

| Figure 15: Behavior without the Keep Alive mode and without the source .....           | 38 |

| Figure 16: Thermal Monitoring Behavior .....                                           | 39 |

| Figure 17: AEM00901 DCDC conversion efficiency (LDCDC: Coilcraft LPS4018-333MRB) ..... | 40 |

| Figure 18: AEM00900 DCDC conversion efficiency (LDCDC: TDK VLS252012HBX-6R8M-1) .....  | 41 |

| Figure 19: Quiescent current .....                                                     | 42 |

| Figure 20: QFN28 4x4 mm .....                                                          | 43 |

| Figure 21: QFN28 4x4 mm board layout .....                                             | 43 |

| Figure 22: AEM0090x schematic .....                                                    | 44 |

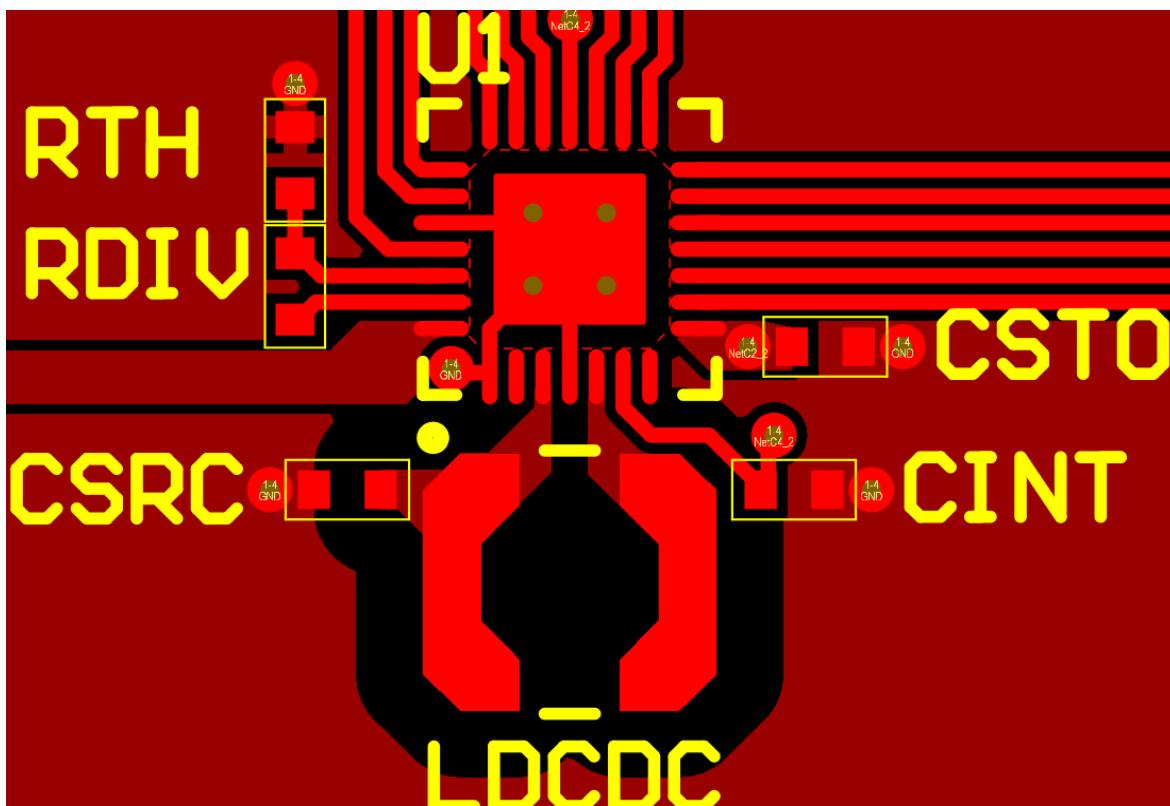

| Figure 23: AEM00900 QFN28 layout example .....                                         | 45 |

| Figure 24: AEM00901 QFN28 layout example .....                                         | 46 |

## List of Tables

|                                                                 |    |

|-----------------------------------------------------------------|----|

| Table 1: Pins description QFN28 .....                           | 7  |

| Table 2: Absolute maximum ratings .....                         | 9  |

| Table 3: Thermal data .....                                     | 9  |

| Table 4: Electrical characteristics .....                       | 10 |

| Table 5: Recommended operating conditions .....                 | 11 |

| Table 6: Configuration of SRC_LVL_CFG[5:0] .....                | 17 |

| Table 7: Usage of STO_CFG[2:0] .....                            | 18 |

| Table 8: Register summary .....                                 | 21 |

| Table 9: VERSION register .....                                 | 23 |

| Table 10: SRCREGU register (0x01) .....                         | 24 |

| Table 11: TEMP_COLD register .....                              | 25 |

| Table 12: TEMP_HOT register .....                               | 26 |

| Table 13: PWR register .....                                    | 26 |

| Table 14: SLEEP register .....                                  | 27 |

| Table 15: Configuration of the sleep threshold .....            | 27 |

| Table 16: Acquisition rates for STO ADC .....                   | 28 |

| Table 17: APM register .....                                    | 28 |

| Table 18: Configuration of APM computation windows .....        | 28 |

| Table 19: IRQEN register .....                                  | 29 |

| Table 20: CTRL register .....                                   | 30 |

| Table 21: IRQFLG register .....                                 | 30 |

| Table 22: Status register .....                                 | 31 |

| Table 23: APM registers in pulse counter mode .....             | 32 |

| Table 24: APM to nano-Joule conversion factor .....             | 32 |

| Table 25: APM register in power meter mode .....                | 32 |

| Table 26: TEMP register .....                                   | 32 |

| Table 27: STO register .....                                    | 33 |

| Table 28: Typical application circuit 2 register settings ..... | 36 |

| Table 29: AEM0090x bill of material .....                       | 44 |

| Table 30: Revision history .....                                | 48 |

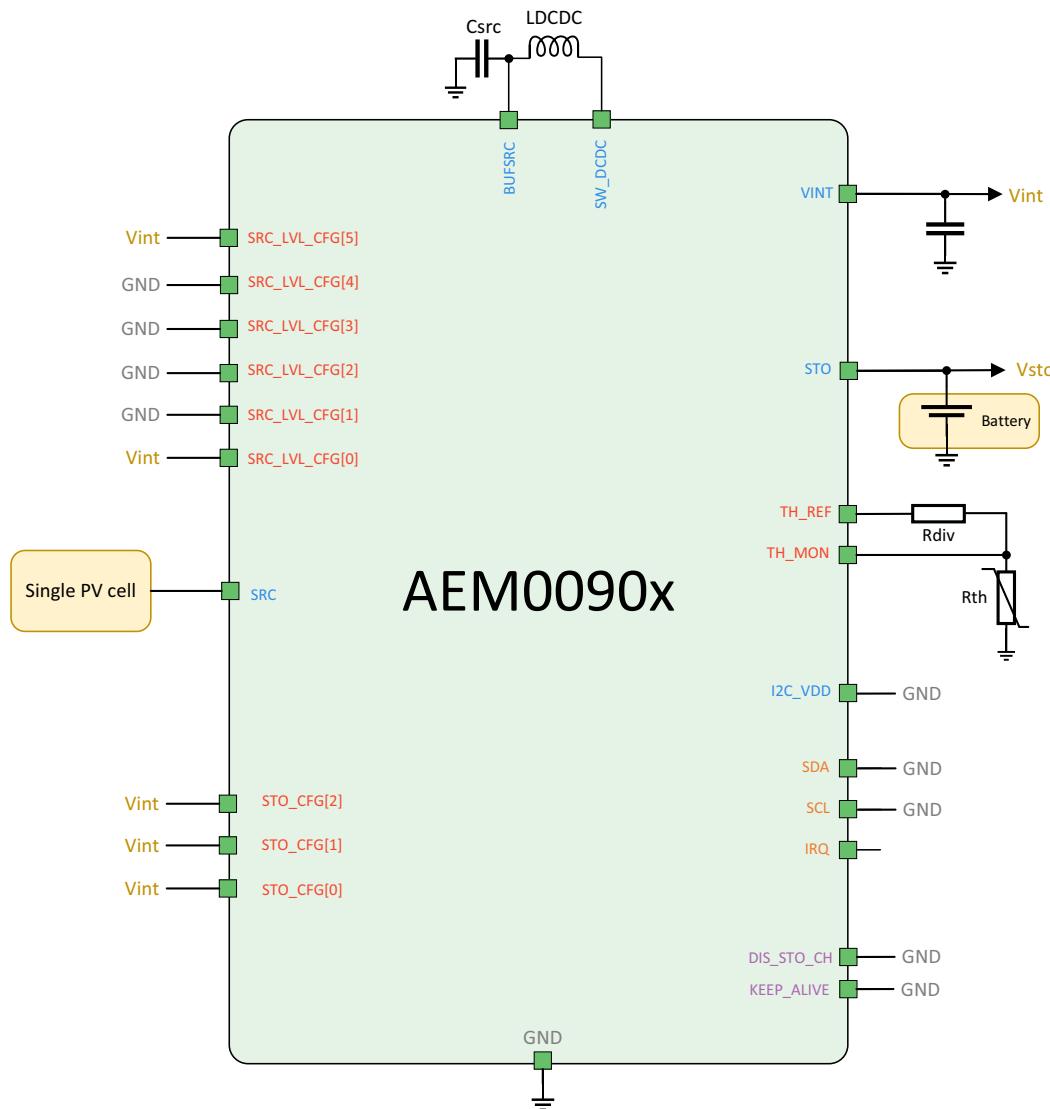

Figure 1: Simplified schematic view

## 1. Introduction

The AEM0090x is a full-featured energy efficient battery charger able to charge a storage element (connected to **STO**) from an energy source (connected to **SRC**).

The core of the AEM0090x is a regulated switching converter (boost) with high power conversion efficiency.

At first start-up, as soon as a required cold-start voltage of 250 mV and a sparse amount of power of at least 5  $\mu$ W is available at the source (**KEEP\_ALIVE** set to HIGH), the AEM0090x coldstarts. After the cold start, the AEM extracts the power available from the source if the input voltage is higher than  $V_{SRC,REG}$ .

The AEM0090x can be fully configured through the I<sup>2</sup>C or partially by configuration pins. I<sup>2</sup>C configuration is not mandatory, as the default configuration is made to fit the most common needs, along with the configuration pins for the most common settings.

Through I<sup>2</sup>C communication or through the configuration pins, the user can select a specific operating mode from a variety of modes that cover most application requirements without any dedicated external component. The battery protection thresholds ( $V_{OVCH}$  and  $V_{OVDIS}$ ) can be configured with the help of the **STO\_CFG[2:0]** pins. They can also be configured in 60 mV steps using the I<sup>2</sup>C bus.

Depending on the harvester, the source regulation voltage,  $V_{SRC,REG}$ , can be configured using six configuration pins (**SRC\_LVL\_CFG[5:0]**) or using I<sup>2</sup>C communication.

The AEM0090x features an optional temperature protection. It can be set through the I<sup>2</sup>C interface and allows to define a temperature range so that, when the ambient temperature is outside that range, battery charging is disabled. One additional resistor and one additional thermistor are needed for this feature.

The **KEEP\_ALIVE** functionality sets the source from which the AEM0090x supplies its internal circuitry **VINT**. It can be supplied either from the harvester connected on **SRC** or from the battery connected to **STO**.

When **KEEP\_ALIVE** is disabled, the AEM0090x internal circuitry is running as long as enough energy is available on **SRC**. If no energy is available on **SRC**, the internal voltage drops down to reset voltage and the AEM needs to go through a cold start before being able to charge the battery again. This is useful for applications with long periods without energy on **SRC** and when the I<sup>2</sup>C is not used. If the I<sup>2</sup>C communication is used, the AEM will need to be reconfigured after the cold-start. With this setting there is no quiescent current taken from the battery to supply the AEM0090x and the power balance is always positive.

When **KEEP\_ALIVE** is enabled, the AEM0090x is supplied by **STO**, the circuit stays in **SUPPLY STATE** or **SLEEP STATE** as long as the battery connected to **STO** is above the overdischarge threshold. It prevents loosing the I<sup>2</sup>C configuration when energy harvesting is not occurring and offers faster reactivity as the AEM is not reset depending on the available energy on **SRC**.

## 2. Pin Configuration and Functions

Figure 2: Pinout diagram QFN28

| NAME                       | PIN NUMBER | Function                                                                                                                                                                                                                          |

|----------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Power Pins</b>          |            |                                                                                                                                                                                                                                   |

| SRC                        | 28         | Connection to the harvested energy source.                                                                                                                                                                                        |

| BUFSRC                     | 3          | Connection to an external capacitor buffering the boost converter input.                                                                                                                                                          |

| SWDCDC                     | 5          | Switching node of the boost converter.                                                                                                                                                                                            |

| VINT                       | 6, 18      | Internal supply voltage.                                                                                                                                                                                                          |

| STO                        | 8          | Connection to the energy storage element (rechargeable battery). Cannot be left floating, voltage must always be above 2.5 V.                                                                                                     |

| I2C_VDD                    | 10         | Connection to supply the I <sup>2</sup> C interface. <ul style="list-style-type: none"> <li>Connect to a 1.5 V to 5.0 V power supply if I<sup>2</sup>C is used.</li> <li>Connect to GND if I<sup>2</sup>C is not used.</li> </ul> |

| <b>I<sup>2</sup>C Pins</b> |            |                                                                                                                                                                                                                                   |

| SDA                        | 13         | Bidirectional data line. Connect to I2C_VDD if not used.                                                                                                                                                                          |

| SCL                        | 12         | Unidirectional serial clock for I <sup>2</sup> C. Connect to I2C_VDD if not used.                                                                                                                                                 |

| IRQ                        | 11         | Output Interrupt request. Leave floating if not used.                                                                                                                                                                             |

| <b>Configuration Pins</b>  |            |                                                                                                                                                                                                                                   |

| STO_CFG[0]                 | 19         | Used for the configuration of the threshold voltages for the energy storage element. Read as HIGH if left floating.                                                                                                               |

| STO_CFG[1]                 | 17         |                                                                                                                                                                                                                                   |

| STO_CFG[2]                 | 22         |                                                                                                                                                                                                                                   |

| SRC_LVL_CFG[0]             | 23         | Used for the configuration of the source voltage level. Read as HIGH if left floating.                                                                                                                                            |

| SRC_LVL_CFG[1]             | 16         |                                                                                                                                                                                                                                   |

| SRC_LVL_CFG[2]             | 21         |                                                                                                                                                                                                                                   |

| SRC_LVL_CFG[3]             | 15         |                                                                                                                                                                                                                                   |

| SRC_LVL_CFG[4]             | 25         |                                                                                                                                                                                                                                   |

| SRC_LVL_CFG[5]             | 20         |                                                                                                                                                                                                                                   |

| TH_REF                     | 27         | Reference voltage for thermal monitoring. Leave floating if not used.                                                                                                                                                             |

| TH_MON                     | 26         | Pin for temperature monitoring. Connect to VINT if not used.                                                                                                                                                                      |

| <b>Control Pins</b>        |            |                                                                                                                                                                                                                                   |

| DIS_STO_CH                 | 9          | When HIGH, the AEM stops charging the battery. Read as LOW if left floating.                                                                                                                                                      |

| KEEP_ALIVE                 | 14         | When HIGH, the internal circuitry is supplied from STO. When LOW, the internal circuitry is supplied from SRC.                                                                                                                    |

Table 1: Pins description QFN28

| NAME              | PIN NUMBER                    | Function                                                                                                                                              |

|-------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Other pins</b> |                               |                                                                                                                                                       |

| GND               | 1, 4, 24, 29<br>(thermal pad) | Ground connection, each terminal should be strongly tied to the PCB ground plane, pin 29 (thermal pad) being the main GND connection of the AEM0090x. |

| NC                | 2, 7                          | Not connected pins, leave floating.                                                                                                                   |

Table 1: Pins description QFN28

### 3. Absolute Maximum Ratings

| Parameter                                                                                                                                                                                                 | Value          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Voltage on <a href="#">SRC</a>                                                                                                                                                                            | 2.0 V          |

| Voltage on <a href="#">BUFSRC</a> , <a href="#">SWDCDC</a> , <a href="#">STO</a> , <a href="#">I2C_VDD</a> , <a href="#">SDA</a> , <a href="#">SCL</a> , <a href="#">IRQ</a> , <a href="#">KEEP_ALIVE</a> | 5.5 V          |

| Voltage on <a href="#">VINT</a> , <a href="#">DIS_STO_CH</a> , <a href="#">STO_CFG[2:0]</a> , <a href="#">SRC_LVL_CFG[5:0]</a> , <a href="#">TH_REF</a> , <a href="#">TH_MON</a>                          | 2.75 V         |

| Operating junction temperature                                                                                                                                                                            | -40°C to 125°C |

| ESD HBM voltage                                                                                                                                                                                           | TBD            |

| ESD CDM voltage                                                                                                                                                                                           | TBD            |

Table 2: Absolute maximum ratings

#### ESD CAUTION

ESD (ELECTROSTATIC DISCHARGE) SENSITIVE DEVICE

These devices have limited built-in ESD protection and damage may thus occur on devices subjected to high-energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality

### 5. Material

#### 5.1. RoHS Compliance

e-peas product complies with RoHS requirement.

e-peas defines “RoHS” to mean that semiconductor end-products are compliant with RoHS regulation for all 10 RoHS substances.

This applies to silicon, die attached adhesive, gold wire bonding, lead frames, mold compound, and lead finish (pure tin).

#### 4. Thermal Resistance

| Package | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|---------|---------------|---------------|------|

| QFN28   | TBD           | TBD           | °C/W |

Table 3: Thermal data

#### 5.2. REACH Compliance

The component and elements used by e-peas subcontractors to manufacture e-peas PMICs and devices are REACH compliant. For more detailed information, please contact e-peas sales team.

## 6. Typical Electrical Characteristics at 25 °C

| Symbol                                         | Parameter                                                                                                                                                                                       | Conditions                                                                                             | Min              | Typ  | Max | Unit |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------|------|-----|------|

| <b>Power Conversion</b>                        |                                                                                                                                                                                                 |                                                                                                        |                  |      |     |      |

| $P_{SRC,CS}$                                   | Minimum source power required for cold start <sup>1</sup>                                                                                                                                       | During cold start<br>$KEEP\_ALIVE = V_{INT}$                                                           |                  | 5    |     | μW   |

|                                                |                                                                                                                                                                                                 | During cold start<br>$KEEP\_ALIVE = GND$                                                               |                  | 14   |     | μW   |

| $V_{SRC,CS}$                                   | Minimum source voltage required for cold start <sup>1</sup>                                                                                                                                     |                                                                                                        | 0.25             |      |     | V    |

| $V_{SRC,REG}$                                  | Target regulation voltage of the source (depending on $SRC\_LVL\_CFG[5:0]$ configuration or I <sup>2</sup> C register)                                                                          | 0.12                                                                                                   |                  | 1.47 |     | V    |

| $V_{OC}$                                       | Open-circuit voltage of the source                                                                                                                                                              |                                                                                                        |                  | 2.0  |     | V    |

| <b>Storage Element</b>                         |                                                                                                                                                                                                 |                                                                                                        |                  |      |     |      |

| $V_{STO}$                                      | Voltage on the storage element                                                                                                                                                                  | 2.5                                                                                                    |                  | 4.8  |     | V    |

| $V_{OVCH}$                                     | Maximum voltage accepted on the storage element before disabling its charging                                                                                                                   | 3                                                                                                      | See section 10.3 | 4.8  |     | V    |

| $V_{OVDIS}$                                    | Minimum voltage accepted on the storage element before stopping to supply $V_{INT}$ if Keep-alive is enabled.                                                                                   | 2.8                                                                                                    |                  | 4.05 |     | V    |

| <b>Internal supply &amp; Quiescent Current</b> |                                                                                                                                                                                                 |                                                                                                        |                  |      |     |      |

| $V_{INT}$                                      | Internal supply voltage                                                                                                                                                                         |                                                                                                        | 2.2              |      |     | V    |

| $I_{QSUPPLY}$                                  | Quiescent current on $V_{INT}$ in <b>SUPPLY STATE</b>                                                                                                                                           | $V_{STO} = 3.7$ V                                                                                      | 300              |      |     | nA   |

| $I_{QSLEEP}$                                   | Quiescent current on $V_{INT}$ in <b>SLEEP STATE</b>                                                                                                                                            | $V_{STO} = 3.7$ V                                                                                      | 150              |      |     | nA   |

| $I_{QSTO}$                                     | Quiescent current on <b>STO</b> when Keep-alive functionality is disabled                                                                                                                       |                                                                                                        | 1                |      |     | nA   |

| $T_{RESET,SLEEP}$                              | Delay before $V_{INT}$ crossing reset voltage when no energy on <b>SRC</b> and Keep-alive functionality disabled, or if Keep-alive is enabled but the battery voltage dropped below $V_{OVDIS}$ | $C_{INT} = 3.3$ μF (leakage neglected), AEM in <b>SLEEP STATE</b> , no I <sup>2</sup> C communication  | 2.2              |      |     | s    |

| $T_{RESET,SUPPLY}$                             |                                                                                                                                                                                                 | $C_{INT} = 3.3$ μF (leakage neglected), AEM in <b>SUPPLY STATE</b> , no I <sup>2</sup> C communication | 1.1              |      |     | s    |

| <b>I<sup>2</sup>C interface</b>                |                                                                                                                                                                                                 |                                                                                                        |                  |      |     |      |

| Bus frequency                                  |                                                                                                                                                                                                 |                                                                                                        | 400              | 1000 |     | kHz  |

| $I_{2C\_VDD}$                                  | I <sup>2</sup> C interface supply pin                                                                                                                                                           | 1.5                                                                                                    |                  | 5.0  |     | V    |

| $SCL$                                          | I <sup>2</sup> C interface communication pins                                                                                                                                                   | Pull-up to $I_{2C\_VDD}$ with resistors                                                                |                  |      |     |      |

| $SDA$                                          |                                                                                                                                                                                                 |                                                                                                        |                  |      |     |      |

Table 4: Electrical characteristics

1. These values are valid with the recommended BOM components (see Section 15)

## 7. Recommended Operation Conditions

| Symbol                     | Parameter                                                           | Min        | Typ                  | Max  | Unit          |

|----------------------------|---------------------------------------------------------------------|------------|----------------------|------|---------------|

| <b>External Components</b> |                                                                     |            |                      |      |               |

| $L_{DCDC}$                 | Inductor of the boost converter                                     | AEM00900   | 3.3                  | 6.8  | $\mu\text{H}$ |

|                            |                                                                     | AEM00901   |                      | 33   |               |

| $C_{SRC}$                  | Capacitor decoupling the $\text{BUFSRC}$ terminal                   | 10         |                      |      | $\mu\text{F}$ |

| $C_{INT}$                  | Capacitor decoupling $V_{INT}$                                      | 3.3        |                      |      | $\mu\text{F}$ |

| $C_{STO}$                  | Capacitor decoupling the $STO$ terminal <sup>1</sup>                | 5          | 22                   |      | $\mu\text{F}$ |

| $R_{DIV}$                  | Optional - pull-up resistor for the thermal monitoring              | 5k         | 22k                  | 33k  | $\Omega$      |

| $R_{TH}$                   | Optional - NTC thermistor for the thermal monitoring                | $R_0$      |                      | 10k  | $\Omega$      |

|                            |                                                                     | Beta       |                      | 3380 | K             |

| $R_{SCL}$                  | Optional - pull-up resistors for the $\text{I}^2\text{C}$ interface |            |                      | 1k   |               |

| $R_{SDA}$                  |                                                                     |            |                      |      | $\Omega$      |

| <b>Logic input Pins</b>    |                                                                     |            |                      |      |               |

| $SRC\_LVL\_CFG[5:0]$       | Configuration pins for the $SRC$ voltage level                      | Logic HIGH | Connect to $V_{INT}$ |      |               |

|                            |                                                                     | Logic LOW  | Connect to GND       |      |               |

| $STO\_CFG[2:0]$            | Configuration pins for the storage element thresholds               | Logic HIGH | Connect to $V_{INT}$ |      |               |

|                            |                                                                     | Logic LOW  | Connect to GND       |      |               |

| $KEEP\_ALIVE$              | Configuration for the “Keep alive” functionality                    | Logic HIGH | Connect to $V_{INT}$ |      |               |

|                            |                                                                     | Logic LOW  | Connect to GND       |      |               |

| $DIS\_STO\_CH$             | Configuration for disabling the charging of the battery             | Logic HIGH | Connect to $STO$     |      |               |

|                            |                                                                     | Logic LOW  | Connect to GND       |      |               |

Table 5: Recommended operating conditions

1. Decoupling capacitor of at least  $5\mu\text{F}$  is required to avoid damaging the AEM. The decoupling capacitor is to be sized according to the storage element internal resistance (ESR) to ensure optimal efficiency of the DCDC converter. It is recommended to use a capacitor of at least  $22\mu\text{F}$  when measuring the AEM0090x efficiency with laboratory equipment such as source measurement units (SMU). A battery must be connected to  $STO$  when a harvester is connected to the AEM to avoid damaging it.

## 8. Functional Block Diagram

Figure 3: Functional block diagram

Figure 4: Simplified schematic view of the AEM0090x

## 9. Theory of Operation

### 9.1. Boost Converter

The boost (step-up) converter raises the voltage available at **BUFSRC** to a level suitable for charging the storage element, in the range of 2.8 V to 4.8 V, according to the system configuration. The switching transistors of the boost converter are M2, M3 and M4. The reactive power component of this converter is the external inductor **L<sub>DCDC</sub>**.

When the boost converter is extracting energy from **SRC**, M1 is closed. **BUFSRC** is decoupled by the capacitor **C<sub>SRC</sub>**, which smoothes the voltage against the current pulses induced by the boost converter.

The storage element is connected to the **STO** pin, which voltage is **V<sub>STO</sub>**. This node is linked to the output of the boost converter through transistor M4. When energy harvesting is occurring, the boost converter charges the battery. M4 disconnects the storage element when **V<sub>STO</sub>** reaches **V<sub>OVCH</sub>**. If **V<sub>INT</sub>** drops below its regulation value and if Keep-alive functionality is disabled, the AEM switches its output by enabling M3 instead of M4 until **V<sub>INT</sub>** reaches its target plus a small hysteresis. If the Keep-alive functionality is enabled, **V<sub>INT</sub>** is instead supplied from **STO** by modulating the gate of M5. In this case M3 is never activated.

### 9.2. Source Voltage Regulation

During **SUPPLY STATE**, the voltage on **SRC** is regulated to a voltage configured by the user. The AEM0090x offers a choice of one hundred and three values for the source voltage. If the open-circuit voltage of the harvester is lower than **V<sub>SRC,REG</sub>**, the AEM0090x does not extract the power from the source. If the **SRC** voltage is higher, the AEM0090x regulates **V<sub>SRC</sub>** to **V<sub>SRC,REG</sub>** and extracts power.

### 9.3. Thermal Monitoring

Thermal monitoring allows to protect the storage element by disabling the charge of the storage element and setting the **STATUS.TEMP** register when the temperature is outside of the defined temperature range. Enabling this functionality requires the use of a resistor (**R<sub>DIV</sub>**) and a thermistor (**R<sub>TH</sub>**). See Figure 5 for external components connections. The **TH<sub>REF</sub>** terminal allows a reference voltage to be applied to the resistive divider while **TH<sub>MON</sub>** is the measuring point. An ADC is measuring the voltage on **TH<sub>MON</sub>** between 0 and 1 V. The temperature evaluation is done periodically (typ. every 8 s) to spare power. Information for the thermal monitoring is described in section 10.7.4. Thermal monitoring is optional, if not used connect **TH<sub>MON</sub>** to **V<sub>INT</sub>** and leave **TH<sub>REF</sub>** floating.

## 9.4. Average Power Monitoring

The Average Power Monitoring (APM) allows to evaluate the energy transfer from **SRC** to **STO**. The APM is able to determine the transferred energy by counting the number of current pulses transferred to **STO** by the boost converter over a configurable time window, and thus, evaluate the corresponding energy.

Two modes are available: Pulse Counter Mode and Power Meter Mode.

The APM behavior is described in Figure 6:

- **Phase A:**

- **Pulse Counter Mode:** APM counts the number of DCDC pulses happening during  $T_A$

- **Power Meter Mode:** APM integrates the energy transferred from **SRC** to **STO** during  $T_A$

- **Phase B:** APM waits during  $T_B = T_A$

- **IRQ:** a rising edge is triggered on the **IRQ** pin, if **IRQEN.APMDONE** field is set to 1 (see Section 10.7.9 and Section 10.7.11). A rising edge on **IRQ** along with the **IRQFLAG.APMDONE** field set to 1 indicates to the user that a new value is available and ready to be read in the APM Data Register (Section 10.7.13).

Refer to Sections 10.7.8. and 10.7.13 for further details about how to set modes, how to convert registers value to Joule and how to set  $T_A$ .

Figure 6: Average Power Monitoring description

## 9.5. Automatic High Power Mode (AEM00900 only)

When the AEM detects that the energy available on **SRC** is high enough, the boost converter automatically switches to high-power mode, increasing the harvesting current capability at the price of a slight efficiency degradation.

Preventing the AEM to switch to high-power mode may allow to use an inductor with half peak current rating for  $L_{DCDC}$  (see Section 10.8.2). On the other hand, allowing the AEM to switch to high-power mode increases the maximum current that the AEM can harvest from **SRC** to **STO**.

Automatic high-power mode is enabled by default and can be disabled by setting the **PWR.HPEN** to 0 through the **I<sup>2</sup>C** interface.

*NOTE: this feature is not available on the AEM010901, that is always in high power mode.*

## 9.6. Keep-alive

The internal circuitry connected to **VINT** can be supplied either by **SRC** through the boost converter (keep-alive disabled), or by the battery **STO** (keep-alive enabled).

When the keep-alive feature is disabled, the AEM0090x is supplied from **SRC**. The AEM will switch to **RESET STATE** if the energy on **SRC** is not sufficient.

When the keep-alive feature is enabled, the AEM0090x is supplied from **STO**. **VINT** is regulated as long as enough energy is available from the storage element connected on **STO**. The keep-alive feature allows to maintain the **I<sup>2</sup>C** registers configuration. Referring to Table 4, the quiescent current is then  $I_{QSUPPLY}$  or  $I_{QSLEEP}$ , depending on whether the AEM0090x is in **SUPPLY STATE** or in **SLEEP STATE**.

## 9.7. IRQ Pin

The **IRQ** pin allows user to get notified when various events happen (rising edge on **IRQ** pin). At startup, the only flag that is enabled is **I2CRDY**, allowing user to know when the AEM0090x has finished to coldstart and thus, is out of **RESET STATE** and is ready to be programmed through **I<sup>2</sup>C**. Other flags can be enabled by writing the **IRQEN** register (Section 10.7.9). When the **IRQ** pin shows a rising edge, the flags can be determined by reading the **IRQFLG** register (Section 10.7.11). Reading the registers will reset the **IRQ** pin.

## 9.8. State Description

### 9.8.1. Reset State

In **RESET STATE** all nodes are deeply discharged and there is no available energy to be harvested. The AEM stays in this state until the source connected to **SRC** meets the cold start requirements long enough to make **VINT** rise up to 2.2 V. Cold start requirements depend on whether the Keep-alive feature is enabled or not:

- **KEEP\_ALIVE** = 1:

- $V_{SRC} \geq 250 \text{ mV}$

- $P_{SRC,CS} \geq 5 \mu\text{W}$

- **KEEP\_ALIVE** = 0:

- $V_{SRC} \geq 250 \text{ mV}$

- $P_{SRC,CS} \geq 14 \mu\text{W}$

When **VINT** has reached 2.2 V, the AEM0090x reads the configuration pins and switches to **SENSE STO STATE**.

Figure 7: Diagram of the AEM0090x state machine

### 9.8.2. Sense STO State

In **SENSE STO STATE** the AEM0090x does the following measurements in order to know if the charging condition of the battery are met :

- Battery voltage on **STO**;

- Temperature through pins **TH\_MON** and **TH\_REF** (see Section 9.3. and 10.7.4.).

In this state, Once the measurements are done, AEM0090x switches to **SUPPLY STATE**.

### 9.8.3. Supply State

In **SUPPLY STATE**, the AEM transfers charges directly from to **STO** while maintaining **V<sub>INT</sub>**.

If **V<sub>INT</sub>** drops and the energy available on **SRC** is not sufficient to make **V<sub>INT</sub>** rise again, there are two possible behaviors, depending on the 'Keep Alive' feature:

- If keep-alive is enabled, **V<sub>INT</sub>** is supplied by the battery through M5, so the AEM0090x stays in **SUPPLY STATE** while energy is available on the battery;

- If keep-alive is disabled, **V<sub>INT</sub>** will no longer be maintained and the AEM switches to **RESET STATE**.

### 9.8.4. Sleep State

Please note that the first condition for the AEM0090x to enter **SLEEP STATE** is to set the **SLEEP.EN** field in the **SLEEP** register 1, as shown on Figure 7.

In **SLEEP STATE**, the AEM power consumption is reduced. This mode may be used when the power available on the input is presumably low.

The AEM0090x enters sleep mode when the following conditions are met:

- Field **SLEEP.EN** in the **SLEEP** register is set to 1.

- **SRCREGU** register value is set to 0x0C (I<sup>2</sup>C).

## 10. System Configuration

### 10.1. Configuration Pins and I<sup>2</sup>C

#### 10.1.1. Configuration Pins

After a cold start, the AEM0090x reads the configuration GPIOs. Those are then read periodically every 2 s, with the exception of the **DIS\_STO\_CH** pin that is read every 1 s. The configuration pins can be changed on-the-fly and the corresponding configuration will be updated at the next IO reading. The floating configuration pins are read as HIGH, except **DIS\_STO\_CH** which is read as LOW.

#### 10.1.2. Configuration by I<sup>2</sup>C

To configure the AEM0090x through the I<sup>2</sup>C interface after a cold start, the user must wait for the **IRQ** pin to rise, showing that the AEM0090x is out of **RESET STATE** and is ready to communicate with I<sup>2</sup>C. The interrupt is reseted by reading its register. Please note that the **IRQ** pin is always low during **RESET STATE**. See Section 10.7.11 for further informations about the **IRQ** pin.

Once **IRQ** goes HIGH, the user can then write to the desired registers and validate the configuration by setting the **CTRL.UPDATE** register field. All configuration pins are then ignored and all the configurations are set by the register values. All registers have a default value, that can be found in Table 8. It is possible to go back to the GPIO configuration by resetting the **CTRL.UPDATE** bit. To apply any modification to the configuration, simply change the wanted registers value and set the **CTRL.UPDATE** bit again.

Registers are stored in a volatile memory, so their value are lost when **V<sub>INT</sub>** drops below the reset voltage (2 V), making the AEM0090x switch to **RESET STATE**. Thus, when using the I<sup>2</sup>C configuration, it is highly recommended to enable the keep-alive (see section 10.7.5.). If keep-alive functionality is disabled, register configuration is lost every time the energy available **SRC** is not sufficient to maintain **V<sub>INT</sub>** above the reset voltage (2 V).

## 10.2. Source Level Configuration

| Configuration pins |   |   |   |   |   | Voltage Level |

|--------------------|---|---|---|---|---|---------------|

| SRC_LVL_CFG[5:0]   |   |   |   |   |   | $V_{SRC,REG}$ |

| L                  | L | L | H | H | L | 0.12 V        |

| L                  | L | L | H | H | H | 0.13 V        |

| L                  | L | H | L | L | L | 0.15 V        |

| L                  | L | H | L | L | H | 0.16 V        |

| L                  | L | H | L | H | L | 0.18 V        |

| L                  | L | H | L | H | H | 0.19 V        |

| L                  | L | H | H | L | L | 0.21 V        |

| L                  | L | H | H | L | H | 0.22 V        |

| L                  | L | H | H | H | L | 0.24 V        |

| L                  | L | H | H | H | H | 0.25 V        |

| L                  | H | L | L | L | L | 0.27 V        |

| L                  | H | L | L | L | H | 0.28 V        |

| L                  | H | L | L | H | L | 0.30 V        |

| L                  | H | L | L | H | H | 0.33 V        |

| L                  | H | L | H | L | L | 0.36 V        |

| L                  | H | L | H | L | H | 0.39 V        |

| L                  | H | L | H | H | L | 0.42 V        |

| L                  | H | L | H | H | H | 0.45 V        |

| L                  | H | H | L | L | L | 0.48 V        |

| L                  | H | H | L | L | H | 0.51 V        |

| L                  | H | H | L | H | L | 0.54 V        |

| L                  | H | H | L | H | H | 0.57 V        |

| L                  | H | H | H | L | L | 0.60 V        |

| L                  | H | H | H | L | H | 0.63 V        |

| L                  | H | H | H | H | L | 0.66 V        |

| L                  | H | H | H | H | H | 0.69 V        |

| Configuration pins |   |   |   |   |   | Voltage Level |

|--------------------|---|---|---|---|---|---------------|

| SRC_LVL_CFG[5:0]   |   |   |   |   |   | $V_{SRC,REG}$ |

| H                  | L | L | L | L | L | 0.72 V        |

| H                  | L | L | L | L | H | 0.75 V        |

| H                  | L | L | L | H | L | 0.78 V        |

| H                  | L | L | L | H | H | 0.81 V        |

| H                  | L | L | H | L | L | 0.84 V        |

| H                  | L | L | H | L | H | 0.87 V        |

| H                  | L | L | H | H | L | 0.90 V        |

| H                  | L | L | H | H | H | 0.93 V        |

| H                  | L | H | L | L | L | 0.96 V        |

| H                  | L | H | L | L | H | 0.99 V        |

| H                  | L | H | L | H | L | 1.02 V        |

| H                  | L | H | L | H | H | 1.05 V        |

| H                  | L | H | H | L | L | 1.08 V        |

| H                  | L | H | H | L | H | 1.11 V        |

| H                  | L | H | H | H | L | 1.14 V        |

| H                  | L | H | H | H | H | 1.17 V        |

| H                  | H | L | L | L | L | 1.20 V        |

| H                  | H | L | L | L | H | 1.23 V        |

| H                  | H | L | L | H | L | 1.26 V        |

| H                  | H | L | L | H | H | 1.29 V        |

| H                  | H | L | H | L | L | 1.32 V        |

| H                  | H | L | H | L | H | 1.35 V        |

| H                  | H | L | H | H | L | 1.38 V        |

| H                  | H | H | L | H | H | 1.41 V        |

| H                  | H | H | L | L | L | 1.44 V        |

| H                  | H | H | L | L | H | 1.47 V        |

Table 6: Configuration of SRC\_LVL\_CFG[5:0]

The source voltage regulation can be configured using GPIO or I<sup>2</sup>C communication.

Six dedicated configuration pins, SRC\_LVL\_CFG[5:0], allow selecting the  $V_{SRC,REG}$  at which the source regulates its voltage. All configurations set below SRC\_LVL\_CFG[LLLHHL] will be set at 0.12 V.

The I<sup>2</sup>C communication allows more precision than the GPIO configuration (see Section 10.7.2), as SRCREGU.VALUE (0x01) is a 7-bit register.

## 10.3. Storage Element Thresholds Configuration

The user must set the voltage thresholds for which the storage element is considered to be discharged ( $V_{OVDIS}$ ) and fully charged ( $V_{OVCH}$ ).

$V_{OVDIS}$  is configured on the VOVDIS (0x02) register and encoded on 6 bits. The value to be written to the register is determined using the following equation:

$$\text{THRESH} = \frac{V_{OVDIS} - 0.50625}{0.05625}$$

THRESH is the integer value to be written in the register. The minimum value is 2.8 V. If the register value corresponds to  $V_{OVDIS} < 2.8$  V, the threshold voltage is forced to 2.8 V.

$V_{OVCH}$  is configured on the VOVCH (0x03) register and encoded on 6 bits. The value to be written to the register is determined using the following equation:

$$THRESH = \frac{V_{OVCH} - 1.2375}{0.05625}$$

THRESH is the integer value to be written in the register. The minimum value is 3.0 V. If the register value corresponds to  $V_{OVCH} < 3.0$  V, the threshold voltage is forced to 3.0 V.

It is also possible to configure  $V_{OVDIS}$  and  $V_{OVCH}$  with configuration pins **STO\_CFG[2:0]** as shown in table 7.

| Configuration       | Storage element threshold | Battery type                          |

|---------------------|---------------------------|---------------------------------------|

| <b>STO_CFG[2:0]</b> | $V_{OVCH}$                | $V_{OVDIS}$                           |

| LLL                 | 4.50 V                    | 3.30 V<br>NiCd 3 cells                |

| LLH                 | 4.00 V                    | 2.80 V<br>Tadrian TLI1020A            |

| LHL                 | 3.63 V                    | 2.80 V<br>LiFePO4                     |

| LHH                 | 3.90 V                    | 2.80 V<br>Tadrian HLC1020             |

| HLL                 | 3.90 V                    | 3.50 V<br>Li-ion (ultra long life)    |

| HLH                 | 3.90 V                    | 3.01 V<br>Li-ion (long life)          |

| HHL                 | 4.35 V                    | 3.01 V<br>LiPo                        |

| HHH                 | 4.12 V                    | 3.01 V<br>Li-ion/solid-state/<br>NiMH |

Table 7: Usage of **STO\_CFG[2:0]**

**DISCLAIMER:** the provided storage element thresholds in the table above are indicative to support a wide range of storage element variants. They are provided as is to the best knowledge of e-peas's application laboratory. They should not replace the actual values provided in the storage element manufacturer's specifications and datasheet.

## 10.4. Disable Storage Element Charging

Pulling up **DIS\_STO\_CH** to **STO** disables the charging of the storage element connected to **STO**.

Please note that, if the keep-alive feature is enabled by pulling up **KEEP\_ALIVE** to **VINT**, **VINT** is supplied by **STO** regardless of the setting of **DIS\_STO\_CH**. To make sure that the storage element is neither charged nor used to supply **VINT**, user must both tie **DIS\_STO\_CH** to **STO** and tie **KEEP\_ALIVE** to **GND**.

## 10.5. I<sup>2</sup>C Serial Interface Protocol

The AEM0090x uses I<sup>2</sup>C communication for configuration as well as to provide information about system status and measurement data. Communication requires a serial data line (**SDA**) and a serial clock line (**SCL**). A device sending data is defined as a transmitter and a device receiving data as a receiver. The device that controls the communication is called a master and the device it controls is defined as the slave.

Figure 8: I<sup>2</sup>C transmission frame

The master is in charge of generating the clock, managing bus accesses and generating the start and stop bits. The AEM0090x is a slave that will receive configuration data or send the informations requested by the master.

The AEM0090x supports I<sup>2</sup>C Standard-mode (100 kHz maximum clock rate), Fast-mode (400 kHz maximum clock rate), and Fast-mode Plus (1 MHz maximum clock rate) device. Data are sent with the most significant bit first.

Here are some typical I<sup>2</sup>C interface states:

- When the communication is idle, both transmission lines are pulled-up (**SDA** and **SCL** are open drain outputs);

- Start bit (S): to initiates the transmission, the master switches the **SDA** line low while keeping **SCL** high. This is called the start bit;

- Stop bit (P): to end the transmission, the master switches the **SDA** line from low to high while keeping **SCL** high. This is called a stop bit;

- Repeated Start bit (Sr): it is used as a back-to-back start and stop bit. It is similar to a start condition, but when the bus is not on idle;

- ACK: to acknowledge a transmission, the device receiving the data (master in case of a read mode transmission, slave in case of a write mode transmission) switches **SDA** low;

- NACK: when the device receiving data keeps **SDA** high after the transmission of a byte. When reading a byte, this can mean that the master is done reading bytes from the slave.

To initiate the communication, the master sends a byte with the following informations:

- Bits [7:1] is the slave address, which is 0x40 or 0x41 for the AEM0090x, depending on the value of the **I2C\_ADDR** pin. For packages where the **I2C\_ADDR** pin is not present, the address is 0x41;

- Bit [0] is the communication mode: 1 for 'read mode' (used when the master reads informations from the slave) and 0 for 'write mode' (when the master writes informations to the slave);

- Slave replies with an ACK to acknowledge that the address has been successfully transmitted.

Here is the procedure for the master to write a slave register:

- Master sends the address of the slave in 'write' mode;

- Slave sends an ACK;

- Master sends the address of the register to be written. For example, for the **TEMPCOLD** register, the master sends the value 0x04;

- Slave sends an ACK;

- Master sends the data to write to the register;

- Slave sends an ACK;

- If the master wants to write register at the next address (**TEMPPHOT** in our example), it sends next value to write, without having to specify the address again. This can be done several times in a row for writing several consecutive registers;

- Else the master sends a stop bit (P).

Here is the procedure for the master to read a slave register:

- Master sends the address of the slave in 'write' mode;

- Slave sends an ACK;

- Master sends the address of the register to be read. For example, for the **SRC\_REGU** register, the master sends the value 0x18;

- Slave sends an ACK;

- Master sends a repeated start bit (Sr);

- Master sends the address of the slave in 'read' mode;

- Slave sends an ACK;

- Master provides the clock on **SCL** to allow the slave to shift the data of the read register on **SDA**;

- If the master wants to read register at the next address (**STATUS.VOVDIS** in our example), it sends an ACK and provides the clock for the slave to shift its following 8 bits of data. This can be done several times in a row for writing several registers;

- If the master wants to end the transmission, it sends a NACK to notify the slave that the transmission is over, and then sends a stop bit (P). Both communications are described in the figure 9. Refer to Table 8 for all register addresses.

*Figure 9: Read and write transmission*

## 10.6. Registers Map

| Address | Name     | Bit   | Field Name | Access | RESET        | Description                                            |

|---------|----------|-------|------------|--------|--------------|--------------------------------------------------------|

| 0x00    | VERSION  | [3:0] | MINOR      | R      | -            | Chip ID                                                |

|         |          | [7:4] | MAJOR      | R      | -            |                                                        |

| 0x01    | SRCREGU  | [7:0] | VALUE      | R/W    | 0x77 (1.47V) | Source voltage regulation                              |

| 0x02    | VOVDIS   | [5:0] | THRESH     | R/W    | 0x2D (3.05V) | Overdischarge level of the storage element             |

| 0x03    | VOVCH    | [5:0] | THRESH     | R/W    | 0x33 (4.1V)  | Overcharge level of the storage element                |

| 0x04    | TEMPCOLD | [7:0] | THRESH     | R/W    | 0x8F (0°C)   | Cold temperature level                                 |

| 0x05    | TEMPHOT  | [7:0] | THRESH     | R/W    | 0x2F (45°C)  | Hot temperature level                                  |

| 0x06    | PWR      | [0:0] | KEEPALEN   | R/W    | 0x01         | Keepalive enable                                       |

|         |          | [1:1] | HPEN       | R/W    | 0x01         | AEM00900: High power mode enable<br>AEM00901: Reserved |

|         |          | [2:2] | TMONEN     | R/W    | 0x01         | Temperature monitoring enable                          |

|         |          | [3:3] | STOCHDIS   | R/W    | 0x00         | Battery charging disable                               |

| 0x07    | SLEEP    | [0:0] | EN         | R/W    | 0x01         | Sleep mode enable                                      |

|         |          | [3:1] | SRCTHRESH  | R/W    | 0x00         | SRC LOW threshold                                      |

| 0x08    | STOMON   | [2:0] | RATE       | R/W    | 0x00         | ADC rate                                               |

| 0x09    | APM      | [0:0] | EN         | R/W    | 0x00         | APM enable                                             |

|         |          | [1:1] | MODE       | R/W    | 0x00         | APM mode                                               |

|         |          | [3:2] | WINDOW     | R/W    | 0x00         | APM computation window                                 |

| 0x0A    | IRQEN    | [0:0] | I2CRDY     | R/W    | 0x01         | IRQ serial interface ready enable                      |

|         |          | [1:1] | VOVDIS     | R/W    | 0x00         | IRQ STO OVDIS enable                                   |

|         |          | [2:2] | VOVCH      | R/W    | 0x00         | IRQ STO OVCH enable                                    |

|         |          | [3:3] | SRCTHRESH  | R/W    | 0x00         | IRQ SRC LOW enable                                     |

|         |          | [4:4] | TEMP       | R/W    | 0x00         | IRQ temperature enable                                 |

|         |          | [5:5] | APMDONE    | R/W    | 0x00         | IRQ APM done enable                                    |

| 0x0B    | CTRL     | [0:0] | UPDATE     | R/W    | 0x00         | Load I <sup>2</sup> C registers configuration          |

|         |          | [2:2] | SYNCBUSY   | R      | 0x00         | Synchronization busy flag                              |

| 0x0C    | IRQFLG   | [0:0] | I2CRDY     | R      | 0x00         | IRQ serial interface ready flag                        |

|         |          | [1:1] | VOVDIS     | R      | 0x00         | IRQ STOR OVDIS flag                                    |

|         |          | [2:2] | VOVCH      | R      | 0x00         | IRQ STOR OVCH flag                                     |

|         |          | [3:3] | SRCTHRESH  | R      | 0x00         | IRQ SRC LOW flag                                       |

|         |          | [4:4] | TEMP       | R      | 0x00         | IRQ temperature flag                                   |

|         |          | [5:5] | APMDONE    | R      | 0x00         | IRQ APM done flag                                      |

| 0x0D    | STATUS   | [1:1] | VOVDIS     | R      | 0x00         | Status STO OVDIS                                       |

|         |          | [2:2] | VOVCH      | R      | 0x00         | Status STO OVCH                                        |

|         |          | [3:3] | SRCTHRESH  | R      | 0x00         | Status SRC LOW                                         |

|         |          | [4:4] | TEMP       | R      | 0x00         | Status temperature                                     |

|         |          | [6:6] | CHARGE     | R      | 0x00         | Status STO CH                                          |

|         |          | [7:7] | BSTDIS     | R      | 0x00         | Status BST DIS GPIO                                    |

| 0x0E    | APMO     | [7:0] | DATA       | R      | 0x00         | APM data 0                                             |

Table 8: Register summary

| Address | Name | Bit   | Field Name | Access | RESET | Description        |

|---------|------|-------|------------|--------|-------|--------------------|

| 0x0F    | APM1 | [7:0] | DATA       | R      | 0x00  | APM data 1         |

| 0x10    | APM2 | [7:0] | DATA       | R      | 0x00  | APM data 2         |

| 0x11    | TEMP | [7:0] | DATA       | R      | 0x00  | Temperature data   |

| 0x12    | STO  | [7:0] | DATA       | R      | 0x00  | Battery voltage    |

| 0x13    | RSVD | [7:0] | -          | R      | -     | Reserved           |

| 0xE0    | PNO  | [7:0] | DATA       | R      | 0X30  | Part number 0 data |

| 0xE1    | PN1  | [7:0] | DATA       | R      | 0X30  | Part number 1 data |

| 0xE2    | PN2  | [7:0] | DATA       | R      | 0X39  | Part number 2 data |

| 0xE3    | PN3  | [7:0] | DATA       | R      | 0X30  | Part number 3 data |

| 0xE4    | PN4  | [7:0] | DATA       | R      | 0X31  | Part number 4 data |

Table 8: Register summary

## 10.7. Registers Configurations

### 10.7.1. Version Register (VERSION)

The VERSION register holds the version of the chip, with major and minor revision numbers.

| VERSION Register |  | 0x00      | R |

|------------------|--|-----------|---|

| Bit [7:4]        |  | Bit [3:0] |   |

| MAJOR            |  | MINOR     |   |

| 0x00             |  | 0x00      |   |

Table 9: VERSION register

Bit [7:4]: major revision number (VERSION.MAJOR).

Bit [3:0]: minor revision number (VERSION.MINOR).

### 10.7.2. Source Voltage Regulation Register (SRCREGU)

The source voltage regulation can be set thanks to the I<sup>2</sup>C communication with more precision. The register is made of 7 bits. Use the table 10 to set the SRCREGU.VALUE register according the desired  $V_{SRC,REG}$ .

| SRC<br>.DATA<br>[7:0] | V <sub>SRC,REG</sub><br>[V] |

|-----------------------|-----------------------------|-----------------------|-----------------------------|-----------------------|-----------------------------|-----------------------|-----------------------------|

| 0x00                  | 0.1125                      | 0x25                  | 0.3                         | 0x40                  | 0.705                       | 0x5B                  | 1.11                        |

| ...                   | 0.1125                      | 0x26                  | 0.315                       | 0x41                  | 0.72                        | 0x5C                  | 1.125                       |

| 0x0C                  | 0.1125                      | 0x27                  | 0.33                        | 0x42                  | 0.735                       | 0x5D                  | 1.14                        |

| 0x0D                  | 0.12                        | 0x28                  | 0.345                       | 0x43                  | 0.75                        | 0x5E                  | 1.155                       |

| 0x0E                  | 0.1275                      | 0x29                  | 0.36                        | 0x44                  | 0.765                       | 0x5F                  | 1.17                        |

| 0x0F                  | 0.135                       | 0x2A                  | 0.375                       | 0x45                  | 0.78                        | 0x60                  | 1.185                       |

| 0x10                  | 0.1425                      | 0x2B                  | 0.39                        | 0x46                  | 0.795                       | 0x61                  | 1.2                         |

| 0x11                  | 0.15                        | 0x2C                  | 0.405                       | 0x47                  | 0.81                        | 0x62                  | 1.215                       |

| 0x12                  | 0.1575                      | 0x2D                  | 0.42                        | 0x48                  | 0.825                       | 0x63                  | 1.23                        |

| 0x13                  | 0.165                       | 0x2E                  | 0.435                       | 0x49                  | 0.84                        | 0x64                  | 1.245                       |

| 0x14                  | 0.1725                      | 0x2F                  | 0.45                        | 0x4A                  | 0.855                       | 0x65                  | 1.26                        |

| 0x15                  | 0.18                        | 0x30                  | 0.465                       | 0x4B                  | 0.87                        | 0x66                  | 1.275                       |

| 0x16                  | 0.1875                      | 0x31                  | 0.48                        | 0x4C                  | 0.885                       | 0x67                  | 1.29                        |

| 0x17                  | 0.195                       | 0x32                  | 0.495                       | 0x4D                  | 0.9                         | 0x68                  | 1.305                       |

| 0x18                  | 0.2025                      | 0x33                  | 0.51                        | 0x4E                  | 0.915                       | 0x69                  | 1.32                        |

| 0x19                  | 0.21                        | 0x34                  | 0.525                       | 0x4F                  | 0.93                        | 0x6A                  | 1.335                       |

| 0x1A                  | 0.2175                      | 0x35                  | 0.54                        | 0x50                  | 0.945                       | 0x6B                  | 1.35                        |

| 0x1B                  | 0.225                       | 0x36                  | 0.555                       | 0x51                  | 0.96                        | 0x6C                  | 1.365                       |

| 0x1C                  | 0.2325                      | 0x37                  | 0.57                        | 0x52                  | 0.975                       | 0x6D                  | 1.38                        |

| 0x1D                  | 0.24                        | 0x38                  | 0.585                       | 0x53                  | 0.99                        | 0x6E                  | 1.395                       |

| 0x1E                  | 0.2475                      | 0x39                  | 0.6                         | 0x54                  | 1.005                       | 0x6F                  | 1.41                        |

| 0x1F                  | 0.255                       | 0x3A                  | 0.615                       | 0x55                  | 1.02                        | 0x70                  | 1.425                       |