## Building Hardware State Machines Using CIPs

### Introduction

Author: Keith Curtis, Microchip Technology Inc.

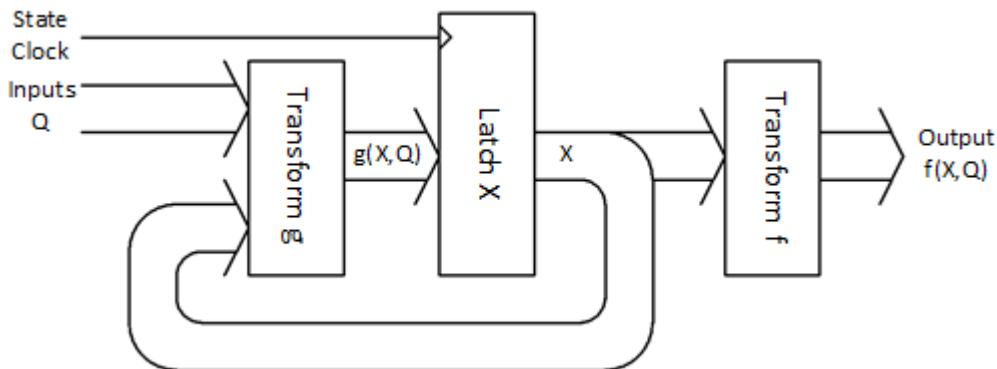

A state machine is a combination of logic, a memory element and feedback. The inputs to the state machine are combined with the current state of the state machine, to determine the next state. The next state becomes the current state when the state clock occurs and the outputs of the state machine are determined by the current state. See [Figure 1](#) for a general block diagram.

**Figure 1. Block Diagram of a Generic State Machine**

In the block diagram, input Q is combined with the current output of Latch X. The result,  $g(X, Q)$ , are the next state and are latched on the active edge of the system clock. The outputs of Latch X can also be passed through additional logic (Transform f) to generate the output. This configuration is typically referred to as a Moore state machine.

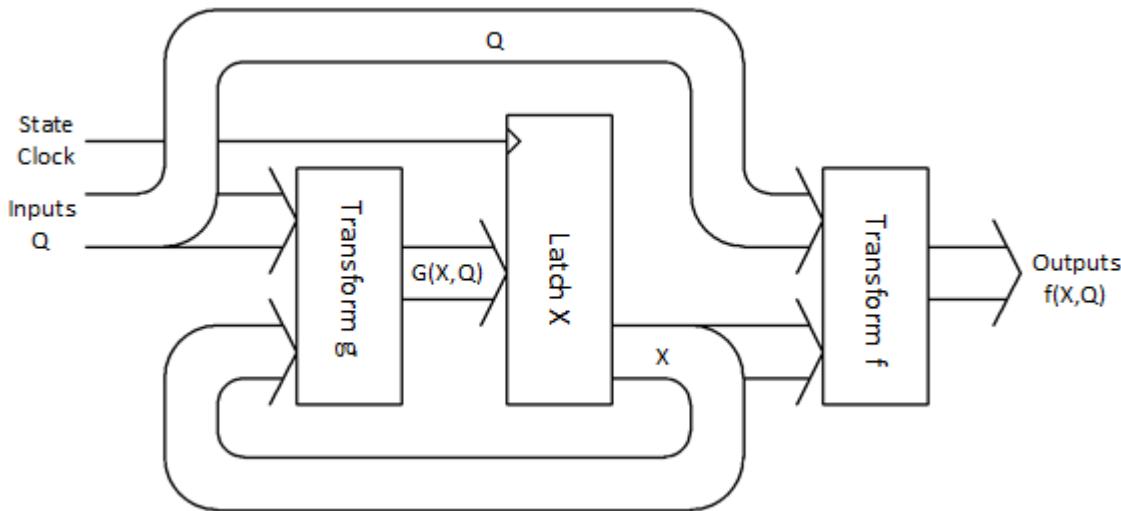

An alternative configuration utilizes feed forward from the inputs to the outputs that are not synchronized by the latch. See [Figure 2](#) for a general block diagram.

**Figure 2. Generic State Machine Block Diagram**

In this block diagram, input  $Q$  is combined with the current output of Latch  $X$ . The result,  $G(X, Q)$  are the next states and are latched on the active edge of the system clock. The outputs of Latch  $X$  can also be passed through additional logic (Transform  $f$ ) to generate the output. This configuration is typically referred to as a Moore state machine.

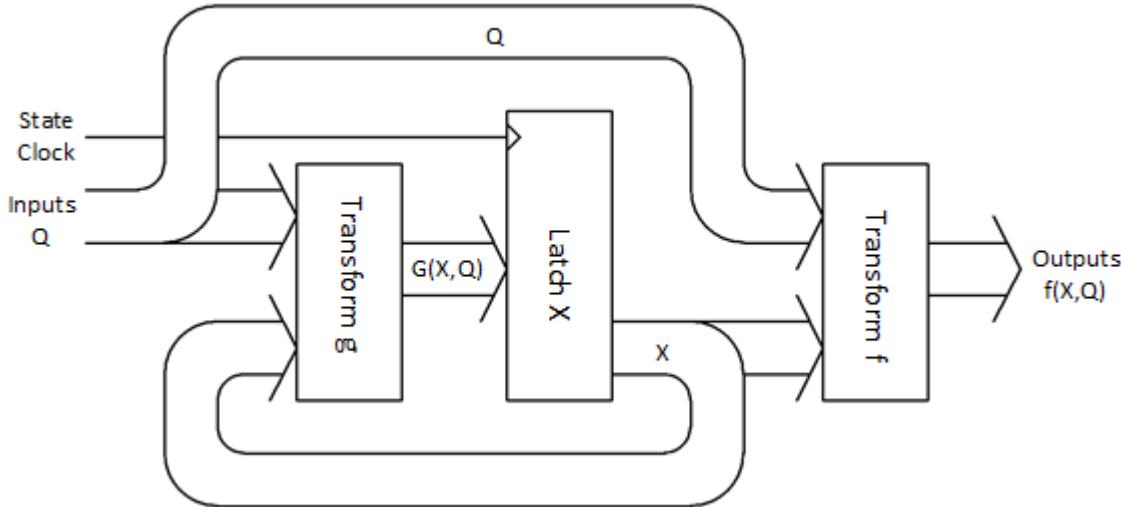

An alternative configuration utilizes feedforward from the inputs to the outputs that are not synchronized by the latch. See [Figure 3](#) for its general block diagram.

**Figure 3. Generic State Machine with Feedforward Block Diagram**

In this block diagram, the same elements of the Moore design are present, with the addition of the feedforward path from the inputs to the outputs. This configuration is typically referred to as a Mealy state machine.

Typically, a Mealy state machine has fewer states than a Moore design because a single state enables multiple different outputs from the feedforward path. A Moore design is generally considered safer because the outputs are synchronized to the state clock, reducing the possibility of logical race conditions on the state machine output. However, Mealy state machines respond faster to input changes than a Moore state machine.

---

## Table of Contents

---

|                                                            |    |

|------------------------------------------------------------|----|

| Introduction.....                                          | 1  |

| 1. Overview.....                                           | 4  |

| 2. Moore State Machine (Without an Input Transform G)..... | 5  |

| 3. Moore State Machine (With an Input Transform G).....    | 7  |

| 4. Moore State Machine Designs Using CLC and Ports.....    | 9  |

| 5. Using Timer Peripherals as State Machines.....          | 11 |

| 5.1. State Machine Using TMR2 and CCP.....                 | 11 |

| 5.2. State Machine using TMR1, CCP and CLC.....            | 11 |

| 5.3. State Machine Using Horizontal Sync Timing.....       | 13 |

| 6. Conclusions.....                                        | 15 |

| The Microchip Website.....                                 | 16 |

| Product Change Notification Service.....                   | 16 |

| Customer Support.....                                      | 16 |

| Microchip Devices Code Protection Feature.....             | 16 |

| Legal Notice.....                                          | 16 |

| Trademarks.....                                            | 17 |

| Quality Management System.....                             | 17 |

| Worldwide Sales and Service.....                           | 18 |

## 1. Overview

This application note will explore several potential designs, which can be implemented with either configuration, using the DMA peripheral.

The DMA peripheral is a byte-wide data transfer peripheral that can be triggered either by software or a selected hardware event. This application will be using the DMA to transfer data from one register to another as:

1. The latch element of the state machine, latching and transferring data from the input Transform G to the output Transform F.

2. A generic transfer mechanism to move the state data from the output of the latch to the input of Transform G.

3. A generic transfer mechanism to move the state from the output of the latch to the output Transform F.

4. Or, a generic transfer mechanism to reconfigure a state machine on-the-fly.

While the DMA is the focus of this application note, it will not delve deeply into the configuration of the DMA. For information on the configuration of the DMA, refer to “*Configuring the DMA Peripheral*” Technical Brief (DS90003242) for more information.

## 2. Moore State Machine (Without an Input Transform G)

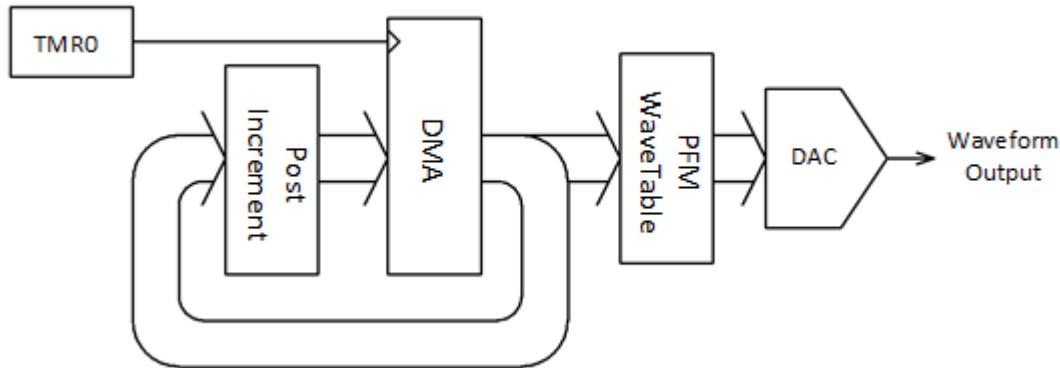

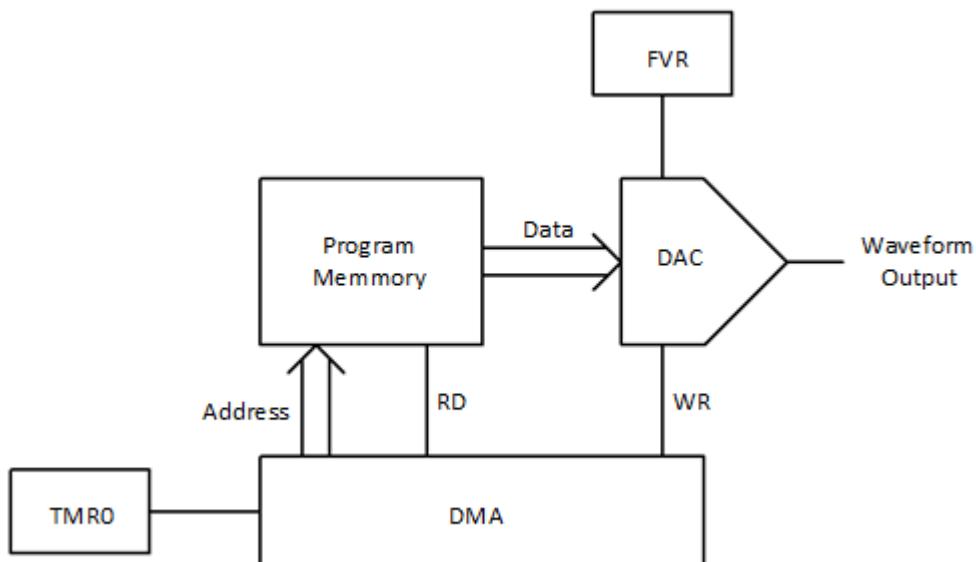

To demonstrate a simple Moore configuration, a simple arbitrary waveform generator is presented. The wavetable for the waveform is stored sequentially in Programmable Flash Memory (PFM) and the output is the data register of a Digital-to-Analog Converter (DAC) peripheral. Timer0 provides the periodic state clock, which triggers the DMA peripheral to copy the data from PFM to the DAC on each rising edge. See [Figure 2-1](#) below.

**Figure 2-1. Waveform Generator Block Diagram**

In this example:

1. TMR0 is configured as the state clock.

2. A table of waveform values is stored in PFM.

3. A 5-bit DAC is used as the state machine output and the FVR is used as the DAC reference.

4. The DMA is configured to read 64 1-byte values from PFM with post-increment and the count register, equal to the size of the PFM table.

5. DMA is further configured to write the 1-byte value to the DAC register using the Fixed Address mode.

6. DMA is configured for continuous operation using TMR0 as the trigger.

**Figure 2-2. CIP Connections for a Waveform Generator Block Diagram**

In [Figure 2-2](#), Timer0 provides the state clock by triggering the DMA transaction. The transaction loads a value from PFM based on its current source address. The value is then written to the data register of the DAC. Once the transfer is complete, the DMA increments the source address register and reloads the address register if the maximum size of

the table is reached. Because the DMA is configured for Continuous mode, this transaction cycle repeats at every state clock transition, out of Timer0, until the DMA or TMR0 is disabled.

While this design doesn't use an external input to the state machine (Transform g), and the feedback is internal to the DMA peripheral (address increment), the basic requirements for a Moore state machine are satisfied. The source address register of the DMA acts as the state machine Latch X. The DMA's post-increment function is the feedback from the output to the input of the latch, providing a sequential source address. The DMA transaction also converts the PFM address to an output value for conversion by the DAC.

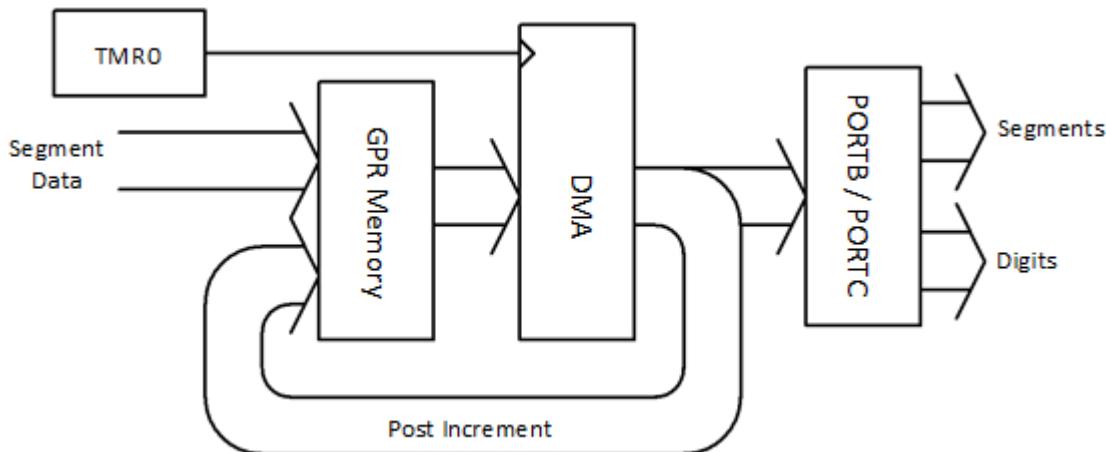

### 3. Moore State Machine (With an Input Transform G)

A LED display driver is implemented as a slight variation on the previous design. In this example, the source memory is GPR memory and the outputs are two contiguous parallel ports, which drive segment and digit drivers. In operation, the DMA will load two values, a segment drive value and a digit enable value. See [Table 3-1](#). These values are transferred to the ports by the DMA, generating the appropriate drive for one of the 7-segment displays.

**Table 3-1. Data Storage in GPR Memory**

| Address | Data       |

|---------|------------|

| 0x00    | Digit 1    |

| 0x01    | 0b00000001 |

| 0x02    | Digit 2    |

| 0x03    | 0b00000010 |

| 0x04    | Digit 3    |

| 0x05    | 0b00000100 |

| 0x06    | Digit 4    |

| 0x07    | 0b00001000 |

Because the source is GPR memory, it allows the system code to make changes on-the-fly as the state machine is running, so any values loaded into the GPR memory are automatically displayed on the 7-segment display. See [Figure 3-1](#) for the block diagram and [Figure 3-2](#) for the CIP connections.

**Figure 3-1. LED Display Driver Block Diagram**

Figure 3-2. CIP Connections for LED Driver

In Figure 3-2, Timer0 provides the state clock by triggering the DMA transaction. The transaction loads the segment and digit values from the GPR memory based on its current source address. The values are then written to PORTB and PORTC. After the transfer of each byte, the DMA increments the source address and reloads the register if the maximum size of the table is reached. Once the value is loaded into the ports, drivers buffer the signals and drive the individual displays. Given the DMA is configured for Continuous mode, the cycle repeats for every state clock transition from Timer0, until the DMA or TMR0 is disabled.

In this design, the input to the state machine is handled by a software update of the display data and the feedback is internal to the DMA peripheral (auto-increment). Together, both systems provide the basic requirements for a Moore state machine. The source address register of the DMA acts as the state machine latch. The DMA's post-increment function is the feedback from the output to the input of the latch, providing a sequential address output. The GPR data, combined with the DMA action, convert the address to data values for both the segment and digit drivers for the displays.

In both of the preceding examples, the DMA peripheral acted as the latch, part of the feedback and a transport mechanism to move the data from memory to the output peripheral. The latch was implemented by the DMA Source Address Pointer (DMAxSPTR). The feedback mechanism was DMAxSPTR's auto-increment, plus the reload countdown in the DMAxSCNT registers. Also, the transport mechanism was the DMA transaction, transferring data pointed at by DMAxSPTR, from memory, to the DAC/port peripherals.

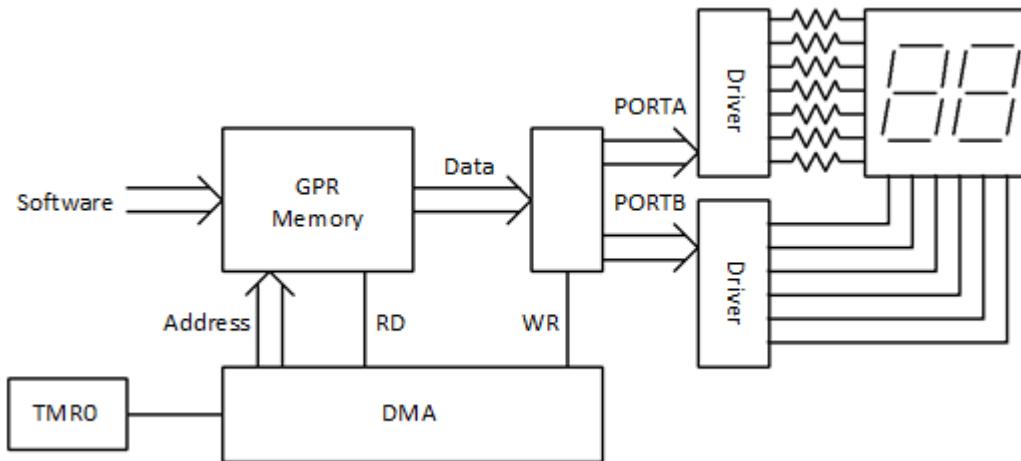

## 4. Moore State Machine Designs Using CLC and Ports

In application note [AN2912](#), multiple CLC peripherals are combined to create a hardware state machine. One group of the CLCs are used as the state machine latch, while others perform the transforms for the system. While this approach does work, the limited number of CLCs prevents the creation of a complex state machine.

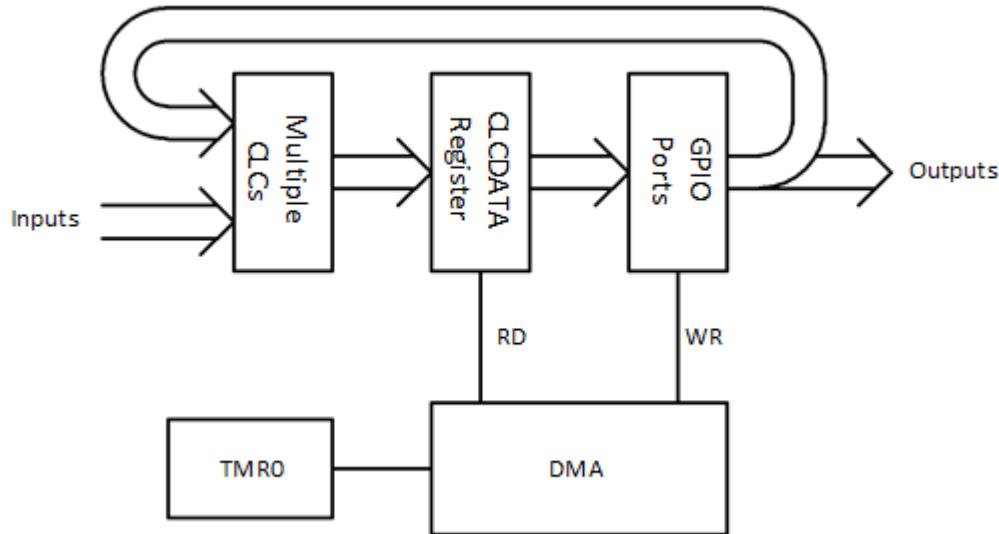

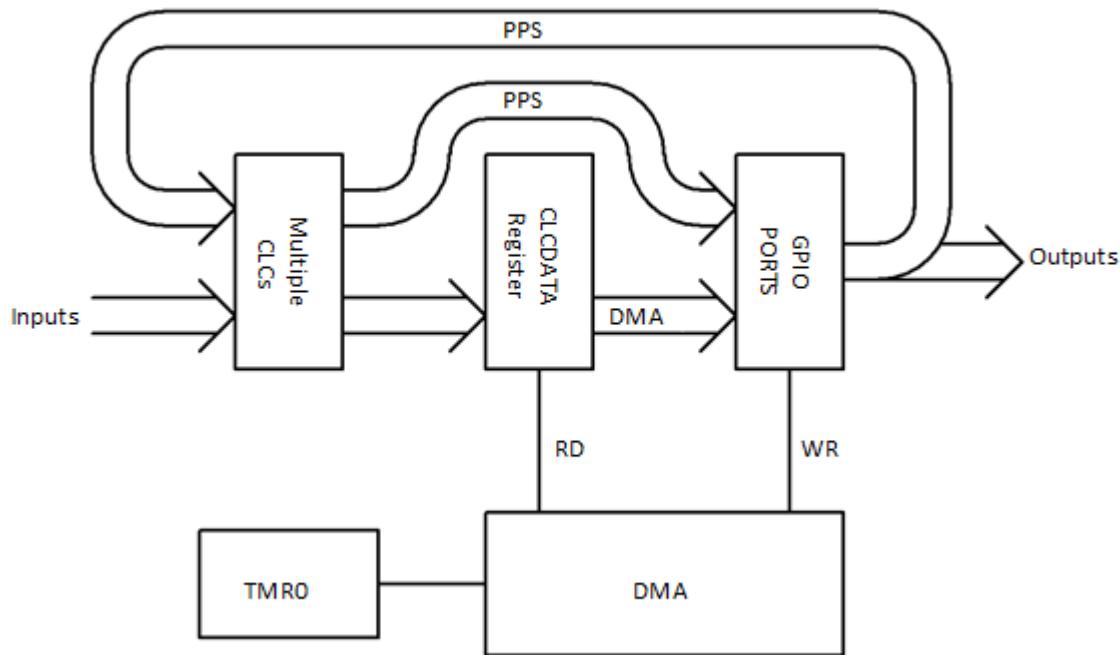

If the CLCs were not needed for the latch function, a somewhat larger, more complex state machine would be possible. One way to accomplish this goal would be to replace the latch function with a combination of the DMA function and a GPIO PORT register. See [Figure 4-1](#).

**Figure 4-1. CLC, DMA, PORT Moore State Machine Block Diagram**

The CLC peripherals in the design take their input from both the GPIO port, and other system inputs, to form an input transform function using the Boolean functions of the CLC peripheral. The outputs of the CLCs are then latched by the DMA, transferring the CLC outputs to a GPIO port.

**Note:** The CLC outputs are available as a single byte via the CLCDATA register.

Using the rollover output of TMR0 to trigger the DMA, the outputs of the CLCs are copied from the CLCDATA register and stored in the GPIO port. The individual port pins are then connected to the CLC inputs, using the PPS function. This completes a full latch with feedback from the output to the input.

**Note:** The full eight bits of the port need not be used for the state machine. Only those port bits configured in PPS to display the LAT data will be affected by the DMA write. Any bits configured to output other CIP functions will continue to output their selected function.

If the microcontroller contains unused CLC peripherals, they can be used to form an output transform Function f. These CLCs would take their inputs from the GPIO port, perform a Boolean transform and then provide their outputs to either other CIP functions, a different GPIO port or the unused GPIO port bits via PPS.

In fact, if the output CLCs also accept inputs from sources other than the state output (GPIO port), then the output transform will include asynchronous inputs, making the design a Mealy state machine. See [Figure 4-2](#).

Figure 4-2. CLC, DMA, PORT Mealy State Machine Block Diagram

## 5. Using Timer Peripherals as State Machines

For state machine designs that require a minimum number of Active states and long delays between state transitions, a timer can be used as the state machine latch. The advantage of this design is the large number of bits in the latch and the automated increment of the state value.

To provide feedback, the output of the timer is accessible through the CCP and PWM peripherals.

1. If Timer2 is used, then a specific state can be decoded using the PWM logic of the CCP.

2. If Timer1 is used, the decoding can be accomplished by the output compare function in the CCP.

3. If the new 16-bit PWM is used, then left, center, right and variable alignment are available, increasing the options for decoding specific timer values.

The decoded outputs of the CCP/PWM can then be used to generate outputs, trigger the DMA to change the state value in the timer or reconfigure the timer. See [Figure 5-1](#).

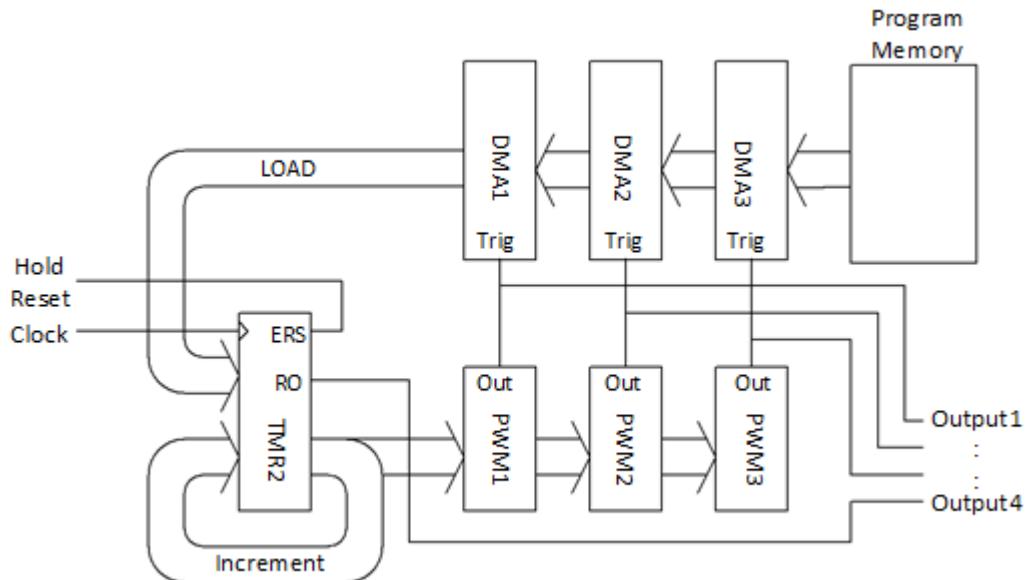

### 5.1 State Machine Using TMR2 and CCP

[Figure 5-1](#) shows a state machine based on TMR2 and the PWM section of three CCP peripherals. Inputs include the state machine clock and a hold/Reset input to the timer. The output of the timer feeds into CCP1, CCP2 and CCP3. Each PWM output is then routed to the trigger of a DMA module. When the timer out equals the duty cycle setting of the PWM, the associated DMA is triggered and the timer is set to a constant stored in program memory. Each of the PWM outputs also doubles as an output of the state machine, as well as, the rollover output of the timer.

This configuration creates a “Moore State Machine without an Input Transform,” like the first example above. The difference is that this state machine can generate programmable delays between state changes that are both long and variable, under software control. To change the delays, the software need only reprogram the duty cycle register for the appropriate CCP PWM peripherals. In addition, the hold/Reset input allows some control via CIP signals.

**Figure 5-1. State Machine Using TMR2 and CCP**

### 5.2 State Machine using TMR1, CCP and CLC

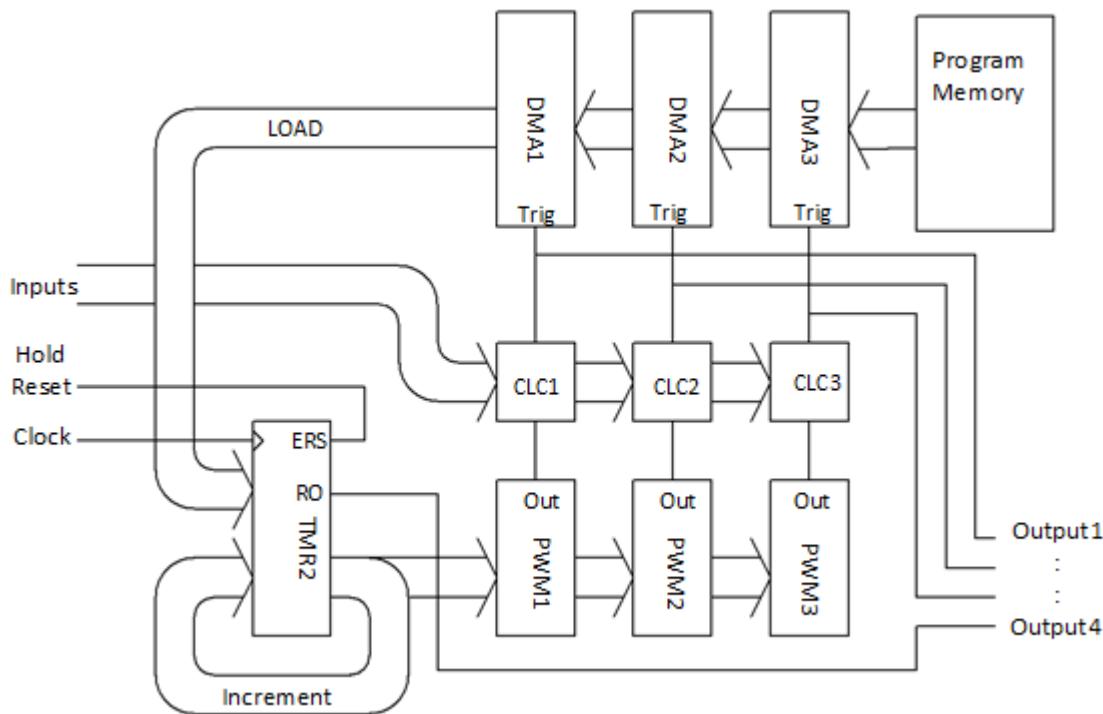

[Figure 5-2](#) shows a modified version of [Figure 5-1](#) that uses CLC peripherals between the decoded PWM output and the triggers for the DMA. The purpose of the CLC modules is to allow external inputs to the system that combine or enable/disable the feedback based on inputs to the state machine. The CLC combinational logic could also combine different PWM signals to generate more complex state machine outputs.

Figure 5-2. State Machine Using TMR1, CCP and CLC

Implementation of a Mealy version of this state machine can also be created by using additional CLC peripherals to combine asynchronous inputs with the PWM outputs, to generate the state machine outputs.

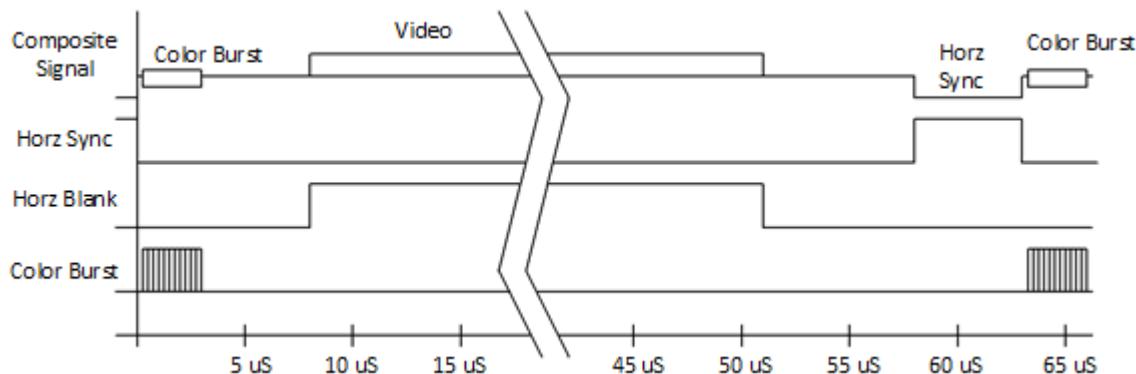

As an example, consider a NTSC horizontal sync timing generator for a television signal. The video pulse chain is 63  $\mu$ s long with 43  $\mu$ s of video, 10  $\mu$ s of blanking and 10  $\mu$ s of horizontal sync pulse. The horizontal pulse has a 2  $\mu$ s front porch, a 5  $\mu$ s pulse and a 3  $\mu$ s back porch with 2.5  $\mu$ s of a 3.579545 MHz color burst signal. See [Figure 5-3](#) for a diagram of the timing signals.

Figure 5-3. Horizontal Video Signal Example

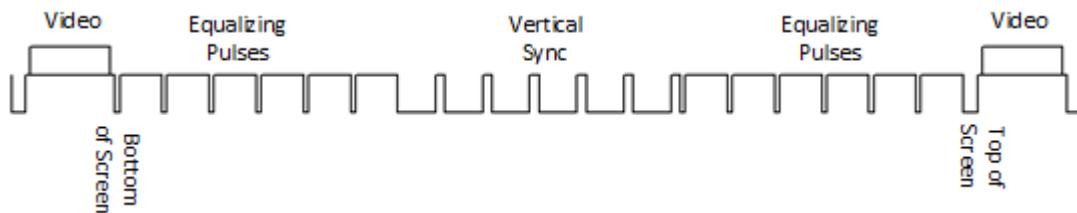

During the vertical sync portion of the signal, the 63  $\mu$ s pulse chain is replaced with a 31.5  $\mu$ s pulse chain with a 2.3  $\mu$ s pulse for the first six equalizing pulses, then 27.1  $\mu$ s vertical sync pulses for another six, and then another six equalizing pulses with the original 2.3  $\mu$ s, before returning to the normal 63  $\mu$ s pulse chain. See [Figure 5-4](#) for an example of the vertical timing.

**Figure 5-4. Vertical Sync Pulses**

**Note:** This example will only generate the horizontal timing, not the vertical. However, it does accept inputs from the vertical timing to alter the horizontal timing for the vertical sync portion of the signal. This design will also only implement a non-interlace signal, not a full interlaced timing signal.

### 5.3 State Machine Using Horizontal Sync Timing

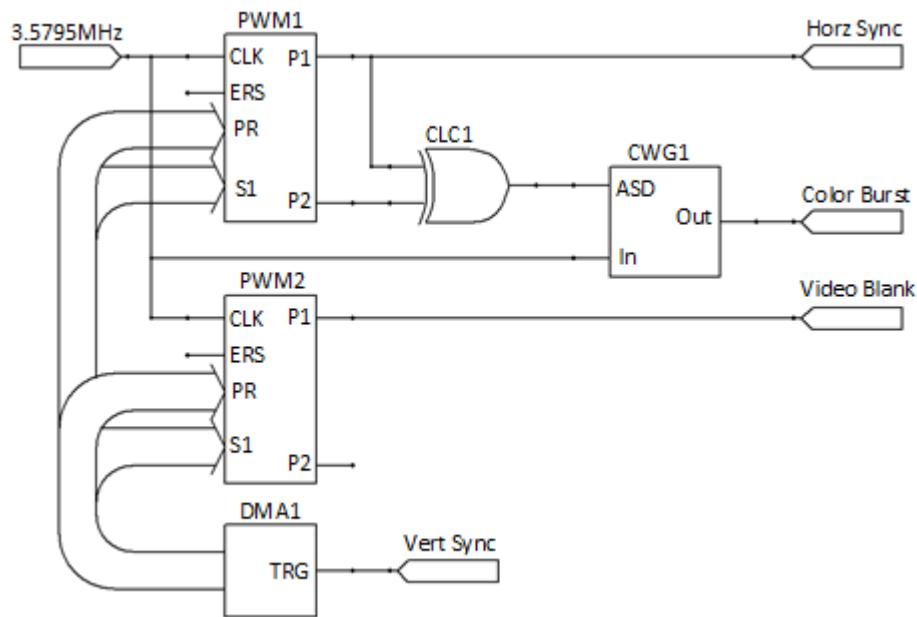

To implement the Horizontal Sync Timing state machine, the new 16-bit PWM module will be used in conjunction with a CLC and DMA peripheral. [Figure 5-5](#) shows the block diagram of the combined CIP peripherals.

**Figure 5-5. CIP Block Diagram of the Horizontal Sync Timing System**

In the example:

1. PWM1 is configured for dual output, left justified PWM output with a period of 63  $\mu$ s.

2. P1 of PWM1 is configured to generate the 5  $\mu$ s horizontal sync pulse.

3. P2 of PWM1 is configured to generate an 8  $\mu$ s gating signal for the color burst signal.

4. The XOR in CLC1 combines the two signals to generate the 3  $\mu$ s gating pulse that follows the horizontal sync pulse.

5. The input to the CWG is the raw 3.5795 MHz clock for the color burst.

6. The 3  $\mu$ s gating pulse drives the auto-shutdown input of the CWG, gating the color burst signal.

7. PWM2 is configured for variable alignment. This allows variable start and stop times for the PWM. This output provides the Video Blank signal.

8. DMA1 is configured to load the period and phase registers for both PWM, from a table in program memory, triggered by the vertical timing chain and the rollover of PWM1's timer.

In normal horizontal video operation, the period of both PWMs is set to 63  $\mu$ s. PWM1 generates the 5  $\mu$ s horizontal sync and the 8  $\mu$ s gating signal. Together, they generate the 3  $\mu$ s gate for the color burst immediately following the

horizontal sync pulse. PWM2 generates the blanking signal, providing 7  $\mu$ S of blanking before the horizontal sync pulse and 8  $\mu$ S following the pulse.

The vertical sync system triggers the DMA transfer at the bottom of the page:

1. It reconfigures the horizontal state machine to generate a 2.3  $\mu$ S equalizing sync pulse with a 31.5  $\mu$ S period for six pulses. The Blanking PWM is also configured for 100%, to prevent inadvertent video generation.

2. Following the six equalization pulses, the DMA reconfigures the state machine to generate a 27.1  $\mu$ S sync pulse with a 31.5  $\mu$ S period for six vertical sync pulses. The blanking PWM remains at 100%.

3. After the vertical sync pulses, the DMA reconfigures the state machine to generate a 2.3  $\mu$ S sync pulse with a 31.5  $\mu$ S period for another six equalizing pulses. The Blanking PWM remains at 100%.

4. Finally, it reconfigures the state machine to generate the original horizontal timing and blanking to restart the video at the top of the screen.

**Note:** To accomplish the reconfiguration using the DMA, the contiguous PWM Mirror registers in the Special Function Register map are used (address = 4020h). This register map is convenient because the period and phase registers have been remapped into adjacent memory locations. See the “Special Function Register Map” figure in the “*PIC18F2747/57Q43 Data Sheet*” (DS40002147) for more information.

**Note:** For this design, a 14.31818 MHz (3.5795 x 4) external crystal oscillator was used for the microcontroller clock.

In this example, the state machine latch is the base timer for the two PWM peripherals. The state clock is the 3.5795 MHz clock supplied to the PWM clock inputs. The internal counter increment function provides the feedback and the PWM logic, combined with the external CLC and CWG peripherals, provides the output Transform f. The input to the state machine is provided by the DMA peripheral that reconfigures the two PWMs in response to control signals from the vertical timing state machine and the horizontal sync PWM.

**Note:** Because PWM1 and PWM2 operate from different internal timers, it is necessary to enable both PWM peripherals at the same time. This is accomplished by using the PWMEN register, which has mirror enable bits for all three PWM modules. Both PWM peripherals were configured and then enabled together by setting the appropriate bits in the register.

## **6. Conclusions**

In this document a variety of different hardware state machine designs have been presented;

1. Using the DMA peripheral to pull sequential state data out of program memory to create a sequential control state machine. This method uses the counter register in the DMA peripheral as the state latch.

2. Using the DMA peripheral to pull sequential state data out of data memory to create sequential control state machines with software-controlled input. This method also uses the counter register in the DMA peripheral as the state latch.

3. Using the DMA peripheral to copy the outputs of the CLC peripherals to a GPIO port, with direction connection of additional CLC outputs to the same port, to create a traditional Mealy hardware state machine. This design also used the latch function in the CLC as the state latch.

4. Finally, a Moore design based on a timer PWM combination that uses the PWM output as an output transform, and the DMA as an input transform that reconfigured the PWM on-the-fly.

While several configurations have been shown, they are not an exhaustive list of the possible configurations. However, the application of a specific example of design will be dictated by the complexity of the design required, and the availability of peripherals on a target device. The examples in this application note were designed using the PIC18F47Q43.

## The Microchip Website

Microchip provides online support via our website at <http://www.microchip.com/>. This website is used to make files and information easily available to customers. Some of the content available includes:

- **Product Support** – Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- **General Technical Support** – Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- **Business of Microchip** – Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## Product Change Notification Service

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to <http://www.microchip.com/pcn> and follow the registration instructions.

## Customer Support

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Embedded Solutions Engineer (ESE)

- Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: <http://www.microchip.com/support>

## Microchip Devices Code Protection Feature

Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

## Legal Notice

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with

your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

## Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBloX, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TempTrackr, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, Vite, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQL, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2020, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-5673-5

## Quality Management System

For information regarding Microchip's Quality Management Systems, please visit <http://www.microchip.com/quality>.

**Worldwide Sales and Service**

| AMERICAS                                                                                                                                                                                                                                                                                                             | ASIA/PACIFIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ASIA/PACIFIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | EUROPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Corporate Office</b><br>2355 West Chandler Blvd.<br>Chandler, AZ 85224-6199<br>Tel: 480-792-7200<br>Fax: 480-792-7277<br>Technical Support:<br><a href="http://www.microchip.com/support">http://www.microchip.com/support</a><br>Web Address:<br><a href="http://www.microchip.com">http://www.microchip.com</a> | <b>Australia - Sydney</b><br>Tel: 61-2-9868-6733<br><b>China - Beijing</b><br>Tel: 86-10-8569-7000<br><b>China - Chengdu</b><br>Tel: 86-28-8665-5511<br><b>China - Chongqing</b><br>Tel: 86-23-8980-9588<br><b>China - Dongguan</b><br>Tel: 86-769-8702-9880<br><b>China - Guangzhou</b><br>Tel: 86-20-8755-8029<br><b>China - Hangzhou</b><br>Tel: 86-571-8792-8115<br><b>China - Hong Kong SAR</b><br>Tel: 852-2943-5100<br><b>China - Nanjing</b><br>Tel: 86-25-8473-2460<br><b>China - Qingdao</b><br>Tel: 86-532-8502-7355<br><b>China - Shanghai</b><br>Tel: 86-21-3326-8000<br><b>China - Shenyang</b><br>Tel: 86-24-2334-2829<br><b>China - Shenzhen</b><br>Tel: 86-755-8864-2200<br><b>China - Suzhou</b><br>Tel: 86-186-6233-1526<br><b>China - Wuhan</b><br>Tel: 86-27-5980-5300<br><b>China - Xian</b><br>Tel: 86-29-8833-7252<br><b>China - Xiamen</b><br>Tel: 86-592-2388138<br><b>China - Zhuhai</b><br>Tel: 86-756-3210040 | <b>India - Bangalore</b><br>Tel: 91-80-3090-4444<br><b>India - New Delhi</b><br>Tel: 91-11-4160-8631<br><b>India - Pune</b><br>Tel: 91-20-4121-0141<br><b>Japan - Osaka</b><br>Tel: 81-6-6152-7160<br><b>Japan - Tokyo</b><br>Tel: 81-3-6880- 3770<br><b>Korea - Daegu</b><br>Tel: 82-53-744-4301<br><b>Korea - Seoul</b><br>Tel: 82-2-554-7200<br><b>Malaysia - Kuala Lumpur</b><br>Tel: 60-3-7651-7906<br><b>Malaysia - Penang</b><br>Tel: 60-4-227-8870<br><b>Philippines - Manila</b><br>Tel: 63-2-634-9065<br><b>Singapore</b><br>Tel: 65-6334-8870<br><b>Taiwan - Hsin Chu</b><br>Tel: 886-3-577-8366<br><b>Taiwan - Kaohsiung</b><br>Tel: 886-7-213-7830<br><b>Taiwan - Taipei</b><br>Tel: 886-2-2508-8600<br><b>Thailand - Bangkok</b><br>Tel: 66-2-694-1351<br><b>Vietnam - Ho Chi Minh</b><br>Tel: 84-28-5448-2100 | <b>Austria - Wels</b><br>Tel: 43-7242-2244-39<br>Fax: 43-7242-2244-393<br><b>Denmark - Copenhagen</b><br>Tel: 45-4450-2828<br>Fax: 45-4485-2829<br><b>Finland - Espoo</b><br>Tel: 358-9-4520-820<br><b>France - Paris</b><br>Tel: 33-1-69-53-63-20<br>Fax: 33-1-69-30-90-79<br><b>Germany - Garching</b><br>Tel: 49-8931-9700<br><b>Germany - Haan</b><br>Tel: 49-2129-3766400<br><b>Germany - Heilbronn</b><br>Tel: 49-7131-72400<br><b>Germany - Karlsruhe</b><br>Tel: 49-721-625370<br><b>Germany - Munich</b><br>Tel: 49-89-627-144-0<br>Fax: 49-89-627-144-44<br><b>Germany - Rosenheim</b><br>Tel: 49-8031-354-560<br><b>Israel - Ra'anana</b><br>Tel: 972-9-744-7705<br><b>Italy - Milan</b><br>Tel: 39-0331-742611<br>Fax: 39-0331-466781<br><b>Italy - Padova</b><br>Tel: 39-049-7625286<br><b>Netherlands - Drunen</b><br>Tel: 31-416-690399<br>Fax: 31-416-690340<br><b>Norway - Trondheim</b><br>Tel: 47-72884388<br><b>Poland - Warsaw</b><br>Tel: 48-22-3325737<br><b>Romania - Bucharest</b><br>Tel: 40-21-407-87-50<br><b>Spain - Madrid</b><br>Tel: 34-91-708-08-90<br>Fax: 34-91-708-08-91<br><b>Sweden - Gothenberg</b><br>Tel: 46-31-704-60-40<br><b>Sweden - Stockholm</b><br>Tel: 46-8-5090-4654<br><b>UK - Wokingham</b><br>Tel: 44-118-921-5800<br>Fax: 44-118-921-5820 |