## Biassing and Readout of ON Semiconductor SiPM Sensors

ON Semiconductor®

[www.onsemi.com](http://www.onsemi.com)

### APPLICATION NOTE

This application note covers all aspects of Silicon Photomultiplier (SiPM) biasing and readout for ON Semiconductor SiPMs. Readout options for both the standard and fast terminals are discussed.

#### SiPM STRUCTURE

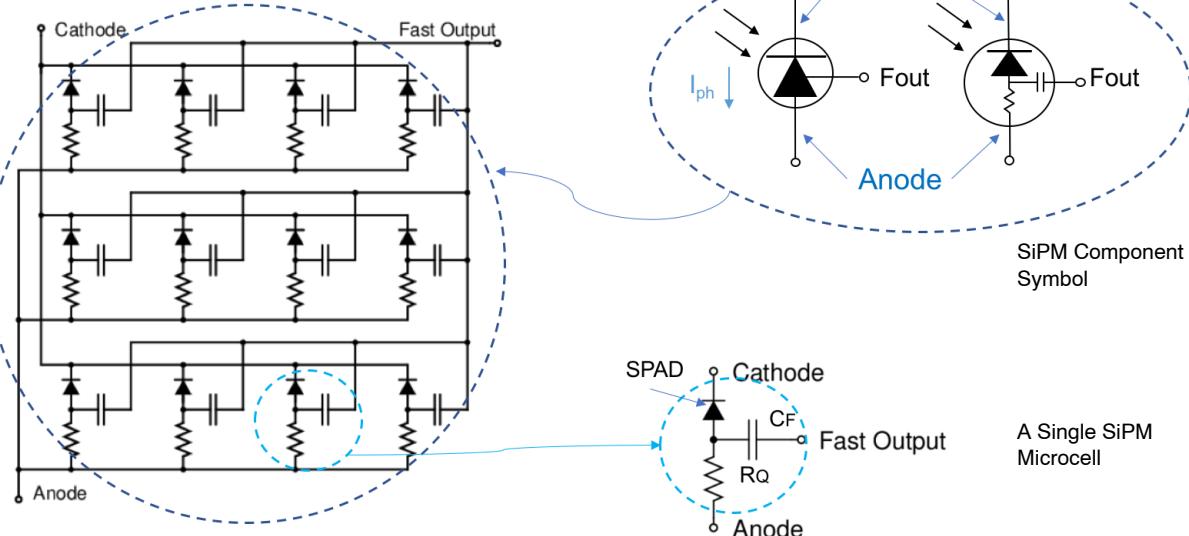

The SiPM consists of an array of microcells. Each microcell consists of a Single Photon Avalanche Diode (SPAD) and a quench resistor. ON Semiconductor SiPMs have 3 terminals; *cathode*, *anode* and *fast output*. For further details of SiPM technology please refer the [Introduction to the Silicon Photomultiplier](#) application note. The SiPM circuit structure and circuit schematic symbol are shown in Figure 2.

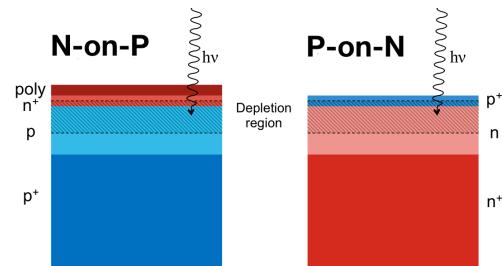

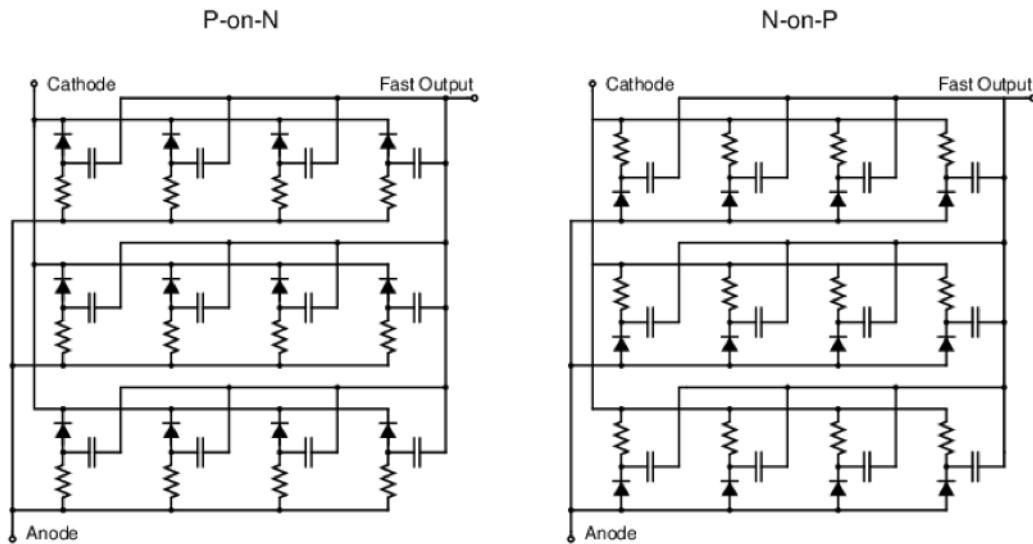

ON Semiconductor SiPMs are either P-on-N or N-on-P type diode structures. Figure 1 shows the diode structure and Figure 3 shows the SiPM schematics for both types.

Figure 1. N-on-P and P-on-N Diode Structures

Figure 2. SiPM Internal Structure and Component Symbol. The SiPM Consists of an Array of Microcells Connected in Parallel. Each Microcell Features a SPAD, Quench Resistor  $R_Q$ , and Fast Capacitor  $C_F$

**Figure 3. Schematic Differences of N-on-P and P-on-N SiPM Structures**

P-on-N structures are used for blue-sensitive SiPMs ([C-Series](#), [J-Series](#)) while an N-on-P structure creates a more red-sensitive SiPM ([RB-Series](#)).

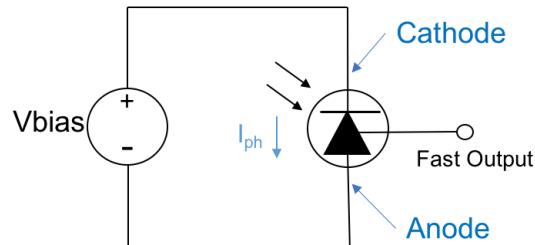

### BIASING THE SiPM

The SiPM is designed to operate in Geiger mode where the *cathode* must be positively biased with respect to the *anode* above the breakdown voltage, as per Figure 4. The breakdown voltage of the SiPM is the minimum reverse bias voltage at which the SPAD operates in Geiger or avalanche mode. The overvoltage is the excess applied bias above the breakdown voltage.

Breakdown voltage and overvoltage range are both a function of the particular SiPM technology. The applied bias voltage should be guided by the datasheet specification for the SiPM, noting that the overvoltage influences SiPM parameters such as PDE (photon detection efficiency), gain and noise.

SiPM breakdown voltage is temperature dependent. The temperature coefficient of breakdown voltage is process dependent and given in the product datasheet. For accurate quantitative detection in an uncontrolled thermal environment, temperature measurement and compensation of the bias voltage may be required to maintain a consistent overvoltage and performance.

### Output Polarity

The *standard output* polarity depends on whether the *anode* or the *cathode* is being used for readout and does not depend on the sensor type. Reading out from the *cathode* will give a negative polarity and reading out from the *anode* will produce positive polarity.

The polarity of the *fast output* is determined by the sensor type. The *fast output* polarity is always positive for P-on-N sensors and negative for N-on-P sensor types. Examples of biasing options are shown in Figures 5–8 on the following pages.

**Figure 4. Biasing the SiPM**

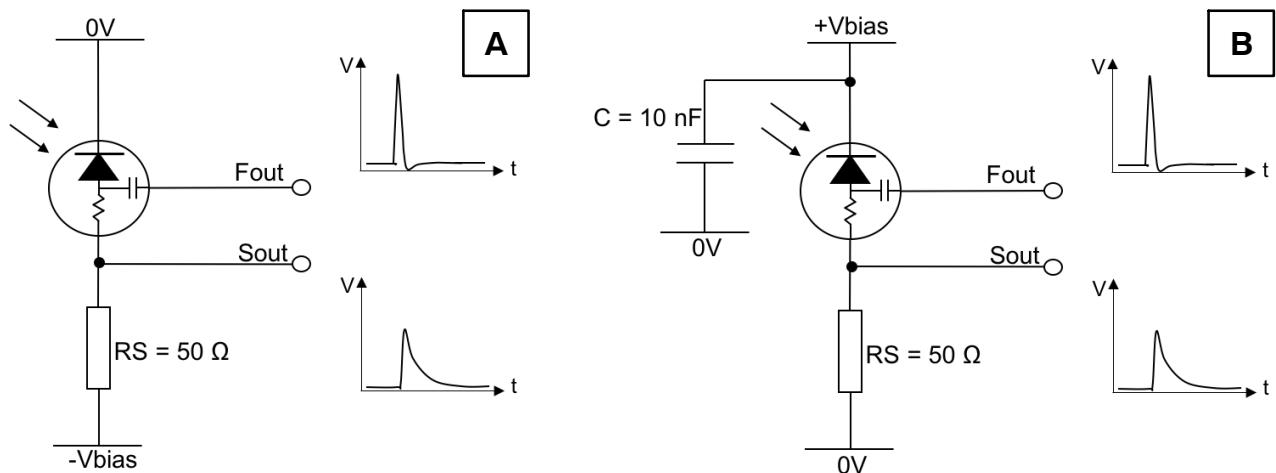

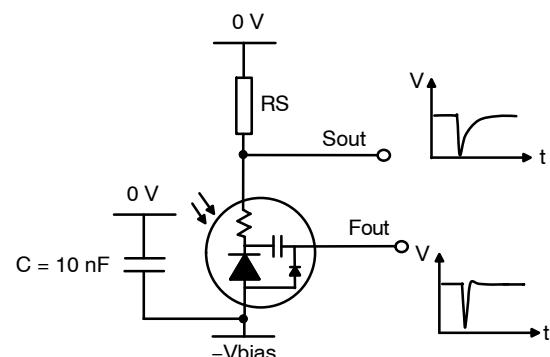

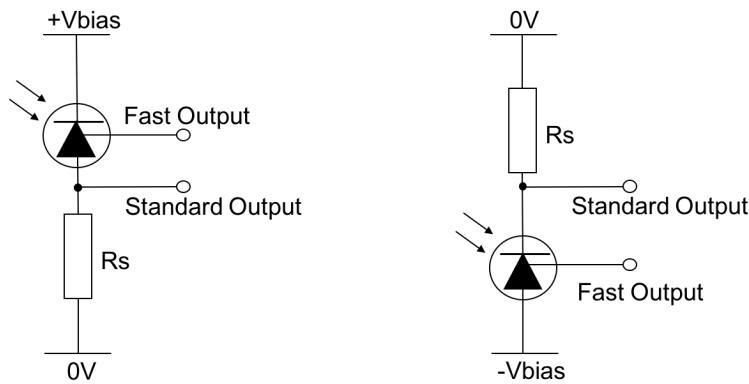

### P-on-N SiPM Structure

The best *fast output* timing and pulse amplitude can be achieved with circuits A or B. If using the *fast output* in circuit B, then a 10 nF, 100 V, low ESR decoupling capacitor must be connected between the *cathode* and 0 V. The track length from the *cathode* to the capacitor should be minimized to reduce track inductance.

Circuit configurations C and D will result in less optimal *fast output* timing and amplitude but will still provide good performance otherwise.

For all circuits, the sense resistor,  $R_S$ , sets up a voltage output on  $S_{out}$ . To minimize the microcell recovery time, the series resistance can be  $R_S = 0 \Omega$ . However in this scenario only the *fast output* is available.

**Figure 5. Biasing and Readout Circuits A and B, for C-Series and J-Series Products. These Configurations Give the Best Fast Output Timing Performance. Note that the Fast Output is always Referenced to 0 V. Sout is Referred to  $-V_{bias}$  in A and to 0 V in B**

**Figure 6. Biasing Circuits C and D, for C-Series and J-Series Products. These Configurations Give Less Optimum Fast Output Timing Performance Compared to A and B. Note that the Fast Output is always Referenced to 0 V. Sout is Referred to  $+V_{bias}$  in C and to 0 V in D**

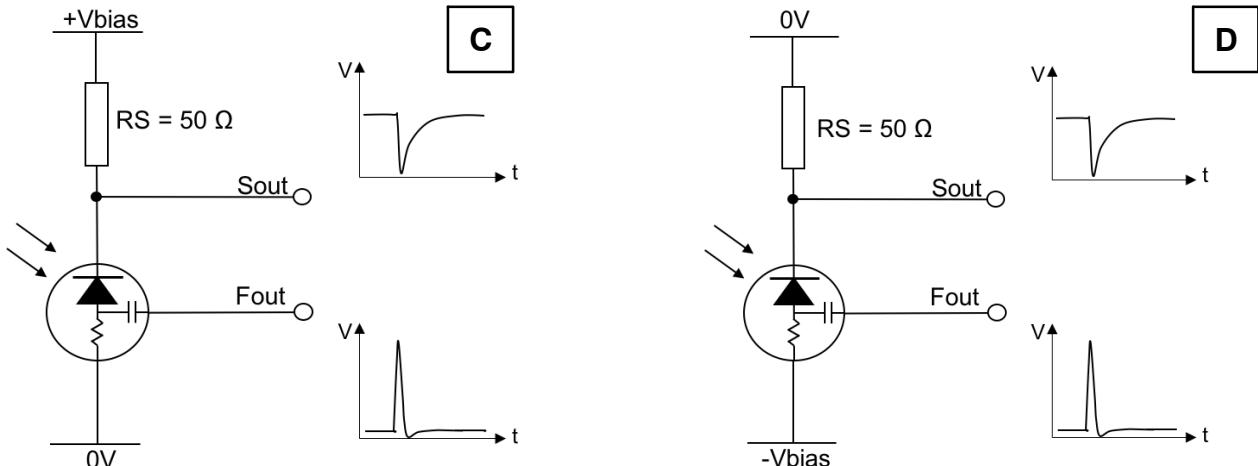

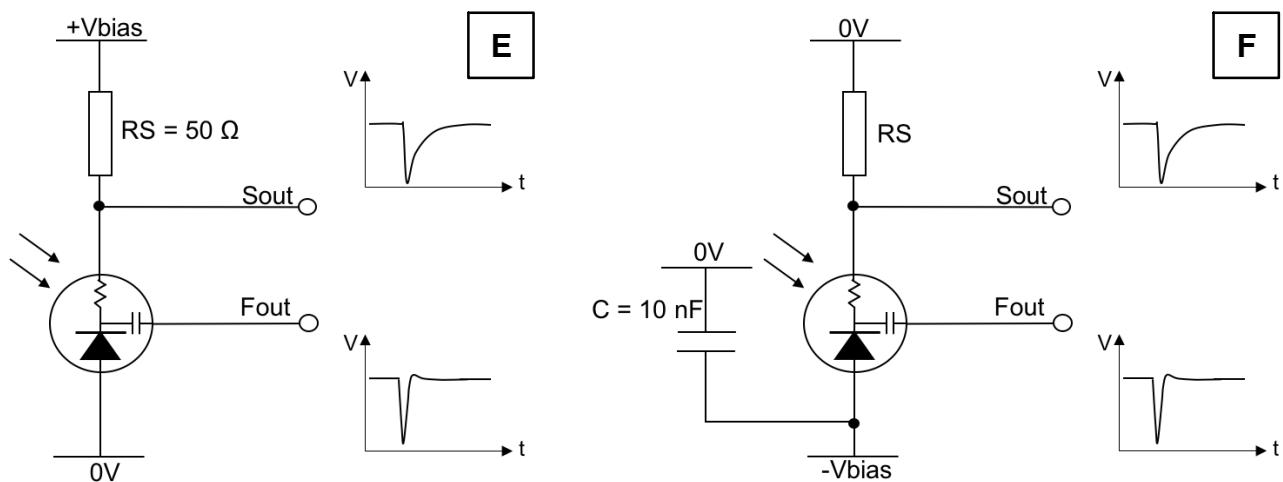

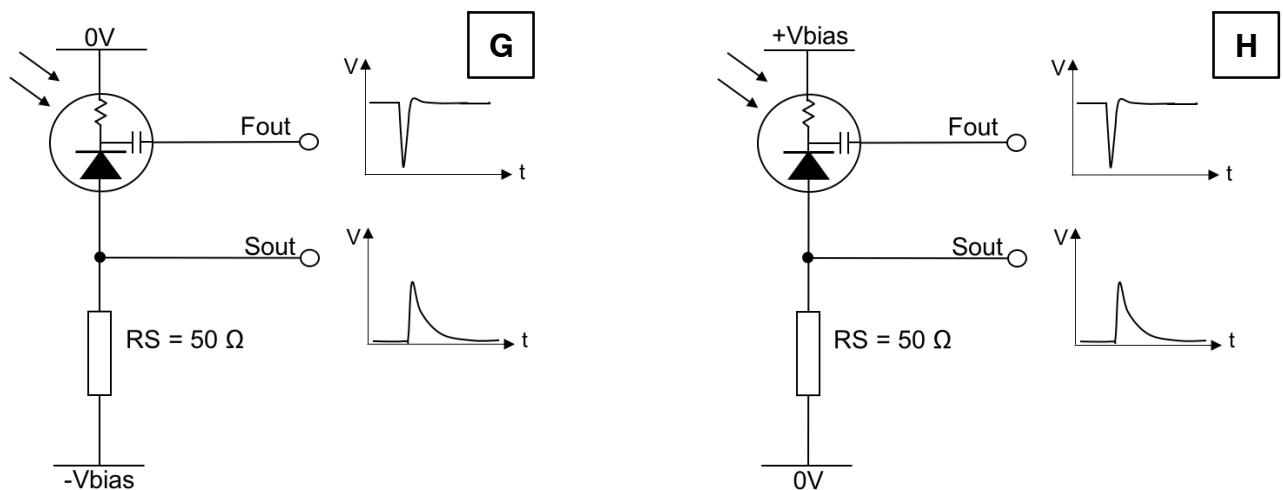

### N-on-P SiPM Structure

#### Biasing RB-Series SiPMs

For the N-on-P type RB-Series SiPM the best *fast output* timing and pulse amplitude can be achieved with circuits E or F. If using the *fast output* in circuit F, then a 10 nF, 100 V, low ESR decoupling capacitor must be connected between the *anode* and 0 V. The track length from the *cathode* to the capacitor should be minimized to reduce track inductance.

Circuit configurations G and H will result in less optimal *fast output* timing and amplitude but will still provide good performance otherwise.

For all circuits, the sense resistor,  $R_S$ , sets up a voltage output on  $S_{out}$ . To minimize the microcell recovery time, the series resistance can be  $R_S = 0 \Omega$ . However in this scenario only the *fast output* is available.

**Figure 7. Recommended Bias Scheme for RB-Series SiPMs. Configurations E & F Give Best Fast Output Performance.  $F_{out}$  is Referenced to 0 V.  $S_{out}$  is Referred to  $+V_{bias}$  in E and to 0 V in F**

**Figure 8. Alternate Bias Scheme for RB-Series SiPMs. Configurations G & H Give Less Optimal  $F_{out}$  Performance Compared to E and F.  $F_{out}$  is Referenced to 0 V.  $S_{out}$  is Referred to  $-V_{bias}$  in G and to 0 V in H**

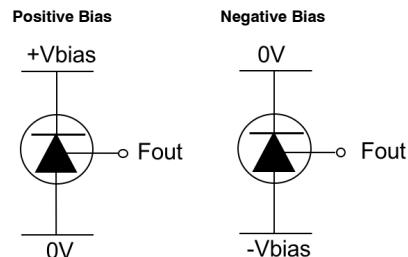

**Figure 9. Recommended Bias Scheme for RD-Series SiPMs.  $S_{out}$  and  $F_{out}$  are Both Referred to 0 V**

#### RD-Series SiPM Biasing Restriction

RD-Series devices are n-on-p type SiPMs that feature an ESD protection diode on the Fast output.

The recommended bias scheme for RD-Series is shown in Figure 9. Note that this is the same as configuration F in Figure 7.

The ESD protection diode leads to a restriction in the way the sensor can be biased. To guarantee correct operation a negative bias must be applied to the anode, with the cathode held at 0 V and the fast output referred to 0 V.

Applying a positive bias voltage (configuration E or H) could result in the ESD protection diode being forward biased during operation and a consequent reduction in the signal output amplitude. Therefore positive bias voltage is not recommended for this device.

Bias scheme G may also be used, however this results in standard output being referred to  $-V_{bias}$ , which may be

undesirable.

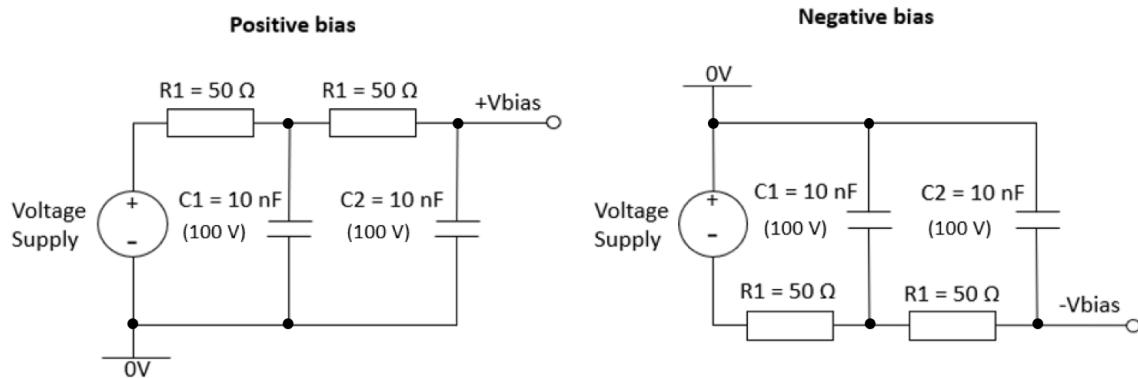

Figure 10. ON Semiconductor Generic Bias Filter

### Bias Filter

A bias filter such as that in Figure 9 may be used with the SiPM to help supply a stable bias voltage by filtering out any noise that may come from the power supply. The components used may be varied to suit the intended application if a specific cut-off frequency is required. This filter is recommended for applications using noisy or switched power supplies. However, the filter may not be suitable for applications requiring fast recovery time or high dynamic range as the series resistance will increase recovery times. For this reason, the values of R1 and R2 should be kept small. Please see the [Optimizing Recovery Time](#) section for more details.

### Bias Decoupling

When a light pulse is detected by the SiPM it will draw a fast transient current from the bias supply which can cause the supply voltage to drop slightly for a short period of time. A decoupling capacitor acts as a charge storage device providing energy when required by the SiPM and making it less susceptible to short term changes in the bias voltage. Changes in the bias voltage are effectively changes to the applied overvoltage which controls the gain and PDE of the SiPM. The capacitance of the selected decoupling capacitor should be greater than the capacitance of the SiPM being used. To maintain a consistent bias supply it is recommended that a good quality, 10 nF, 100 V, ceramic SMT decoupling capacitor, with low ESR and ESL, be connected between Vbias and 0 V, as close to the SiPM Vbias terminal (*anode* or *cathode*) as possible. See Figure 11.

Figure 11. Decoupling of the Bias

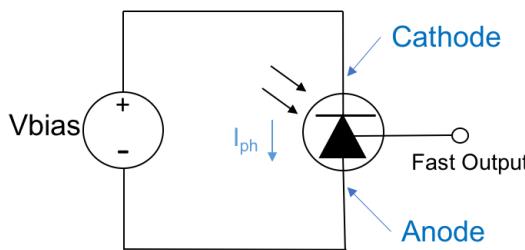

## BASIC SiPM READOUT

When biased in Geiger mode, the SiPM produces a photocurrent proportional to the number of microcells that have fired, which provides a measure of the amount of light detected by the sensor. The photocurrent ( $I_{ph}$ ) flows through the sensor from *cathode* to *anode*, as shown in Figure 12, and either of these terminals may be used as the *standard output*.

The *fast output* is a capacitively coupled output derived from the fast switching pulse that occurs within the microcell. Unlike the *standard output* there is no net charge transfer across the *fast output*. The *fast output* amplitude is proportional to the number of microcells that have fired and can therefore provide information on the number of photons detected. The *fast output* is AC coupled and does not provide any DC information.

Figure 12. Photocurrent in the SiPM

Both the *standard* and *fast outputs* can be used alone or together and either can be used for amplitude or timing

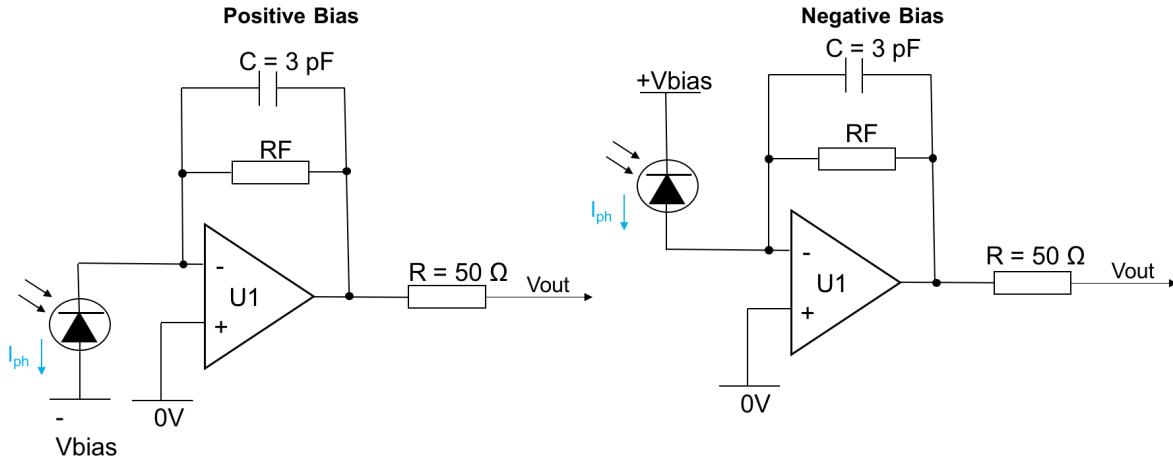

Figure 13. Standard Readout of the SiPM using a TIA (Transimpedance Amplifier)

measurements. Using both outputs simultaneously is possible and this enables measuring of timing and charge via separate circuits.

If the *fast output* is not used it should be left floating without any cables or wires attached. If the *standard output* is not required simply connect the bias supply directly across the SiPM as in Figure 12.

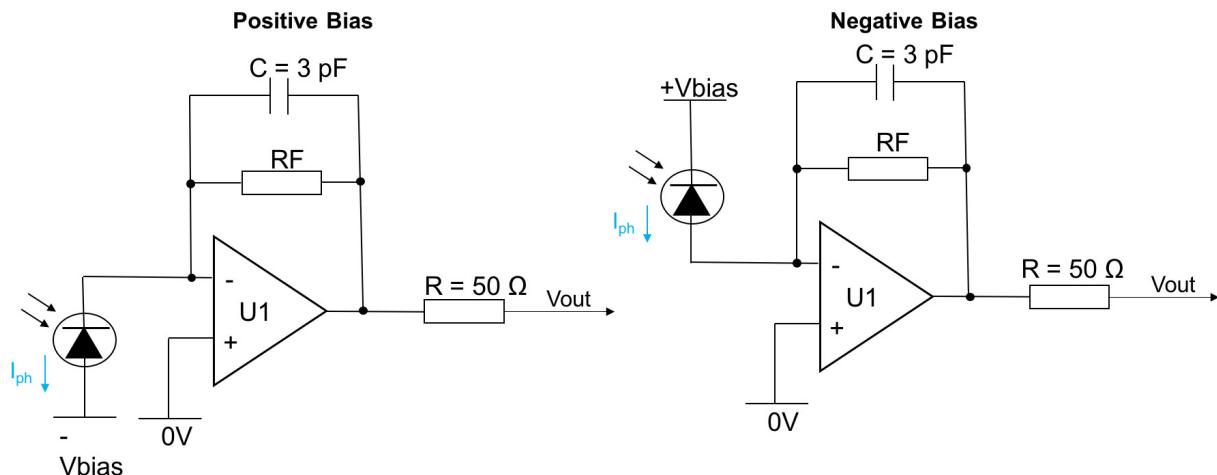

## Standard Output Readout

To read out the SiPM from the *standard output*, the photocurrent generated on detection of photons needs to be converted to a voltage. This can be achieved using a transimpedance amplifier (TIA) as depicted in Figure 13 or using a series resistor as shown in Figure 14. Either *cathode* or *anode* may be used as the *standard output* in both cases.

When detecting low power optical signals, amplification of the *standard output* may be required. When using a TIA the transimpedance gain is equal to the value of the feedback resistor,  $R_F$ .

If a series resistor is used, then the transimpedance gain is set by the series resistor,  $R_S$ .

More than one amplifier stage may be required to provide sufficient gain. A low noise 50 Ω voltage amplifier with a bandwidth of 1 GHz with a gain of 20 dB is suggested.

Example pulses from the *standard output* are given in Figures 16–18.

**Figure 14. Standard Readout using a Sense Resistor with Positive Bias (Left) and Negative Bias (Right).**

Typically,  $R_S = 50 \Omega$  for 1 mm, 3 mm and 4 mm SiPMs and  $10 \Omega$  for 6 mm SiPMs

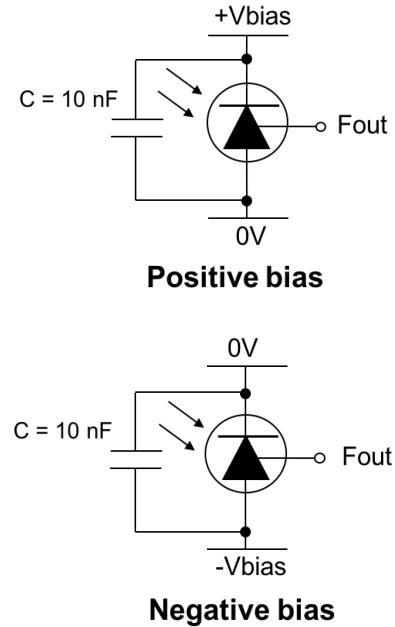

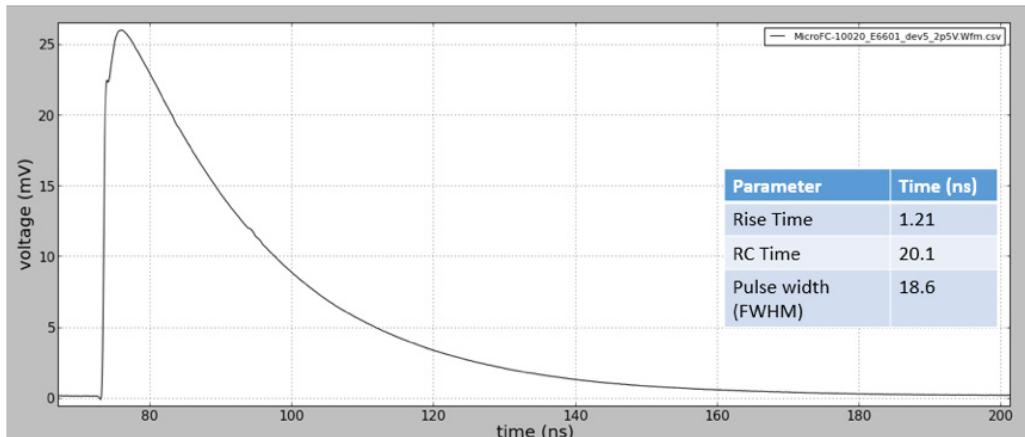

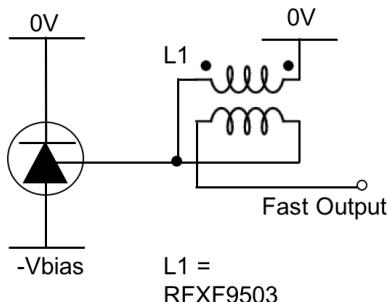

### Fast Output Readout

To read out the *fast output* the SiPM must be correctly biased as per [Biasing of the SiPM](#) section. No sense resistor is required if the *standard output* is not used and this also results in the best microcell recovery time for the SiPM.

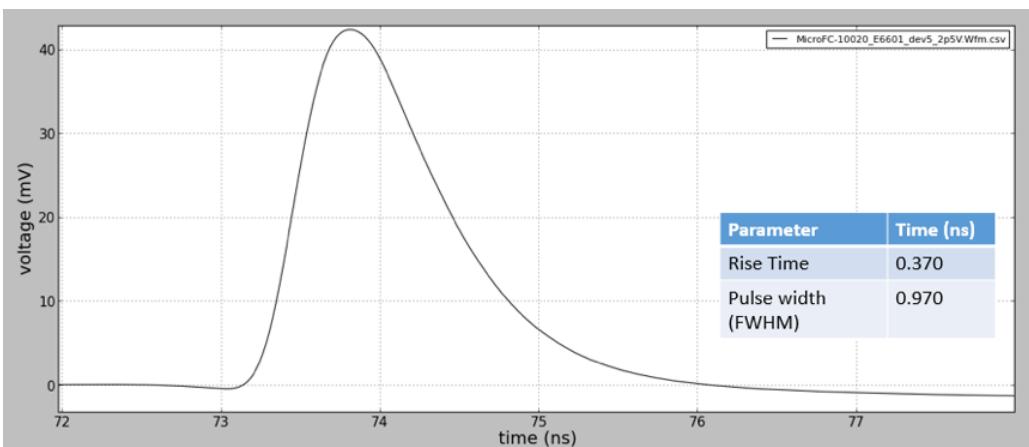

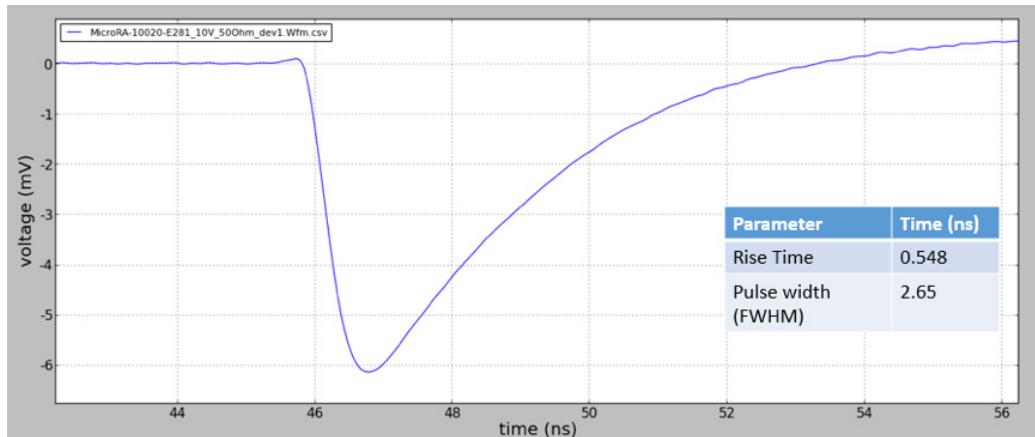

The *fast output* is a voltage pulse that can be read directly into an oscilloscope or digitizer circuit. *Fast output* rise times and pulse widths are of the order 1 ns depending on sensor size. The *fast output* capacitance is much smaller than that of the *standard output* and the values for specific SiPMs can be found in their respective datasheets. Example pulses from the *fast output* are given in Figures 19–20.

Optimal *fast output* performance depends on the sensor type.

- P-on-N sensors are optimally biased with a negative voltage on the *anode*, and the *cathode* (which is the substrate in this case) connected to 0 V.

- For N-on-P sensors a positive bias should be connected to the *cathode* and the *anode* (which is the substrate in this case) should be connected to 0 V.

If the sensor cannot be biased in the optimal way as described above, a 10 nF, 100 V, low ESR decoupling capacitor must be connected between the substrate terminal and 0 V. This provides a high frequency return path to the substrate for the *fast output*, which helps to improve the pulse timing.

For amplification of the *fast output* signal a low noise 50  $\Omega$  RF voltage amplifier with a frequency range up to 1 GHz and a gain of 20 dB is recommended. For example Mini-Circuits ZX60-43S+ or Mini-Circuits ZFL-1000LN+ are regularly used in ON Semiconductor lab. More than one amplifier may be required to provide sufficient gain.

**Figure 15. Fast Output Readout**

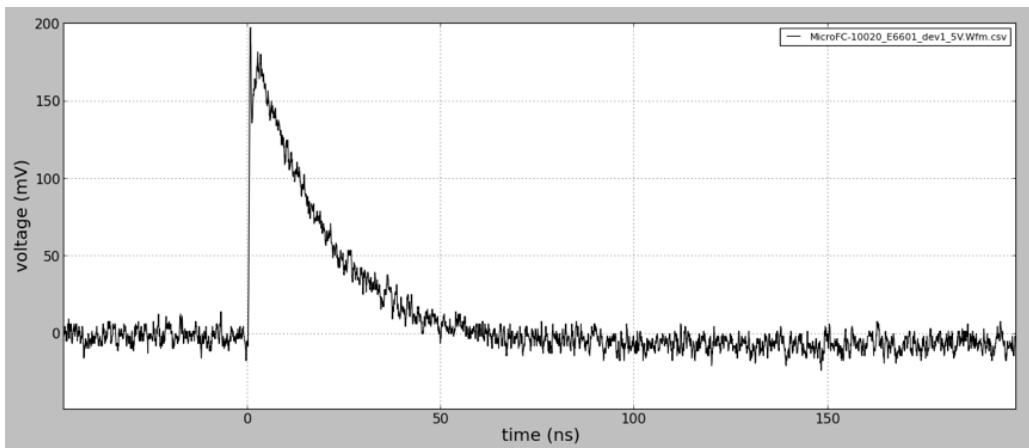

**Figure 16. Pulse Response of MicroFC-10020 to 420 nm Laser with 50 ps Pulse width. Overvoltage = 5 V.**

Scope Input is 50  $\Omega$ . Readout using 50  $\Omega$  Series Resistor on Standard Output. (SMA Board)

## AND9782/D

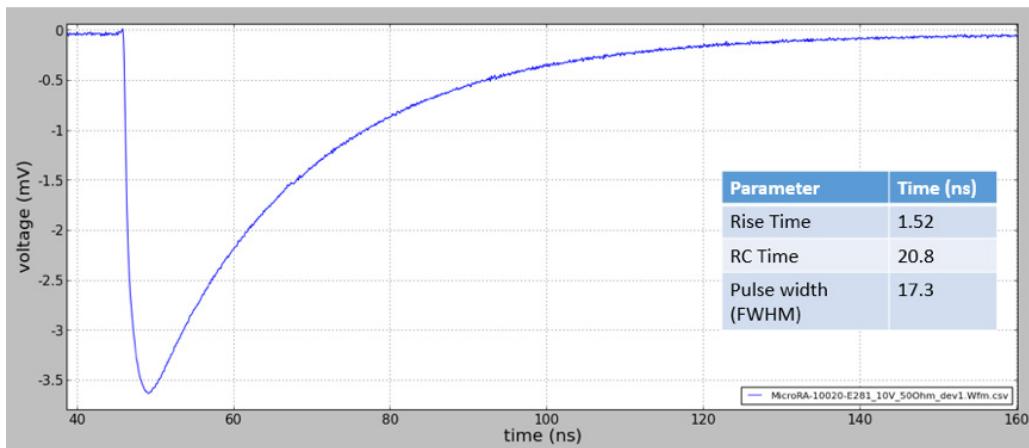

**Figure 17. Pulse Response of MicroRA-10020 to 905 nm Laser with 50 ps Pulse Width. Overvoltage = 10 V. Scope input is 50  $\Omega$ . Readout using 50  $\Omega$  Series Resistor on Standard Output. (SMA Board)**

**Figure 18. MicroFC-10020 Dark Pulse Shape. Readout on Standard Output with 50  $\Omega$  Series Resistor Connected to 2 x ZX60-43S+ Amplifiers in Series. Overvoltage = 5 V**

**Figure 19. Fast Output Pulse Response of MicroFC-10020 to 420 nm Laser with 50 ps Pulse Width. Overvoltage = 5 V. Scope Input is 50  $\Omega$ . Readout with Direct Connection to Oscilloscope**

**Figure 20. Fast Output Pulse Response of MicroRA-10020 to 905 nm Laser with 50 ps Pulse Width.**

Overvoltage = 10 V. Scope Input is 50  $\Omega$ . Readout with Direct Connection to Oscilloscope

## DUAL READOUT CONSIDERATIONS

For dual readout cases, where a TIA is being used to read out the *standard output* there are two instances where a 100 V, low ESR, 100 pF capacitor should be used. See Figure 21. This capacitor provides the high frequency return path for the *fast output* when the SiPM is connected to a virtual ground while not affecting the stability of the TIA.

- For P-on-N structures the capacitor is used when a negative bias is connected to the *anode* and the *cathode* is connected to the virtual ground.

- For N-on-P structures the capacitor is used when the *cathode* is connected to a positive bias and the *anode* is connected to virtual ground.

## ARRAY READOUT

Many applications require the use of multiple sensors in the form of an array, such as the ON Semiconductor Array products. Large arrays can pose a readout challenge due to the many channels of amplification and processing that are required. Therefore, methods of reducing the number of channels are often employed to reduce the readout requirements. Many examples of this can be found in the literature and from specialist suppliers.

Further details can be found in the [Readout Methods for Arrays of Silicon Photomultipliers](#) application note.

**Figure 21. Dual Readout Cases where a 100 pF Capacitor must be Used**

## SERIES RESISTANCE AND MICROCELL RECOVERY TIME

The microcell recovery time is a measure of the time taken for a microcell to return to its normal (ready) state following a detection event and is a function of the total number of microcells, the microcell capacitance and resistance and the series resistance of the circuit.

$$\tau_R = C_{\mu\text{cell}} (R_Q + N \cdot R_S) \quad (\text{eq. 1})$$

Where:

$\tau_R$  = recovery time constant

$C_{\mu\text{cell}}$  = microcell capacitance

$R_Q$  = quench resistance

$N$  = number of microcells in the SiPM

$R_S$  = series resistance

In addition note that the 90% to 10 % microcell recovery time:

$$T_{90\% - 10\%} = 2.2 \tau_R \quad (\text{eq. 2})$$

As can be seen in the equation the series resistance is multiplied by the number of microcells affects the microcell RC time constant. The series resistance includes any parasitic resistances that may be present in the PCB traces on the *cathode* and the *anode*. The series resistance  $R_S$  should be kept as small as possible to optimize the SiPM recovery time. For this reason, it may be necessary to exclude the ON Semiconductor recommended bias filter, particularly for larger SiPMs or for arrays of SiPMs when short recovery time is required.

Please see ON Semiconductor's [Linearity of the Silicon Photomultiplier](#) application note for more details.

## IMPEDANCE MATCHING

Due to the fast rising edge on both *fast* and *standard outputs*, care should be taken in the routing of the signal to maintain good signal integrity. Common microwave/RF design rules, such as controlled impedance microstrip lines, may be used.

When driving an amplifier on a PCB it is recommended to keep the distance between SiPM and amplifier as short as possible to ensure there will not be any reflections along the trace.

**Figure 22. Impedance Matching Circuitry that can be used with 3 mm and 6 mm Sensors when Driving Signals through a Long Trace or Cable**

The ON Semiconductor SMA evaluation board is intended to drive long cables and in this scenario impedance matching is necessary to avoid reflections. The *standard output* is terminated with an appropriate resistor to provide reasonably good impedance matching and good signal performance. The capacitance of the *fast output* is much lower (of the order of 2–3 pF for a 1 mm device) than the *anode-cathode* capacitance. For 1 mm devices the capacitance is low enough to allow direct 50  $\Omega$  connection even through a long cable. Devices larger than 1 mm have higher capacitance and signal integrity will be less optimal in such a scenario. For larger SiPMs ON Semiconductor uses the X9503 balun, which is connected on the SMA board as in Figure 22 to set up a 50  $\Omega$  impedance at the *fast output*. This provides optimal *fast output* pulse amplitude and timing characteristics when used with a 50  $\Omega$  cable and 50  $\Omega$  scope termination. The balun is not required for application specific circuits.

## LAYOUT GUIDELINES

Best practices for PCB design should be followed when creating custom PCBs using ON Semiconductor SiPMs. Attention should be paid to the following items for best performance.

Use power/ground planes to help with providing a low impedance supply to the SiPM. This becomes more important with larger areas of arrays. Decoupling capacitors should be placed as close as possible to the Vbias terminal (*anode* or *cathode*) and amplifiers where used should be placed as close as possible to the signal terminal to maintain good signal integrity.

Power and ground planes also provide parasitic power supply decoupling.

High speed layout techniques should be employed for optimum results, especially when using the *fast output*, which can have a rise time as fast as 300 ps. For best results short, wide, matched impedance traces are recommended to reduce inductance.

It is advisable to consider thermal effects and employ efficient heatsinking to minimize temperature rise due to photocurrent in the SiPM. NC pins in the SiPMs are not electrically connected and connection to a plane is not necessary for signal integrity, however connecting NC pins to a plane helps with heat dissipation by providing a thermal path from the SiPM package to the copper plane.

ON Semiconductor and  are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at [www.onsemi.com/site/pdf/Patent-Marking.pdf](http://www.onsemi.com/site/pdf/Patent-Marking.pdf). ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

**PUBLICATION ORDERING INFORMATION****LITERATURE FULFILLMENT:**

Literature Distribution Center for ON Semiconductor

19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA

**Phone:** 303-675-2175 or 800-344-3860 Toll Free USA/Canada

**Fax:** 303-675-2176 or 800-344-3867 Toll Free USA/Canada

**Email:** [orderlit@onsemi.com](mailto:orderlit@onsemi.com)

**N. American Technical Support:** 800-282-9855 Toll Free

USA/Canada

**Europe, Middle East and Africa Technical Support:**

Phone: 421 33 790 2910

**ON Semiconductor Website:** [www.onsemi.com](http://www.onsemi.com)

**Order Literature:** <http://www.onsemi.com/orderlit>

For additional information, please contact your local

Sales Representative