# AN251216

## Thermal networks of ART LDMOS devices

Rev. 1 — 1 January 2026

AMPEON

Application note

### Document information

| Info            | Content                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Keywords</b> | RC thermal, Models, Foster, Cauer, Zth, Rth, power amplifier                                                                                                                                                                                                                                                                                                                                                                                        |

| <b>Abstract</b> | This application note presents a modeling approach for capturing the thermal behavior of ART LDMOS RF power devices using compact RC networks. Based on an electrical analogy, the method enables efficient prediction of junction temperature and transient thermal response. The extracted models support integration into circuit simulations and system-level thermal analysis, facilitating reliable and thermally optimized RF power designs. |

**Revision history**

| Rev        | Date     | Description      |

|------------|----------|------------------|

| AN251216#1 | 20260101 | Initial version. |

**Contact information**

For more information, please visit: <http://www.ampleon.com>

For sales office addresses, please visit: <http://www.ampleon.com/sales>

## 1. Introduction

The thermal behavior of RF power amplifier devices plays a critical role in ensuring reliable performance and device integrity within their specified safe operating area. Accurate temperature prediction supports both circuit design optimization and system-level thermal management.

A practical approach to modeling thermal performance is to use RC thermal networks, which describe the transient temperature response of a device through an equivalent electrical analogy. These compact models can be implemented using Foster or Cauer representations, both of which reproduce the measured thermal impedance characteristics. They can be directly applied within a SPICE environment or imported into any other electrical simulator for transient or steady-state simulation.

In addition to their use in circuit-level analysis, compact RC thermal networks can be integrated into system-level thermal simulations. This enables customers to incorporate device-level thermal models into their complete assembly stack-ups such as PCBs, heat spreaders, and mechanical enclosures for accurate junction temperature prediction under realistic conditions.

This application note provides an overview of the Foster and Cauer modeling approaches, explains their derivation from measured thermal impedance data, and presents examples of how to apply them in thermal simulations. More detailed guidance on the extraction of the RC parameters from measurement and simulation data can be found in AN221014: Thermal Characteristics of ART LDMOS Power Transistors.

## 2. Thermal impedance

The thermal impedance denoted  $Z_{th}(t)$ , represents the time-dependent temperature response of the device to a power dissipation pulse. It is a key quantity for describing transient thermal behavior and is the basis for deriving the equivalent RC model.

When an RF power transistor is exposed to a continuous power pulse lasting longer than approximately one second, the device reaches thermal equilibrium and the thermal impedance reaches its plateau value, known as the steady-state thermal resistance  $R_{th}$ . This parameter defines the permanent temperature rise per unit power at steady-state operation.

For shorter pulse durations, the temperature rise lags the applied power due to the thermal inertia of materials in the die and package. This delay allows the device to tolerate higher power levels during short bursts without exceeding its thermal limits. The transient thermal impedance  $Z_{th}(t)$  curves therefore provide valuable information on the allowable power levels for various pulse widths and duty cycles.

## 3. Junction temperature rise

To evaluate the junction temperature rise ( $\Delta T_j$ ) of an RF device, both the dissipated power and pulse characteristics must be known. For square power pulses, the temperature rise can be determined directly from the thermal impedance curve by multiplying the peak dissipated power ( $P_{diss}$ ) by the corresponding value of  $Z_{th}(t)$ :

$$\Delta T_j = Z_{th}(t) * P_{diss} \quad (1)$$

For constant or long-duration power, the steady-state thermal resistance  $R_{th}$  is used in place of  $Z_{th}(t)$ .

For complex or arbitrary waveforms, such as modulated or sinusoidal power pulses, the thermal response can be calculated using a convolution integral that accounts for the full temporal variation of power dissipation and the device's transient response. In practice, power profiles are often approximated as a series of rectangular pulses, and the resulting temperature rise is obtained by superposition of their individual effects. This method provides sufficient accuracy for most design evaluations.

## 4. Foster and Cauer RC thermal models

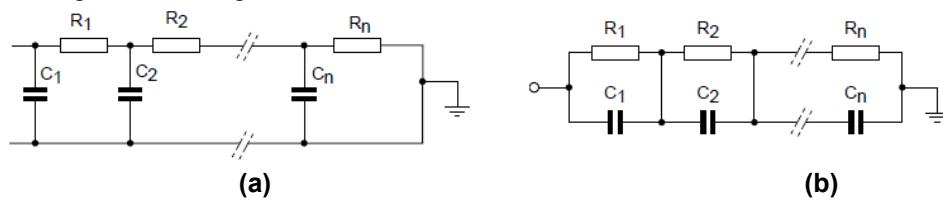

### 4.1 Cauer model

The Cauer model is a ladder network in which thermal capacitances are connected to a common thermal ground corresponding to ambient temperature. This configuration mirrors the physical structure of the device, where each RC pair represents a distinct layer or thermal interface such as the semiconductor die, solder attach, substrate, and package.

As shown in Fig. 1a, the Cauer model provides direct access to internal temperature nodes and can be readily connected to external thermal networks, including system-level models of printed circuit boards or heat sinks. This makes the Cauer model more versatile and physically interpretable than the Foster representation.

### 4.2 Foster model

The Foster model is obtained by fitting the measured  $Z_{th}(t)$  curve with a series of exponential terms, each represented by an RC pair. The resulting network forms a parallel RC chain, as illustrated in Fig. 1b.

Although the Foster representation is mathematically straightforward and convenient for quick analysis, the parameters  $R_i$  and  $C_i$  do not correspond to specific physical locations or material layers within the device. Consequently, Foster models are not suitable for extending or combining with other thermal networks.

Figure 1. (a) Cauer and (b) Foster RC thermal networks

## 5. RC thermal modeling: Example and application

### 5.1 Datasheet thermal information

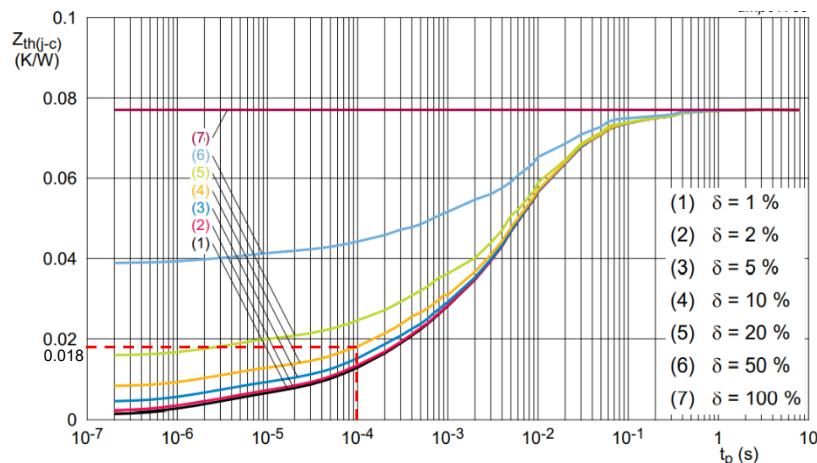

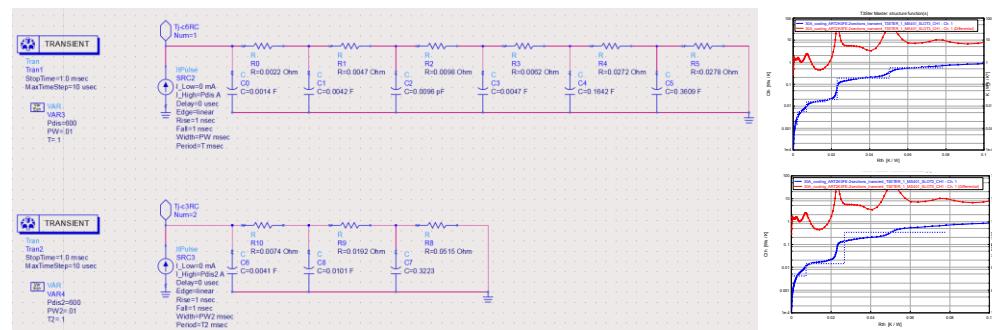

To demonstrate the application of RC thermal modeling, the ART2K0FE LDMOS transistor is used as an example. The device's thermal characteristics, including the thermal resistance between junction and case  $R_{th(j-c)}$  and the transient thermal impedance  $Z_{th(j-c)}$  for specific pulse time and duty cycle, are provided in the product datasheet listed in Table 1. The transient thermal impedance curves covering range of pulse times and duty cycles are also presented in Fig. 2. Based on these data, both Foster and Cauer networks have been extracted and are summarized in the SPICE netlist shown in Fig. 3.

Table 1. Thermal characteristics of ART2K0FE

| Symbol        | Parameter                                         | Conditions                                                            | Typ   | Unit |

|---------------|---------------------------------------------------|-----------------------------------------------------------------------|-------|------|

| $R_{th(j-c)}$ | thermal resistance from junction to case          | $T_j = 95^\circ\text{C}$                                              | 0.077 | K/W  |

| $Z_{th(j-c)}$ | transient thermal impedance from junction to case | $T_j = 95^\circ\text{C}$ ; $t_p = 100\ \mu\text{s}$ ; $\delta = 10\%$ | 0.018 | K/W  |

Figure 2. Transient thermal impedance from junction to the case as a function of pulse duration and duty cycle for the ART2K0FE

|                                               |                                               |

|-----------------------------------------------|-----------------------------------------------|

| * Stages= 6                                   | * Stages= 6                                   |

| * Rth junction-to-case= 0.077 K/W             | * Rth junction-to-case= 0.077 K/W             |

| * R2= 0.999424 Max. difference= 0.0012585 K/W | * R2= 0.999424 Max. difference= 0.0012585 K/W |

| *****                                         | *****                                         |

| .SUBCKT FOSTER 1 7                            | .SUBCKT CAUER 1 7                             |

| C0 1 2 0.00200                                | C0 1 0 0.00140                                |

| R0 1 2 0.00117                                | R0 1 2 0.00229                                |

| C1 2 3 0.01557                                | C1 2 0 0.00428                                |

| R1 2 3 0.00092                                | R1 2 3 0.00470                                |

| C2 3 4 0.01286                                | C2 3 0 0.00969                                |

| R2 3 4 0.00157                                | R2 3 4 0.00986                                |

| C3 4 5 0.01514                                | C3 4 0 0.00479                                |

| R3 4 5 0.01603                                | R3 4 5 0.00629                                |

| C4 5 6 0.30527                                | C4 5 0 0.16421                                |

| R4 5 6 0.00961                                | R4 5 6 0.02725                                |

| C5 6 7 0.35357                                | C5 6 0 0.36094                                |

| R5 6 7 0.04894                                | R5 6 7 0.02784                                |

| .ENDS FOSTER                                  | .ENDS CAUER                                   |

Figure 3. ART2K0FE Foster and Cauer model netlist

## 5.2 Temperature rise calculation

As an example of how to determine the junction temperature rise during pulsed operation, the transient thermal impedance curve provided in the device datasheet can be used. For a pulse width of 100  $\mu\text{s}$  and a 10% duty cycle, the curve indicates a

junction-to-case transient thermal impedance of approximately  $Z_{th(j-c)}$  (100  $\mu$ s, 10%)  $\approx$  0.018  $K/W$ . With a peak power dissipation of  $P_{diss} = 800$  W, the resulting junction temperature rise during each RF pulse is calculated as:

$$\Delta T_{j-c} = Z_{th(j-c)} * P_{diss} = 0.018 \frac{K}{W} * 800W = 14.4 K \quad (2)$$

Therefore, with an assumed case temperature  $T_c = 85$  °C, the junction temperature under pulsed operation becomes:

$$T_j = T_c + \Delta T_{j-c} = 85 \text{ } ^\circ\text{C} + 14.4 \text{ } ^\circ\text{C} = 99.4 \text{ } ^\circ\text{C} \quad (3)$$

The case temperature represents the maximum temperature at the backside of the device flange, theoretically corresponding to the highest solder temperature between the transistor and the heatsink.

For long-duration or continuous-wave (CW) operation, the steady-state junction-to-case thermal resistance  $R_{th(j-c)}$  must be used instead of the transient impedance. Using the datasheet value  $R_{th(j-c)} = 0.077$   $K/W$  and an average power dissipation  $P_{diss} = 440$  W, the steady-state junction temperature rise is:

$$\Delta T_{j-c} = R_{th(j-c)} * P_{diss} = 0.077 \frac{K}{W} * 440W = 33.9 K \quad (4)$$

Therefore, at  $T_c = 85$  °C, the steady-state CW junction temperature is:

$$T_j = T_c + \Delta T_{j-c} = 85 \text{ } ^\circ\text{C} + 33.9 \text{ } ^\circ\text{C} = 118.9 \text{ } ^\circ\text{C} \quad (5)$$

### 5.3 Simulation in electrical platform

These RC networks reproduce the measured transient thermal impedance behavior of the device and can be used in thermal-only simulations to estimate junction temperature rise in response to transient power dissipation. In such simulations, the network can be excited by a time-varying power waveform, and the resulting voltage at the junction node ( $T_j$ ) reflects the temperature increase above ambient. The internal Cauer model uses Pin 1 as the junction temperature node, and Pins 6 and 7 as ambient reference points. For simple test conditions, both ambient pins may be tied to a constant voltage source representing a fixed ambient temperature ( $T_{amb}$ ).

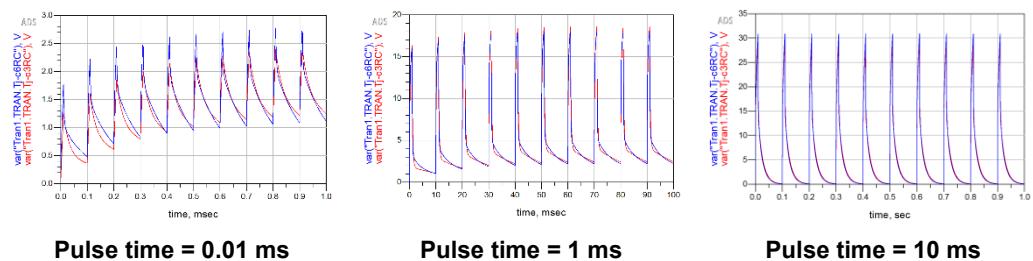

As a practical example, the RC thermal model of the ART2K0FE device has been implemented and simulated in Keysight ADS or other SPICE-compatible tools, as shown in Fig. 4 for Keysight ADS. In this setup, two versions of the Cauer network, one with three stages and one with six stages, were modeled and driven with a pulsed power waveform under different pulse durations. The simulation evaluates the transient junction temperature rise over time for a fixed duty cycle of 10%. The results in Fig. 5. illustrate the effectiveness of using the RC thermal network in transient thermal simulations, with temperature waveforms generated for pulse widths ranging from 0.01 ms to 10 ms. The simulation captures the thermal accumulation and cooling between pulses, demonstrating how the RC network translates power input into time-dependent temperature behavior. More RC stages better predict the temperature response, particularly for shorter pulse durations where the thermal time constants of different package layers become more influential. This example confirms the applicability of compact thermal models in system-level simulation tools, where they can be used to study dynamic thermal effects under realistic operating conditions.

**Figure 4. ADS modeling of Cauer RC thermal network based on the fitted 6-stage and 3-stage structure function**

**Figure 5. Transient temperature profile of 3-red and 6-blue stages at D=10% for various pulse times**

## 5.4 Extension with external thermal network

When thermal effects beyond the device itself need to be included, such as those from PCB, interface material, or heatsink, the model can be extended by connecting the internal RC network to an external thermal network. In this case, Pin 6 of the internal Cauer model is connected to the first node of the external thermal network representing the system-level thermal stack-up, while Pin 7 remains tied to ambient. The final node of the external thermal network must also be connected to ambient to ensure proper termination of the thermal path. This configuration allows designers to evaluate the combined thermal performance of the device and its operating environment, including the effect of different board materials, copper layouts, and cooling strategies.

## 5.5 Integration into FEM thermal model

In addition to these circuit-based approaches, the RC thermal model can also be embedded in a system-level thermal finite element method (FEM) simulation. In this case, the RC ladder is used to model the die-to-case thermal path and is applied as a compact boundary condition at the mounting interface of the transistor in the FEM model. The dissipated power is applied at this boundary, and the RC network determines the junction temperature rise as a function of time and system-level heat flow. This method eliminates the need for detailed meshing of the die and package structure, significantly reducing simulation time while maintaining fidelity with measured device behavior.

This hybrid approach enables integration of verified device-level thermal performance into complete assembly simulations, allowing accurate prediction of junction temperature in complex thermal environments. For these implementations, the RC parameters are

entered directly into the simulation tool, or imported as a behavioral model script. The junction temperature computed by the compact model can then be monitored for thermal design optimization or reliability assessment.

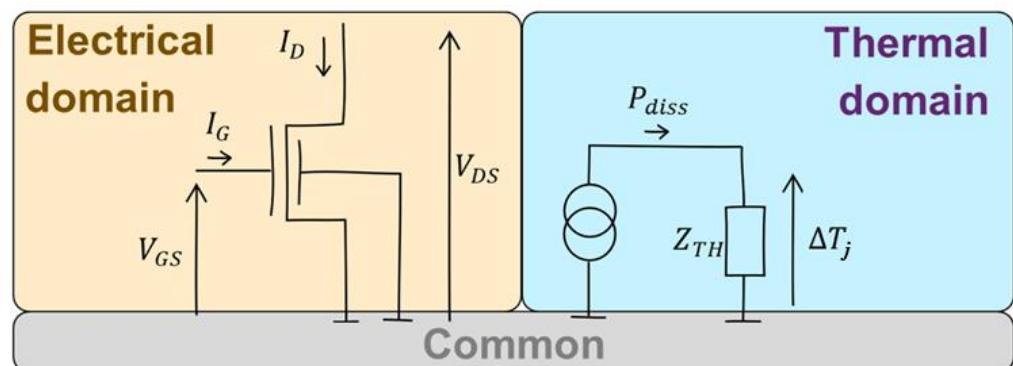

## 5.6 Integration into electro-thermal circuit model

The compact RC thermal model can be integrated into the transistor subcircuit to enable dynamic electro-thermal simulation. In this configuration, the dissipated power is treated as a current that flows into the RC thermal network, and the resulting voltage represents the temperature rise at the junction. This voltage, typically assigned to the node  $T_j$ , is then used to influence temperature-dependent electrical parameters within the model.

The RC network is implemented normally in SPEAR model as a 3<sup>rd</sup> order Foster network, representing the internal thermal path from junction to case. It connects the junction temperature node to ambient through a ladder of resistor and capacitor. It can be extended with additional stages to model external thermal components such as PCBs or heatsinks. For accurate operation, it is essential that the final node of the thermal network is connected to ambient through a defined impedance. Leaving the thermal node floating or incorrectly terminated will result in simulation errors or non-convergence.

This configuration enables the device to respond to its own power dissipation during simulation. Junction temperature rises dynamically as power is applied and feeds back into the electrical model as shown in Fig. 6., allowing realistic simulation of heating effects under modulated signals or pulsed operation. To align with pulsed measurement results, the self-heating coefficient can be adjusted below 1.0 to reflect lower average thermal loading based on duty cycle and pulse time.

Figure 6. Self-heating and thermal impedance in SPEAR device modeling

## 6. Legal information

### 6.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Ampleon does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

### 6.2 Disclaimers

**Limited warranty and liability** — Information in this document is believed to be accurate and reliable. However, Ampleon does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Ampleon takes no responsibility for the content in this document if provided by an information source outside of Ampleon.

In no event shall Ampleon be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Ampleon' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of Ampleon.

**Right to make changes** — Ampleon reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — Ampleon products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Ampleon product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Ampleon and its suppliers accept no liability for inclusion and/or use of Ampleon products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Ampleon makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Ampleon products, and Ampleon accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Ampleon product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Ampleon does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Ampleon products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). Ampleon does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

**Terms and conditions of commercial sale** — Ampleon products are sold subject to the general terms and conditions of commercial sale, as published at <http://www.ampleon.com/terms>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Ampleon hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of Ampleon products by customer.

### Trademarks

Notice: All referenced brands, product names, service names and trademarks are property of their respective owners.

## 7. Contents

|     |                                                     |    |

|-----|-----------------------------------------------------|----|

| 1.  | Introduction .....                                  | 3  |

| 2.  | Thermal impedance.....                              | 3  |

| 3.  | Junction temperature rise .....                     | 3  |

| 4.  | Foster and Cauer RC thermal models .....            | 4  |

| 4.1 | Cauer model.....                                    | 4  |

| 4.2 | Foster model .....                                  | 4  |

| 5.  | RC thermal modeling: Example and application .....  | 4  |

| 5.1 | Datasheet thermal information .....                 | 4  |

| 5.2 | Temperature rise calculation .....                  | 5  |

| 5.3 | Simulation in electrical platform.....              | 6  |

| 5.4 | Extension with external thermal network.....        | 7  |

| 5.5 | Integration into FEM thermal model .....            | 7  |

| 5.6 | Integration into electro-thermal circuit model..... | 8  |

| 6.  | Legal information .....                             | 9  |

| 6.1 | Definitions .....                                   | 9  |

| 6.2 | Disclaimers.....                                    | 9  |

| 6.3 | Trademarks .....                                    | 9  |

| 7.  | Contents.....                                       | 10 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.