# AN13193

## Self-test procedure for FXLS896xAF and FXLS897xCF

Rev. 2.1 — 30 November 2021

Application note

### Document information

| Information | Content                                                                                                                                                                                                                                                                   |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | FXLS8964AF, FXLS8967AF, FXLS8968AF, FXLS8974CF                                                                                                                                                                                                                            |

| Abstract    | This document provides the needed information to deploy a self-test routine for FXLS896xAF and FXLS897xCF in a complete system. This document also discusses an optional procedure to validate the embedded Sensor Data Change Detection (SDCD) function using self-test. |

Table 1. Revision history

| Rev | Date     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1 | 20211130 | <a href="#">Section 9.1</a> , <a href="#">Table 27</a> , revised "178" to "-178" in the "Min" column for " $\pm 16\text{ g}$ mode, Z axis".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

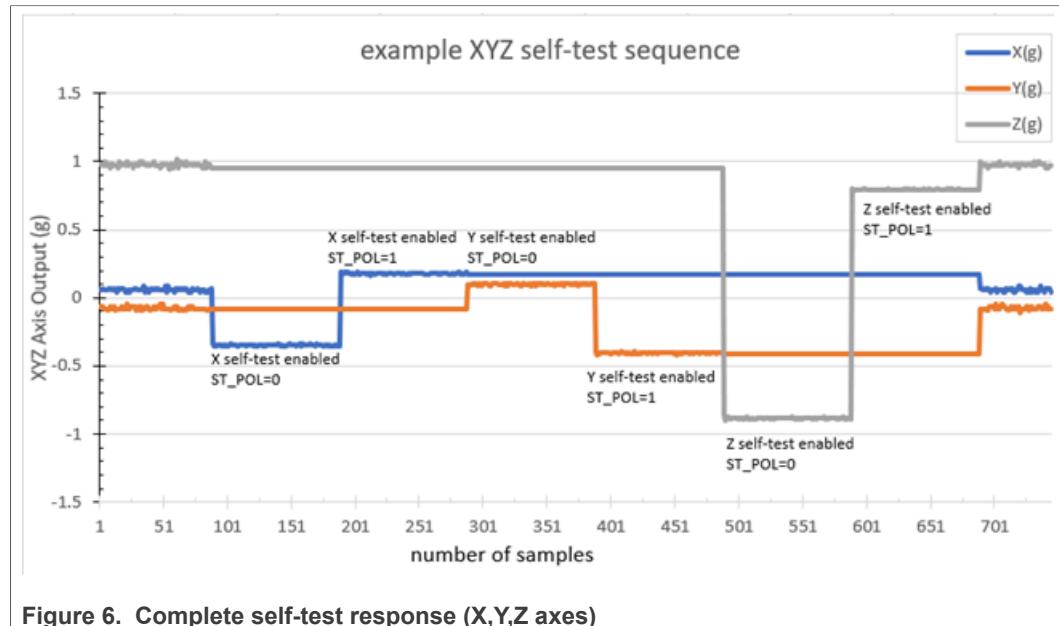

| 2   | 20211019 | <ul style="list-style-type: none"> <li>• <a href="#">Section 4</a>, revised "minimize" to "avoid" in the first sentence of the fifth paragraph.</li> <li>• <a href="#">Section 5</a>, revised "If <math>\text{STOC} &gt; \text{W}</math> LSB, the device passed self-test. The value of 'W' is based on..." to "If <math>\text{LSL} \leq \text{STOC} \leq \text{USL}</math> (Lower Spec Limit in LSB), the device passed self-test. The LSL and USL values are based on..." in the paragraph below the equation.</li> <li>• <a href="#">Section 6.3</a>, revised as follows: <ul style="list-style-type: none"> <li>– Step 6a: revised "If <math>\text{STOC} &gt; \text{W}</math> LSB, the device passed self-test. The value of 'W' is based on..." to "If <math>\text{LSL} \leq \text{STOC} \leq \text{USL}</math> (Upper Spec Limit in LSB), the device passed self-test. LSL and USL values are based on...."</li> <li>– Step 6b: Added "Let <math>\text{W} = \min(\text{abs}(\text{LSL}), \text{abs}(\text{USL}))</math>".</li> <li>– Moved the table titled "Self-test output change limits" to <a href="#">Section 9.1</a> and revised the table to reflect STOC values found in the product data sheet.</li> </ul> </li> <li>• <a href="#">Section 6.4</a>, revised as follows: <ul style="list-style-type: none"> <li>– Step 8a: revised "If <math>\text{STOC} &gt; \text{W}</math> LSB, the device passed self-test. The value of 'W' is based on..." to "If <math>\text{LSL} \leq \text{STOC} \leq \text{USL}</math> (Upper Spec Limit in LSB), the device passed self-test. LSL and USL values are based on...."</li> <li>– Step 8b: Added "Let <math>\text{W} = \min(\text{abs}(\text{LSL}), \text{abs}(\text{USL}))</math>".</li> </ul> </li> <li>• <a href="#">Section 7</a>, added new section.</li> <li>• <a href="#">Section 9.1</a>, revised as follows: <ul style="list-style-type: none"> <li>– Revised "FXLS8962AF" to "FXLS8964AF" in the first paragraph.</li> <li>– Removed table titled "Self-test measurement results for DUT1".</li> <li>– Removed table titled "Self-test measurement results for DUT2".</li> <li>– <a href="#">Table 26</a>, revised the table title, removed the last column titled "Data (g)" and revised the values in the table.</li> <li>– Revised the note "For all axes and for <math>\text{ST\_POL} = 0</math>, the output data is positive only when compared to the self-test offset. The opposite holds true for the <math>\text{ST\_POL} = 1</math> case." to "Refer to the FXLS8964AF data sheet for valid self-test limits."</li> </ul> </li> <li>• <a href="#">Section 9.2</a>, revised as follows: <ul style="list-style-type: none"> <li>– First paragraph: revised "reference output plots for FXLS8962AF..." to "example output X, Y, Z plots for FXLS8964AF...."</li> <li>– Removed the figure titled "Self-test response for X-axis".</li> <li>– Second and Third paragraphs: performed minor grammatical corrections.</li> <li>– Removed the figure titled "Self-test response for Y-axis".</li> <li>– <a href="#">Figure 6</a>: revised the image.</li> </ul> </li> <li>• <a href="#">Section 9.3</a>, revised as follows: <ul style="list-style-type: none"> <li>– Revised "FXLS8962AF" to "FXLS8964AF" in the second paragraph.</li> <li>– <a href="#">Table 28</a>, revised the table values.</li> <li>– Revised the values in Step 2, Calculate Self-test Offset and Self-test output change.</li> <li>– Revised the values in Step 3, Set SDSD thresholds.</li> </ul> </li> </ul> |

| 1   | 20210514 | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## 1 Introduction

The accelerometer self-test feature generates an artificial acceleration signal by deflecting the MEMS transducer proof mass with an electrostatic force. As a consequence, an artificially induced acceleration is measured at the device output indicating proper operation of both MEMS transducer and ASIC signal chain.

The main objective of this document is to provide the user all the information needed to deploy a self-test routine for FXLS896xAF and FXLS897xCF in a complete system. Such a procedure can be readily implemented in the host MCU handling the sensor and executed when appropriate. An appropriate execution time might be at system power-up prior to sensor initialization.

## 2 Applicable devices

This document applies to FXLS896xAF and FXLS897xCF devices with PROD\_REV register value equal to 13h or 14h.

The PROD\_REV register contains the revision number, stored in BCD format, as MAJ.MIN with a range from 1.0 to 9.9. Refer to the respective device data sheet for more details on the PROD\_REV product revision register.

## 3 Accelerometer and self-test principle

The FXLS896xAF/FXLS897xCF 3-axis inertial sensors measure acceleration through its inertial proof mass inside the MEMS transducer. When the device undergoes acceleration, the movement of the proof mass equates to a slight change in capacitance that is translated into a voltage and digitized inside the sensor mixed-signal chain.

In order to check the operation of the sensor (transducer and signal chain) without any applied acceleration, a self-test function is executed. The self-test function applies a voltage to the MEMS transducer electrodes, creating an electrostatic force that deflects the proof mass and causes an output response similar to a response seen during acceleration. The application of the self-test electrostatic force can be viewed as a step input, with the inertial proof mass following a first order response curve and settling to a final value after a finite amount of time (settling time).

The self-test procedure is performed in two steps for each axis. The two-step process moves the proof mass in a positive, then negative direction, which allows higher sensitivity and removes any constant acceleration or sensor offsets.

The device is not required to be at rest during the test sequence and may also be arbitrarily oriented. It is important to check that the output data registers do not become saturated at the maximum positive or negative value to ensure clipping is not occurring. Thus, during self-test, a higher full-scale range ( $\pm 4$  g or higher) is selected to ensure proper results.

## 4 Self-test procedure

The self-test procedure relies on a serial communication interface between the sensor and a host MCU. The serial bus can be I<sup>2</sup>C or SPI, as FXLS896xAF and FXLS897xCF support both types. In addition to the serial interface, an interrupt line is required between the host MCU and the sensor.

In order to activate the FXLS896xAF/FXLS897xCF self-test feature, the SENS\_CONFIG1 register is accessed and programmed (address 15h). The SENS\_CONFIG1 full content description and bit fields details are shown in the data sheet.

A full-scale measurement range of  $\pm 4$  g or higher is recommended for self-test. Note that in  $\pm 16$  g mode, 1 g corresponds to 128 LSBs, or equivalently, 1 LSB  $\approx 7.81$  mg, in  $\pm 8$  g mode, 1 g corresponds to 256 LSBs, or equivalently, 1 LSB  $\approx 3.91$  mg and in  $\pm 4$  g mode, 1 g corresponds to 512 LSBs, or equivalently, 1 LSB  $\approx 1.95$  mg.

The default output data rate (ODR) for self-test is 3200 Hz (this *out-of-reset* value can be subsequently changed by use of the SELF\_TEST\_CONFIG2 register). For more details, see [Section 4.1.4 "SELF\\_TEST\\_CONFIG2 - self-test configuration register 2 \(address 38h\)"](#). The self-test procedure detailed in this document uses an ODR of 100 Hz, which is realized by programming the SELF\_TEST\_CONFIG2 register with a value of 05h.

NXP recommends users avoid communication traffic on the device serial interface during the measurement phase of the sensor in order to reduce the susceptibility of the self-test response signal to induced noise. The most effective way to prevent induced noise during self-test is to employ data ready interrupts to synchronize the collection of data over serial interface and ensure digital communications do not coincide with the measurement phase of the self-test sequence.

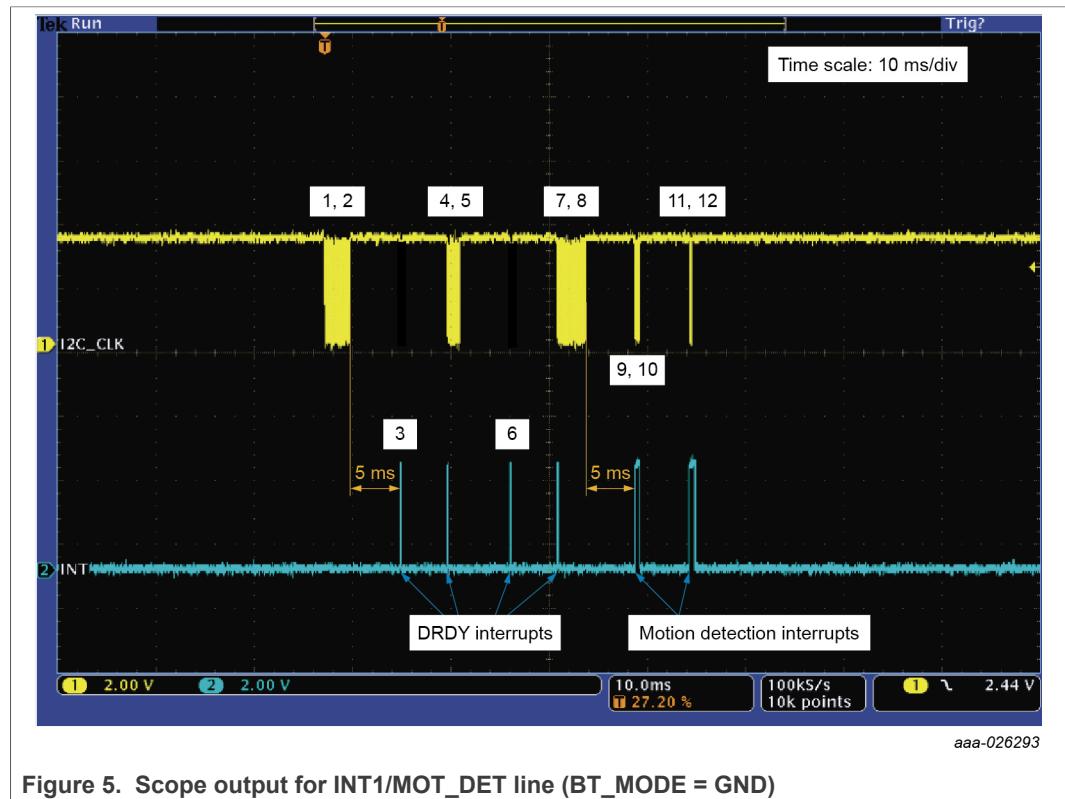

When the BT\_MODE pin is connected to V<sub>DD</sub>, the data ready interrupt is signaled for TPULSE-MOT seconds (5 ms typ) and then is automatically cleared. As a result, the maximum recommended self-test ODR when the BT\_MODE pin is connected to V<sub>DD</sub> is 100 Hz.

When BT\_MODE pin is connected to GND, the data ready interrupt clears immediately after reading the data. Therefore, self-test ODR can be configured up to 3200 Hz.

**Note:** *Only one axis can be tested at a time during self-test mode, because the signal chain processes only the selected axis. This is an important difference from normal operation, where all three axes are processed sequentially during a measurement cycle.*

After reviewing [Section 4 "Self-test procedure"](#), see [Section 9](#) for example results.

## 4.1 Register used in the self-test procedure

For self-test configuration, the user needs to program specific settings in the following registers. Note that after a POR, soft-reset, or exit from Hibernate mode, these settings will be overwritten by the default values as indicated by the register description table in the data sheet.

The following sections summarize the bit fields relevant to the self-test sequence. The data sheet contains the full descriptions of the registers.

Table 2. Key register involved in sensor self-test

| Name              | Address | Access | Comment                                                                           | Accessibility                            |

|-------------------|---------|--------|-----------------------------------------------------------------------------------|------------------------------------------|

| SENS_CONFIG1      | 15h     | R/W    | Full-scale range, self-test control, soft reset, Active mode enable               | Read: always<br>Write: standby mode only |

| SENS_CONFIG4      | 18h     | R/W    | Pulse generation option for DRDY event, output pin logic polarity and driver type | Read: always<br>Write: standby mode only |

| SELF_TEST_CONFIG1 | 37h     | R/W    | Self-test idle phase duration                                                     | Read: always<br>Write: standby mode only |

| SELF_TEST_CONFIG2 | 38h     | R/W    | Self-test measurement phase decimation factor                                     | Read: always<br>Write: standby mode only |

| INT_EN            | 20h     | R/W    | Interrupt output enable register                                                  | Read: always<br>Write: standby mode only |

#### 4.1.1 SENS\_CONFIG1 - sensor configuration register 1 (address 15h)

Table 3. SENS\_CONFIG1 - sensor configuration register 1 (address 15h) bit allocation

| Bit           | 7   | 6                | 5      | 4     | 3        | 2   | 1   | 0      |

|---------------|-----|------------------|--------|-------|----------|-----|-----|--------|

| <b>Name</b>   | RST | ST_AXIS_SEL[1:0] | ST_POL | SPI_M | FSR[1:0] |     |     | ACTIVE |

| <b>Reset</b>  | 0   | 0                | 0      | 0     | 0        | 0   | 0   | 0      |

| <b>Access</b> | R/W | R/W              | R/W    | R/W   | R/W      | R/W | R/W | R/W    |

Register reset value provided above assumes that BT\_MODE = GND.

As this register is thoroughly described in the sensor product data sheet, the following table mainly summarizes the bit fields relevant to the self-test sequence.

Table 4. SENS\_CONFIG1 - sensor configuration register 1 (address 15h) bit description

| Bit    | Name             | Description                                                                                                                                                                                                                                                  |

|--------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6 to 5 | ST_AXIS_SEL[1:0] | Self-test axis selection<br><b>00</b> — self-test function is disabled (reset value)<br><b>01</b> — self-test function is enabled for X-axis<br><b>10</b> — self-test function is enabled for Y-axis<br><b>11</b> — self-test function is enabled for Z-axis |

| 4      | ST_POL           | Self-test displacement polarity<br><b>0</b> — Proof mass displacement for the selected axis is in the positive direction (reset value)<br><b>1</b> — Proof mass displacement for the selected axis is in the negative direction                              |

Table 4. SENS\_CONFIG1 - sensor configuration register 1 (address 15h) bit description...continued

| Bit    | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3      | SPI_M    | <p>SPI interface mode selection; selects between 3- and 4-wire operating modes for the SPI interface:</p> <p><b>0</b> — 4-wire interface mode is selected (reset value)</p> <p><b>1</b> — 3-wire interface mode is selected</p> <p><b>Notes:</b></p> <ul style="list-style-type: none"> <li><i>The state of this bit is only relevant when the SPI interface mode is selected (INTF_SEL = V<sub>DD</sub>).</i></li> <li><i>When INTF_SEL = V<sub>DD</sub> and SPI_M = 1, the SDA/SPI_MOSI pin becomes the bidirectional SPI_DATA pin; the SA0/MISO pin is unused and placed in a high-impedance state.</i></li> <li><i>4-wire mode is selected by default after a POR/BOR event or when exiting Hibernate mode.</i></li> <li><i>If INTF_SEL = V<sub>DD</sub> and the SPI_MOSI and SPI_MISO lines are directly connected together on the PCB, 3-wire SPI mode is enabled regardless of the setting of this bit</i></li> </ul> |

| 2 to 1 | FSR[1:0] | <p>Full-scale measurement range (FSR) selection</p> <p><b>00</b> — <math>\pm 2</math> g; 0.98 mg/LSB (1024 LSB/g) nominal sensitivity (reset value)</p> <p><b>01</b> — <math>\pm 4</math> g; 1.95 mg/LSB (512 LSB/g) nominal sensitivity</p> <p><b>10</b> — <math>\pm 8</math> g; 3.91 mg/LSB (256 LSB/g) nominal sensitivity</p> <p><b>11</b> — <math>\pm 16</math> g; 7.81 mg/LSB (128 LSB/g) nominal sensitivity</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0      | ACTIVE   | Standby/Active mode selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### 4.1.2 SENS\_CONFIG4 - sensor configuration register 4 (address 18h)

Table 5. SENS\_CONFIG4 - sensor configuration register 4 (address 18h) bit allocation

| Bit           | 7          | 6            | 5            | 4           | 3        | 2         | 1         | 0       |

|---------------|------------|--------------|--------------|-------------|----------|-----------|-----------|---------|

| <b>Name</b>   | EXT_TRIG_M | WAKE_SDCD_WT | WAKE_SDCD_OT | WAKE_ORIENT | DRDY_PUL | INT2_FUNC | INT_PP_OD | INT_POL |

| <b>Reset</b>  | 0          | 0            | 0            | 0           | 0        | 0         | 0         | 1       |

| <b>Access</b> | R/W        | R/W          | R/W          | R/W         | R/W      | R/W       | R/W       | R/W     |

Table 6. SENS\_CONFIG4 field descriptions

| Bit | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | DRDY_PUL | <p>Pulse generation option for DRDY event</p> <p><b>0</b> — A SRC_DRDY event is output on the INTx pin as an active high or active low signal depending on the polarity setting made in INT_POL. The INTx pin will remain asserted until the host reads any of the OUT_X/Y/Z registers. (reset value)</p> <p><b>1</b> — A 32 <math>\mu</math>s (nominal) duration pulse is output on the configured INTx pin once per ODR cycle. The output pulse is either positive or negative, depending on the INT_POL setting. Note: The pulsed output signal is OR'd with all of the other interrupt events assigned to the INTx pin. Note: In Motion Detection mode (BT_MODE = V<sub>DD</sub>), the state of this bit is ignored and has no effect on device operation.</p> |

Table 6. SENS\_CONFIG4 field descriptions...continued

| Bit | Name      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | INT_PP_OD | <p>INT1 and INT2 pins output driver selection</p> <p><b>0</b> — INTx output pin driver is push-pull type. (reset value)</p> <p><b>1</b> — INTx output pin driver is open-drain/open-source type. An external pull-up/pull-down resistor is required.</p> <p><b>Notes:</b></p> <ul style="list-style-type: none"> <li><i>If a user operation sets INT_PP_OD before issuing a soft reset command, the setting is maintained through the reset sequence (only lost when V<sub>DD</sub> supply is removed or Hibernate mode is enabled).</i></li> <li><i>The INT_PP_OD bit setting is ignored when BT_MODE = V<sub>DD</sub> as the INT1/MOT_DET and INT2/BOOT_OUT output driver type is fixed to open-drain.</i></li> </ul>                                                                                                                                                                                                                                                                                                                                                                          |

| 0   | INT_POL   | <p>Interrupt logic polarity on INT1 and INT2 pins</p> <p>Selects the polarity of the interrupt output signal on the INT1 and INT2 pins.</p> <p><b>0</b> — Active low: interrupt events are signaled with a logical '0' level. If DRDY_PUL=1, a SRC_DRDY event pulse is negative going. The inactive state of the INTx pins is logic '1' (V<sub>DD</sub>).</p> <p><b>1</b> — Active high: interrupt events are signaled with a logical '1' level. If DRDY_PUL=1, a SRC_DRDY event pulse is positive going. The inactive state of the INTx pins is logic '0' (GND). (reset value)</p> <p><b>Notes:</b></p> <ul style="list-style-type: none"> <li><i>If a user operation sets INT_POL before issuing a soft reset command the setting is maintained through the reset sequence (only lost if V<sub>DD</sub> supply is removed or Hibernate mode is enabled).</i></li> <li><i>The INT_POL bit setting is ignored when BT_MODE = V<sub>DD</sub> as the INT1/MOT_DET and INT2/BOOT_OUT interrupt logic polarity is fixed at active low (external pull-up resistor(s) is/are required).</i></li> </ul> |

#### 4.1.3 SELF\_TEST\_CONFIG1 - self-test configuration register 1 (address 37h)

Table 7. SELF\_TEST\_CONFIG1 - self-test configuration register1 (address 37h) bit allocation

| Bit           | 7   | 6   | 5   | 4            | 3   | 2   | 1   | 0   |  |  |

|---------------|-----|-----|-----|--------------|-----|-----|-----|-----|--|--|

| <b>Name</b>   | —   | —   | —   | ST_IDLE[4:0] |     |     |     |     |  |  |

| <b>Reset</b>  | 0   | 0   | 0   | 0            | 0   | 0   | 0   | 0   |  |  |

| <b>Access</b> | R/W | R/W | R/W | R/W          | R/W | R/W | R/W | R/W |  |  |

Table 8. SELF\_TEST\_CONFIG1 (address 37h) bit description

| Bit    | Name         | Description                                                                                                                                                                           |

|--------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 to 0 | ST_IDLE[4:0] | Self-test Idle phase duration: The value contained in ST_IDLE determines the Self-test Idle phase duration per the following equation: ST_IDLE = 312.5 µs + (ST_IDLE[4:0] * 31.25) µs |

#### 4.1.4 SELF\_TEST\_CONFIG2 - self-test configuration register 2 (address 38h)

Table 9. SELF\_TEST\_CONFIG2 - self-test configuration register1 (address 38h) bit allocation

| Bit           | 7   | 6   | 5   | 4   | 3           | 2   | 1   | 0   |  |  |

|---------------|-----|-----|-----|-----|-------------|-----|-----|-----|--|--|

| <b>Name</b>   | —   | —   | —   | —   | ST_DEC[3:0] |     |     |     |  |  |

| <b>Reset</b>  | 0   | 0   | 0   | 0   | 0           | 0   | 0   | 0   |  |  |

| <b>Access</b> | R/W | R/W | R/W | R/W | R/W         | R/W | R/W | R/W |  |  |

Table 10. SELF\_TEST\_CONFIG2 - self-test configuration register1 (address 38h) bit description

| Bit    | Name        | Description                                                                                                                                                                                                                                           |

|--------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3 to 0 | ST_DEC[3:0] | Self-test measurement phase decimation factor This bit field selects the self-test measurement phase decimation factor. The decimation selection ranges from 1 to 4096. The default ST_DEC setting (00h), configures ODR for self-test to be 3200 Hz. |

Table 11. Self-test measurement phase decimation settings

| ST_DEC[3] | ST_DEC[2] | ST_DEC[1] | ST_DEC[0] | Decimation selection<br>(number of samples) | Self-test<br>measurement<br>period<br>(ms) | Self-test<br>ODR <sup>[1]</sup><br>(Hz) |

|-----------|-----------|-----------|-----------|---------------------------------------------|--------------------------------------------|-----------------------------------------|

| 0         | 0         | 0         | 0         | 1                                           | 0.3125                                     | 3200                                    |

| 0         | 0         | 0         | 1         | 2                                           | 0.625                                      | 1600                                    |

| 0         | 0         | 1         | 0         | 4                                           | 1.25                                       | 800                                     |

| 0         | 0         | 1         | 1         | 8                                           | 2.5                                        | 400                                     |

| 0         | 1         | 0         | 0         | 16                                          | 5                                          | 200                                     |

| 0         | 1         | 0         | 1         | 32                                          | 10                                         | 100                                     |

| 0         | 1         | 1         | 0         | 64                                          | 20                                         | 50                                      |

| 0         | 1         | 1         | 1         | 128                                         | 40                                         | 25                                      |

| 1         | 0         | 0         | 0         | 256                                         | 80                                         | 12.5                                    |

| 1         | 0         | 0         | 1         | 512                                         | 160                                        | 6.25                                    |

| 1         | 0         | 1         | 0         | 1024                                        | 320                                        | 3.125                                   |

| 1         | 0         | 1         | 1         | 2048                                        | 640                                        | 1.56125                                 |

| 1         | 1         | 0         | 0         | 4096                                        | 1280                                       | 0.78125                                 |

| 1         | 1         | 0         | 1         | 4096                                        | 1280                                       | 0.78125                                 |

| 1         | 1         | 1         | 0         | 4096                                        | 1280                                       | 0.78125                                 |

| 1         | 1         | 1         | 1         | 4096                                        | 1280                                       | 0.78125                                 |

[1] The ST recurrence and period shown in this table correspond to ST\_IDLE = 0. Otherwise, the formula provided in note 1 shall be used.

**Notes:**

1. During the self-test sequence, the accelerometer measurement period in  $\mu$ s (for each axis and each direction) is given by the following equation:

$$ST\_PERIOD (\mu\text{s}) = 2^{ST\_DEC[3:0]} * [312.5 + (ST\_IDLE[4:0] * 31.25)] \mu\text{s}$$

2. The user-selected ODR in SENS\_CONFIG3 register and power mode settings are ignored during self-test operation. The user-selected settings for ODR and power mode are applied after self-test is disengaged, for example, ST\_AXIS\_SEL[1:0] = 0b00.

**4.1.5 INT\_EN - interrupt output enable register (address 20h)**

This register is used to enable and disable the various interrupt event generators embedded within the device.

**Table 12. INT\_EN - interrupt output enable register (address 20h) bit allocation**

| Bit                                     | 7       | 6      | 5          | 4          | 3         | 2       | 1        | 0           |

|-----------------------------------------|---------|--------|------------|------------|-----------|---------|----------|-------------|

| <b>Name</b>                             | DRDY_EN | BUF_EN | SDCD_OT_EN | SDCD_WT_EN | ORIENT_EN | ASLP_EN | BOOT_DIS | WAKE_OUT_EN |

| <b>Reset (BT_MODE = GND)</b>            | 0       | 0      | 0          | 0          | 0         | 0       | 0        | 0           |

| <b>Reset (BT_MODE = V<sub>DD</sub>)</b> | 0       | 0      | 1          | 0          | 0         | 0       | 0        | 0           |

| <b>Access</b>                           | R/W     | R/W    | R/W        | R/W        | R/W       | R/W     | R/W      | R/W         |

**Table 13. INT\_EN - interrupt output enable register (address 20h) bit description**

| Bit | Name       | Description                                                                                                                                                                                                                   |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DRDY_EN    | Data ready interrupt output enable<br><b>0</b> — Interrupt is disabled (reset value)<br><b>1</b> — Interrupt is enabled and signaled on either the INT1 or INT2 output pins as configured by the setting made in INT_PIN_SEL  |

| 5   | SDCD_OT_EN | SDCD outside of thresholds interrupt output enable<br><b>0</b> — Interrupt is disabled (reset value)<br><b>1</b> — Interrupt is routed to either the INT1 or INT2 output pin as configured by the setting made in INT_PIN_SEL |

**4.1.6 Output data validity**

Since the self-test output response takes time to settle to a final value after placing the device in ACTIVE mode, the following factors must be considered while collecting response data.

**Table 14. Valid output sample considerations***After placing the device in ACTIVE mode*

| Setting |                                                  | Valid sample number/ data ready interrupt |

|---------|--------------------------------------------------|-------------------------------------------|

| ST_IDLE | ST_DEC                                           |                                           |

| 00h     | 0 (self-test ODR = 3200 Hz)                      | fourth sample and later                   |

| 00h     | 1 (self-test ODR = 1600 Hz)                      | third sample and later                    |

| 00h     | 1 < ST_DEC < 5 (200 Hz ≤ self-test ODR ≤ 800 Hz) | second sample and later                   |

| 00h     | ST_DEC ≥ 5 (self-test ODR ≤ 100 Hz)              | first sample and later                    |

## 5 Self-test sequence per axis

1. Enter Standby mode by setting **SENS\_CONFIG1[ACTIVE]** to 0 (address 15h)

2. Set the self-test measurement phase decimation factor **SELF\_TEST\_CONFIG2[ST\_DEC]** to 05h (address 38h). In this procedure, Self-test ODR is set to 100 Hz.

**Note:** Complete step [3](#) through step [9](#) for each axis (i = X, Y, Z).

3. When **BT\_MODE** = **V<sub>DD</sub>**, enable data ready interrupt by setting **INT\_EN[DRDY\_EN]** bit to 1. Interrupt is routed to INT1 line. INT2 line cannot be used, because only BOOT interrupt can be routed to INT2 line when BT\_MODE = **V<sub>DD</sub>**.

When **BT\_MODE** = **GND**, enable data ready interrupt by setting **INT\_EN[DRDY\_EN]** bit to 1. Interrupt is routed to INT1 line. INT2 line can also be used. Enable pulse generation option for the DRDY event by setting **SENS\_CONFIG4[DRDY\_PUL]** bit to 1.

4. Write **SENS\_CONFIG1** register (address 15h) with the following content

- Enable self-test on the desired axis by setting **ST\_AXIS\_SEL[1:0]** to 0b01 for X-axis, 0b10 for Y-axis or 0b11 for Z-axis

- Select self-test positive polarity by setting **ST\_POL** to 0

- Select FSR measurement range. In this example ±16 g range is selected by setting **FSR[1:0]** to 0b11

- Select Active mode by setting **ACTIVE** to 1

5. Wait for DRDY interrupt. Upon reception of first data ready interrupt, enter Standby mode by setting **SENS\_CONFIG1[ACTIVE]** to 0. For valid samples/data ready interrupt for each self-test ODR, see [Table 14](#).

6. Read the acceleration data in the output registers corresponding to the selected axis (X data at register addresses 04h and 05h, Y data at register addresses 06h and 07h, Z data at register addresses 08h and 09h). Store the output data as a temporary variable, such as **ST\_OUTp(i)**.

7. Write **SENS\_CONFIG1** register (address 15h) with the following content:

- Enable self-test on the desired axis by setting **ST\_AXIS\_SEL[1:0]** to 0b01 for X-axis, 0b10 for Y-axis or 0b11 for Z-axis

- Select self-test negative polarity by setting **ST\_POL** to 1

- Select Active mode by setting **ACTIVE** to 1

8. Wait for DRDY interrupt. Upon reception of first data ready interrupt, enter Standby mode by setting **SENS\_CONFIG1[ACTIVE]** to 0. For valid samples/data ready interrupt for each self-test ODR, see [Table 14](#).

9. Read the acceleration data in the output registers corresponding to the selected axis (X data at register addresses 04h and 05h, Y data at register addresses 06h and

07h, Z data at register addresses 08h and 09h). Store the output data as a temporary variable, such as `ST_OUTm(i)`.

#### Self-test measurement phase per axis

Complete the following steps [List item](#) through step [List item](#) for each axis (i = X,Y,Z).

Assuming there was no output data clipping, such as the maximum positive value not equal to +2047 and maximum negative value not equal to -2048, the self-test output change (STOC) for each axis can be computed with the following equation:

$$STOC(i) = \frac{ST\_OUTp(i) - ST\_OUTm(i)}{2}$$

The `STOC(i)` value can be compared to the data sheet specification for a given axis and FSR g range. If  $LSL \leq STOC \leq USL$  (Lower Spec Limit in LSB)  $\leq$  STOC  $\leq$  Upper Spec Limit in LSB), the device passed self-test. The LSL and USL values are based on the FSR range and axis under test (X or Y or Z). See [Table 27](#)

As mentioned in the measurement procedure, it is important that the host MCU collects measurement data only in interrupt mode. Interrupt mode is enabled using the `INT_EN` (address 20h) and `INT_PIN_SEL` (address 21h) registers.

Map the data ready interrupt to one of the `INTx` pins available on the device and wait for the event to be signaled to the host MCU before reading data. See `DRDY_EN` field of the `INT_EN` register (address 20h) and `DRDY_INT2` field of the `INT_PIN_SEL` register (address 21h). In that case, sensor data collection is handled very effectively by the host MCU with an interrupt service routine. In the case of `BT_MODE = VDD` (motion detect mode), `INT2` pin function is reserved for boot output pulse, thus is not available for this purpose. Consequently, only `INT1` pin can be used.

The user-selected ODR and power mode are overridden during self-test operation. They are restored when self-test is disengaged, such as when `ST_AXIS_SEL[1:0] = 0b00` and `ACTIVE` is set back again to 1.

## 6 Sensor Data Change Detection (SDCD) block validation through self-test

Besides basic verification of MEMS transducer and ASIC signal chain, the self-test feature can also be utilized to verify some of the embedded features of the sensor. This section describes how to verify the SDCD block in the ASIC through self-test.

After reviewing [Section 6 "Sensor Data Change Detection \(SDCD\) block validation through self-test"](#), see [Section 9.3 "Example implementation for SDCD block validation"](#)

### 6.1 SDCD block validation principle

The Sensor Data Change Detection (SDCD) block is an inertial event detection function available to assist host software algorithms in detecting various inertial events such as motion/no-motion (key fob), high-g/low-g, tap/double tap and transient acceleration events.

It incorporates a flexible digital window comparator block useful for implementing several different interrupt generation functions. The circuit may be operated in either relative or

absolute modes and features user-programmable debounce times, polarity detection and interrupt generation logic.

Since **self-test response is an inertial event caused by an electrostatic actuation force applied to the proof mass**, this event can be detected by the SDCD block as a motion event. The generation of a motion detection interrupt in response to self-test stimulus verifies proper operation of the SDCD block. It is also to be noted that, indirectly, the interrupt capabilities of the sensor are also being validated.

The device's response to a self-test stimulus on a specific axis and polarity (direction) is a DC signal that does not vary with any physical acceleration applied to the device. Thus, the device need not be static while executing self test.

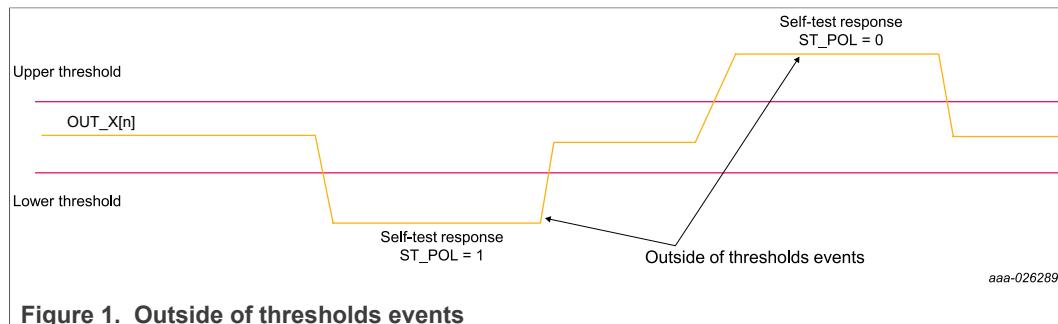

When this response signal is used as an input to the SDCD block in absolute comparison mode against a defined threshold (as shown in [Figure 1](#)), this inertial event caused by the self-test stimulus is detected as an Outside-of Thresholds (OT) event, when the magnitude of the response signal is greater than the threshold. A corresponding motion detection interrupt will also be triggered for the event.

**Figure 1. Outside of thresholds events**

## 6.2 Registers used in the SDCD block validation procedure

Apart from the registers configured for self test ([Section 4.1](#)), the following SDCD registers require configuration.

**Table 15. SDCD registers requiring configuration**

| Name          | Address | Access | Comment                                                                                                                                                                                                            | Accessibility                                                                            |

|---------------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| SDCD_CONFIG1  | 2Fh     | R/W    | Sensor Data Change Detection function configuration register 1 – Event latch enable and individual axis enable bits for OT and WT logic function participation.                                                    | Read: always<br>Write: standby mode only                                                 |

| SDCD_CONFIG2  | 30h     | R/W    | Sensor Data Change Detection function configuration register 2 – SDCD function enable, reference values initialization and update behavior, relative/absolute operating mode selection, debounce counter behavior. | Read: always<br>Write (REF_UPD bit): always<br>Write (all other bits): standby mode only |

| SDCD_LTHS_LSB | 33h     | R/W    | Sensor Data Change Detection lower threshold value LSB - sdcld_lths[7:0]                                                                                                                                           | Read: always<br>Write: standby mode only                                                 |

**Table 15. SDCD registers requiring configuration...continued**

| Name          | Address | Access | Comment                                                                    | Accessibility                            |

|---------------|---------|--------|----------------------------------------------------------------------------|------------------------------------------|

| SDCD_LTHS_MSB | 34h     | R/W    | Sensor Data Change Detection lower threshold value MSB - sdcld_lths[11:8]. | Read: always<br>Write: standby mode only |

| SDCD_UTHS_LSB | 35h     | R/W    | Sensor Data Change Detection upper threshold value LSB - sdcld_uths[7:0]   | Read: always<br>Write: standby mode only |

| SDCD_UTHS_MSB | 36h     | R/W    | Sensor Data Change Detection upper threshold value MSB - sdcld_uths[11:8]  | Read: always<br>Write: standby mode only |

| INT_EN        | 20h     | R/W    | Interrupt output enable register                                           | Read: always<br>Write: standby mode only |

As these registers are thoroughly described in the data sheet, the following tables mainly summarize the bit fields relevant to the validation procedure.

### 6.2.1 SDCD\_CONFIG1 - SDCD function configuration register 1 (address 2Fh)

**Table 16. SDCD\_CONFIG1 - SDCD function configuration register 1 (address 2Fh) bit allocation**

| Bit                                     | 7      | 6      | 5       | 4       | 3       | 2       | 1       | 0       |

|-----------------------------------------|--------|--------|---------|---------|---------|---------|---------|---------|

| <b>Name</b>                             | OT_ELE | WT_ELE | X_OT_EN | Y_OT_EN | Z_OT_EN | X_WT_EN | Y_WT_EN | Z_WT_EN |

| <b>Reset (BT_MODE = GND)</b>            | 0      | 0      | 0       | 0       | 0       | 0       | 0       | 0       |

| <b>Reset (BT_MODE = V<sub>DD</sub>)</b> | 0      | 0      | 1       | 1       | 1       | 0       | 0       | 0       |

| <b>Access</b>                           | R/W    | R/W    | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

**Table 17. SDCD\_CONFIG1 - SDCD function configuration register 1 (address 2Fh) bit description**

| Bit | Name    | Description                                                                                                                                                                                                                          |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | X_OT_EN | SDCD function X-axis outside-of-thresholds condition<br>0: X-axis data or delta is not used in the outside of thresholds condition evaluation.<br>1: X-axis data or delta is used in the outside of thresholds condition evaluation. |

| 4   | Y_OT_EN | SDCD function Y-axis outside-of-thresholds condition<br>0: Y-axis data or delta is not used in the outside of thresholds condition evaluation.<br>1: Y-axis data or delta is used in the outside of thresholds condition evaluation. |

| 3   | Z_OT_EN | SDCD function Z-axis outside-of-thresholds condition<br>0: Z-axis data or delta is not used in the outside of thresholds condition evaluation.<br>1: Z-axis data or delta is used in the outside of thresholds condition evaluation. |

### 6.2.2 SDCD\_CONFIG2 - SDCD function configuration register 2 (address 30h)

Table 18. SDCD\_CONFIG2 - SDCD function configuration register 2 (address 30h) bit allocation

| Bit                                     | 7       | 6             | 5   | 4        | 3        | 2          | 1    | 0       |

|-----------------------------------------|---------|---------------|-----|----------|----------|------------|------|---------|

| <b>Read</b>                             | SDCD_EN | REF_UPDM[1:0] |     | OT_DBCTM | WT_DBCTM | WT_LOG_SEL | MODE | REF_UPD |

| <b>Reset (BT_MODE = GND)</b>            | 0       | 0             | 0   | 0        | 0        | 0          | 0    | 0       |

| <b>Reset (BT_MODE = V<sub>DD</sub>)</b> | 1       | 1             | 0   | 1        | 1        | 0          | 0    | 0       |

| <b>Access</b>                           | R/W     | R/W           | R/W | R/W      | R/W      | R/W        | R/W  | R/W     |

Table 19. SDCD\_CONFIG2 - SDCD function configuration register 2 (address 30h) bit description

| Bit    | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | SDCD_EN  | SDCD function<br>0 (default after a POR or soft reset event when BT_MODE = GND): SDCD function is disabled. All clocks and power for the function are turned off.<br>1 (default after a POR or soft reset event when BT_MODE = V <sub>DD</sub> and MOT_DET = 1): SDCD function is enabled. When this bit is set, the 12-bit reference values ( <b>REF_X/Y/Z</b> ) are initialized per the settings made in REF_UPDM[1:0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6 to 5 | REF_UPDM | SDCD internal reference values update mode<br>00: The function stores the first 12-bit X/Y/Z decimated and trimmed input data (OUT_X/Y/Z[n=0]) as the internal REF_X/Y/Z values after the function is enabled (SDCD_EN is set to 1). The REF_X/Y/Z values are updated with the current 12-bit X/Y/Z decimated input data (OUT_X/Y/Z[n]) at the time the SDCD_OT_EA flag transitions from False to True.<br>01: The function stores the first decimated and trimmed X/Y/Z acceleration input data (OUT_X/Y/Z[n=0]) as the internal REF_X/Y/Z values when the SDCD function is enabled; the REF_X/Y/Z values are then held constant and never updated until the SDCD function is disabled and subsequently re-enabled, or asynchronously when the REF_UPD bit is set by the host.<br>10: The function updates the SDCD_REF_X/Y/Z values with the current decimated and trimmed X/Y/Z acceleration input data after the function evaluation. This allows for acceleration slope detection with Data(n) to Data(n-1) always used as the input to the window comparator.<br>11: The function uses a fixed value of 0 for each of the SDCD_REF_X/Y/Z registers, making the function operate in absolute comparison mode. |

| 4      | OT_DBCTM | SDCD outside-of-threshold event debounce counter behavior<br>0 (default): Debounce counter is decremented by 1 when the current outside of thresholds result for the enabled axes is false. In this mode, the debounce counter de-bounces the outside of thresholds event in both directions, meaning that once the event flag has been set (after SDCD_OT_DBCNT ODR periods with the condition true), the condition must also remain false for at least SDCD_OT_DBCNT + 1 consecutive ODR periods before the next event detection cycle can begin.<br>1: Debounce counter is cleared whenever the current outside of thresholds result for the enabled axes is false.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

### 6.2.3 SDCD\_LTHS\_LSB - SDCD lower threshold value register LSB (address 33h)

Sensor Data Change Detection function 12-bit 2's complement lower threshold least significant byte. **SDCD\_LTHS[11:0]** must always be set to a lower value than **SDCD\_UTHS[11:0]** to ensure that the SDCD circuit functions correctly and produces meaningful results.

The scaling for this register is always the same as the selected FSR's sensitivity.

Table 20. SDCD\_LTHS\_LSB - SDCD lower threshold value register LSB (address 33h) bit allocation

| Bit                                     | 7              | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------------------------------------|----------------|-----|-----|-----|-----|-----|-----|-----|

| <b>Name</b>                             | SDCD_LTHS[7:0] |     |     |     |     |     |     |     |

| <b>Reset (BT_MODE = GND)</b>            | 0              | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| <b>Reset (BT_MODE = V<sub>DD</sub>)</b> | 1              | 1   | 0   | 0   | 0   | 0   | 0   | 0   |

| <b>Access</b>                           | R/W            | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

### 6.2.4 SDCD\_LTHS\_MSB - SDCD lower threshold value register MSB (address 34h)

Sensor Data Change Detection function 12-bit 2's complement lower threshold most significant byte (nibble). **SDCD\_LTHS[11:0]** must always be set to a lower value than **SDCD\_UTHS[11:0]** to ensure that the SDCD circuit functions correctly and produces meaningful results.

The scaling for this register is always the same as the selected FSR's sensitivity.

Table 21. SDCD\_LTHS\_MSB - SDCD lower threshold value register MSB (address 34h) bit allocation

| Bit                                     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| <b>Name</b>                             | —   |     |     |     |     |     |     |     |

| <b>Reset (BT_MODE = GND)</b>            | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| <b>Reset (BT_MODE = V<sub>DD</sub>)</b> | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 1   |

| <b>Access</b>                           | R/W |

### 6.2.5 SDCD\_UTHS\_LSB - SDCD upper threshold value LSB (address 35h)

Sensor Data Change Detection function 12-bit 2's complement upper-threshold least significant byte. **SDCD\_UTHS[11:0]** must always be set to a higher value than **SDCD\_LTHS[11:0]** to ensure that the SDCD circuit functions correctly and produces meaningful results.

The scaling for this register is the same as the selected FSR sensitivity.

Table 22. SDCD\_UTHS\_LSB - SDCD upper threshold value LSB (address 35h) bit allocation

| Bit                                     | 7              | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------------------------------------|----------------|-----|-----|-----|-----|-----|-----|-----|

| <b>Name</b>                             | SDCD_UTHS[7:0] |     |     |     |     |     |     |     |

| <b>Reset (BT_MODE = GND)</b>            | 0              | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| <b>Reset (BT_MODE = V<sub>DD</sub>)</b> | 0              | 1   | 0   | 0   | 0   | 0   | 0   | 0   |

| <b>Access</b>                           | R/W            | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

### 6.2.6 SDCD\_UTHS\_MSB - SDCD upper threshold value MSB (address 36h)

Sensor Data Change Detection function 12-bit 2's complement upper-threshold most-significant byte (nibble). **SDCD\_UTHS[11:0]** must always be set to a higher value than **SDCD\_LTHS[11:0]** to ensure that the SDCD circuit functions correctly and produces meaningful results.

The scaling for this register is always the same as the selected FSR's sensitivity.

Table 23. SDCD\_UTHS\_MSB - SDCD upper threshold value MSB (address 36h) bit allocation

| Bit                                     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0               |

|-----------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----------------|

| <b>Name</b>                             | —   |     |     |     |     |     |     | SDCD_UTHS[11:8] |

| <b>Reset (BT_MODE = GND)</b>            | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0               |

| <b>Reset (BT_MODE = V<sub>DD</sub>)</b> | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0               |

| <b>Access</b>                           | R/W             |

### 6.2.7 INT\_EN - interrupt output enable register (address 20h)

This register is used to enable and disable the various interrupt event generators embedded within the device.

Table 24. INT\_EN - interrupt output enable register (address 20h) bit allocation

| Bit                                     | 7       | 6      | 5          | 4          | 3         | 2       | 1        | 0           |

|-----------------------------------------|---------|--------|------------|------------|-----------|---------|----------|-------------|

| <b>Name</b>                             | DRDY_EN | BUF_EN | SDCD_OT_EN | SDCD_WT_EN | ORIENT_EN | ASLP_EN | BOOT_DIS | WAKE_OUT_EN |

| <b>Reset (BT_MODE = GND)</b>            | 0       | 0      | 0          | 0          | 0         | 0       | 0        | 0           |

| <b>Reset (BT_MODE = V<sub>DD</sub>)</b> | 0       | 0      | 1          | 0          | 0         | 0       | 0        | 0           |

| <b>Access</b>                           | R/W     | R/W    | R/W        | R/W        | R/W       | R/W     | R/W      | R/W         |

Table 25. INT\_EN - interrupt output enable register (address 20h) bit description

| Bit | Name       | Description                                                                                                                                                                                                                   |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DRDY_EN    | Data ready interrupt output enable<br><b>0</b> — Interrupt is disabled (reset value)<br><b>1</b> — Interrupt is enabled and signaled on either the INT1 or INT2 output pins as configured by the setting made in INT_PIN_SEL  |

| 5   | SDCD_OT_EN | SDCD outside of thresholds interrupt output enable<br><b>0</b> — Interrupt is disabled (reset value)<br><b>1</b> — Interrupt is routed to either the INT1 or INT2 output pin as configured by the setting made in INT_PIN_SEL |

## 6.3 Self-test sequence for SDCD block validation (BT\_MODE = V<sub>DD</sub>)

### SDCD block validation phase per axis

Complete the following procedure for each axis (i = X, Y, Z).

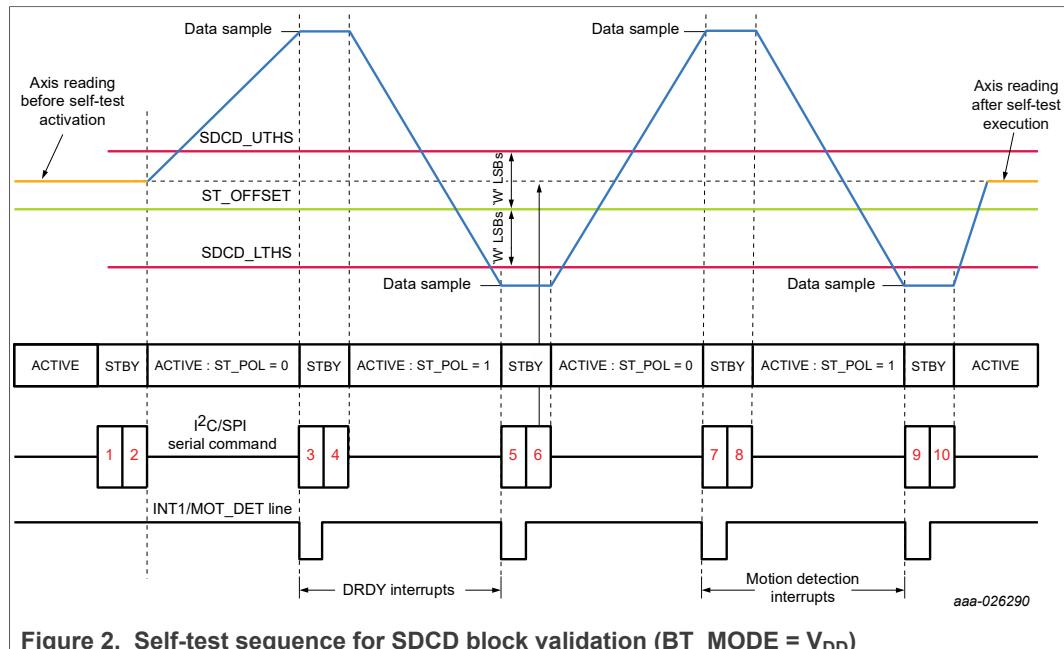

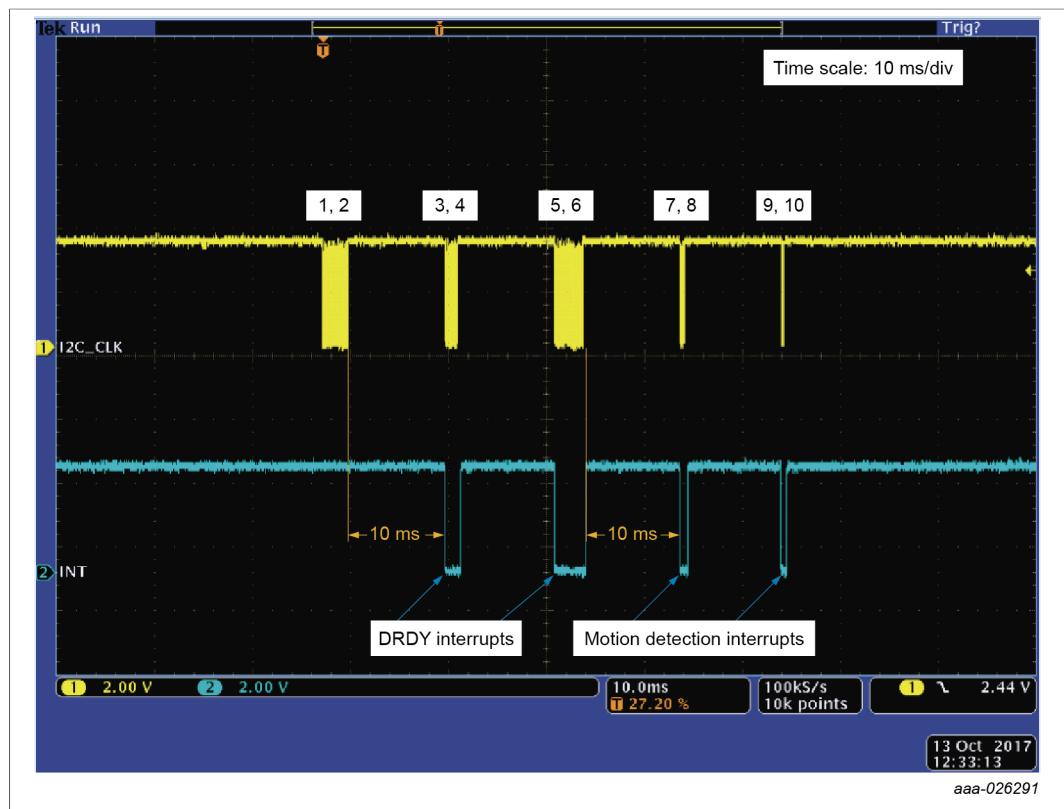

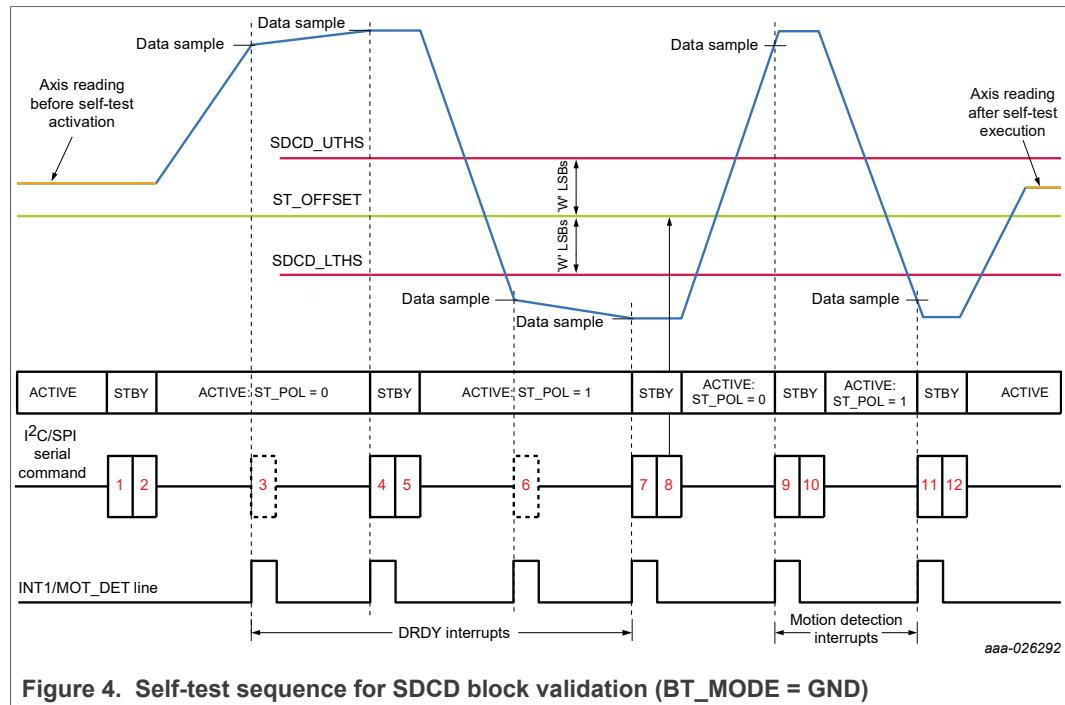

The steps below refer to the serial commands as shown in [Figure 2](#) and [Figure 3](#).

1. Enter Standby mode by setting **SENS\_CONFIG1[ACTIVE]** to 0 (address 15h).

2. Configure registers.

- a. Set the Self-test measurement phase decimation factor by setting **SELF\_TEST\_CONFIG2[ST\_DEC]** to 05h (address 38h). In this example, Self-test ODR is set to 100 Hz. Note that when BT\_MODE pin is connected to VDD, the data ready interrupt is signaled for  $T_{PULSE-MOT}$  seconds (5 ms typ) and it clears itself automatically. Hence maximum recommended ODR when BT\_MODE pin is connected to VDD is 100 Hz.

- b. Enable data ready interrupt by setting **INT\_EN[DRDY\_EN]** bit to 1. Interrupt is routed to INT1 line. INT2 line cannot be used, because only BOOT interrupt can be routed to INT2 line when BT\_MODE = V<sub>DD</sub>.

- c. Write **SENS\_CONFIG1** register (address 15h) with the following content:

- i. Self-test enabled on the desired axis by setting ST\_AXIS\_SEL[1:0] to 0b01 for X-axis, 0b10 for Y-axis or 0b11 for Z-axis

- ii. Self-test positive polarity selected by setting ST\_POL to 0

- iii. Select FSR measurement range. In this example  $\pm 16\text{ g}$  range is selected by setting FSR[1:0] to 0b11

- iv. Active mode selected by setting ACTIVE to 1

3. Wait for DRDY interrupt. Upon reception of the first data ready interrupt, put device in Standby mode by setting **SENS\_CONFIG1[ACTIVE]** to 0 (address 15h). Read the acceleration data in the output registers corresponding to the selected axis (X data at register addresses 04h and 05h, Y data at register addresses 06h and 07h, Z data at register addresses 08h and 09h). Store the output data as a temporary variable, such as ST\_OUTp(i).

4. Write **SENS\_CONFIG1** register (address 15h) with the following content:

- a. Self-test enabled on the desired axis by setting ST\_AXIS\_SEL[1:0] to 0b01 for X-axis, 0b10 for Y-axis or 0b11 for Z-axis

- b. Self-test negative polarity selected by setting ST\_POL to 1

- c. Active mode selected by setting ACTIVE to 1

5. Wait for DRDY interrupt. Upon reception of the first data ready interrupt, put device in Standby mode by setting **SENS\_CONFIG1[ACTIVE]** to 0 (address 15h). Read the acceleration data in the output registers corresponding to the selected axis (X data at register addresses 04h and 05h, Y data at register addresses 06h and 07h, Z data at register addresses 08h and 09h). Store the output data as a temporary variable, such as ST\_OUTm(i).

6. Measure self-test output change, self-test offset and configure registers.

- a. Calculate Self-Test Output Change (STOC). If LSL (Lower Spec Limit in LSB)  $\leq$  STOC  $\leq$  USL (Upper Spec Limit in LSB), the device passed self-test. LSL and