# AN12988

## PN7160 Hardware design guide

Rev. 1.4 — 28 September 2021

Application note

COMPANY PUBLIC

### Document information

| Information | Content                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | PN7160 hardware design guide, power modes, clock, IC interfaces                                                                                                                                                                                                                                                                                                                                                                    |

| Abstract    | This document is intended to provide an overview on how to integrate the NFC contactless frontend from hardware perspective. It presents the different hardware design options offered by the IC and provides guidelines on how to select the most appropriate ones for a given implementation. This document highlights the different IC power states and how to operate them in order to minimize the average power consumption. |

## Revision history

| Rev | Date     | Description                                                                                                                             |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1.4 | 20210928 | TVDD pin renamed as VDD(TX) to align with data sheet                                                                                    |

| 1.3 | 20210913 | Security status changed into "Company public", no content change                                                                        |

| 1.2 | 20210819 | <ul style="list-style-type: none"><li>TVDD CFG1 description updated</li><li>Security status changed into "Company restricted"</li></ul> |

| 1.1 | 20210705 | Editorial updates                                                                                                                       |

| 1.0 | 20210302 | Initial version                                                                                                                         |

## 1 Introduction

The PN7160 is a full feature NFC controller designed for integration in devices compliant with NFC standards (NFC Forum including NCI and EMVCo).

It is designed based on learning from previous NXP NFC device generation to ease the integration of the NFC technology in devices by providing:

- A low PCB footprint and a reduced external Bill of Material by enabling as unique feature the capability to achieve RF standards (NFC Forum, EMVCo)

- An optimized architecture for low power consumption in different modes (standby, low-power polling loop)

- A highly efficient integrated power management unit allowing direct supply from a mobile battery while a constant power (operating distance in Reader/Writer mode) for extended battery supply range (2.8 V to 5.5 V) can be achieved.

- Support of an external DC-DC converter like NXP PCA9412A, to provide more output power.

The RF contactless front-end support various transmission modes according to NFCIP-1 and NFCIP-2, ISO/IEC 14443, ISO/IEC 15693, MIFARE and FeliCa specifications. This new contactless front-end design brings a major performance step-up with on one hand a higher sensitivity and on the other hand the capability to work in active load modulation communication enabling the support of small antenna form factor (for listen mode). It also allows to provide a higher output power by supplying the transmitter output stage from 2.7 V to 5.25 V. This NFC controller provides new features:

- Enhanced Dynamic LMA (DLMA) to optimize and to enhance load modulation amplitude depending on external field strength. It allows higher range communication distance in card mode.

- 5° steps for LMA phase adjustment

- Dynamic power control which allows to make use of the maximum power in reader mode without exceeding the maximum power allowed by the standard in 0 distance

- Improved receiver sensitivity

- 1.25 W output transmitter power

In this document, the generic word NFCC is used to designate the PN7160.

## 2 Abbreviations

| Acronym          | Description                                         |

|------------------|-----------------------------------------------------|

| AN               | Application note                                    |

| BOM              | Bill of material                                    |

| CFG              | Configuration                                       |

| CLK              | Clock                                               |

| DWL_REQ          | DoWnLoad REQuest pin                                |

| EEPROM           | Electrically Erasable Programmable Read Only Memory |

| GND              | Ground                                              |

| GPIO             | General Purpose Input Output                        |

| HW               | Hardware                                            |

| I <sup>2</sup> C | Inter-Integrated Circuit (serial data bus)          |

| IC               | Integrated Circuit                                  |

| IO               | Input / Output                                      |

| IRQ              | Interrupt Request                                   |

| mA               | milliampere                                         |

| MHz              | Mega Hertz                                          |

| mW               | milliwatt                                           |

| NFC              | Near Field Communication                            |

| NFCC             | Near Field Communication Controller                 |

| PMU              | Power Management unit                               |

| RF               | Radiofrequency                                      |

| RST              | Reset                                               |

| SPI              | Serial Peripheral Interface                         |

| VEN              | V ENable pin (PN7160 Hard reset control)            |

### 3 References

[I<sup>2</sup>C] I<sup>2</sup>C -bus specification and user manual Rev 03, defined by NXP. Last revision from June 2007 can be found here: <http://ics.nxp.com/support/documents/interface/pdf/i2c.bus.specification.pdf>

[SPI] SPI Block Guide, Freescale — [V04.0114 July2004]

User Manual - UM11495 PN7160 NFC controller

Product data sheet - PN7160\_PN7161 Near Field Communication (NFC) controller

Application note - AN13219 PN7160 Antenna design and matching guide

## 4 NFCC interfaces

The purpose of this chapter is to give an overview of the NFCC interfaces and to show how the chip is interconnected to the external world.

The PN7160 provides the following interfaces:

- Host interface

- Clock interface

- Power interface

- Antenna interface

Table 1. PN7160 interface summary

| Interface                         | Short description                                                                               | Options                                                                                                                                                                             |

|-----------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <a href="#">Host interface</a>    | Link PN7160 with host controller                                                                | <ul style="list-style-type: none"><li>• <a href="#">I<sup>2</sup>C, SPI</a></li><li>• <a href="#">IRQ</a></li><li>• <a href="#">VEN</a></li><li>• <a href="#">DWL_REQ</a></li></ul> |

| <a href="#">Clock interface</a>   | Input clock needed by the PN7160 when generating RF field                                       | <ul style="list-style-type: none"><li>• <a href="#">XTAL based</a></li><li>• <a href="#">External clock based</a></li></ul>                                                         |

| <a href="#">Power interface</a>   | Interface to PN7160 power management unit                                                       | <ul style="list-style-type: none"><li>• <a href="#">CFG1</a></li><li>• <a href="#">CFG2</a></li></ul>                                                                               |

| <a href="#">Antenna interface</a> | Link PN7160 to an NFC antenna in order to enable communication with a remote contactless device |                                                                                                                                                                                     |

## 5 Typical application schematics

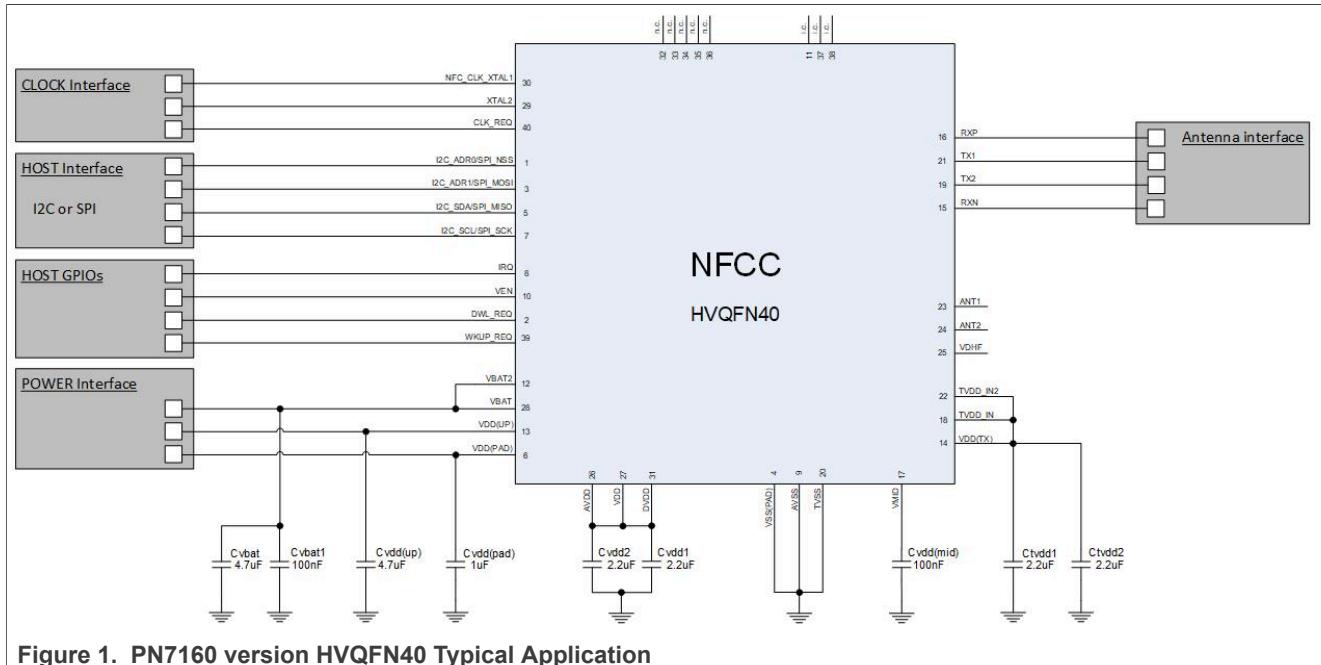

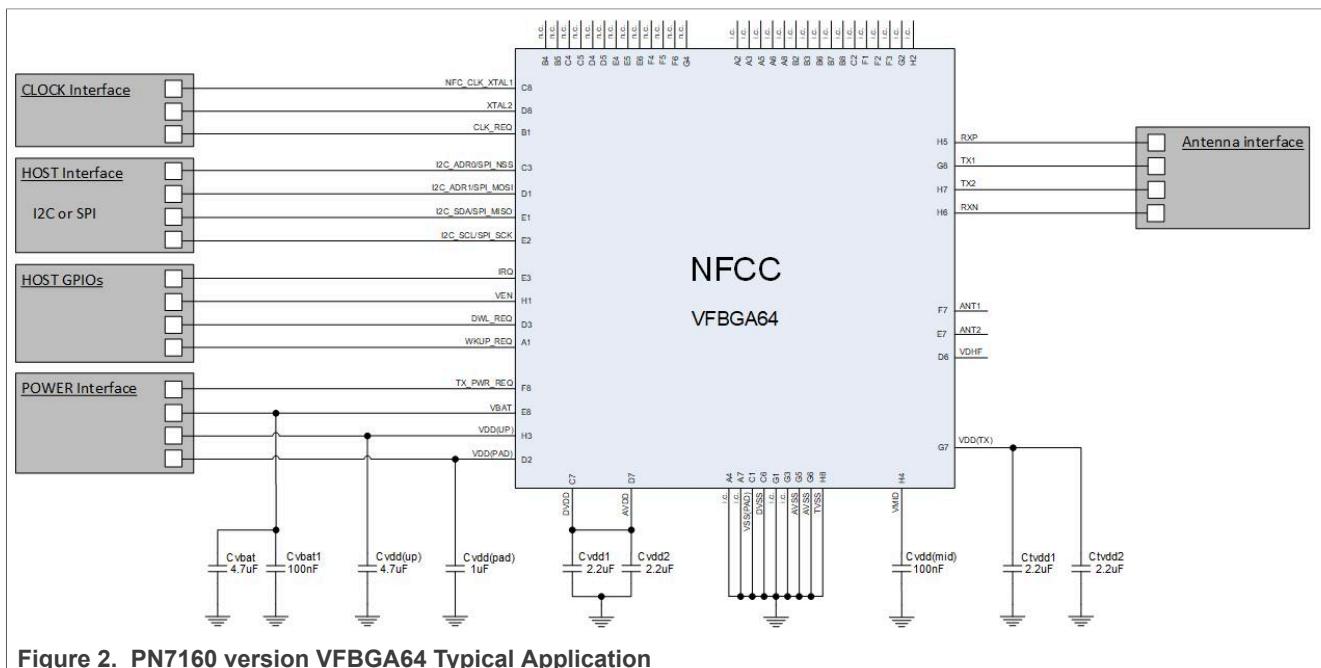

The purpose of this chapter is to propose application schematics for PN7160 IC.

### 5.1 PN7160 HVQFN40

Figure 1. PN7160 version HVQFN40 Typical Application

### 5.2 PN7160 VFBGA64

Figure 2. PN7160 version VFBGA64 Typical Application

## 6 NFC controller host interface

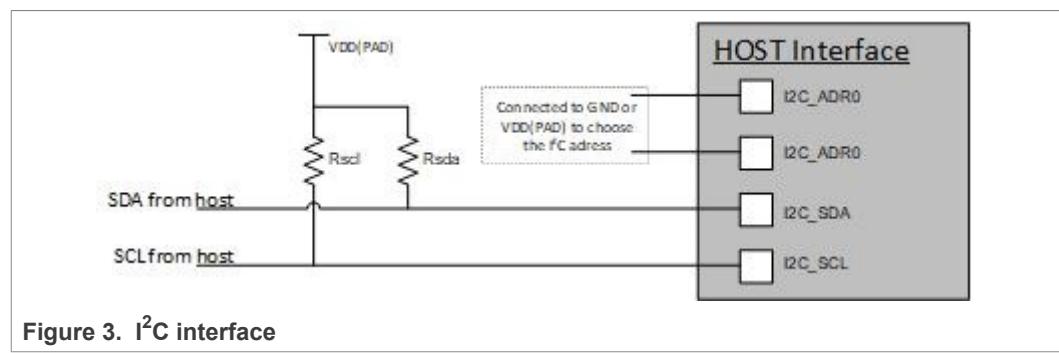

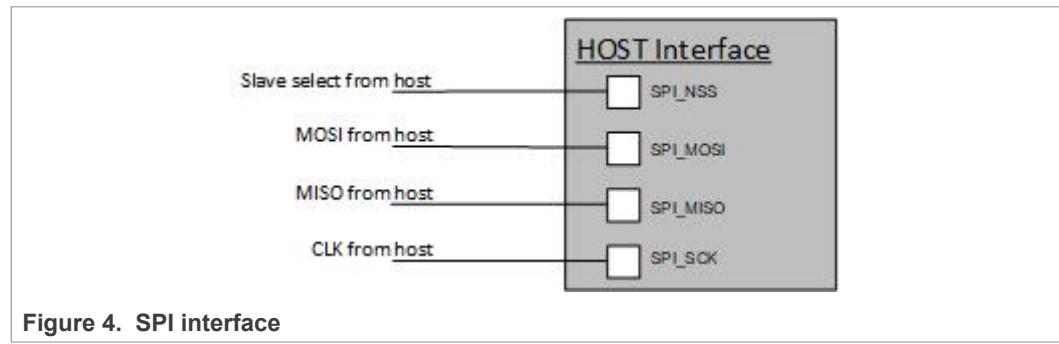

2 host interfaces are available:

- I<sup>2</sup>C interface

- SPI interface

Please note that the host interface (SPI, I<sup>2</sup>C) used by the PN7160 is configured during chip production. A separate ordering number is assigned to each host interface.

Figure 3. I<sup>2</sup>C interface

Figure 4. SPI interface

PN7160 is intended to be connected to a host controller, from a hardware point of view the interface can be an I<sup>2</sup>C or a SPI link.

An IRQ pin is used by the NFCC chip to inform the host that a message must be read (for more detail see [Section 7.1](#)).

### 6.1 Host interface connection

The selection between both interfaces is configured during IC manufacturing so there are different ordering numbers for the I<sup>2</sup>C version and the SPI version of the PN7160.

Therefore, no board level configuration is needed to select the host interface which will be used by the chip.

The following pinning assignment applies based on the selected interface:

Table 2. PN7160 VFBGA - Host interface pinning

| Interface Pin    | HIF1 C3               | HIF2 D1               | HIF3 E2 | HIF4 E1  |

|------------------|-----------------------|-----------------------|---------|----------|

| I <sup>2</sup> C | I <sup>2</sup> C_ADR0 | I <sup>2</sup> C_ADR1 | SCL     | SDA      |

| SPI              | SPI_NSS               | SPI_MOSI              | SPI_SCK | SPI_MISO |

Table 3. PN7160 HVQFN - Host interface pinning

| Interface Pin    | HIF1 #5  | HIF2 #7 | HIF3 #1               | HIF4 #3               |

|------------------|----------|---------|-----------------------|-----------------------|

| I <sup>2</sup> C | SDA      | SCL     | I <sup>2</sup> C_ADR0 | I <sup>2</sup> C_ADR1 |

| SPI              | SPI_MISO | SPI_SCK | SPI_NSS               | SPI_MOSI              |

## 6.2 I<sup>2</sup>C bus specificities

### Slave address:

In the case where I<sup>2</sup>C is the selected host interface, the chip will answer to a given I<sup>2</sup>C slave address.

This is determined by the combination of a base address and the logical state of I<sup>2</sup>C\_ADR0 and I<sup>2</sup>C\_ADR1 pins:

b'0 1 0 1 0 I<sup>2</sup>C\_ADR1 I<sup>2</sup>C\_ADR0' where I<sup>2</sup>C\_ADR0 is the least significant bit.

For instance, if I<sup>2</sup>C\_ADR0 and I<sup>2</sup>C\_ADR1 are both tied to ground, the 7-bits slave address of the PN7160 is 0x28.

Table 4. I<sup>2</sup>C slave 8-bits address

| I2C_ADR1 level | I2C_ADR0 level | PN7160 write address (R/W bit = 0) | PN7160 read address (R/W bit = 1) |

|----------------|----------------|------------------------------------|-----------------------------------|

| 0 (GND)        | 0 (GND)        | 0x50                               | 0x51                              |

| 0 (GND)        | 1 (VDD(PAD))   | 0x52                               | 0x53                              |

| 1 (VDD(PAD))   | 0 (GND)        | 0x54                               | 0x55                              |

| 1 (VDD(PAD))   | 1 (VDD(PAD))   | 0x56                               | 0x57                              |

### Pull-up selection:

Pull-up resistors to VDD(PAD) are required on the I<sup>2</sup>C lines SDA and SCL. The resistors value must be selected in order to meet the I<sup>2</sup>C timing requirements based on the line capacitance, the VDD(PAD) level and the targeted maximum I<sup>2</sup>C clock speed.

More details can be found in the [I<sup>2</sup>C bus specification](#) document.

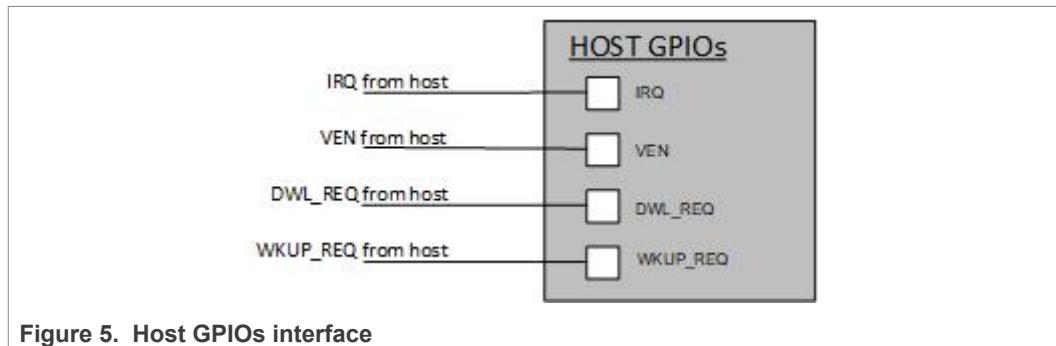

## 7 Host GPIOs

The PN7160 host GPIOs are directly connected to host processor GPIOs.

### 7.1 PN7160 frames reading synchronization (IRQ pin)

PN7160 answers / notifications toward the host controller are asynchronous and they can be triggered by an external event (e.g detection of a card in the RF field).

Therefore, a mechanism must be put in place so that asynchronous frames from the PN7160 are well captured by the host controller. For this, 3 implementations can be foreseen on the host controller side:

- 1- IRQ pin external interrupt

- 2- IRQ pin polling

- 3- Read polling

For "1-", connect pin IRQ of the PN7160 to an external interrupt line on the host controller side. In this case, when the PN7160 has some data available, the IRQ line will be asserted and if configured accordingly, a software interrupt is generated on the host controller side. A host interface read is then managed by the corresponding interrupt handler.

For "2-", the principle is to regularly poll the status of the IRQ pin and when it toggles, to perform a read on the host interface.

For "3-", the principle is to regularly perform some read on the host interface and to discard frames starting with the default value as in this case it would mean that no data is available from the PN7160. Default value is 0xFF in case of SPI bus. For the I<sup>2</sup>C bus, the I<sup>2</sup>C address will not be acknowledged in case the PN7160 does not have any meaningful data to send to the host.

|  |                                    |

|--|------------------------------------|

|  | Implementation "1-" is recommended |

|--|------------------------------------|

IRQ pin polarity (e.g. active high or low) is configurable with register settings. Details can be found in the [PN7160 User Manual](#).

#### IRQ Signal Specification:

- The signal can be configured active high or active low via the NCI Configuration API, this configuration being stored in non-volatile memory

- The signal will be active anytime data is available in the PN7160 send buffer

- The pad state is maintained during the standby mode

- The pad is configured to pull down in hard power-down mode

## 7.2 Reset control (VEN Pin)

The PN7160 HW is activated using the input pin VEN. When VEN is greater than 1.1 V the PN7160 core is supplied from VBAT. For VEN lower than 0.4 V, the PN7160 is in hard power down state and the chip's internal core is no more supplied. The chip is reset when VEN is switched back to a voltage level higher than 1.1 V.

It is strongly recommended to foresee a control of VEN pin from the host controller side so that it can reset PN7160 whenever needed.

The VEN pin state is considered as valid information only when the VDD(PAD) pad is supplied. Indeed, VEN signal is supposed to be driven by the host controller with which VDD(PAD) supply is shared. When the supply is not there, this means that the host controller is not able to drive a meaningful state on the PN7160 VEN pin.

When VDD(PAD) is not present, the level of VEN is determined thanks to a 2-bit register stored in a non-volatile memory to define if the chip is operating in hard power down state or in active mode (VEN\_Pulld and VEN\_Value) as depicted in [Table 5](#).

**Table 5. VEN configuration**

| VEN external                                   | VDD(PAD) active | VEN_Pulldown cases | VEN_Value cases | Actual VEN internal value   |

|------------------------------------------------|-----------------|--------------------|-----------------|-----------------------------|

| 0 (via host)                                   | Y               | 0                  | X               | = 0 (via Host) <sup>2</sup> |

| 1 (via host)                                   | Y               | 0                  | X               | = 1 (via Host) <sup>2</sup> |

| 0 (via host)                                   | Y               | 1 (default)        | X               | = 0 (via Host)              |

| 1 (via host)                                   | Y               | 1 (default)        | X               | = 1 (via Host)              |

| VDD(PAD) not active = VEN via Host not defined | N               | 0                  | X               | X (Undefined) <sup>1</sup>  |

|                                                | N               | 0                  | X               | X (Undefined) <sup>1</sup>  |

|                                                | N               | 1 (default)        | 0               | = 0 (VEN_Value)             |

|                                                | N               | 1 (default)        | 1               | = 1 (VEN_Value)             |

<sup>1</sup> VEN\_Pulld default value being 1, it is strongly recommended not to program it to 0 since, when VDD(PAD) is inactive, VEN internal value will be undefined.

<sup>2</sup> VEN\_Pulld default value being 1, there is no added value to program it to 0 due to <sup>1</sup>.

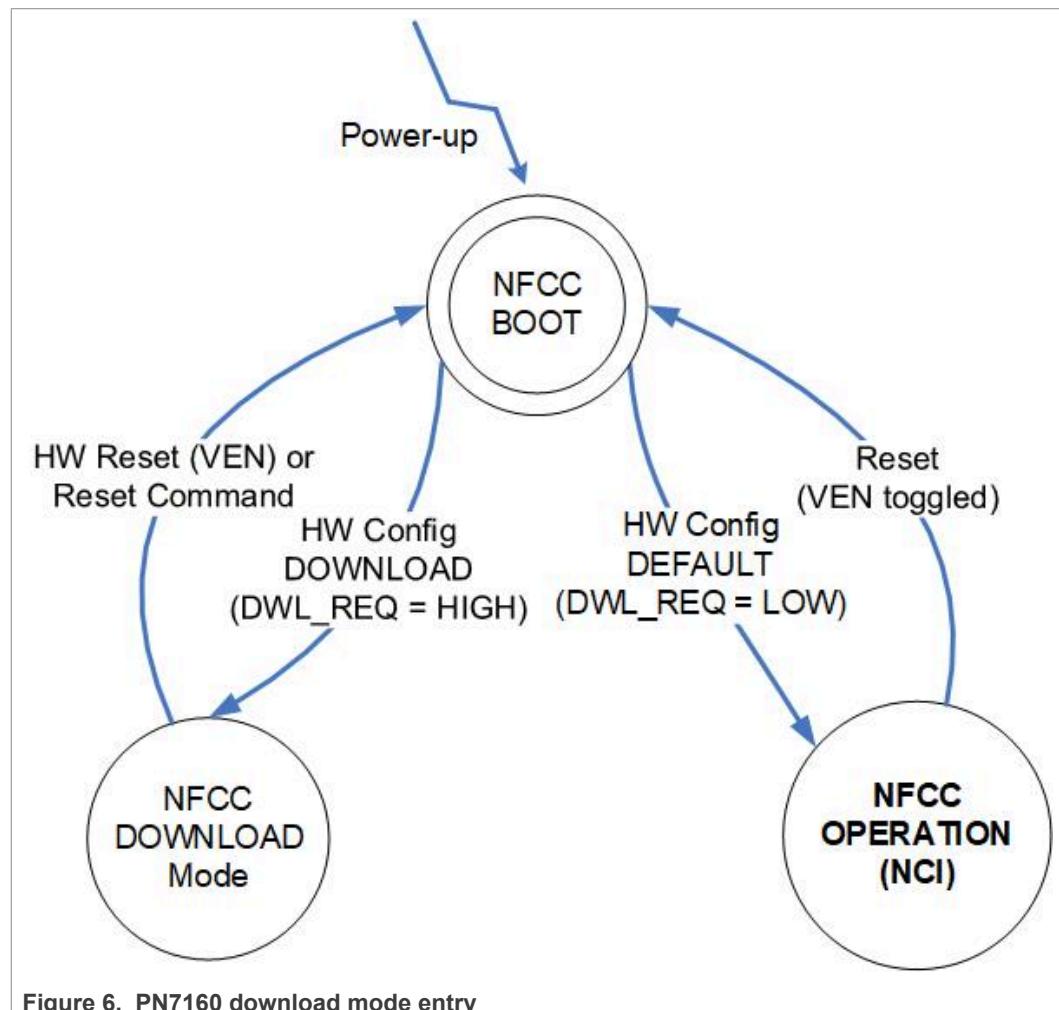

## 7.3 Download mode control (DWL\_REQ Pin)

PN7160 entry in download mode is managed through the DWL\_REQ pin.

Although NXP strongly advises driving this pin through the host controller, in case where download mode control is not supported, this pin must be tied to ground or left open (internal pull-down).

When the DWL\_REQ pin is set to the digital high level (this pin is referenced to VDD(PAD) power level) at reset (VEN transition from digital low to digital high), the chip will boot in download mode.

In this case, the download protocol described in the [PN7160 User Manual](#) can be used to load a new firmware image into the chip.

This firmware upgrade feature is fully supported by the NXP HAL middleware stack (Android and Linux) provided that the DWL\_REQ (DL\_REQ) pin is connected a GPIO pin of the host controller.

A comparison between the operation of the PN7160 in both download mode and normal mode is given in the diagram below:

Figure 6. PN7160 download mode entry

#### 7.4 Wake-up request pin (WKUP\_REQ Pin)

When the PN7160 goes in standby mode, there are 3 possibilities to wake it up:

- PN7160 detects an external RF field

- Host controller sends a command (via host interface) to PN7160

- Host drives WKUP\_REQ pin to high level

#### 7.5 Host interface pins characteristics

Detailed characteristics of the host interface pins can be found in the [PN7160 Product datasheet](#).

## 8 Clock interface

The PN7160 core can run without any external clock (based on an internal oscillator), however a 27.12 MHz clock is needed:

- to generate the RF field in poll mode

- to generate the ALM load modulation in listen mode

2 clock configurations can be considered:

- CLK provided by an XTAL oscillator

- CLK provided by an external source

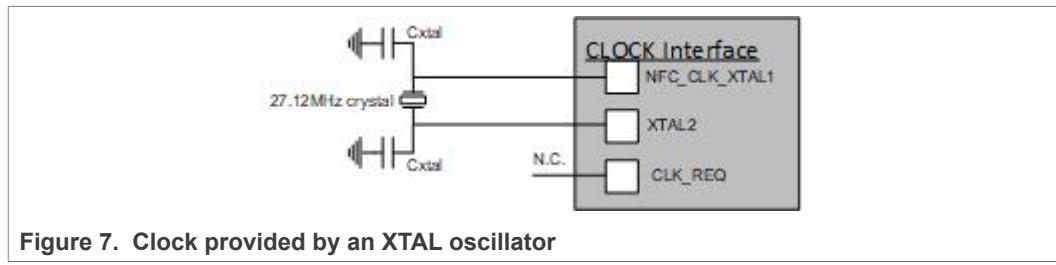

### 8.1 Clock provided by an XTAL oscillator

A 27.12 MHz crystal can be used as input clock for PN7160.

Figure 7. Clock provided by an XTAL oscillator

When using a crystal, frequency accuracy and drive level must be carefully selected according to the specification provided in the [PN7160 Product Datasheet](#).

The PN7160 clock interface must be configured properly to reflect whether it is connected to a 27.12 MHz crystal oscillator or to an external clock. This is done through the NCI host interface (details can be found in [PN7160 User Manual](#)).

Please note that the crystal-based solution is less optimized from Bill of Material perspective as it not only requires a crystal oscillator but also 2 additional decoupling capacitors on NFC\_CLK\_XTAL1 and XTAL2 pins. However, the crystal-based solution guarantees the same kind of performances.

#### 8.1.1 XTAL references

PN7160 clock interface with xtal oscillator has been verified with several references as given below. Other crystal units might be suitable for the specified usage, but only the ones below have been validated by NXP.

- NDK:

- NX2016SA 27.12 MHz EXS00A-CS06346.

- NX2016HA 27.12 MHz EXS00A-CH00075

- MURATA

- XRCGB27M120F3M10R0

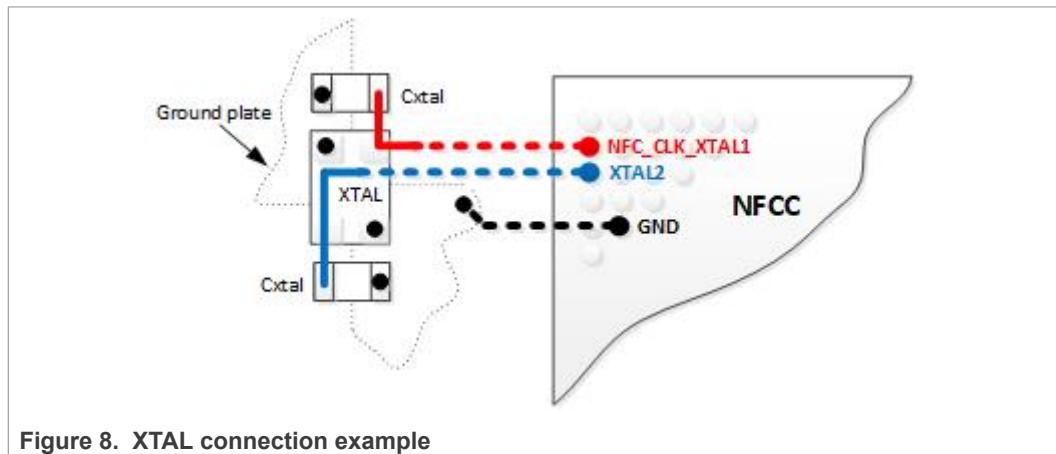

#### 8.1.2 XTAL layout recommendations

The XTAL must be connected as close as possible to the CLK1 and CLK2 pins from the PN7160 to achieve the best performances as possible.

Please follow these guidelines for the layout of the XTAL connections:

- As the XTAL is very sensitive to parasitic capacitance and noise, we advise to:

- put the XTAL far from other signals (especially other CLK lines or signals with frequent switching)

- limit the crosstalk between CLK lines and other signals

- Load capacitor connections:

- Choose capacitor with a good temperature stability like COG

- Place the capacitors closed to each other and close to the XTAL

- Avoid connecting them to a dirty ground (perturbed by return current from others functionalities on the board like USB, PWM or power supply lines)

Figure 8. XTAL connection example

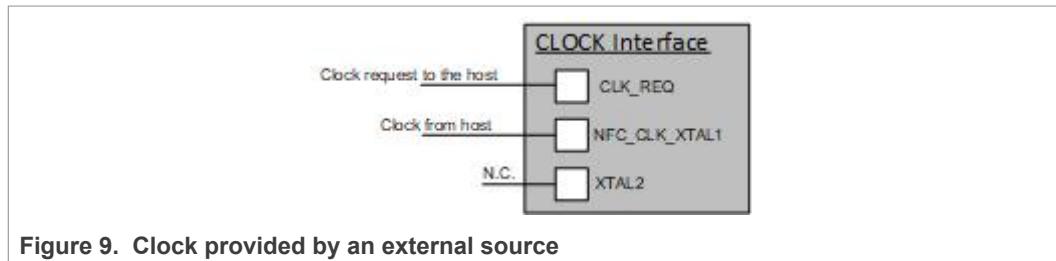

## 8.2 Clock provided by an external source

Figure 9. Clock provided by an external source

### 8.2.1 External clock source requirements

When an external system clock is used, the input clock frequency must be one of the following values:

- 13 MHz

- 19.2 MHz

- 24 MHz

- 26 MHz

- 32 MHz

- 38.4 MHz

- 52 MHz

For proper operation, the external clock frequency must be indicated to PN7160. This is done through the NCI host interface (details can be found in [PN7160 User Manual](#)).

Please note that the voltage level of the system clock signal provided to PN7160 must fulfill to data sheet ([PN7160 Product Datasheet](#)) requirements (voltage levels, phase noise). On top of these data sheet requirements, square shape must fulfill below requirements:

**Table 6. NFC\_CLK\_XTAL1 square shape input clock specifications**

| Parameter            | Min   | Typ | Max   |

|----------------------|-------|-----|-------|

| peak-to-peak voltage | 0.4 V | -   | 1.8 V |

| rising/falling time  | -     | -   | 10 ns |

The PN7160 input impedance on the NFC\_CLK\_XTAL1 pin depends on the input clock frequency (see table below).

**Table 7. NFC\_CLK\_XTAL1 pin input impedance**

| Input clock frequency | Active mode |        | Standby or hard power mode |       |

|-----------------------|-------------|--------|----------------------------|-------|

|                       | min         | Max    | Min                        | Max   |

| 13 MHz                | 25 kΩ       | 86 kΩ  | 49 kΩ                      | 53 kΩ |

| 52 MHz                | 5 kΩ        | 7.5 kΩ | 12 kΩ                      | 14 kΩ |

Based on this input clock signal, the PN7160 internal PLL generates the required 27.12 MHz internal clock for field generation.

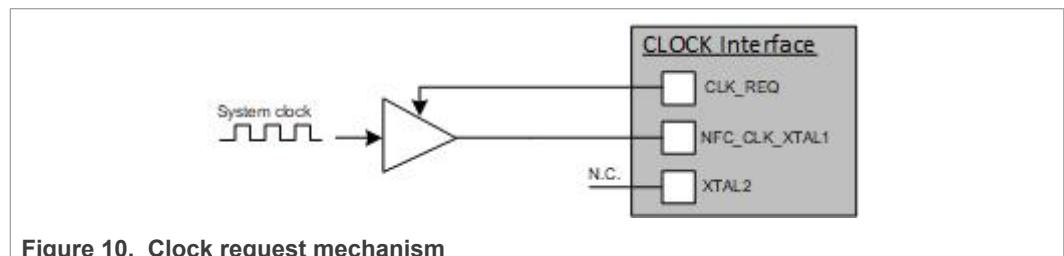

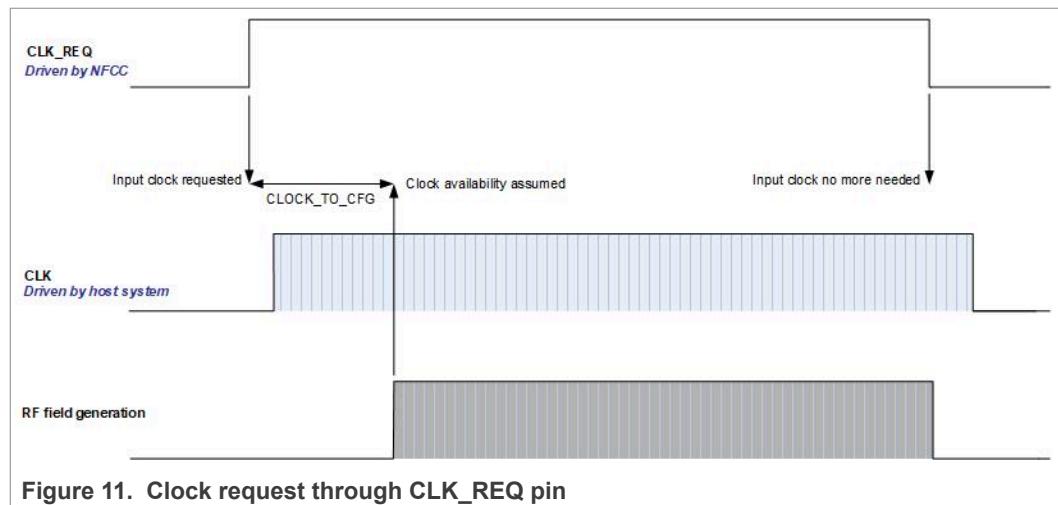

### 8.2.2 Clock request mechanism

In order to optimize the device power consumption, the PN7160 input clock could be provided by the system only when it is actually needed by the chip (e.g. when the PN7160 needs to generate an RF field). For this, a clock request mechanism has been put in place, only applicable when an external clock is used (not with a crystal). This is enabled via CLOCK\_REQUEST\_CFG parameter, configured through the NCI host interface (details can be found in [PN7160 User Manual](#)).

**Figure 10. Clock request mechanism**

When the PN7160 needs an input clock, it will toggle the CLK\_REQ pin to the digital high level and keeps it high as long as the input clock is required.

It requires then a specific connection of the CLK\_REQ pin which would switch on the system clock signal whenever the pin is at the digital high level and switch it off when the pin is set back to the digital low level.

CLOCK\_TO\_CFG is a timeout which can be configured through EEPROM settings. It represents the duration after PN7160 has raised its CLK\_REQ pin during which the host system must provide a valid and stable clock on CLK pin.

CLK\_REQ pin shall be left unconnected when not used since it is driven low

## 9 Power interface

### 9.1 External capacitors requirement

The recommended external capacitors are listed below (referring to application schematics in chapter [Section 5](#)):

**Table 8. Decoupling capacitors need**

| Capacitor | Value       | Comments                                                      |

|-----------|-------------|---------------------------------------------------------------|

| Cvdd(up)  | 4.7uF/7V    | Voltage tolerance depends on the voltage on Vdd(up)           |

| Cvbat     | 4.7uF/ 5.5V |                                                               |

| Cvbat1    | 100nF/ 5.5V |                                                               |

| Cvdd1     | 2.2uF/2V    | 2 *2.2uF one as close as possible of each pin (DVDD and AVDD) |

| Cvdd2     | 2.2uF/2V    |                                                               |

| Ctvdd1    | 2.2uF/5.5V  | 2 *2.2uF are needed to avoid derating issue                   |

| Ctvdd2    | 2.2uF/5.5V  |                                                               |

| Cvdd(pad) | 1μF/3.3V    |                                                               |

| Cvdd(mid) | 100nF/1.8V  |                                                               |

A tolerance of 10% or better is recommended for those capacitors.

|                                                                                     |                                                                                                                                  |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|  | Component de-rating over voltage and temperature must be carefully considered during the decoupling capacitors selection process |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

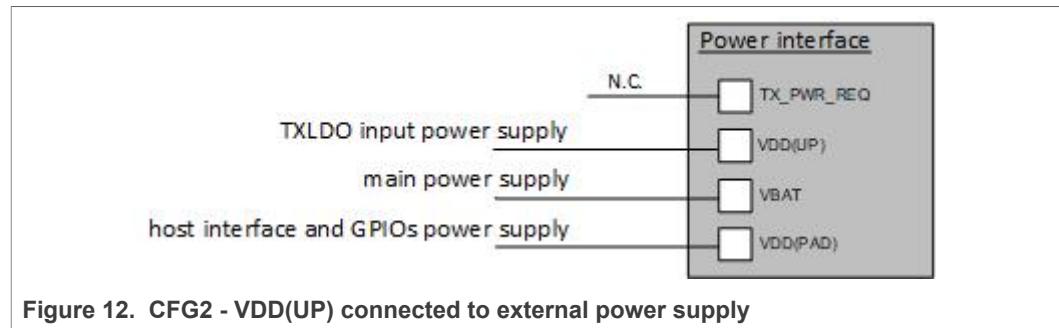

### 9.2 External power supplies

The PN7160 needs 3 external power supplies to operate.

- VBAT: This is the main power supply of the NFCC.

- VDD(PAD): This is the power supply for the host interface and GPIOs.

- VDD(UP): This is the power supply allowing to generate TXLDO.

**Table 9. External power supplies voltage**

| Parameter | Min  | Typ | Max  | Unit |

|-----------|------|-----|------|------|

| VBAT      | 2.8  | -   | 5.5  | V    |

| VDD(PAD)  | 1.65 | 1.8 | 1.95 | V    |

|           | 3.0  | 3.3 | 3.6  |      |

| VDD(UP)   | 2.8  | -   | 5.8  | V    |

### 9.3 TXLDO power level

The strength of the field emitted by the PN7160 is linked to several parameters such as the antenna geometrical characteristics, the antenna matching circuit and the voltage level on TX output buffer.

The voltage level on TX output buffer is coming from VDD(TX) and this pin is powered internally by the PN7160 thanks to the TXLDO block. The output voltage of this TXLDO can be set between 2.7 V to 5.25 V depending on the VDD(UP) voltage.

2 VDD(UP) configurations are considered:

- VDD(UP) connected to an external supply (CFG1)

- VDD(UP) supplied via DC-DC converter (CFG2)

### 9.3.1 CFG1

In CFG1, the VDD(UP) pin is connected to an external power supply.

Figure 12. CFG2 - VDD(UP) connected to external power supply

In this configuration TXLDO voltage possible settings are 2.7V, 3V, 3.3V, 3.6V, 3.9V, 4.2V, 4.5V, 4.7V, 4.75V, 5V and 5.25V.

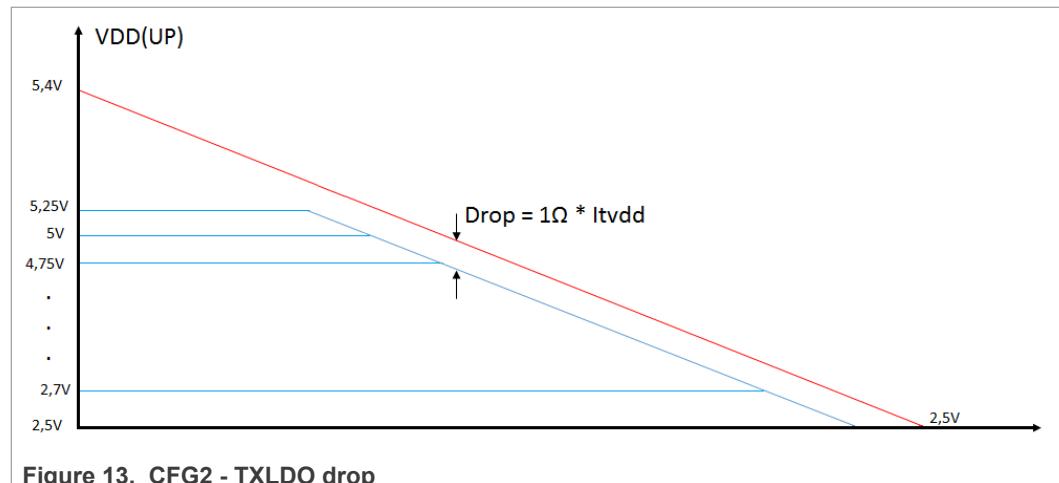

Figure 13. CFG2 - TXLDO drop

In Standby state, TXLDO is always regulated @2.5V

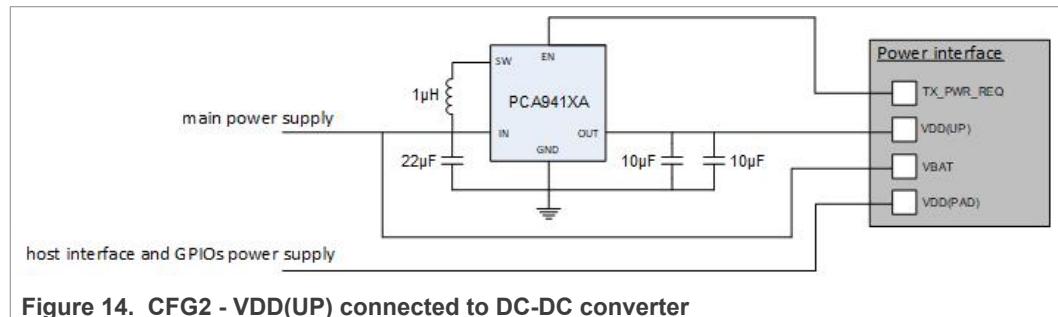

### 9.3.2 CFG2

In CFG2, a DC-DC converter is used in order to increase VDD(UP) voltage the main supply voltage.

NXP proposes several DC-DC references to provide the best in class performances:

- PCA9410A => output voltage = 5 V

- PCA9411A => output voltage = 5.25 V

- PCA9412A => output voltage = 5.4 V

Figure 14. CFG2 - VDD(UP) connected to DC-DC converter

For the DC-DC external components, NXP recommends these parts:

- 10  $\mu$ F on OUT pin: CL05A106MQ5NUNC

- 22  $\mu$ F on IN pin: C1608X5R0J226M080AC

- 1  $\mu$ H on IN pin; ASMPH-0603-1R0M-T

Depending on the chosen DC-DC converter, providing then different output voltage, the following TXLDO voltage can be set:

Table 10. TXLDO voltage in CFG2

| DC-DC reference | DC-DC output voltage | TXLDO voltage available                          |

|-----------------|----------------------|--------------------------------------------------|

| PCA9410A        | 5 V                  | 2.7V/3V/3.3V/3.6V/3.9V/4.2V/4.5V/4.75V           |

| PCA9411A        | 5.2 V                | 2.7V/3V/3.3V/3.6V/3.9V/4.2V/4.5V/4.75V/5V        |

| PCA9412A        | 5.4 V                | 2.7V/3V/3.3V/3.6V/3.9V/4.2V/4.5V/4.75V/5V/5.25V* |

\*For 5.25 V the TXLDO drop (1 Ohm \* Itvdd) must be below than 150 mV.

### 9.3.2.1 Tx\_PWR\_REQ pin

To drive the external power supply used by the PN7160, the pin TX\_PWR\_REQ is available.

The Enable pin input impedance of the DC-DC (driven by the TX\_PWR\_REQ pin) must be higher than 200 k $\Omega$ .

The TX\_PWR\_REQ pin is rising when the polling phase is starting in reader mode and when an external field is detected in card mode.

Pay attention that TX\_PWR\_REQ pin is only available on VFBGA64 PN7160 variant.

### 9.3.2.2 DC-DC recommendations

The NXP DC-DC PCA941XA is recommended to be used with the PN7160.

If another DC-DC is used it must respect the specification of the table below, additionally the DC-DC must have a pass-through function to be able to always supply at least VDD(UP) > 2.5 V.

Table 11. DC-DC requirements

| Parameter                                               | Min  | Typ | Max  | Unit  |

|---------------------------------------------------------|------|-----|------|-------|

| Vin                                                     | 2.5  | 3.6 | 5    | V     |

| Iout DC-DC                                              | -    | 350 | 500  | mA    |

| Output voltage accuracy                                 | 2    | -   | 4    | %     |

| Spurious less frequency range                           | 12.5 | -   | 14.5 | MHz   |

| Switching frequency                                     | 848  | -   | -    | kHz   |

| Vorms noise (incoherent noise)<br>100kHz to 1.5MHz band | -    | -   | 660  | uVrms |

| Vorms noise (incoherent noise)<br>12 MHz to 15MHz band  | -    |     | 660  | uVrms |

| Output ripple voltage                                   | -100 | -   | 50   | mV    |

| Enable pin impedance                                    | 200  | -   | -    | kΩ    |

| Start up time                                           | -    | 500 | 1000 | us    |

## 10 Antenna interface

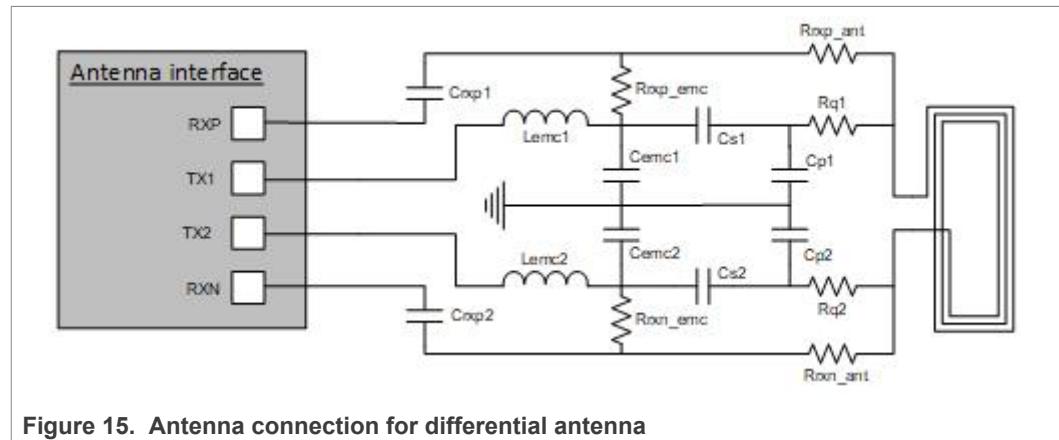

Below figure show the way to connect a differential antenna to the PN7160.

**Figure 15. Antenna connection for differential antenna**

All the details on the antenna matching and connections are listed in the [PN7160 Antenna design guide](#).

## 11 Legal information

### 11.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

### 11.2 Disclaimers

**Limited warranty and liability** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Terms and conditions of commercial sale** — NXP Semiconductors products are sold subject to the general terms and conditions of commercial

sale, as published at <http://www.nxp.com/profile/terms>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer. In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages. Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

**Security** — Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at [PSIRT@nxp.com](mailto:PSIRT@nxp.com)) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

### 11.3 Licenses

#### Purchase of NXP ICs with NFC technology

Purchase of an NXP Semiconductors IC that complies with one of the Near Field Communication (NFC) standards ISO/IEC 18092 and ISO/IEC 21481 does not convey an implied license under any patent right infringed by implementation of any of those standards. Purchase of NXP Semiconductors IC does not include a license to any NXP patent (or other IP right) covering combinations of those products with other products, whether hardware or software.

## 11.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

**I<sup>2</sup>C-bus** — logo is a trademark of NXP B.V.

**MIFARE** — is a trademark of NXP B.V.

**NXP** — wordmark and logo are trademarks of NXP B.V.

**FeliCa** — is a trademark of Sony Corporation.

## Tables

|         |                                                                |    |          |                                         |    |

|---------|----------------------------------------------------------------|----|----------|-----------------------------------------|----|

| Tab. 1. | PN7160 interface summary .....                                 | 6  | Tab. 7.  | NFC_CLK_XTAL1 pin input impedance ..... | 15 |

| Tab. 2. | PN7160 VFBGA - Host interface pinning .....                    | 9  | Tab. 8.  | Decoupling capacitors need .....        | 17 |

| Tab. 3. | PN7160 HVQFN - Host interface pinning .....                    | 9  | Tab. 9.  | External power supplies voltage .....   | 17 |

| Tab. 4. | I2C slave 8-bits address .....                                 | 9  | Tab. 10. | TXLDO voltage in CFG2 .....             | 19 |

| Tab. 5. | VEN configuration .....                                        | 11 | Tab. 11. | DC-DC requirements .....                | 20 |

| Tab. 6. | NFC_CLK_XTAL1 square shape input<br>clock specifications ..... | 15 |          |                                         |    |

## Figures

|         |                                                  |    |          |                                                         |    |

|---------|--------------------------------------------------|----|----------|---------------------------------------------------------|----|

| Fig. 1. | PN7160 version HVQFN40 Typical Application ..... | 7  | Fig. 9.  | Clock provided by an external source .....              | 14 |

| Fig. 2. | PN7160 version VFBGA64 Typical Application ..... | 7  | Fig. 10. | Clock request mechanism .....                           | 15 |

| Fig. 3. | I2C interface .....                              | 8  | Fig. 11. | Clock request through CLK_REQ pin .....                 | 16 |

| Fig. 4. | SPI interface .....                              | 8  | Fig. 12. | CFG2 - VDD(UP) connected to external power supply ..... | 18 |

| Fig. 5. | Host GPIOs interface .....                       | 10 | Fig. 13. | CFG2 - TXLDO drop .....                                 | 18 |

| Fig. 6. | PN7160 download mode entry .....                 | 12 | Fig. 14. | CFG2 - VDD(UP) connected to DC-DC converter .....       | 19 |

| Fig. 7. | Clock provided by an XTAL oscillator .....       | 13 | Fig. 15. | Antenna connection for differential antenna ....        | 21 |

| Fig. 8. | XTAL connection example .....                    | 14 |          |                                                         |    |

## Contents

---

|           |                                                    |           |

|-----------|----------------------------------------------------|-----------|

| <b>1</b>  | <b>Introduction</b>                                | <b>3</b>  |

| <b>2</b>  | <b>Abbreviations</b>                               | <b>4</b>  |

| <b>3</b>  | <b>References</b>                                  | <b>5</b>  |

| <b>4</b>  | <b>NFCC interfaces</b>                             | <b>6</b>  |

| <b>5</b>  | <b>Typical application schematics</b>              | <b>7</b>  |

| 5.1       | PN7160 HVQFN40                                     | 7         |

| 5.2       | PN7160 VFBGA64                                     | 7         |

| <b>6</b>  | <b>NFC controller host interface</b>               | <b>8</b>  |

| 6.1       | Host interface connection                          | 8         |

| 6.2       | I2C bus specificities                              | 9         |

| <b>7</b>  | <b>Host GPIOs</b>                                  | <b>10</b> |

| 7.1       | PN7160 frames reading synchronization<br>(IRQ pin) | 10        |

| 7.2       | Reset control (VEN Pin)                            | 11        |

| 7.3       | Download mode control (DWL_REQ Pin)                | 11        |

| 7.4       | Wake-up request pin (WKUP_REQ Pin)                 | 12        |

| 7.5       | Host interface pins characteristics                | 12        |

| <b>8</b>  | <b>Clock interface</b>                             | <b>13</b> |

| 8.1       | Clock provided by an XTAL oscillator               | 13        |

| 8.1.1     | XTAL references                                    | 13        |

| 8.1.2     | XTAL layout recommendations                        | 13        |

| 8.2       | Clock provided by an external source               | 14        |

| 8.2.1     | External clock source requirements                 | 14        |

| 8.2.2     | Clock request mechanism                            | 15        |

| <b>9</b>  | <b>Power interface</b>                             | <b>17</b> |

| 9.1       | External capacitors requirement                    | 17        |

| 9.2       | External power supplies                            | 17        |

| 9.3       | TXLDO power level                                  | 17        |

| 9.3.1     | CFG1                                               | 18        |

| 9.3.2     | CFG2                                               | 18        |

| 9.3.2.1   | Tx_PWR_REQ pin                                     | 19        |

| 9.3.2.2   | DC-DC recommendations                              | 19        |

| <b>10</b> | <b>Antenna interface</b>                           | <b>21</b> |

| <b>11</b> | <b>Legal information</b>                           | <b>22</b> |

---

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.