## Migration from Everspin MR2xH40 to Avalanche AS3004101 Application Note

AN000013 details the feature differences when migrating from the Everspin MR2xH40 serial MRAM to Avalanche AS3004101 Serial Persistent SRAM (P-SRAM).

### 1. Introduction

AS3004101 is a 4Mb serial (SPI) spin-transfer torque magneto-resistive random-access memory (STT-MRAM). MRAM technology is analogous to Flash technology with SRAM compatible read/write timings (Persistent SRAM, P-SRAM). Data is always non-volatile.

MRAM is a true random-access memory; allowing both reads and writes to occur randomly in memory. MRAM is ideal for applications that must store and retrieve data without incurring large latency penalties. It offers low latency, low power, virtually infinite endurance and scalable non-volatile memory technology.

AS3004101 has a Serial Peripheral Interface (SPI) compatible bus interface supporting hardware/software based data protection mechanisms.

This application note provides a comparison of features that need to be taken into consideration when migrating from the Everspin MR2xH40 MRAM to the Avalanche AS3004101 MRAM.

### 2. Feature Comparison

The AS3004101 is a magneto resistive random access memory supporting SPI interface operating at up to 50MHz SDR. The Everspin MR2xH40 also supports single I/O SPI operation at a maximum frequency of 50 MHz SDR.

In addition to the 8-pad WSON, the AS3004204 is also available in 8-pin SOIC package. These packages are compatible with similar low-power volatile and non-volatile products. For non-automotive applications, the AS3004204 is offered over the same industrial (-40°C to 85°C), and industrial plus (-40°C to 105°C) temperature ranges as the MR2xH40.

Table 1 provides a feature comparison between the MR2xH40 and the AS3004204.

**Table 1: Feature Comparison**

| Feature                   | Everspin<br>MR2xH40                                                                     | Avalanche<br>AS3004101 |

|---------------------------|-----------------------------------------------------------------------------------------|------------------------|

| Family                    | Serial                                                                                  | Serial                 |

| Technology                | Toggle MRAM                                                                             | STT-MRAM               |

| Density                   | 4Mbit, 1Mbit                                                                            | 4Mbit, 1Mbit           |

| Voltage - V <sub>CC</sub> | 3.0 to 3.6V                                                                             | 2.7 to 3.6V            |

| Interface                 | SPI                                                                                     | SPI                    |

| Bus Width                 | x1                                                                                      | x1                     |

| Mode                      | 0,3                                                                                     | 0,3                    |

| Frequency (MHz max)       | 50 (SDR)                                                                                | 50 (SDR)               |

| Endurance <sup>1</sup>    | Unlimited                                                                               | $10^{14}$              |

| Data Retention (yrs)      | >20                                                                                     | >20                    |

| Temperature Range         | 0°C to +70°C<br>-40°C to +85°C<br>-40°C to +105°C<br>-40°C to +125°C (AEC-Q100 Grade 1) | ✓<br>✓<br>✓<br>✓       |

| Package                   | 8-WSON / 8-DFN / 8-DFN Small Flag<br>8-SOIC                                             | ✓<br>✓                 |

Note 1: Everspin does not list actual endurance number. MRAM devices have a finite number of write cycles. "Unlimited" is typically in reference to other non-volatile memories such as NOR or NAND with endurances of  $10^5$  to  $10^6$  cycles.

### 3. 8-Pad WSON Pinout Comparison

The Avalanche AS3004101 is offered in two industry-standard packages: 8-pad WSON and 8-pin SOIC.

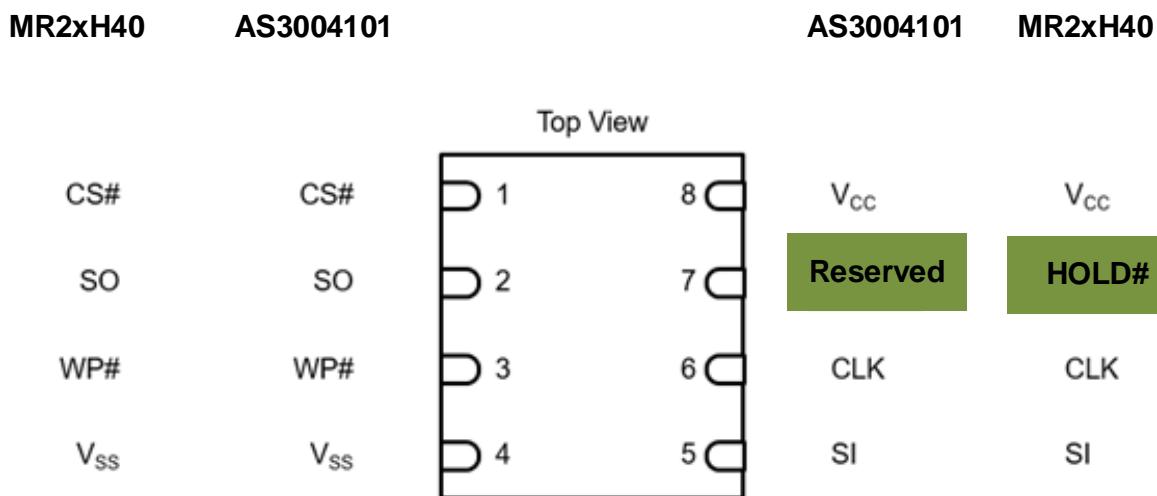

The 8-pad WSON has the same footprint as the 8-pad DFN and 8-pad DFN Small Flag the MR2xH40 is offered in. Figure 1 compares the WSON pinouts of the AS3004101 to the MR2xH40.

**Figure 1: 8-WSON vs DFN/DFN Small Flag Pinout Comparison**

The pinout of the AS3004101 is the same as the MR2xH40. Everspin supports the HOLD# pin which is a legacy feature not commonly used.

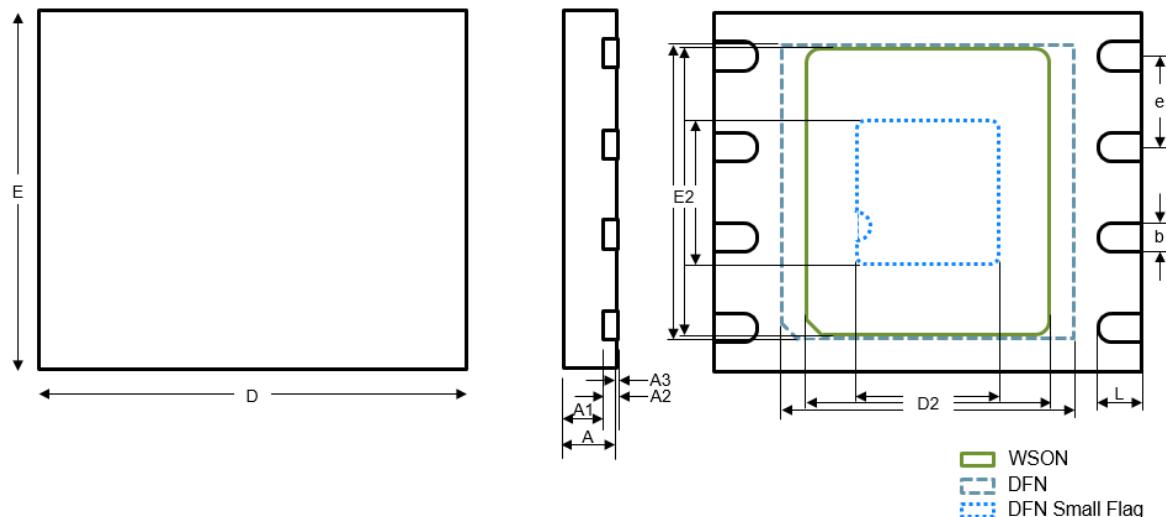

*Figure 2: WSON vs DFN/DFN Small Flag Dimension Comparison*

Table 2 lists the differences in dimensions of the three packages.

*Table 2: Package Dimensions*

| Package        | A         | A1       | A2          | A3          | D          | E         | b          | D2        | E2       | e          | L         |

|----------------|-----------|----------|-------------|-------------|------------|-----------|------------|-----------|----------|------------|-----------|

|                | Thickness | Standoff | Mold Thick. | Lead Thick. | Body Width | Body Len. | Lead Width | Pad Width | Pad Len. | Lead Pitch | Lead Len. |

| WSON           | 0.75      | 0.02     | 0.55        | 0.2 Ref     | 6.00       | 5.00      | 0.40       | 3.40      | 4.00     | 1.27 BSC   | 0.60      |

| DFN            | 0.95      | 0.025    | 0.747       | 0.203       | 6.00       | 5.00      | 0.40       | 4.10      | 4.10     | 1.27 BSC   | 0.60      |

| DFN Small Flag | 0.95      | 0.025    | 0.747       | 0.203       | 6.00       | 5.00      | 0.40       | 2.00      | 2.00     | 1.27 BSC   | 0.60      |

With a package thickness of 0.75 mm, the 8-WSON is thinner than the either DFN or DFN small Flag with a thickness of 0.95 mm. The thinner package offered by the AS3004101 is an advantage for systems with height restrictions.

The exposed pad on the bottom of the package is different for the three packages. PCB's designed for either DFN or DFN small flag will accommodate the Avalanche WSON exposed metal pad.

## 4. Command (Op Code) Comparison

The AS3004101 supports a superset of the commands supported by the MR2xH40. A comparison of the Op Codes is listed in Table 3.

*Table 3: Op Code Comparison*

| Instruction Name      | Op Code | MR2xH40 | AS3004101 | Comment                                   |

|-----------------------|---------|---------|-----------|-------------------------------------------|

| Write Enable          | WREN    | 06h     | ✓         |                                           |

| Write Disable         | WRDI    | 04h     | ✓         | ✓                                         |

| Read Status Register  | RDSR    | 05h     | ✓         | ✓                                         |

| Write Status Register | WRSR    | 01h     | ✓         | ✓                                         |

| Read Memory           | READ    | 03h     | ✓         | ✓                                         |

| Write Memory          | WRTE    | 02h     | ✓         | ✓                                         |

| Enter Sleep Mode      | DPDE    | B9h     | ✓         | ✓                                         |

| Exit Sleep Mode       | DPDX    | ABh     | ✓         | ✓                                         |

| Read Device ID        | RDID    | 9Fh     | -         | ✓ Everspin does not support this function |

## 5. Registers

The AS3004101 provides a superset of registers to access features not supported by the MR2xH40. A comparison of the AS3004101 and the MR2xH40 registers is listed in Table 4

*Table 4: Register Comparison*

| Register Name                  | MR2xH40 | AS3004101 | Comment                                 |

|--------------------------------|---------|-----------|-----------------------------------------|

| Status Register                | ✓       | ✓         |                                         |

| Device Identification Register | -       | ✓         | Everspin does not support this register |

The Status Register functions for the AS3004101 and the MR2xH40 are the same for bits SR[0], SR[1], SR[2], SR[3] and SR7. The AS3004101 uses SR[4]-SR[5] to provide additional features not supported by the MR2xH40. Table 5 lists the Status Register bit definition for the AS3004101 and MR2xH40.

**Note: The AS3004101 additional features are set after the device has boot-up. The default state of the status registers are same for both the AS3004101 and MR2xH40. See Table 6: Status Register – Default State Comparison.**

**Table 5: Status Register – Bit Definition Comparison**

| Bits  | MR2xH40     | AS3004101 | Comment                                                                                                                                                                                                            |

|-------|-------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SR[7] | SRWD        | WP#EN     | Hardware based WP# Protection Enable/Disable.<br>1: Protection Enabled – write protects when WP# is Low<br>0: Protection Disabled – Doesn't write protect when WP# is Low<br><b>Functionally the same.</b>         |

| SR[6] | Do Not Care | Reserved  |                                                                                                                                                                                                                    |

| SR[5] | Do Not Care | TBSEL     | Software Top/Bottom Memory Array Protection Selection.<br>1: Bottom Protection Enabled (Lower Address Range)<br>0: Top Protection Enabled (Higher Address Range)<br><b>Note: Everspin only supports Top Block.</b> |

| SR[4] | Do Not Care | BPSEL[2]  | High order Block Protection Bit provides additional memory array protection areas.<br><b>Note: Not supported by Everspin. Refer to 6. Block Protection Configuration for more detail.</b>                          |

| SR[3] | BP1         | BPSEL[1]  | Block Protection Bits                                                                                                                                                                                              |

| SR[2] | BP0         | BPSEL[0]  | Block Protection Bits                                                                                                                                                                                              |

| SR[1] | WEL         | WREN      | Write Operation Protection Enable/Disable.<br>1: Write Operation Protection Disabled<br>0: Write Operation Protection Enabled<br><b>Functionally the same.</b>                                                     |

| SR[0] | Do Not Care | RSVD      | 'Reserved for future use' on Avalanche.<br><b>Functionally the same.</b>                                                                                                                                           |

The Status Register default setting on boot up for both the AS3004101 and the MR2xH40 is 00h. This means that both parts are initiated in the same state with regard to write protection which is disabled for the Status Register and the memory array and Top Protection selected. The Serial Number write protection feature SR[6] is not a concern as the Serial Number feature is not supported on the MR2xH40 (e.g. do not care).

**Table 6: Status Register – Default State Comparison**

| Bits  | MR2xH40 | AS3004101 | Comment                                                                                                                                         |

|-------|---------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| SR[7] | 0       | 0         | Everspin: Protection Disabled – Doesn't write protect when WP# is Low<br>Avalanche: Protection Disabled – Doesn't write protect when WP# is Low |

| SR[6] | 0       | 0         | Everspin: Function not supported<br>Avalanche: Reserved                                                                                         |

| SR[5] | 0       | 0         | Everspin: Only Supports Top Protection<br>Avalanche: Top Protection Enabled (Higher Address Range)                                              |

| SR[4] | 0       | 0         |                                                                                                                                                 |

| SR[3] | 0       | 0         | Everspin: All Blocks Unprotected<br>Avalanche: All Blocks Unprotected                                                                           |

| SR[2] | 0       | 0         |                                                                                                                                                 |

| SR[1] | 0       | 0         | Everspin: Write Operation Protection Enabled<br>Avalanche: Write Operation Protection Enabled                                                   |

| SR[0] | 0       | 0         | Everspin: N/A<br>Avalanche: N/A                                                                                                                 |

## 6. Block Protection Configuration

The AS3004101 provides four additional sizes for protecting the memory array in comparison to the MR2xH40. To support this, the AS3004101 uses an extra bit in the Status Register SR[4] as BLSEL[2] as the high-order Block Protection Bit. BPSEL[2] on Avalanche device must be set appropriately to match Everspin configuration. Table 7 compares the Block Protection for the AS3004101 and the MR2xH40.

*Table 7: Block Protection Comparison*

| Block      | MR2xH40       |     |

|------------|---------------|-----|

| Protected  | BP1           | BP0 |

| None       | 0             | 0   |

| Upper 1/64 | Not Supported |     |

| Upper 1/32 | Not Supported |     |

| Upper 1/16 | Not Supported |     |

| Upper 1/8  | Not Supported |     |

| Upper 1/4  | 0             | 1   |

| Upper 1/2  | 1             | 0   |

| All        | 1             | 1   |

| AS3004101 |          |          |

|-----------|----------|----------|

| BPSEL[2]  | BPSEL[1] | BPSEL[0] |

| 0         | 0        | 0        |

| 0         | 0        | 1        |

| 0         | 1        | 0        |

| 0         | 1        | 1        |

| 1         | 0        | 0        |

| 1         | 0        | 1        |

| 1         | 1        | 0        |

| 1         | 1        | 1        |

## 7. DC Parameters

Table 8 compares the DC Parameters for the MR2xH40 and AS3004204. For most parameters the Avalanche AS3004204 provides an advantage over the MR2xH40.

**Table 8: DC Parameter Comparison**

| Parameter                    | Symbol                 | MR2xH40                                                                                               | AS3004101                                                                                             | Comments                                                                                                                                                        |

|------------------------------|------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supply Voltage               | V <sub>CC</sub>        | 3.0V to 3.6V                                                                                          | 2.7V to 3.6V                                                                                          |                                                                                                                                                                 |

| Read Current (1-1-1)         | I <sub>READ1</sub>     | 13.8 mA @50MHz                                                                                        | 8 mA @50MHz                                                                                           |                                                                                                                                                                 |

| Write Current (1-1-1)        | I <sub>WRITE1</sub>    | 33 mA @50MHz                                                                                          | 14 mA @50MHz                                                                                          |                                                                                                                                                                 |

| Standby Current <sup>1</sup> | I <sub>SB</sub>        | 90 $\mu$ A                                                                                            | 160 $\mu$ A                                                                                           |                                                                                                                                                                 |

| Deep Power Down <sup>1</sup> | I <sub>DPD</sub>       | 15 $\mu$ A                                                                                            | 5 $\mu$ A                                                                                             |                                                                                                                                                                 |

| Input High Voltage           | V <sub>IH</sub>        | 2.2V to V <sub>CC</sub> +0.3                                                                          | 0.7xV <sub>CC</sub> to V <sub>CC</sub> +0.3                                                           | Avalanche supports lower V <sub>IH</sub> (min) of 2.1V @ 3.0V V <sub>CC</sub>                                                                                   |

| Input Low Voltage            | V <sub>IL</sub>        | -0.5V to 0.8V                                                                                         | -0.3V to 0.3xV <sub>CC</sub>                                                                          | Avalanche supports higher V <sub>IL</sub> (max) of 0.9V @ 3.0V V <sub>CC</sub> .<br>Voltage swings cannot go below V <sub>IL</sub> (min) of -0.3V for Avalanche |

| Output High Voltage Level    | V <sub>OH</sub>        | V <sub>CC</sub> -0.2V (min)<br>I <sub>OH</sub> =-100 $\mu$ A<br>2.4V (min)<br>I <sub>OH</sub> = -4 mA | V <sub>CC</sub> -0.2V (min)<br>I <sub>OH</sub> =-100 $\mu$ A<br>2.4V (min)<br>I <sub>OH</sub> = -1 mA | No change required. Note: V <sub>OH</sub> must remain within logic levels for inputs on heavily loaded system buses                                             |

| Output Low Voltage Level     | V <sub>OL</sub>        | V <sub>SS</sub> +0.2V (max),<br>I <sub>OL</sub> =100 $\mu$ A<br>0.4V (max)<br>I <sub>OL</sub> = 4 mA; | 0.2V (max),<br>I <sub>OL</sub> =150 $\mu$ A<br>0.4V (max)<br>I <sub>OL</sub> = 2 mA;                  | No change required. Note: V <sub>OL</sub> must remain within logic levels for inputs on heavily loaded system buses                                             |

| Magnetic Field During Write  | H <sub>max_write</sub> | 12,000 A/m                                                                                            | 24,000 A/m                                                                                            | Avalanche has a higher magnetic immunity                                                                                                                        |

| Magnetic Field During Read   | H <sub>max_read</sub>  | 12,000 A/m                                                                                            | 24,000 A/m                                                                                            | Avalanche has a higher magnetic immunity                                                                                                                        |

## 8. AC Parameters

Table 9 compares selected AC Parameters for the MR2xH40 and AS3004204. The Avalanche AS3004204 provides equivalent or better timing than the MR2xH40.

**Table 9: AC Parameter Comparison**

| Parameter                        | Symbol             | MR2xH40           | AS3004204         | Comments                                                                                                                                                                                                              |

|----------------------------------|--------------------|-------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deep Power Down Entry Time       | t <sub>EDPD</sub>  | 3 $\mu$ s (min)   | 3 $\mu$ s (min)   |                                                                                                                                                                                                                       |

| Deep Power Down Exit Time        | t <sub>EXDPD</sub> | 400 $\mu$ s (min) | 400 $\mu$ s (min) |                                                                                                                                                                                                                       |

| Output Disable Time (w.r.t. CS#) | t <sub>HZCS</sub>  | 12 ns (min)       | 7.0 ns (max)      | Avalanche specifies this parameter as a Maximum while Everspin specifies a Minimum.<br><br>Avalanche device ensures the bus is available after 7ns while the Everspin device releases the output sometime after 12ns. |

## 9. Power-Up and Power-Down Behavior

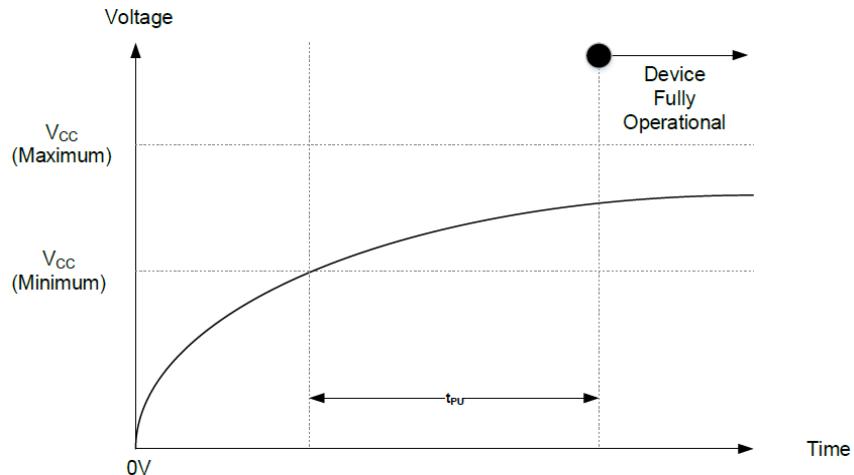

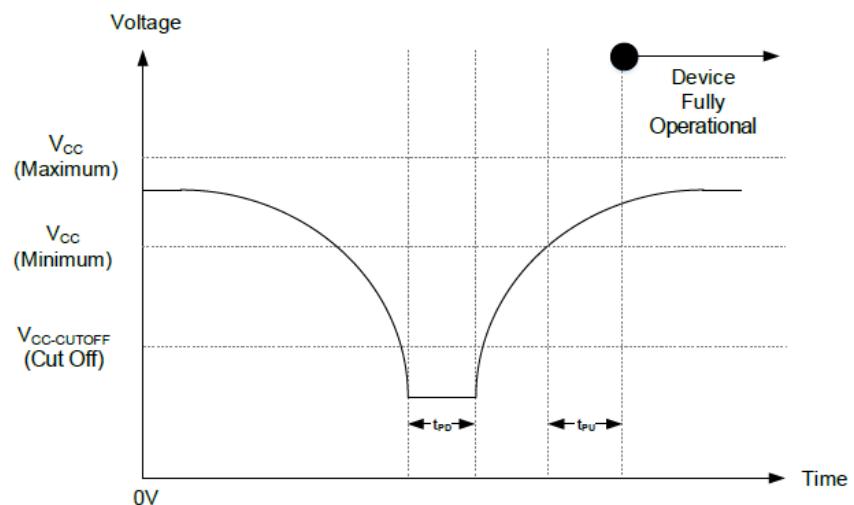

Figure 3 and Figure 4 depict the Power-Up and Power-Down behavior. The AS3004204 provides a shorter Power-Up to first instruction time than the MR2xH40.

*Figure 3: Power-Up Behavior*

*Figure 4: Power-Down Behavior*

*Table 10: Power-Up and Power-Down Comparison*

| Parameter                              | Symbol   | MR2xH40           | AS3004204          | Comment                            |

|----------------------------------------|----------|-------------------|--------------------|------------------------------------|

| $V_{CC}$ Power Up to First Instruction | $t_{PU}$ | 400 $\mu$ s (min) | 250 $\mu$ s (min)  | Avalanche power-up time is shorter |

| $V_{CC}$ Ramp Up Time                  | $R_{VR}$ | Not Listed        | 30 $\mu$ s/V (min) |                                    |

| $V_{CC}$ Ramp Down Time                | $R_{VF}$ | Not Listed        | 20 $\mu$ s/V (min) |                                    |

## 10. Summary

The features of the AS3004204 provide system designers a straightforward migration path from the MR2xH420 at the same system performance for read and write operations with lower power consumption.

## 11. Revision History

| Revision | Date       | Change Summary  |

|----------|------------|-----------------|

| REV A    | 09/22/2020 | Initial release |