Texas Instruments DS90UB941AS-Q1 Bridge Serializers

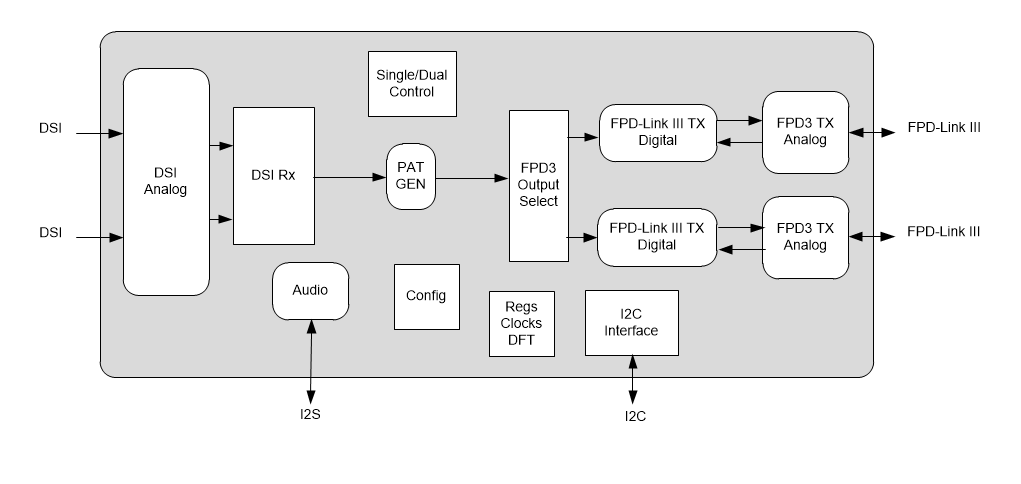

Texas Instruments DS90UB941AS-Q1 DSI to FPD-Link III Bridge Serializers are ideal for automotive infotainment applications. The DS90UB941AS-Q1, when paired with an FPD-Link III DS90UB940N-Q1, DS90UB948-Q1, DS90UB924-Q1, DS90UB926Q-Q1 or DS90UB928Q-Q1 deserializer, can supply high-speed serial streams over single-ended coaxial cables. These devices supply high-speed serial streams over 100Ω, differential shielded twisted-pair (STP), and shielded twisted-quad (STQ) cables. The DS90UB941AS-Q1 can support symmetric and asymmetric splitting in response to the rise in the number and variance of displays in infotainment systems.The DSI to FPD-Link III Bridge Serializers can consolidate video data over two differential pairs to simplify system design and decrease the interconnect size and weight of the application. The FPD-Link III interface supports video and audio data transmission and full-duplex control. This support includes I2C communication and up to eight I2S audio channels over the same high-speed serial link. Low voltage differential signaling, data scrambling, and randomization minimize the EMI.

The Texas Instruments DS90UB941AS-Q1 serializes a MIPI DSI input that supports a video resolution of up to 2K, WUXGA, and 1080p60 with 24-bit color depth. The device supports up to WXGA and 720p resolutions with 24-bit color depth over one differential link in backward-compatible mode.

Features

- AEC-Q100 qualified for automotive applications with the following results

- Device temperature grade 2 (-40°C to +105°C ambient operating temperature)

- Single and dual FPD-Link III outputs

- Single-link: up to 105MHz pixel clock

- Dual-link: up to 210MHz pixel clock

- Symmetric and asymmetric video splitting

- Supports pixel clock frequency up to 210MHz for 3K (2880x1620) at 30Hz, QXGA (2048x1536), 2K (2880x1080), WUXGA (1920x1200), or 1080p60 (1920x1080) resolutions with 24-bit color depth

- MIPI D-PHY / Display Serial Interface (DSI) receiver provides a high-bandwidth interface to a video processor or FPGA

- Dual DSI input ports with up to four data lanes each

- Up to 1.5Gbps per lane

- Superframe with symmetric and asymmetric unpacking capability

- ECC and CRC generation

- Virtual channel capability

Applications

- Automotive infotainment

- IVI head units and HMI modules

- Central information displays

- Digital instrument clusters

- Rear seat entertainment systems

Functional Diagram