Skyworks Solutions Inc. Si5330 Clock Buffers/Level Translators

Skyworks Solutions Inc. Si5330 Clock Buffers/Level Translators are low-jitter, low-skew fanout buffers designed for high-performance PCB clock distribution applications. These Si5330 buffers and translators support single-ended or differential input clock signals. The devices produce four differential/eight single-ended, low-jitter output clocks from a single input clock allowing them to function as clock level translators. The output driver voltage of these devices is 1.5, 1.8V, 2.5V, or 3.3V and is independent of the core supply of 1.8V, 2.5V, or 3.3V. These buffers/translators consume low power with just 10mA typical core current. These clock buffers/level translators have 150fs RMS of additive jitter and 100ps of output-output skew. The typical applications include high-speed clock distribution, ethernet switches and routers, SONET/SDH, fiber channels, and telecom line cards.The Skyworks Solutions Inc. Si5330 Clock Buffers/Level Translators are available in a compact 4mm × 4mm QFN-24 package ideal for space-constrained applications.

Features

- Supports single-ended/differential input clock signals

- Generates four differential (LVPECL, LVDS, HCSL) or eight single-ended (CMOS, SSTL,HSTL) outputs

- Provides signal level translation:

- Differential to single-ended

- Single-ended to differential

- Differential to differential

- Single-ended to single-ended

- Wide frequency range:

- 5HMz to 710MHz LVPECL, LVDS

- 5HMz to 250 MHz HCSL

- 5HMz to 350 MHzSSTL, HSTL

- 5HMz to 200 MHz CMOS

- 150fs RMS typical additive jitter

- 100ps output-output skew:

- 2.5ns typical propagation delay

- 1.8V, 2.5V, or 3.3V single-core supply with excellent PSRR

- 1.5V, 1.8V, 2.5V, or 3.3V output driver supply voltage independent of core supply

- Loss of Signal (LOS) indicator allows system clock monitoring

- Output Enable (OEB) pin allows glitchless control of output clocks

- 10mA low power typical core current

- Industrial temperature range

- 4mm × 4mm QFN-24 package

Applications

- High-speed clock distribution

- Ethernet switches and routers

- SONET/SDH

- PCI express 2.0/3.0

- Fiber channels

- MSAN/DSLAM/PON

- Telecom line cards

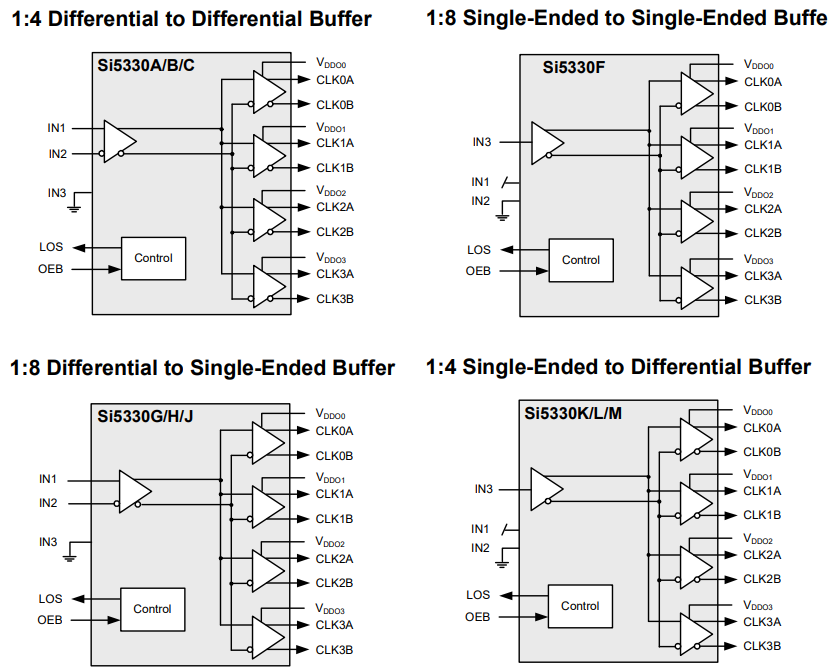

Simplified Block Diagram

Block Diagrams

Paskelbta: 2022-05-20

| Atnaujinta: 2022-06-21