Lattice Semiconductor MachXO PLDs

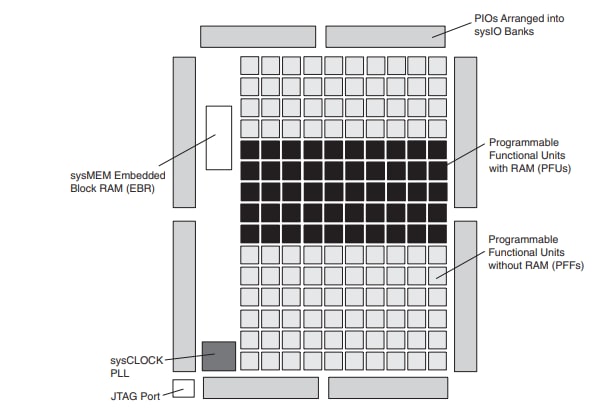

Lattice Semiconductor MachXO PLDs are non-volatile, infinitely reconfigurable Programmable Logic Devices (PLDs) designed for applications traditionally implemented using CPLDs or low-density FPGAs. Widely adopted in a broad range of applications that require general purpose I/O expansion, interf ace bridging, and power-up management functions, MachXO PLDs offer the benefits of increased system integration by providing embedded memory, built-in PLLs, high performance LVDS I/O, remote field upgrade (TransFR™ technology) and a low power sleep mode, all in a single-device. Designed for a broad range of low density applications including system control designs, the MachXO PLD family is used in a variety of end markets including consumer, automotive, communications, computing, industrial, and medical. Lattice Semiconductor LCMXO2280 MachXO PLDs offer a density of 2280 LUTs.Features

- Non-volatile, infinitely reconfigurable, instant-on powers up in microseconds

- Single-chip, no external configuration memory required

- Sleep mode allows up to 100x static current reduction

- TransFR™ Reconfiguration (TFR) In-field logic update while the system operates

- High I/O to logic density

- 256 to 2280 LUT4s

- 73 to 271 I/Os with extensive package options

- Embedded and distributed memory

- Up to 27.6Kbits sysMEM™ embedded block RAM

- sysCLOCK™ PLLs

- Up to two analog PLLs per device

- Clock multiply, divide, and phase shifting

- Flexible I/O buffer

- Programmable sysIO™ buffer supports a wide range of interfaces:

- LVCMOS 3.3/2.5/1.8/1.5/1.2

- LVTTL

- PCI

- LVDS, Bus-LVDS, LVPECL, RSDS

- Programmable sysIO™ buffer supports a wide range of interfaces:

- System-Level Support

- IEEE Standard 1149.1 boundary scan

- Onboard oscillator

Layout

Paskelbta: 2012-03-23

| Atnaujinta: 2022-03-11