## Features

- Tx Gain: 11 dB

- Tx P<sub>SAT</sub>: 23 dBm

- Rx Gain: 24 dB

- Rx Noise Figure: 2 dB

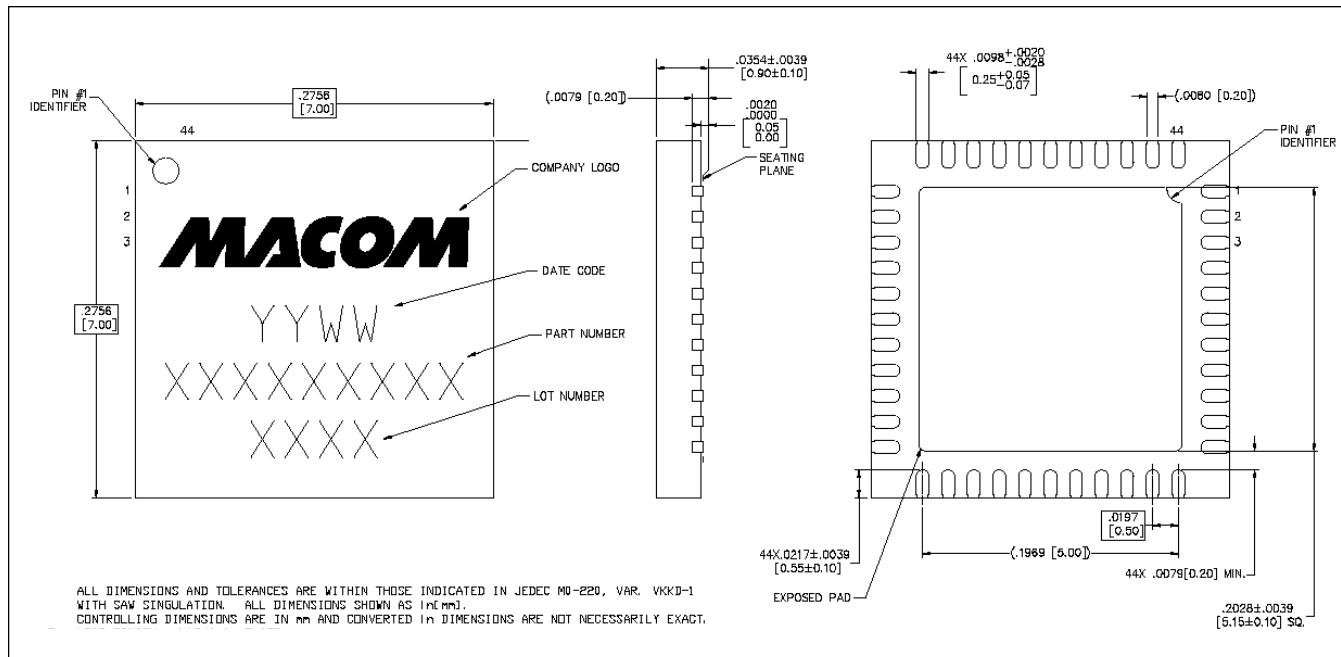

- Lead-Free 7 mm 44-Lead PQFN Package

- RoHS\* Compliant

## Description

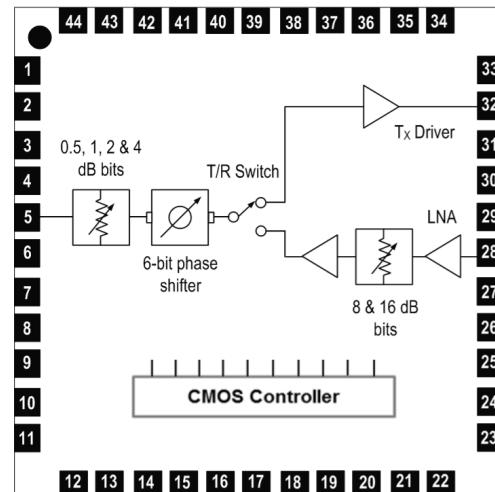

The MAMF-011015 is an 8 - 11 GHz multifunction GaAs MMIC designed for communication radar and weather applications. It functions in combination with an advanced Si serial-controller which addresses the GaAs chip for the necessary Rx/Tx selection path and the required signal controls, along with several other functionalities.

The MAMF-011015's GaAs chip utilizes a 0.25  $\mu$ m pHEMT GaAs process which has been optimized for RF power, low noise, and RF signal control applications which is ideal for high levels of integration on a single IC. This GaAs MMIC includes a "Common path" circuit where it incorporates a 4-BIT digital attenuator, a 6-BIT digital phase shifter, and a T/R SPDT switch for Rx/Tx selection. The "Rx path" incorporates a low noise amplifier and 2 additional higher attenuation bits. The "Tx path" driver amplifier is designed to deliver sufficient RF power and gain for an outside power amplifier.

The MAMF-011015's Si serial-controller chip is designed to address the GaAs chip's common path signal control components along with several other functionalities such as external G/D control enabling or disabling internal gate/drain switching of the LNA or driver amplifier. When internal gate switching is disabled, external drain switching may be used for fast T/R switching (pulsing).

## Ordering Information<sup>1</sup>

| Part Number        | Package        |

|--------------------|----------------|

| MAMF-011015-TR0500 | 500 Piece Reel |

| MAMF-011015-001SMB | Sample Board   |

1. Reference Application Note M513 for reel size information.

## Functional Schematic

## Pin Configuration<sup>2</sup>

| Pin #                             | Function         | Pin #           | Function            |

|-----------------------------------|------------------|-----------------|---------------------|

| 1 - 3, 9 - 11, 19, 36, 39, 42, 44 | No Connection    | 24              | SW2B50              |

| 4, 6, 8, 27, 29, 31, 33           | Ground           | 25              | V <sub>OPT2</sub>   |

| 5                                 | Common           | 26              | V <sub>G_LNA</sub>  |

| 7, 22                             | V <sub>EE</sub>  | 28              | R <sub>x</sub> IN   |

| 12                                | V <sub>CC2</sub> | 30              | V <sub>CC1</sub>    |

| 13                                | SER IN           | 32              | T <sub>x</sub> OUT  |

| 14                                | CLK              | 34              | DET                 |

| 15                                | LE               | 35              | REF                 |

| 16                                | RS               | 37              | V <sub>DD2</sub>    |

| 17                                | TR               | 38              | V <sub>DD1</sub>    |

| 18                                | EN               | 40              | TEMP SENSE          |

| 20                                | SWEN2            | 41              | V <sub>G_PA12</sub> |

| 21                                | SER OUT          | 43              | G/D                 |

| 23                                | SW2A50           | 45 <sup>3</sup> | Ground              |

2. MACOM recommends connecting unused (no connection) pins to RF and DC ground.

3. The exposed pad centered on the package bottom must be connected to RF and DC ground.

<sup>1</sup> \* Restrictions on Hazardous Substances, compliant to current RoHS EU directive.

## Description of Pin Functions

| Pin    | Function            | Description of Function                                                                                                                                                      |

|--------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4, 6   | Ground              | RF and DC Ground (RF Launch)                                                                                                                                                 |

| 5      | Common              | RF Common Port - See Block Diagram                                                                                                                                           |

| 7      | V <sub>EE</sub>     | Negative Supply for Logic Driver (Defines negative Voltages for GaAs switch outputs)                                                                                         |

| 8      | Ground              | ED Ground                                                                                                                                                                    |

| 12     | V <sub>CC2</sub>    | Positive Supply for Logic Driver                                                                                                                                             |

| 13     | SER IN              | Serial Input for Data Stream                                                                                                                                                 |

| 14     | CLK                 | Clock for Data Stream                                                                                                                                                        |

| 15     | LE                  | Load Enable for Data Stream                                                                                                                                                  |

| 16     | RS                  | Register Select - Selects from two interleaved data streams                                                                                                                  |

| 17     | TR                  | Transmit/Receive Switch Select; Works with "EN" to enable or disable LNA or driver amp                                                                                       |

| 18     | EN                  | The enable control can disable all amplifiers; Works with "TR" to disable amplifiers in path that is off                                                                     |

| 20     | SWEN2               | Determines if External PIN switch is driven (see truth table)                                                                                                                |

| 21     | SER OUT             | Serial Output for Data Stream                                                                                                                                                |

| 22     | V <sub>EE</sub>     | Negative Supply for Logic Driver (Defines negative Voltage for PIN switch outputs)                                                                                           |

| 23     | SW2A50              | Control for external PIN diode switch                                                                                                                                        |

| 24     | SW2B50              | Control for external PIN diode switch (complement of SW2A50)                                                                                                                 |

| 25     | V <sub>OPT2</sub>   | Positive Supply for Logic Driver (Defines positive Voltage for PIN switch outputs)                                                                                           |

| 26     | V <sub>G_LNA</sub>  | Provides gate bias (negative voltage) for LNA (this is a fixed, not adjustable voltage)                                                                                      |

| 27, 29 | Ground              | RF and DC Ground (RF Launch)                                                                                                                                                 |

| 28     | R <sub>x</sub> IN   | Receive RF input - See block diagram                                                                                                                                         |

| 30     | V <sub>CC1</sub>    | Positive bias for LNA                                                                                                                                                        |

| 31, 33 | Ground              | RF and DC Ground (RF Launch)                                                                                                                                                 |

| 32     | T <sub>x</sub> OUT  | Transmit RF output - See block diagram                                                                                                                                       |

| 34     | DET                 | Detector output, which monitors transmit power                                                                                                                               |

| 35     | REF                 | Reference output for the detector (using a differential amplifier, this is used to compensate for the temperature drift of the detector output)                              |

| 37     | V <sub>DD2</sub>    | Bias for the second stage of the driver amplifier                                                                                                                            |

| 38     | V <sub>DD1</sub>    | Bias for the first stage of the driver amplifier                                                                                                                             |

| 40     | TEMP SENSE          | Temperature sensor to output the variation of chip temperature. The temperature sensor is located on chip, close to the driver amplifiers                                    |

| 41     | V <sub>G_PA12</sub> | Gate bias (negative voltage) for first two driver amp stages (this is a fixed, not adjustable voltage)                                                                       |

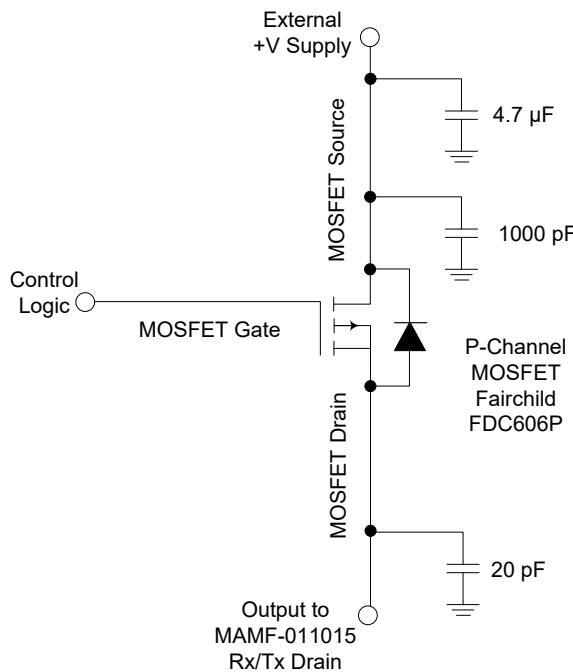

| 43     | G/D                 | G/D Select switch; if the LNA (R <sub>x</sub> path) and Driver Amplifier (T <sub>x</sub> Path) are gate switched (by CMOS driver) or drain switched (using external MOSFETs) |

| 45     | Ground              | Exposed pad centered on the package bottom must be connected to RF and DC ground                                                                                             |

**Electrical Specifications: Freq. = 8.5, 9.5, 10.5 GHz, T<sub>A</sub> = 25°C, Z<sub>0</sub> = 50 Ω<sup>4,5,6,7</sup>**

**T<sub>X</sub> State bias:**

V<sub>DD1</sub> = V<sub>DD2</sub> = 5 V, V<sub>G\_PA12</sub> = -5 V, V<sub>CC1</sub> = 3.3 V, V<sub>G\_LNA</sub> = -5 V, V<sub>CC2</sub> = V<sub>OPT2</sub><sup>8</sup> = 5 V, V<sub>EE</sub><sup>9</sup> = -5 V, TR = 5 V, SWEN2 = G/D = 0 V

| Symbol                          | Parameter                                                                 | Conditions                                                                               | Units | Min.    | Typ.  | Max. |

|---------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------|---------|-------|------|

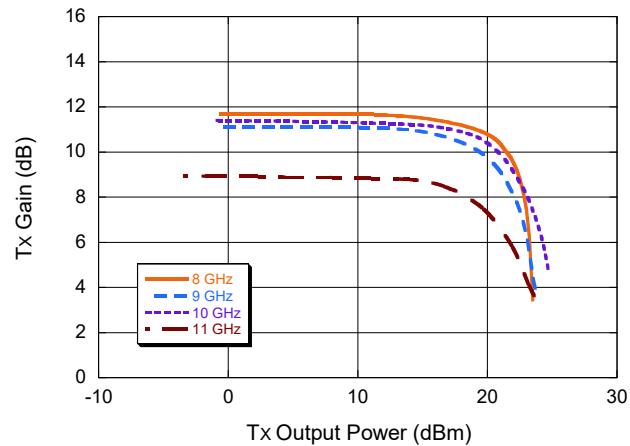

| T <sub>X</sub> Gain             | Transmit Gain (Common to T <sub>X_out</sub> )                             | R <sub>X</sub> Amplifier OFF, (0 dB ATT, 0°Phase)<br>Freq. 8 - 9.5 GHz<br>Freq. 10.5 GHz | dB    | 10<br>9 | 11    | —    |

| T <sub>X</sub> IN RL            | Transmit Input Return Loss                                                | “                                                                                        | dB    | 10      | 14    | —    |

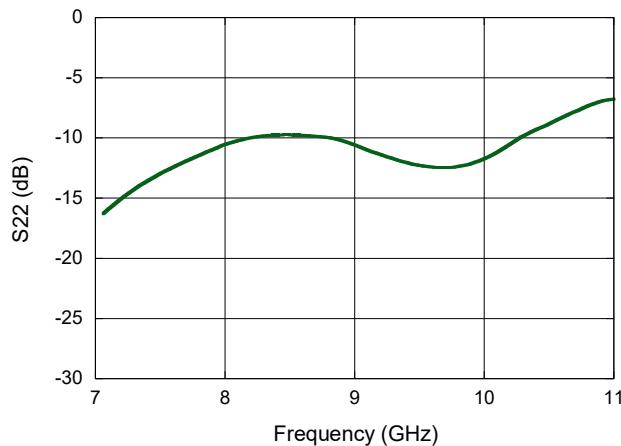

| T <sub>X</sub> OUT RL           | Transmit Output Return Loss                                               | “                                                                                        | dB    | 8       | 9     | —    |

| T <sub>X</sub> P1dB             | Transmit P1dB                                                             | “                                                                                        | dBm   | 21.5    | 23    | —    |

| DPS                             | Phase Shifter (6-Bit) LSB                                                 | R <sub>X</sub> Amplifier OFF, (0 dB ATT)                                                 | deg   | —       | 5.625 | —    |

| DPS_Phase_Er                    | RMS Phase Error                                                           | “                                                                                        | deg   | —       | 3.0   | —    |

| DPS_Amp_Er                      | RMS Amplitude Error                                                       | “                                                                                        | dB    | —       | 0.6   | —    |

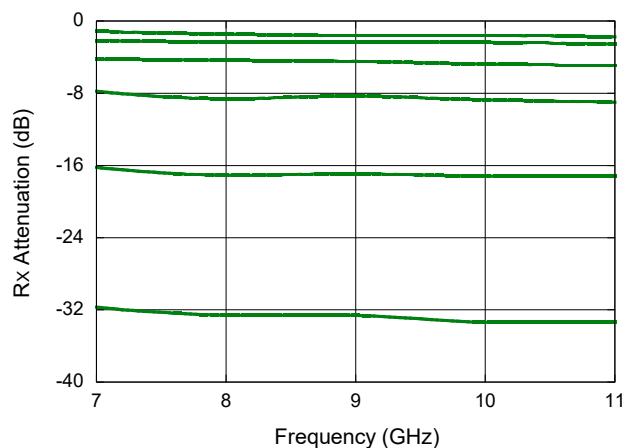

| DAT                             | Attenuator (4-Bit) LSB                                                    | R <sub>X</sub> Amplifier OFF, (0°Phase)                                                  | dB    | —       | 0.5   | —    |

| DPS_DAT_Er                      | RMS Attenuation Accuracy Error                                            | “                                                                                        | dB    | —       | 0.4   | —    |

| T <sub>X</sub> Idq              | Total T <sub>X</sub> Drain Current (V <sub>DD1</sub> , V <sub>DD2</sub> ) | “                                                                                        | mA    | —       | 140   | —    |

| I <sub>DD1</sub>                | Quiescent supply current of V <sub>DD1</sub>                              | R <sub>X</sub> Amplifier OFF, (0 dB ATT, 0°Phase)                                        | mA    | 28      | 43    | 60   |

| I <sub>DD2</sub>                | Quiescent supply current of V <sub>DD2</sub>                              | “                                                                                        | mA    | 60      | 98    | 125  |

| I <sub>G_PA12</sub>             | Quiescent supply current of V <sub>G_PA12</sub>                           | “                                                                                        | mA    | —       | 10    | —    |

| I <sub>CC1</sub>                | Quiescent supply current of V <sub>CC1</sub>                              | “                                                                                        | mA    | —       | 0     | —    |

| I <sub>G_LNA</sub>              | Quiescent supply current of V <sub>G_LNA</sub>                            | “                                                                                        | mA    | —       | 0     | —    |

| I <sub>CC2</sub>                | Quiescent supply current of V <sub>CC2</sub>                              | “                                                                                        | μA    | —       | 0.1   | —    |

| I <sub>EE</sub>                 | Quiescent supply current of V <sub>EE</sub>                               | “                                                                                        | mA    | —       | 1     | 2    |

| I <sub>OPT2</sub> <sup>10</sup> | Quiescent supply current of V <sub>OPT2</sub>                             | “                                                                                        | μA    | —       | 0.1   | —    |

**RF Specifications: Freq. = 8.5, 9.5, 10.5 GHz,  $T_A = 25^\circ\text{C}$ ,  $Z_0 = 50 \Omega^{4,5,6,7}$**

**R<sub>X</sub> State bias:**

$V_{DD1} = V_{DD2} = 5 \text{ V}$ ,  $V_{G\_PA12} = -5 \text{ V}$ ,  $V_{CC1} = 3.3 \text{ V}$ ,  $V_{G\_LNA} = -5 \text{ V}$ ,  $V_{CC2} = V_{OPT2}^8 = 5 \text{ V}$ ,  $V_{EE}^9 = -5 \text{ V}$ ,  $TR = SWEN2 = G/D = 0 \text{ V}$

| Symbol                          | Parameter                                       | Conditions                                         | Units | Min. | Typ.  | Max. |

|---------------------------------|-------------------------------------------------|----------------------------------------------------|-------|------|-------|------|

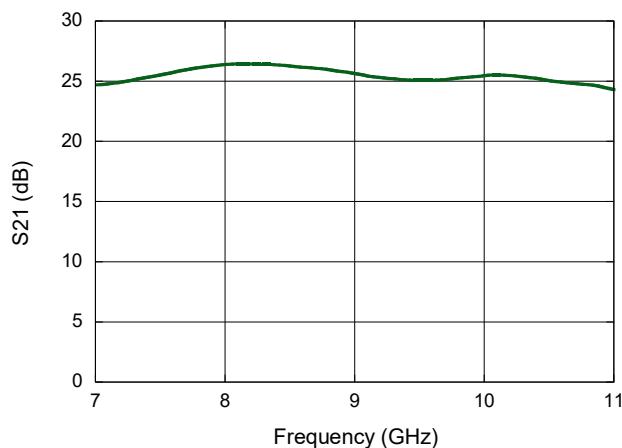

| R <sub>X</sub> Gain             | Receive Gain (R <sub>X</sub> IN to Common )     | T <sub>X</sub> Amplifier OFF (0 dB ATT, 0° Phase)  | dB    | 21   | 24    | —    |

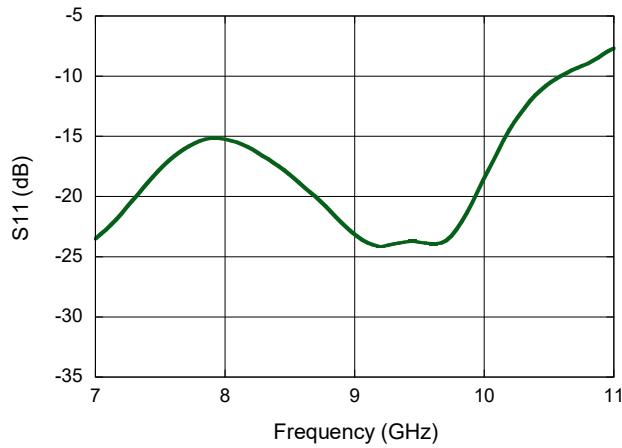

| R <sub>X</sub> IN RL            | Receive Input Return Loss                       | “                                                  | dB    | 10   | 15    | —    |

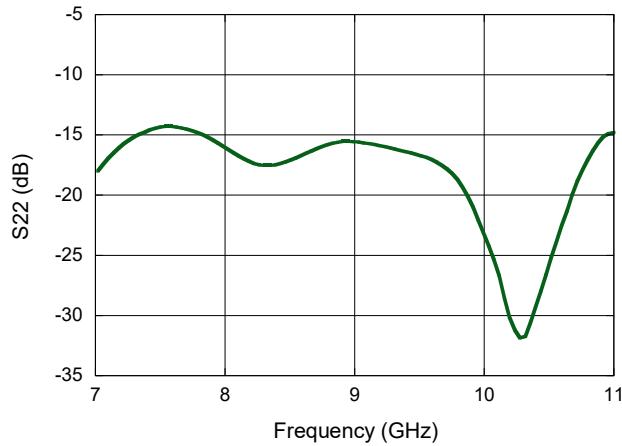

| R <sub>X</sub> OUT RL           | Receive Output Return Loss                      | “                                                  | dB    | 8    | 14    | —    |

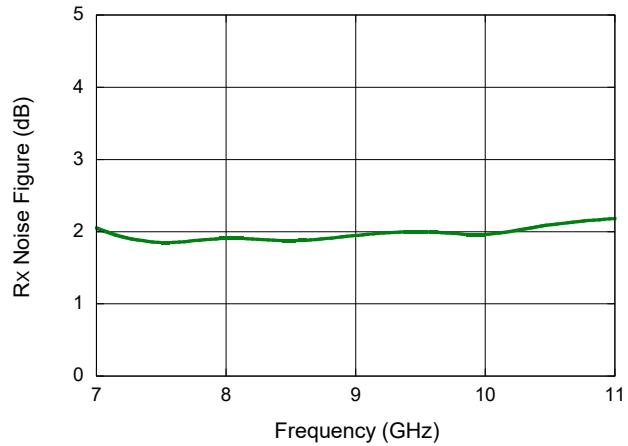

| R <sub>X</sub> NF               | Receive Noise Figure                            | “                                                  | dBm   | —    | 2     | 2.5  |

| R <sub>X</sub> OIP3             | Receive Output OIP3                             | “                                                  | dBm   | 15   | 18    | —    |

| DPS                             | Phase Shifter (6-Bit) LSB                       | T <sub>X</sub> Amplifier OFF (0 dB ATT)            | deg   | —    | 5.625 | —    |

| DPS_Phase_Er                    | RMS Phase Error                                 | “                                                  | deg   | —    | 3.0   | —    |

| DPS_Amp_Er                      | RMS Amplitude Error                             | “                                                  | dB    | —    | 0.6   | —    |

| DAT                             | Attenuator (4-Bit) LSB                          | T <sub>X</sub> Amplifier OFF (0°Phase)             | dB    | —    | 0.5   | —    |

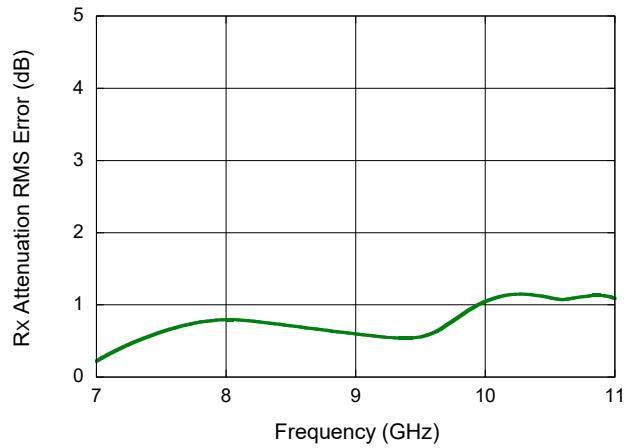

| DPS_DAT_Er                      | RMS Attenuation Accuracy Error                  | “                                                  | dB    | —    | 0.4   | —    |

| I <sub>DD1</sub>                | Quiescent supply current of V <sub>DD1</sub>    | T <sub>X</sub> Amplifier OFF, (0 dB ATT, 0° Phase) | mA    | —    | 0     | 0.5  |

| I <sub>DD2</sub>                | Quiescent supply current of V <sub>DD2</sub>    | “                                                  | mA    | —    | 0.5   | 1.5  |

| I <sub>G_PA12</sub>             | Quiescent supply current of V <sub>G_PA12</sub> | “                                                  | mA    | —    | 10    | —    |

| I <sub>CC1</sub>                | Quiescent supply current of V <sub>CC1</sub>    | “                                                  | mA    | 80   | 110   | 135  |

| I <sub>G_LNA</sub>              | Quiescent supply current of V <sub>G_LNA</sub>  | “                                                  | mA    | —    | 10    | —    |

| I <sub>CC2</sub>                | Quiescent supply current of V <sub>CC2</sub>    | “                                                  | mA    | —    | 0     | 1    |

| I <sub>EE</sub>                 | Quiescent supply current of V <sub>EE</sub>     | “                                                  | mA    | —    | 1     | —    |

| I <sub>OPT2</sub> <sup>10</sup> | Quiescent supply current of V <sub>OPT2</sub>   | “                                                  | µA    | —    | 0.2   | —    |

**Controls for PIN Driver**<sup>4,5,6,7,8,9,10</sup>

**Electrical Specifications: Freq. = 8.5, 9.5, 10.5 GHz, T<sub>A</sub> = 25 °C, Z<sub>0</sub> = 50 Ω**

| Symbol              | Parameter                                                              | Conditions                                                                            | Units | Min.                 | Typ.                  | Max.                 |

|---------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------|----------------------|-----------------------|----------------------|

| R <sub>PSW50</sub>  | Output Pull-up FET On Resistance for SWnA50 and SWnB50 Ports at 25°C   | V <sub>CC2</sub> = V <sub>OPT2</sub> = +5 V,<br>V <sub>EE</sub> = -5 V,<br>50 mA load | Ω     | —                    | 18                    | —                    |

| R <sub>NSW50</sub>  | Output Pull-down FET On Resistance for SWnA50 and SWnB50 Ports at 25°C | V <sub>CC2</sub> = V <sub>OPT2</sub> = +5 V,<br>V <sub>EE</sub> = -5 V,<br>50 mA load | Ω     | —                    | 15                    | —                    |

| V <sub>IH</sub>     | Input High Voltage                                                     | —                                                                                     | V     | 0.7xV <sub>CC2</sub> | V <sub>CC</sub>       | V <sub>CC2</sub>     |

| V <sub>IL</sub>     | Input Low Voltage                                                      | —                                                                                     | V     | GND                  | GND                   | 0.3xV <sub>CC2</sub> |

| V <sub>OHS</sub>    | Output High for Serial Out                                             | I <sub>OH</sub> = -1 mA                                                               | V     | —                    | V <sub>CC</sub> - 0.1 | —                    |

| V <sub>OLS</sub>    | Output Low for Serial Out                                              | I <sub>OL</sub> = +1 mA                                                               | V     | —                    | 0.1                   | —                    |

| I <sub>SOURCE</sub> | DC Output Sourcing Current for SWnA50 and SWnB50 Ports                 | V <sub>CC2</sub> = V <sub>OPT2</sub> = +5 V,<br>V <sub>EE</sub> = -5 V                | mA    | —                    | —                     | 50                   |

| I <sub>SINK</sub>   | DC Output Sinking Current for SWnA50, SWnB50 Ports                     | V <sub>CC2</sub> = V <sub>OPT2</sub> = +5 V,<br>V <sub>EE</sub> = -5 V                | mA    | —                    | —                     | 50                   |

4. V<sub>CC1</sub>, V<sub>DD1</sub>, and V<sub>DD2</sub> should be turned on after V<sub>G\_LNA</sub> and V<sub>G\_PA12</sub> have been turned on. When turning power off, turn off V<sub>CC1</sub>, V<sub>DD1</sub>, and V<sub>DD2</sub> prior to turning off V<sub>G\_LNA</sub> and V<sub>G\_PA12</sub>.

5. Unused logic inputs must be tied to either ground or V<sub>CC2</sub>.

6. All voltages are relative to ground.

7. 0.01 μF decoupling capacitors are required on the power supply lines.

8. V<sub>OPT2</sub> determines the output high voltage for the external PIN driver output, and is usually tied to V<sub>CC2</sub>. When the PIN driver section is unused, V<sub>OPT2</sub> should be grounded and SW2A50 and SW2B50 should be left open.

9. V<sub>EE</sub> is tied to the substrate of the die and should be the most negative voltage potential. V<sub>EE</sub> should never be biased higher than any other power supplies.

10. I<sub>OPT2</sub> and I<sub>EE</sub> are determined by the external PIN diode switches. They should not exceed 50 mA.

**Electrical Pulsing Specifications<sup>11</sup>:**

Freq. = 8.5, 9.5, 10.5 GHz,  $T_A = 25^\circ\text{C}$ ,  $Z_0 = 50 \Omega$

| Symbol                                   | Parameter              | Conditions            | Units | Min. | Typ. | Max. |

|------------------------------------------|------------------------|-----------------------|-------|------|------|------|

| <b>Gate Switching Mode<sup>12</sup></b>  |                        |                       |       |      |      |      |

| $T_x T_{ON}$                             | Transmit Turn-on Time  | 50% Control to 90% RF | ns    | —    | 240  | —    |

| $T_x T_{OFF}$                            | Transmit Turn-off Time | 50% Control to 10% RF | ns    | —    | 100  | —    |

| $R_x T_{ON}$                             | Receive Turn-on Time   | 50% Control to 90% RF | ns    | —    | 200  | —    |

| $R_x T_{OFF}$                            | Receive Turn-off Time  | 50% Control to 10% RF | ns    | —    | 90   | —    |

| <b>Drain Switching Mode<sup>13</sup></b> |                        |                       |       |      |      |      |

| $T_x T_{ON}$                             | Transmit Turn-on Time  | 50% Control to 90% RF | ns    | —    | 50   | —    |

| $T_x T_{OFF}$                            | Transmit Turn-off Time | 50% Control to 10% RF | ns    | —    | 30   | —    |

| $R_x T_{ON}$                             | Receive Turn-on Time   | 50% Control to 90% RF | ns    | —    | 40   | —    |

| $R_x T_{OFF}$                            | Receive Turn-off Time  | 50% Control to 10% RF | ns    | —    | 20   | —    |

11. When switching states, it is important to avoid having  $T_x$  and  $R_x$  on at the same time, which could potentially lead to undesired spurious signals or a damaging oscillation.

12. When gate switching, we recommend lingering in the idle state for 20 ns when transitioning between  $T_x$  and  $R_x$  to ensure that the  $T_x$  and  $R_x$  amplifiers are not both on at the same.

13. Typical drain switching times are with the control applied to the gate of the recommended external MOSFETS, including the recommended bypass capacitors.

**Tx / Rx Drain Switching Circuit Recommendation**

**Tx / Rx Drain Switching Truth Table**

| Path State       | External +V supply | Control Logic | Output to          |

|------------------|--------------------|---------------|--------------------|

| $T_x\text{_ON}$  | +5.0 V             | 0 V           | $V_{DD1}, V_{DD2}$ |

| $T_x\text{_OFF}$ |                    | +5.0 V        |                    |

| $R_x\text{_ON}$  | +3.3 V             | 0 V           | $V_{CC1}$          |

| $R_x\text{_OFF}$ |                    | +3.3 V        |                    |

**Absolute Maximum Ratings**<sup>14,15,16,17,18,19</sup>

| Symbol                              | Parameter                                              | Min.            | Max.                                               | Unit |

|-------------------------------------|--------------------------------------------------------|-----------------|----------------------------------------------------|------|

| V <sub>DD1</sub> , V <sub>DD2</sub> | T <sub>x</sub> Amplifier Bias                          | -0.5            | +7.0                                               | V    |

| V <sub>G_LNA</sub>                  | Gate Bias to R <sub>x</sub> Amplifier                  | -6.0            | +0.5                                               | V    |

| V <sub>G_PA12</sub>                 | Gate Bias to T <sub>x</sub> Amplifier                  | -6.0            | +0.5                                               | V    |

| V <sub>CC1</sub>                    | Positive DC Supply Voltage LNA                         | -0.5            | +5.0                                               | V    |

| V <sub>CC2</sub>                    | Positive DC Supply Voltage Driver                      | -0.5            | +7.0                                               | V    |

| V <sub>OPT2</sub>                   | Optional DC Output Supply Voltage                      | -0.5            | V <sub>CC</sub> +0.5, or +7.0<br>Whichever is less | V    |

| V <sub>EE</sub>                     | Negative DC Supply Voltage <sup>16</sup>               | -7              | Note 16                                            | V    |

| V <sub>IN</sub>                     | Digital Input Voltage <sup>17</sup>                    | -0.5<br>Note 17 | V <sub>CC</sub> +0.5 or +7.0<br>Whichever is less  | V    |

| I <sub>OH</sub>                     | Output High Current for SER OUT                        | -10             | 0                                                  | mA   |

| I <sub>OL</sub>                     | Output Low Current for SER OUT                         | 0               | +10                                                | mA   |

| R <sub>x</sub> IN                   | Receive RF Input                                       | —               | 24                                                 | dBm  |

| I <sub>SOURCE</sub>                 | DC Output Sourcing Current for SW2A50 and SW2B50 Ports | 0               | 60                                                 | mA   |

| I <sub>SINK</sub>                   | DC Output Sinking Current for SW2A50, SW2B50 Ports     | 0               | 60                                                 | mA   |

| T <sub>OPER</sub>                   | Operating Temperature                                  | -40             | +125                                               | °C   |

| T <sub>STG</sub>                    | Storage Temperature                                    | -65             | +150                                               | °C   |

| T <sub>J</sub>                      | Junction Temperature <sup>18, 19</sup>                 | —               | +150                                               | °C   |

14. Exceeding any one or combination of these limits may cause permanent damage to this device.

15. MACOM does not recommend sustained operation near these survivability limits.

16. The absolute maximum rating for V<sub>EE</sub> is the minimum of "V<sub>OPT2</sub> + 0.5 V", "V<sub>CC2</sub> +0.5 V", and "+0.5 V".

17. If V<sub>CC2</sub> ≥ 6.5 V, then the minimum for V<sub>IN</sub> is V<sub>CC2</sub> - 7.0 V.

18. Operating at nominal conditions with T<sub>J</sub> ≤ +150°C will ensure MTTF > 1 x 10<sup>6</sup> hours.

19. Junction Temperature (T<sub>J</sub>) = T<sub>C</sub> + Θ<sub>JC</sub> \* ((P<sub>DC</sub>) - (P<sub>OUT</sub> - P<sub>IN</sub>))

Typical Thermal Resistance in T<sub>x</sub> mode (Θ<sub>JC</sub>) = 67.0°C/W

Typical Power Dissipation in the T<sub>x</sub> state at 25°C is 0.6 W

Typical Power Dissipation in the R<sub>x</sub> state at 25°C is 0.27 W

Typical Power Dissipation in the idle state at 25°C is 0.01 W

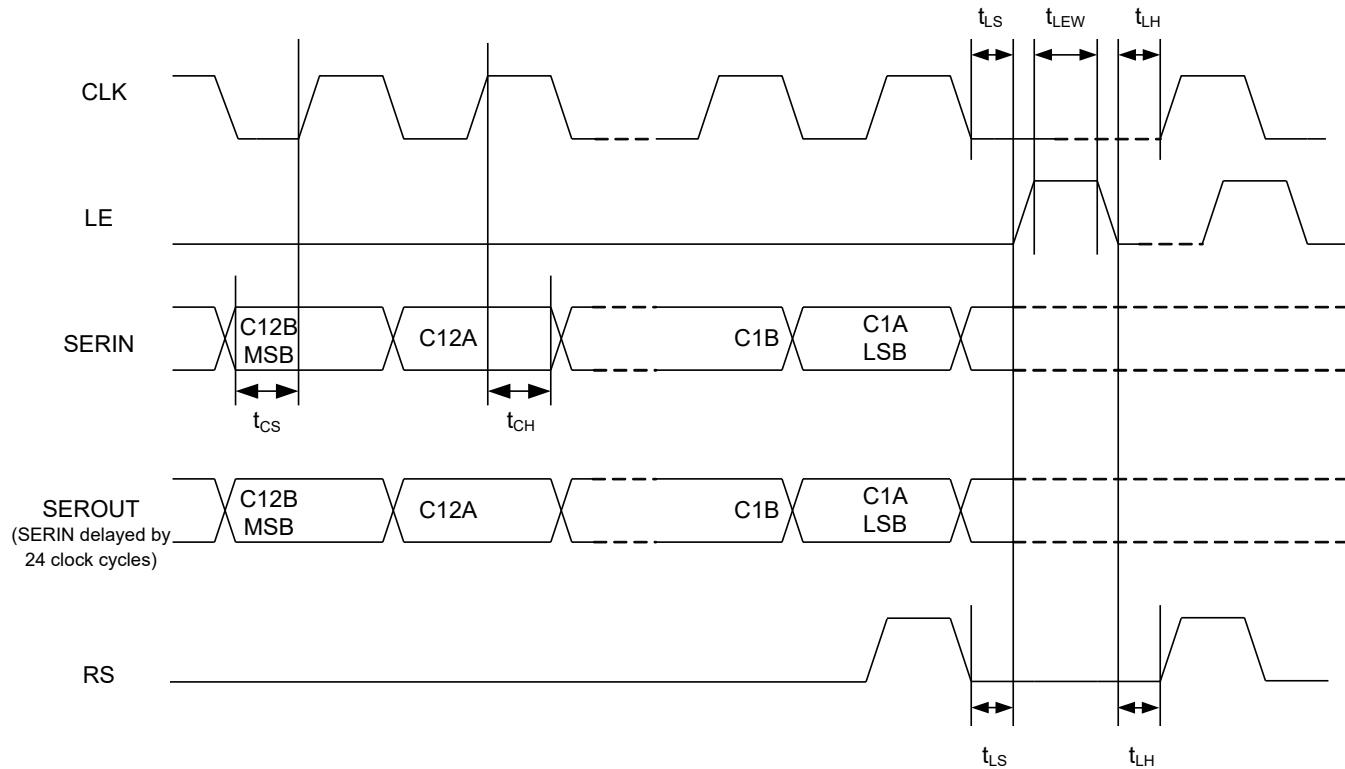

### 12-bit Serial to Parallel Driver

The phase shifting and attenuation settings are controlled by a serial data stream. Two states are entered in a single 24-bit data stream, 12-bit for each complete set of phase and attenuation settings.

The 24-bit serial interface (SERIN, CLK, LE, SER-OUT) is compatible with SPI protocol. The two 12-bit control words are loaded with MSB first. Note that the bits for the two states are interlaced, as shown in the "serial Input Bits Order and Function Table". When LE is high, the 24-bit data in the serial input register will be transferred to a 24-bit latch, and one of the two control words will be loaded to the complementary An and Bn outputs based on the logic state of RS control. "State A" uses the "A" bits while "State B" uses the "B" bits from the 24-bit stream. The RS control line allows fast toggling between the two states settings.

CLK will be masked to prevent data transition when LE is high. SEROUT is the SERIN delayed by 24 clock cycles.

Please refer to application note AN-0004028 for more detailed instructions on the driver operation. AN-0004028 also includes instructions to interface with USB-910H [USB-to-SPI/I2C embedded system interface] for quick operation of the device.

### Register Select Truth Table<sup>20</sup>

| RS | Bits Selected |

|----|---------------|

| 0  | "A" Bits      |

| 1  | "B" Bits      |

20. See  $V_{IH}$  and  $V_{IL}$  for logic levels

### Attenuator and Phase Shifter Control

The 6-bit attenuator and 6-bit phase shifter are controlled by serial input bits C1 ~ C12. The serial input bits order and control function are listed in following tables.

### Serial Input Bits Order & Function Table

| Function               | Bit           | RS = 0<br>State A | RS = 1<br>State B |

|------------------------|---------------|-------------------|-------------------|

| -180°<br>Phase Shift   | C12B<br>(MSB) | --                | State B           |

|                        | C12A          | State A           | --                |

| -90°<br>Phase Shift    | C11B          | --                | State B           |

|                        | C11A          | State A           | --                |

| -45°<br>Phase Shift    | C10B          | --                | State B           |

|                        | C10A          | State A           | --                |

| -22.5°<br>Phase Shift  | C9B           | --                | State B           |

|                        | C9A           | State A           | --                |

| -11.25°<br>Phase Shift | C8B           | --                | State B           |

|                        | C8A           | State A           | --                |

| -5.6°<br>Phase Shift   | C7B           | --                | State B           |

|                        | C7A           | State A           | --                |

| 16 dB<br>Attenuator    | C6B           | --                | State B           |

|                        | C6A           | State A           | --                |

| 8 dB<br>Attenuator     | C5B           | --                | State B           |

|                        | C5A           | State A           | --                |

| 4 dB<br>Attenuator     | C4B           | --                | State B           |

|                        | C4A           | State A           | --                |

| 2 dB<br>Attenuator     | C3B           | --                | State B           |

|                        | C3A           | State A           | --                |

| 1 dB<br>Attenuator     | C2B           | --                | State B           |

|                        | C2A           | State A           | --                |

| 0.5 dB<br>Attenuator   | C1B           | --                | State B           |

|                        | C1A<br>(LSB)  | State A           | --                |

## T/R Switches Control

Switch drivers are designed to drive the SP2T switch in the MMIC which switch the T/R module between transmit and receive modes.

The SW2A50 and SW2B50 outputs are designed to drive PIN diode SP2T switches (External to the module). They are able to sink and source 50 mA current and provide back bias voltage as high as -5.5 V. They can be used to drive GaAs switches to improve the intermodulation performance and achieve higher P1dB at low frequencies.

For applications where an external PIN switch is used, SWEN2 is set to 0 V. In most cases,  $V_{OPT2}$  would be set to 0 V if an external GaAs switch is used.

## T/R Switches Control Truth Table<sup>21</sup>

| INPUTS |    | OUTPUTS    |            |                     |                     |

|--------|----|------------|------------|---------------------|---------------------|

| SWEN2  | TR | SW2A50     | SW2B50     | R <sub>x</sub> Path | T <sub>x</sub> Path |

| 0      | 0  | $V_{EE}$   | $V_{OPT2}$ | ON                  | OFF                 |

| 0      | 1  | $V_{OPT2}$ | $V_{EE}$   | OFF                 | ON                  |

| 1      | X  | $V_{OPT2}$ | $V_{EE}$   | N/A                 | N/A                 |

21. If no external switch is used, set SWEN2 high to conserve current.

## Gate/Drain Switching Truth Table

| G/D      | Function                      |

|----------|-------------------------------|

| 0 V      | Drain Switching <sup>22</sup> |

| $V_{EE}$ | Gate Switching <sup>23</sup>  |

22. When set in the drain switching mode, external MOSFETs will be needed to supply the bias voltage.

23. When gate switching, the internal driver will enable/disable the LNA (Receive amplifier) and Driver Amplifier (Transmit amplifier).

## T/R Amplifiers Control

The combination of TR and EN inputs will be able to turn on/off the MMIC receive path LNAs and transmit path PAs.

## T/R Amplifiers Control Truth Table<sup>20, 24</sup>

| INPUTS   |     |    | T <sub>x</sub> or<br>R <sub>x</sub> Switch<br>STATE | OUTPUTS |         |

|----------|-----|----|-----------------------------------------------------|---------|---------|

| G/D      | EN  | TR |                                                     | PA      | LNA     |

| $V_{EE}$ | 0   | 0  | Receive                                             | OFF     | OFF     |

| $V_{EE}$ | 0   | 1  | Transmit                                            | OFF     | OFF     |

| $V_{EE}$ | 1   | 0  | Receive                                             | OFF     | ON      |

| $V_{EE}$ | 1   | 1  | Transmit                                            | ON      | OFF     |

| 0 V      | N/A | 0  | Receive                                             | Note 25 | Note 25 |

| 0 V      | N/A | 1  | Transmit                                            | Note 25 | Note 25 |

24. In this table, the transmit or receive state signifies the how the switches are set. It does not mean that the amplifiers are enabled (ON).

25. The PA and LNA are enable/disabled depending on if external MOSFETs are "ON" or "OFF". See the suggested T<sub>x</sub> and R<sub>x</sub> drain switching circuits.

## Handling Procedures

Please observe the following precautions to avoid damage:

### Static Sensitivity

Integrated Circuits are sensitive to electrostatic discharge (ESD) and can be damaged by static electricity. Proper ESD control techniques should be used when handling these devices.

### Serial Interface Timing Characteristics

| Symbol     | Parameter                                | Typical Performance | Unit |

|------------|------------------------------------------|---------------------|------|

| $f_{data}$ | Max. Clock Rate for Shifting Serial Data | >80                 | MHz  |

| $t_{cs}$   | Min. Control Set-up Time                 | 3.5                 | ns   |

| $t_{CH}$   | Min. Control Hold Time                   | 3.5                 | ns   |

| $t_{LS}$   | Min. LE Set-up Time                      | 3.5                 | ns   |

| $t_{LEW}$  | Min. LE Pulse Width                      | 20.0                | ns   |

| $t_{LH}$   | Min. LE Hold Time from CLK               | 3.5                 | ns   |

| $f_{RS}$   | Frequency for RS control, 50% Duty Cycle | 25.0                | MHz  |

### Serial Interface Timing Diagram

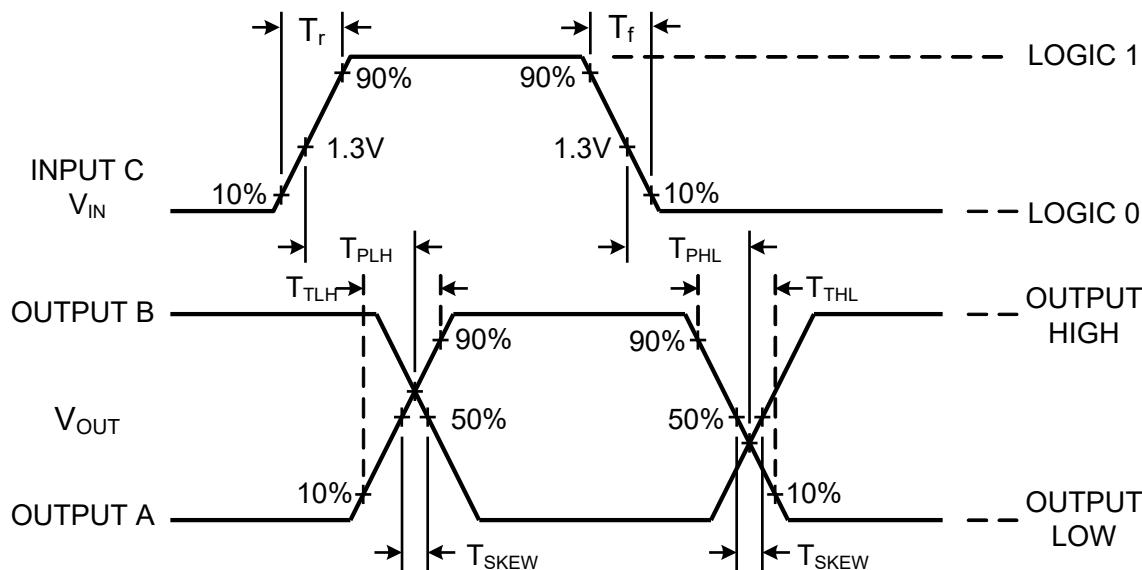

**PIN Diode Driver Switching Speed:<sup>26</sup>**

| Symbol    | Parameter                             | Typical performance | Unit |

|-----------|---------------------------------------|---------------------|------|

| $T_{PLH}$ | Propagation Delay                     | 13                  | ns   |

| $T_{PHL}$ | Propagation Delay                     | 13                  | ns   |

| $T_{TLH}$ | Output Transition Time (Rising Edge)  | 8                   | ns   |

| $T_{THL}$ | Output Transition Time (Falling Edge) | 4.5                 | ns   |

26.  $V_{CC2} = V_{opt2} = 3.0$  V,  $V_{EE} = -5.0$  V,  $C_L = 24$  pF, input LOGIC1 = 3 V, LOGIC0 = 0 V,  $T_{RISE}$ ,  $T_{FALL} = 6$  ns.

**Switching Waveforms**

### Typical Performance Curves

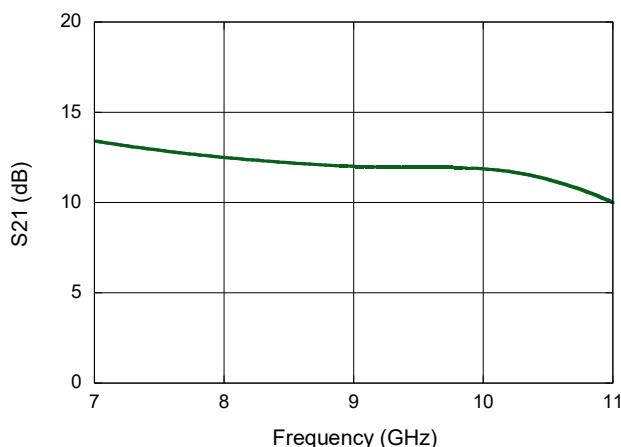

***T<sub>x</sub> Gain***

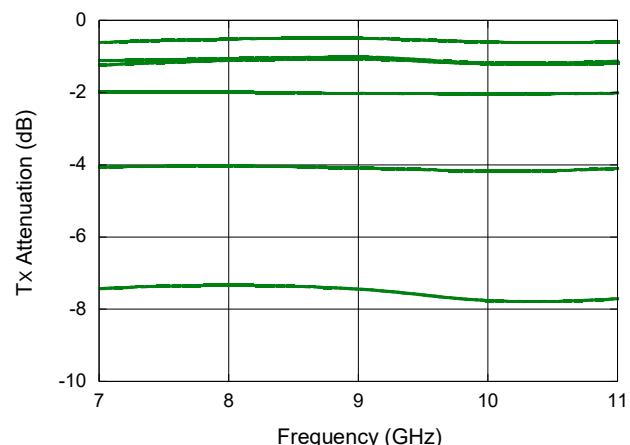

***T<sub>x</sub> Attenuation - Major Bits***

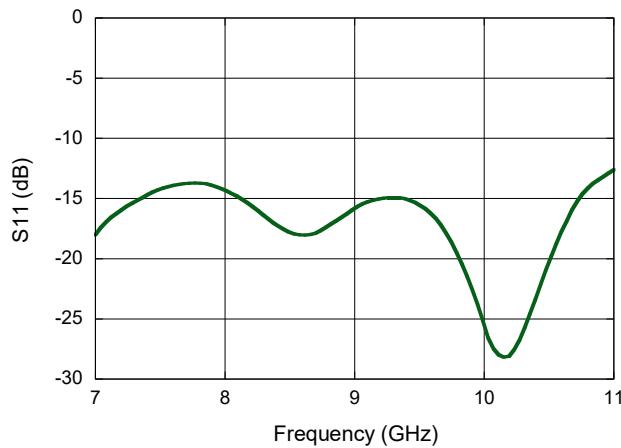

***T<sub>x</sub> Input Return Loss***

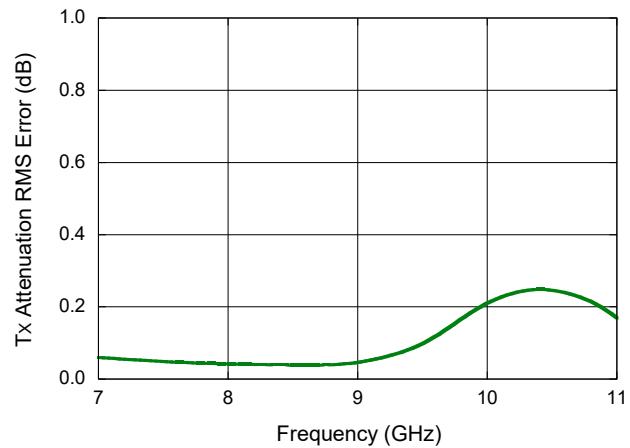

***T<sub>x</sub> Attenuation RMS Error***

***T<sub>x</sub> Output Return Loss***

***T<sub>x</sub> Output P<sub>SAT</sub>***

## Typical Performance Curves

**R<sub>x</sub> Gain**

**R<sub>x</sub> Attenuation - Major Bits**

**R<sub>x</sub> Input Return Loss**

**R<sub>x</sub> Attenuation RMS Error**

**R<sub>x</sub> Output Return Loss**

**R<sub>x</sub> Noise**

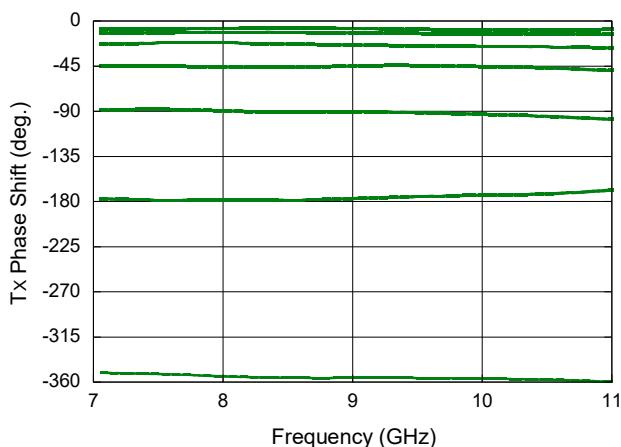

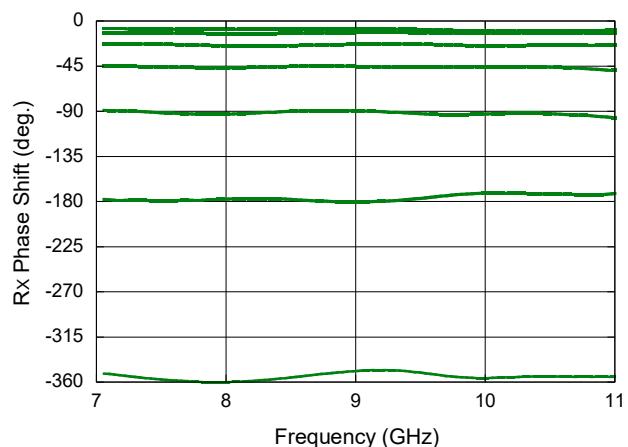

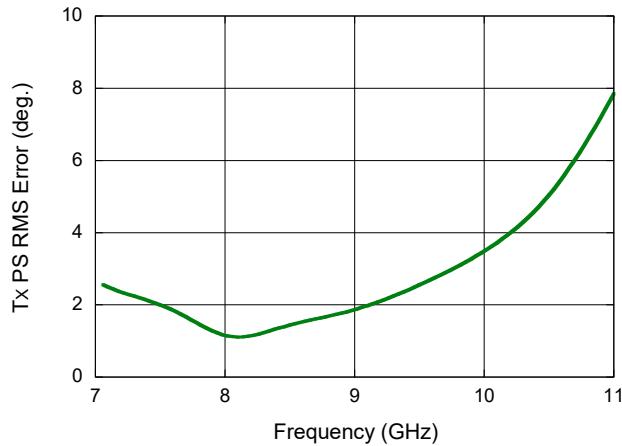

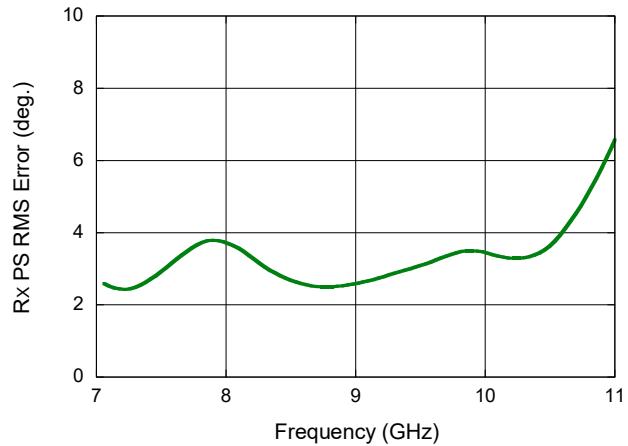

## Typical Performance Curves

***T<sub>x</sub> Phase Shift***

***R<sub>x</sub> Phase Shift***

***T<sub>x</sub> PS RMS Error (deg.)***

***R<sub>x</sub> PS RMS Error (deg.)***

**Lead Free 7 mm 44-lead PQFN<sup>†</sup>**

<sup>†</sup> Reference Application Note S2083 for lead-free solder reflow recommendations.

JEDEC moisture sensitivity levels MSL 3.

Plating is NiPdAu.

MACOM Technology Solutions Inc. ("MACOM"). All rights reserved.

These materials are provided in connection with MACOM's products as a service to its customers and may be used for informational purposes only. Except as provided in its Terms and Conditions of Sale or any separate agreement, MACOM assumes no liability or responsibility whatsoever, including for (i) errors or omissions in these materials; (ii) failure to update these materials; or (iii) conflicts or incompatibilities arising from future changes to specifications and product descriptions, which MACOM may make at any time, without notice. These materials grant no license, express or implied, to any intellectual property rights.

THESE MATERIALS ARE PROVIDED "AS IS" WITH NO WARRANTY OR LIABILITY, EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF MACOM PRODUCTS INCLUDING FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHT, ACCURACY OR COMPLETENESS, OR SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES WHICH MAY RESULT FROM USE OF THESE MATERIALS.

MACOM products are not intended for use in medical, lifesaving or life sustaining applications. MACOM customers using or selling MACOM products for use in such applications do so at their own risk and agree to fully indemnify MACOM for any damages resulting from such improper use or sale.