**MxL86288L**

Ethernet PHY

**8-Port 2.5 Gigabit Ethernet PHY**

MxL86288L

**Data Sheet**

Revision 1.1, 2025-10-27

Reference ID 621444

## Legal Notice

The content of this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by MaxLinear, Inc. MaxLinear, Inc. assumes no responsibility or liability for any errors or inaccuracies that may appear in the informational content contained in this document. Complying with all applicable copyright laws is the responsibility of the user. Without limiting the rights under copyright, no part of this document may be reproduced into, stored in, or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), or for any purpose, without the express written permission of MaxLinear, Inc.

EXCEPT AS OTHERWISE PROVIDED EXPRESSLY IN WRITING BY MAXLINEAR, AND TO THE MAXIMUM EXTENT PERMITTED BY LAW: (A) THE MAXLINEAR PRODUCTS ARE PROVIDED ON AN "AS IS" BASIS WITHOUT REPRESENTATIONS OR WARRANTIES OF ANY KIND, INCLUDING WITHOUT LIMITATION ANY IMPLIED OR STATUTORY WARRANTIES AND ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, NON-INFRINGEMENT, OR TITLE; AND (B) MAXLINEAR DOES NOT GUARANTEE THAT THE PRODUCTS WILL BE FREE OF ERRORS OR DEFECTS. MAXLINEAR PRODUCTS SHOULD NOT BE USED IN ANY EMERGENCY, SECURITY, MILITARY, LIFE-SAVING, OR OTHER CRITICAL USE CASE WHERE A FAILURE OR MALFUNCTION COULD CAUSE PERSONAL INJURY OR DEATH, OR DAMAGE TO OR LOSS OF PROPERTY. USERS ASSUME ALL RISK FOR USING THE MAXLINEAR PRODUCTS IN SUCH USE CASE. CUSTOMERS AND USERS ARE SOLELY RESPONSIBLE FOR USING THEIR OWN SKILL AND JUDGMENT TO DETERMINE WHETHER MAXLINEAR PRODUCTS ARE SUITABLE FOR THE INTENDED USE CASE.

MaxLinear, Inc. may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from MaxLinear, Inc., the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

MaxLinear, the MaxLinear logo, any other MaxLinear trademarks (including but not limited to MxL, Full-Spectrum Capture, FSC, AirPHY, Puma, AnyWAN, VectorBoost, MXL WARE, and Panther), are all property of MaxLinear, Inc. or one of MaxLinear's subsidiaries in the U.S.A. and other countries. All rights reserved.

All third-party marks and logos are trademarks™ or registered® trademarks of their respective holders/owners. Use of such marks does not imply any affiliation with, sponsorship or endorsement by the owners/holders of such trademarks. All references by MaxLinear to third party trademarks are intended to constitute nominative fair use under applicable trademark laws.

The URLs provided are for informational purposes only; they do not constitute an endorsement or an approval by MaxLinear of any of the products or services of the corporation or organization or individual. MaxLinear bears no responsibility for the accuracy, legality or content of the external site or for that of subsequent links. Contact the external site for answers to questions regarding its content.

© 2025 MaxLinear, Inc. All rights reserved.

MaxLinear, Inc.

5966 La Place Court, Suite 100

Carlsbad, CA 92008

Tel.: +1 (760) 692-0711

Fax: +1 (760) 444-8598

[www.maxlinear.com](http://www.maxlinear.com)

## Revision History

Current: Revision 1.1, 2025-10-27

Previous: Revision 1.0, 2025-08-29

| Page | Major changes since previous revision                                                                                                                                     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 260  | <a href="#"><b>Table 61 Product and Package Naming:</b></a> <ul style="list-style-type: none"><li>Changed shipping format information and ordering part number.</li></ul> |

|      |                                                                                                                                                                           |

## Third-Party Trademark and Registered Trademark Declarations

|             |                                                                                                                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANSI®       | “ANSI”, the ANSI logo, and numerous other identifiers containing "ANSI" are registered trademarks, service marks, and accreditation marks of the American National Standards Institute (ANSI).                                                                                                                              |

| Cisco®      | Cisco is a registered trademark or trademark of Cisco Systems, Inc. and/or its affiliates in the United States and certain other countries. A list of other Cisco marks is available at <a href="https://www.cisco.com/c/en/us/about/legal/trademarks.html">https://www.cisco.com/c/en/us/about/legal/trademarks.html</a> . |

| IEEE®       | “IEEE”, the IEEE logo, and other IEEE logos and titles are registered trademarks or service marks of The Institute of Electrical and Electronics Engineers, Incorporated.                                                                                                                                                   |

| IEEE 802.1™ | IEEE 802.1 is a trademark of The Institute of Electrical and Electronics Engineers, Incorporated.                                                                                                                                                                                                                           |

| IEEE 802.3™ | IEEE 802.3 is a trademark of The Institute of Electrical and Electronics Engineers, Incorporated.                                                                                                                                                                                                                           |

| ITU-T®      | ITU-T is a registered trademark of the ITU, a specialized agency of the United Nations.                                                                                                                                                                                                                                     |

| JEDEC®      | JEDEC is a registered trademark of the JEDEC Solid State Technology Association.                                                                                                                                                                                                                                            |

| Macronix®   | Macronix, MXIC, MXIC logo, XtraROM, NBit and Macronix NBit are trademarks of Macronix International Co., Ltd.                                                                                                                                                                                                               |

| Microsoft®  | Microsoft is a registered trademark of Microsoft Corporation in the United States and/or other countries.                                                                                                                                                                                                                   |

| NXP®        | NXP is a trademark of NXP B.V.                                                                                                                                                                                                                                                                                              |

| Philips®    | The PHILIPS wordmark and shield emblem are registered trademarks of Koninklijke Philips N.V.                                                                                                                                                                                                                                |

| Winbond®    | Winbond is a registered trademark of Winbond Electronics Corporation.                                                                                                                                                                                                                                                       |

All other trademarks or registered trademarks are the property of their respective holders/owners.

## Table of Contents

## Table of Contents

|                                                 |    |

|-------------------------------------------------|----|

| <b>Table of Contents</b>                        | 5  |

| <b>List of Figures</b>                          | 8  |

| <b>List of Tables</b>                           | 9  |

| <b>Preface</b>                                  | 11 |

| <b>1 Product Overview</b>                       | 12 |

| 1.1 Features                                    | 13 |

| 1.2 Block Diagram                               | 15 |

| <b>2 External Signals</b>                       | 16 |

| 2.1 Logic Symbol                                | 16 |

| 2.2 External Signal Description                 | 17 |

| 2.2.1 Ball Diagram                              | 17 |

| 2.2.2 Abbreviations                             | 19 |

| 2.2.3 Input/Output Signals                      | 20 |

| 2.2.3.1 Ethernet Twisted Pair Interface         | 20 |

| 2.2.3.2 USXGMII Interface                       | 22 |

| 2.2.3.3 MDIO Interface                          | 23 |

| 2.2.3.4 QSPI Interface                          | 24 |

| 2.2.3.5 I <sup>2</sup> C Interface              | 26 |

| 2.2.3.6 Reset Interface                         | 27 |

| 2.2.3.7 LED/UART/JTAG Interface                 | 28 |

| 2.2.3.8 Miscellaneous Signals                   | 34 |

| 2.2.3.9 Power Supply for GPHY                   | 36 |

| 2.2.3.10 Power Supply for USXGMII               | 38 |

| 2.2.3.11 Power Supply for TPI (AFE)             | 39 |

| 2.2.3.12 Ground                                 | 40 |

| 2.2.3.13 Not Connected Signals                  | 41 |

| <b>3 Functional Description</b>                 | 42 |

| 3.1 Power Supply, Clock, and Reset              | 42 |

| 3.1.1 Power Supply                              | 42 |

| 3.1.2 Clock                                     | 42 |

| 3.1.3 Reset Generation                          | 42 |

| 3.1.4 Power-On Sequence                         | 42 |

| 3.1.5 Configuration by Pin Strapping            | 43 |

| 3.2 MDIO Slave Interface                        | 45 |

| 3.3 Configuration via MDIO Management Interface | 46 |

| 3.4 I <sup>2</sup> C Master Interface           | 47 |

| 3.5 Quad Serial Peripheral Interface            | 48 |

| 3.5.1 Supported Flash Memory Devices            | 48 |

| 3.6 GPIO Mapping                                | 50 |

| 3.7 Ethernet PHY Interface                      | 52 |

| 3.7.1 Twisted Pair Interface                    | 52 |

| 3.7.2 Transformerless Ethernet                  | 52 |

| 3.7.3 Auto-Negotiation                          | 53 |

| 3.7.4 Auto-Downspeed                            | 53 |

| 3.7.5 Polarity Reversal Correction              | 53 |

| 3.7.6 Auto-Crossover Correction                 | 53 |

**Table of Contents**

|          |                                                           |            |

|----------|-----------------------------------------------------------|------------|

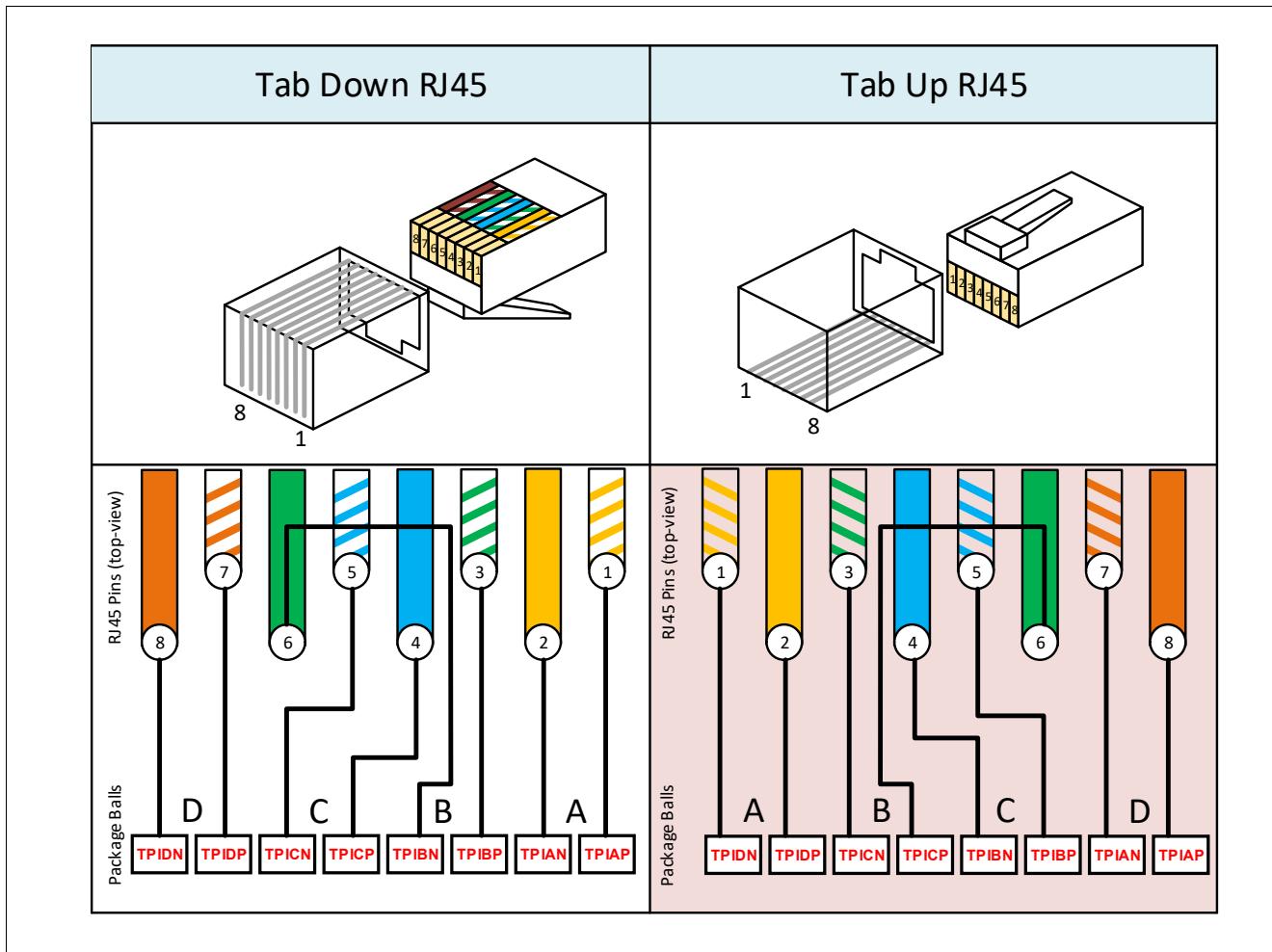

| 3.7.7    | RJ45 Tab Up or Tab Down Configuration .....               | 54         |

| 3.7.8    | Wake-on-LAN .....                                         | 56         |

| 3.8      | Ethernet SerDes Interface .....                           | 57         |

| 3.8.1    | Ethernet SerDes Interface Configuration at Power On ..... | 57         |

| 3.9      | LED Interface .....                                       | 58         |

| 3.9.1    | LED .....                                                 | 58         |

| 3.9.2    | LED Configuration .....                                   | 58         |

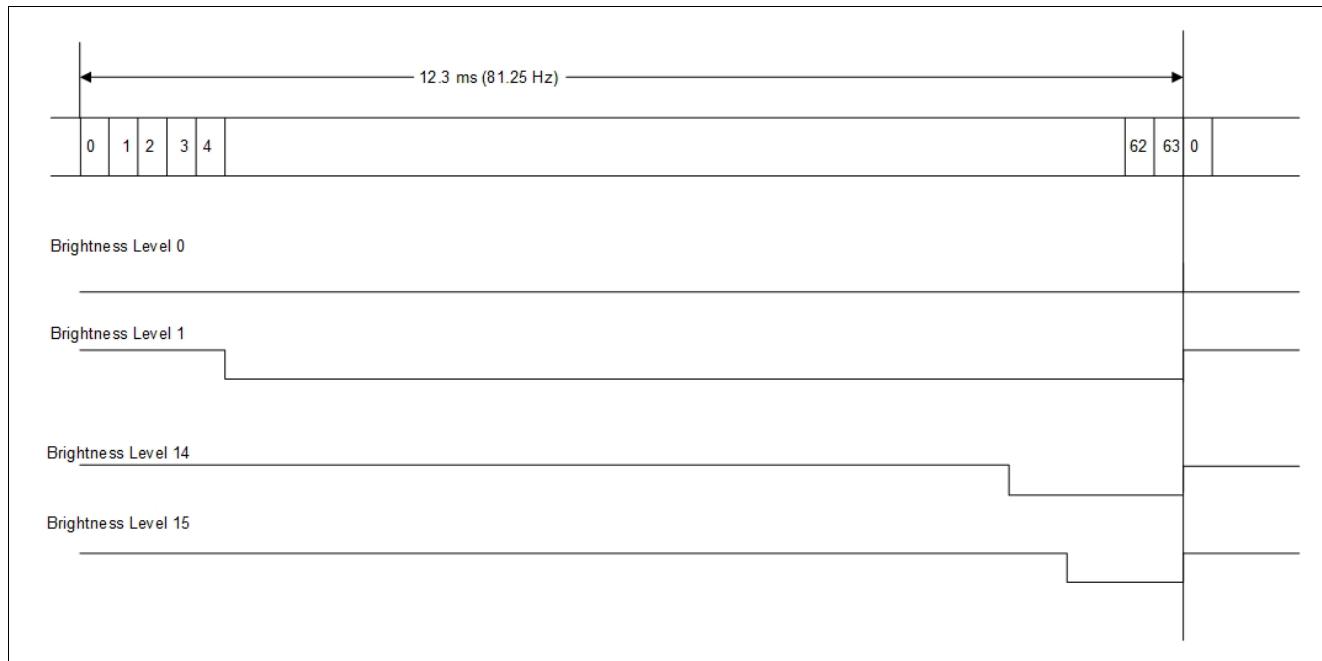

| 3.9.3    | LED Brightness Control .....                              | 60         |

| 3.10     | Smart-AZ .....                                            | 61         |

| 3.11     | Preemption .....                                          | 62         |

| 3.12     | Power Management .....                                    | 63         |

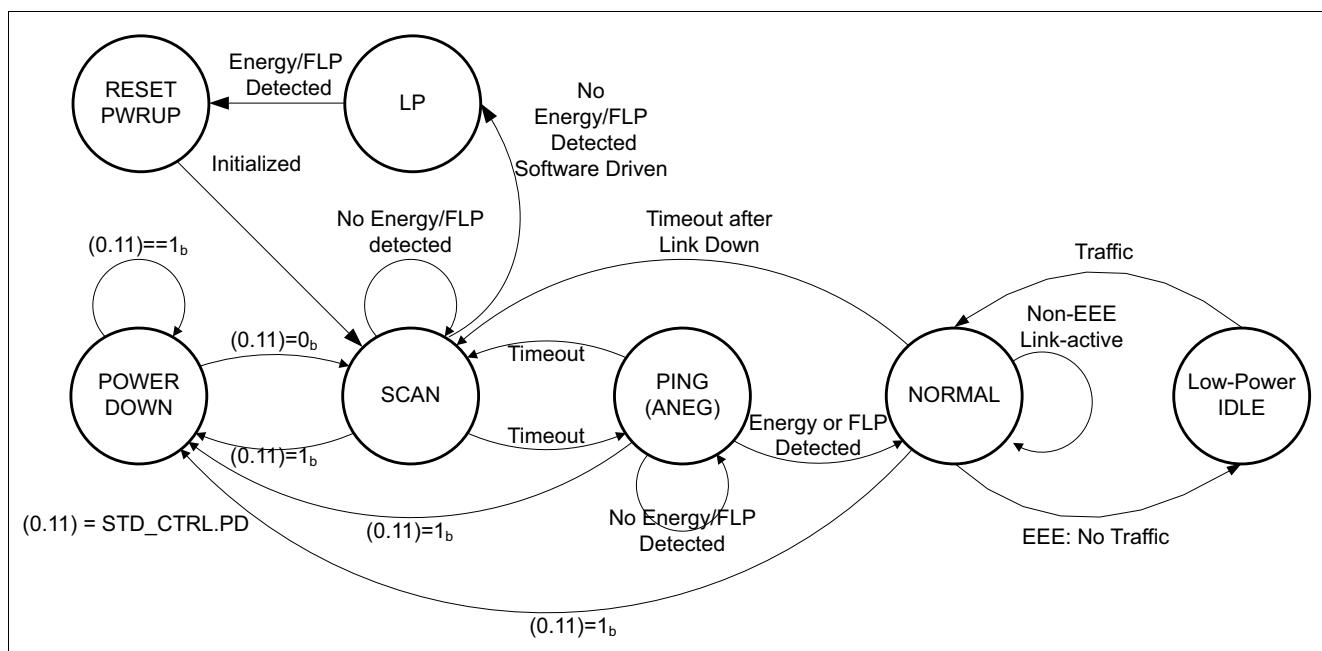

| 3.12.1   | Power States .....                                        | 63         |

| 3.12.2   | RESET PWRUP .....                                         | 63         |

| 3.12.3   | POWER DOWN State .....                                    | 63         |

| 3.12.4   | SCAN (ANEG) State .....                                   | 64         |

| 3.12.5   | PING (ANEG) State .....                                   | 64         |

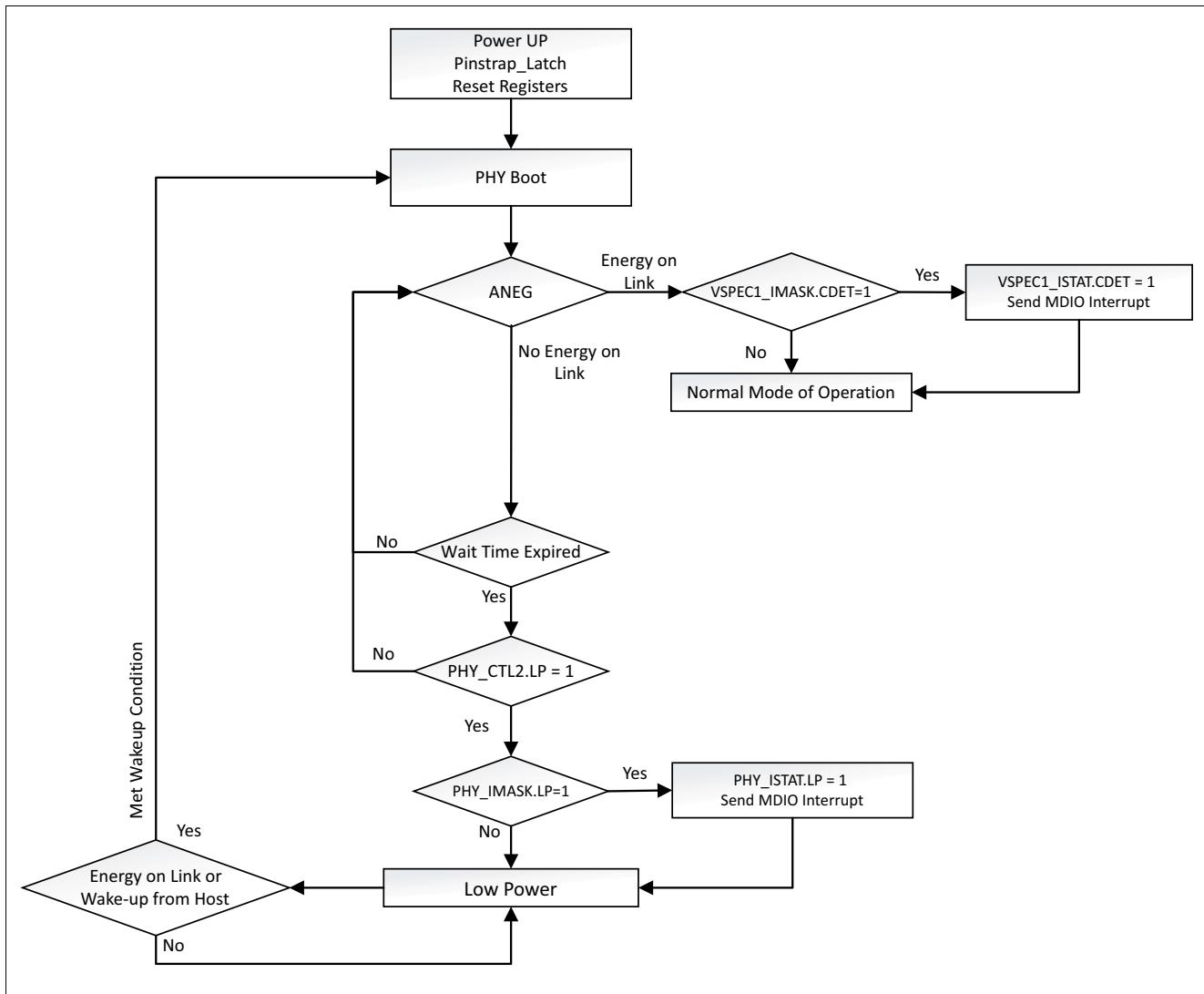

| 3.12.6   | Low-Power State .....                                     | 64         |

| 3.12.7   | NORMAL State .....                                        | 68         |

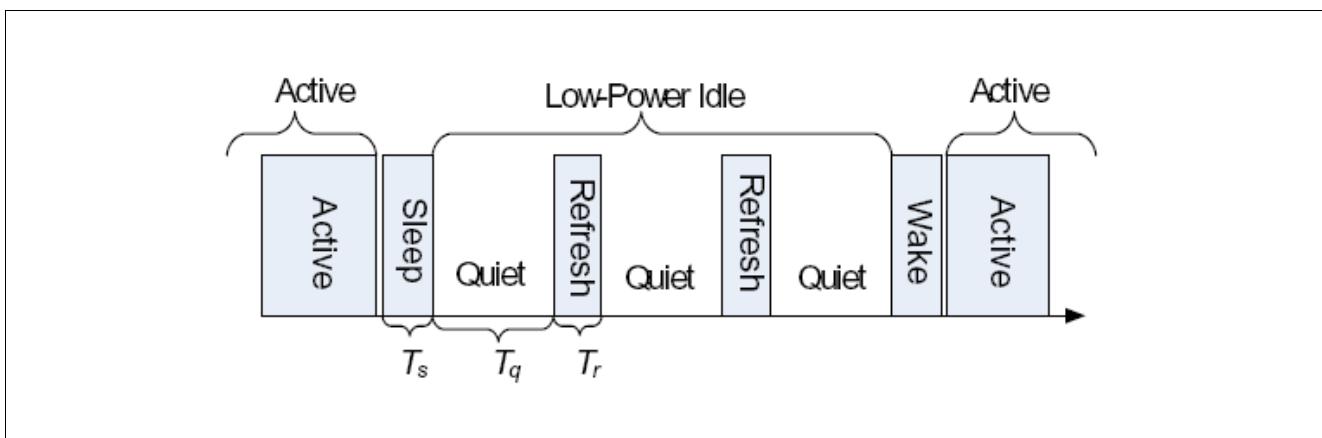

| 3.12.8   | Low Power IDLE State - Energy-Efficient Ethernet .....    | 69         |

| 3.13     | Firmware Upgrade .....                                    | 70         |

| <b>4</b> | <b>MDIO and MMD Register Interface Description .....</b>  | <b>71</b>  |

| 4.1      | MDIO-specific Terminology .....                           | 71         |

| 4.2      | Register Naming and Numbering .....                       | 72         |

| 4.2.1    | Register Numbering .....                                  | 72         |

| 4.2.2    | Register Naming .....                                     | 72         |

| 4.2.3    | Examples .....                                            | 72         |

| 4.3      | MMD Devices Present in MxL86288L .....                    | 73         |

| 4.4      | Responsibilities of the STA .....                         | 74         |

| 4.5      | MDIO Access Protocols to Read / Write Registers .....     | 75         |

| <b>5</b> | <b>MDIO Registers Detailed Description .....</b>          | <b>76</b>  |

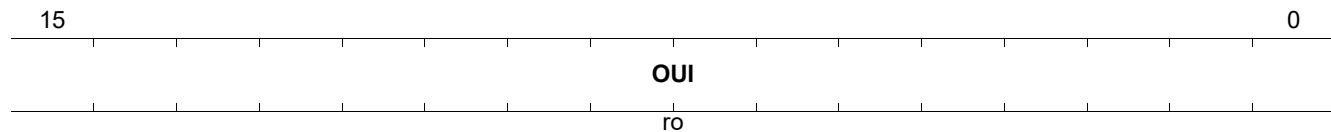

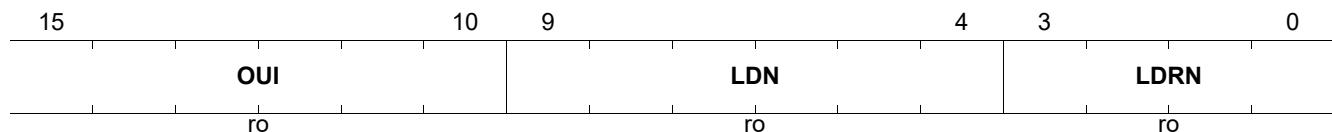

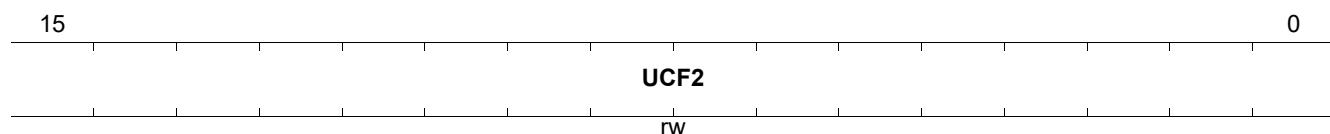

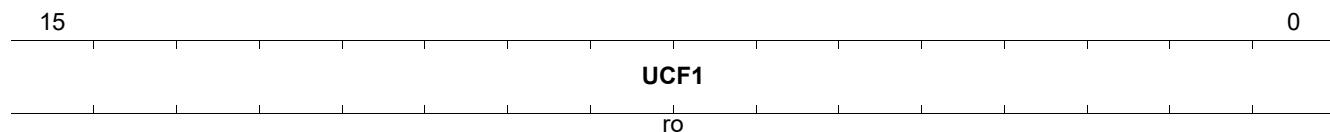

| 5.1      | Standard Management Registers .....                       | 77         |

| 5.1.1    | Standard Management Register Descriptions .....           | 78         |

| 5.2      | PHY-specific Management Registers .....                   | 100        |

| 5.2.1    | PHY-specific Management Register Descriptions .....       | 101        |

| <b>6</b> | <b>MMD Registers Detailed Description .....</b>           | <b>118</b> |

| 6.1      | Standard PMAPMD Registers for MMD=0x01 .....              | 119        |

| 6.1.1    | PMAPMD Register Descriptions .....                        | 121        |

| 6.2      | Standard PCS Registers .....                              | 160        |

| 6.2.1    | PCS Register Descriptions .....                           | 161        |

| 6.3      | Standard Auto-Negotiation Registers for MMD=0x07 .....    | 180        |

| 6.3.1    | ANEG Register Descriptions .....                          | 181        |

| 6.4      | Vendor Specific 1 Device Registers .....                  | 209        |

| 6.4.1    | VSPEC1 Register Descriptions .....                        | 210        |

| 6.5      | Vendor Specific 2 Device Registers .....                  | 229        |

| 6.5.1    | VSPEC2 Register Descriptions .....                        | 230        |

| <b>7</b> | <b>Electrical Characteristics .....</b>                   | <b>237</b> |

| 7.1      | Absolute Maximum Ratings .....                            | 237        |

| 7.2      | Operating Range .....                                     | 239        |

| 7.3      | Typical Power Consumption .....                           | 240        |

| 7.4      | Maximum Thermal Design Power .....                        | 240        |

---

Table of Contents

|         |                                                                    |     |

|---------|--------------------------------------------------------------------|-----|

| 7.5     | Maximum Current .....                                              | 240 |

| 7.6     | DC Characteristics .....                                           | 242 |

| 7.6.1   | Digital Interfaces .....                                           | 242 |

| 7.6.2   | Twisted Pair Interface .....                                       | 242 |

| 7.6.3   | Built-in Temperature Sensor .....                                  | 243 |

| 7.7     | AC Characteristics .....                                           | 244 |

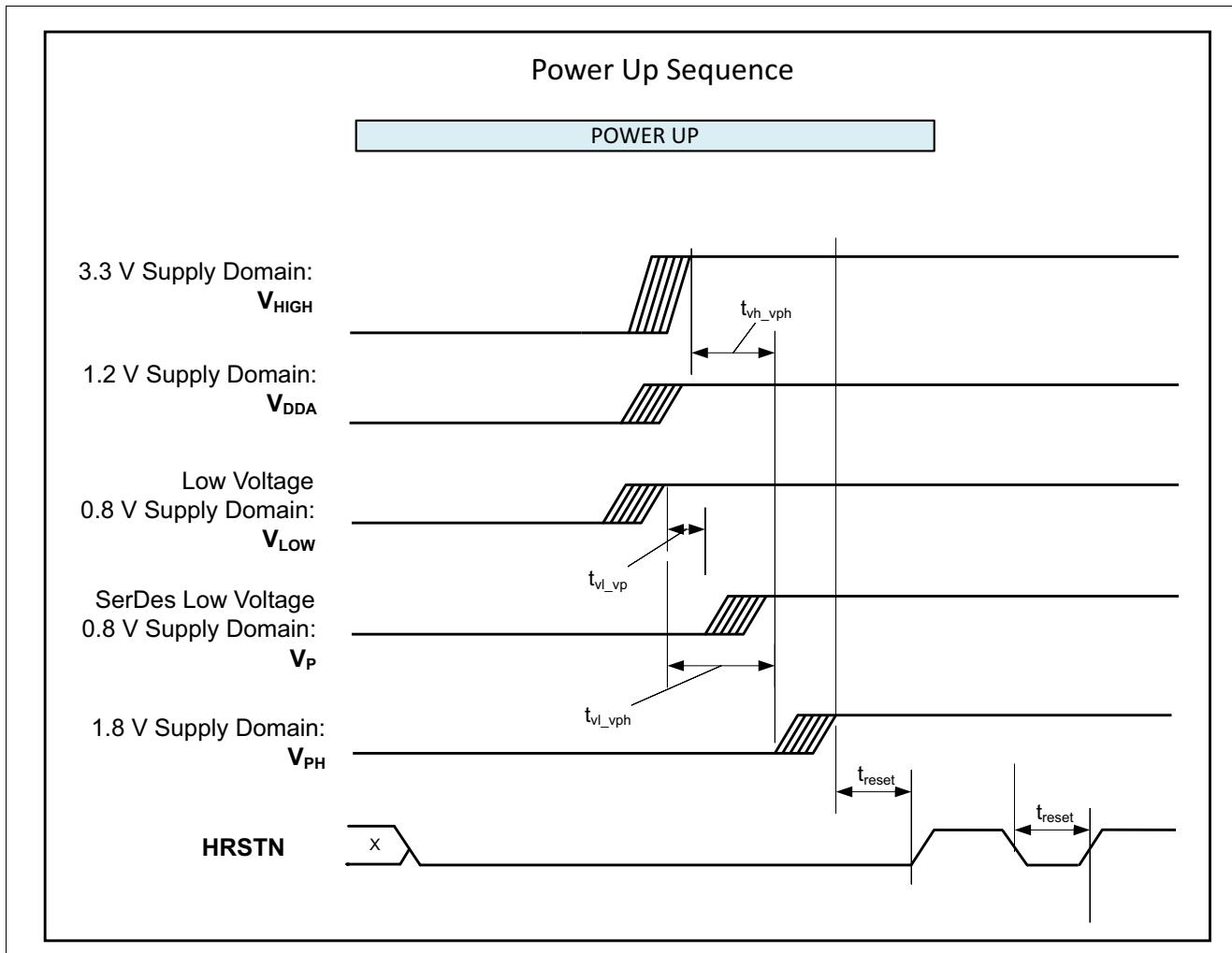

| 7.7.1   | Power Up Sequence .....                                            | 244 |

| 7.7.2   | Input Clock .....                                                  | 246 |

| 7.7.3   | Power Supply Rail Requirements .....                               | 246 |

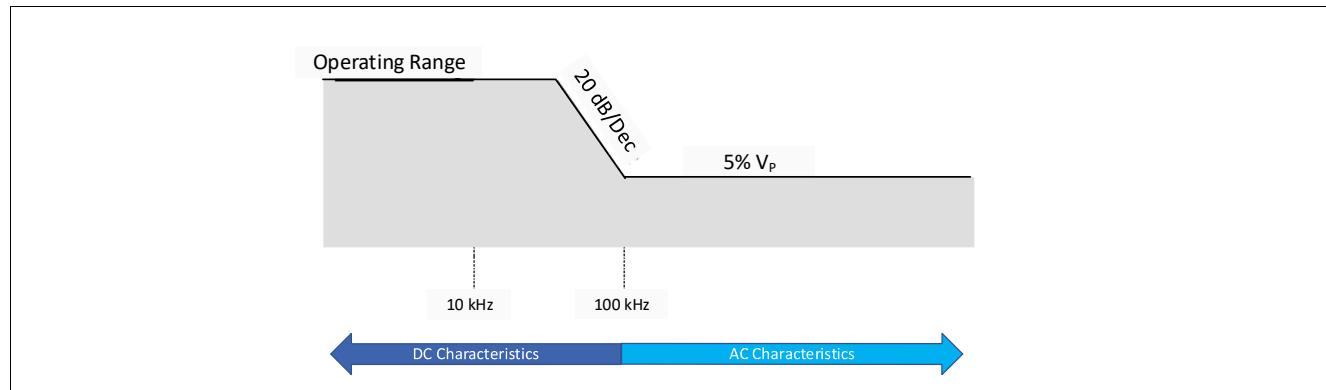

| 7.7.3.1 | $V_P$ AC and DC Power Supply Recommendations .....                 | 247 |

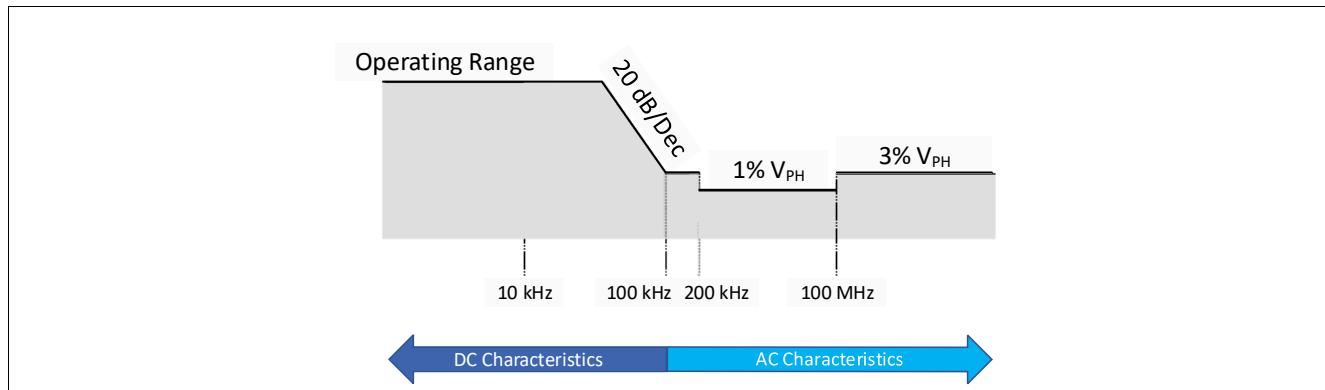

| 7.7.3.2 | $V_{PH}$ AC and DC Power Supply Recommendations .....              | 248 |

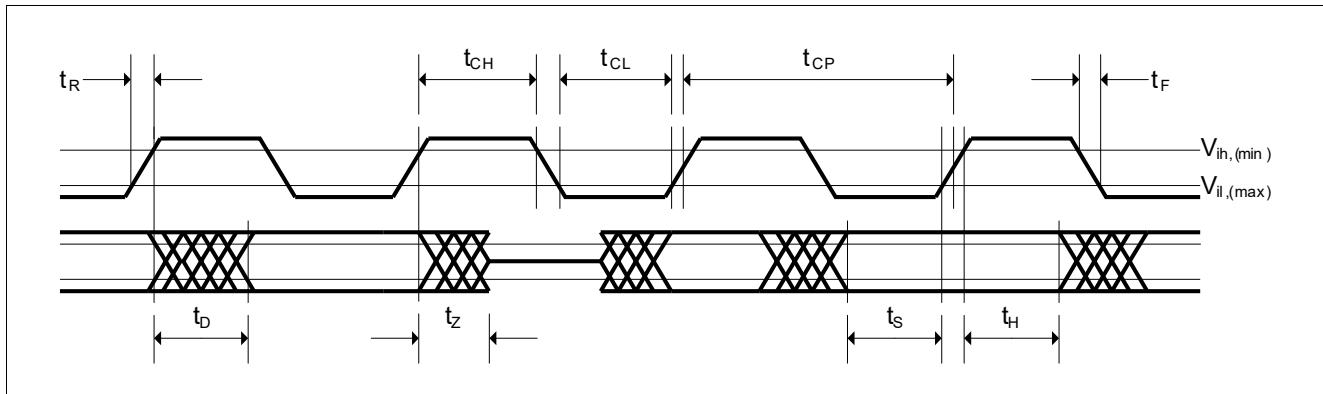

| 7.7.4   | MDIO Slave Interface .....                                         | 249 |

| 7.7.5   | Quad Serial Peripheral Interface (QSPI) .....                      | 250 |

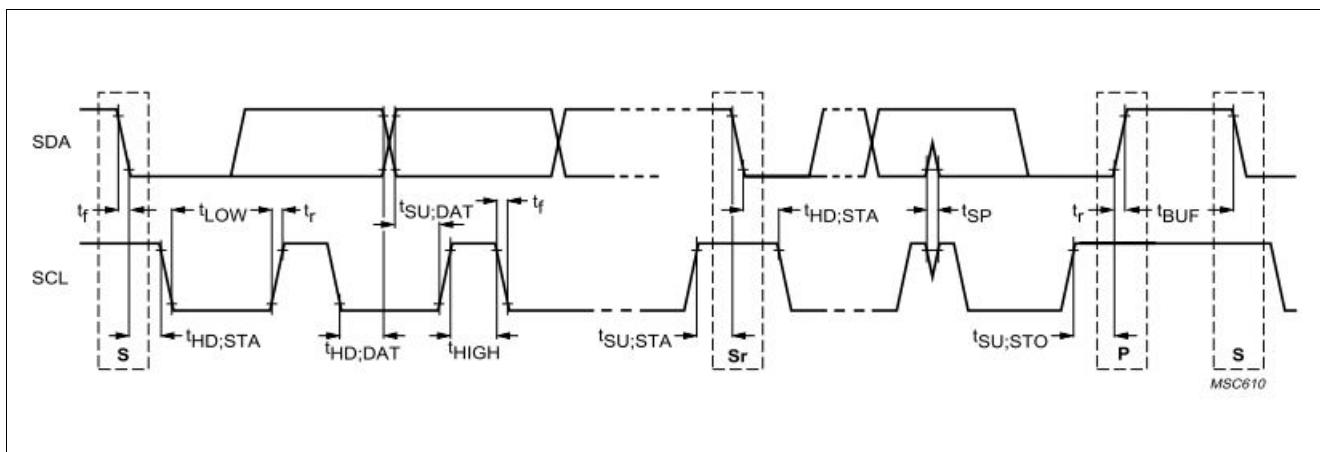

| 7.7.6   | I <sup>2</sup> C Interface .....                                   | 251 |

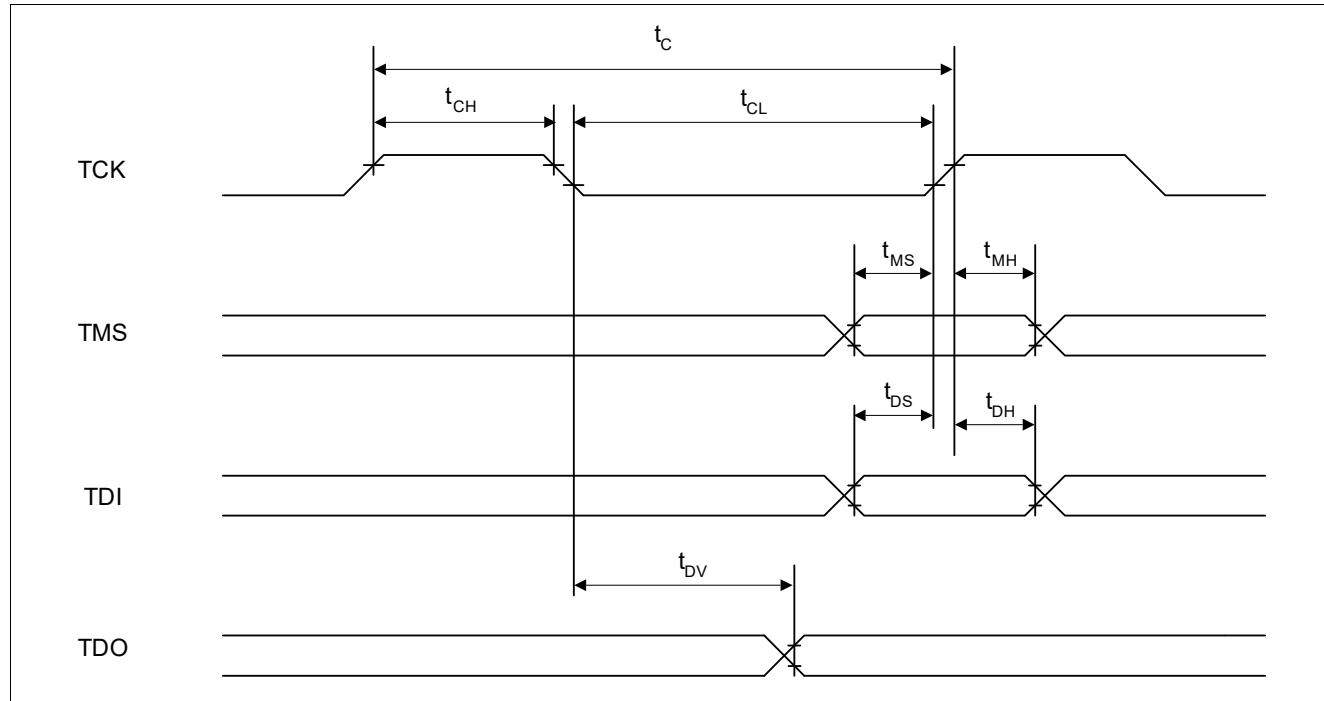

| 7.7.7   | JTAG Interface .....                                               | 252 |

| 7.7.8   | USXGMII Interface Characteristics .....                            | 253 |

| 7.7.8.1 | USXGMII Transmit Characteristics .....                             | 253 |

| 7.7.8.2 | USXGMII Receive Characteristics .....                              | 253 |

| 7.7.9   | Crystal Specification .....                                        | 254 |

| 7.8     | External Circuitry .....                                           | 255 |

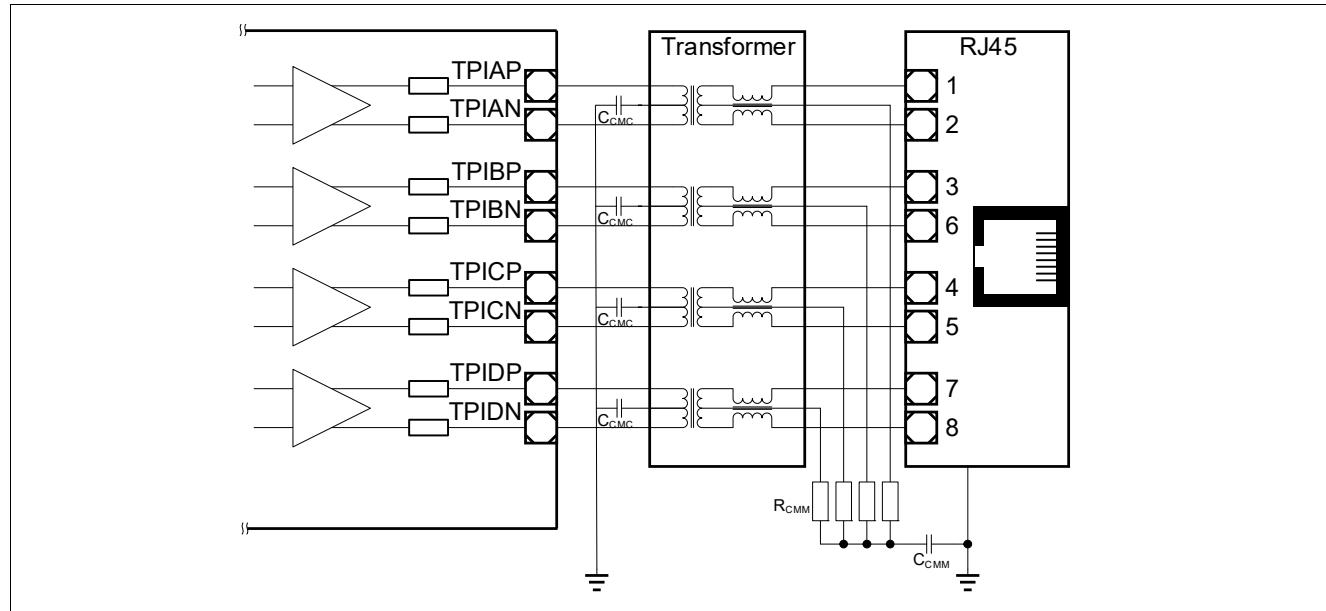

| 7.8.1   | Twisted-Pair Common-Mode Rejection and Termination Circuitry ..... | 255 |

| 7.8.2   | Transformer (Magnetics) .....                                      | 256 |

| 7.8.3   | RJ45 Plug .....                                                    | 257 |

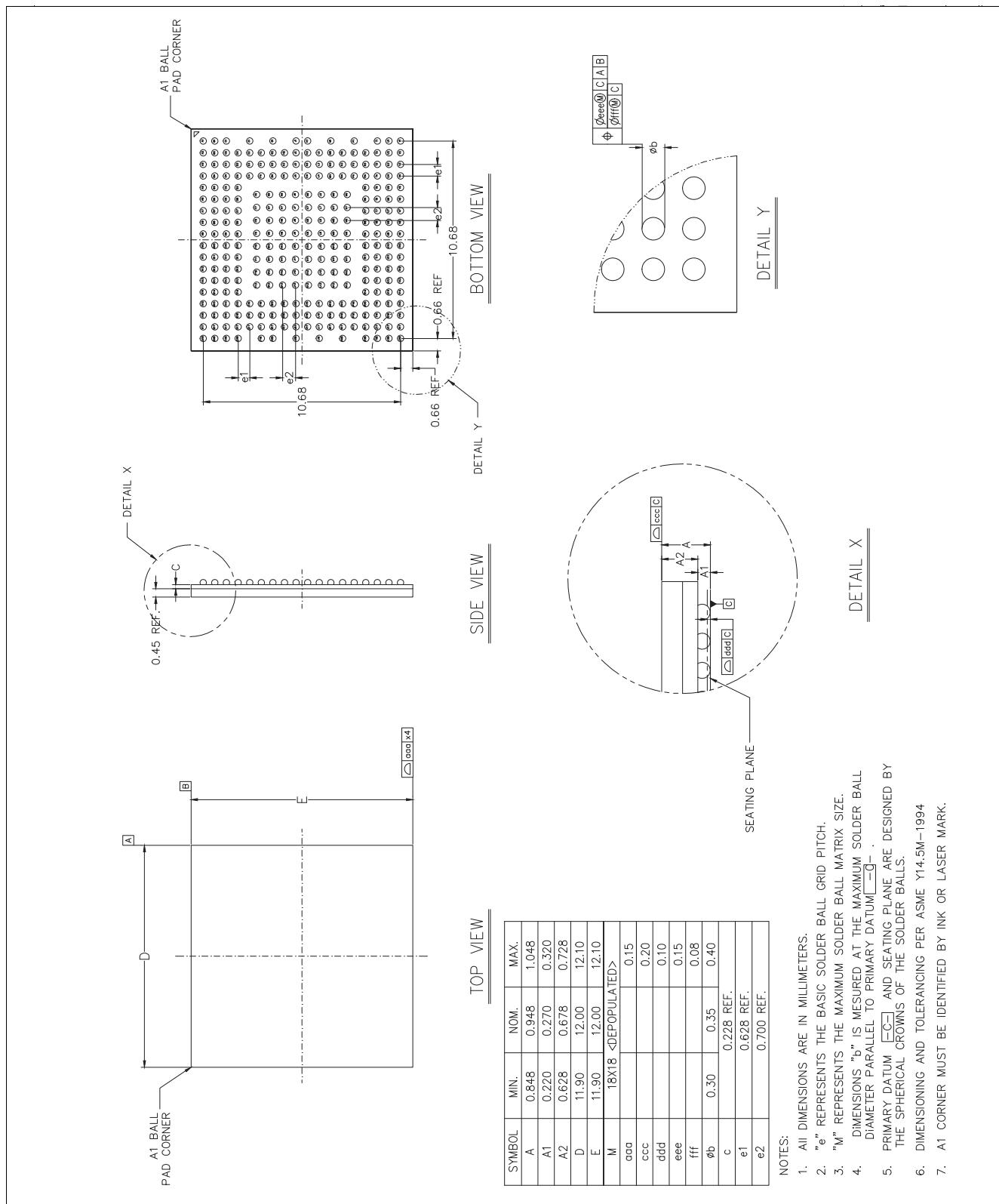

| 8       | <b>Package Outline</b> .....                                       | 258 |

| 9       | <b>Product Ordering Information</b> .....                          | 260 |

|         | <b>Literature References</b> .....                                 | 261 |

|         | <b>Standards References</b> .....                                  | 261 |

|         | <b>Terminology</b> .....                                           | 262 |

## List of Figures

|           |                                                                         |     |

|-----------|-------------------------------------------------------------------------|-----|

| Figure 1  | MxL86288L Block Diagram                                                 | 15  |

| Figure 2  | MxL86288L External Signal Overview                                      | 16  |

| Figure 3  | Ball Diagram for PG-FCLBGA-277 (Top View)                               | 18  |

| Figure 4  | MDIO Slave                                                              | 45  |

| Figure 5  | MDIO Access Timing                                                      | 46  |

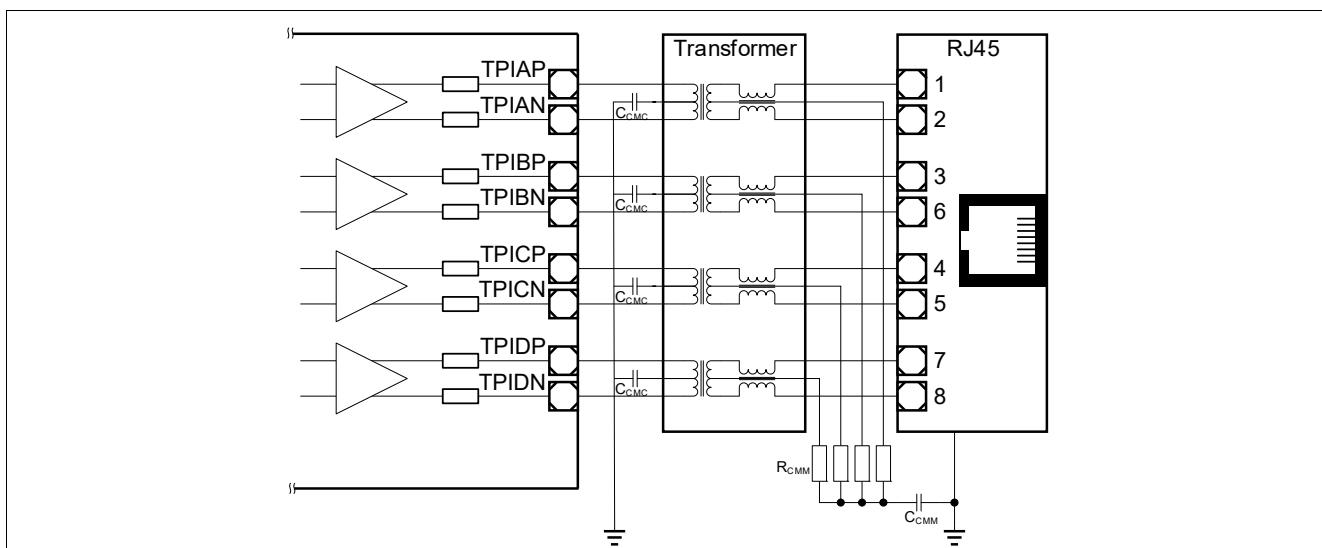

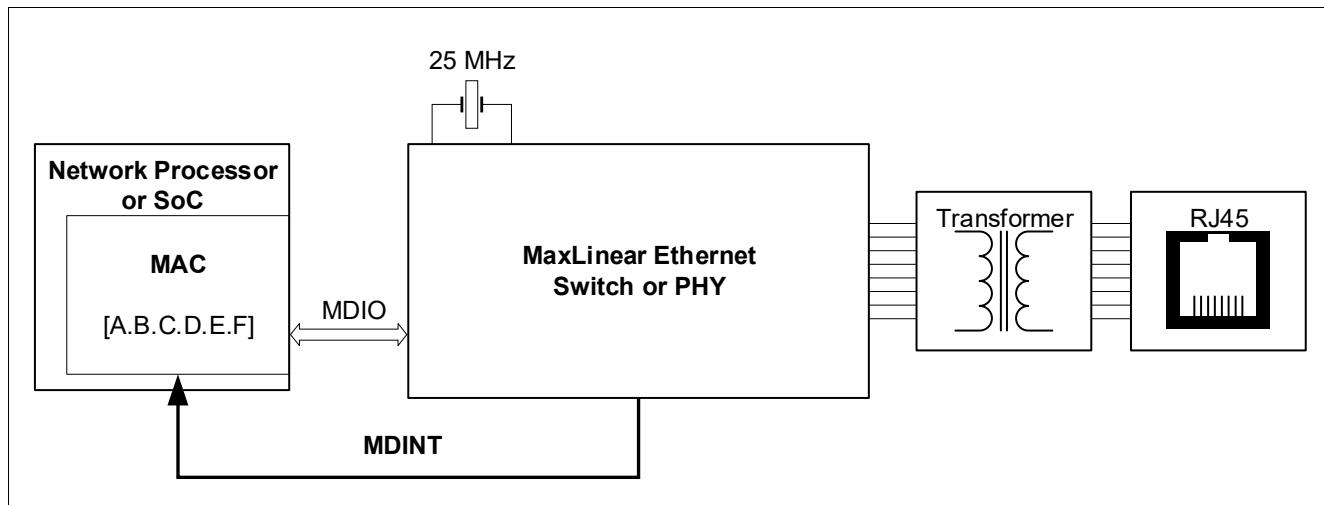

| Figure 6  | Twisted-Pair Interface of MxL86288L Including Transformer and RJ45 Plug | 52  |

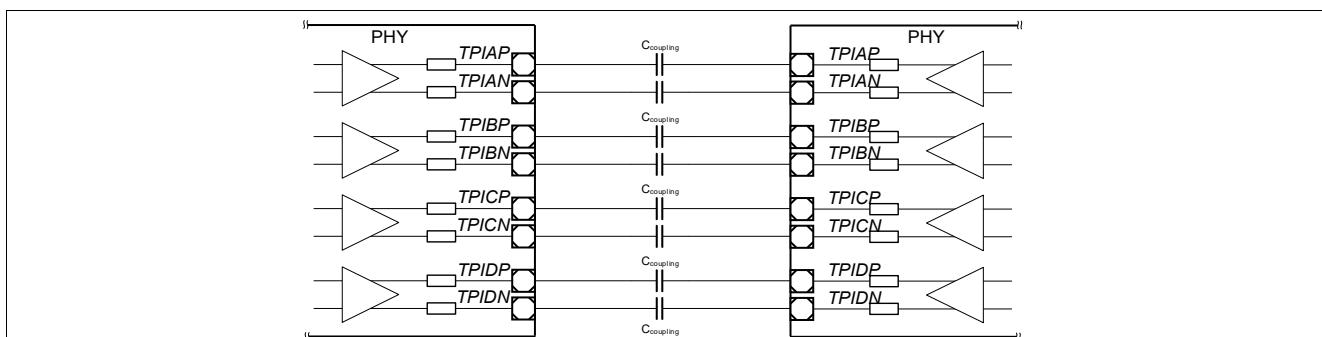

| Figure 7  | External Circuitry for the Transformerless Ethernet Application         | 52  |

| Figure 8  | RJ45 Tab Up or Tab Down Configuration                                   | 55  |

| Figure 9  | WoL Application Block Diagram                                           | 56  |

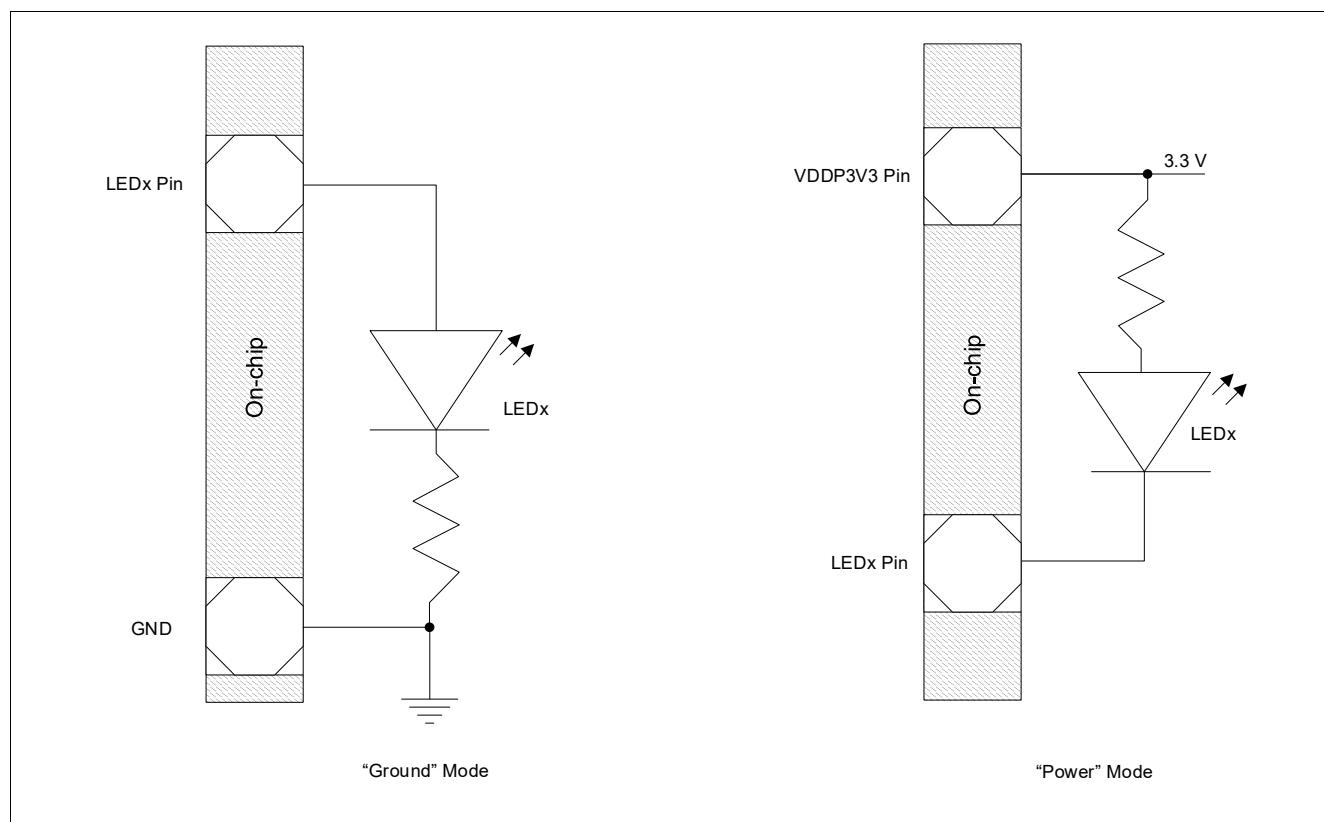

| Figure 10 | LED Connection Options to Ground or Power Supply                        | 58  |

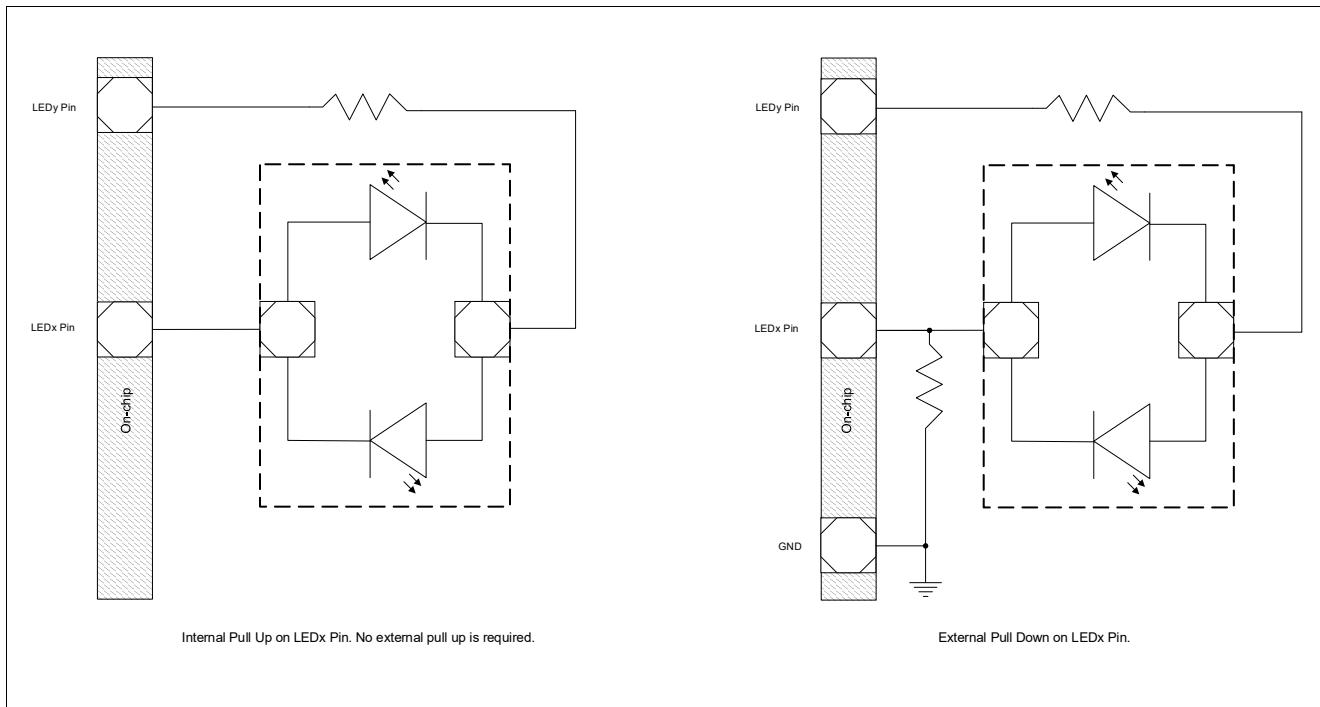

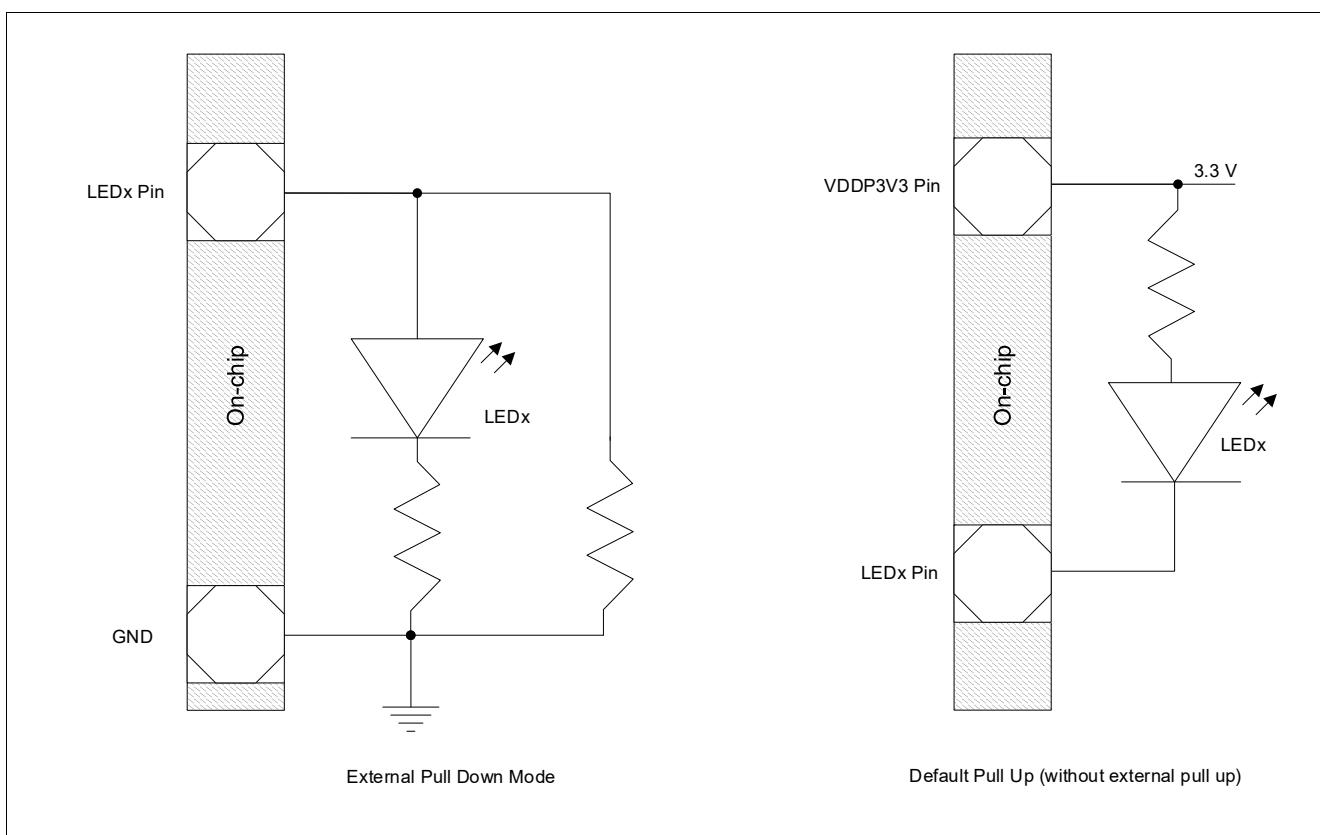

| Figure 11 | Connection of a Dual Color LED and Configuring Pin Strap Value          | 59  |

| Figure 12 | Connection of a Single Color LED and Configuring Pin Strap Value        | 59  |

| Figure 13 | LED Brightness Control by Controlling LED Output Enable/Disable         | 60  |

| Figure 14 | State Diagram for Power Down State Management                           | 63  |

| Figure 15 | Low Power Sequence                                                      | 65  |

| Figure 16 | EEE Low Power Idle Sequence                                             | 69  |

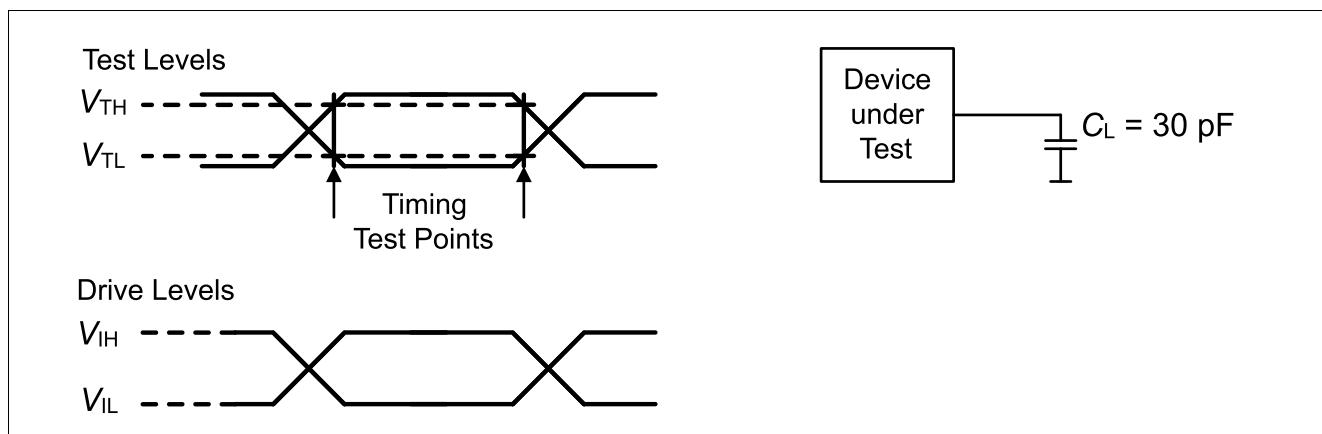

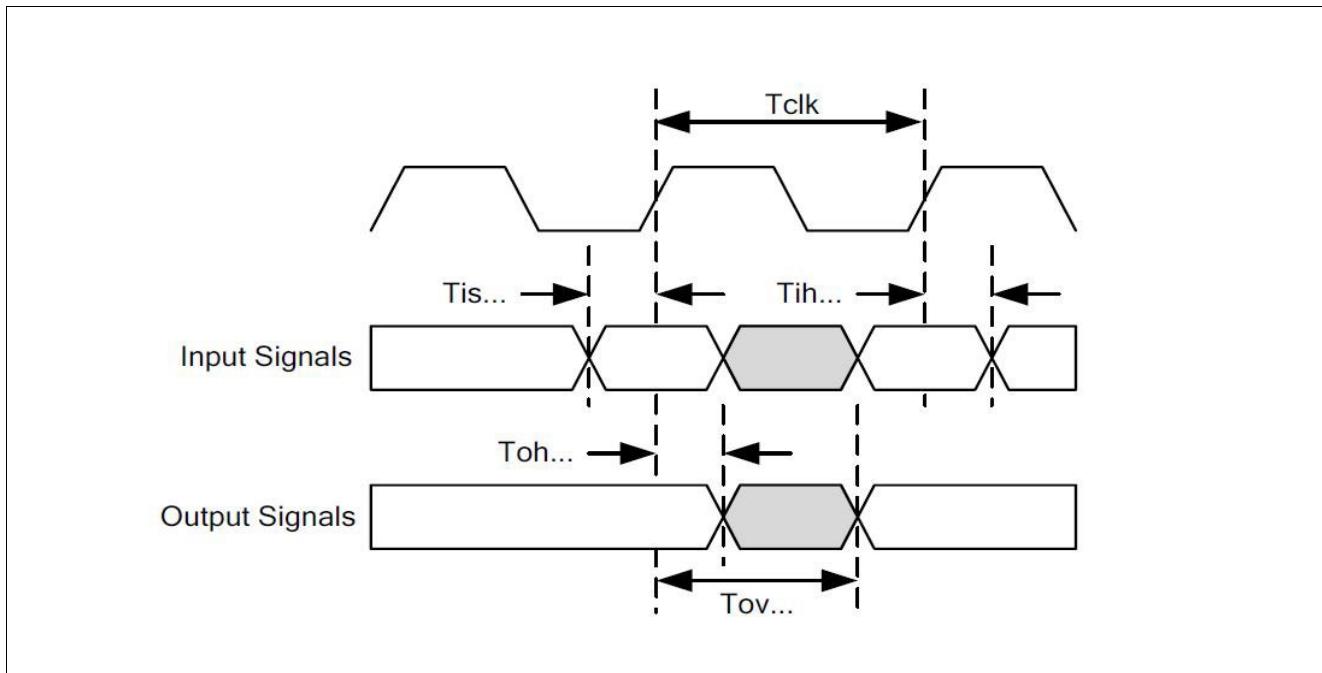

| Figure 17 | Input/Output Waveform for AC Tests                                      | 244 |

| Figure 18 | Timing Diagram for the Reset Sequence                                   | 245 |

| Figure 19 | DC and AC Characteristics for $V_P$ Supply                              | 247 |

| Figure 20 | DC and AC Characteristics for $V_{PH}$ Supply                           | 248 |

| Figure 21 | Timing Diagram for the MDIO Slave Interface                             | 249 |

| Figure 22 | QSPI Master Interface Timing                                            | 250 |

| Figure 23 | I <sup>2</sup> C Timing                                                 | 251 |

| Figure 24 | Test Interface Timing                                                   | 252 |

| Figure 25 | Twisted Pair Common-Mode Rejection and Termination Circuitry            | 255 |

| Figure 26 | Schematic of an Ethernet Transformer Device                             | 256 |

| Figure 27 | PG-FCLBGA-277 12 mm x 12 mm Package Outline                             | 259 |

## List of Tables

|          |                                                                      |     |

|----------|----------------------------------------------------------------------|-----|

| Table 1  | Ball Diagram Color Codes . . . . .                                   | 17  |

| Table 2  | Abbreviations for Pin Type . . . . .                                 | 19  |

| Table 3  | Abbreviations for Buffer Type . . . . .                              | 19  |

| Table 4  | Ethernet Twisted Pair Interface Signals . . . . .                    | 20  |

| Table 5  | USXGMII Interface Signals . . . . .                                  | 22  |

| Table 6  | MDIO Management Interface Signals . . . . .                          | 23  |

| Table 7  | QSPI Management Interface Signals . . . . .                          | 24  |

| Table 8  | I <sup>2</sup> C Management Interface Signals . . . . .              | 26  |

| Table 9  | Reset Signals . . . . .                                              | 27  |

| Table 10 | LED and Debug Interface Signals . . . . .                            | 28  |

| Table 11 | Miscellaneous Signals . . . . .                                      | 34  |

| Table 12 | Power Supply Pins for GPHY . . . . .                                 | 36  |

| Table 13 | Power Supply Pins for USXGMII . . . . .                              | 38  |

| Table 14 | Power Supply Pins for TPI (AFE) . . . . .                            | 39  |

| Table 15 | Ground Pins . . . . .                                                | 40  |

| Table 16 | Not Connected Signals . . . . .                                      | 41  |

| Table 17 | Pin Names Used for Pin Strapping . . . . .                           | 43  |

| Table 18 | Pin Strapping Configuration Description . . . . .                    | 43  |

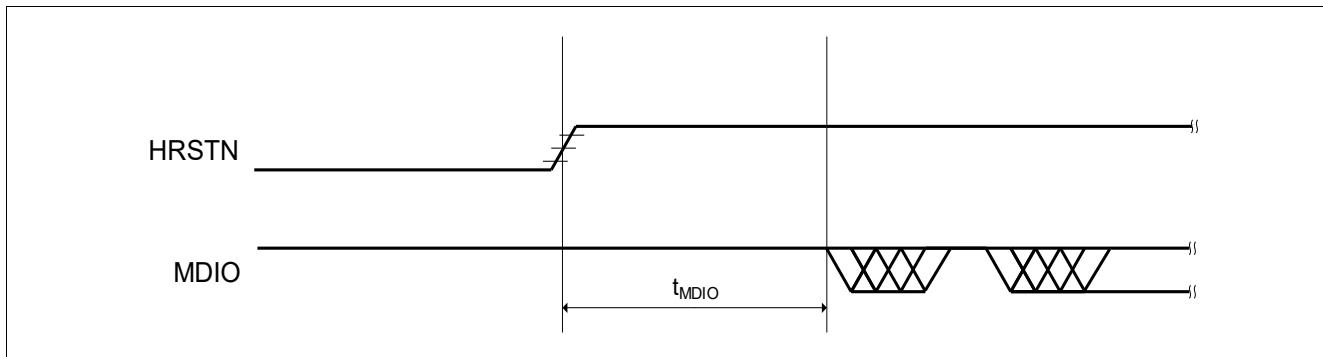

| Table 19 | MDIO Ready Timing . . . . .                                          | 46  |

| Table 20 | Supported Flash Memory Devices . . . . .                             | 48  |

| Table 21 | Flash Command and Timing . . . . .                                   | 49  |

| Table 22 | GPIO Mapping . . . . .                                               | 50  |

| Table 23 | Supported Twisted Pair Mappings on a Cat 5 or Better Cable . . . . . | 54  |

| Table 24 | Programming Sequence for the Wake-on-LAN Functionality . . . . .     | 56  |

| Table 25 | Ethernet SerDes Interface Feature List . . . . .                     | 57  |

| Table 26 | Low Power State Entry and Exit Sequence . . . . .                    | 66  |

| Table 27 | MDIO/MMD Devices Present in MxL86288L . . . . .                      | 73  |

| Table 28 | Register Access Type . . . . .                                       | 76  |

| Table 29 | Registers Overview- Standard Management Registers . . . . .          | 77  |

| Table 30 | Registers Overview- PHY-specific Management Registers . . . . .      | 100 |

| Table 31 | Register Access Type . . . . .                                       | 118 |

| Table 32 | Registers Overview- Standard PMAPMD Registers . . . . .              | 119 |

| Table 33 | Registers Overview- Standard PCS Registers . . . . .                 | 160 |

| Table 34 | Registers Overview- Standard Auto-Negotiation Registers . . . . .    | 180 |

| Table 35 | Registers Overview- Vendor Specific 1 Device Registers . . . . .     | 209 |

| Table 36 | Registers Overview- Vendor Specific 2 Device Registers . . . . .     | 229 |

| Table 37 | Absolute Maximum Ratings . . . . .                                   | 237 |

| Table 38 | Operating Range . . . . .                                            | 239 |

| Table 39 | Typical Power Consumption . . . . .                                  | 240 |

| Table 40 | Maximum Power Consumption . . . . .                                  | 240 |

| Table 41 | Maximum Current Per Rail . . . . .                                   | 241 |

| Table 42 | DC Characteristics of the GPIO Interfaces (VDDP = 3.3 V) . . . . .   | 242 |

| Table 43 | DC Characteristics of the GPIO Interfaces (VDDP = 1.8 V) . . . . .   | 242 |

| Table 44 | Temperature Sensor Characteristics . . . . .                         | 243 |

| Table 45 | Power Supply Timings . . . . .                                       | 245 |

| Table 46 | AC Characteristics of Input Clock on XTAL1 Pin . . . . .             | 246 |

| Table 47 | AC Characteristics of the Power Supply . . . . .                     | 246 |

| Table 48 | Timing Characteristics of the MDIO Slave Interface . . . . .         | 249 |

| Table 49 | QSPI Interface Timing Parameters . . . . .                           | 250 |

---

List of Tables

|          |                                                                                          |     |

|----------|------------------------------------------------------------------------------------------|-----|

| Table 50 | I <sup>2</sup> C Timing . . . . .                                                        | 251 |

| Table 51 | Test Interface Clock . . . . .                                                           | 252 |

| Table 52 | JTAG Timing . . . . .                                                                    | 252 |

| Table 53 | Transmit Characteristics of the USXGMII . . . . .                                        | 253 |

| Table 54 | Receive Characteristics of the USXGMII . . . . .                                         | 253 |

| Table 55 | Specification of the Crystal . . . . .                                                   | 254 |

| Table 56 | Electrical Characteristics for Common-Mode Rejection and Termination Circuitry . . . . . | 255 |

| Table 57 | Electrical Characteristics for Supported Transformers (Magnetics) . . . . .              | 256 |

| Table 58 | Electrical Characteristics for Supported RJ45 Plugs . . . . .                            | 257 |

| Table 59 | JEDEC Thermal Resistance Package Parameter - Compact 2-R Model Network . . . . .         | 258 |

| Table 60 | Stress Force Package Parameter . . . . .                                                 | 258 |

| Table 61 | Product and Package Naming . . . . .                                                     | 260 |

## Preface

This Data Sheet describes the features and system architecture of the Ethernet PHY MxL86288L, which is an 8-Port 2.5 Gigabit Ethernet PHY.

## Document Conventions

In the interest of brevity, this document uses short names to represent full product names.

**MxL86288L**      Ethernet PHY MxL86288L

## Document Information

This document's identifying information is:

### Document Reference (Citation) Name

*MxL86288L Ethernet PHY Data Sheet Rev. 1.1*

### File Name

621444\_MxL86288L\_DS\_Rev1.1.pdf

## Organization of this Document

- **Chapter 1, Product Overview**

This chapter provides an overview of the MxL86288L.

- **Chapter 2, External Signals**

This chapter provides a pinout of the MxL86288L device package.

- **Chapter 3, Functional Description**

This chapter provides the functional description for the MxL86288L.

- **Chapter 4, MDIO and MMD Register Interface Description**

This chapter describes the MDIO and MMD registers available to support the MxL86288L feature set.

- **Chapter 5, MDIO Registers Detailed Description**

This chapter describes the fields and reset values of the MDIO registers.

- **Chapter 6, MMD Registers Detailed Description**

This chapter describes the fields and reset values of the MMD registers.

- **Chapter 7, Electrical Characteristics**

This chapter provides the electrical characteristics for the MxL86288L.

- **Chapter 8, Package Outline**

This chapter provides a package outline for the MxL86288L.

- **Chapter 9, Product Ordering Information**

This chapter provides the product ordering details for the MxL86288L.

- **Standards References**

## 1 Product Overview

The MxL86288L device is a low power multi-port Ethernet PHY transceiver integrated circuit with two 10G Ethernet SerDes interfaces. The MxL86288L has eight integrated Ethernet BASE-T PHYs which support four data rates: 2500, 1000, 100, and 10 Mbps.

On the Ethernet Twisted Pair Interface (TPI), the MxL86288L is compliant with the standards from IEEE 802.3 referenced in [\[2\]](#):

- 2.5GBASE-T (IEEE 802.3 Clause 126, NBASE-T)

- 1000BASE-T (IEEE 802.3 Clause 40)

- 100BASE-TX (IEEE 802.3 Clause 25)

- 10BASE-Te (IEEE 802.3 Clause 14)

This interface supports the Energy-Efficient Ethernet (EEE) feature to reduce idle mode power consumption. Power saving at the system level is also possible with the wake-on-LAN feature. A low-EMI line driver with integrated termination facilitates the PCB design.

With reference to the Open System Interconnection (OSI) model, the MxL86288L implements eight layer 1 physical media access devices, and each is connected to a layer 2 MAC using a SerDes data interface, and an MDIO management interface.

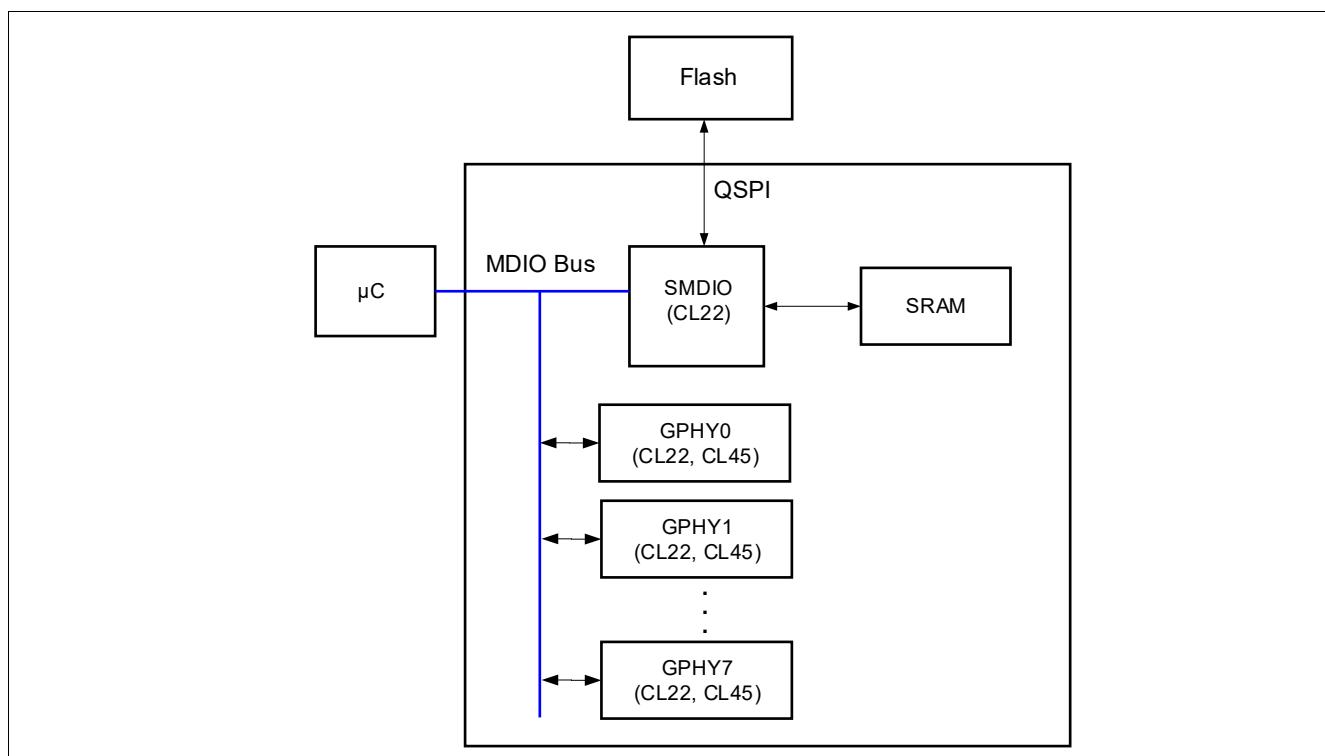

The MxL86288L provides two Ethernet SerDes data interfaces to connect to a MAC processor with multi-port (4 x 2.5G) USXGMII interface using an MDIO slave interface for management.

The MxL86288L supports a standard MDIO management interface as defined in IEEE 802.3 Clause 22 and Clause 45 [\[2\]](#). The MDIO serial interface is operable with a clock running up to 25 MHz. It allows a management entity (the external chip implementing the MAC) to access standard MDIO/MMD registers to control the MxL86288L's behavior, or to read the link status. The MxL86288L is also configurable via pin strapping.

The MxL86288L is capable of driving up to 24 LEDs (three per BASE-T port). Each LED is independently programmable to indicate the link speed and traffic activities. Several indication schemes are selectable.

External supplies of 0.8 V, 1.2 V, 1.8 V, and 3.3 V are required to power the MxL86288L device.

The MxL86288L uses a ball grid array package (type BGA 18 x18 matrix, size 12 mm x 12 mm).

## 1.1 Features

This section provides an overview of the features supported by the MxL86288L.

### Communication Interfaces

- The eight Ethernet BASE-T interfaces support:

- Ethernet modes and standards

- 2.5GBASE-T (IEEE 802.3, NBASE-T), 1000BASE-T (IEEE 802.3), 100BASE-TX (IEEE 802.3), and 10BASE-T (IEEE 802.3)

- Ethernet twisted pair copper cable of category Cat5 or higher

- Low EMI voltage mode line driver with integrated termination resistors

- Transformerless Ethernet for backplane applications

- Auto-Negotiation (ANEG) with extended next page support

- Auto-MDIX and polarity correction

- Auto-Downspeed (ADS)

- 100BASE-TX EEE, 1000BASE-T EEE, 2.5GBASE-T EEE, and power down mode

- Cable diagnostics: cable open/short detection and cable length estimation

- Wake-on-LAN (WoL)

- Jumbo frames of up to 10 kB

- Two Ethernet SerDes interfaces, where each interface supports:

- 10G-USXGMII

- The PHY complies with all of the required features specified in the Cisco USXGMII Multiport Copper PHY Specification [\[5\]](#) and Cisco USXGMII Single-port Copper PHY Specification [\[6\]](#)

- Back channel equalization, auto-negotiation, Forward Error Correction (FEC)

- Clock and Data Recovery (CDR), no clock forwarding required

- Clause 37 auto-negotiation

- Packet Control Header (PCH) over Preamble

- The management interface supports the communication between the Station Manager (STA, per IEEE 802.3) and the MxL86288L using:

- A Management Data Input/Output (MDIO) slave interface providing access to the standard registers in the MMD

- An MDIO interface clock of up to 25 MHz

- 3 MDIO message frame types as described in IEEE 802.3: Clause 22, Clause 22 Extended, and Clause 45 [\[2\]](#)

- The Quad SPI master interface connecting to serial external Quad-SPI flash memory supports:

- Programmable interface clock: maximum 101 MHz

- Internal firmware code access from external Quad-SPI flash memory

- Write access to the Quad-SPI flash memory

- Different Quad-SPI flash memory sizes up to 512 MB

- Secure firmware upgrade of the flash memory

- One instance of the I<sup>2</sup>C master interface controlling external devices supports these speed modes:

- Standard mode (<100 Kbps)

- Fast mode (<400 Kbps)

- Fast mode plus (<1000 Kbps)

- High speed mode (<3.4 Mbps)

- The JTAG interface supports:

- Boundary scan

- Test and debug interface

- Shared pins with GPIO functions

- The LED interface supports:

- Programmable LED

- Up to three LEDs per BASE-T port

- Single and dual color LEDs

- Connection of LED to ground or 3.3 V

- Several LED indication schemes (link/activity, duplex/collision, and link speed)

- Configuration of LED indication via MDIO registers

- Control of LED brightness via software driver API

- Alternative configuration of LED pins as GPIO for custom indication

- Supports two external interrupts:

- Configurable as output to an external controller

- Configurable as input from external device(s)

- Configurable edge, level, and polarity

### Flash and Flashless Mode

- In flash mode, an external QSPI memory device is required to store the firmware

- In flashless mode, the firmware is downloaded from a host MAC SoC via the MDIO interface:

- Broadcast firmware download support

- Secure firmware download

### Clocking and Timing Features

- The input reference clock options are:

- 25 MHz crystal operation

- 25 MHz direct from an external oscillator

- An external CML/LVPECL reference clock operating at 50 MHz or 156.25 MHz

### Preemption

- Recognize preemption packet types defined in IEEE 802.3br.

- Forwarding of preemption packets

- PCH support of preemption packets

### Other Features

- Temperature Sensor (warning, interrupt, reset, and auto-downspeed)

### Power Supply

- 3.3 V, 1.8 V, 1.2 V, and 0.8 V external power sources

## 1.2 Block Diagram

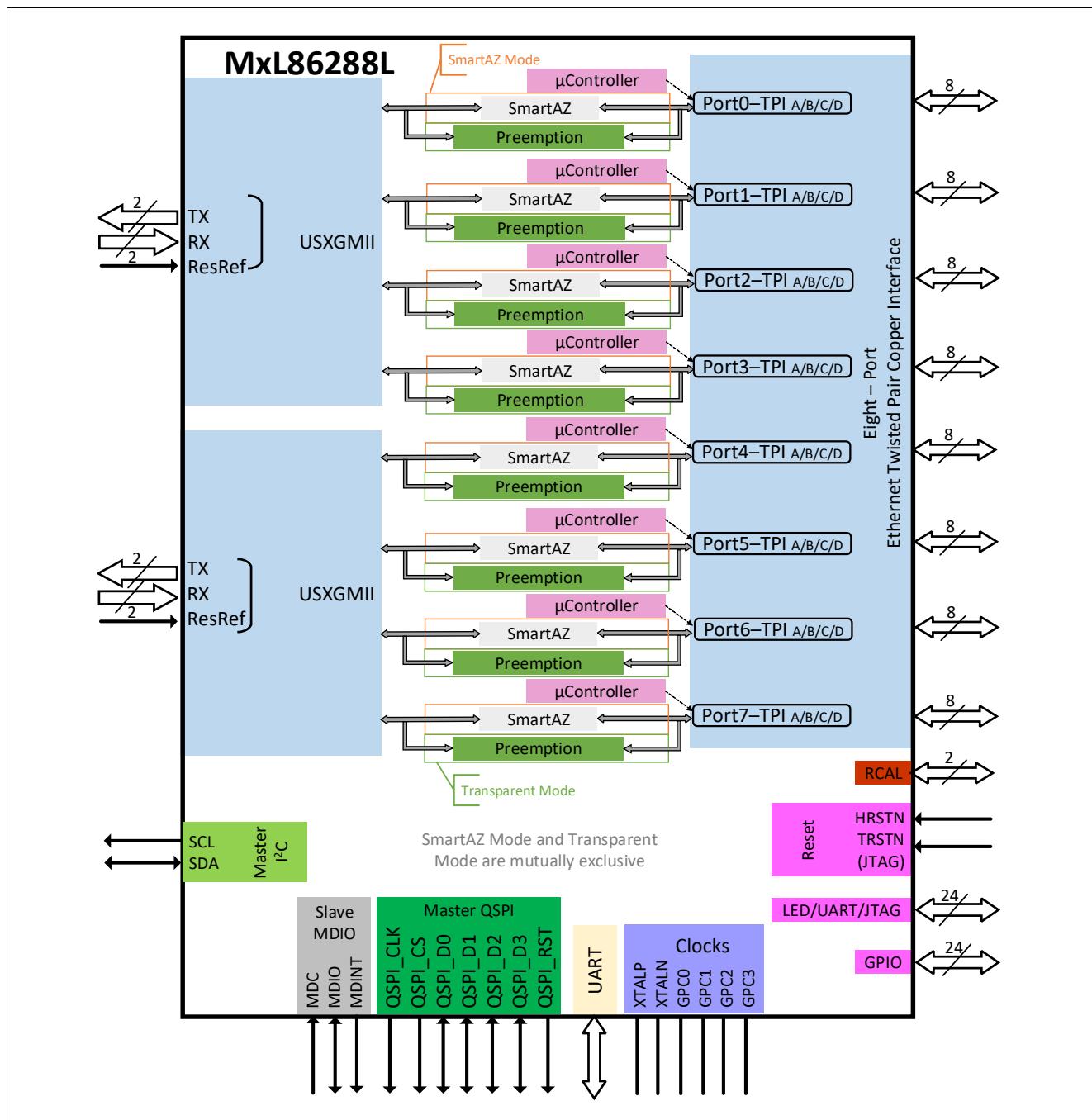

Figure 1 shows the block diagram of the MxL86288L. The main interfaces are:

- Data interface to SoC/MAC processor, using USXGMII

- Slave control interface driven by a SoC/MAC processor, using MDIO slave

- Master control interface using I<sup>2</sup>C master

- Interrupt signal MDINT allowing the MxL86288L to notify the SoC/MAC processor about a change of status

- LED control

- Twisted pair interfaces (TPI)

- Master Quad Serial Peripheral Interface (QSPI) interface

Figure 1 MxL86288L Block Diagram

## 2 External Signals

This chapter describes the signal mapping to the package.

### 2.1 Logic Symbol

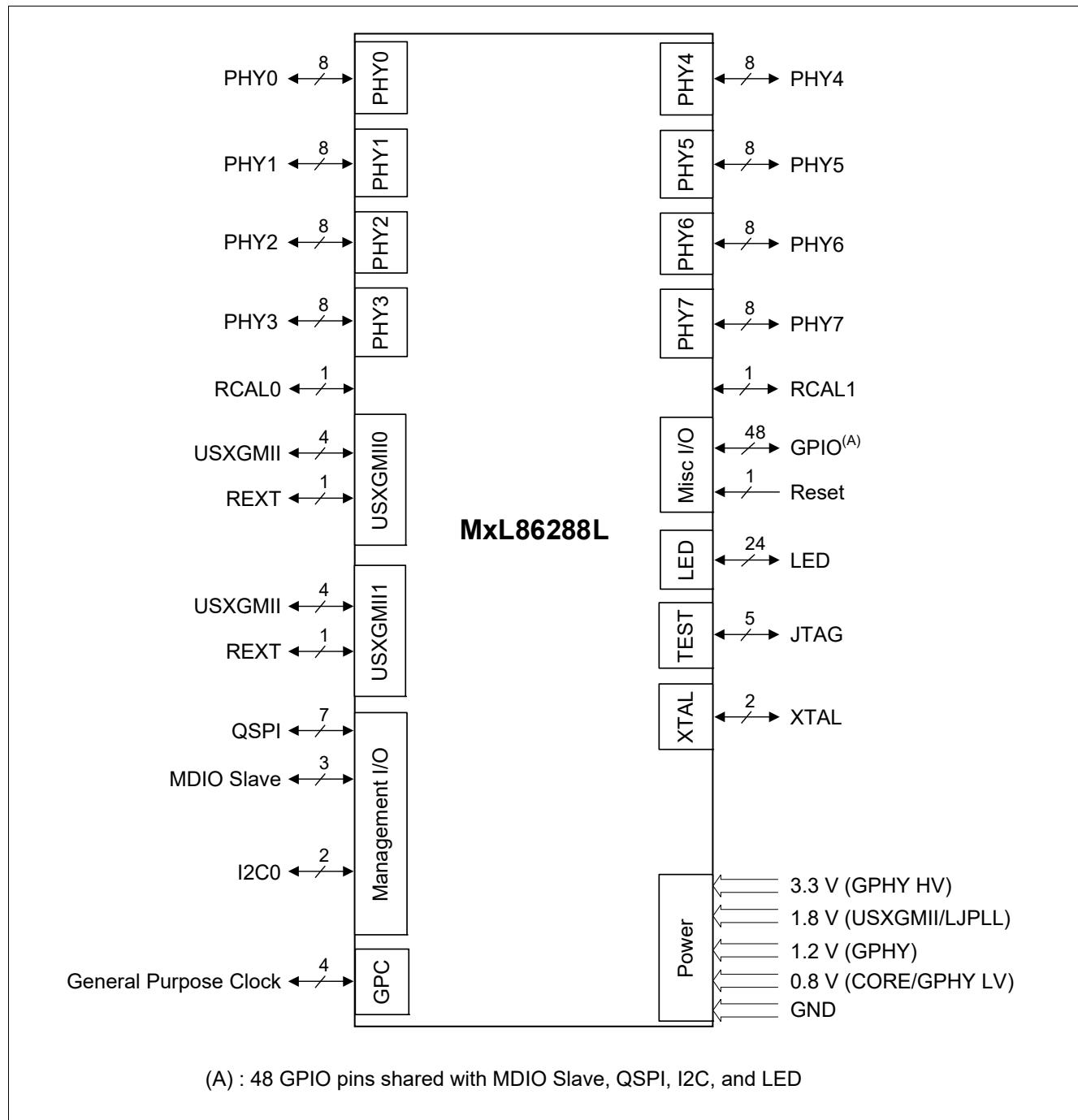

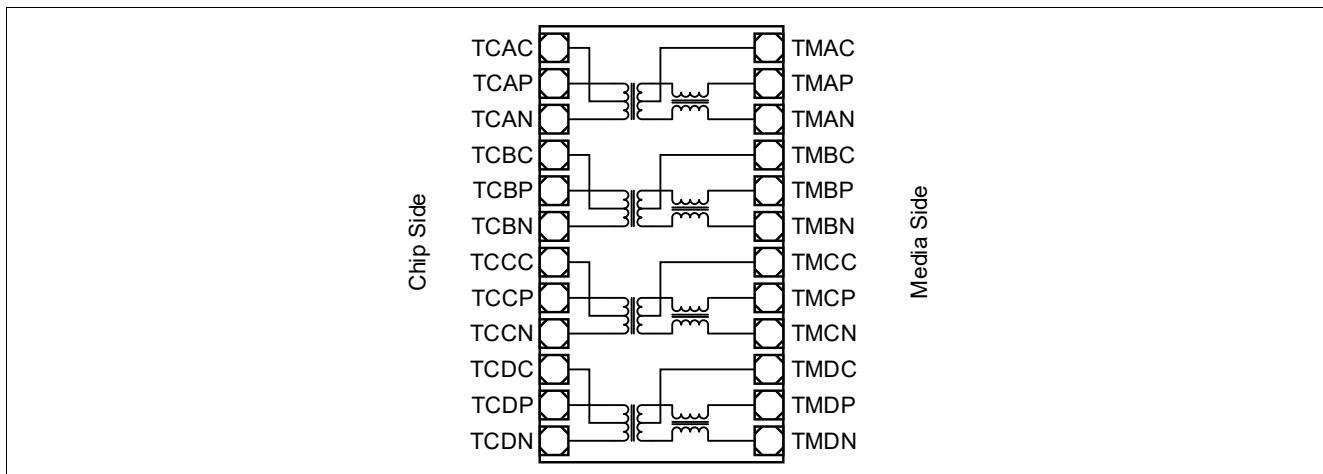

**Figure 2** gives an overview of the device's external interfaces.

**Figure 2** MxL86288L External Signal Overview

## 2.2 External Signal Description

This section provides the ball diagram, abbreviations for pin types and buffer types, and the table of input and output signals.

### 2.2.1 Ball Diagram

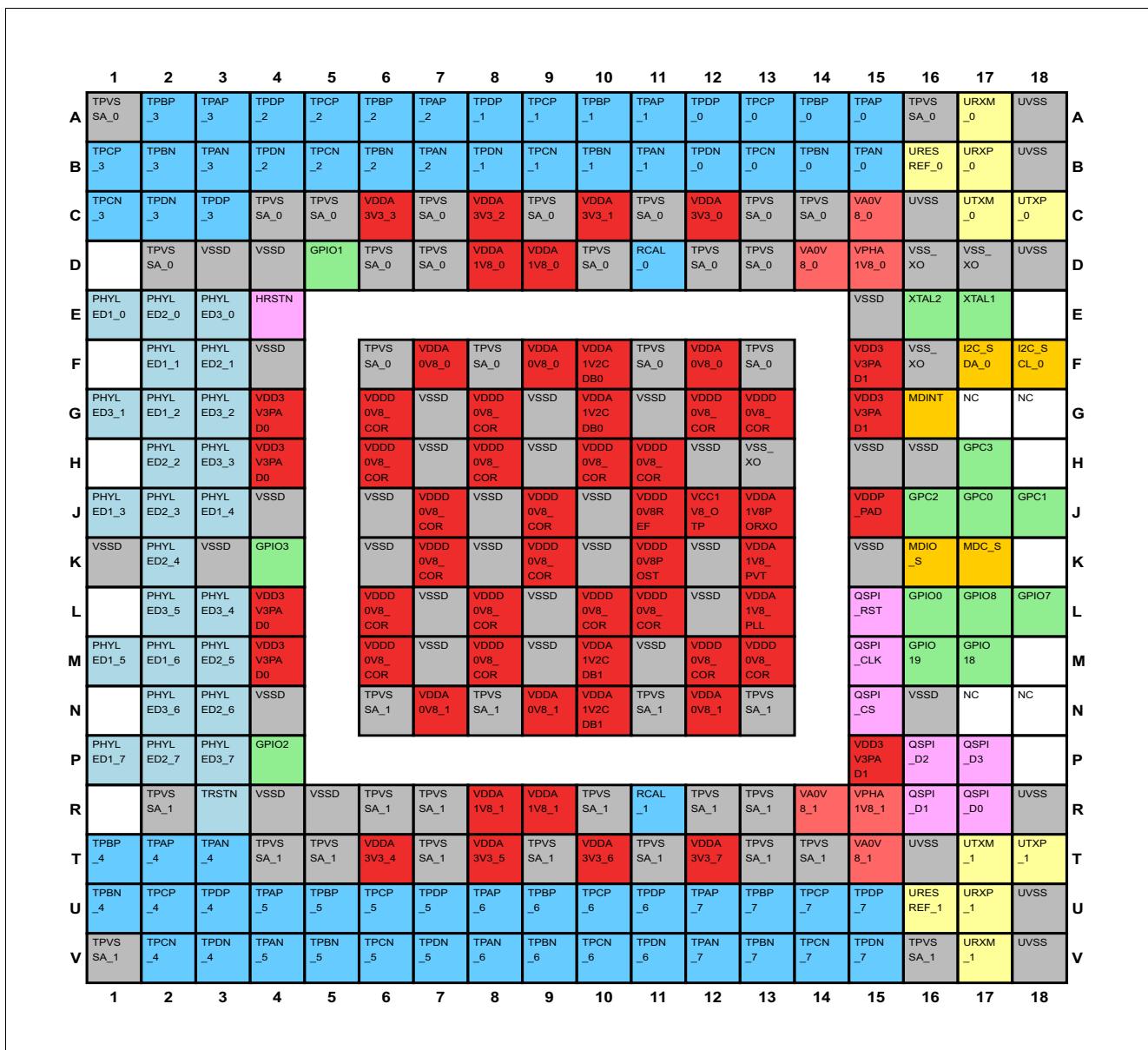

[Figure 3](#) shows the ball diagram. [Table 1](#) lists the ball diagram color codes.

**Table 1 Ball Diagram Color Codes**

| Color       | Description                    |

|-------------|--------------------------------|

| White       | Unpopulated Balls              |

| Red         | Power                          |

| Light Red   | USXGMII Power                  |

| Orange      | MDIO, I <sup>2</sup> C Signals |

| Grey        | Ground                         |

| Blue        | TPI-related Signals            |

| Pink        | QSPI, Reset Signals            |

| Yellow      | USXGMI Signals                 |

| Light Green | Clock, GPIO Signals            |

| Light Blue  | LED, JTAG Signals              |

| White       | NC                             |

## External Signals

**Figure 3 Ball Diagram for PG-FCLBGA-277 (Top View)**

## 2.2.2 Abbreviations

**Table 2** and **Table 3** summarize the abbreviations used in the signal tables.

**Table 2 Abbreviations for Pin Type**

| Abbreviations | Description                                                                          |

|---------------|--------------------------------------------------------------------------------------|

| I             | Input-only, digital levels                                                           |

| O             | Output-only, digital levels                                                          |

| I/O           | Bidirectional input/output signal, digital levels                                    |

| Prg           | Bidirectional pin, programmable to operate either as input or output, digital levels |

| AI            | Input-only, analog levels                                                            |

| AO            | Output-only, analog levels                                                           |

| AI/AO         | Bidirectional, analog levels                                                         |

| PWR           | Power                                                                                |

| GND           | Ground                                                                               |

**Table 3 Abbreviations for Buffer Type**

| Abbreviations | Description                                                                            |

|---------------|----------------------------------------------------------------------------------------|

| A             | Analog characteristics, see the AC/DC specification for more information.              |

| Prg           | Programmable (open-drain/push-pull, pull-up/pull-down characteristic are programmable) |

| PU            | Pull up (internal, weak)                                                               |

## 2.2.3 Input/Output Signals

Table 4 to Table 16 provide a detailed description of all the pins.

### 2.2.3.1 Ethernet Twisted Pair Interface

Unused TPI signals must be unconnected.

**Table 4 Ethernet Twisted Pair Interface Signals**

| Ball No.                                    | Name          | Pin Type | Buffer Type | Function                                         |

|---------------------------------------------|---------------|----------|-------------|--------------------------------------------------|

| <b>Ethernet Port Twisted Pair Interface</b> |               |          |             |                                                  |

| A15                                         | <b>TPAP_0</b> | AI/AO    | A           | <b>Port 0 Transmit/Receive Positive/Negative</b> |

| B15                                         | <b>TPAN_0</b> | AI/AO    | A           |                                                  |

| A14                                         | <b>TPBP_0</b> | AI/AO    | A           |                                                  |

| B14                                         | <b>TPBN_0</b> | AI/AO    | A           |                                                  |

| A13                                         | <b>TPCP_0</b> | AI/AO    | A           |                                                  |

| B13                                         | <b>TPCN_0</b> | AI/AO    | A           |                                                  |

| A12                                         | <b>TPDP_0</b> | AI/AO    | A           |                                                  |

| B12                                         | <b>TPDN_0</b> | AI/AO    | A           |                                                  |

| A11                                         | <b>TPAP_1</b> | AI/AO    | A           | <b>Port 1 Transmit/Receive Positive/Negative</b> |

| B11                                         | <b>TPAN_1</b> | AI/AO    | A           |                                                  |

| A10                                         | <b>TPBP_1</b> | AI/AO    | A           |                                                  |

| B10                                         | <b>TPBN_1</b> | AI/AO    | A           |                                                  |

| A9                                          | <b>TPCP_1</b> | AI/AO    | A           |                                                  |

| B9                                          | <b>TPCN_1</b> | AI/AO    | A           |                                                  |

| A8                                          | <b>TPDP_1</b> | AI/AO    | A           |                                                  |

| B8                                          | <b>TPDN_1</b> | AI/AO    | A           |                                                  |

| A7                                          | <b>TPAP_2</b> | AI/AO    | A           | <b>Port 2 Transmit/Receive Positive/Negative</b> |

| B7                                          | <b>TPAN_2</b> | AI/AO    | A           |                                                  |

| A6                                          | <b>TPBP_2</b> | AI/AO    | A           |                                                  |

| B6                                          | <b>TPBN_2</b> | AI/AO    | A           |                                                  |

| A5                                          | <b>TPCP_2</b> | AI/AO    | A           |                                                  |

| B5                                          | <b>TPCN_2</b> | AI/AO    | A           |                                                  |

| A4                                          | <b>TPDP_2</b> | AI/AO    | A           |                                                  |

| B4                                          | <b>TPDN_2</b> | AI/AO    | A           |                                                  |

| A3                                          | <b>TPAP_3</b> | AI/AO    | A           | <b>Port 3 Transmit/Receive Positive/Negative</b> |

| B3                                          | <b>TPAN_3</b> | AI/AO    | A           |                                                  |

| A2                                          | <b>TPBP_3</b> | AI/AO    | A           |                                                  |

| B2                                          | <b>TPBN_3</b> | AI/AO    | A           |                                                  |

| B1                                          | <b>TPCP_3</b> | AI/AO    | A           |                                                  |

| C1                                          | <b>TPCN_3</b> | AI/AO    | A           |                                                  |

| C3                                          | <b>TPDP_3</b> | AI/AO    | A           |                                                  |

**Table 4** **Ethernet Twisted Pair Interface Signals (cont'd)**

| Ball No. | Name          | Pin Type | Buffer Type | Function                                         |

|----------|---------------|----------|-------------|--------------------------------------------------|

| C2       | <b>TPDN_3</b> | AI/AO    | A           |                                                  |

| T2       | <b>TPAP_4</b> | AI/AO    | A           | <b>Port 4 Transmit/Receive Positive/Negative</b> |

| T3       | <b>TPAN_4</b> | AI/AO    | A           |                                                  |

| T1       | <b>TPBP_4</b> | AI/AO    | A           |                                                  |

| U1       | <b>TPBN_4</b> | AI/AO    | A           |                                                  |

| U2       | <b>TPCP_4</b> | AI/AO    | A           |                                                  |

| V2       | <b>TPCN_4</b> | AI/AO    | A           |                                                  |

| U3       | <b>TPDP_4</b> | AI/AO    | A           |                                                  |

| V3       | <b>TPDN_4</b> | AI/AO    | A           |                                                  |

| U4       | <b>TPAP_5</b> | AI/AO    | A           | <b>Port 5 Transmit/Receive Positive/Negative</b> |

| V4       | <b>TPAN_5</b> | AI/AO    | A           |                                                  |

| U5       | <b>TPBP_5</b> | AI/AO    | A           |                                                  |

| V5       | <b>TPBN_5</b> | AI/AO    | A           |                                                  |

| U6       | <b>TPCP_5</b> | AI/AO    | A           |                                                  |

| V6       | <b>TPCN_5</b> | AI/AO    | A           |                                                  |

| U7       | <b>TPDP_5</b> | AI/AO    | A           |                                                  |

| V7       | <b>TPDN_5</b> | AI/AO    | A           |                                                  |

| U8       | <b>TPAP_6</b> | AI/AO    | A           | <b>Port 6 Transmit/Receive Positive/Negative</b> |

| V8       | <b>TPAN_6</b> | AI/AO    | A           |                                                  |

| U9       | <b>TPBP_6</b> | AI/AO    | A           |                                                  |

| V9       | <b>TPBN_6</b> | AI/AO    | A           |                                                  |

| U10      | <b>TPCP_6</b> | AI/AO    | A           |                                                  |

| V10      | <b>TPCN_6</b> | AI/AO    | A           |                                                  |

| U11      | <b>TPDP_6</b> | AI/AO    | A           |                                                  |

| V11      | <b>TPDN_6</b> | AI/AO    | A           |                                                  |

| U12      | <b>TPAP_7</b> | AI/AO    | A           | <b>Port 7 Transmit/Receive Positive/Negative</b> |

| V12      | <b>TPAN_7</b> | AI/AO    | A           |                                                  |

| U13      | <b>TPBP_7</b> | AI/AO    | A           |                                                  |

| V13      | <b>TPBN_7</b> | AI/AO    | A           |                                                  |

| U14      | <b>TPCP_7</b> | AI/AO    | A           |                                                  |

| V14      | <b>TPCN_7</b> | AI/AO    | A           |                                                  |

| U15      | <b>TPDP_7</b> | AI/AO    | A           |                                                  |

| V15      | <b>TPDN_7</b> | AI/AO    | A           |                                                  |

**Ethernet Port Test Point**

|     |               |       |   |                                                                                 |

|-----|---------------|-------|---|---------------------------------------------------------------------------------|

| D11 | <b>RCAL_0</b> | AI/AO | A | <b>Test Point for GPHY Ethernet Ports 0 to 3</b><br>Test point, do not connect. |

| R11 | <b>RCAL_1</b> | AI/AO | A | <b>Test Point for GPHY Ethernet Ports 4 to 7</b><br>Test point, do not connect. |

## 2.2.3.2 USXGMII Interface

Table 5 USXGMII Interface Signals

| Ball No. | Name             | Pin Type | Buffer Type | Function                                                                                                                                                                                                                                               |

|----------|------------------|----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B17      | <b>URXP_0</b>    | AI       | A           | <b>Differential USXGMII 0 Data Input Pair</b>                                                                                                                                                                                                          |

| A17      | <b>URXM_0</b>    | AI       | A           | These are the negative and positive signals of the differential input pair of the USXGMII SerDes interface. Due to the integrated CDR, no external transmission peer source-synchronous clock is required for USXGMII. These pins must be AC-coupled.  |

| C18      | <b>UTXP_0</b>    | AO       | A           | <b>Differential USXGMII 0 Data Output Pair</b>                                                                                                                                                                                                         |

| C17      | <b>UTXM_0</b>    | AO       | A           | These are the negative and positive signals of the differential output pair of the USXGMII SerDes interface. Due to the integrated CDR, no external transmission peer source-synchronous clock is required for USXGMII. These pins must be AC-coupled. |

| B16      | <b>URESREF_0</b> | AI/AO    | A           | <b>External USXGMII Tuning Resistor 0</b><br>Attach a 200 $\Omega$ ( $\pm 1\%$ ) resistor-to-ground on the board.                                                                                                                                      |

| U17      | <b>URXP_1</b>    | AI       | A           | <b>Differential USXGMII 1 Data Input Pair</b>                                                                                                                                                                                                          |

| V17      | <b>URXM_1</b>    | AI       | A           | These are the negative and positive signals of the differential input pair of the USXGMII SerDes interface. Due to the integrated CDR, no external transmission peer source-synchronous clock is required for USXGMII. These pins must be AC-coupled.  |

| T18      | <b>UTXP_1</b>    | AO       | A           | <b>Differential USXGMII 1 Data Output Pair</b>                                                                                                                                                                                                         |

| T17      | <b>UTXM_1</b>    | AO       | A           | These are the negative and positive signals of the differential output pair of the USXGMII SerDes interface. Due to the integrated CDR, no external transmission peer source-synchronous clock is required for USXGMII. These pins must be AC-coupled. |

| U16      | <b>URESREF_1</b> | AI/AO    | A           | <b>External USXGMII Tuning Resistor 1</b><br>Attach a 200 $\Omega$ ( $\pm 1\%$ ) resistor-to-ground on the board.                                                                                                                                      |

## 2.2.3.3 MDIO Interface

Table 6 MDIO Management Interface Signals

| Ball No.                    | Name          | Pin Type | Buffer Type | Function                                                                                                                                                                                                                                                        |

|-----------------------------|---------------|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>MDIO Slave Interface</b> |               |          |             |                                                                                                                                                                                                                                                                 |

| G16                         | <b>MDINT</b>  | O        | Prg         | <b>MDIO Interrupt from Any GPHY</b><br>The interrupt interrupts an external block such as a higher-level management entity or a device controller of an SoC, on detection of certain events and states inside the GPHY device.<br>Voltage Domain: 1.8 V / 3.3 V |

|                             | GPIO4         | Prg      |             | <b>General Purpose IO 4</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 1.8 V / 3.3 V                                                                                                       |

| K17                         | <b>MDC_S</b>  | I        | Prg         | <b>MDIO Slave Clock</b><br>The external controller provides the serial clock of up to 25 MHz on this input.<br>Voltage Domain: 1.8 V / 3.3 V                                                                                                                    |

|                             | GPIO5         | Prg      |             | <b>General Purpose IO 5</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 1.8 V / 3.3 V                                                                                                       |

| K16                         | <b>MDIO_S</b> | I/O      | Prg         | <b>MDIO Slave Data Input/Output</b><br>The external controller uses this signal to address internal registers and to transfer data to and from the internal registers.<br>Voltage Domain: 1.8 V / 3.3 V                                                         |

|                             | GPIO6         | Prg      |             | <b>General Purpose IO 6</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 1.8 V / 3.3 V                                                                                                       |

## 2.2.3.4 QSPI Interface

Table 7 QSPI Management Interface Signals

| Ball No. | Name     | Pin Type | Buffer Type | Function                                                                                                                                           |

|----------|----------|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| R17      | QSPI_D0  | I/O      | Prg         | <b>QSPI Data 0</b><br>QSPI interface data 0<br>Voltage Domain: 3.3 V                                                                               |

|          | GPIO9    | Prg      |             | <b>General Purpose IO 9</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V  |

| R16      | QSPI_D1  | I/O      | Prg         | <b>QSPI Data 1</b><br>QSPI interface data 1<br>Voltage Domain: 3.3 V                                                                               |

|          | GPIO10   | Prg      |             | <b>General Purpose IO 10</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

| P16      | QSPI_D2  | I/O      | Prg         | <b>QSPI Data 2</b><br>QSPI interface data 2<br>Voltage Domain: 3.3 V                                                                               |

|          | GPIO11   | Prg      |             | <b>General Purpose IO 11</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

| P17      | QSPI_D3  | I/O      | Prg         | <b>QSPI Data 3</b><br>QSPI interface data 3<br>Voltage Domain: 3.3 V                                                                               |

|          | GPIO12   | Prg      |             | <b>General Purpose IO 12</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

| M15      | QSPI_CLK | O        | Prg         | <b>QSPI Clock</b><br>QSPI interface clock output<br>Voltage Domain: 3.3 V                                                                          |

|          | GPIO13   | Prg      |             | <b>General Purpose IO 13</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

Table 7 QSPI Management Interface Signals (cont'd)

| Ball No. | Name     | Pin Type | Buffer Type | Function                                                                                                                                           |

|----------|----------|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| N15      | QSPI_CS  | O        | Prg         | <b>QSPI Chip Select</b><br>QSPI interface chip select<br>Voltage Domain: 3.3 V                                                                     |

|          | GPIO14   | Prg      |             | <b>General Purpose IO 14</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

| L15      | QSPI_RST | O        | Prg         | <b>QSPI Reset</b><br>QSPI Reset<br>Voltage Domain: 3.3 V                                                                                           |

|          | GPIO15   | Prg      |             | <b>General Purpose IO 15</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

2.2.3.5 I<sup>2</sup>C InterfaceTable 8 I<sup>2</sup>C Management Interface Signals

| Ball No. | Name                   | Pin Type | Buffer Type | Function                                                                                                                                           |

|----------|------------------------|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| F18      | I <sup>2</sup> C_SCL_0 | O        | Prg         | <b>I<sup>2</sup>C 0 Clock Output</b><br>I <sup>2</sup> C 0 interface clock output<br>Voltage Domain: 3.3 V                                         |

|          | GPIO16                 | Prg      |             | <b>General Purpose IO 16</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

| F17      | I <sup>2</sup> C_SDA_0 | I/O      | Prg         | <b>I<sup>2</sup>C 0 Data</b><br>I <sup>2</sup> C 0 interface data<br>Voltage Domain: 3.3 V                                                         |

|          | GPIO17                 | Prg      |             | <b>General Purpose IO 17</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

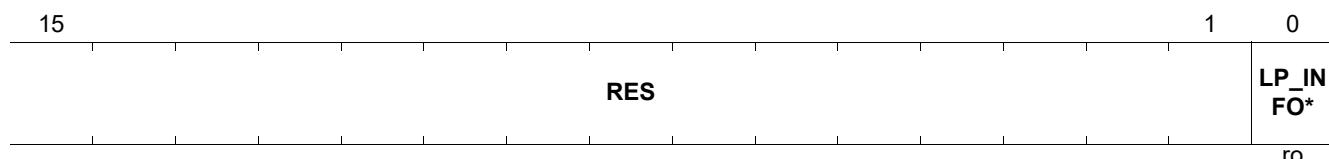

### 2.2.3.6 Reset Interface

Table 9 Reset Signals

| Ball No. | Name  | Pin Type | Buffer Type | Function                                                                               |

|----------|-------|----------|-------------|----------------------------------------------------------------------------------------|

| E4       | HRSTN | I        | PU          | <b>Hardware Reset</b><br>Asynchronous active low device reset<br>Voltage Domain: 3.3 V |

## 2.2.3.7 LED/UART/JTAG Interface

Table 10 LED and Debug Interface Signals

| Ball No.           | Name             | Pin Type | Buffer Type | Function                                                                                                                                           |

|--------------------|------------------|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>LED Signals</b> |                  |          |             |                                                                                                                                                    |

| E1                 | <b>PHYLED1_0</b> | I/O      |             | <b>GPHY LED1 for Port 0</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|                    | GPIO20           | Prg      | Prg         | <b>General Purpose IO 20</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

|                    | FW_UTXD          | O        |             | <b>Firmware UART Data Output</b><br>Firmware UART interface data output<br>Voltage Domain: 3.3 V                                                   |

| E2                 | <b>PHYLED2_0</b> | I/O      |             | <b>GPHY LED2 for Port 0</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|                    | GPIO21           | Prg      | Prg         | <b>General Purpose IO 21</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

|                    | FW_URXD          | I        |             | <b>Firmware UART Data Input</b><br>Firmware UART interface data input<br>Voltage Domain: 3.3 V                                                     |

| E3                 | <b>PHYLED3_0</b> | I/O      |             | <b>GPHY LED3 for Port 0</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|                    | GPIO22           | Prg      | Prg         | <b>General Purpose IO 22</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

| F2                 | <b>PHYLED1_1</b> | I/O      |             | <b>GPHY LED1 for Port 1</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|                    | GPIO23           | Prg      | Prg         | <b>General Purpose IO 23</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

|                    | FW_UTXD          | O        |             | <b>Firmware UART Data Output</b><br>Firmware UART interface data output<br>Voltage Domain: 3.3 V                                                   |

Table 10 LED and Debug Interface Signals (cont'd)

| Ball No. | Name             | Pin Type | Buffer Type | Function                                                                                                                                           |

|----------|------------------|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| F3       | <b>PHYLED2_1</b> | I/O      |             | <b>GPHY LED2 for Port 1</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO24           | Prg      | Prg         | <b>General Purpose IO 24</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

| G1       | <b>PHYLED3_1</b> | I/O      |             | <b>GPHY LED3 for Port 1</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO25           | Prg      | Prg         | <b>General Purpose IO 25</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

| G2       | <b>PHYLED1_2</b> | I/O      |             | <b>GPHY LED1 for Port 2</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO26           | Prg      | Prg         | <b>General Purpose IO 26</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

|          | TDI              | I        |             | <b>JTAG Serial Test Data Input</b><br>Voltage Domain: 3.3 V<br><i>Note: No external pull-up required.</i>                                          |

|          | FW_UTXD          | O        |             | <b>Firmware UART Data Output</b><br>Firmware UART interface data output<br>Voltage Domain: 3.3 V                                                   |

| H2       | <b>PHYLED2_2</b> | I/O      |             | <b>GPHY LED2 for Port 2</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO27           | Prg      | Prg         | <b>General Purpose IO 27</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

|          | TMS              | I        |             | <b>JTAG Test Mode Select</b><br>Voltage Domain: 3.3 V<br><i>Note: No external pull-up required.</i>                                                |

| G3       | <b>PHYLED3_2</b> | I/O      |             | <b>GPHY LED3 for Port 2</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO28           | Prg      | Prg         | <b>General Purpose IO 28</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

Table 10 LED and Debug Interface Signals (cont'd)

| Ball No. | Name             | Pin Type | Buffer Type | Function                                                                                                                                           |

|----------|------------------|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| J1       | <b>PHYLED1_3</b> | I/O      |             | <b>GPHY LED1 for Port 3</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO29           | Prg      | Prg         | <b>General Purpose IO 29</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

|          | TCK              | I        |             | <b>JTAG Test Clock</b><br>The signals TDI, TDO, and TMS are synchronous, subject to this JTAG test clock.<br>Voltage Domain: 3.3 V                 |

|          | FW_UTXD          | O        |             | <b>Firmware UART Data Output</b><br>Firmware UART interface data output<br>Voltage Domain: 3.3 V                                                   |

| J2       | <b>PHYLED2_3</b> | I/O      |             | <b>GPHY LED2 for Port 3</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO30           | Prg      | Prg         | <b>General Purpose IO 30</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

|          | TDO              | I/O      |             | <b>JTAG Serial Test Data Output</b><br>JTAG test data output.<br>Voltage Domain: 3.3 V<br><i>Note: No external pull-up required.</i>               |

| H3       | <b>PHYLED3_3</b> | I/O      |             | <b>GPHY LED3 for Port 3</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO31           | Prg      | Prg         | <b>General Purpose IO 31</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

| J3       | <b>PHYLED1_4</b> | I/O      |             | <b>GPHY LED1 for Port 4</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO32           | Prg      | Prg         | <b>General Purpose IO 32</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

|          | FW_UTXD          | O        |             | <b>Firmware UART Data Output</b><br>Firmware UART interface data output<br>Voltage Domain: 3.3 V                                                   |

Table 10 LED and Debug Interface Signals (cont'd)

| Ball No. | Name             | Pin Type | Buffer Type | Function                                                                                                                                           |

|----------|------------------|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| K2       | <b>PHYLED2_4</b> | I/O      |             | <b>GPHY LED2 for Port 4</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO33           | Prg      | Prg         | <b>General Purpose IO 33</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

| L3       | <b>PHYLED3_4</b> | I/O      |             | <b>GPHY LED3 for Port 4</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO34           | Prg      | Prg         | <b>General Purpose IO 34</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

| M1       | <b>PHYLED1_5</b> | I/O      |             | <b>GPHY LED1 for Port 5</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO35           | Prg      | Prg         | <b>General Purpose IO 35</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

|          | FW_UTXD          | O        |             | <b>Firmware UART Data Output</b><br>Firmware UART interface data output<br>Voltage Domain: 3.3 V                                                   |

| M3       | <b>PHYLED2_5</b> | I/O      |             | <b>GPHY LED2 for Port 5</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO36           | Prg      | Prg         | <b>General Purpose IO 36</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

| L2       | <b>PHYLED3_5</b> | I/O      |             | <b>GPHY LED3 for Port 5</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO37           | Prg      | Prg         | <b>General Purpose IO 37</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

Table 10 LED and Debug Interface Signals (cont'd)

| Ball No. | Name             | Pin Type | Buffer Type | Function                                                                                                                                           |

|----------|------------------|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| M2       | <b>PHYLED1_6</b> | I/O      |             | <b>GPHY LED1 for Port 6</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO38           | Prg      | Prg         | <b>General Purpose IO 38</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

|          | FW_UTXD          | O        |             | <b>Firmware UART Data Output</b><br>Firmware UART interface data output<br>Voltage Domain: 3.3 V                                                   |

| N3       | <b>PHYLED2_6</b> | I/O      |             | <b>GPHY LED2 for Port 6</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO39           | Prg      | Prg         | <b>General Purpose IO 39</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

| N2       | <b>PHYLED3_6</b> | I/O      |             | <b>GPHY LED3 for Port 6</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO40           | Prg      | Prg         | <b>General Purpose IO 40</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

| P1       | <b>PHYLED1_7</b> | I/O      |             | <b>GPHY LED1 for Port 7</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO41           | Prg      | Prg         | <b>General Purpose IO 41</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

|          | FW_UTXD          | O        |             | <b>Firmware UART Data Output</b><br>Firmware UART interface data output<br>Voltage Domain: 3.3 V                                                   |

| P2       | <b>PHYLED2_7</b> | I/O      |             | <b>GPHY LED2 for Port 7</b><br>LED control output, drives single-color or dual color LEDs.<br>Voltage Domain: 3.3 V                                |

|          | GPIO42           | Prg      | Prg         | <b>General Purpose IO 42</b><br>Either input or output mode. The output characteristic is either open drain or push-pull.<br>Voltage Domain: 3.3 V |

## External Signals

Table 10 LED and Debug Interface Signals (cont'd)

| Ball No. | Name      | Pin Type | Buffer Type | Function                                                                                                                                                                                                          |

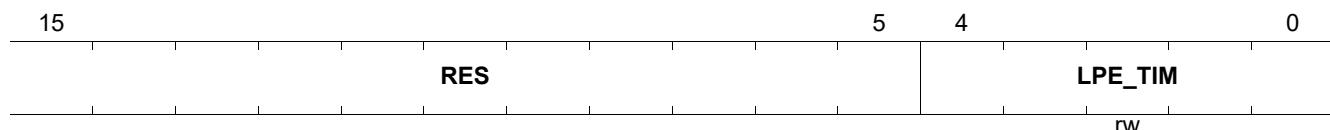

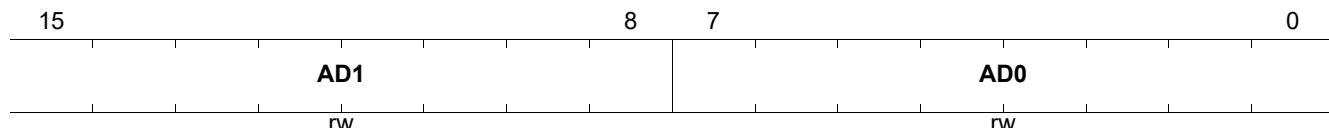

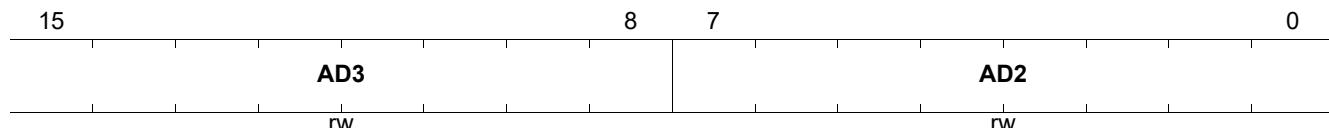

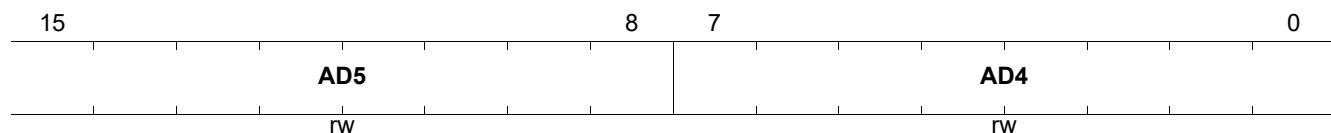

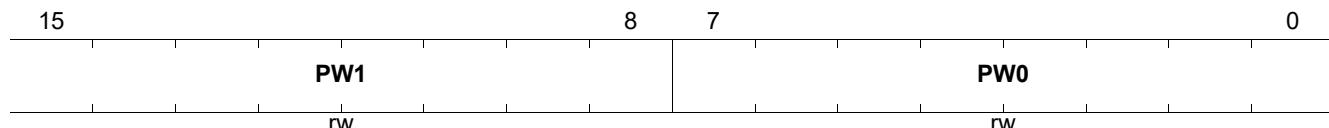

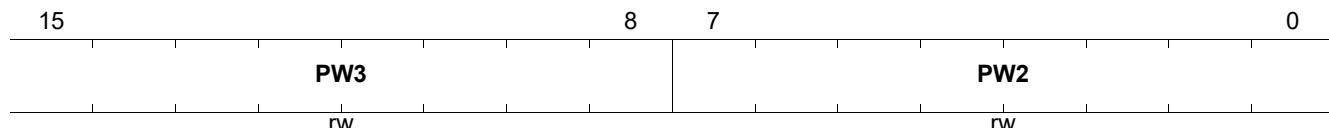

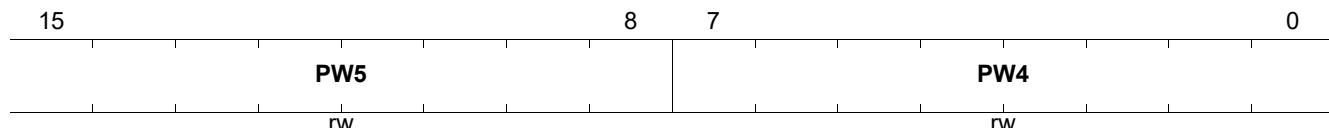

|----------|-----------|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|