# SiT6723EBB Evaluation Board User Manual

## Contents

|       |                                             |   |

|-------|---------------------------------------------|---|

| 1     | Introduction .....                          | 1 |

| 2     | I/O Descriptions .....                      | 2 |

| 3     | EVB Usage Descriptions .....                | 3 |

| 3.1   | EVB Configurations.....                     | 3 |

| 3.1.1 | I <sup>2</sup> C Support .....              | 4 |

| 3.2   | Waveform Capturing Using Active Probe ..... | 4 |

| 3.3   | Measuring Jitter and Phase Noise.....       | 5 |

| 3.4   | Current Measurement .....                   | 6 |

|       | Appendix A.....                             | 7 |

## 1 Introduction

The SiT6723EBB evaluation board (EVB) is designed for use with SiTime's Elite X<sup>TM</sup> Super-TCXOs in the 10-pin, 7.0 x 5.0 mm x mm ceramic packages and LVC MOS output type. It enables the evaluation of key functionalities of these precision Super-TCXOs in two configuration modes: TCXO and DCTCXO with I<sup>2</sup>C.

The SiT6723EBB supports 7.0 x 5.0 mm x mm package size including the following products:

| Base Part Number        | Type                  | Output frequency | Package        |

|-------------------------|-----------------------|------------------|----------------|

| <a href="#">SIT5501</a> | Super-TCXO            | 1 MHz – 60 MHz   | 7.0 x 5.0 CQFN |

| <a href="#">SIT5503</a> | Super-TCXO            | 1 MHz – 60 MHz   | 7.0 x 5.0 CQFN |

| <a href="#">SIT5541</a> | Ruggedized Super-TCXO | 1 MHz – 60 MHz   | 7.0 x 5.0 CQFN |

| <a href="#">SIT5543</a> | Ruggedized Super-TCXO | 1 MHz – 60 MHz   | 7.0 x 5.0 CQFN |

### EVB Features

- Support for two Super-TCXO configuration modes: TCXO, DCTCXO

- SMA output for direct or buffered connection to measurement equipment

- Probing points for accurate waveform measurement

- Connector access for controlling the output frequency via I<sup>2</sup>C

SiTime typically ships the EVB with the Super-TCXO mounted using SiTime recommended reflow profile. The Super-TCXO device should only be evaluated in its original soldered down state for best signal integrity and frequency stability. The device performance is not guaranteed if it is de-soldered and then re-soldered either manually or via reflow process.

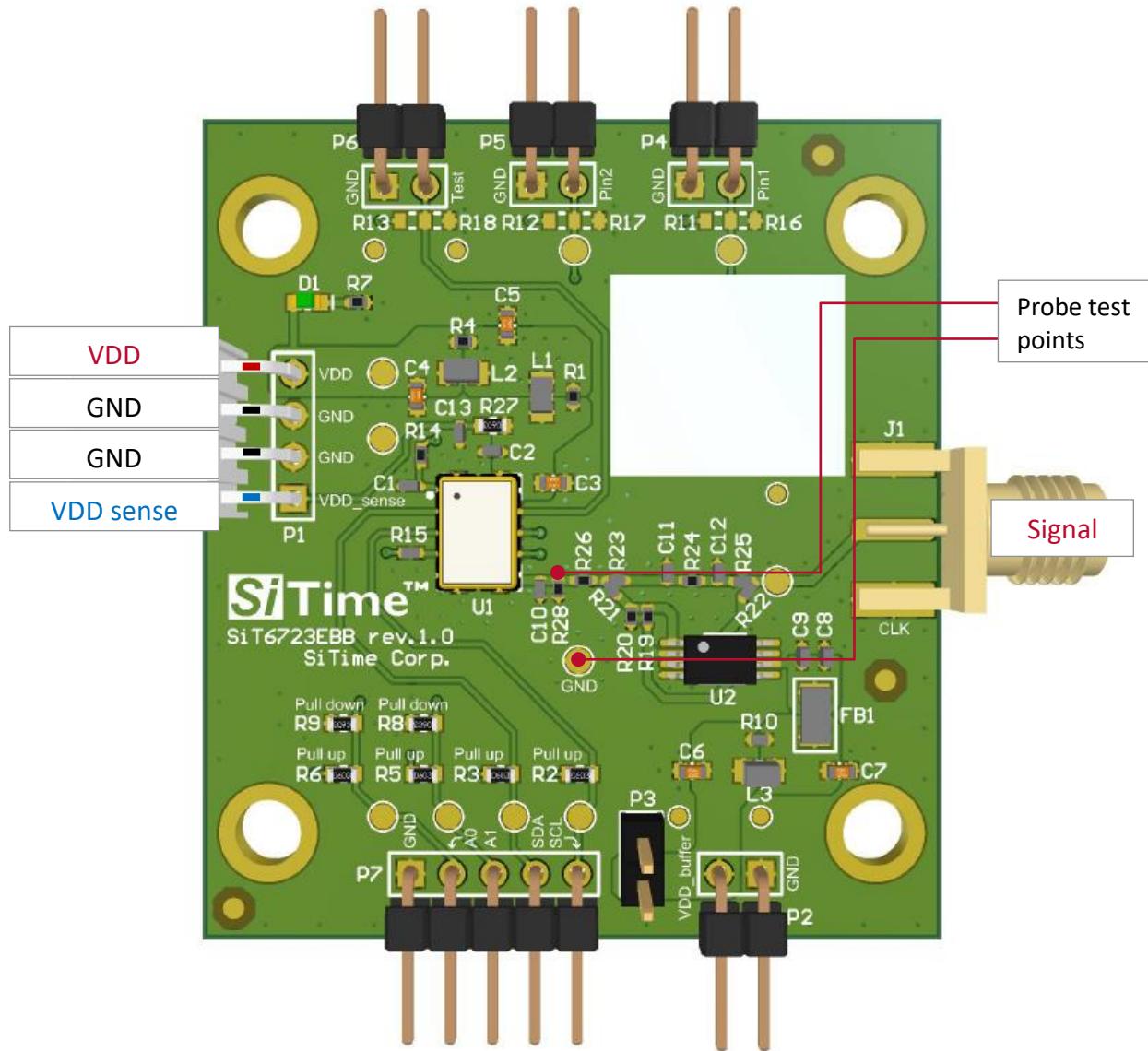

## 2 I/O Descriptions

**Table 1. SiT6723EBB I/O**

| Connector designator | I/O                                         | Description                                                                                                                                                                                                                                                                                                                                                             |

|----------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1                   | <b>Power Supply and Sense</b>               | Four-pin connector for DC power supply and power sensing.<br><b>VDD is connected to Pin 1, GND – to Pin2 of P1.</b><br><b>VDD sense is connected to Pin 4, GND – to Pin3 of P1.</b>                                                                                                                                                                                     |

| P2                   | <b>Buffer power</b>                         | Two-pin connector for DC buffer power supply.                                                                                                                                                                                                                                                                                                                           |

| P3                   | <b>Buffer power supply jumper</b>           | A two-pin header (P3) provides access to using a jumper for buffer power supply configuration: <ul style="list-style-type: none"> <li>Without jumper (default shipment configuration) buffer is powered by the P2 connector.</li> <li>With jumper buffer is powered by the DUT power supply P1 connector (not recommended for best phase noise measurement).</li> </ul> |

| P4                   | <b>Pin 1 access</b>                         | A two-pin header (P4) provides access to the pin 1 of the Super- TCXO in OE mode. In OE mode, pin 1 can be left floating as there is an internal pull-up resistor.                                                                                                                                                                                                      |

| P5, P6               | <b>Service connectors</b>                   | P5, P6 are reserved for SiTime internal use only.                                                                                                                                                                                                                                                                                                                       |

| P7                   | <b>Frequency control via I<sup>2</sup>C</b> | A five-pin header (P7) provides access to I <sup>2</sup> C (SDA, SCL, A0, A1).                                                                                                                                                                                                                                                                                          |

| J1                   | <b>Output</b>                               | Oscillator output can be accessed either using active probe or SMA connector. The test points for active probe are placed closely to the oscillator output for better signal integrity (see <a href="#">Figure A2</a> ). Section 3.2 describes in details the recommended measurement configurations.                                                                   |

## 3 EVB Usage Descriptions

### 3.1 EVB Configurations

SiT6723EBB can be configured to support two Super-TCXO configuration modes including TCXO with output enable (OE) and DCTCXO with I<sup>2</sup>C.

Oscillator output waveform can be measured with an active probe in all configurations. The value of the load capacitor C10 can be adjusted to match the load conditions in the target application. This enables the user to measure waveform characteristics under similar conditions as close to those on the target board as possible.

Oscillator output can be accessed in several ways listed in Table 1. Table 2 describes components configuration to support all output configurations.

**Table 2. Components configuration to support all output configurations**

| Output configuration                 | C10    | R28  | R26            | R21 | R19 | R20 | R23            | C11 | R24 | C12 | R25 | R22 |

|--------------------------------------|--------|------|----------------|-----|-----|-----|----------------|-----|-----|-----|-----|-----|

| Direct                               | DNP    | DNP  | 0.1 uF/<br>0 Ω | DNP | DNP | DNP | 0 Ω            | DNP | 0 Ω | DNP | 0 Ω | DNP |

| Direct + LVCMOS-to-sinewave filter** | DNP    | DNP  | Contact SiTime | DNP | DNP | DNP | Contact SiTime |     |     |     | DNP |     |

| Buffered output                      | DNP    | DNP  | 0 Ω            | 0 Ω | DNP | DNP | DNP            | DNP | DNP | DNP | DNP | 0 Ω |

| Probe                                | 15 pF* | DNP* | DNP            | DNP | DNP | DNP | DNP            | DNP | DNP | DNP | DNP | DNP |

\* The value of the load capacitor C10 and load resistor R28 can be adjusted to match the load conditions in the target application. This enables the user to measure waveform characteristics under similar conditions as close to those on the target board as possible.

\*\* LVCMOS-to-sinewave filter components values will depend on the carrier frequency of the device. Contact SiTime to get recommended nominals for filter components.

The test points for active probe are placed closely to the oscillator output for better signal integrity (see Figure A2).

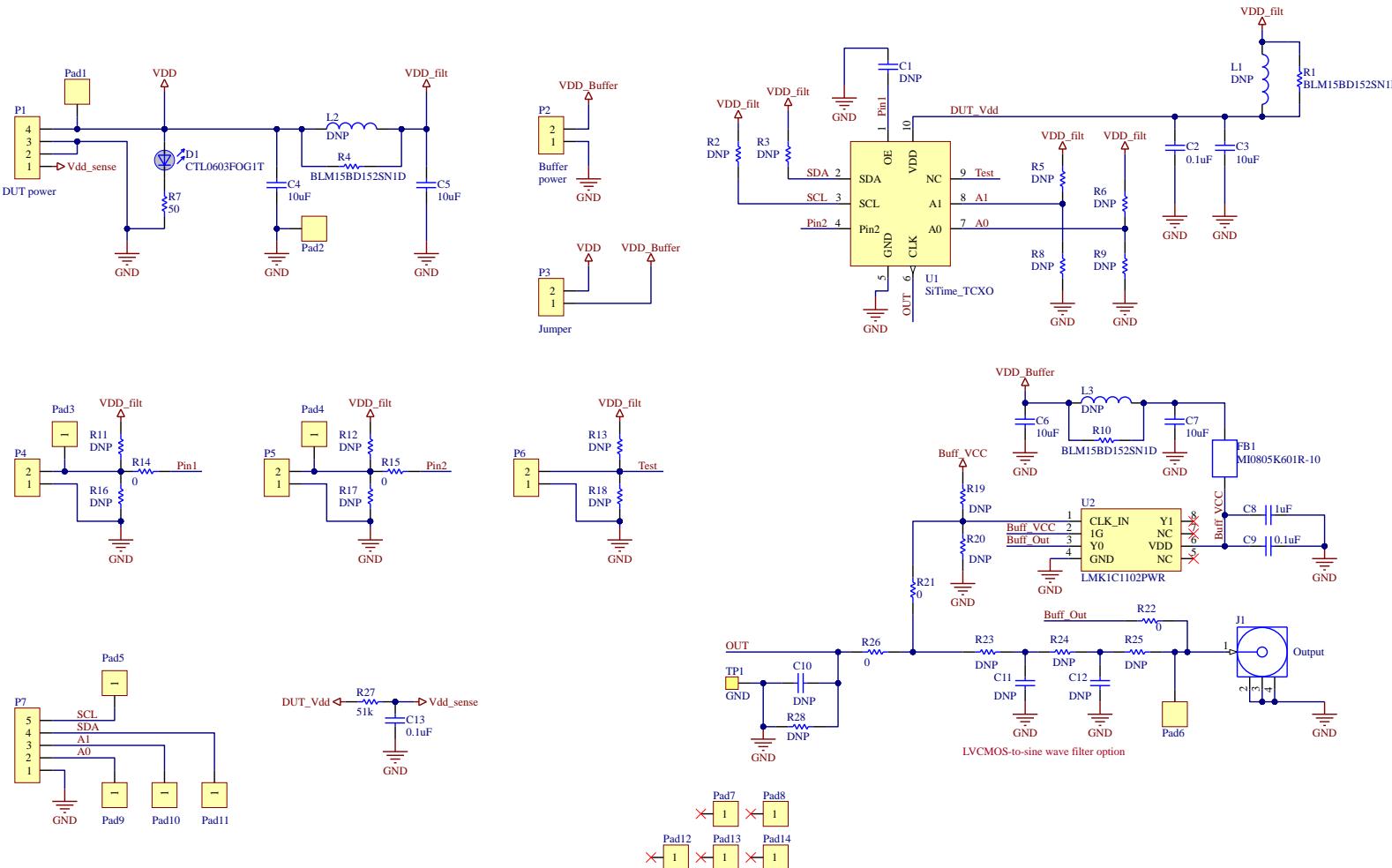

[Figure A1 in Appendix A](#) shows the complete electrical schematic of SiT6723EBB. Components labeled “DNP” are not assembled.

### Shipment Configuration

SiT6723EBB is shipped configured for buffered output allowing connecting it to the instrument input using 50 Ω coax cable. Details on the board assembly for shipment configuration can be found on the schematic (see [Figure A1 in Appendix A](#)).

### 3.1.1 I<sup>2</sup>C Support

The two pull up resistors (R2 and R3 with 4.7 kΩ value) can be assembled to support the I<sup>2</sup>C configuration (in case I<sup>2</sup>C master does not have it). If requested, the EVB will ship with these resistors.

## 3.2 Waveform Capturing Using Active Probe

SiTime Elite X™ Super-TCXO is a high-speed logic output device. It is critical that the proper logic and high frequency measurement techniques are used along with the high-quality active probe to ensure best measurement results.

SiTime recommends the following minimum equipment for proper clock waveform measurement

- 1) 4 GHz or higher active probe with capacitance <1 pF, such as a Keysight 1134B;

- 2) Oscilloscope with 4 GHz bandwidth or higher such as a Keysight DSA90604A.

A passive voltage probe should not be used as it adds a high capacitive load to the part and the long ground lead clip is not suitable for high frequency measurement applications. The inductance of the long ground lead coupled with the input capacitance of the probe results in a resonant circuit. The consequence of this resonance results in the distortion of the clock signal. Typical manifestations of this distortion include ringing, overshoot, and undershoot of the clock signal.

Eliminating such distortion requires a probe with the lowest input capacitance and a low inductance ground lead. In addition, SiTime TCXOs are typically configured for fast rise and fall times with 15 pF load. It is therefore critical that the probe tip ground be as short as possible, lowest inductance, and the return path for the ground be located as close as possible to the trace carrying the RF logic signal.

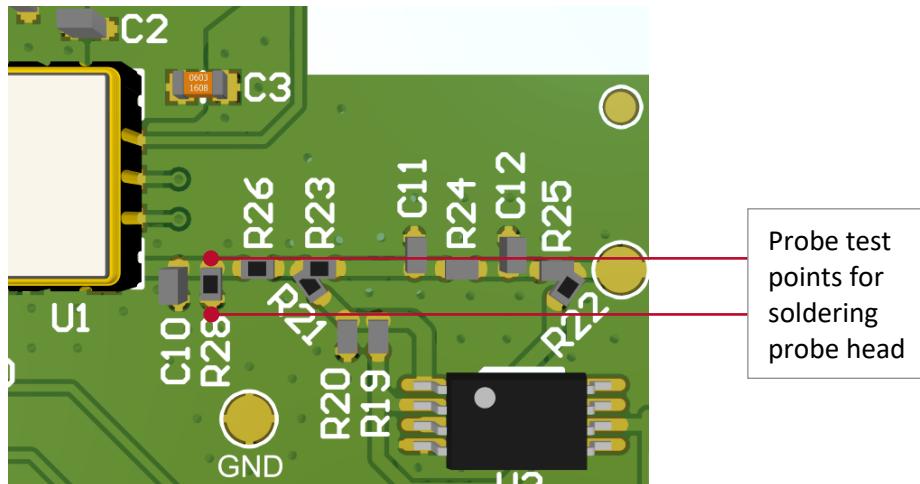

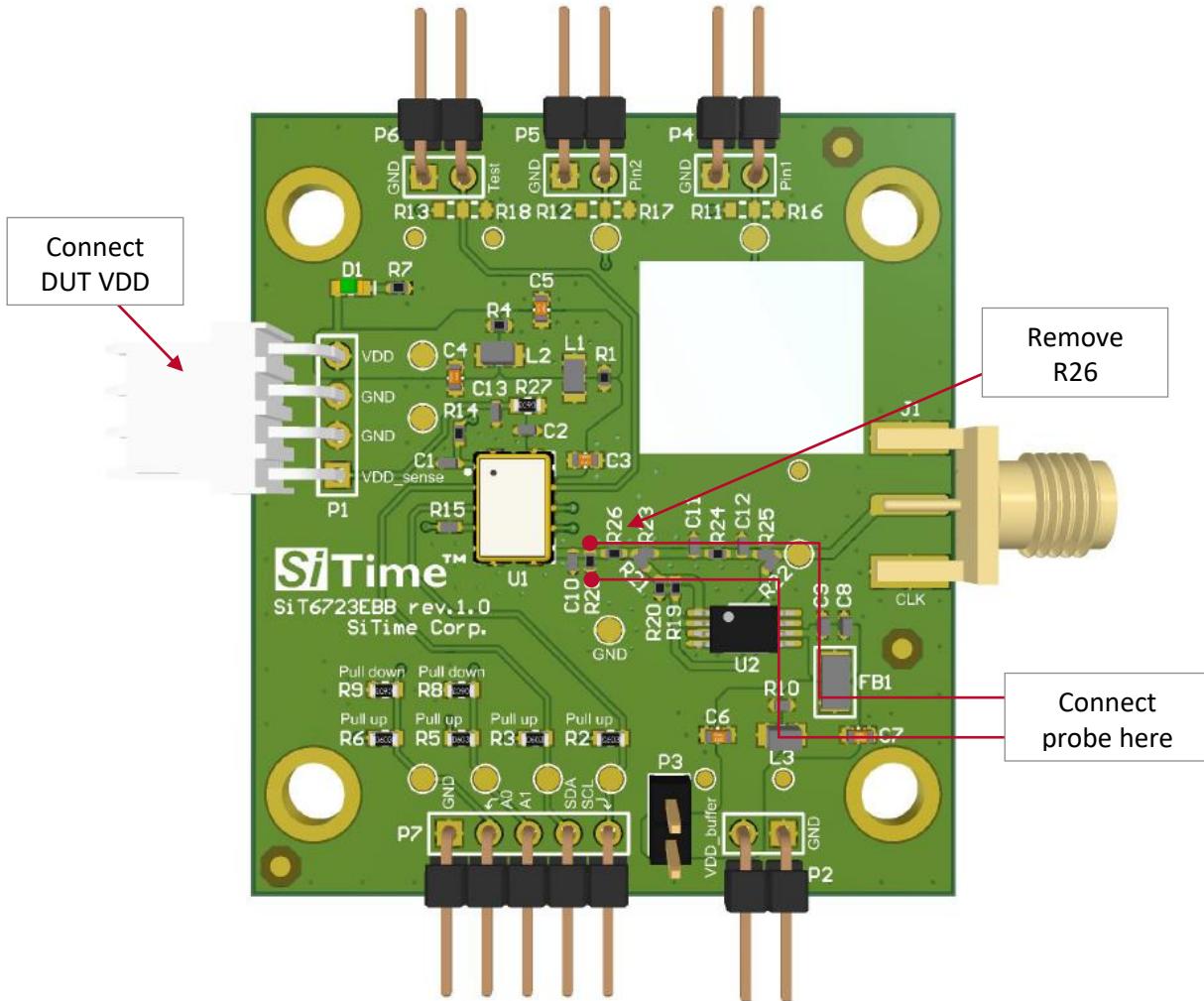

For waveform measurement, it's recommended to remove resistor R26. Please refer to Figure A2 for test point locations on the SiT6723EBB. If the soldering probe is used, it is recommended to use R28 resistor pads or solder it over it if necessary (Figure 1).

Figure 1: Recommended points for soldering probe head

More details on the SiTime recommendations on the oscillator's output probing can be found in [AN10028](#).

Figure 2: Signal measurement using probe

### 3.3 Measuring Jitter and Phase Noise

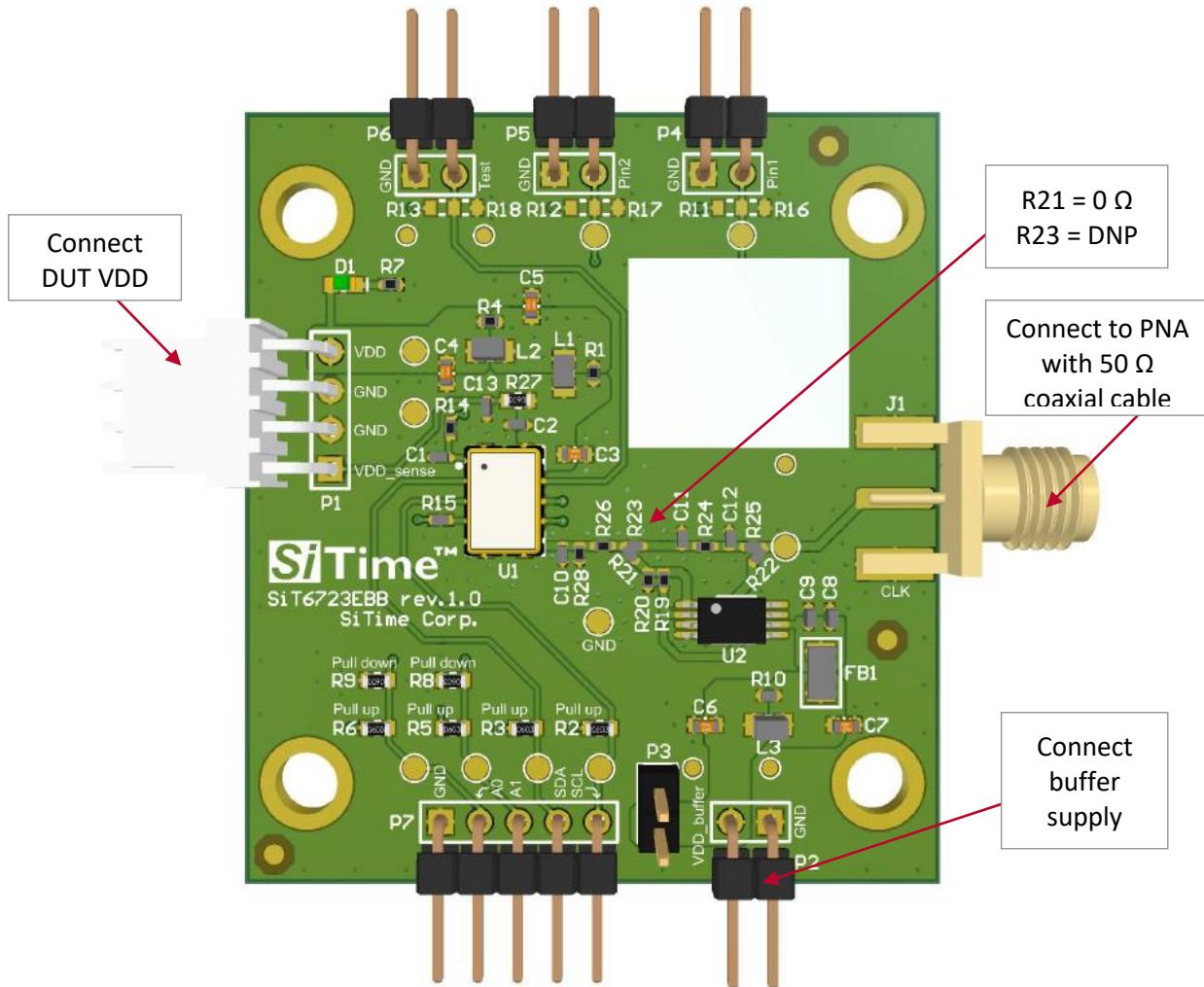

For jitter and phase noise measurements, buffered output configuration is recommended. SiTime TCXO was not designed to drive  $50\ \Omega$  load directly so buffer avoids excessive current draw from the device output. For minimal impact on the measurement LMK1C1102 low-additive jitter buffer is used on the board.

SMA connector is used to connect directly to the jitter measurement instrument, such as Time Interval Analyzer (TIA) or high-bandwidth real-time oscilloscope. Jitter measurement technique is described in SiTime [AN10007](#).

The SMA can also be connected through  $50\ \Omega$  coaxial cable to signal source analyzers or spectrum analyzers to measure phase noise. In such case the use of AC-coupling configuration is recommended because not all measurement instruments can accept DC voltage at their inputs.

**Note:** It is highly recommended to use separate supply for the LMK1C1102 buffer for best phase noise and jitter measurement to avoid negative impact on TCXO supply from high-speed, high magnitude current draw of buffer into the  $50\ \Omega$  load.

Figure 3: Phase noise measurement using buffer

### 3.4 Current Measurement

To measure the current consumption, user need to use ammeter/multi-meter in the power supply circuit. We recommend removing diode D1 to avoid measuring the additional current of the diode circuit. It is recommended to measure the voltage on DUT VDD and adjust for any drop on the DMM to ensure known VDD voltage on the device. VDD adjustment must be completed before every current measurement.

## Appendix A

Figure A1: SiT6723EBB electrical schematics

**Table A1: Bill of Materials (BOM)**

| #  | Reference Designators                                | Description   | Qty | SMD component size | Value            |

|----|------------------------------------------------------|---------------|-----|--------------------|------------------|

| 1  | C1, C10, C11, C12                                    | Capacitors    | 4   | 0402               | DNP              |

| 2  | C2, C9, C13                                          | Capacitors    | 3   | 0402               | 0.1 uF           |

| 3  | C3, C4, C5, C6, C7                                   | Capacitors    | 5   | 0603               | 10 uF            |

| 4  | C8                                                   | Capacitor     | 1   | 0402               | 1 uF             |

| 5  | D1                                                   | LED           | 1   | 0603               | Green            |

| 6  | FB1                                                  | Ferrite bead  | 1   | 0805               | 600 Ω @ 100 MHz  |

| 7  | L1, L2, L3                                           | Inductance    | 3   | 0805               | DNP              |

| 8  | R1, R4, R10                                          | Ferrite Beads | 3   | 0402               | 1.5 kΩ @ 100 MHz |

| 9  | R2, R3, R5, R6, R8, R9, R11, R12, R13, R16, R17, R18 | Resistors     | 12  | 0603               | DNP              |

| 10 | R7                                                   | Resistor      | 1   | 0402               | 50 Ω             |

| 11 | R14, R15, R21, R22, R26                              | Resistors     | 5   | 0402               | 0 Ω              |

| 12 | R19, R20, R23, R24, R25, R28                         | Resistors     | 6   | 0402               | DNP              |

| 13 | R27                                                  | Resistor      | 1   | 0603               | 51 kΩ            |

| 14 | U2                                                   | Buffer        | 1   | TSSOP8-TI          | LMK1C1102        |

| 15 | P1                                                   | 4-pin header  | 1   | -                  | -                |

| 16 | P2, P3, P4, P5, P6                                   | 2-pin headers | 5   | -                  | -                |

| 17 | P7                                                   | 5-pin header  | 1   | -                  | -                |

| 18 | J1                                                   | SMA connector | 1   | -                  | -                |

**Table A2: Connectors Digi-Key Part Number**

| Connectors                        | Digi-Key part number | Digi-Key part number for mating connector | Digi-Key part number for associated products |

|-----------------------------------|----------------------|-------------------------------------------|----------------------------------------------|

| <b>Power/Power adjust</b>         | WM10299-ND           | WM2002-ND                                 | WM1114TR-ND                                  |

| <b>Buffer power</b>               | WM10297-ND           | WM2011-ND                                 | -                                            |

| <b>Buffer power supply jumper</b> | Z5275-ND             | -                                         | S9342-ND                                     |

| <b>Frequency control via I2C</b>  | 2057-PH1RB-05-UA-ND  | -                                         | -                                            |

Figure A2: SiT6723EBB layout

**Table 3: Revision History**

| Version | Release Date | Change Summary                             |

|---------|--------------|--------------------------------------------|

| 1.0     | 14-Sep-2023  | Original doc                               |

| 1.1     | 29-Jul-2024  | Updated power filters on schematic and BOM |

**SiTime Corporation**, 5451 Patrick Henry Drive, Santa Clara, CA 95054, USA | **Phone:** +1-408-328-4400 | **Fax:** +1-408-328-4439

© SiTime Corporation, January 2025. The information contained herein is subject to change at any time without notice. SiTime assumes no responsibility or liability for any loss, damage or defect of a Product which is caused in whole or in part by (i) use of any circuitry other than circuitry embodied in a SiTime product, (ii) misuse or abuse including static discharge, neglect or accident, (iii) unauthorized modification or repairs which have been soldered or altered during assembly and are not capable of being tested by SiTime under its normal test conditions, or (iv) improper installation, storage, handling, warehousing or transportation, or (v) being subjected to unusual physical, thermal, or electrical stress.

**Disclaimer:** SiTime makes no warranty of any kind, express or implied, with regard to this material, and specifically disclaims any and all express or implied warranties, either in fact or by operation of law, statutory or otherwise, including the implied warranties of merchantability and fitness for use or a particular purpose, and any implied warranty arising from course of dealing or usage of trade, as well as any common-law duties relating to accuracy or lack of negligence, with respect to this material, any SiTime product and any product documentation. Products sold by SiTime are not suitable or intended to be used in a life support application or component, to operate nuclear facilities, or in other mission critical applications where human life may be involved or at stake. All sales are made conditioned upon compliance with the critical uses policy set forth below.

**CRITICAL USE EXCLUSION POLICY**

BUYER AGREES NOT TO USE SITIME'S PRODUCTS FOR ANY APPLICATION OR IN ANY COMPONENTS USED IN LIFE SUPPORT DEVICES OR TO OPERATE NUCLEAR FACILITIES OR FOR USE IN OTHER MISSION-CRITICAL APPLICATIONS OR COMPONENTS WHERE HUMAN LIFE OR PROPERTY MAY BE AT STAKE.

SiTime owns all rights, title and interest to the intellectual property related to SiTime's products, including any software, firmware, copyright, patent, or trademark. The sale of SiTime products does not convey or imply any license under patent or other rights. SiTime retains the copyright and trademark rights in all documents, catalogs and plans supplied pursuant to or ancillary to the sale of products or services by SiTime. Unless otherwise agreed to in writing by SiTime, any reproduction, modification, translation, compilation, or representation of this material shall be strictly prohibited.