**IS25LP064D**

**IS25WP064D**

**64Mb**

**SERIAL FLASH MEMORY WITH 166MHZ MULTI I/O SPI &

QUAD I/O QPI DTR INTERFACE**

**DATA SHEET**

## 64Mb

### SERIAL FLASH MEMORY WITH 166MHZ MULTI I/O SPI & QUAD I/O QPI DTR INTERFACE

## FEATURES

### • Industry Standard Serial Interface

- IS25LP064D: 64Mbit/8Mbyte

- IS25WP064D: 64Mbit/8Mbyte

- Supports Standard SPI, Fast, Dual, Dual I/O, Quad, Quad I/O, SPI DTR, Dual I/O DTR, Quad I/O DTR, and QPI

- Software & Hardware Reset

- Supports Serial Flash Discoverable Parameters (SFDP)

### • High Performance Serial Flash (SPI)

- 80MHz Normal Read

- Up to 166Mhz Fast Read

- Up to 80MHz DTR (Dual Transfer Rate)

- Equivalent Throughput of 664 Mb/s

- Selectable Dummy Cycles

- Configurable Drive Strength

- Supports SPI Modes 0 and 3

- More than 100,000 Erase/Program Cycles

- More than 20-year Data Retention

### • Flexible & Efficient Memory Architecture

- Chip Erase with Uniform Sector/Block Erase (4/32/64 Kbyte)

- Program 1 to 256 Byte per Page

- Program/Erase Suspend & Resume

### • Efficient Read and Program modes

- Low Instruction Overhead Operations

- Continuous Read 8/16/32/64 Byte Burst Wrap

- Selectable Burst Length

- QPI for Reduced Instruction Overhead

- AutoBoot Operation

### • Low Power with Wide Temp. Ranges

- Single Voltage Supply

IS25LP: 2.30V to 3.60V

IS25WP: 1.65V to 1.95V

- 10 mA Active Read Current

- 8 µA Standby Current

- 1 µA Deep Power Down

- Temp Grades:

Extended: -40°C to +105°C

Auto Grade (A3) : -40°C to +125°C

### • Advanced Security Protection

- Software and Hardware Write Protection

- Advanced Sector/Block Protection

- Top/Bottom Block Protection

- Power Supply Lock Protection

- 4x256 Byte Dedicated Security Area with OTP User-lockable Bits

- 128 bit Unique ID for Each Device (Call Factory)

### • Industry Standard Pin-out & Packages<sup>(1)</sup>

- M = 16-pin SOIC 300mil

- B = 8-pin SOIC 208mil

- E = 8-contact XSON 4x4mm

- K = 8-contact WSON 6x5mm

- L = 8-contact WSON 8x6mm

- J = 8-contact WSON 8x6mm <sup>(2)</sup>

- G = 24-ball TFBGA (4x6 ball array)

- H = 24-ball TFBGA (5x5 ball array)

- W = KGD (Call Factory)

- Green Package (RoHS Compliant, Halogen-Free) and TSCA Compliant

#### Notes:

1. Call Factory for other package options available.

2. Exposed Pad Size = 3.4mmx4.3mm instead of 4.7mmx4.7mm

## GENERAL DESCRIPTION

The IS25LP064D and IS25WP064D Serial Flash memory offers a versatile storage solution with high flexibility and performance in a simplified pin count package. ISSI's "Industry Standard Serial Interface" Flash is for systems that require limited space, a low pin count, and low power consumption. The device is accessed through a 4-wire SPI Interface consisting of a Serial Data Input (SI), Serial Data Output (SO), Serial Clock (SCK), and Chip Enable (CE#) pins, which can also be configured to serve as multi-I/O (see pin descriptions).

The device supports Dual and Quad I/O as well as standard, Dual Output, and Quad Output SPI. Clock frequencies of up to 166MHz allow for equivalent clock rates of up to 664MHz (166MHz x 4) which equates to 83Mbytes/s of data throughput. The IS25xP series of Flash adds support for DTR (Double Transfer Rate) commands that transfer addresses and read data on both edges of the clock. These transfer rates can outperform 16-bit Parallel Flash memories allowing for efficient memory access to support XIP (execute in place) operation.

Initial state of the memory array is erased (all bits are set to 1) when shipped from the factory.

QPI (Quad Peripheral Interface) supports 2-cycle instruction further reducing instruction times. Pages can be erased in groups of 4Kbyte sectors, 32Kbyte blocks, 64Kbyte blocks, and/or the entire chip. The uniform sector and block architecture allows for a high degree of flexibility so that the device can be utilized for a broad variety of applications requiring solid data retention.

### Supply Voltage & Temperature Range vs. Maximum Speed

|                    | Voltage & Temp.   | Speed                 |

|--------------------|-------------------|-----------------------|

| IS25LP (3.0V typ.) | 2.30~3.6V, 125°C  | 133MHz                |

|                    | 2.70~3.6V, 125°C  | 166MHz                |

| IS25WP (1.8V typ.) | 1.65~1.95V, 125°C | 133MHz                |

|                    | 1.70~1.95V, 105°C | 166MHz <sup>(1)</sup> |

Note:

1. Values are guaranteed by characterization and not 100% tested in production.

**TABLE OF CONTENTS**

|                                                                   |    |

|-------------------------------------------------------------------|----|

| FEATURES .....                                                    | 2  |

| GENERAL DESCRIPTION .....                                         | 3  |

| TABLE OF CONTENTS .....                                           | 4  |

| 1. PIN CONFIGURATION .....                                        | 7  |

| 2. PIN DESCRIPTIONS .....                                         | 9  |

| 3. BLOCK DIAGRAM .....                                            | 11 |

| 4. SPI MODES DESCRIPTION .....                                    | 12 |

| 5. SYSTEM CONFIGURATION .....                                     | 14 |

| 5.1 BLOCK/SECTOR ADDRESSES .....                                  | 14 |

| 5.2 Serial Flash Discoverable Parameters .....                    | 15 |

| 6. REGISTERS .....                                                | 20 |

| 6.1 STATUS REGISTER .....                                         | 20 |

| 6.2 FUNCTION REGISTER .....                                       | 25 |

| 6.3 READ REGISTER .....                                           | 26 |

| 6.4 EXTENDED READ REGISTER .....                                  | 29 |

| 6.5 AUTOBOOT REGISTER .....                                       | 31 |

| 6.6 ADVANCED SECTOR/BLOCK PROTECTION (ASP) RELATED REGISTER ..... | 32 |

| 6.6.1 ADVANCED SECTOR/BLOCK PROTECTION REGISTER (ASPR) .....      | 32 |

| 6.6.2 PASSWORD REGISTER .....                                     | 33 |

| 6.6.3 PPB LOCK REGISTER .....                                     | 33 |

| 6.6.4 PPB REGISTER .....                                          | 34 |

| 6.6.5 DYB REGISTER .....                                          | 34 |

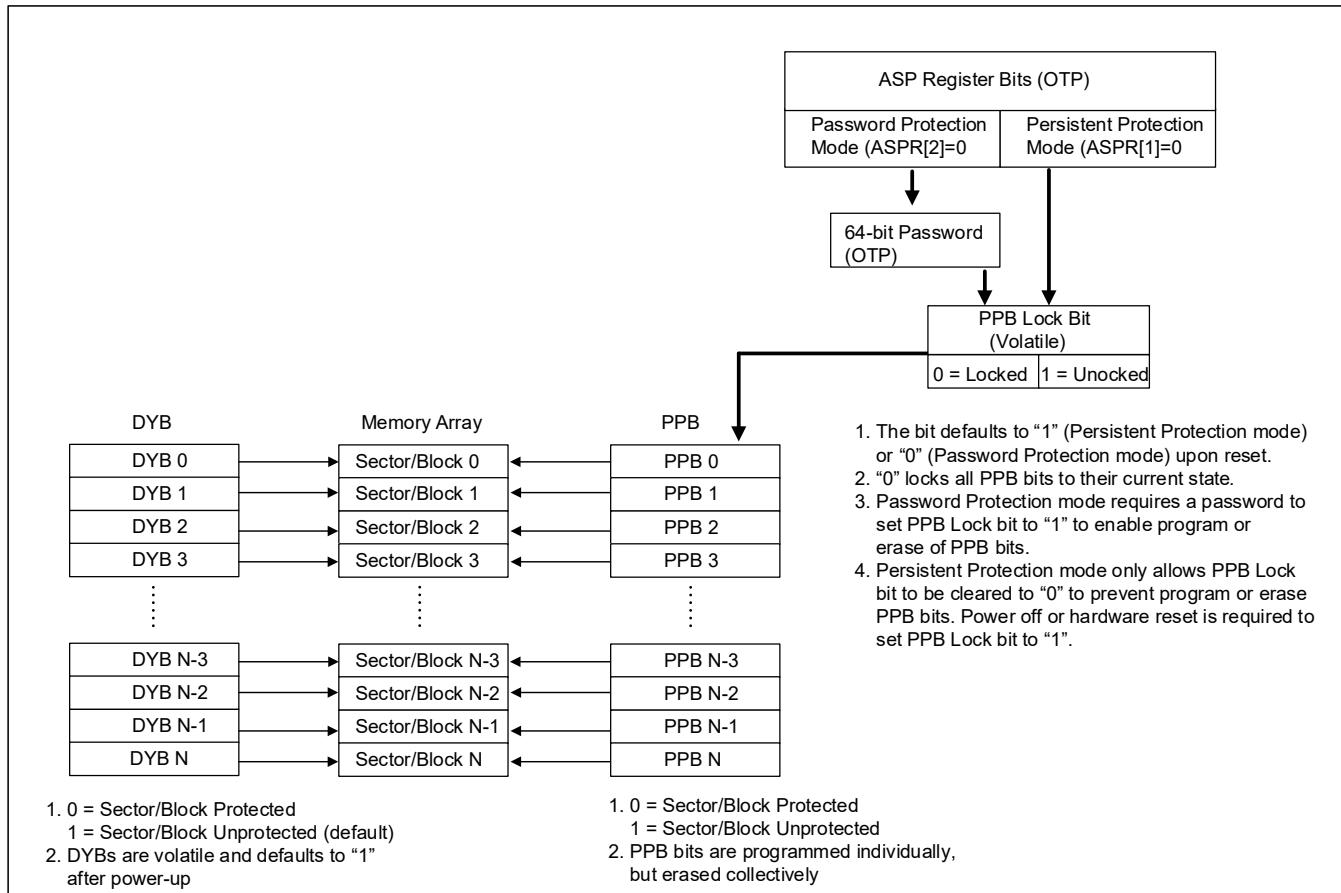

| 7. PROTECTION MODE .....                                          | 35 |

| 7.1 HARDWARE WRITE PROTECTION .....                               | 35 |

| 7.2 SOFTWARE WRITE PROTECTION .....                               | 35 |

| 7.2.1 BLOCK PROTECTION BITS .....                                 | 35 |

| 7.2.2 ADVANCED SECTOR/BLOCK PROTECTION (ASP) .....                | 36 |

| 8. DEVICE OPERATION .....                                         | 43 |

| 8.1 COMMAND OVERVIEW .....                                        | 43 |

| 8.2 COMMAND SET SUMMARY .....                                     | 44 |

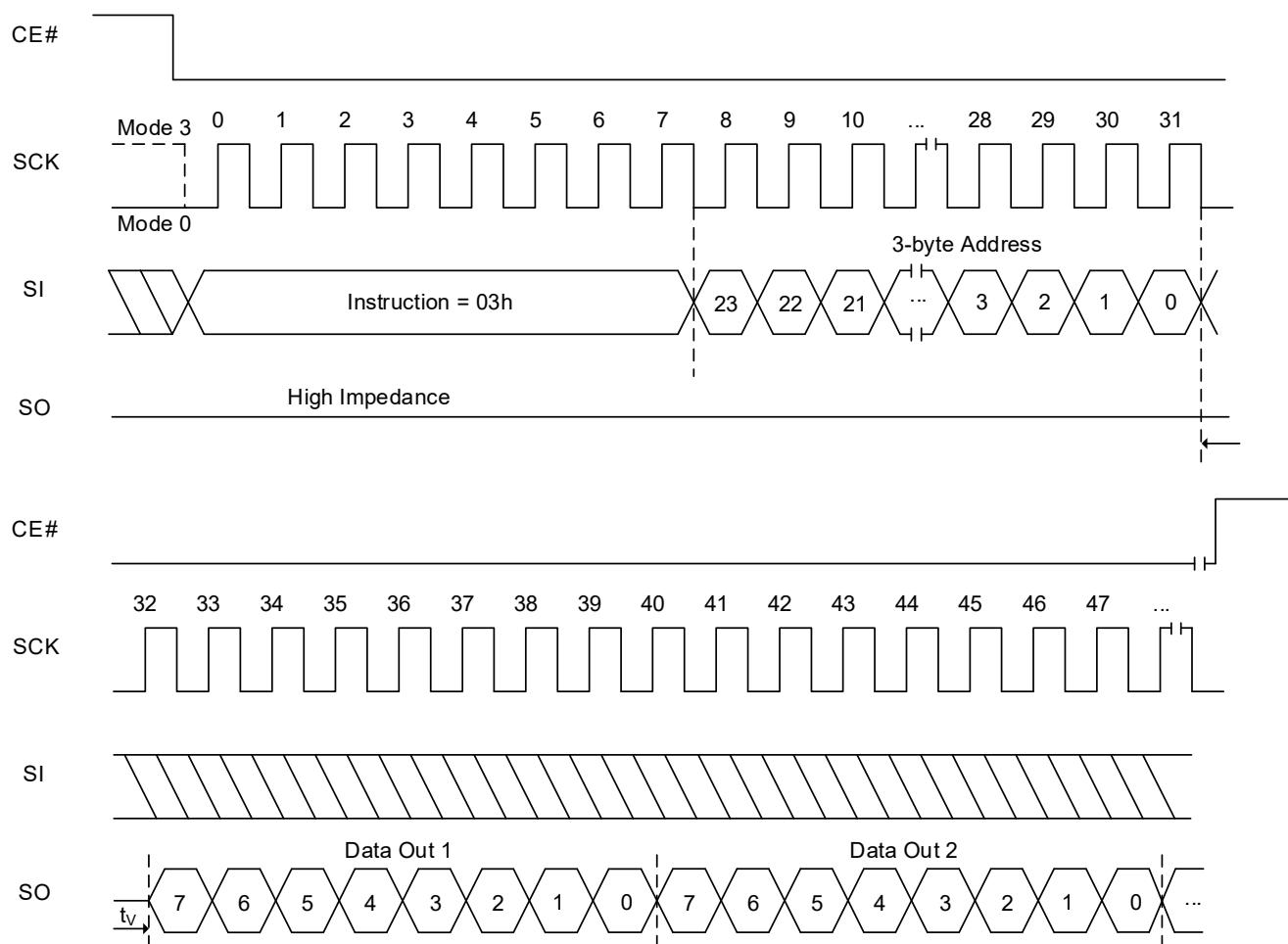

| 8.3 NORMAL READ OPERATION (NORD, 03h) .....                       | 48 |

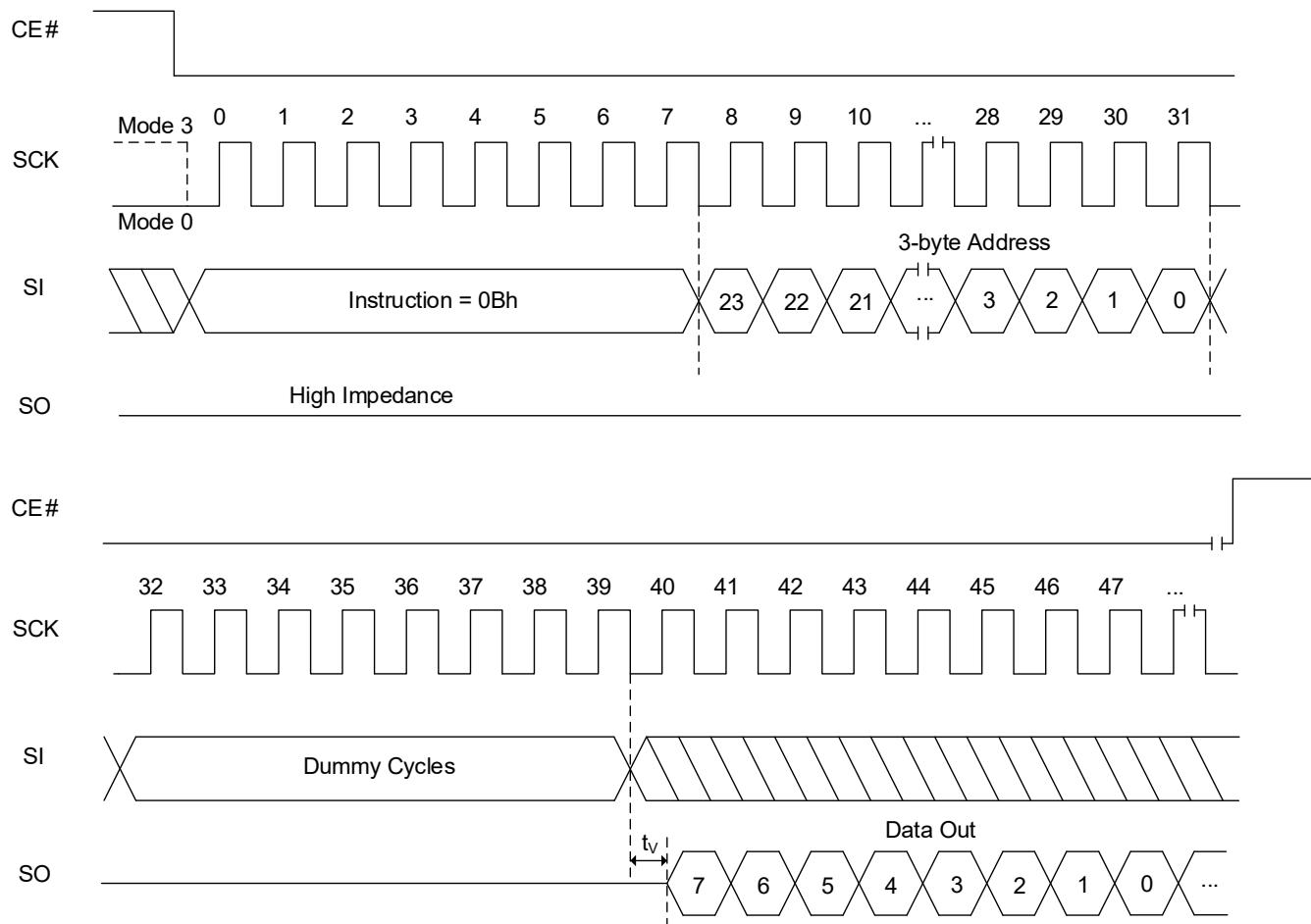

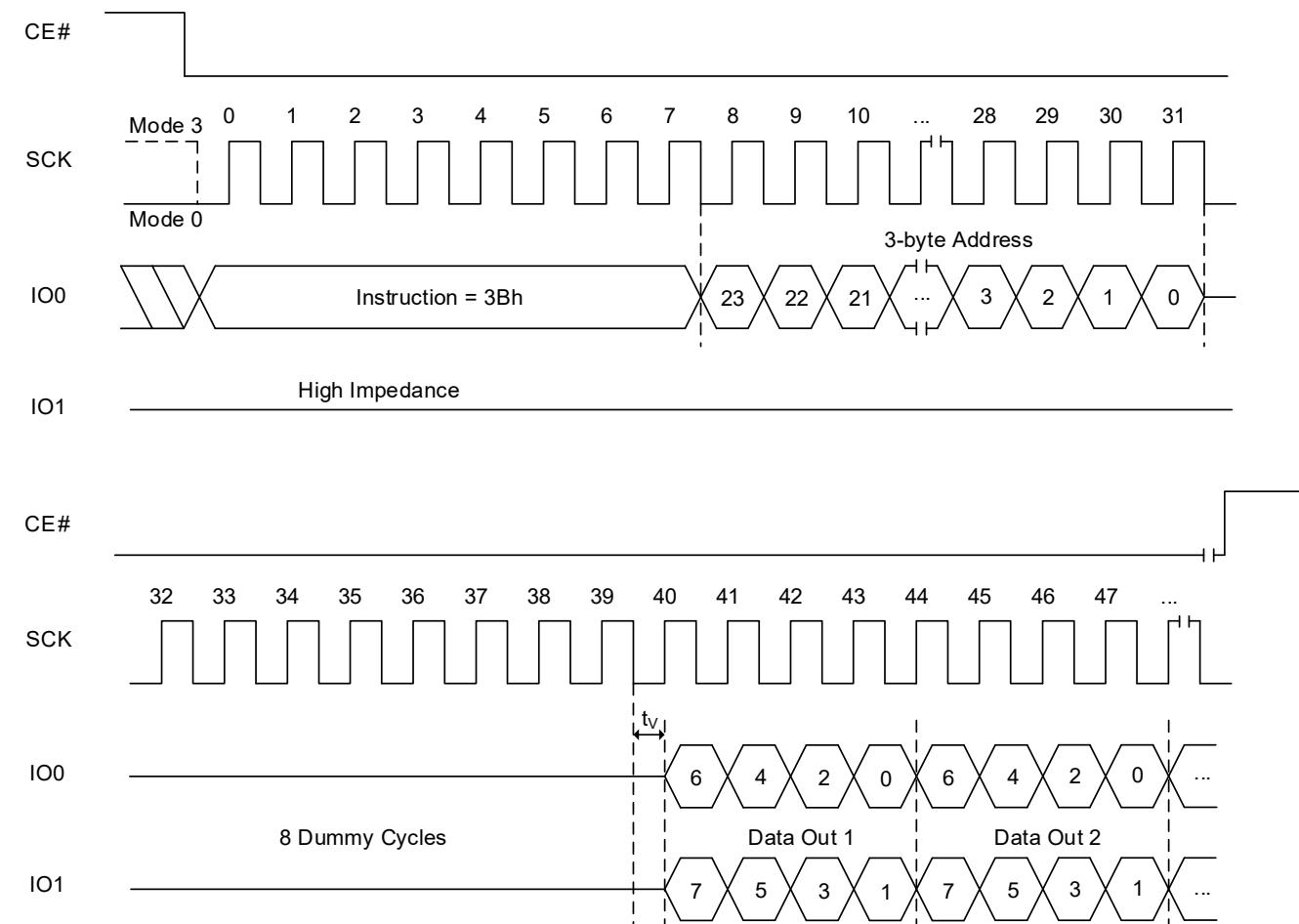

| 8.4 FAST READ OPERATION (FRD, 0Bh) .....                          | 49 |

| 8.5 HOLD OPERATION .....                                          | 51 |

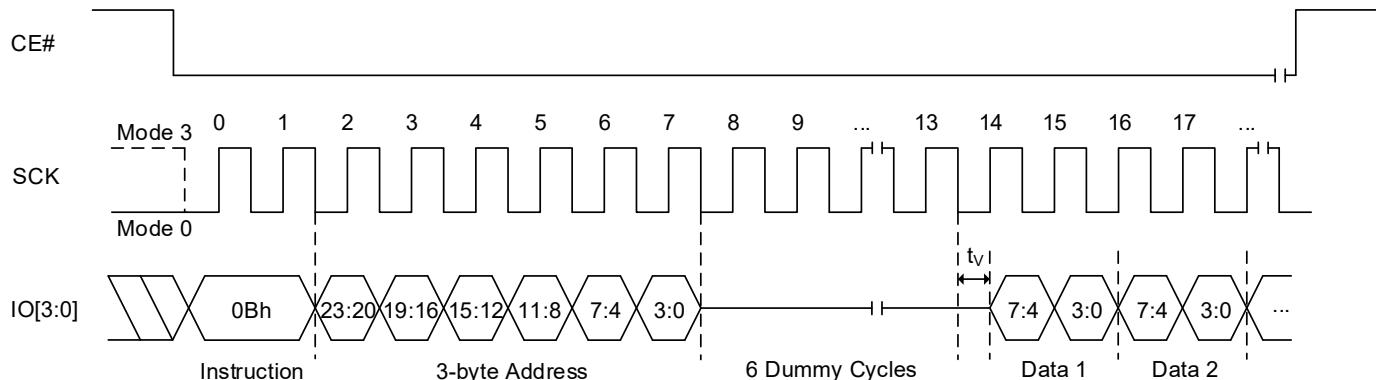

| 8.6 FAST READ DUAL I/O OPERATION (FRDIO, BBh) .....               | 52 |

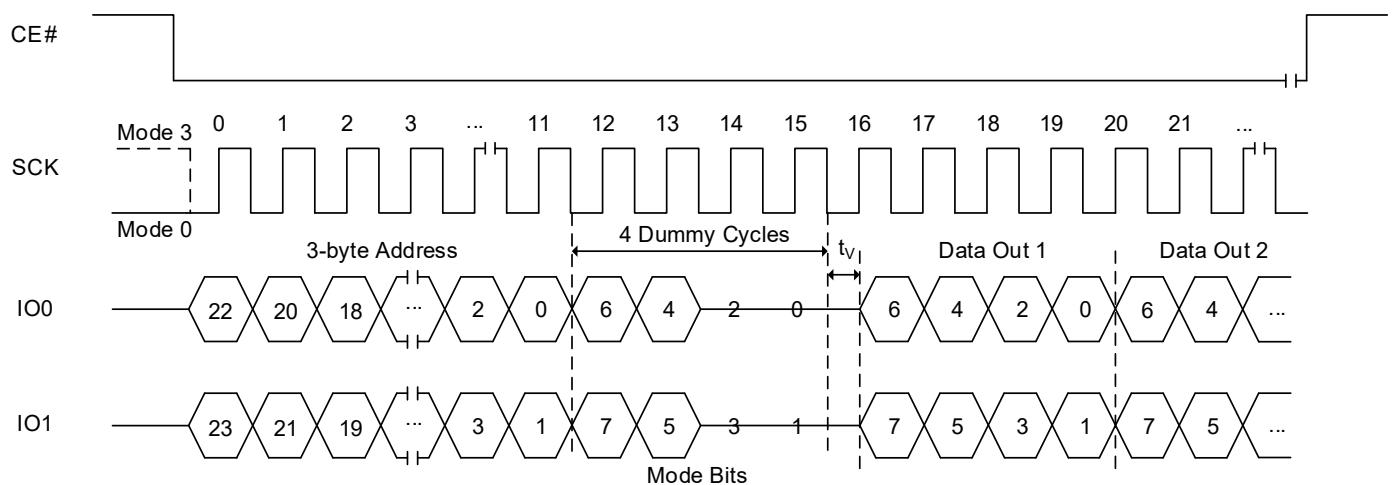

| 8.7 FAST READ DUAL OUTPUT OPERATION (FRDO, 3Bh) .....             | 55 |

| 8.8 FAST READ QUAD OUTPUT OPERATION (FRQO) .....                  | 56 |

| 8.9 FAST READ QUAD I/O OPERATION (FRQIO, EBh) .....               | 58 |

| 8.10 PAGE PROGRAM OPERATION (PP, 02h) .....                       | 61 |

|                                                                                              |     |

|----------------------------------------------------------------------------------------------|-----|

| 8.11 QUAD INPUT PAGE PROGRAM OPERATION (PPQ, 32h/38h) .....                                  | 62  |

| 8.12 ERASE OPERATION .....                                                                   | 63  |

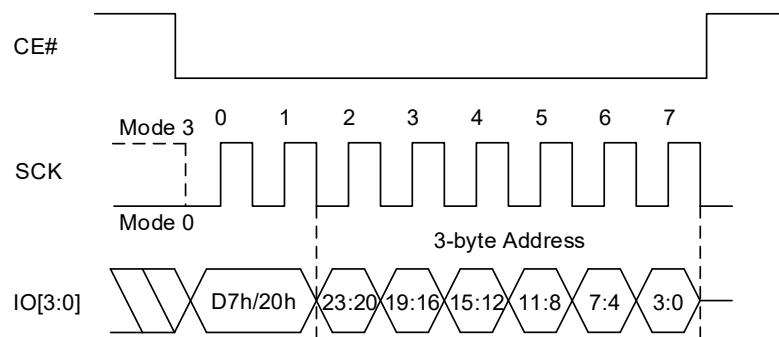

| 8.13 SECTOR ERASE OPERATION (SER, D7h/20h) .....                                             | 64  |

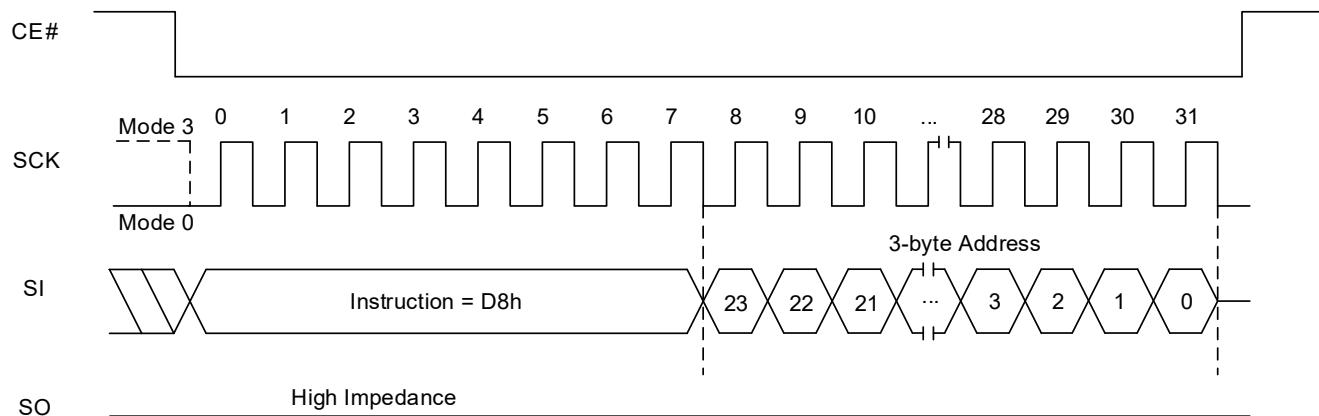

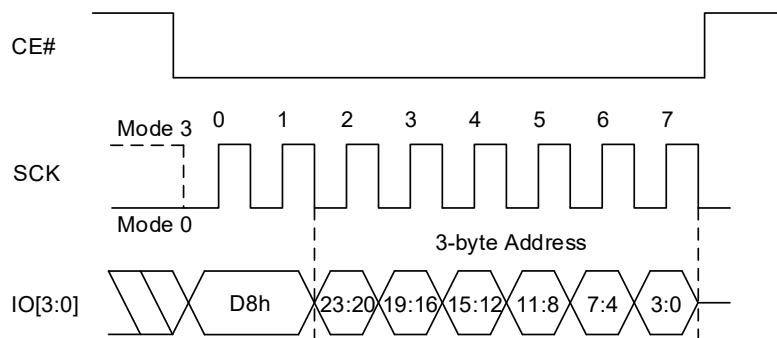

| 8.14 BLOCK ERASE OPERATION (BER32K:52h, BER64K:D8h) .....                                    | 65  |

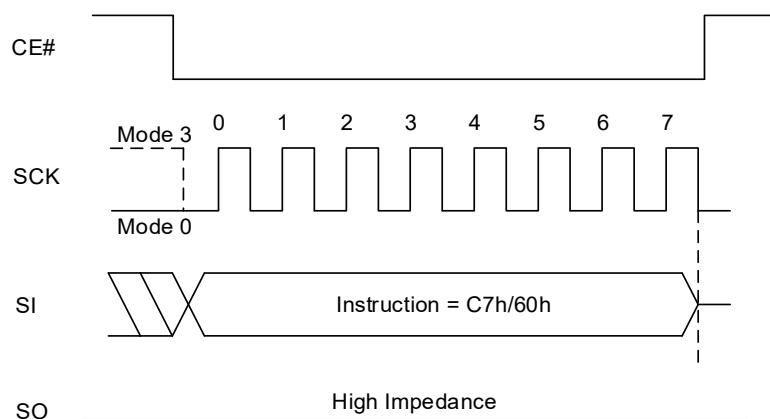

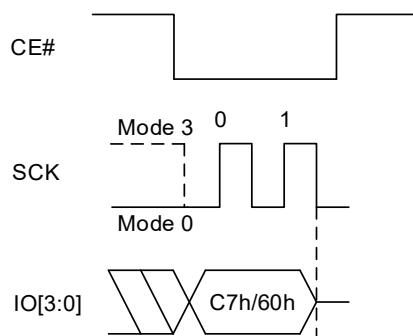

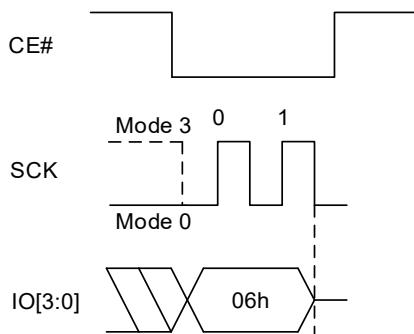

| 8.15 CHIP ERASE OPERATION (CER, C7h/60h) .....                                               | 66  |

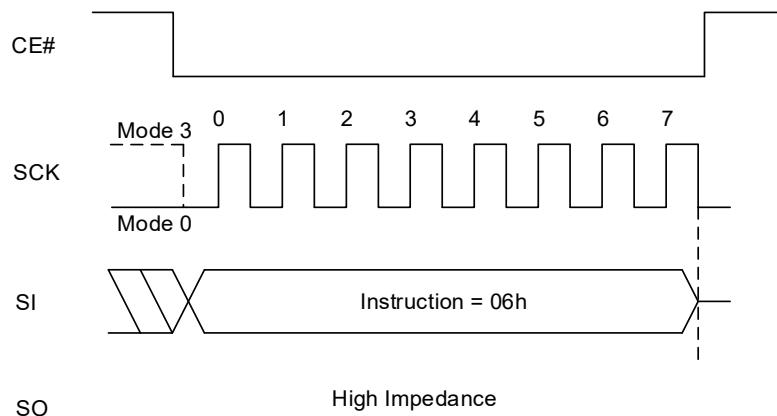

| 8.16 WRITE ENABLE OPERATION (WREN, 06h) .....                                                | 67  |

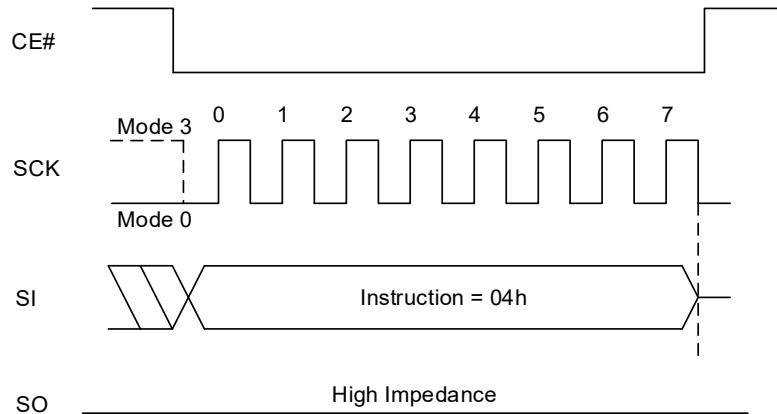

| 8.17 WRITE DISABLE OPERATION (WRDI, 04h) .....                                               | 68  |

| 8.18 READ STATUS REGISTER OPERATION (RDSR, 05h) .....                                        | 69  |

| 8.19 WRITE STATUS REGISTER OPERATION (WRSR, 01h) .....                                       | 70  |

| 8.20 READ FUNCTION REGISTER OPERATION (RDFR, 48h) .....                                      | 71  |

| 8.21 WRITE FUNCTION REGISTER OPERATION (WRFR, 42h) .....                                     | 72  |

| 8.22 ENTER QUAD PERIPHERAL INTERFACE (QPI) MODE OPERATION (QPIEN, 35h; QPIDI,F5h) ..         | 73  |

| 8.23 PROGRAM/ERASE SUSPEND & RESUME .....                                                    | 74  |

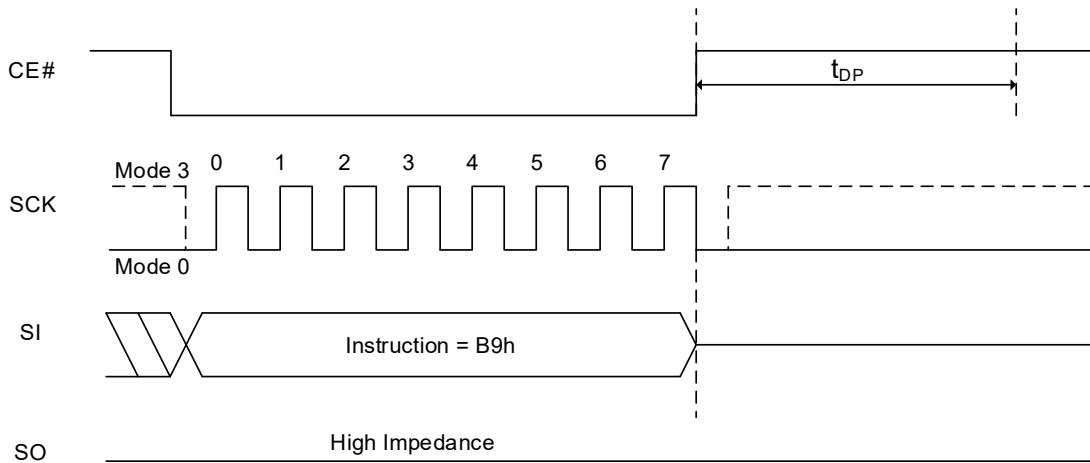

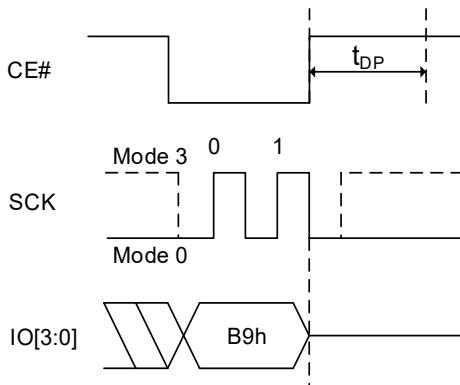

| 8.24 ENTER DEEP POWER DOWN (DP, B9h) .....                                                   | 77  |

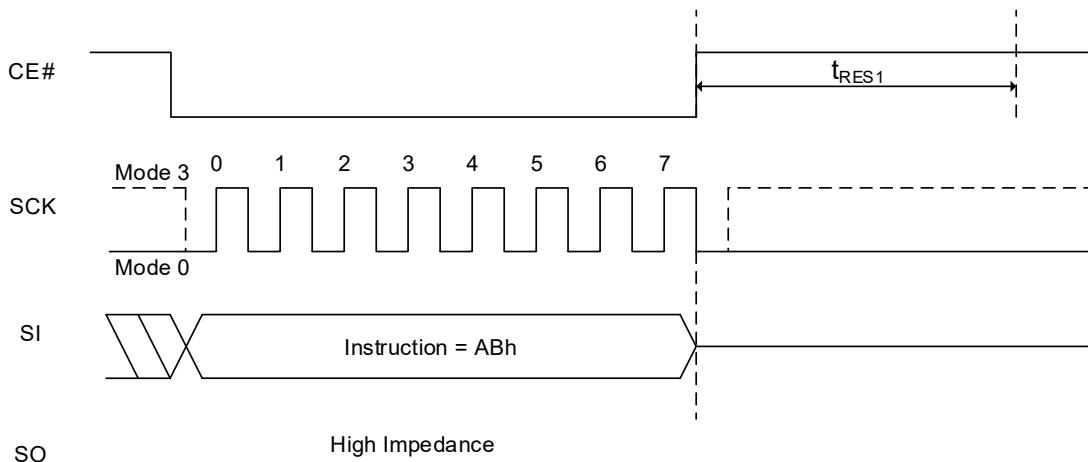

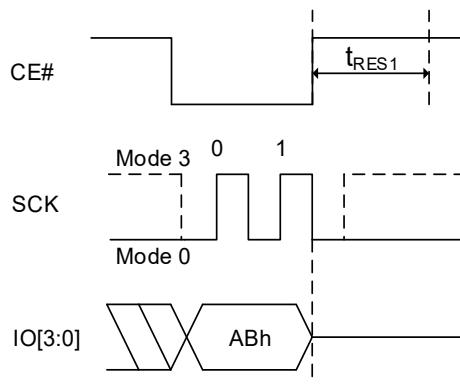

| 8.25 RELEASE DEEP POWER DOWN (RDPD, ABh) .....                                               | 78  |

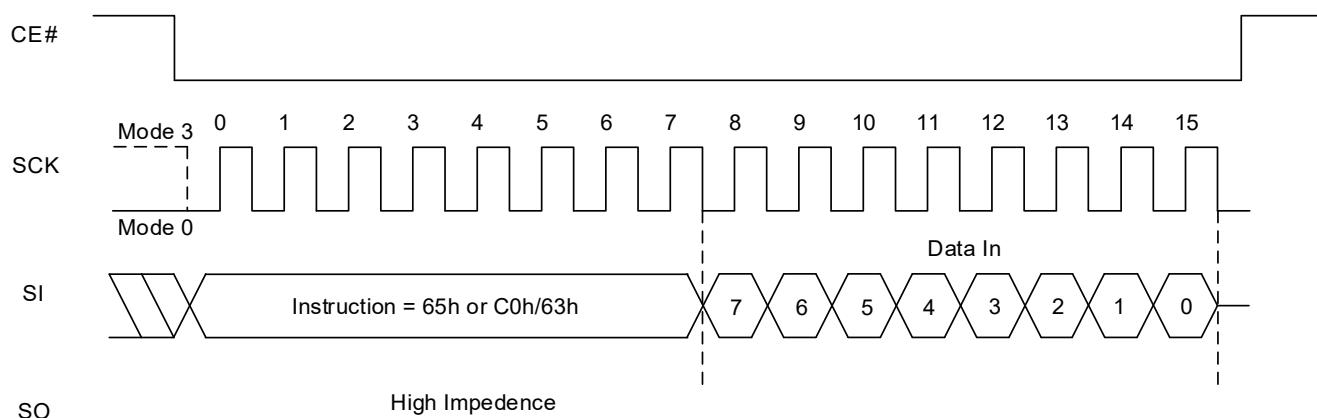

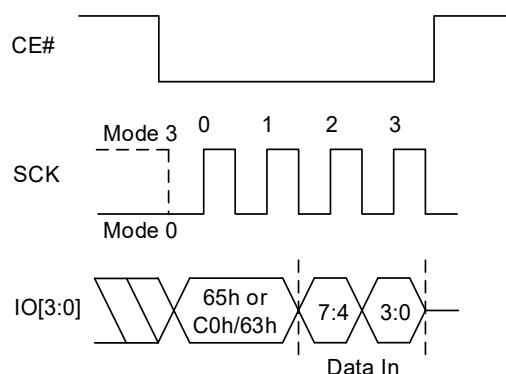

| 8.26 SET READ PARAMETERS OPERATION (SRPNV: 65h, SRPV: C0h/63h) .....                         | 79  |

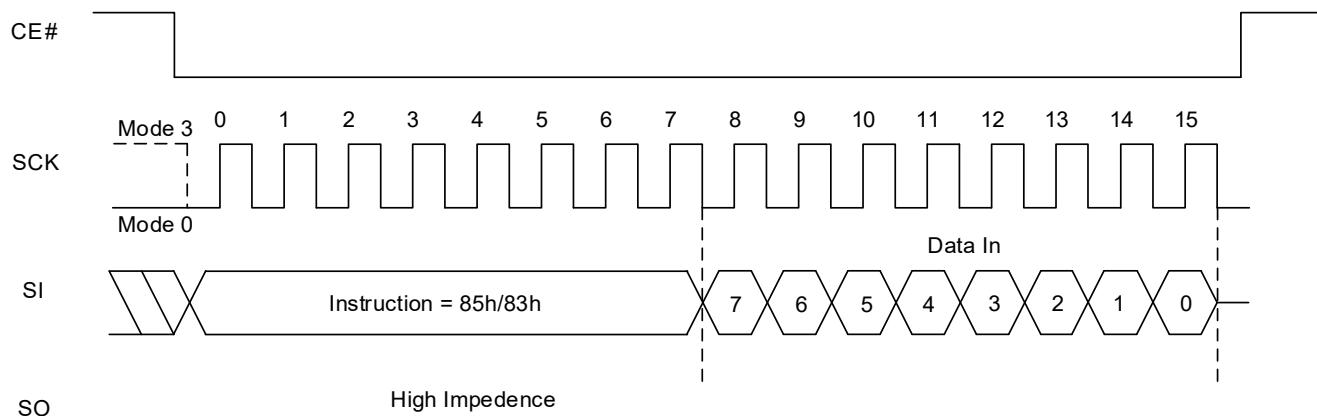

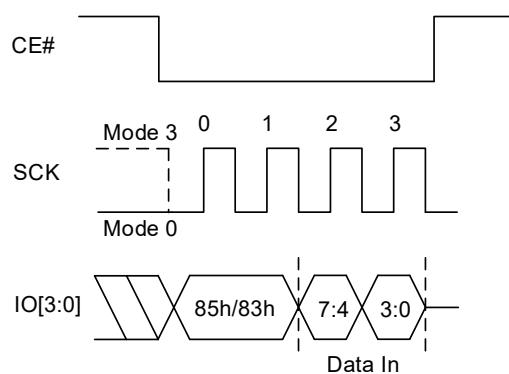

| 8.27 SET EXTENDED READ PARAMETERS OPERATION (SERPNV: 85h, SERPV: 83h) .....                  | 81  |

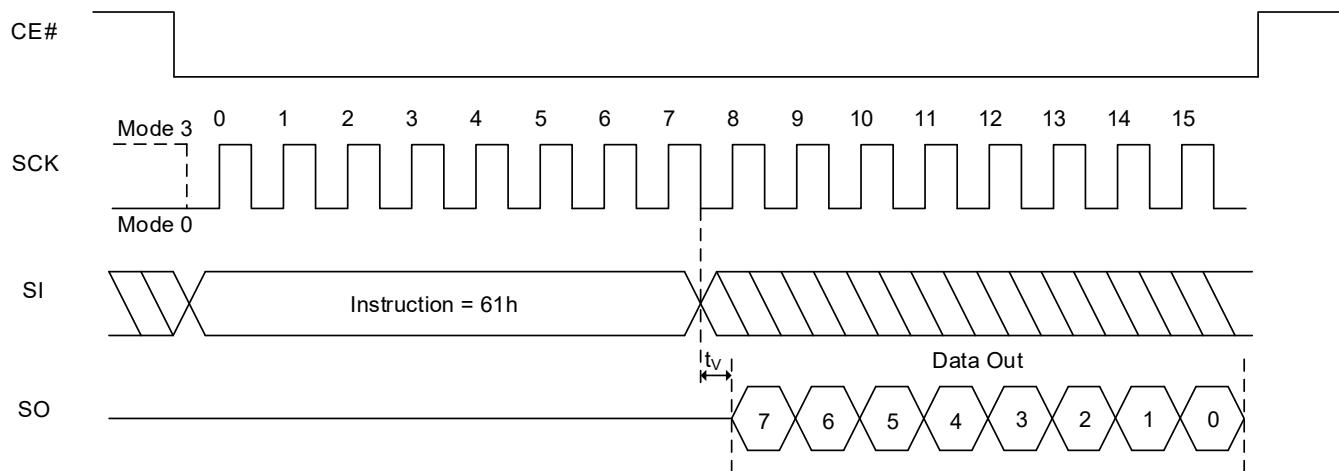

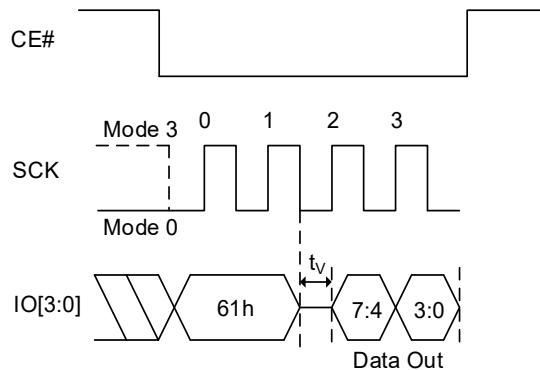

| 8.28 READ READ PARAMETERS OPERATION (RDRP, 61h) .....                                        | 82  |

| 8.29 READ EXTENDED READ PARAMETERS OPERATION (RDERP, 81h) .....                              | 83  |

| 8.30 CLEAR EXTENDED READ REGISTER OPERATION (CLERP, 82h) .....                               | 84  |

| 8.31 READ PRODUCT IDENTIFICATION (RDID, ABh) .....                                           | 85  |

| 8.32 READ PRODUCT IDENTIFICATION BY JEDEC ID OPERATION (RDJDID, 9Fh; RDJDIDQ, AFh) ..        | 87  |

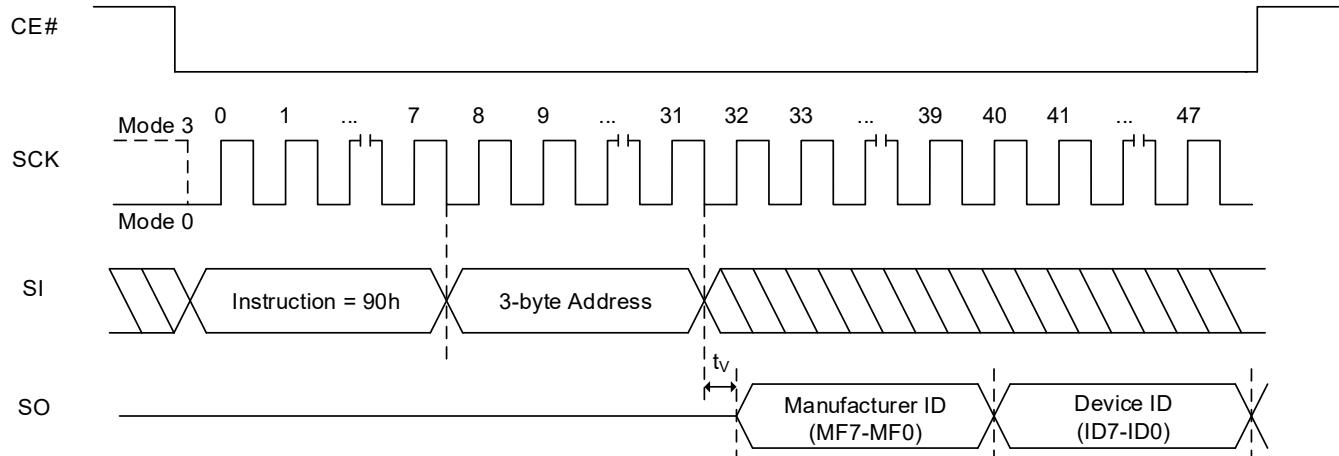

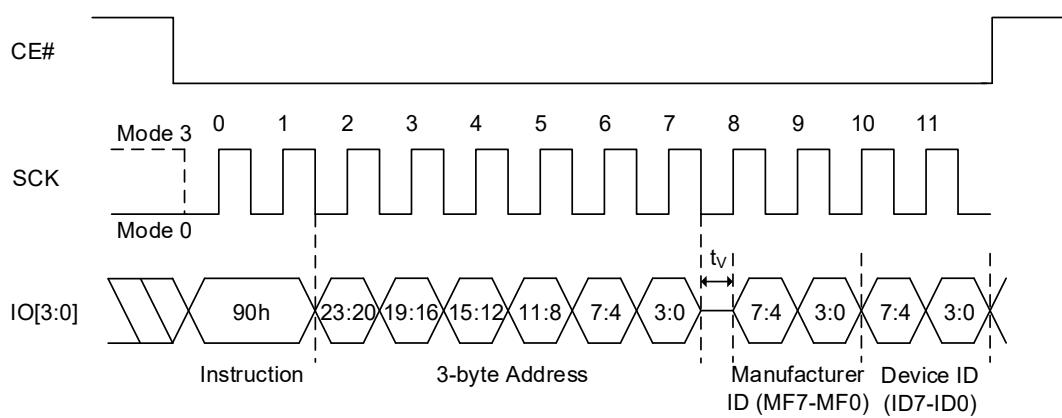

| 8.33 READ DEVICE MANUFACTURER AND DEVICE ID OPERATION (RDMDID, 90h) .....                    | 88  |

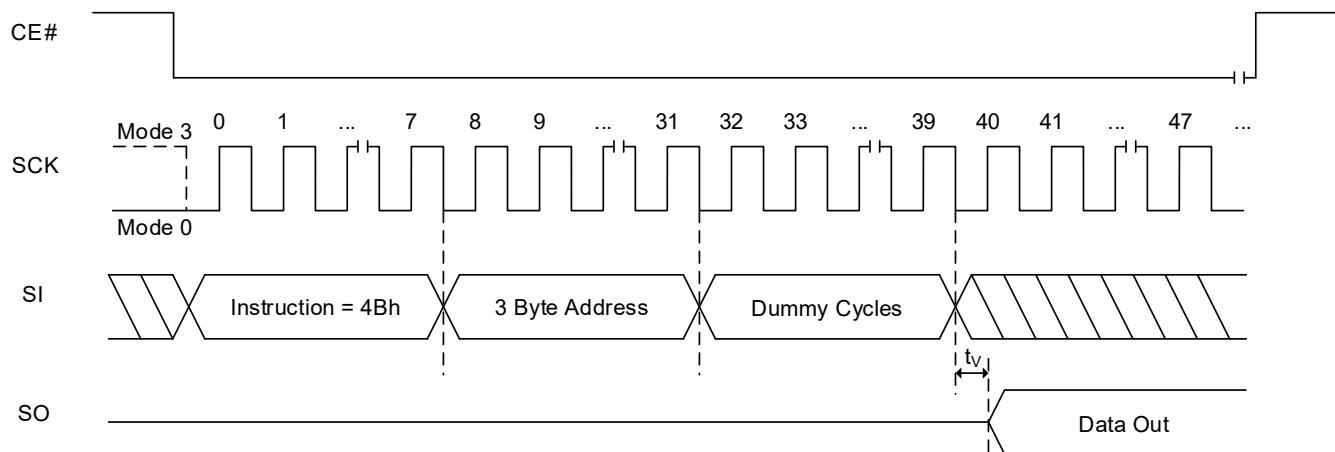

| 8.34 READ UNIQUE ID NUMBER (RDUID, 4Bh) .....                                                | 89  |

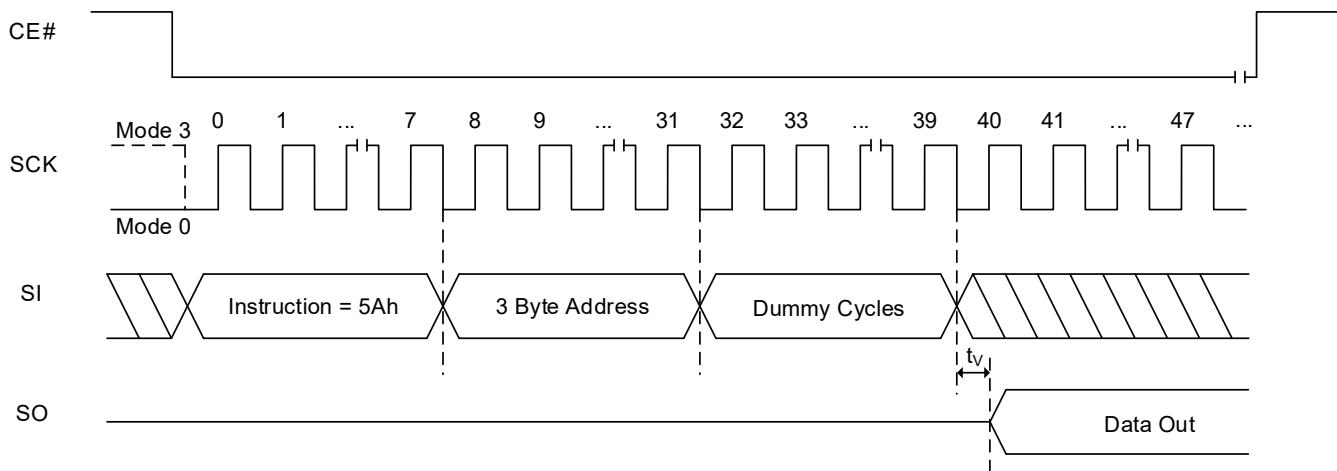

| 8.35 READ SFDP OPERATION (RDSFDP, 5Ah) .....                                                 | 90  |

| 8.36 NO OPERATION (NOP, 00h) .....                                                           | 90  |

| 8.37 SOFTWARE RESET (RESET-ENABLE (RSTEN, 66h) AND RESET (RST, 99h) AND HARDWARE RESET ..... | 91  |

| 8.38 SECURITY INFORMATION ROW .....                                                          | 92  |

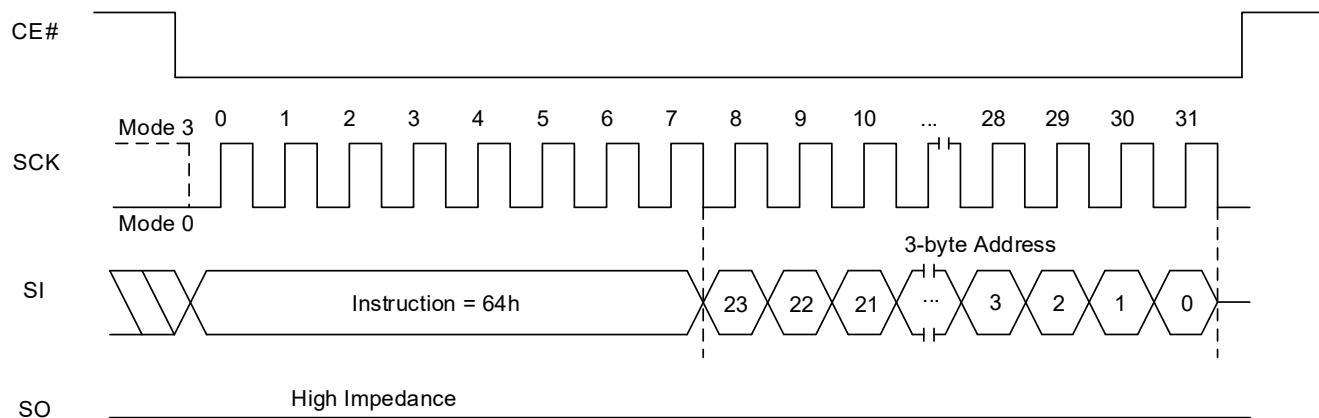

| 8.39 INFORMATION ROW ERASE OPERATION (IRER, 64h) .....                                       | 93  |

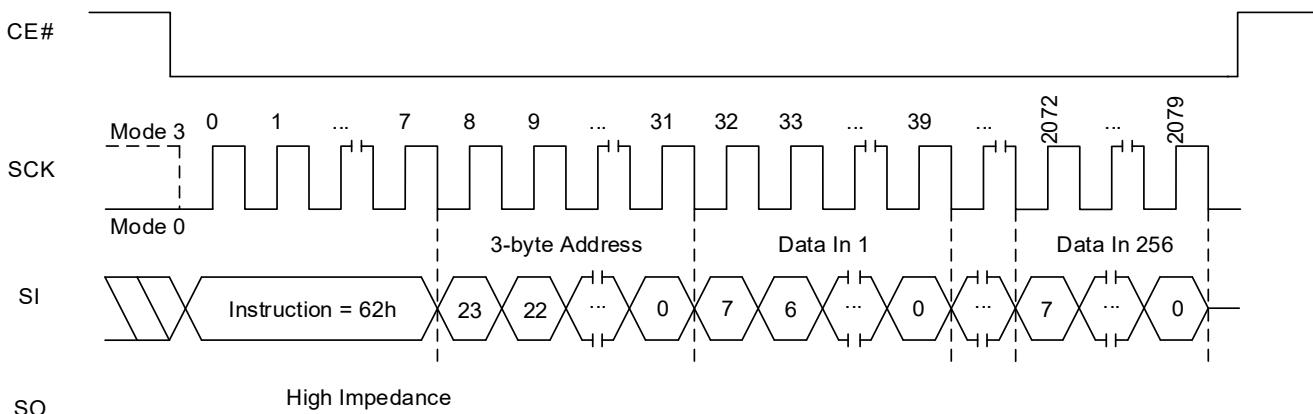

| 8.40 INFORMATION ROW PROGRAM OPERATION (IRP, 62h) .....                                      | 94  |

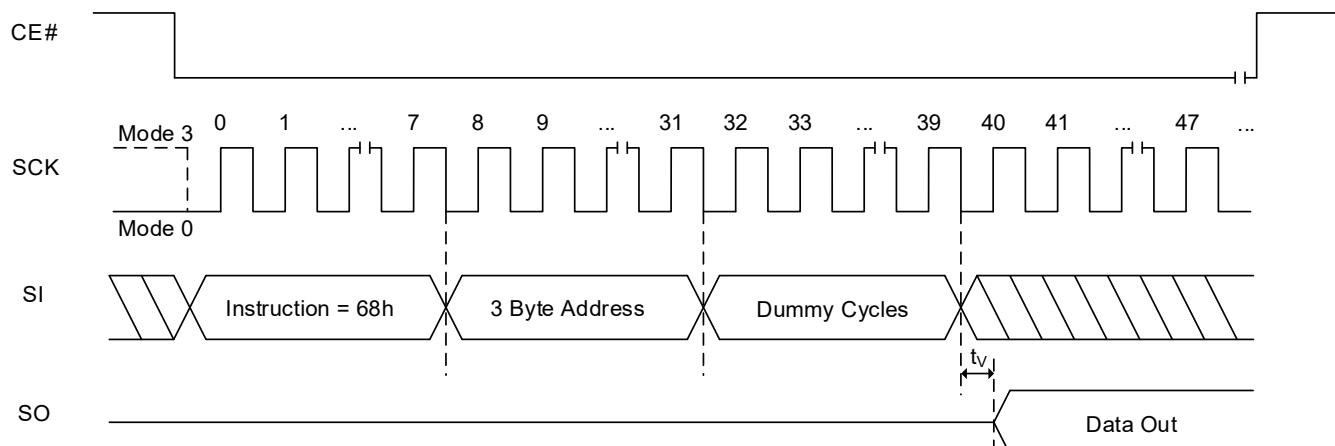

| 8.41 INFORMATION ROW READ OPERATION (IRRD, 68h) .....                                        | 95  |

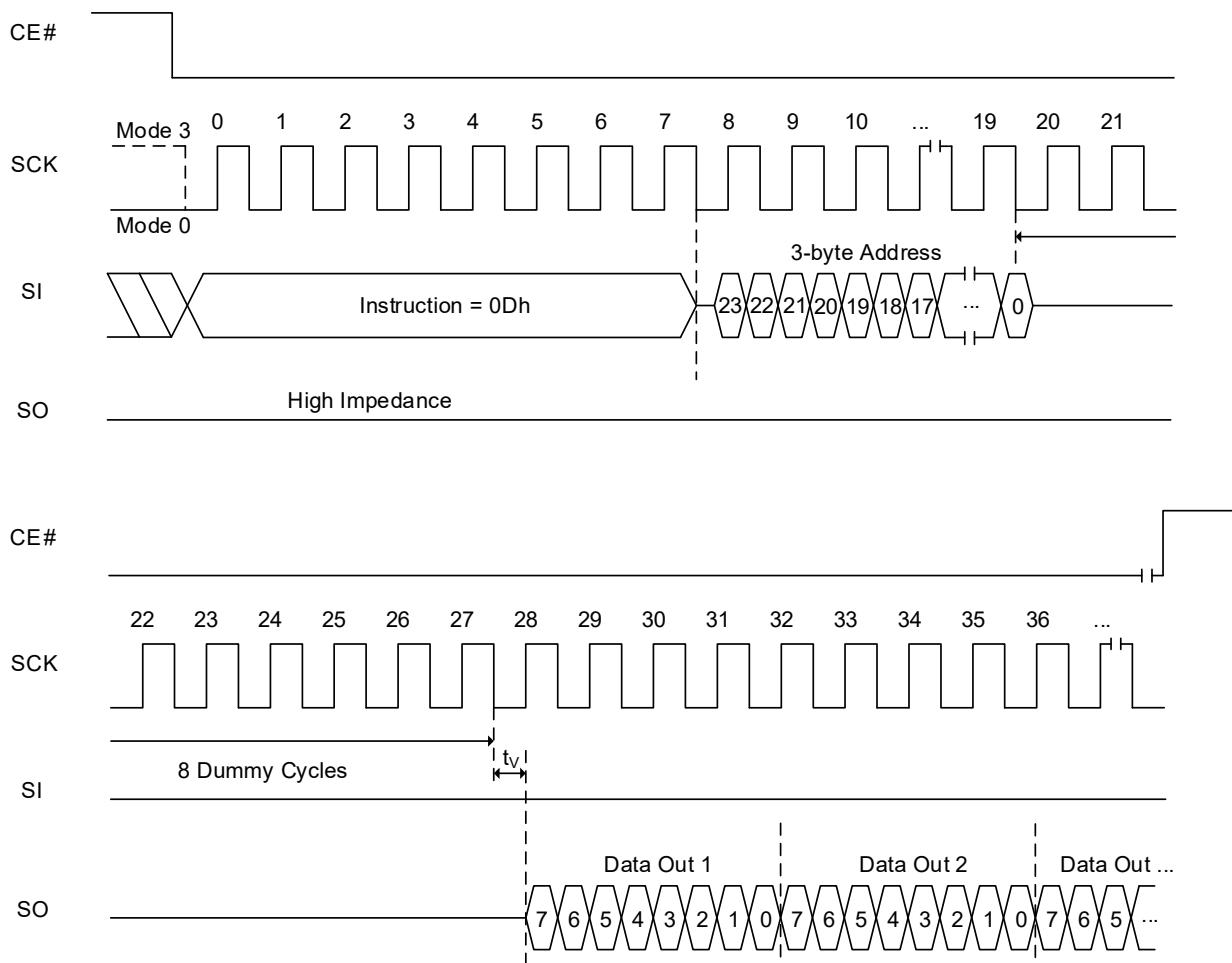

| 8.42 FAST READ DTR MODE OPERATION (FRDTR, 0Dh) .....                                         | 96  |

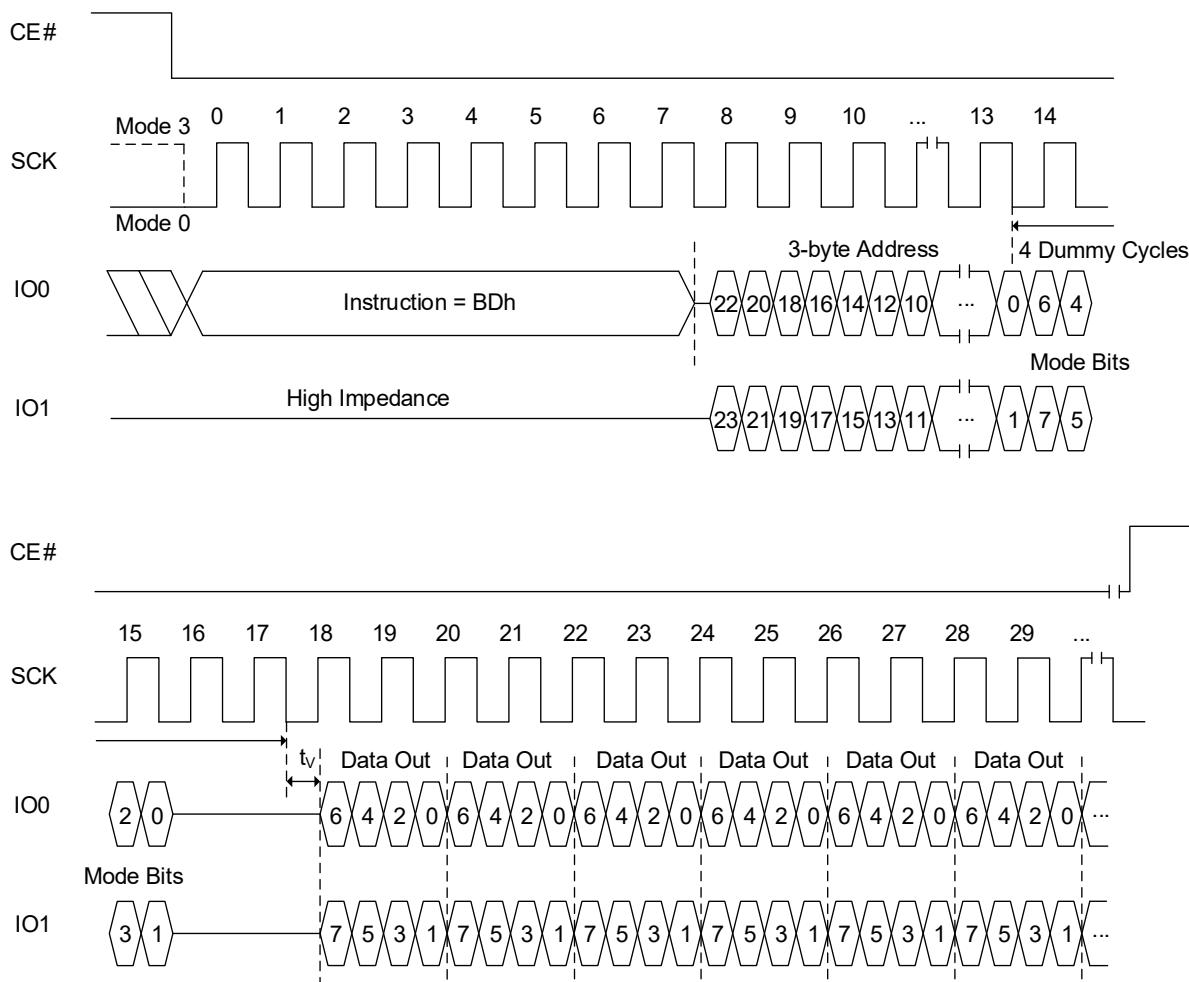

| 8.43 FAST READ DUAL IO DTR MODE OPERATION (FRDDTR, BDh) .....                                | 99  |

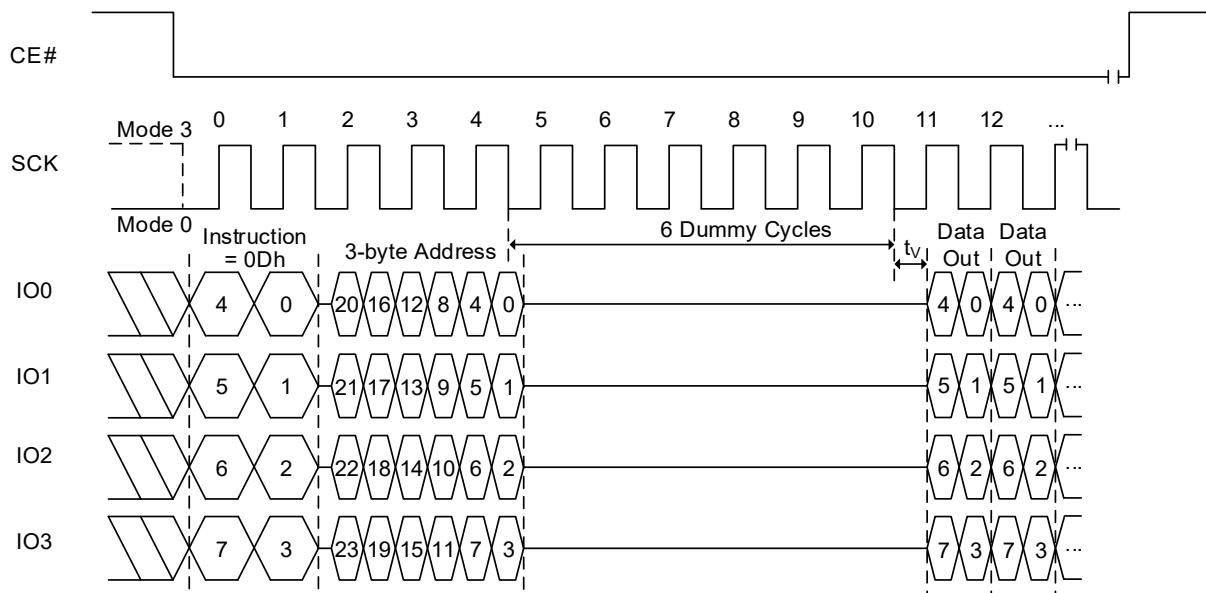

| 8.44 FAST READ QUAD IO DTR MODE OPERATION IN SPI MODE (FRQDTR, EDh) .....                    | 102 |

| 8.45 SECTOR LOCK/UNLOCK FUNCTIONS .....                                                      | 105 |

| 8.46 AUTOBOOT .....                                                                          | 108 |

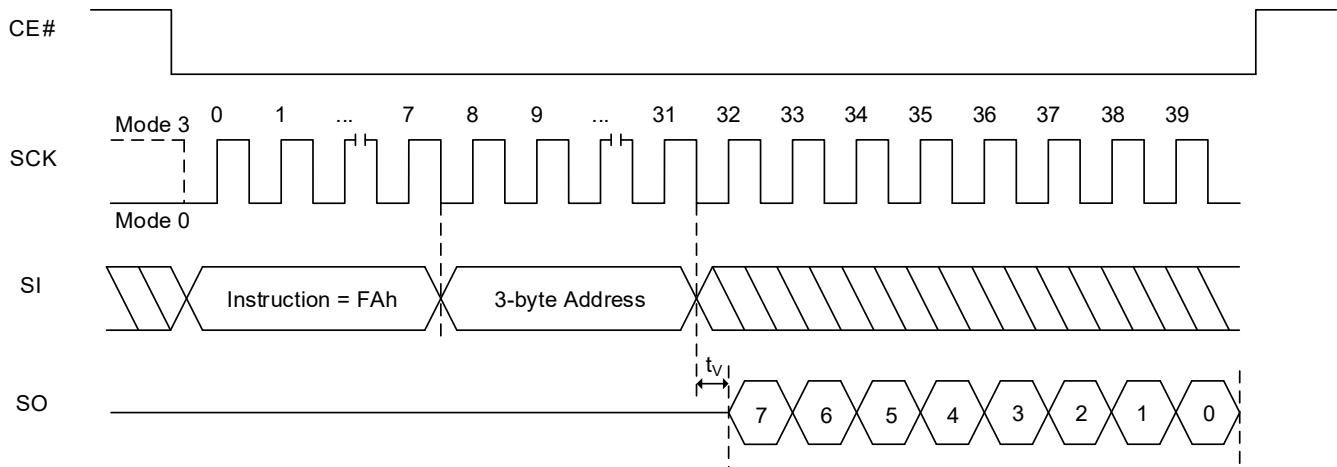

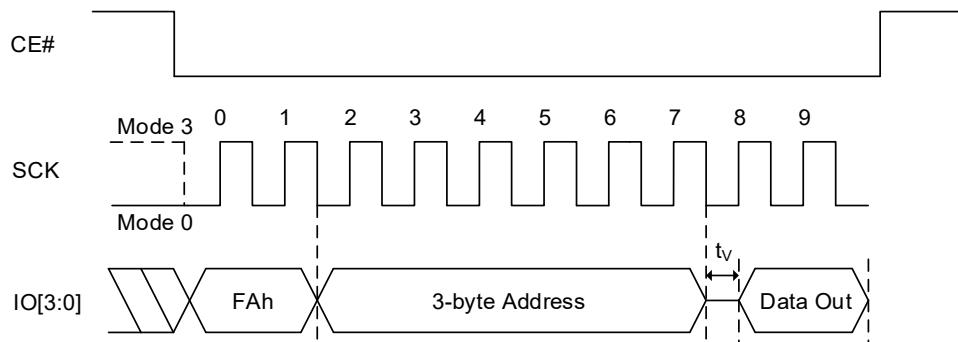

| 8.47 READ DYB OPERATION (RDDYB, FAh) .....                                                   | 112 |

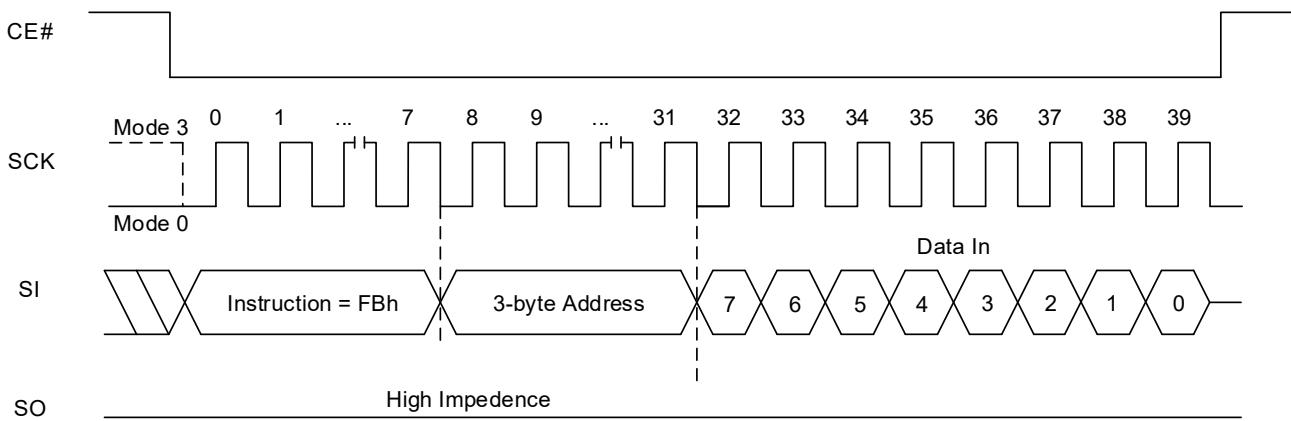

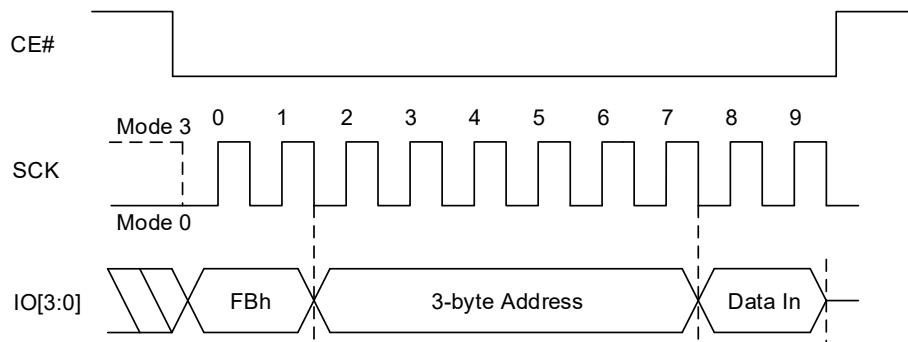

| 8.48 WRITE DYB OPERATION (WRDYB, FBh) .....                                                  | 114 |

| 8.49 READ PPB OPERATION (RDPPB, FCh) .....                                                   | 116 |

|                                                                                         |     |

|-----------------------------------------------------------------------------------------|-----|

| 8.50 PROGRAM PPB OPERATION (PGPPB, FDh) .....                                           | 117 |

| 8.51 ERASE PPB OPERATION (ERPPB, E4h) .....                                             | 118 |

| 8.52 READ ASP OPERATION (RDASP, 2Bh) .....                                              | 119 |

| 8.53 PROGRAM ASP OPERATION (PGASP, 2Fh) .....                                           | 120 |

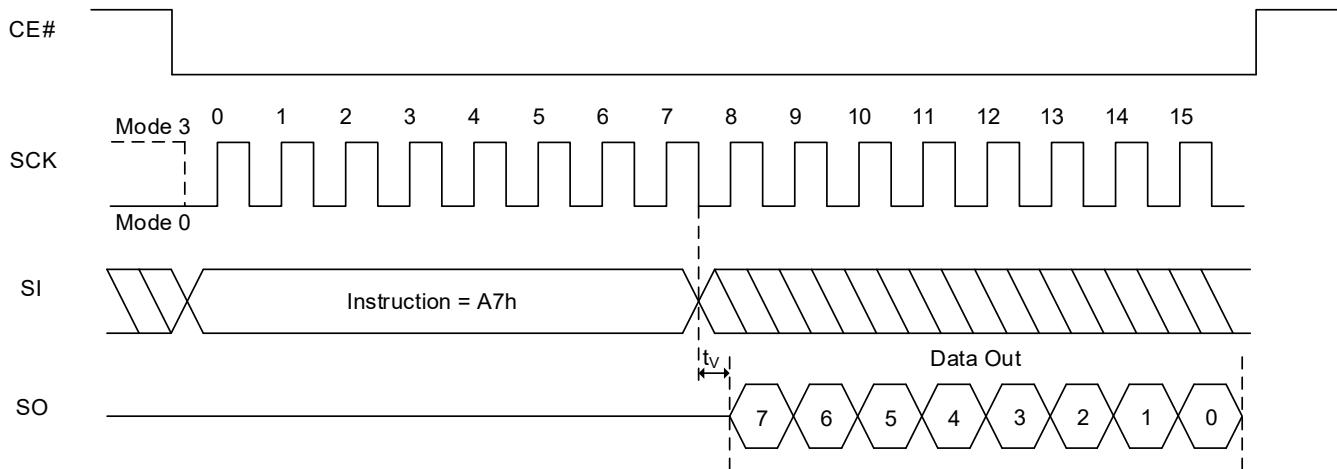

| 8.54 READ PPB LOCK BIT OPERATION (RDPLB, A7h) .....                                     | 121 |

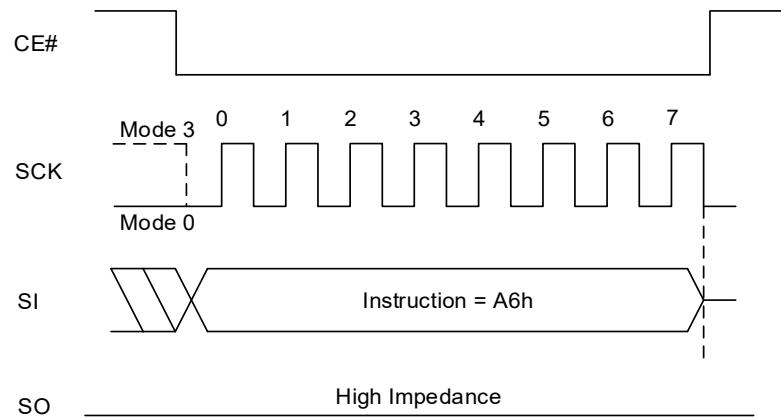

| 8.55 WRITE PPB LOCK BIT OPERATION (WRPLB, A6h) .....                                    | 122 |

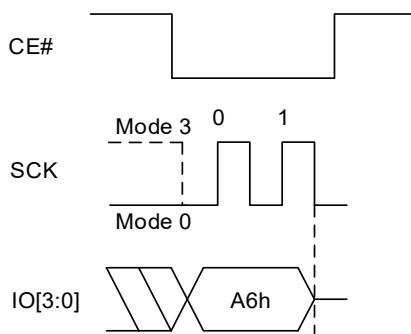

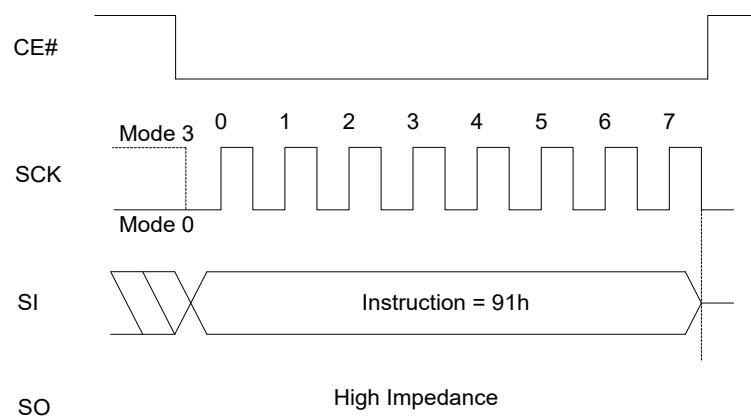

| 8.56 SET FREEZE BIT OPERATION (SFRZ, 91h) .....                                         | 123 |

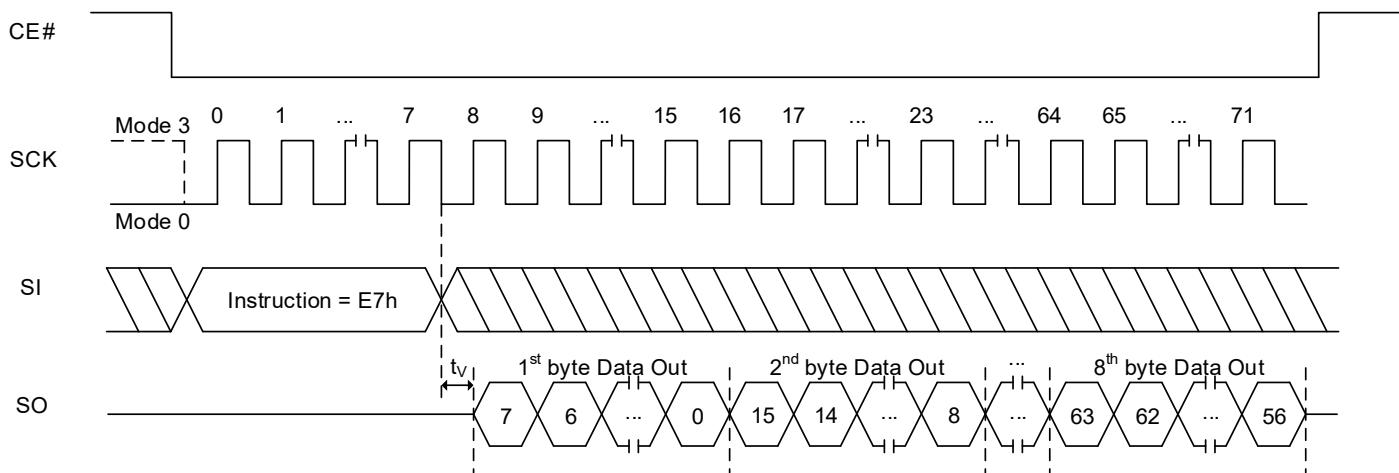

| 8.57 READ PASSWORD OPERATION (RDPWD, E7h) .....                                         | 124 |

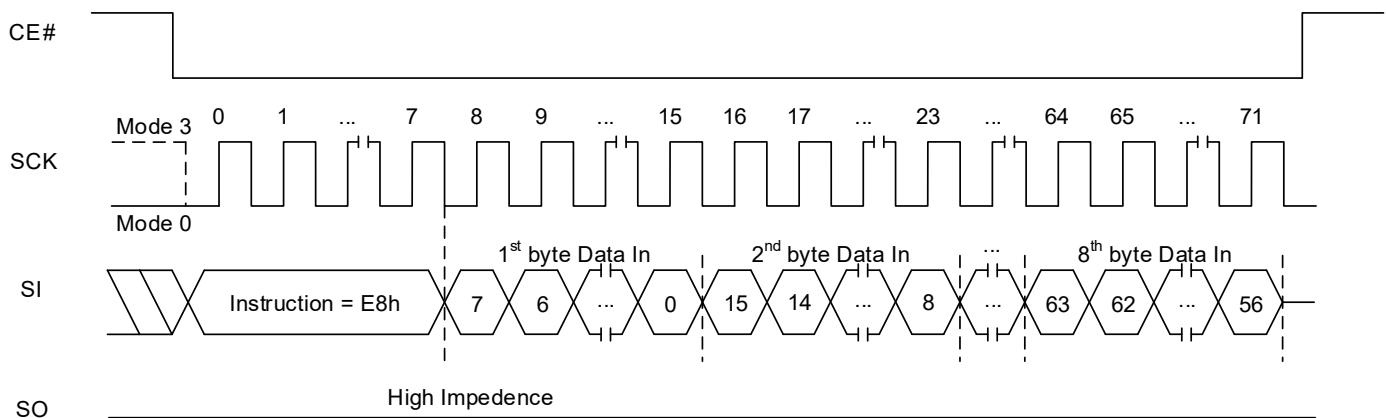

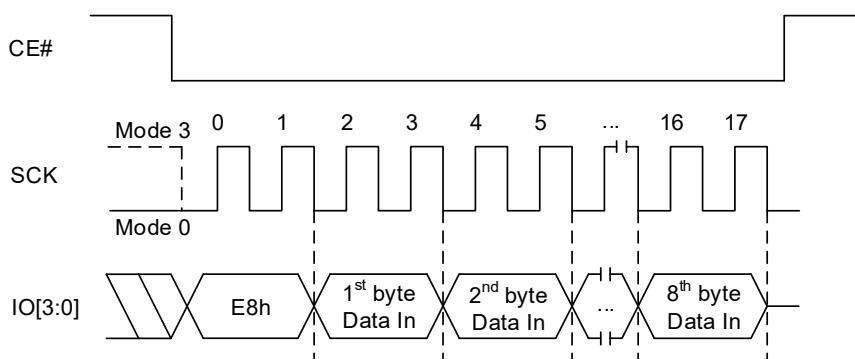

| 8.58 PROGRAM PASSWORD OPERATION (PGPWD, E8h) .....                                      | 125 |

| 8.59 UNLOCK PASSWORD OPERATION (UNPWD, E9h) .....                                       | 126 |

| 8.60 GANG SECTOR/BLOCK LOCK OPERATION (GBLK, 7Eh) .....                                 | 127 |

| 8.61 GANG SECTOR/BLOCK UNLOCK OPERATION (GBUN, 98h) .....                               | 128 |

| 9. ELECTRICAL CHARACTERISTICS .....                                                     | 129 |

| 9.1 ABSOLUTE MAXIMUM RATINGS <sup>(1)</sup> .....                                       | 129 |

| 9.2 OPERATING RANGE .....                                                               | 129 |

| 9.3 DC CHARACTERISTICS .....                                                            | 130 |

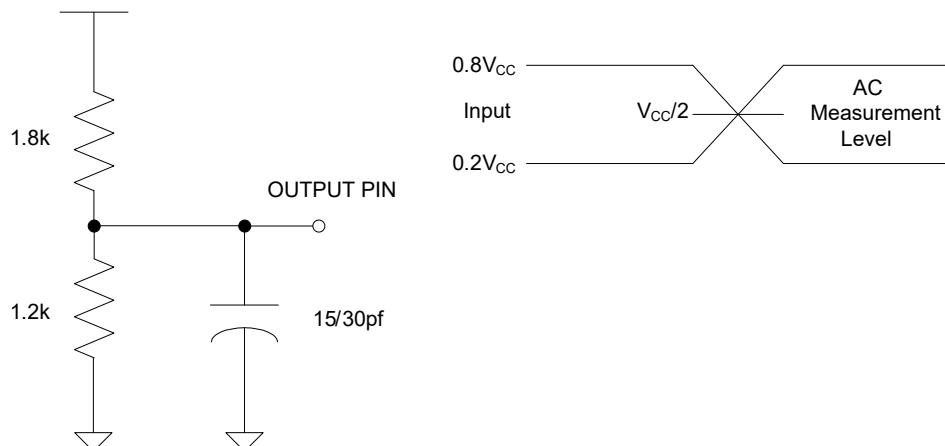

| 9.4 AC MEASUREMENT CONDITIONS .....                                                     | 131 |

| 9.5 PIN CAPACITANCE .....                                                               | 131 |

| 9.6 AC CHARACTERISTICS .....                                                            | 132 |

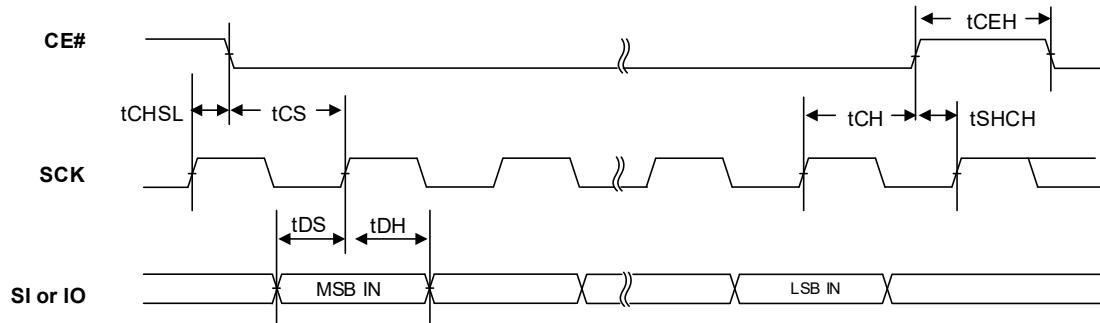

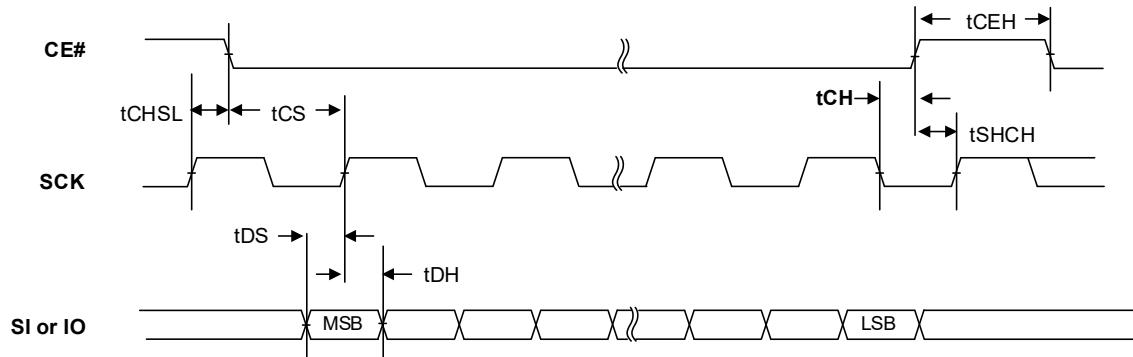

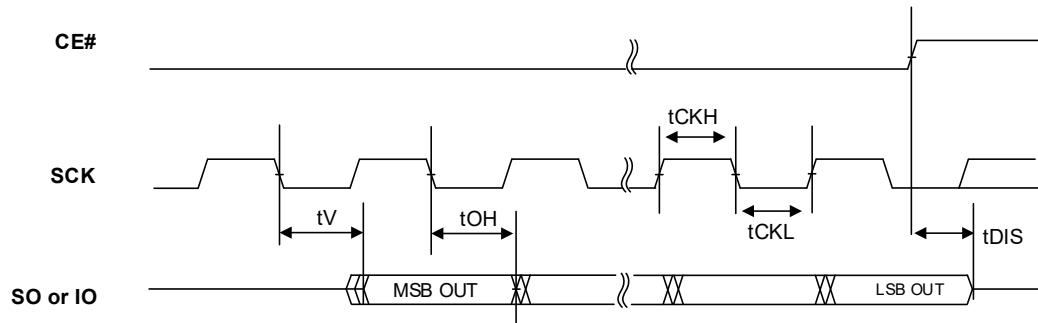

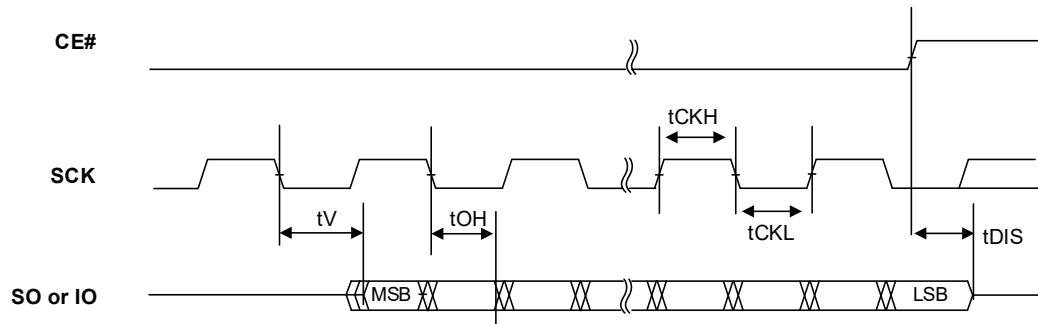

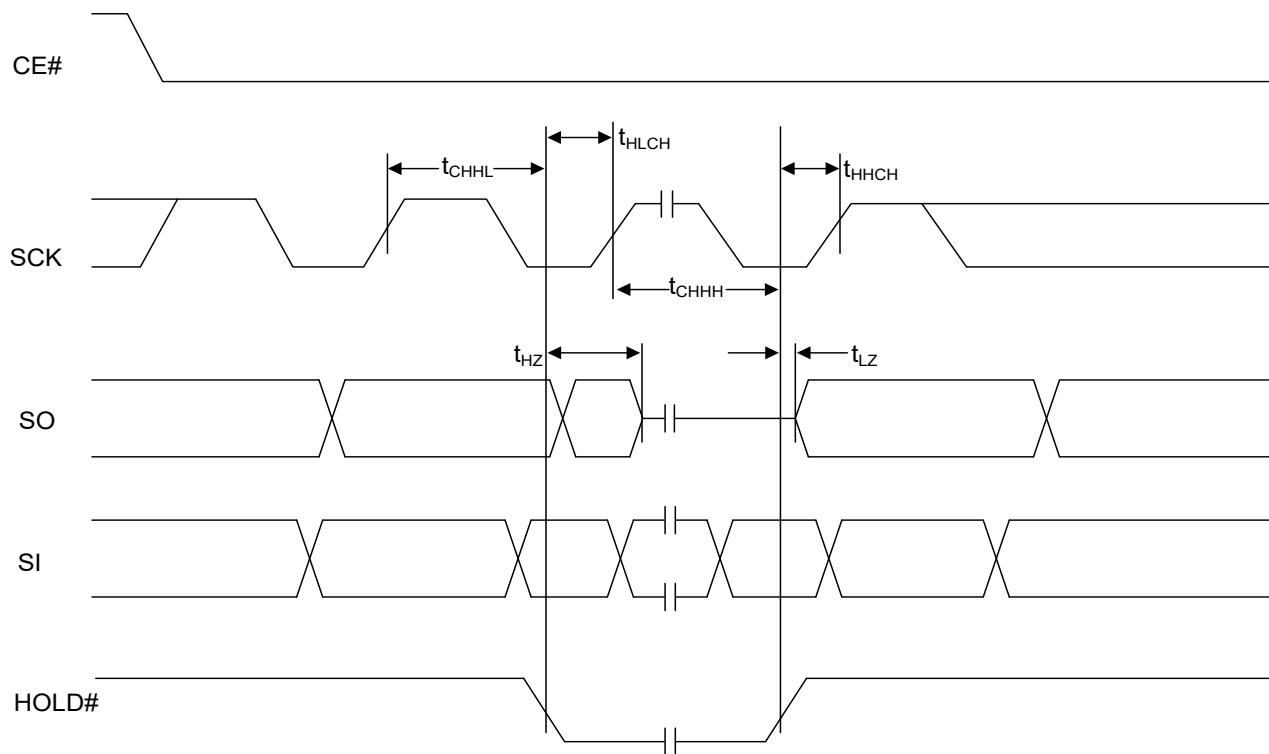

| 9.7 SERIAL INPUT/OUTPUT TIMING .....                                                    | 134 |

| 9.8 POWER-UP AND POWER-DOWN .....                                                       | 137 |

| 9.9 PROGRAM/ERASE PERFORMANCE .....                                                     | 138 |

| 9.10 RELIABILITY CHARACTERISTICS .....                                                  | 138 |

| 10. PACKAGE TYPE INFORMATION .....                                                      | 139 |

| 10.1 8-CONTACT ULTRA-THIN SMALL OUTLINE NO-LEAD (WSON) PACKAGE 8x6mm (L) .....          | 139 |

| 10.2 8-CONTACT ULTRA-THIN SMALL OUTLINE NO-LEAD (WSON) PACKAGE 8x6mm (J) .....          | 140 |

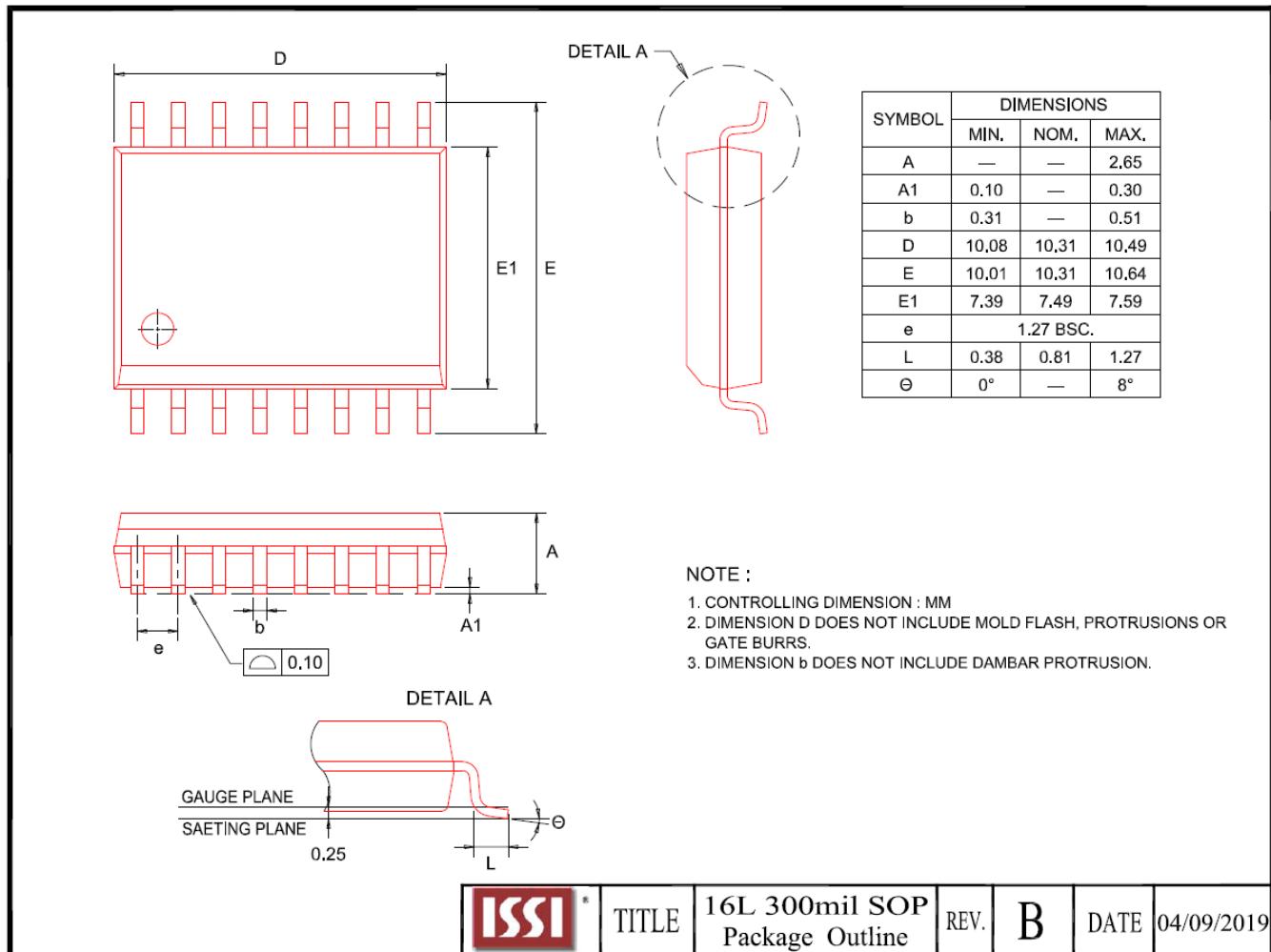

| 10.3 16-LEAD PLASTIC SMALL OUTLINE PACKAGE (300 MILS BODY WIDTH) (M) .....              | 141 |

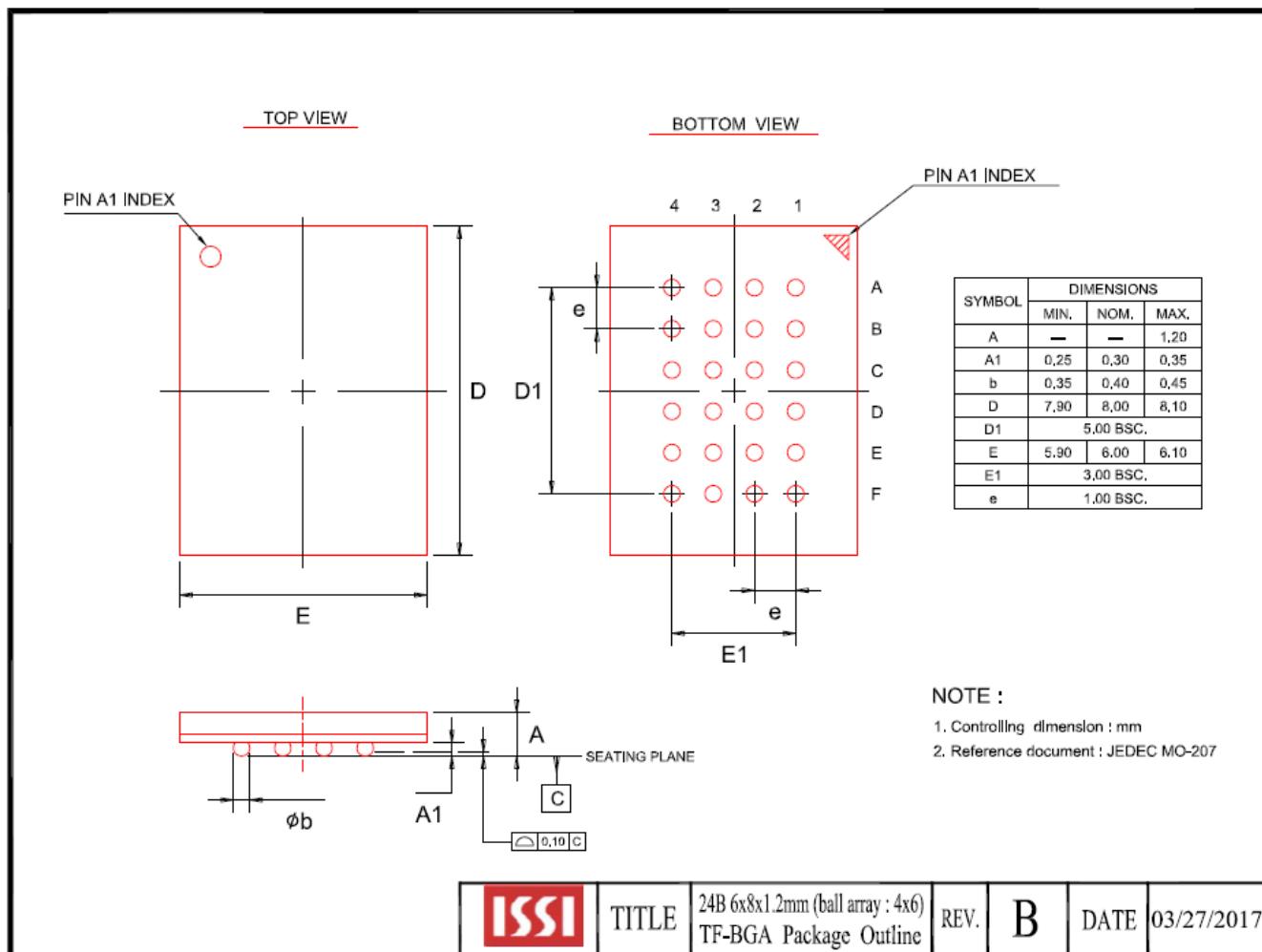

| 10.4 24-BALL THIN PROFILE FINE PITCH BGA 6x8mm 4x6 BALL ARRAY (G) .....                 | 142 |

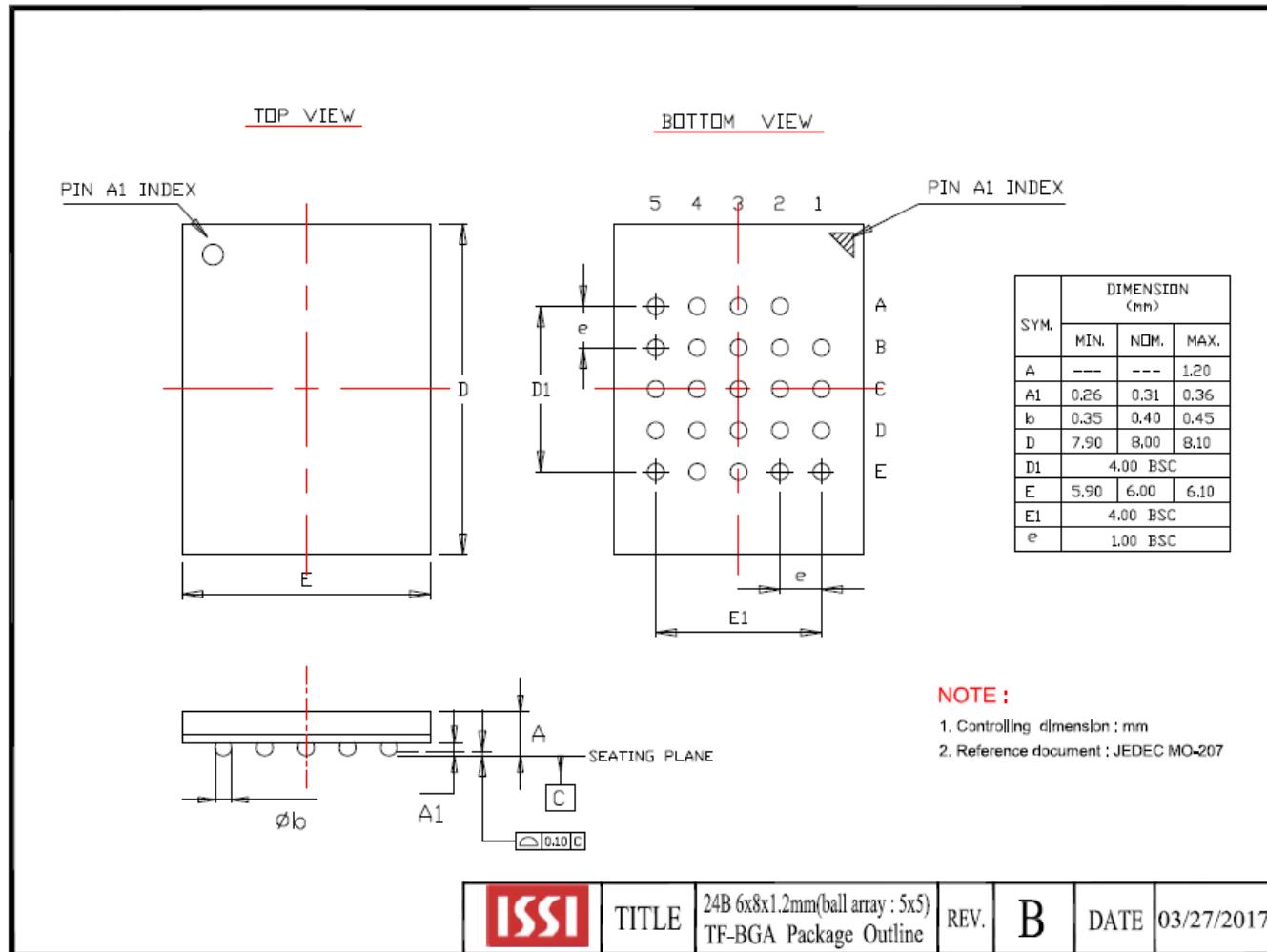

| 10.5 24-BALL THIN PROFILE FINE PITCH BGA 6x8mm 5x5 BALL ARRAY (H) .....                 | 143 |

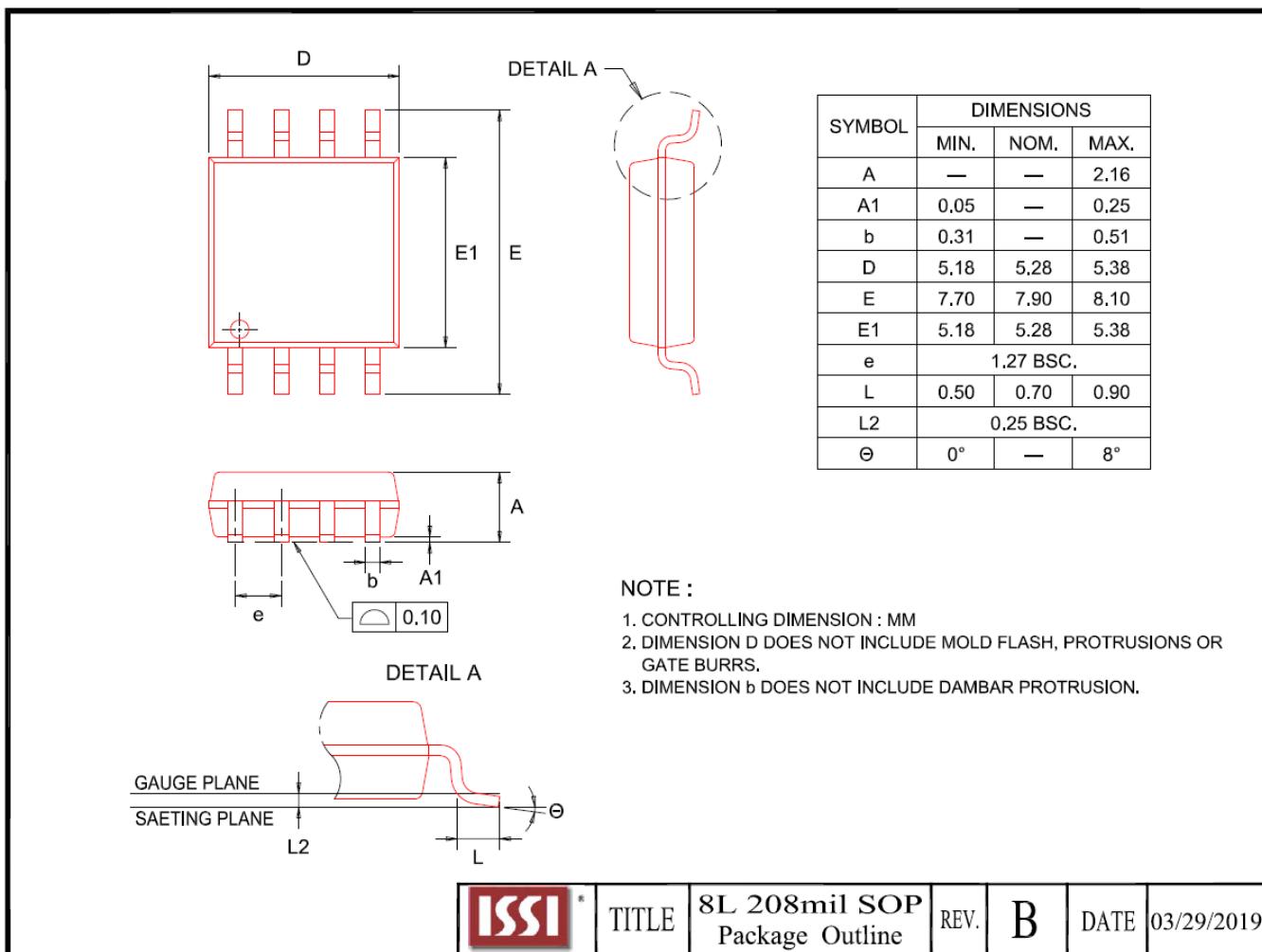

| 10.6 8-Pin JEDEC 208mil Broad Small Outline Integrated Circuit (SOIC) PACKAGE (B) ..... | 144 |

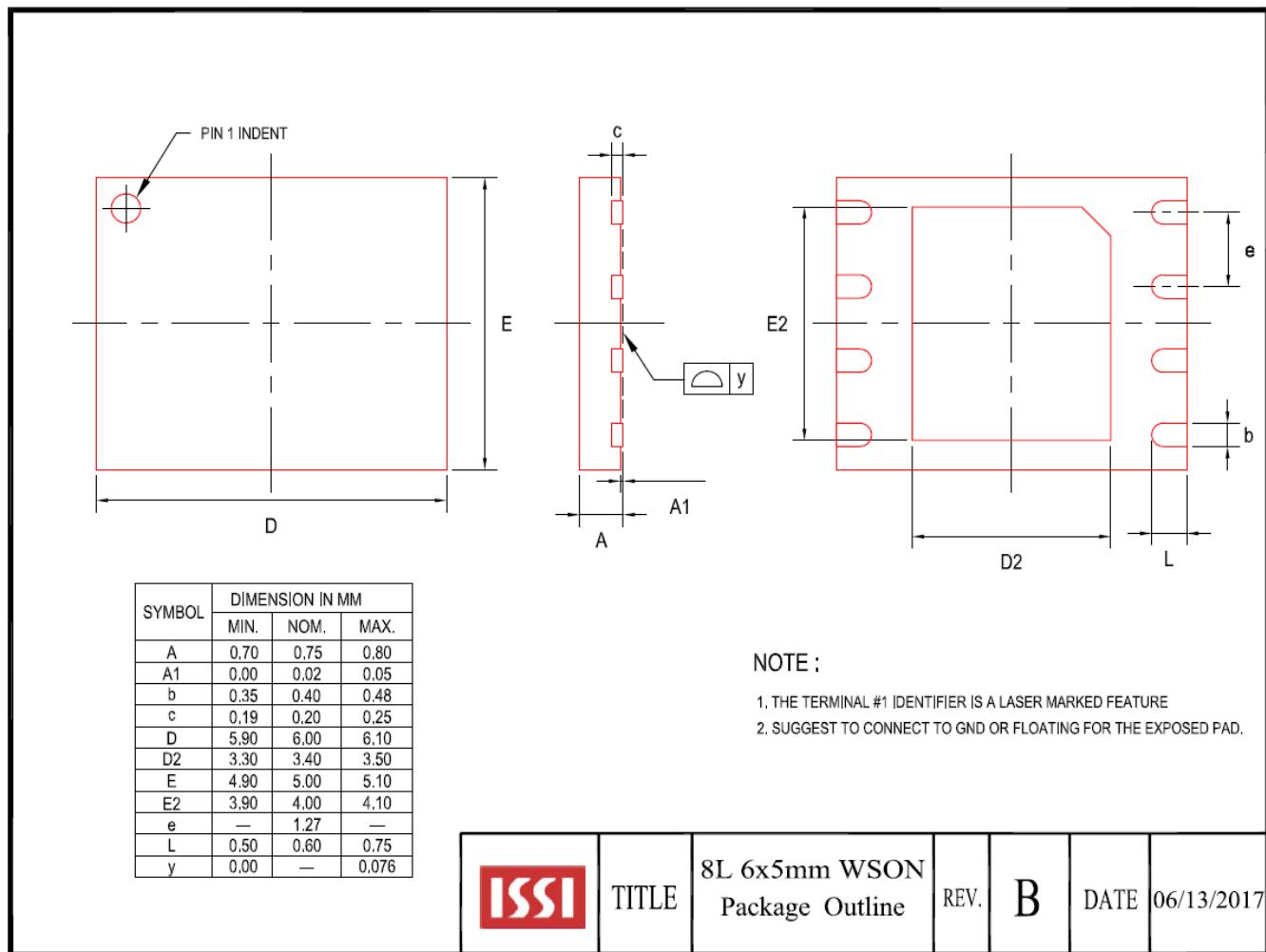

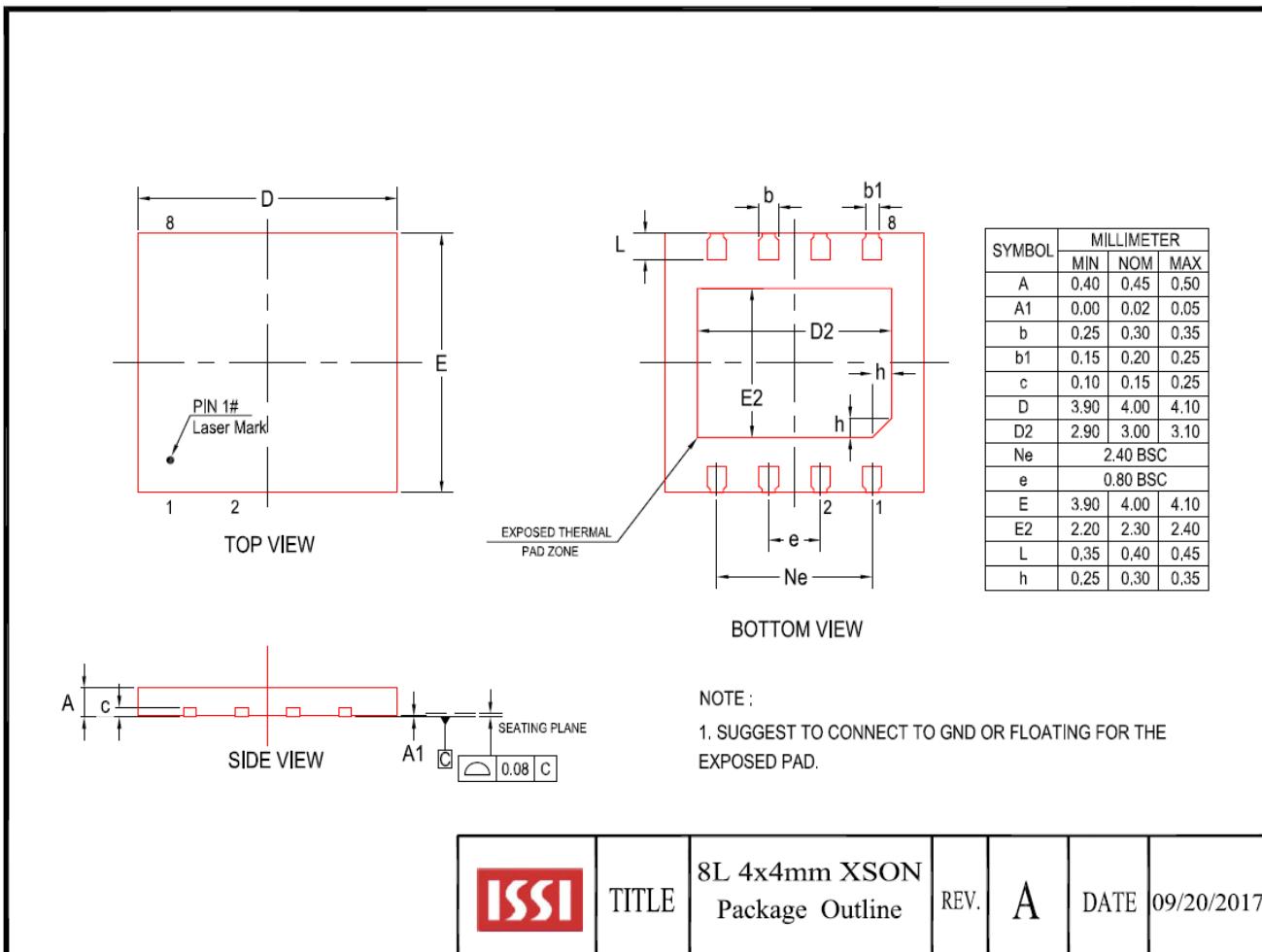

| 10.7 8 Contact Ultra-Thin Small Outline No-Lead (WSON) PACKAGE 6X5MM (K) .....          | 145 |

| 10.8 8 Contact Extremely-Thin Small Outline No-Lead (XSON) Package 4x4mm (E) .....      | 146 |

| 11. ORDERING INFORMATION – Valid Part Numbers .....                                     | 147 |

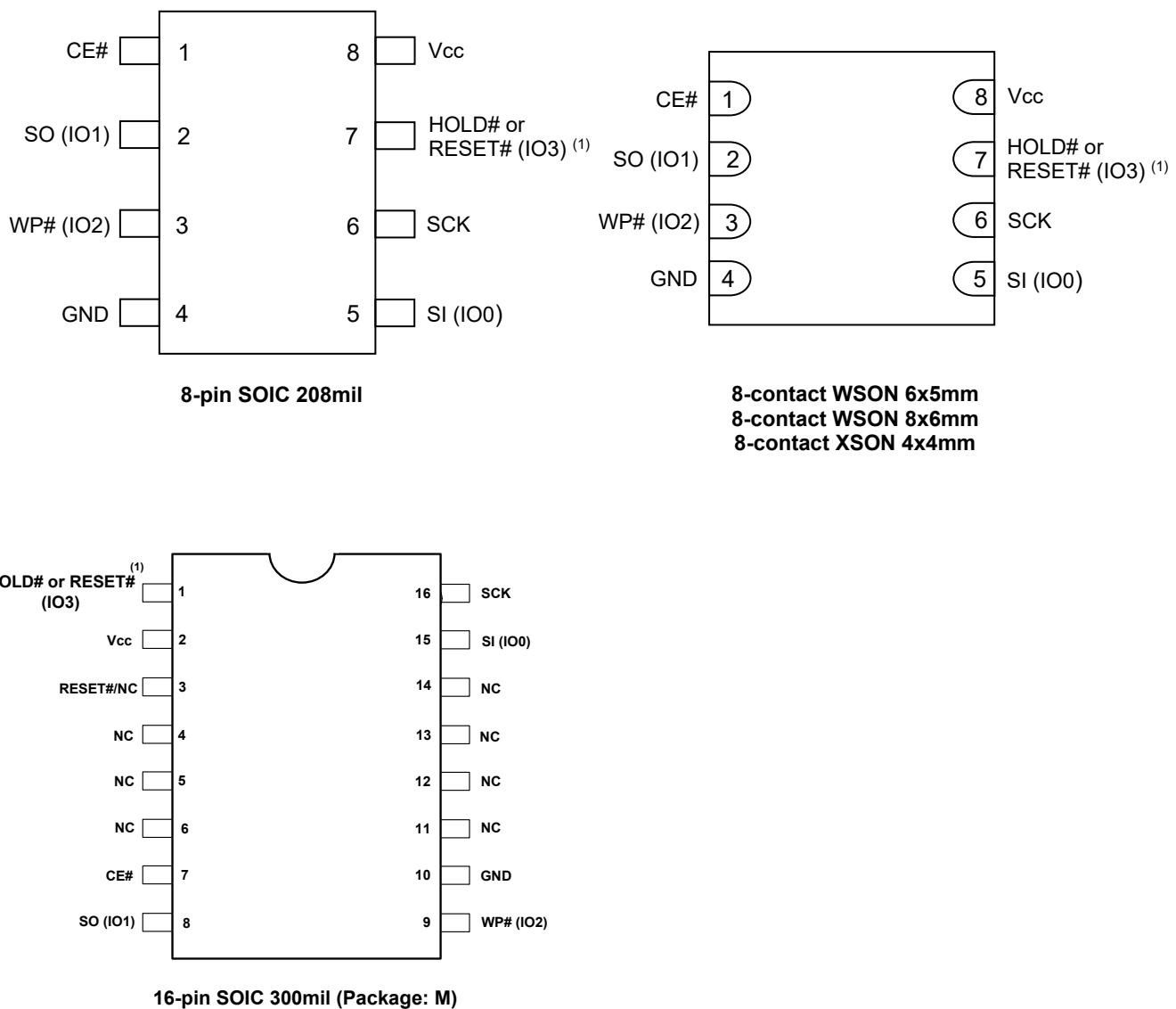

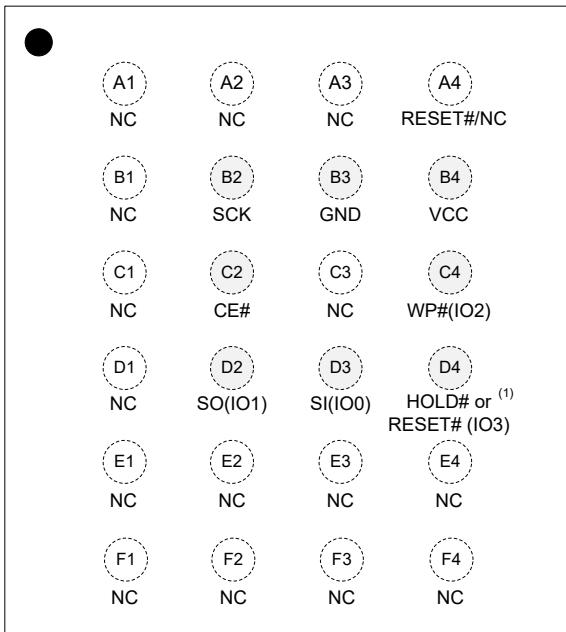

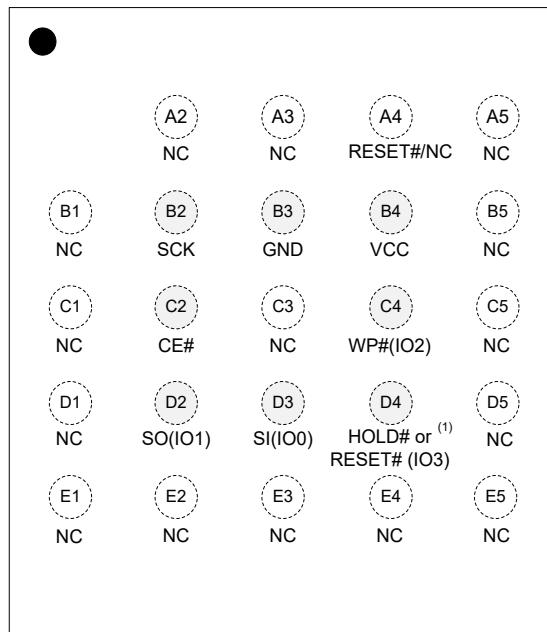

## 1. PIN CONFIGURATION

Top View, Balls Facing Down

24-ball TFBGA 6x8mm (4x6 ball array)

(Package: G)

Top View, Balls Facing Down

24-ball TFBGA 6x8mm (5x5 ball array)

(Package: H)

**Note:**

1. The pin can be configured as Hold# or Reset# by setting P7 bit of the Read Register. Pin default is Hold# (IO3).

## 2. PIN DESCRIPTIONS

| SYMBOL                            | TYPE         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CE#                               | INPUT        | <p><b>Chip Enable:</b> The Chip Enable (CE#) pin enables and disables the devices operation. When CE# is high the device is deselected and output pins are in a high impedance state. When deselected the devices non-critical internal circuitry power down to allow minimal levels of power consumption while in a standby state.</p> <p>When CE# is pulled low the device will be selected and brought out of standby mode. The device is considered active and instructions can be written to, data read, and written to the device. After power-up, CE# must transition from high to low before a new instruction will be accepted.</p> <p>Keeping CE# in a high state deselects the device and switches it into its low power state. Data will not be accepted when CE# is high.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SI (IO0),<br>SO (IO1)             | INPUT/OUTPUT | <p><b>Serial Data Input, Serial Output, and IOs (SI, SO, IO0, and IO1):</b></p> <p>This device supports standard SPI, Dual SPI, and Quad SPI operation. Standard SPI instructions use the unidirectional SI (Serial Input) pin to write instructions, addresses, or data to the device on the rising edge of the Serial Clock (SCK). Standard SPI also uses the unidirectional SO (Serial Output) to read data or status from the device on the falling edge of the serial clock (SCK).</p> <p>In Dual and Quad SPI mode, SI and SO become bidirectional IO pins to write instructions, addresses or data to the device on the rising edge of the Serial Clock (SCK) and read data or status from the device on the falling edge of SCK. Quad SPI instructions use the WP# and HOLD# pins as IO2 and IO3 respectively.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| WP# (IO2)                         | INPUT/OUTPUT | <p><b>Write Protect/Serial Data IO (IO2):</b> The WP# pin protects the Status Register from being written in conjunction with the SRWD bit. When the SRWD is set to "1" and the WP# is pulled low, the Status Register bits (SRWD, QE, BP3, BP2, BP1, BP0) are write-protected and vice-versa for WP# high. When the SRWD is set to "0", the Status Register is not write-protected regardless of WP# state.</p> <p>When the QE bit is set to "1", the WP# pin (Write Protect) function is not available since this pin is used for IO2.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| HOLD# (IO3)<br>or<br>RESET# (IO3) | INPUT/OUTPUT | <p><b>HOLD# or RESET#/Serial Data IO (IO3):</b> When the QE bit of Status Register is set to "1", HOLD# pin or RESET# is not available since it becomes IO3.</p> <p><b>Most packages except for 16-pin SOIC and 24-ball BGA:</b></p> <p>When QE=0, the pin acts as HOLD# or RESET# and either one can be selected by the P7 bit setting in Read Register. HOLD# will be selected if P7=0 (Default) and RESET# will be selected if P7=1.</p> <p><b>16-pin SOIC and 24-ball BGA packages :</b></p> <ul style="list-style-type: none"> <li>- When QE=0 and Dedicated RESET# is Enabled (Default), the pin acts as HOLD# regardless of the P7 bit setting in Read Register.</li> <li>- When QE=0 and Dedicated RESET# is Disabled, the pin acts as HOLD# or RESET# and either one can be selected by the P7 bit setting in Read Register. HOLD# will be selected if P7=0 (Default) and RESET# will be selected if P7=1.</li> </ul> <p>The HOLD# pin allows the device to be paused while it is selected. It pauses serial communication by the master device without resetting the serial sequence. The HOLD# pin is active low. When HOLD# is in a low state and CE# is low, the SO pin will be at high impedance. Device operation can resume when HOLD# pin is brought to a high state.</p> |

| SYMBOL | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET# | INPUT  | <p><b>RESET#:</b> This dedicated RESET# is available in 16-pin SOIC and 24-ball BGA packages.</p> <p>The RESET# pin is a hardware RESET signal. When RESET# is driven HIGH, the memory is in the normal operating mode. When RESET# is driven LOW, the memory enters reset mode and output is High-Z. If RESET# is driven LOW while an internal WRITE, PROGRAM, or ERASE operation is in progress, data may be lost.</p> <p>Dedicated RESET# function can be Disabled when bit 0 of Function Register = 1. It has an internal pull-up resistor and may be left floating if not used.</p> |

| SCK    | INPUT  | <b>Serial Data Clock:</b> Synchronized Clock for input and output timing operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Vcc    | POWER  | <b>Power:</b> Device Core Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| GND    | GROUND | <b>Ground:</b> Connect to ground when referenced to Vcc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| NC     | Unused | <b>NC:</b> Pins labeled "NC" stand for "No Connect" and should be left uncommitted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

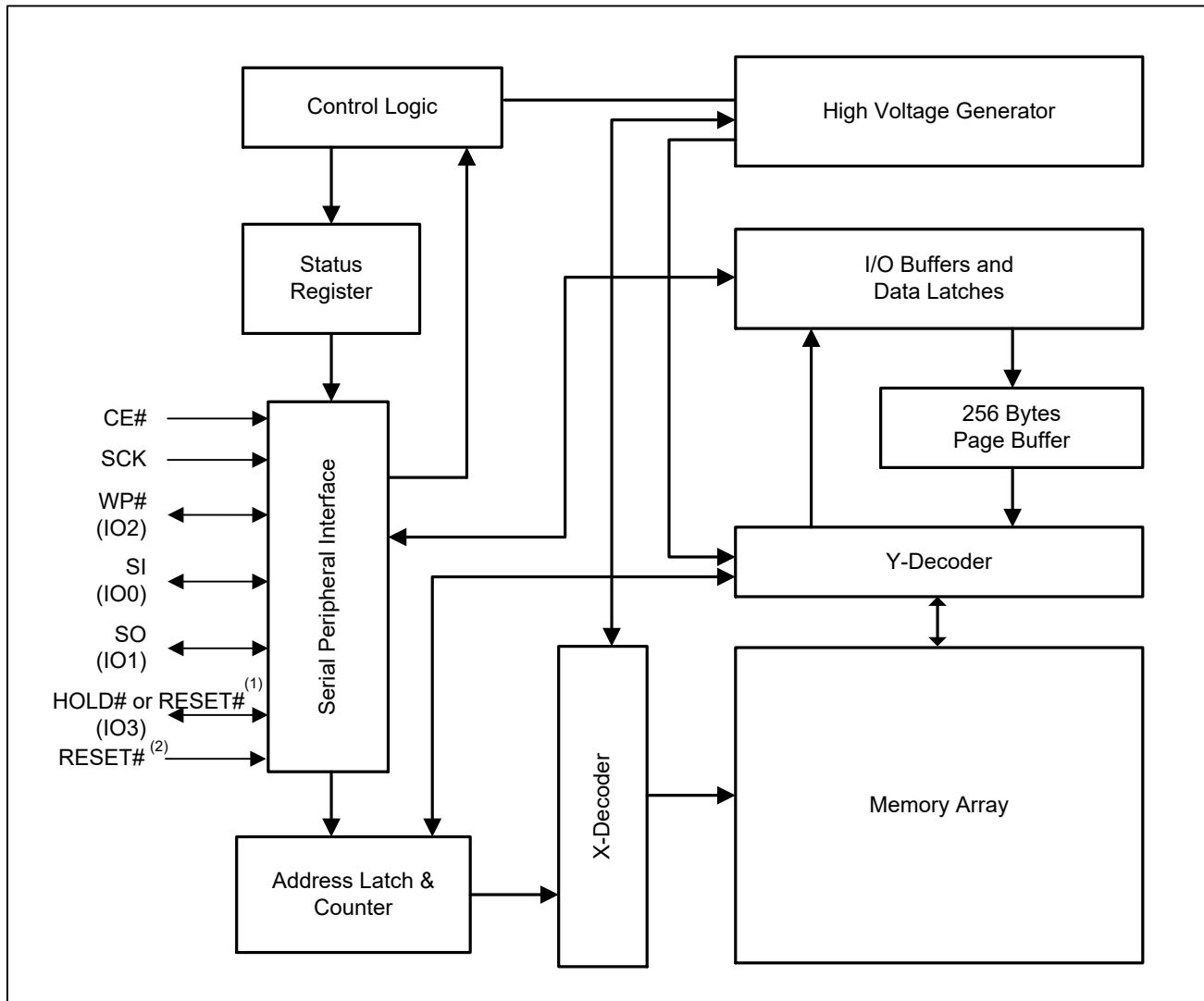

## 3. BLOCK DIAGRAM

## Note:

1: In case of 16-pin SOIC or 24-ball TFBGA, when QE=0 and Dedicated RESET# is Disabled, the pin acts as HOLD# or RESET# and either one can be selected by the P7 bit setting in Read Register. HOLD# will be selected if P7=0 (Default) and RESET# will be selected if P7=1.

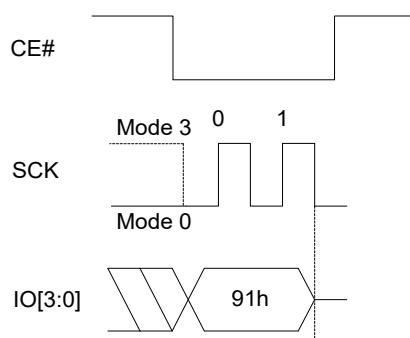

#### 4. SPI MODES DESCRIPTION

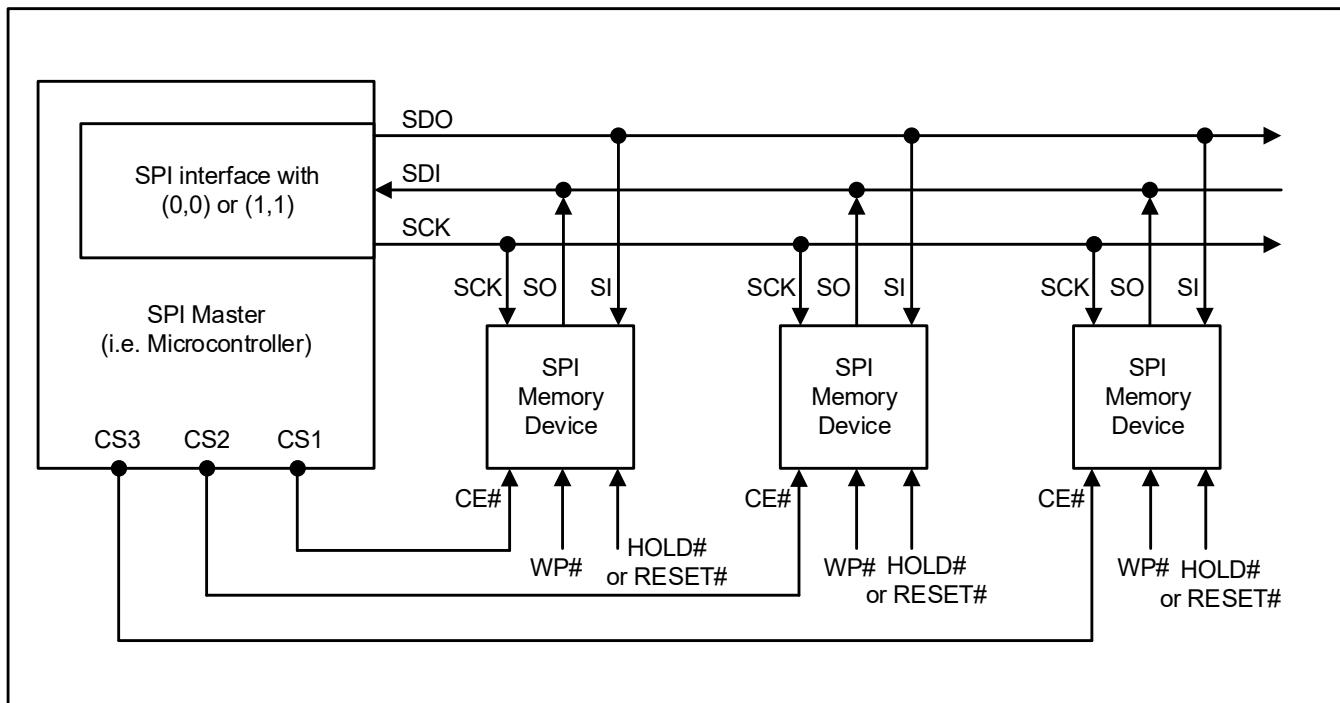

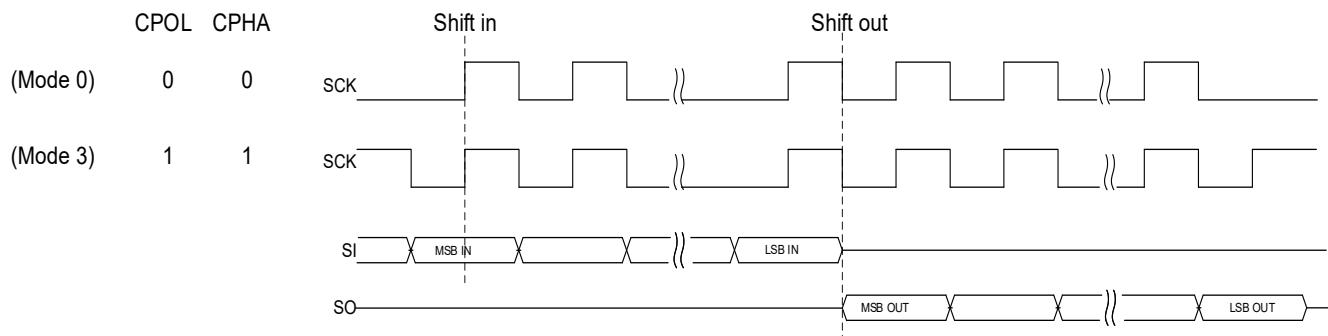

Multiple IS25LP064D devices or multiple IS25WP064D devices can be connected on the SPI serial bus and controlled by a SPI Master, i.e. microcontroller, as shown in Figure 4.1. The devices support either of two SPI modes:

Mode 0 (0, 0)

Mode 3 (1, 1)

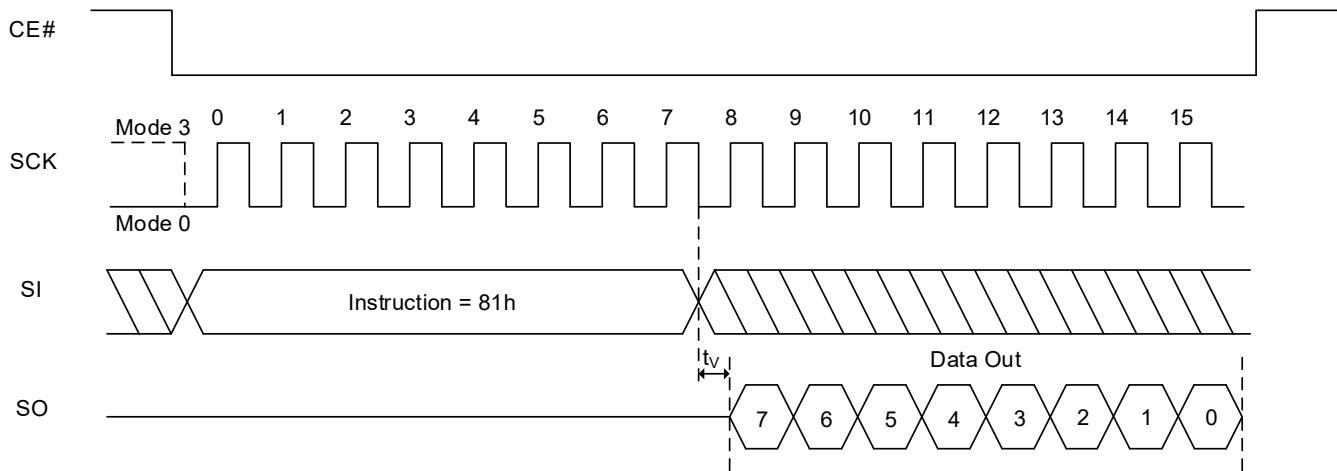

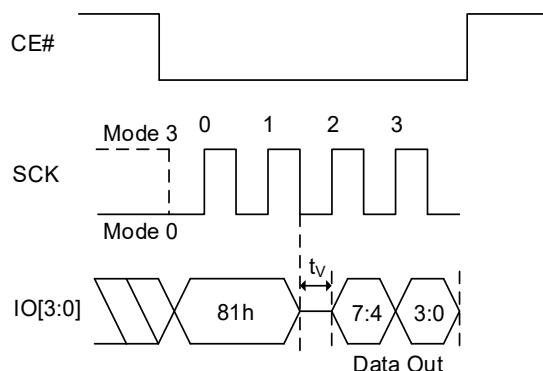

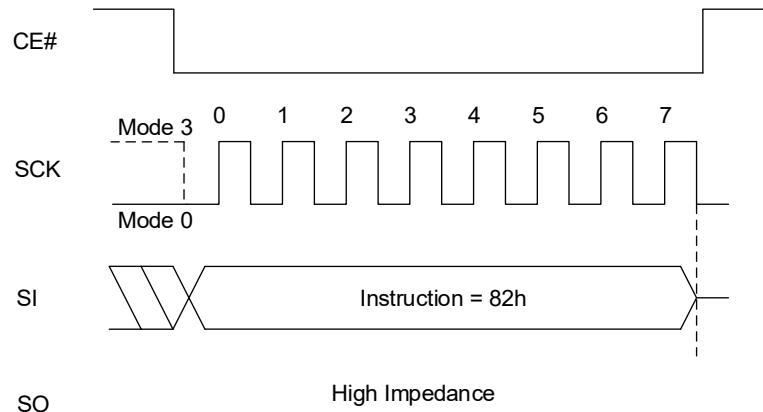

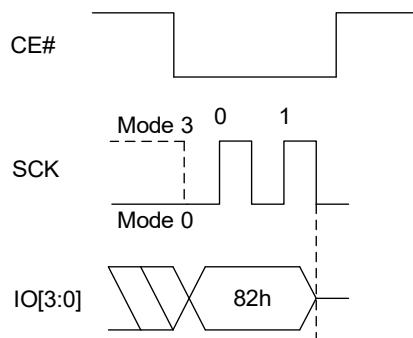

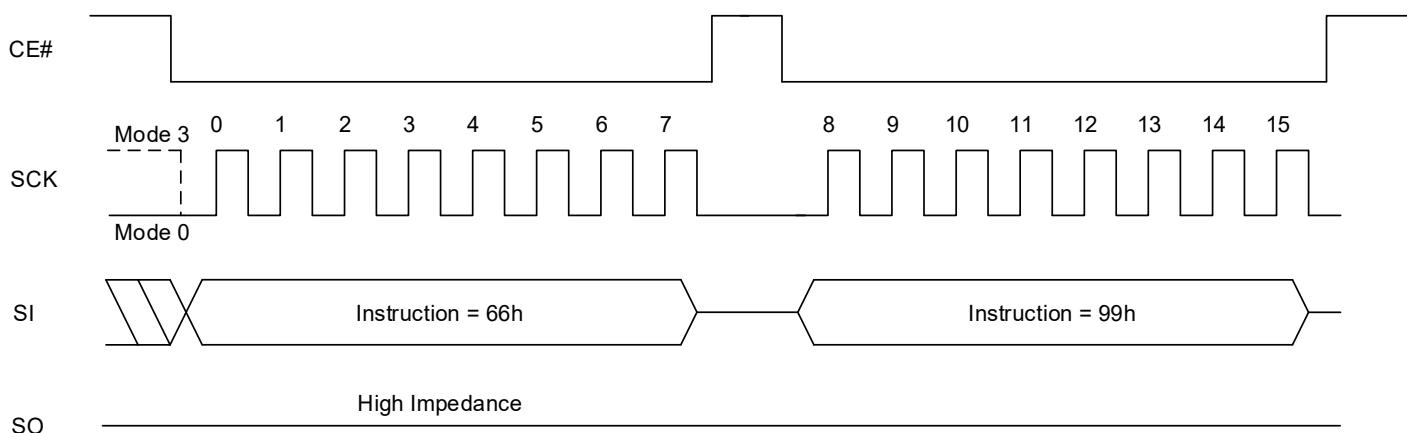

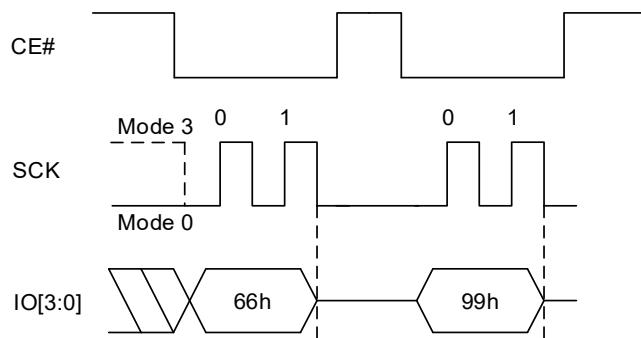

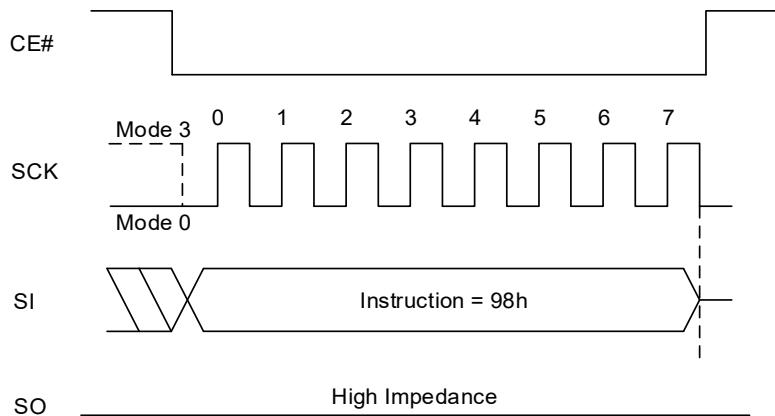

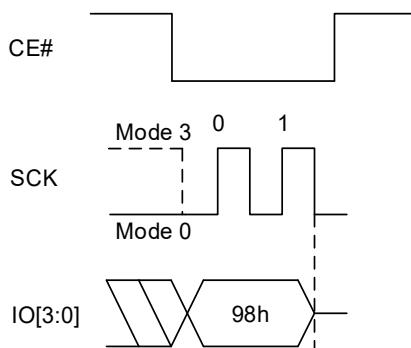

The difference between these two modes is the clock polarity. When the SPI master is in stand-by mode, the serial clock remains at "0" (SCK = 0) for Mode 0 and the clock remains at "1" (SCK = 1) for Mode 3. Please refer to Figure 4.2 and Figure 4.3 for SPI and QPI mode. In both modes, the input data is latched on the rising edge of Serial Clock (SCK), and the output data is available from the falling edge of SCK.

**Figure 4.1 Connection Diagram among SPI Master and SPI Slaves (Memory Devices)**

**Notes:**

1. In case of 16-pin SOIC and 24-ball TFBGA, dedicated RESET# is supported.

2. SI and SO pins become bidirectional IO0 and IO1 respectively during Dual I/O mode and SI, SO, WP#, and HOLD# pins become bidirectional IO0, IO1, IO2, and IO3 respectively during Quad I/O or QPI mode.

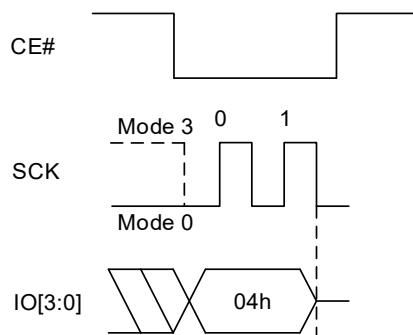

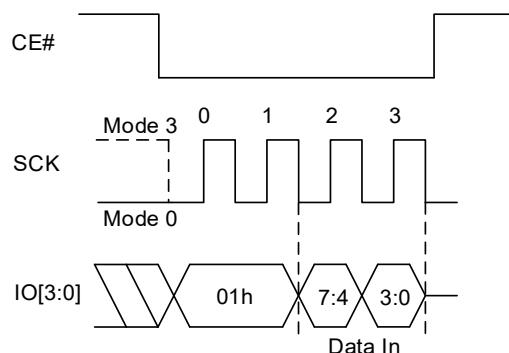

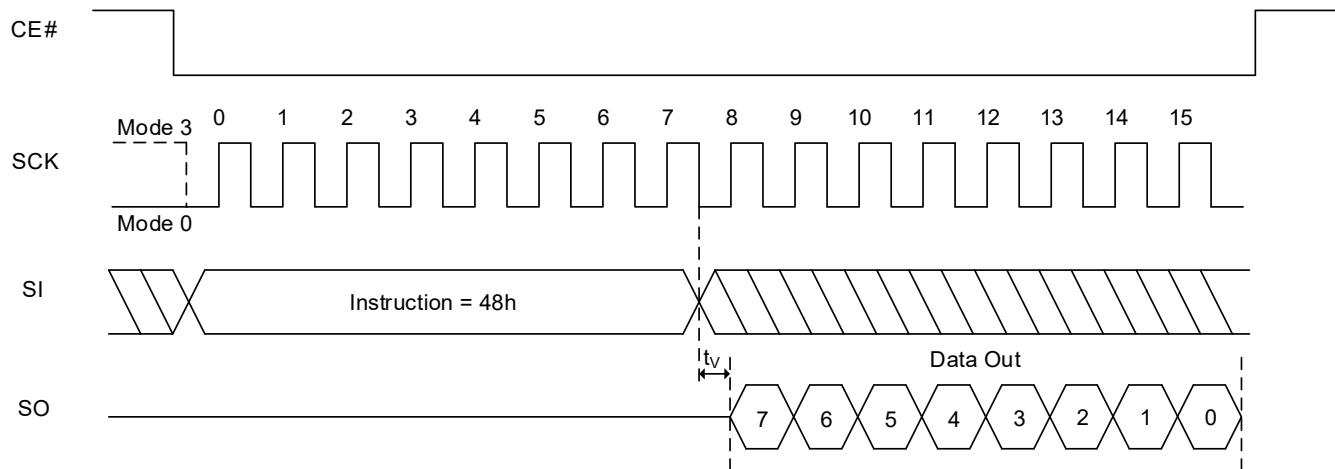

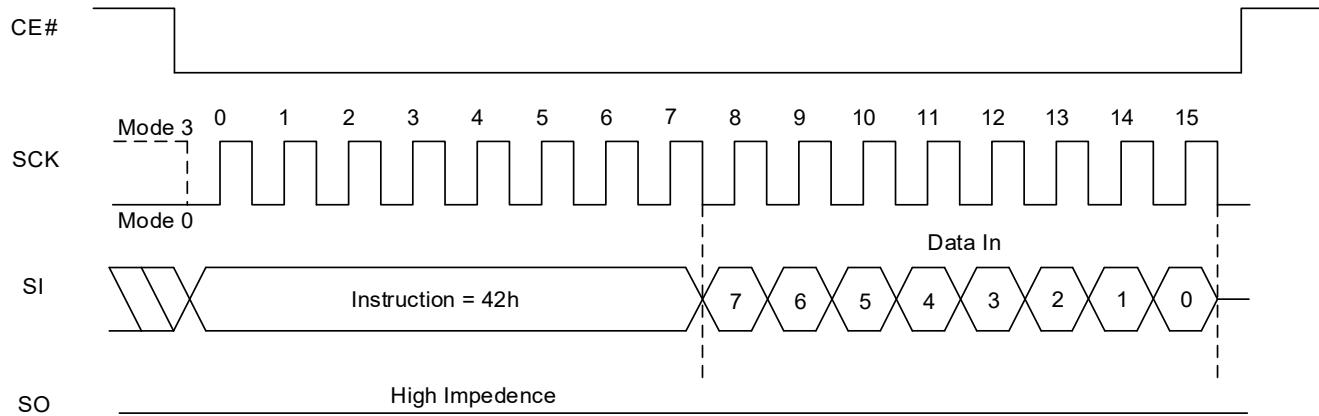

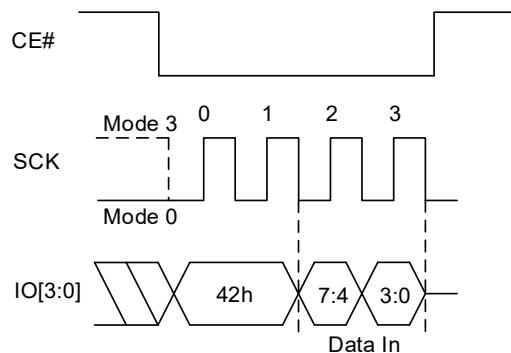

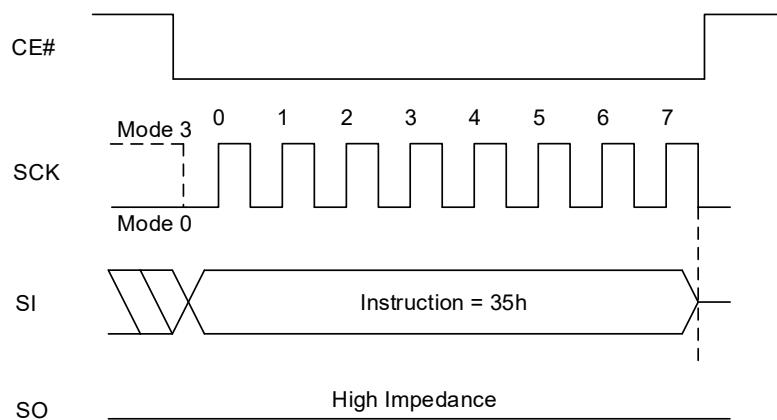

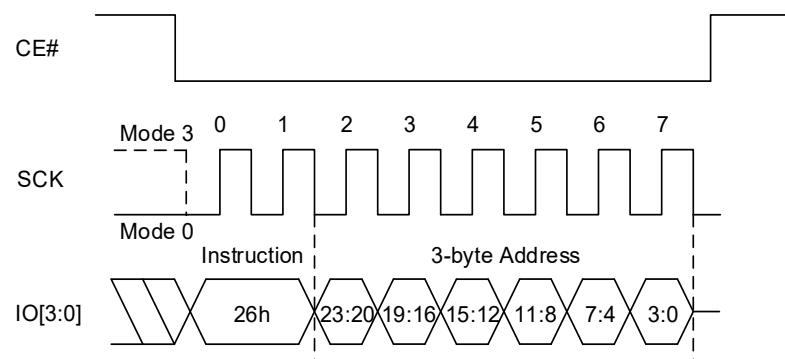

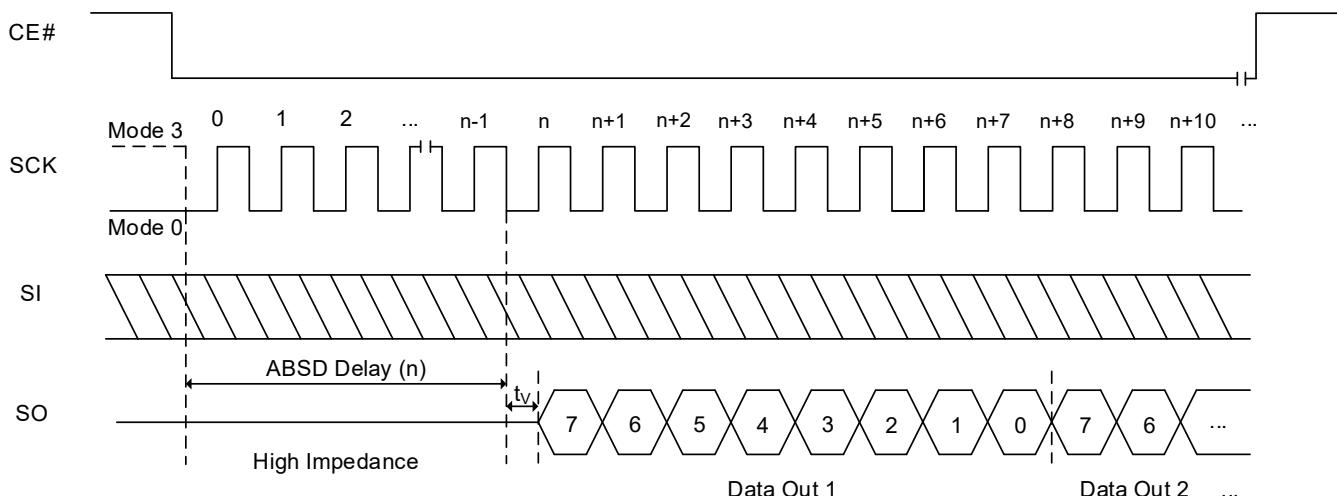

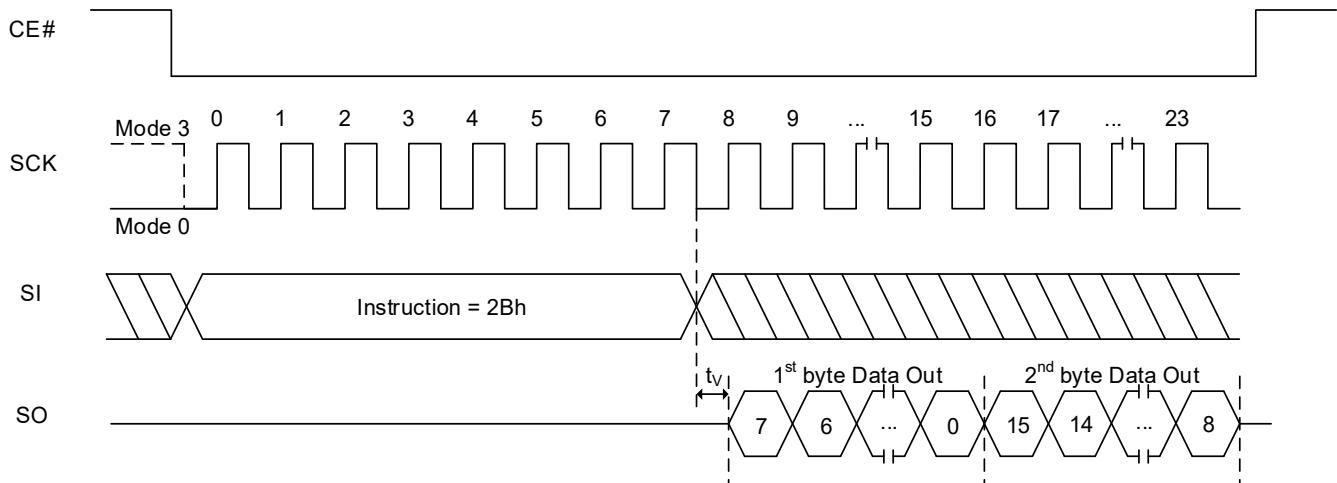

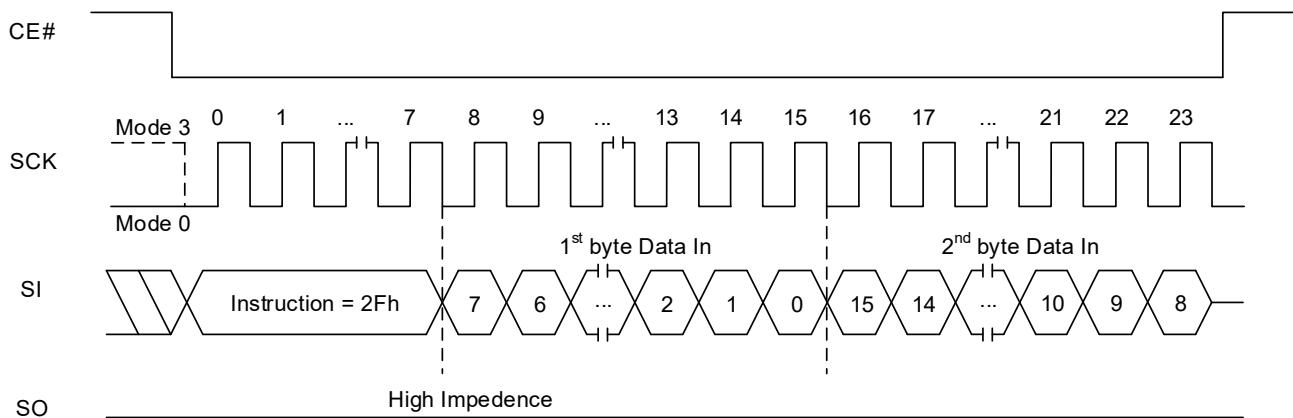

**Figure 4.2 SPI Mode Support**

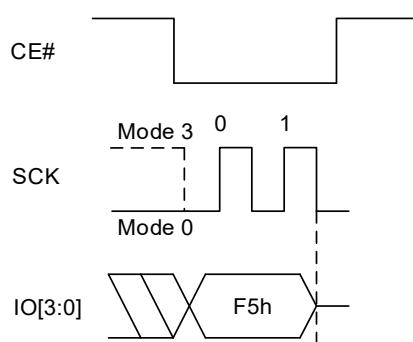

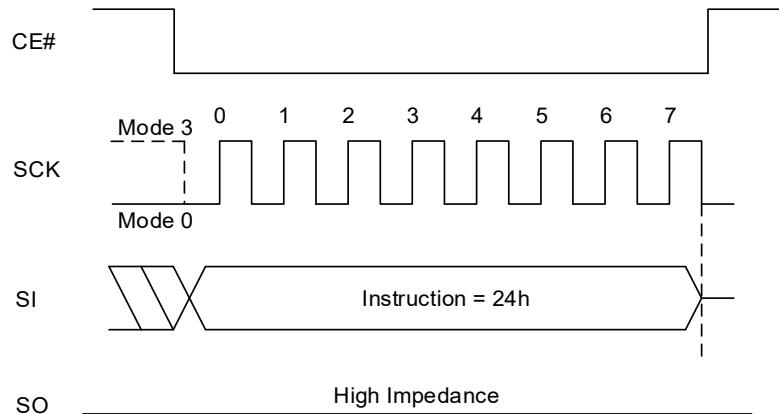

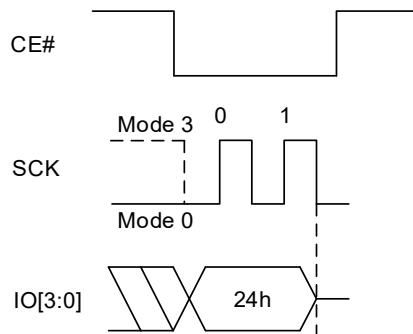

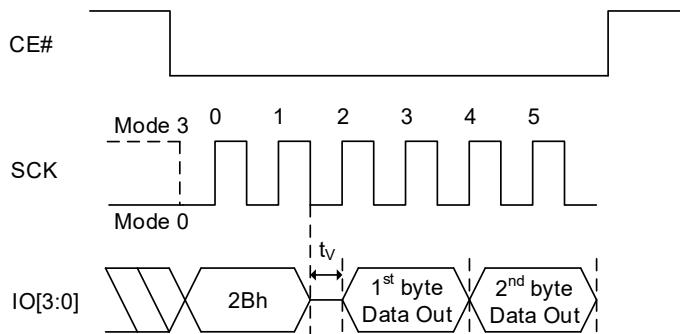

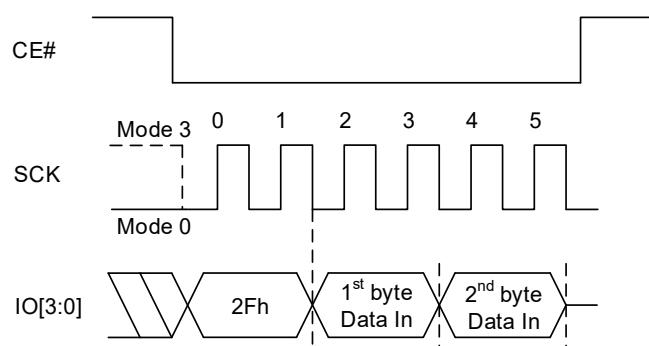

**Figure 4.3 QPI Mode Support**

**Note1: MSB (Most Significant Bit)**

## 5. SYSTEM CONFIGURATION

The memory array is divided into uniform 4 Kbyte sectors or uniform 32/64 Kbyte blocks (a block consists of eight/sixteen adjacent sectors respectively).

Table 5.1 illustrates the memory map of the device. The Status Register controls how the memory is protected.

### 5.1 BLOCK/SECTOR ADDRESSES

**Table 5.1 Block/Sector Addresses**

| Memory Density | Block No. (64Kbyte) | Block No. (32Kbyte) | Sector No.  | Sector Size (Kbytes) | Address Range     |

|----------------|---------------------|---------------------|-------------|----------------------|-------------------|

| 64Mb           | Block 0             | Block 0             | Sector 0    | 4                    | 000000h – 000FFFh |

|                |                     |                     | :           | :                    | :                 |

|                |                     | Block 1             | :           | :                    | :                 |

|                |                     |                     | Sector 15   | 4                    | 00F000h - 00FFFFh |

|                | Block 1             | Block 2             | Sector 16   | 4                    | 010000h – 010FFFh |

|                |                     |                     | :           | :                    | :                 |

|                |                     | Block 3             | :           | :                    | :                 |

|                |                     |                     | Sector 31   | 4                    | 01F000h - 01FFFFh |

|                | Block 2             | Block 4             | Sector 32   | 4                    | 020000h – 020FFFh |

|                |                     |                     | :           | :                    | :                 |

|                |                     | Block 5             | :           | :                    | :                 |

|                |                     |                     | Sector 47   | 4                    | 02F000h – 02FFFFh |

|                | :                   | :                   | :           | :                    | :                 |

|                | Block 63            | Block 126           | Sector 1008 | 4                    | 3F0000h – 3F0FFFh |

|                |                     |                     | :           | :                    | :                 |

|                |                     | Block 127           | :           | :                    | :                 |

|                |                     |                     | Sector 1023 | 4                    | 3FF000h – 3FFFFFh |

|                | :                   | :                   | :           | :                    | :                 |

|                | Block 127           | Block 254           | Sector 2032 | 4                    | 7F0000h – 7F0FFFh |

|                |                     |                     | :           | :                    | :                 |

|                |                     | Block 255           | :           | :                    | :                 |

|                |                     |                     | Sector 2047 | 4                    | 7FF000h – 7FFFFFh |

## 5.2 SERIAL FLASH DISCOVERABLE PARAMETERS

The Serial Flash Discoverable Parameters (SFDP) standard defines the structure of the SFDP database within the memory device. SFDP is the standard of JEDEC JESD216.

The JEDEC-defined header with Parameter ID FF00h and related Basic Parameter Table is mandatory. Additional parameter headers and tables are optional.

**Table 5.2 Signature and Parameter Identification Data Values**

| Description                               |       | Address (Byte) | Address (Bit) | Data |

|-------------------------------------------|-------|----------------|---------------|------|

| SFDP Signature                            |       | 00h            | 7:0           | 53h  |

|                                           |       | 01h            | 15:8          | 46h  |

|                                           |       | 02h            | 23:16         | 44h  |

|                                           |       | 03h            | 31:24         | 50h  |

| SFDP Revision                             | Minor | 04h            | 7:0           | 06h  |

|                                           | Major | 05h            | 15:8          | 01h  |

| Number of Parameter Headers (NPH)         |       | 06h            | 23:16         | 00h  |

| Unused                                    |       | 07h            | 31:24         | FFh  |

| Parameter ID LSB                          |       | 08h            | 7:0           | 00h  |

| Parameter Minor Revision                  |       | 09h            | 15:8          | 06h  |

| Parameter Major Revision                  |       | 0Ah            | 23:16         | 01h  |

| Parameter Table Length (in DWPRDs)        |       | 0Bh            | 31:24         | 10h  |

| Basic Flash Parameter Table Pointer (PTP) |       | 0Ch            | 7:0           | 30h  |

|                                           |       | 0Dh            | 15:8          | 00h  |

|                                           |       | 0Eh            | 23:16         | 00h  |

| Parameter ID MSB                          |       | 0Fh            | 31:24         | FFh  |

**Table 5.3 JEDEC Basic Flash Parameter Table**

| Description                                                             | Address (Byte) | Address (Bit) | Data   |

|-------------------------------------------------------------------------|----------------|---------------|--------|

| Minimum Sector Erase Sizes                                              | 30h            | 1:0           | 01b    |

| Write Granularity                                                       |                | 2             | 1b     |

| Volatile Status Register Block Protect bits                             |                | 3             | 0b     |

| Write Enable Instruction Select for writing to Volatile Status Register |                | 4             | 0b     |

| Unused                                                                  |                | 7:5           | 111b   |

| 4KB Erase Instruction                                                   | 31h            | 15:8          | 20h    |

| Supports (1-1-2) Fast Read                                              | 32h            | 16            | 1b     |

| Address Bytes                                                           |                | 18:17         | 00b    |

| Supports Double Transfer Rate (DTR) Clocking                            |                | 19            | 1b     |

| Supports (1-2-2) Fast Read                                              |                | 20            | 1b     |

| Supports (1-4-4) Fast Read                                              |                | 21            | 1b     |

| Supports (1-1-4) Fast Read                                              |                | 22            | 1b     |

| Unused                                                                  |                | 23            | 1b     |

| Reserved                                                                | 33h            | 31:24         | FFh    |

| Flash memory Density (bits)                                             | 34h            | 7:0           | FFh    |

|                                                                         | 35h            | 15:8          | FFh    |

|                                                                         | 36h            | 23:16         | FFh    |

|                                                                         | 37h            | 31:24         | 03h    |

| 1-4-4 Fast Read Wait Cycle Count                                        | 38h            | 4:0           | 00100b |

| 1-4-4 Fast Read Mode bit Cycle Count                                    |                | 7:5           | 010b   |

| 1-4-4 Fast Read Instruction                                             | 39h            | 15:8          | EBh    |

| 1-1-4 Fast Read Wait Cycle Count                                        | 3Ah            | 20:16         | 01000b |

| 1-1-4 Fast Read Mode bit Cycle Count                                    |                | 23:21         | 000b   |

| 1-1-4 Fast Read Instruction                                             | 3Bh            | 31:24         | 6Bh    |

| 1-1-2 Fast Read Wait Cycle Count                                        | 3Ch            | 4:0           | 01000b |

| 1-1-2 Fast Read Mode bit Cycle Count                                    |                | 7:5           | 000b   |

| 1-1-2 Fast Read Instruction                                             | 3Dh            | 15:8          | 3Bh    |

| 1-2-2 Fast Read Wait Cycle Count                                        | 3Eh            | 20:16         | 00000b |

| 1-2-2 Fast Read Mode bit Cycle Count                                    |                | 23:21         | 100b   |

| 1-2-2 Fast Read Instruction                                             | 3Fh            | 31:24         | BBh    |

**Table 5.3 JEDEC Basic Flash Parameter Table (Continued)**

| Description                                              | Address<br>(Byte) | Address<br>(Bit) | Data    |

|----------------------------------------------------------|-------------------|------------------|---------|

| Supports (2-2-2) Fast Read                               | 40h               | 0                | 0       |

| Reserved                                                 |                   | 3:1              | 111b    |

| Supports (4-4-4) Fast Read                               |                   | 4                | 1       |

| Reserved                                                 |                   | 7:5              | 111b    |

| Reserved                                                 | 43:41h            | 31:8             | FFFFFFh |

| Reserved                                                 | 45:44h            | 15:0             | FFFFh   |

| 2-2-2 Fast Read Wait Cycle Count                         | 46h               | 20:16            | 00000b  |

| 2-2-2 Fast Read Mode bit Cycle Count                     |                   | 23:21            | 000b    |

| 2-2-2 Fast Read Instruction                              | 47h               | 31:24            | FFh     |

| Reserved                                                 | 49:48h            | 15:0             | FFFFh   |

| 4-4-4 Fast Read Wait Cycle Count                         | 4Ah               | 20:16            | 00100b  |

| 4-4-4 Fast Read Mode bit Cycle Count                     |                   | 23:21            | 010b    |

| 4-4-4 Fast Read Instruction                              | 4Bh               | 31:24            | EBh     |

| Erase Type 1 Size (4KB)                                  | 4Ch               | 7:0              | 0Ch     |

| Erase Type 1 Instruction                                 | 4Dh               | 15:8             | 20h     |

| Erase Type 2 Size (32KB)                                 | 4Eh               | 23:16            | 0Fh     |

| Erase Type 2 Instruction                                 | 4Fh               | 31:24            | 52h     |

| Erase Type 3 Size (64KB)                                 | 50h               | 7:0              | 10h     |

| Erase Type 3 Instruction                                 | 51h               | 15:8             | D8h     |

| Erase Type 4 Size (256KB)                                | 52h               | 23:16            | 00h     |

| Erase Type 4 Instruction                                 | 53h               | 31:24            | FFh     |

| Multiplier from typical erase time to maximum erase time | 57:54h            | 3:0              | 0010b   |

| Sector Type 1 ERASE time (typ)                           |                   | 8:4              | 00110b  |

| Sector Type 2 ERASE time (typ)                           |                   | 10:9             | 01b     |

| Sector Type 3 ERASE time (typ)                           |                   | 15:11            | 01000b  |

| Sector Type 4 ERASE time (typ)                           |                   | 17:16            | 01b     |

|                                                          |                   | 22:18            | 01010b  |

|                                                          |                   | 24:23            | 01b     |

|                                                          |                   | 29:25            | 00000b  |

|                                                          |                   | 31:30            | 00b     |

**Table 5.3 JEDEC Basic Flash Parameter Table (Continued)**

| Description                                                              | Address<br>(Byte) | Address<br>(Bit) | Data    |

|--------------------------------------------------------------------------|-------------------|------------------|---------|

| Multiplier from typical time to maximum time for page or byte<br>PROGRAM | 58h               | 3:0              | 0010b   |

| Page size                                                                |                   | 7:4              | 1000b   |

| Page Program Typical time                                                | 5Ah:59h           | 12:8             | 11000b  |

| Byte Program Typical time, first byte                                    |                   | 13               | 0b      |

| Byte Program Typical time, additional byte                               |                   | 17:14            | 0111b   |

| Byte Program Typical time, additional byte                               |                   | 18               | 0b      |

| Byte Program Typical time, additional byte                               |                   | 22:19            | 0000b   |

| Byte Program Typical time, additional byte                               |                   | 23               | 0b      |

| Chip Erase, Typical time                                                 | 5Bh               | 28:24            | 00100b  |

| Units                                                                    |                   |                  |         |

| Reserved                                                                 |                   | 30:29            | 10b     |

| Prohibited Operations During Program Suspend                             |                   | 31               | 1b      |

| Prohibited Operations During Erase Suspend                               | 5Ch               | 3:0              | 1100b   |

| Reserved                                                                 |                   | 7:4              | 1110b   |

| Program Resume to Suspend Interval                                       | 5Eh:5Dh           | 8                | 1b      |

| Suspend in-progress program max latency                                  |                   | 12:9             | 0110b   |

| Erase Resume to Suspend Interval                                         |                   | 17:13            | 01100b  |

| Suspend in-progress erase max latency                                    |                   | 19:18            | 10b     |

| Suspend /Resume supported                                                |                   | 23:20            | 0110b   |

| Program Resume Instruction                                               |                   | 28:24            | 01100b  |

| Program Suspend Instruction                                              | 5Fh               | 30:29            | 10b     |

| Resume Instruction                                                       |                   | 31               | 0b      |

| Suspend Instruction                                                      |                   | 60h              | 7:0     |

| Reserved                                                                 | 64h               | 61h              | 15:8    |

| Status Register Polling Device Busy                                      |                   | 62h              | 23:16   |

|                                                                          |                   | 63h              | 31:24   |

|                                                                          |                   | 64h              | 7:2     |

|                                                                          |                   |                  | 111101b |

**Table 5.3 JEDEC Basic Flash Parameter Table (Continued)**

| Description                                                                                    |      | Address<br>(Byte) | Address<br>(Bit) | Data        |

|------------------------------------------------------------------------------------------------|------|-------------------|------------------|-------------|

| Exit Deep Power-down to next operation delay                                                   | 3V   | 67h:65h           | 12:8             | 00010b      |

|                                                                                                | 1.8V |                   |                  | 00100b      |

| Exit Deep Power-down to next operation delay Units                                             |      |                   | 14:13            | 01b         |

| Exit Deep Power-down Instruction                                                               |      |                   | 22:15            | ABh         |

| Enter Deep Power-down Instruction                                                              |      |                   | 30:23            | B9h         |

| Deep Power-down Supported                                                                      |      |                   | 31               | 0b          |

| 4-4-4 mode disable sequences (QPIDI)                                                           |      | 69h:68h           | 3:0              | 1010b       |

| 4-4-4 mode enable sequences (QPIEN)                                                            |      |                   | 8:4              | 00100b      |

| 0-4-4 Mode Supported                                                                           |      |                   | 9                | 1b          |

| 0-4-4 Mode Exit Method                                                                         |      |                   | 15:10            | 110000b     |

| 0-4-4 Mode Entry Method:                                                                       |      | 6Ah               | 19:16            | 1100b       |

| Quad Enable Requirements (QER)                                                                 |      |                   | 22:20            | 010b        |

| Hold or RESET Disable                                                                          |      |                   | 23               | 0b          |

| Reserved                                                                                       |      | 6Bh               | 31:24            | FFh         |

| Volatile or Non-Volatile Register and Write Enable (WREN)<br>Instruction for Status Register 1 |      | 6Ch               | 6:0              | 1100001b    |

| Reserved                                                                                       |      |                   | 7                | 1b          |

| Soft Reset and Rescue Sequence Support                                                         |      | 6Eh:6Dh           | 13:8             | 110000b     |

| Exit 4-Byte Addressing                                                                         |      |                   | 23:14            | 1100000000b |

| Enter 4-Byte Addressing                                                                        |      | 6Fh               | 31:24            | 10000000b   |

## 6. REGISTERS

The device has various sets of Registers: Status, Function, Read, Extended Read and Autoboot. When the register is read continuously, the same data is output repeatedly until CE# goes HIGH.

### 6.1 STATUS REGISTER

Status Register Format and Status Register Bit Definitions are described in Tables 6.1 & 6.2. During power up sequence, volatile register will be loaded with the value of non-volatile value.

**Table 6.1 Status Register Format**

|         | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

|         | SRWD  | QE    | BP3   | BP2   | BP1   | BP0   | WEL   | WIP   |

| Default | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

**Table 6.2 Status Register Bit Definition**

| Bit   | Name | Definition                                                                                                                                                                               | Read-/Write      | Type         |

|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|

| Bit 0 | WIP  | Write In Progress Bit:<br>"0" indicates the device is ready (default)<br>"1" indicates a write cycle is in progress and the device is busy                                               | R                | Volatile     |

| Bit 1 | WEL  | Write Enable Latch:<br>"0" indicates the device is not write enabled (default)<br>"1" indicates the device is write enabled                                                              | R/W <sup>1</sup> | Volatile     |

| Bit 2 | BP0  | Block Protection Bit: (See Tables 6.4 for details)<br>"0" indicates the specific blocks are not write-protected (default)<br>"1" indicates the specific blocks are write-protected       | R/W              | Non-Volatile |

| Bit 3 | BP1  |                                                                                                                                                                                          |                  |              |

| Bit 4 | BP2  |                                                                                                                                                                                          |                  |              |

| Bit 5 | BP3  |                                                                                                                                                                                          |                  |              |

| Bit 6 | QE   | Quad Enable bit:<br>"0" indicates the Quad output function disable (default)<br>"1" indicates the Quad output function enable                                                            | R/W              | Non-Volatile |

| Bit 7 | SRWD | Status Register Write Disable: (See Table 7.1 for details)<br>"0" indicates the Status Register is not write-protected (default)<br>"1" indicates the Status Register is write-protected | R/W              | Non-Volatile |

**Note:** WEL bit can be written by WREN and WRDI commands, but cannot be written by WRSR and VSRWE command.

The BP0, BP1, BP2, BP3, QE, and SRWD are non-volatile and volatile memory cells that can be written by a Write Status Register (WRSR) instruction. The default value of the BP0, BP1, BP2, BP3, QE, and SRWD bits were set to "0" at factory.

The function of Status Register bits are described as follows:

**WIP bit:** Write In Progress (WIP) is read-only, and can be used to detect the progress or completion of a Program, Erase, Write/Set Non-Volatile/OTP Register, or Gang Sector/Block Lock/Unlock operation. WIP is set to "1" (busy state) when the device is executing the operation. During this time the device will ignore further instructions except for Read Status/Extended Read Register and Software/Hardware Reset instructions. In addition to the instructions, an Erase/Program Suspend instruction also can be executed during a Program or Erase operation. When an operation has completed, WIP is cleared to "0" (ready state) whether the operation is successful or not and the device is ready for further instructions.

**WEL bit:** Write Enable Latch (WEL) bit indicates the status of the internal write enable latch. When WEL bit is “0”, the internal write enable latch is disabled and the Write operations described in Table 6.3 are inhibited. When WEL bit is “1”, the Write operations are allowed. WEL bit is set by a Write Enable (WREN, 06h) instruction. Most of Write Non-Volatile/Volatile Register, Program and Erase instruction must be preceded by a WREN instruction.

WEL bit can be reset by a Write Disable (WRDI) instruction. It will automatically reset after the completion of any Write Non-Volatile Register, Program and Erase operation.

Table 6.3 Instructions requiring WREN instruction ahead

| Instructions must be preceded by the WREN instruction |          |                                             |

|-------------------------------------------------------|----------|---------------------------------------------|

| Name                                                  | Hex Code | Operation                                   |

| PP                                                    | 02h      | Serial Input Page Program                   |

| PPQ                                                   | 32h/38h  | Quad Input Page Program                     |

| SER                                                   | D7h/20h  | Sector Erase 4KB                            |

| BER32 (32KB)                                          | 52h      | Block Erase 32KB                            |

| BER64 (64KB)                                          | D8h      | Block Erase 64KB                            |

| CER                                                   | C7h/60h  | Chip Erase                                  |

| <b>WRSR</b>                                           | 01h      | Write Status Register                       |

| WRFR                                                  | 42h      | Write Function Register                     |

| SRPNV                                                 | 65h      | Set Read Parameters (Non-Volatile)          |

| <b>SRPV<sup>(1)</sup></b>                             | 63h      | Set Read Parameters (Volatile)              |

| SERPNV                                                | 85h      | Set Extended Read Parameters (Non-Volatile) |

| SERPV                                                 | 83h      | Set Extended Read Parameters (Volatile)     |

| IRER                                                  | 64h      | Erase Information Row                       |

| IRP                                                   | 62h      | Program Information Row                     |

| WRABR                                                 | 15h      | Write AutoBoot Register                     |

| WRDYB                                                 | FBh      | Write DYB Register                          |

| PGPPB                                                 | FDh      | Write PPB                                   |

| ERPPB                                                 | E4h      | Erase PPB                                   |

| PGASP                                                 | 2Fh      | Program ASP                                 |

| WRPLB                                                 | A6h      | Write PPB Lock Bit                          |

| SFRZ                                                  | 91h      | Set FREEZE bit                              |

| GBLK                                                  | 7Eh      | GANG Sector/Block Lock                      |

| GBUN                                                  | 98h      | GANG Sector/Block Unlock                    |

| PGPWD                                                 | E8h      | Program Password                            |

**Notes:**

1. C0h command for SRPV operation does not require WREN command ahead.

**BP3, BP2, BP1, BP0 bits:** The Block Protection (BP3, BP2, BP1 and BP0) bits are used to define the portion of the memory area to be protected. Refer to Table 6.4 for the Block Write Protection (BP) bit settings. When a defined combination of BP3, BP2, BP1 and BP0 bits are set, the corresponding memory area is protected. Any program or erase operation to that area will be inhibited.

**Note:** A Chip Erase (CER) instruction will be ignored unless all the Block Protection Bits are “0”s.

**SRWD bit:** The Status Register Write Disable (SRWD) bit operates in conjunction with the Write Protection (WP#) signal to provide a Hardware Protection Mode. When the SRWD is set to “0”, the Status Register is not write-protected. When the SRWD is set to “1” and the WP# is pulled low (V<sub>IL</sub>), the bits of Status Register (SRWD, QE, BP3, BP2, BP1, BP0) become read-only, and a WRSR instruction will be ignored. If the SRWD is set to “1” and WP# is pulled high (V<sub>IH</sub>), the Status Register can be changed by a WRSR instruction.

**QE bit:** The Quad Enable (QE) is a non-volatile bit in the Status Register that allows quad operation. When the QE bit is set to “0”, the pin WP# and HOLD#/RESET# are enabled. When the QE bit is set to “1”, the IO2 and IO3 pins are enabled.

**WARNING:** The QE bit must be set to “0” if WP# or HOLD#/RESET# pin (or ball) is tied directly to the power supply.

**Table 6.4 Block (64Kbyte) assignment by Block Write Protect (BP) Bits**

| Status Register Bits |     |     |     | Protected Memory Area (64Mb, 128Blocks)    |                                            |

|----------------------|-----|-----|-----|--------------------------------------------|--------------------------------------------|

| BP3                  | BP2 | BP1 | BP0 | TBS(T/B selection) = 0, Top area           | TBS(T/B selection) = 1, Bottom area        |

| 0                    | 0   | 0   | 0   | 0( None)                                   | 0( None)                                   |

| 0                    | 0   | 0   | 1   | 1(1 block : 127th)                         | 1(1 block : 0th)                           |

| 0                    | 0   | 1   | 0   | 2(2 blocks : 126th and 127th)              | 2(2 blocks : 0th and 1st)                  |

| 0                    | 0   | 1   | 1   | 3(4 blocks : 124th to 127th)               | 3(4 blocks : 0th to 3rd)                   |

| 0                    | 1   | 0   | 0   | 4(8 blocks : 120th to 127th)               | 4(8 blocks : 0th to 7th)                   |

| 0                    | 1   | 0   | 1   | 5(16 blocks : 112nd to 127th)              | 5(16 blocks : 0th to 15th)                 |

| 0                    | 1   | 1   | 0   | 6(32 blocks : 96th to 127th)               | 6(32 blocks : 0th to 31st)                 |

| 0                    | 1   | 1   | 1   | 7(64 blocks : 64th to 127th)               | 7(64 blocks : 0th to 63rd)                 |

| 1                    | x   | x   | x   | 8~15(128 blocks : 0th to 127th) All blocks | 8~15(128 blocks : 0th to 127th) All blocks |

| Status Register Bits |     |     |     | Byte Protected | Protected Memory Area (Optional BP Table <sup>(2)</sup> , 64Mb, 128Blocks) |                                                         |

|----------------------|-----|-----|-----|----------------|----------------------------------------------------------------------------|---------------------------------------------------------|

| BP3                  | BP2 | BP1 | BP0 |                | TBS(T/B selection) = 0, Top area                                           | TBS(T/B selection) = 1, Bottom area                     |

| 0                    | 0   | 0   | 0   | 0KB            | 0 ( None)                                                                  | 0 ( None)                                               |

| 0                    | 0   | 0   | 1   | 64KB           | 1 (1 block : 127 <sup>th</sup> )                                           | 1 (1 block : 0 <sup>th</sup> )                          |

| 0                    | 0   | 1   | 0   | 128KB          | 2 (2 blocks : 126 <sup>th</sup> and 127 <sup>th</sup> )                    | 2 (2 blocks : 0 <sup>th</sup> and 1 <sup>st</sup> )     |

| 0                    | 0   | 1   | 1   | 256KB          | 3 (4 blocks : 124 <sup>th</sup> to 127 <sup>th</sup> )                     | 3 (4 blocks : 0 <sup>th</sup> to 3 <sup>rd</sup> )      |

| 0                    | 1   | 0   | 0   | 512KB          | 4 (8 blocks : 120 <sup>th</sup> to 127 <sup>th</sup> )                     | 4 (8 blocks : 0 <sup>th</sup> to 7 <sup>th</sup> )      |

| 0                    | 1   | 0   | 1   | 1MB            | 5 (16 blocks : 112 <sup>nd</sup> to 127 <sup>th</sup> )                    | 5 (16 blocks : 0 <sup>th</sup> to 15 <sup>th</sup> )    |

| 0                    | 1   | 1   | 0   | 2MB            | 6 (32 blocks : 96 <sup>th</sup> to 127 <sup>th</sup> )                     | 6 (32 blocks : 0 <sup>th</sup> to 31 <sup>st</sup> )    |

| 0                    | 1   | 1   | 1   | 4MB            | 7 (64 blocks : 64 <sup>th</sup> to 127 <sup>th</sup> )                     | 7 (64 blocks : 0 <sup>th</sup> to 63 <sup>rd</sup> )    |

| 1                    | 0   | 0   | 0   | 6MB            | 8 (96 blocks : 32 <sup>nd</sup> to 127 <sup>th</sup> )                     | 8 (96 blocks : 0 <sup>th</sup> to 95 <sup>th</sup> )    |

| 1                    | 0   | 0   | 1   | 7MB            | 9 (112 blocks : 16 <sup>th</sup> to 127 <sup>th</sup> )                    | 9 (112 blocks : 0 <sup>th</sup> to 111 <sup>st</sup> )  |

| 1                    | 0   | 1   | 0   | 7680KB         | 10 (120 blocks : 8 <sup>th</sup> to 127 <sup>th</sup> )                    | 10 (120 blocks : 0 <sup>th</sup> to 119 <sup>th</sup> ) |

| 1                    | 0   | 1   | 1   | 7936KB         | 11 (124 blocks : 4 <sup>th</sup> to 127 <sup>th</sup> )                    | 11 (124 blocks : 0 <sup>th</sup> to 123 <sup>rd</sup> ) |

| 1                    | 1   | 0   | 0   | 8064KB         | 12 (126 blocks : 2 <sup>nd</sup> to 127 <sup>th</sup> )                    | 12 (126 blocks : 0 <sup>th</sup> to 125 <sup>th</sup> ) |

| 1                    | 1   | 0   | 1   | 8128KB         | 13 (127 blocks : 1 <sup>st</sup> to 127 <sup>th</sup> )                    | 13 (127 blocks : 0 <sup>th</sup> to 126 <sup>th</sup> ) |

| 1                    | 1   | 1   | 0   | 8MB (All)      | 14 (128 blocks : 0 <sup>th</sup> to 127 <sup>th</sup> )                    | 14 (128 blocks : 0 <sup>th</sup> to 127 <sup>th</sup> ) |

| 1                    | 1   | 1   | 1   | 8MB (All)      | 15 (128 blocks : 0 <sup>th</sup> to 127 <sup>th</sup> )                    | 15 (128 blocks : 0 <sup>th</sup> to 127 <sup>th</sup> ) |

**Notes:**

1. x is don't care

2. For Optional BP Table, see the Ordering Information (Option "B")

## 6.2 FUNCTION REGISTER

Function Register Format and Bit definition are described in Table 6.5 and Table 6.6.

**Table 6.5 Function Register Format**

|         | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0                       |

|---------|-------|-------|-------|-------|-------|-------|-------|-----------------------------|

|         | IRL3  | IRL2  | IRL1  | IRL0  | ESUS  | PSUS  | TBS   | Dedicated<br>RESET# Disable |

| Default | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0 or 1                      |

**Table 6.6 Function Register Bit Definition**

| Bit   | Name                        | Definition                                                                                                                                   | Read /Write          | Type     |

|-------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------|

| Bit 0 | Dedicated<br>RESET# Disable | Dedicated RESET# Disable bit<br>“0” indicates Dedicated RESET# was enabled<br>“1” indicates Dedicated RESET# was disabled                    | R/W for 0<br>R for 1 | OTP      |

| Bit 1 | TBS                         | Top/Bottom Selection.<br>“0” indicates Top area.<br>“1” indicates Bottom area.                                                               | R/W                  | OTP      |

| Bit 2 | PSUS                        | Program suspend bit:<br>“0” indicates program is not suspend<br>“1” indicates program is suspend                                             | R                    | Volatile |

| Bit 3 | ESUS                        | Erase suspend bit:<br>“0” indicates Erase is not suspend<br>“1” indicates Erase is suspend                                                   | R                    | Volatile |

| Bit 4 | IR Lock 0                   | Lock the Information Row 0:<br>“0” indicates the Information Row can be programmed<br>“1” indicates the Information Row cannot be programmed | R/W                  | OTP      |

| Bit 5 | IR Lock 1                   | Lock the Information Row 1:<br>“0” indicates the Information Row can be programmed<br>“1” indicates the Information Row cannot be programmed | R/W                  | OTP      |

| Bit 6 | IR Lock 2                   | Lock the Information Row 2:<br>“0” indicates the Information Row can be programmed<br>“1” indicates the Information Row cannot be programmed | R/W                  | OTP      |

| Bit 7 | IR Lock 3                   | Lock the Information Row 3:<br>“0” indicates the Information Row can be programmed<br>“1” indicates the Information Row cannot be programmed | R/W                  | OTP      |

**Note:** Once OTP bits of Function Register are written to “1”, it cannot be modified to “0” any more.

**Dedicated RESET# Disable bit:** The default status of the bit is dependent on package type. The device with dedicated RESET# (16-pin SOIC and 24-ball BGA) can be programmed to “1” to disable dedicated RESET# function to move RESET# function to Hold#/RESET# pin (or ball). So the device with dedicated RESET# can be used for dedicated RESET# application and HOLD#/RESET# application.

**TBS bit:** BP0~3 area assignment can be changed from Top (default) to Bottom by setting TBS bit to “1”. However, once Bottom is selected, it cannot be changed back to Top since TBS bit is OTP.

**PSUS bit:** The Program Suspend Status bit indicates when a Program operation has been suspended. The PSUS changes to “1” after a suspend command is issued during the program operation. Once the suspended Program resumes, the PSUS bit is reset to “0”.

**ESUS bit:** The Erase Suspend Status bit indicates when an Erase operation has been suspended. The ESUS bit is “1” after a suspend command is issued during an Erase operation. Once the suspended Erase resumes, the ESUS bit is reset to “0”.

**IR Lock bit 0 ~ 3:** The default is “0” so that the Information Row can be programmed. If the bit is set to “1”, it cannot be changed back to “0” again since IR Lock bits are OTP.

### 6.3 READ REGISTER

Read Register format and bit definitions are described below. Read Register and Extended Read Register consist of a pair of rewritable non-volatile register and volatile register, respectively. During power up sequence, volatile register will be loaded with the value of non-volatile value.

Table 6.7 and Table 6.8 define all bits that control features in SPI/QPI modes. HOLD#/RESET# pin selection (P7) bit is used to select HOLD# pin or RESET# pin in SPI mode when QE="0" for the device with HOLD#/RESET#. When QE=1 or in QPI mode, P7 bit setting will be ignored since the pin becomes IO3.

For 16-pin SOIC or 24-ball TFBGA with dedicated RESET# device (Dedicated RESET# Disable bit in Functional Register is "0"), HOLD# will be selected regardless of P7 bit setting when QE="0" in SPI mode.

The SET READ PARAMETERS Operations (SRPNV: 65h, SRPV: C0h or 63h) are used to set all the Read Register bits, and can thereby define HOLD#/RESET# pin (or ball) selection, dummy cycles, and burst length with wrap around. SRPNV is used to set the non-volatile register and SRPV is used to set the volatile register.

**Table 6.7 Read Register Parameter Bit Table**

|         | P7           | P6           | P5           | P4           | P3           | P2          | P1           | P0           |

|---------|--------------|--------------|--------------|--------------|--------------|-------------|--------------|--------------|

|         | HOLD#/RESET# | Dummy Cycles | Dummy Cycles | Dummy Cycles | Dummy Cycles | Wrap Enable | Burst Length | Burst Length |

| Default | 0            | 0            | 0            | 0            | 0            | 0           | 0            | 0            |

**Table 6.8 Read Register Bit Definition**

| Bit | Name                    | Definition                                                                                                                                      | Read-/Write | Type                      |

|-----|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------|

| P0  | Burst Length            | Burst Length                                                                                                                                    | R/W         | Non-Volatile and Volatile |

| P1  | Burst Length            | Burst Length                                                                                                                                    | R/W         | Non-Volatile and Volatile |

| P2  | Burst Length Set Enable | Burst Length Set Enable Bit:<br>"0" indicates disable (default)<br>"1" indicates enable                                                         | R/W         | Non-Volatile and Volatile |

| P3  | Dummy Cycles            | Number of Dummy Cycles:<br>Bits1 to Bit4 can be toggled to select the number of dummy cycles (1 to 15 cycles)                                   | R/W         | Non-Volatile and Volatile |

| P4  | Dummy Cycles            |                                                                                                                                                 | R/W         | Non-Volatile and Volatile |

| P5  | Dummy Cycles            |                                                                                                                                                 | R/W         | Non-Volatile and Volatile |

| P6  | Dummy Cycles            |                                                                                                                                                 | R/W         | Non-Volatile and Volatile |

| P7  | HOLD#/RESET#            | HOLD#/RESET# function selection Bit:<br>"0" indicates the HOLD# function is selected (default)<br>"1" indicates the RESET# function is selected | R/W         | Non-Volatile and Volatile |

**Table 6.9 Burst Length Data**

|          | P1 | P0 |

|----------|----|----|

| 8 bytes  | 0  | 0  |

| 16 bytes | 0  | 1  |

| 32 bytes | 1  | 0  |

| 64 bytes | 1  | 1  |

**Table 6.10 Wrap Function**

|                                           |           |

|-------------------------------------------|-----------|

| Wrap around boundary                      | <b>P2</b> |

| Whole array regardless of P1 and P0 value | 0         |

| Burst Length set by P1 and P0             | 1         |

**Table 6.11 Read Dummy Cycles vs Max Frequency**

**IS25LP064D (VDD = 2.70~3.6V, 125°C) <sup>(7)</sup>**

| P[6:3] | Dummy Cycles <sup>(2,3)</sup> | Fast Read 0Bh <sup>(5)</sup> | Fast Read 0Bh <sup>(6)</sup> | Fast Read Dual Output 3Bh | Fast Read Dual IO BBh | Fast Read Quad Output 6Bh | Fast Read Quad IO EBh | FRDTR 0Dh | FRDDTR BDh       | FRQDTR EDh |

|--------|-------------------------------|------------------------------|------------------------------|---------------------------|-----------------------|---------------------------|-----------------------|-----------|------------------|------------|

|        |                               | SPI                          | QPI                          | SPI                       | SPI                   | SPI                       | SPI, QPI              | SPI/QPI   | SPI <sup>4</sup> | SPI, QPI   |

| 0      | Default <sup>(1)</sup>        | 166MHz                       | 90MHz                        | 166MHz                    | 104MHz                | 150MHz                    | 90MHz                 | 80/70MHz  | 60MHz            | 70MHz      |

| 1      | 1                             | 84MHz                        | 33MHz                        | 95MHz                     | 55MHz                 | 70MHz                     | 33MHz                 | 50/15MHz  | 30MHz            | 15MHz      |

| 2      | 2                             | 120MHz                       | 50MHz                        | 104MHz                    | 80MHz                 | 80MHz                     | 50MHz                 | 66/30MHz  | 40MHz            | 30MHz      |

| 3      | 3                             | 133MHz                       | 60MHz                        | 120MHz                    | 95MHz                 | 95MHz                     | 60MHz                 | 80/40MHz  | 50MHz            | 40MHz      |

| 4      | 4                             | 166MHz                       | 70MHz                        | 133MHz                    | 104MHz                | 104MHz                    | 70MHz                 | 80/50MHz  | 60MHz            | 50MHz      |

| 5      | 5                             | 166MHz                       | 80MHz                        | 140MHz                    | 120MHz                | 120MHz                    | 80MHz                 | 80/60MHz  | 70MHz            | 60MHz      |

| 6      | 6                             | 166MHz                       | 90MHz                        | 150MHz                    | 133MHz                | 133MHz                    | 90MHz                 | 80/70MHz  | 80MHz            | 70MHz      |

| 7      | 7                             | 166MHz                       | 104MHz                       | 166MHz                    | 140MHz                | 140MHz                    | 104MHz                | 80/80MHz  | 80MHz            | 80MHz      |

| 8      | 8                             | 166MHz                       | 120MHz                       | 166MHz                    | 150MHz                | 150MHz                    | 120MHz                | 80/80MHz  | 80MHz            | 80MHz      |

| 9      | 9                             | 166MHz                       | 133MHz                       | 166MHz                    | 166MHz                | 160MHz                    | 133MHz                | 80/80MHz  | 80MHz            | 80MHz      |

| 10     | 10                            | 166MHz                       | 140MHz                       | 166MHz                    | 166MHz                | 166MHz                    | 140MHz                | 80/80MHz  | 80MHz            | 80MHz      |

| 11     | 11                            | 166MHz                       | 150MHz                       | 166MHz                    | 166MHz                | 166MHz                    | 150MHz                | 80/80MHz  | 80MHz            | 80MHz      |

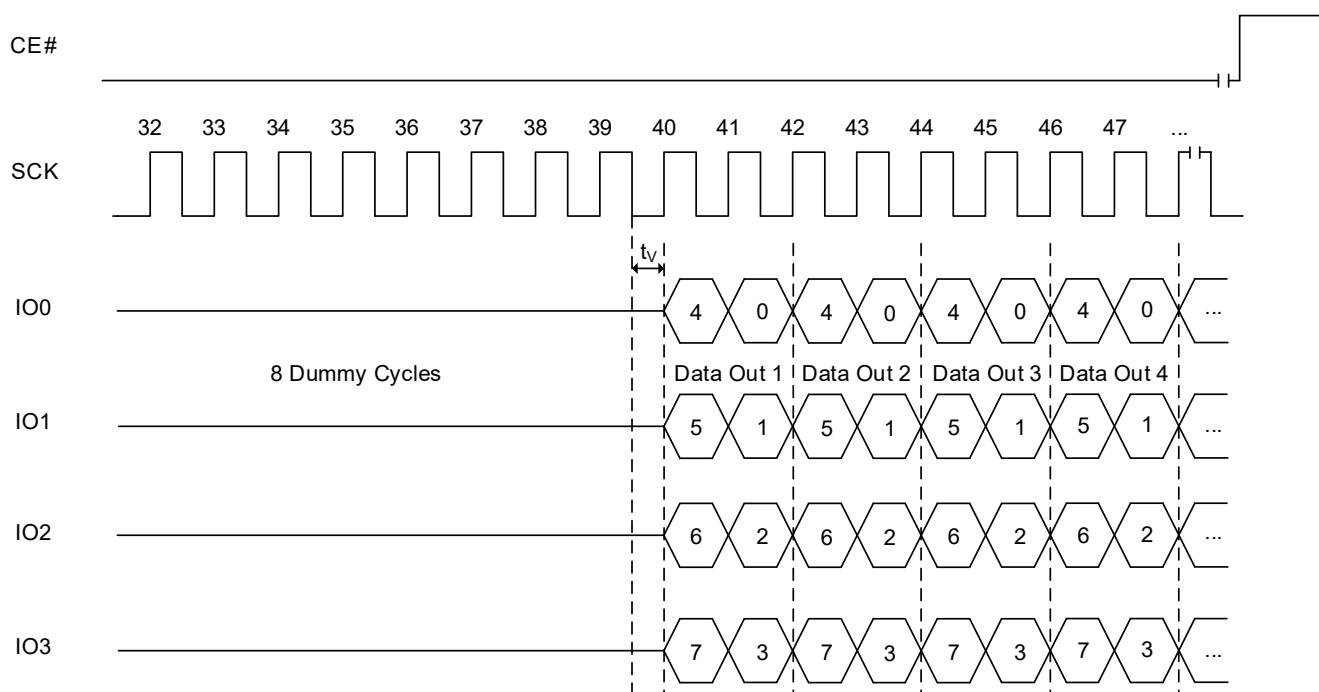

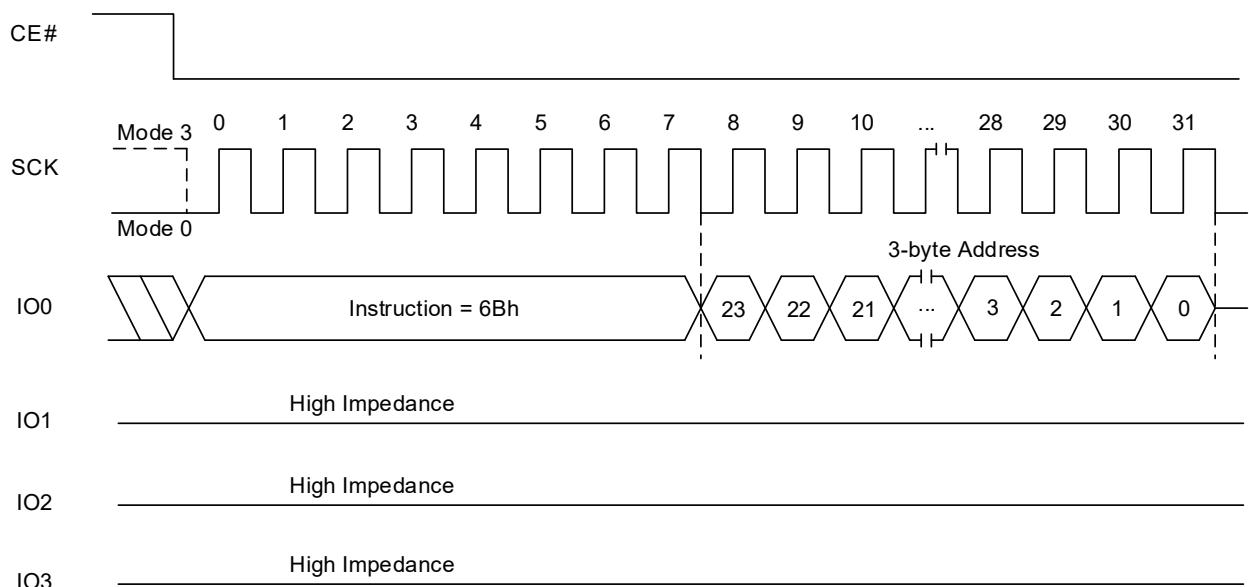

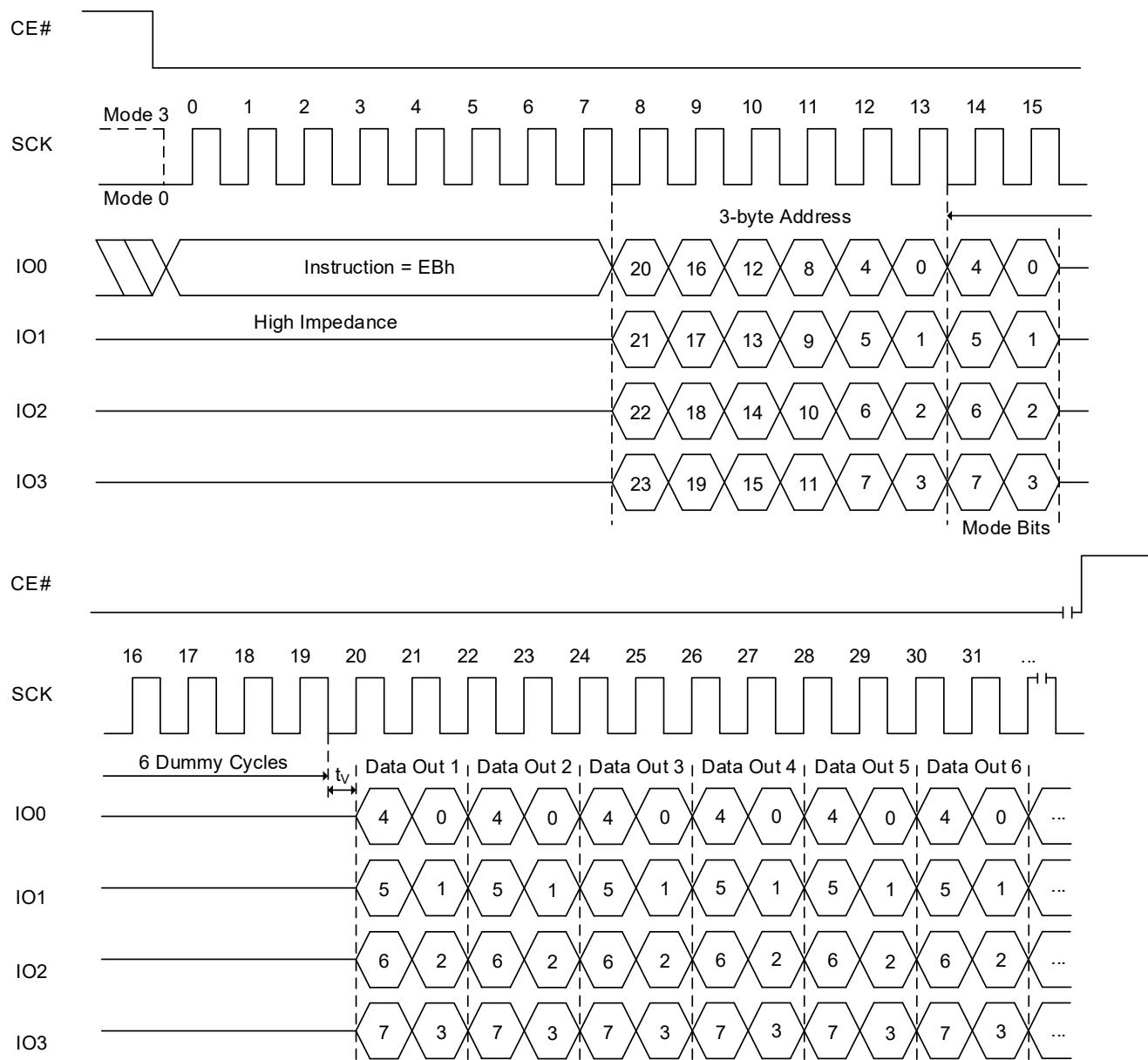

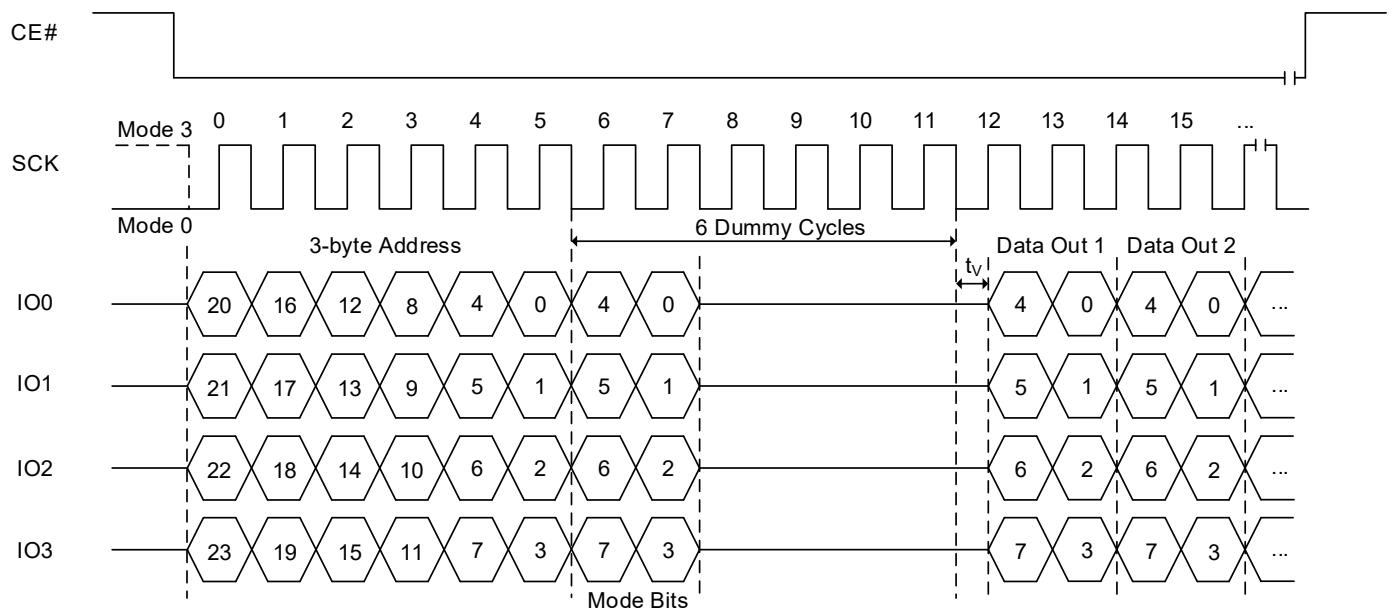

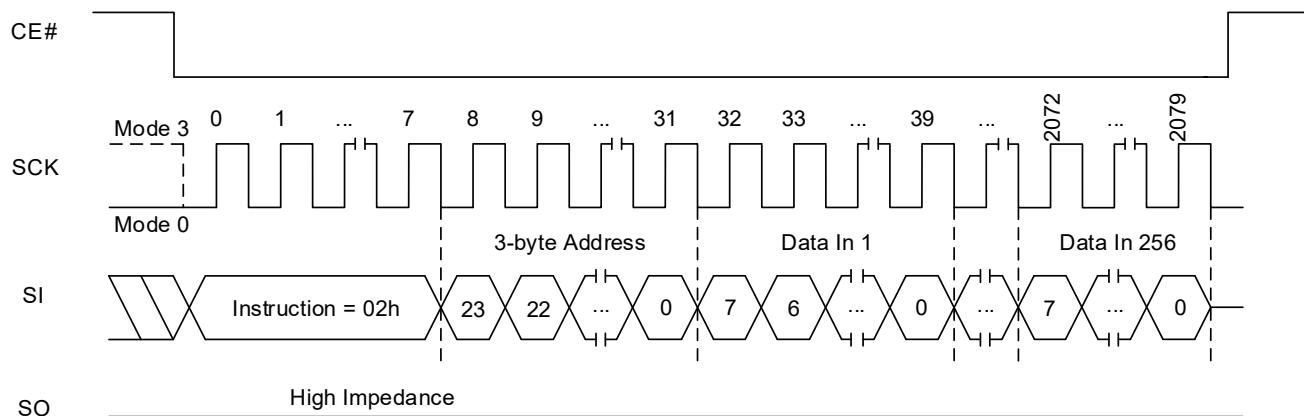

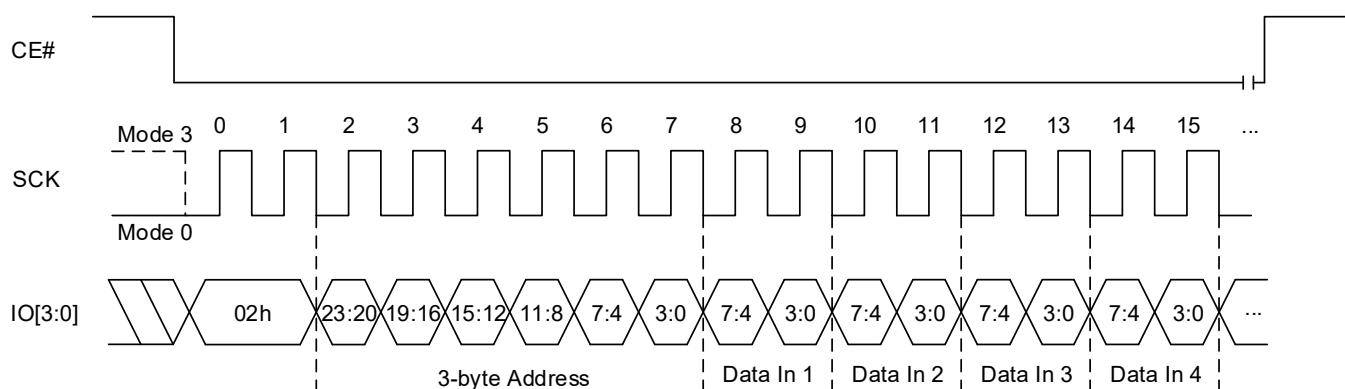

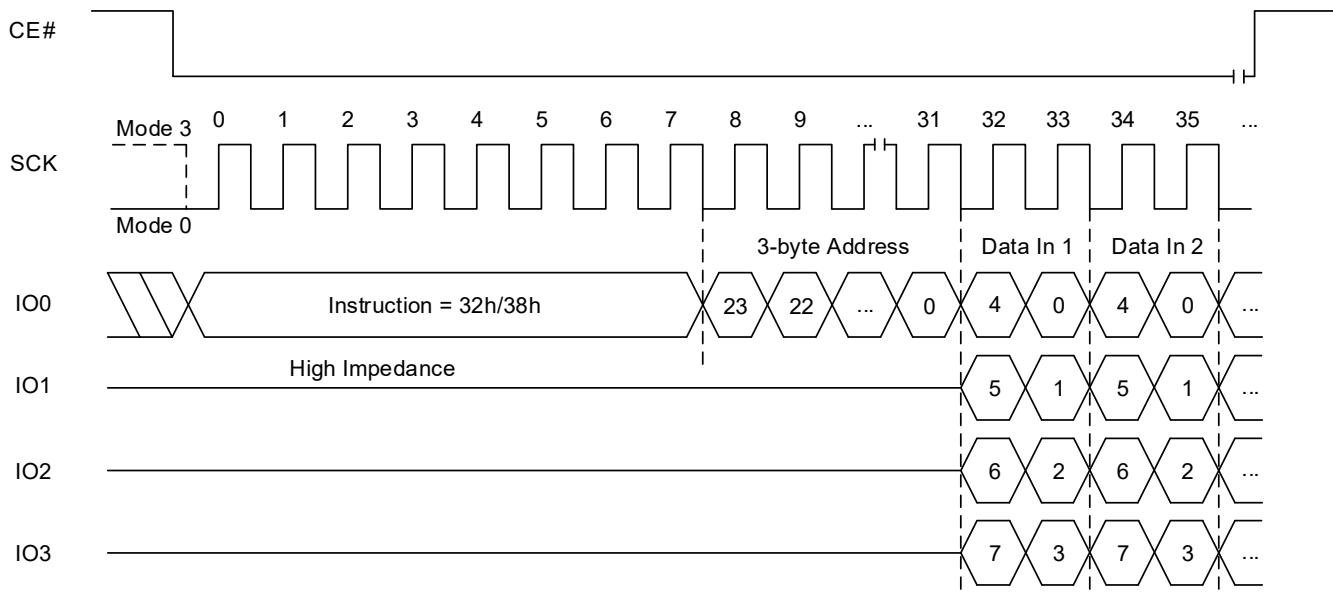

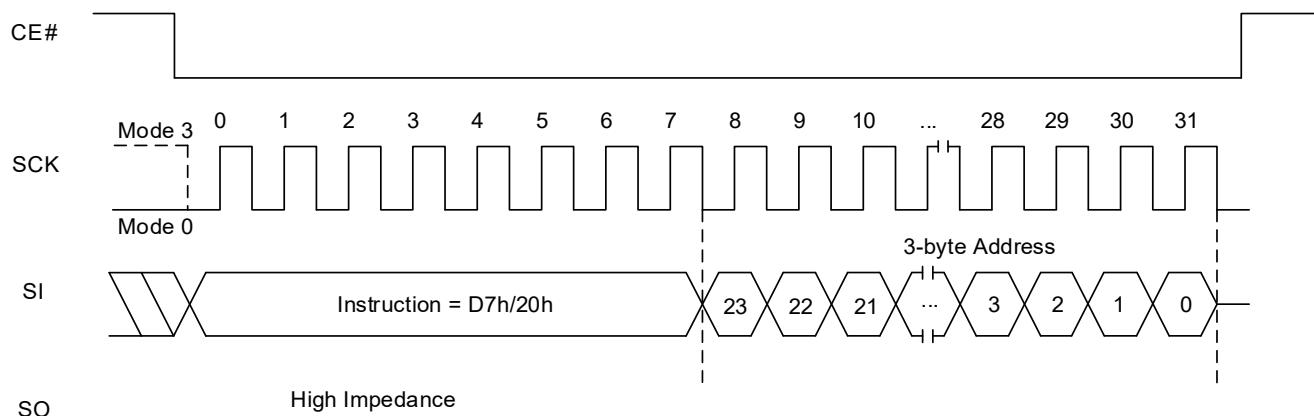

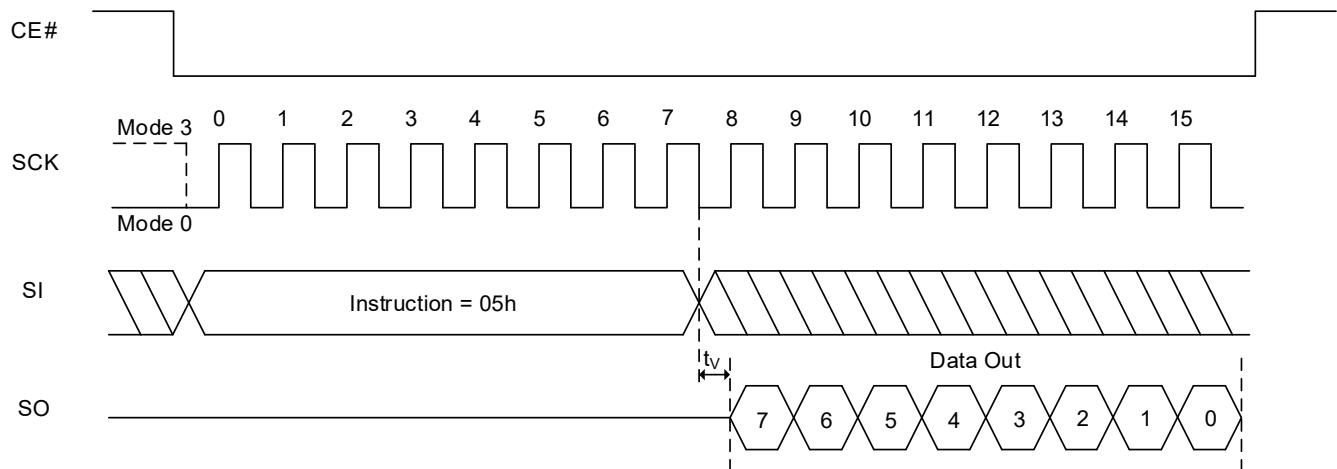

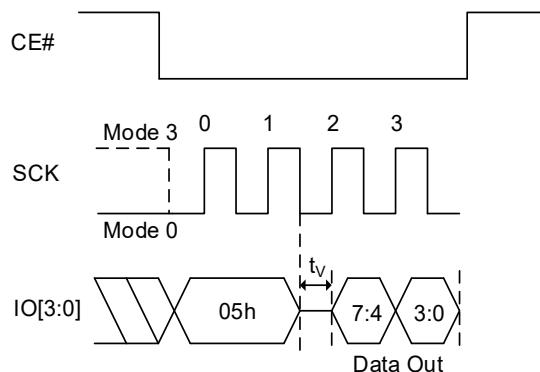

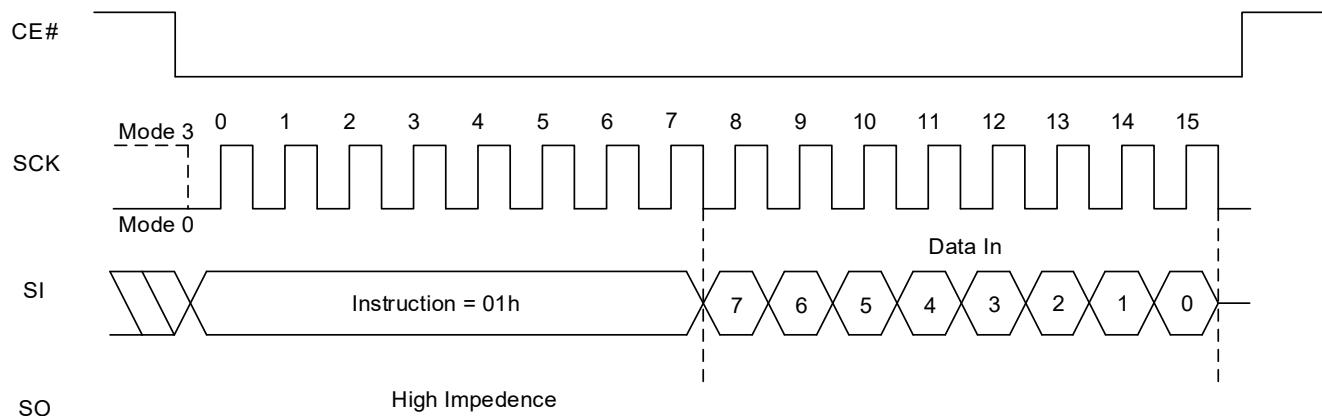

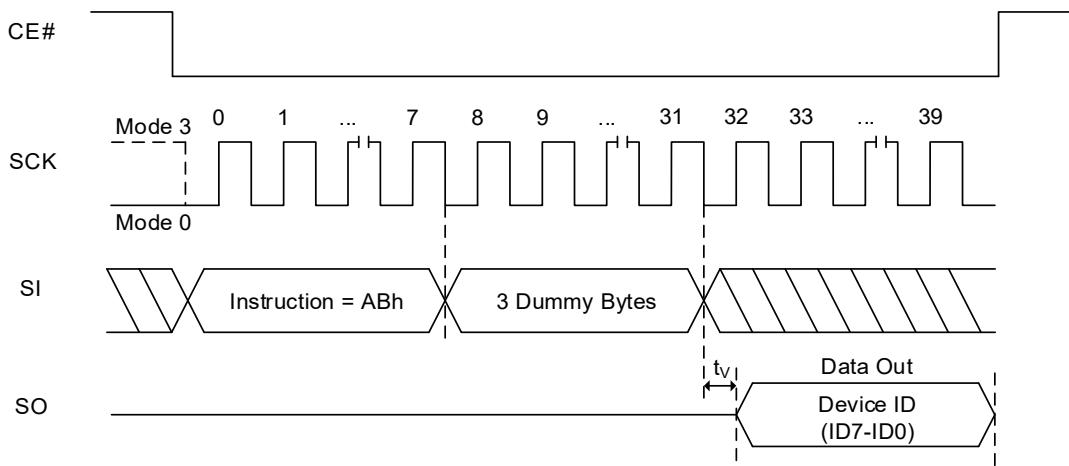

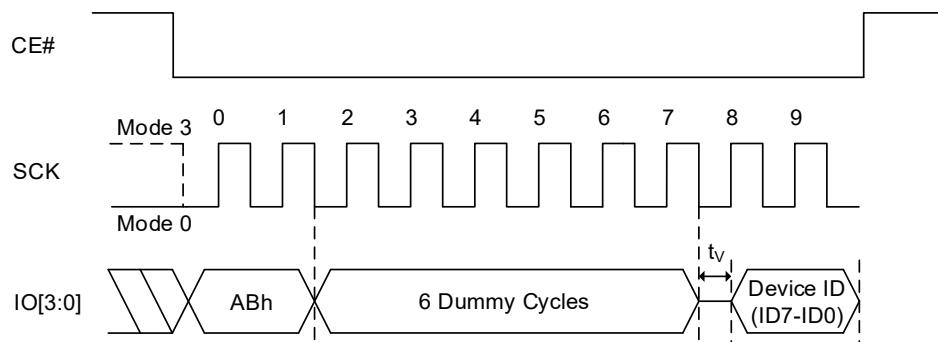

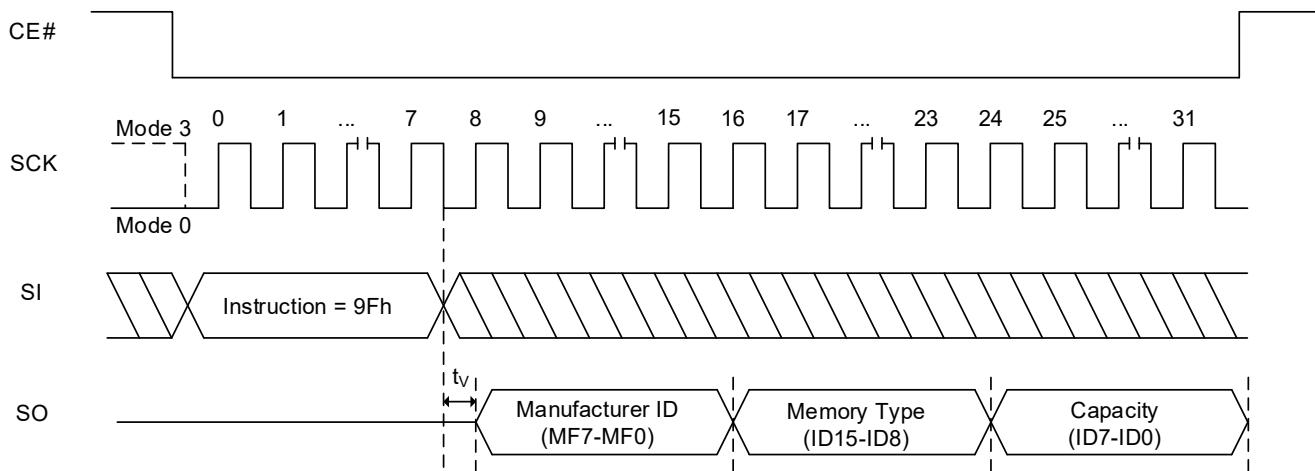

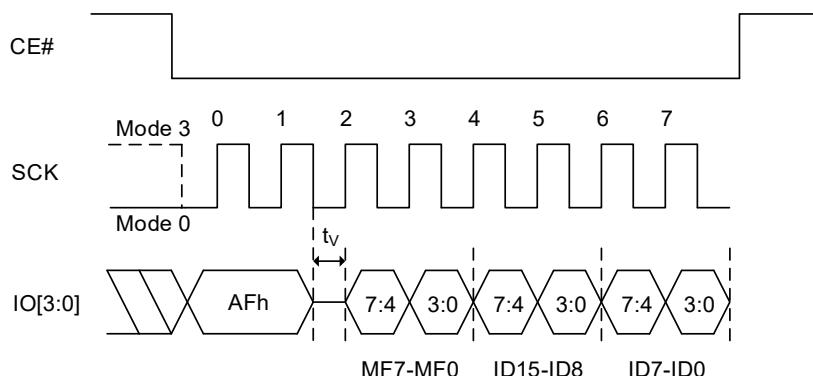

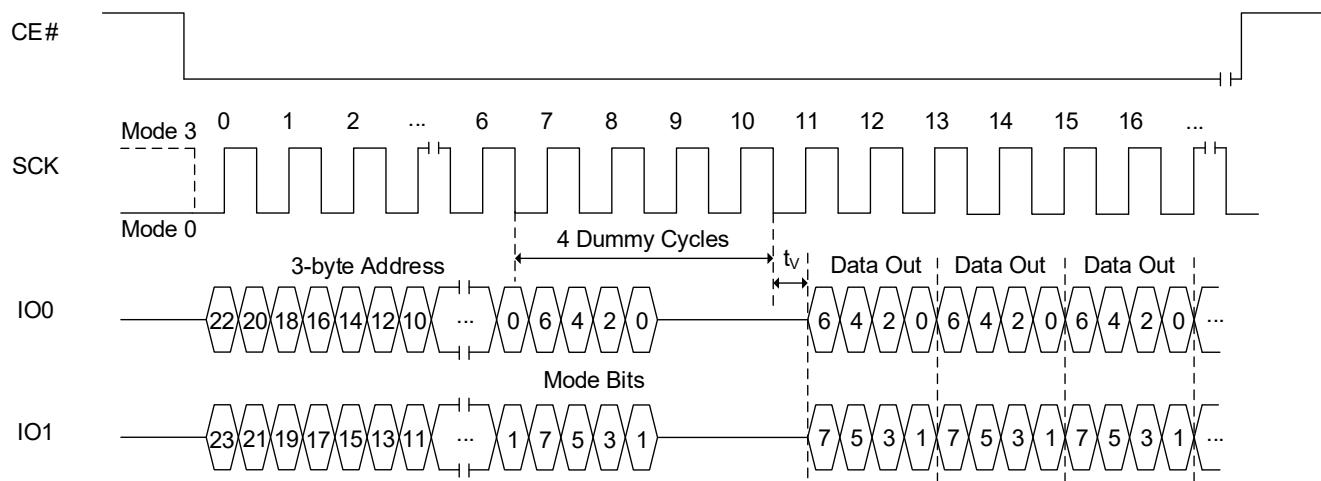

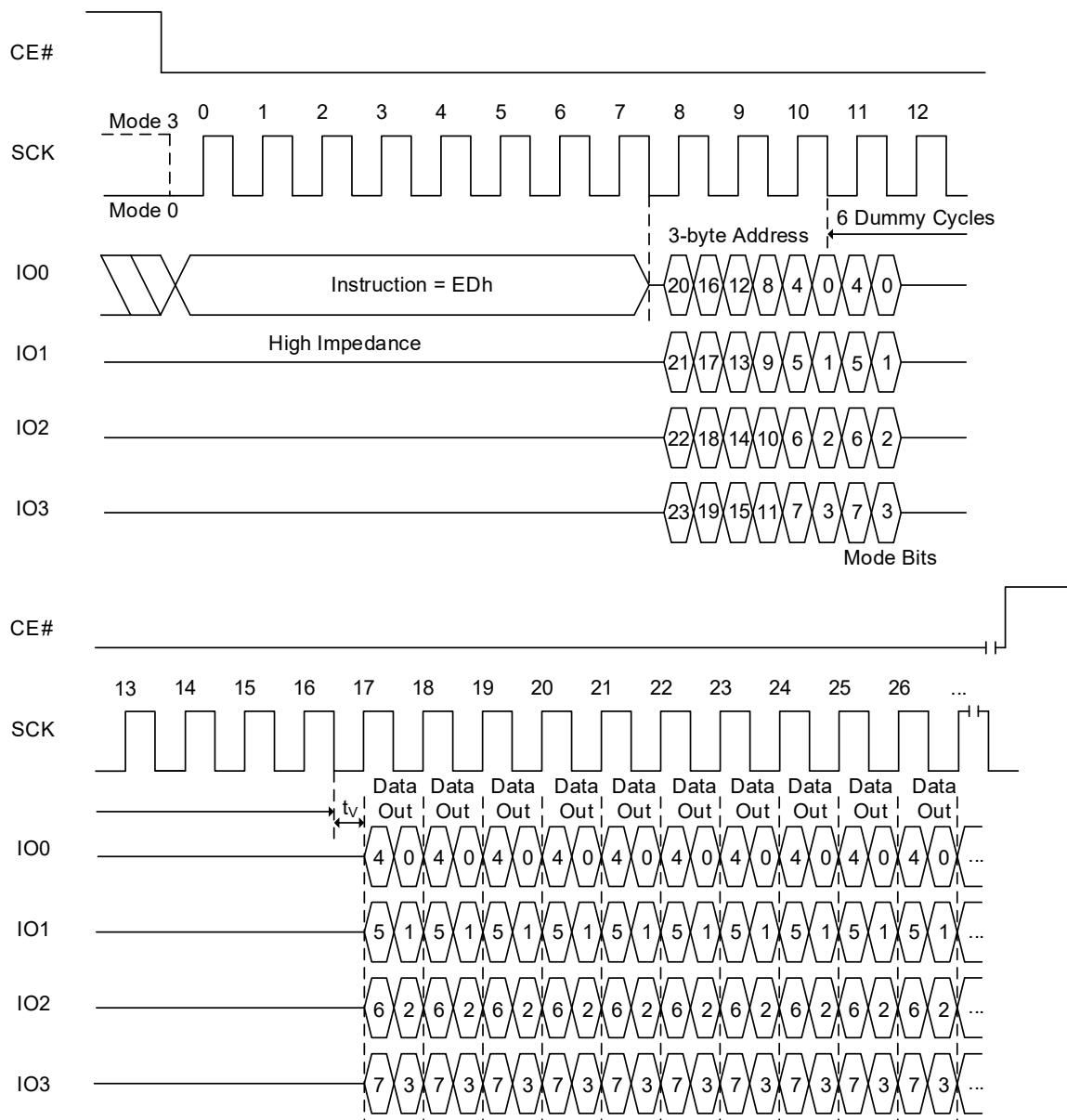

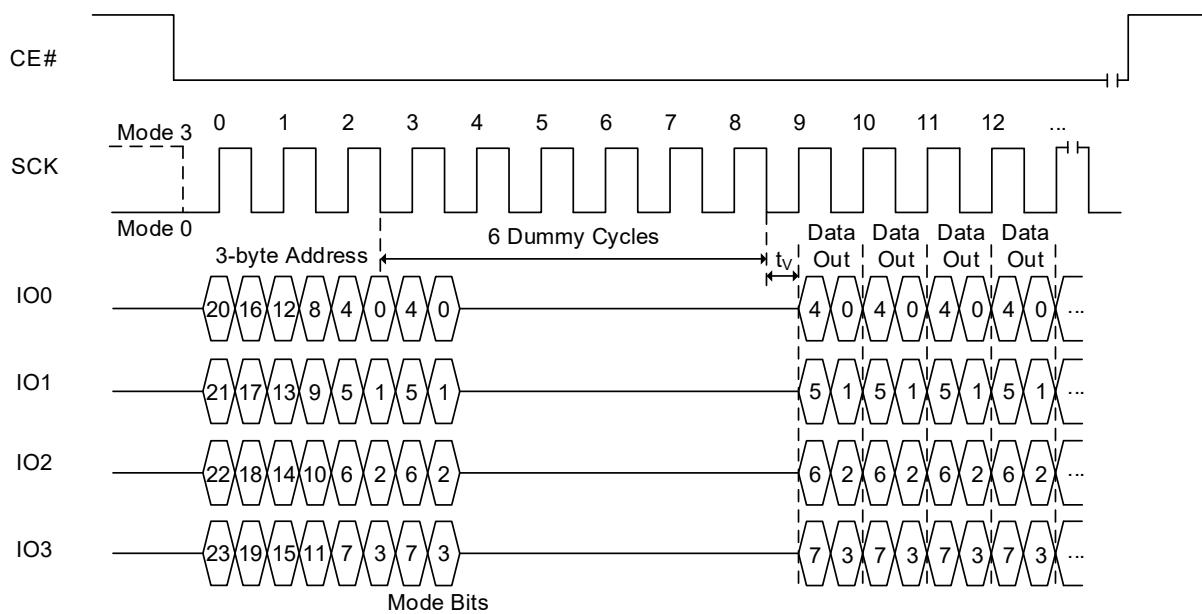

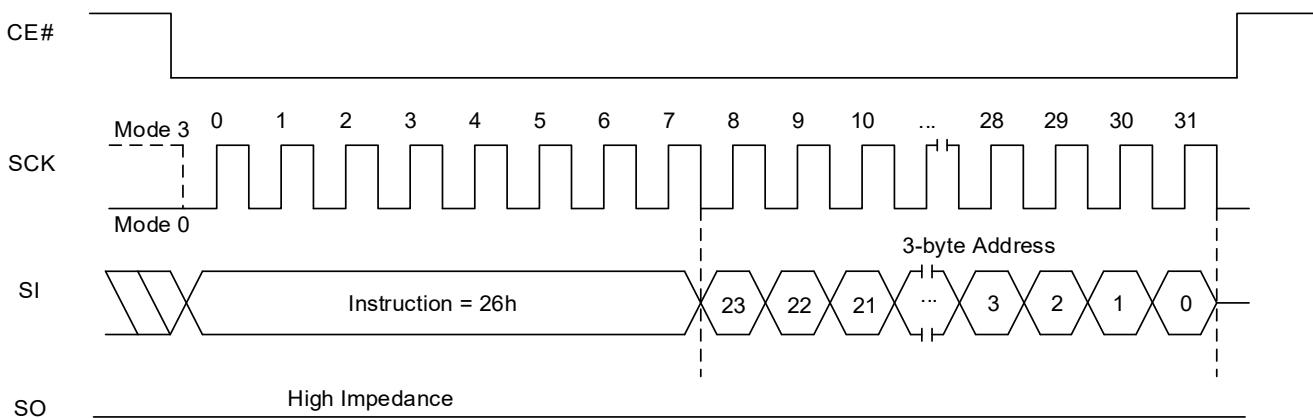

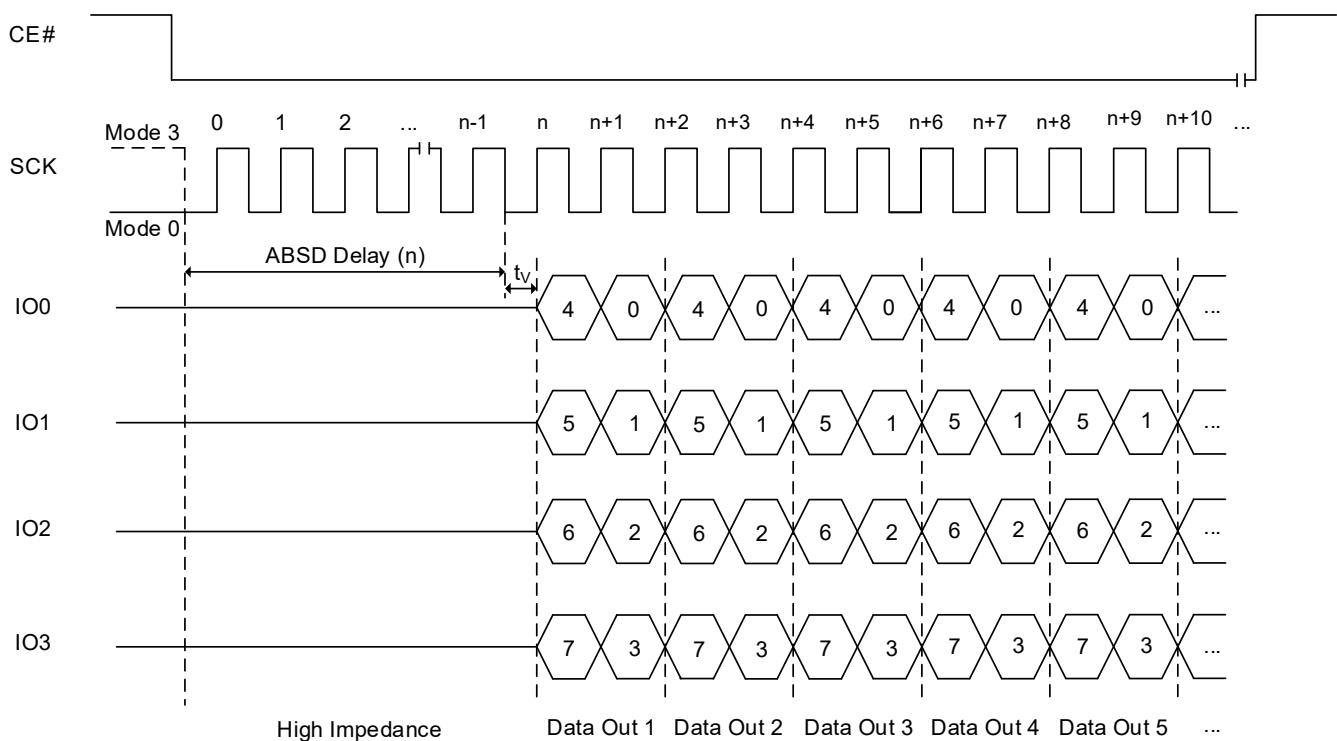

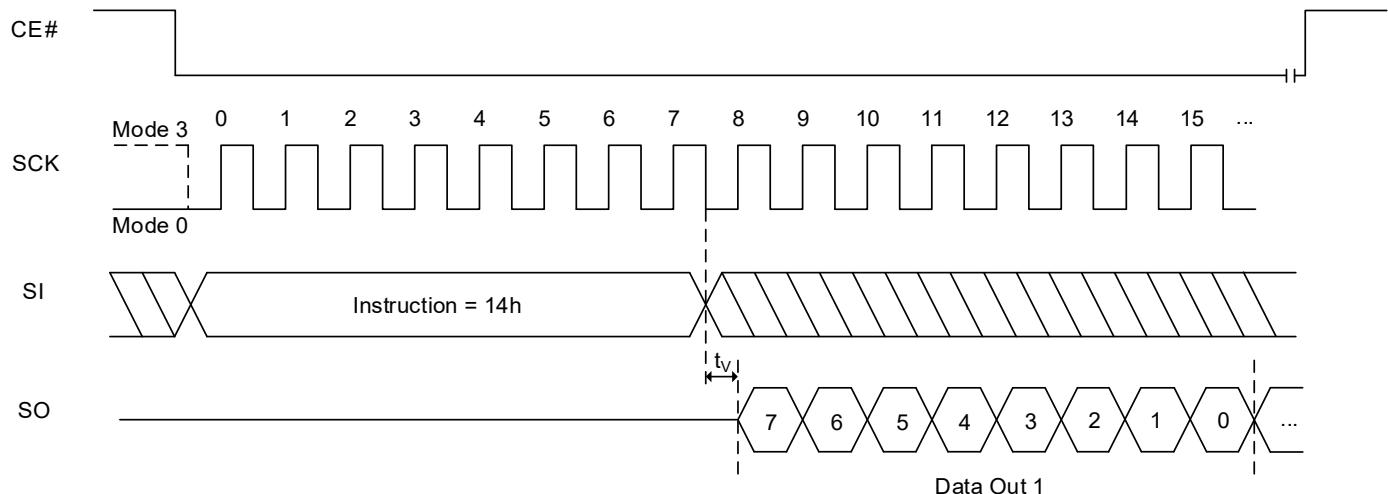

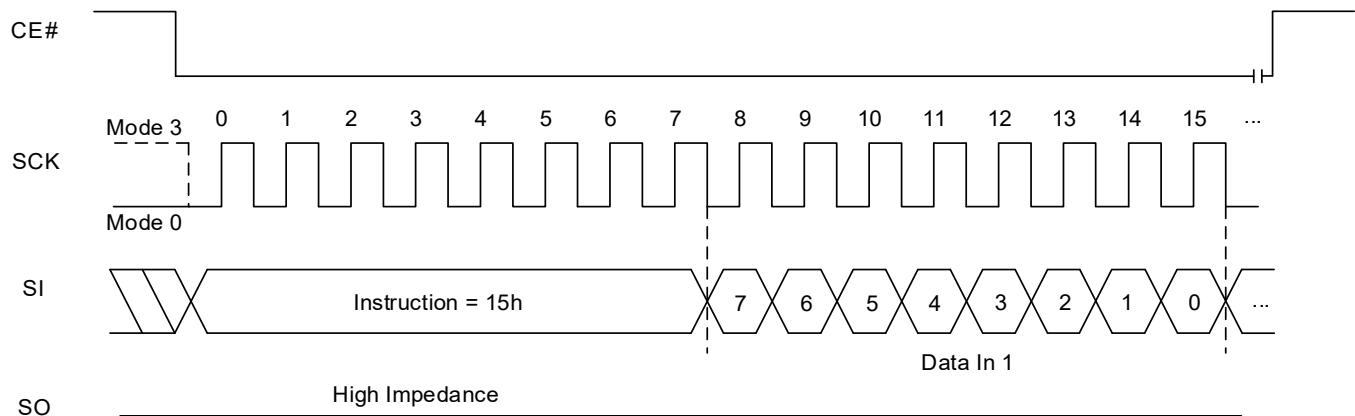

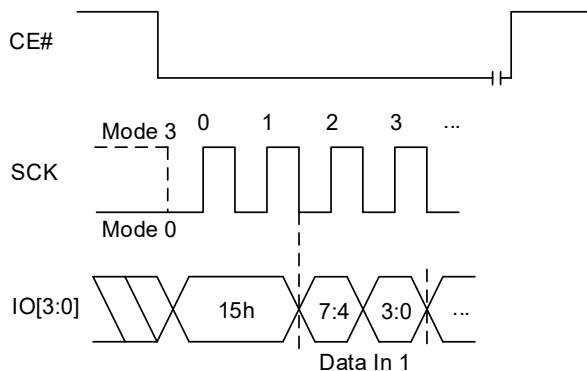

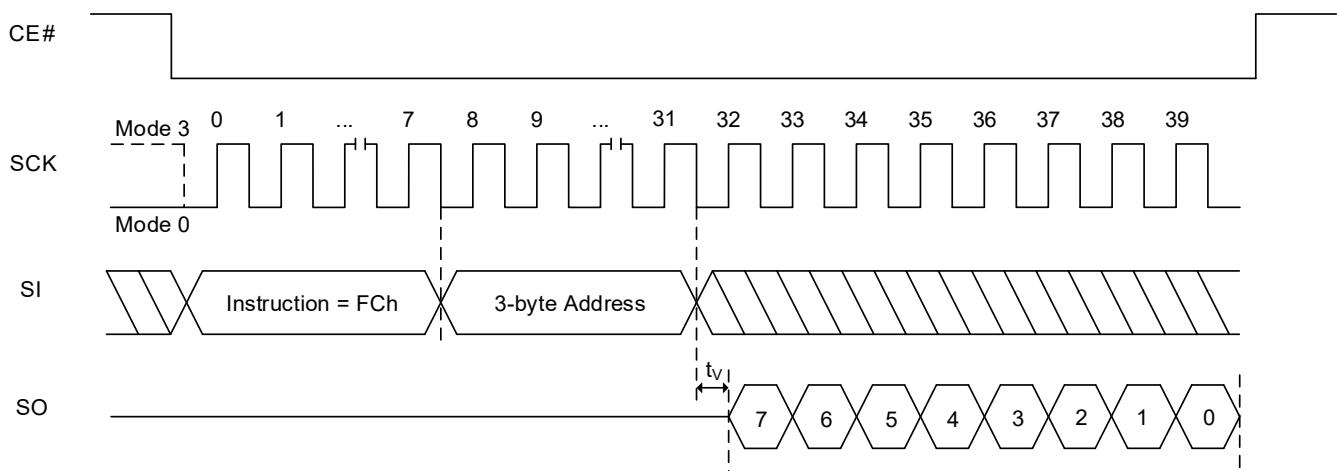

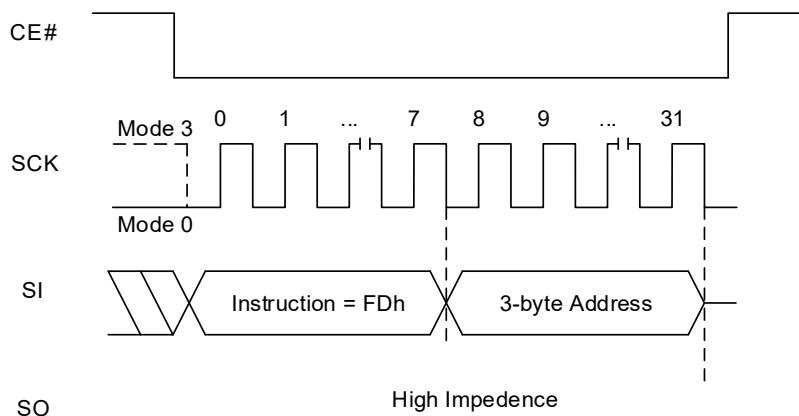

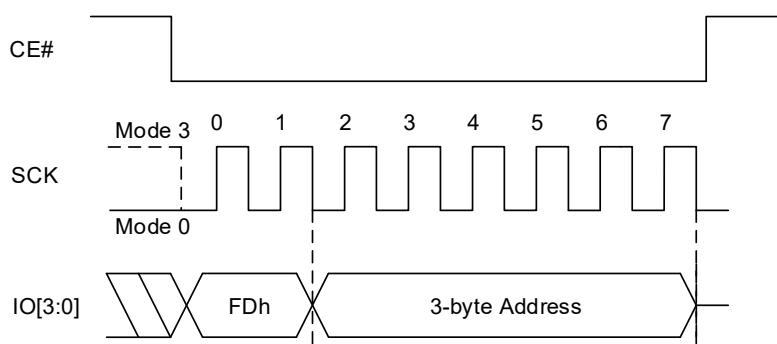

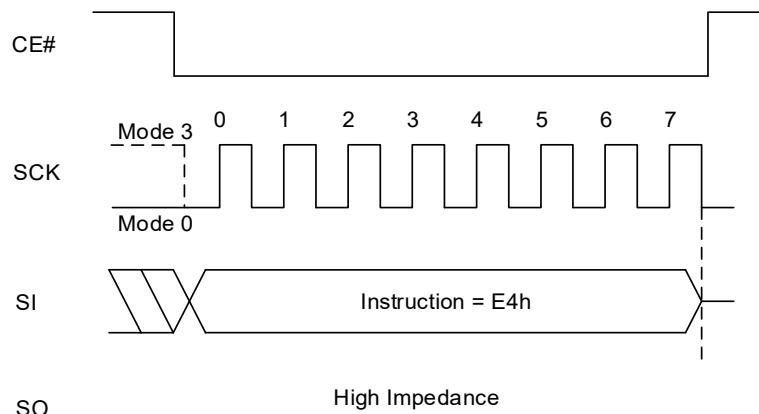

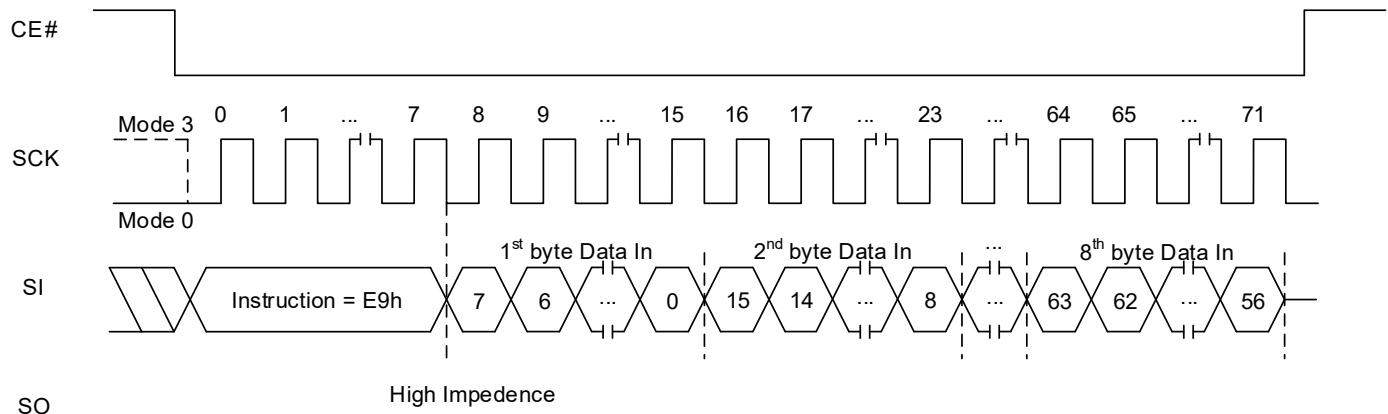

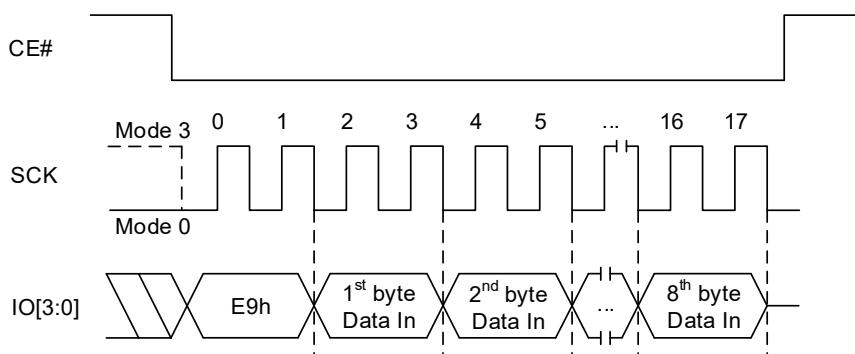

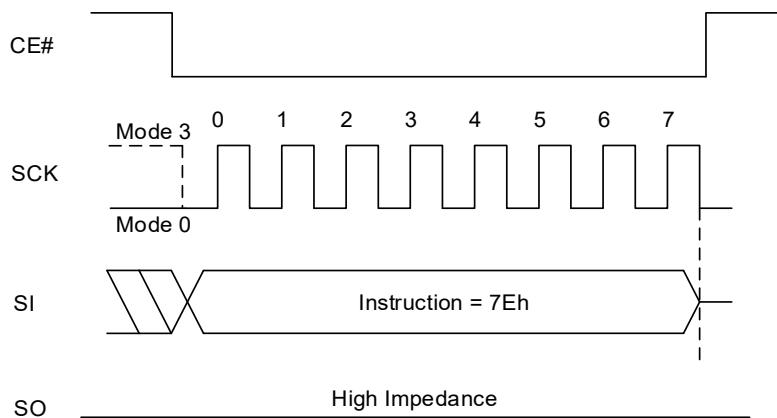

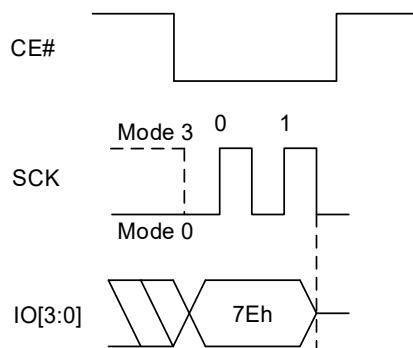

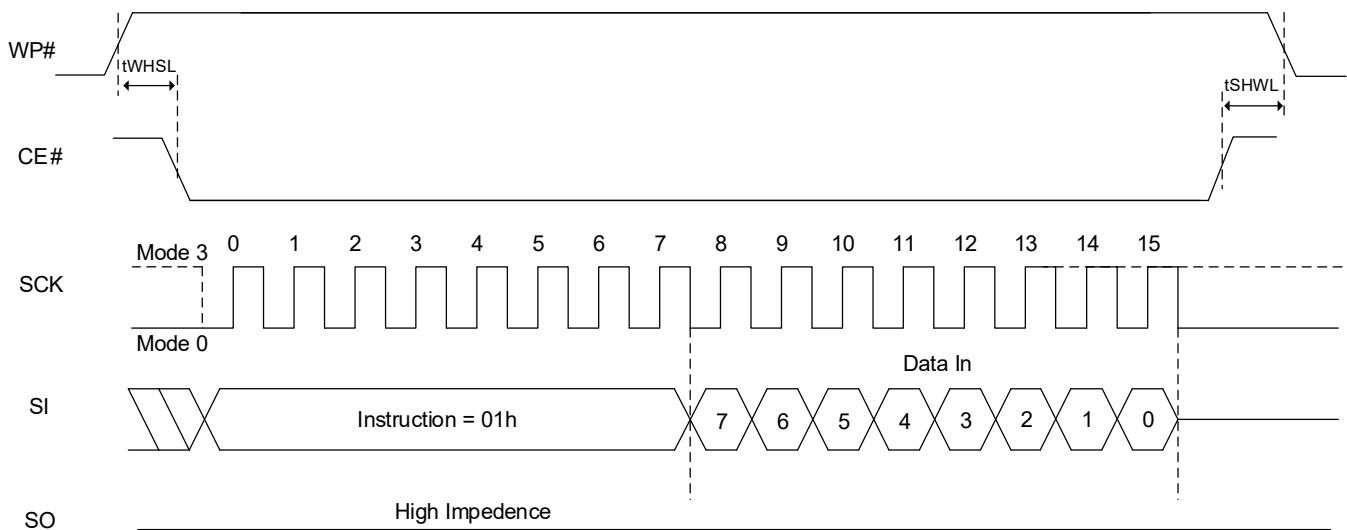

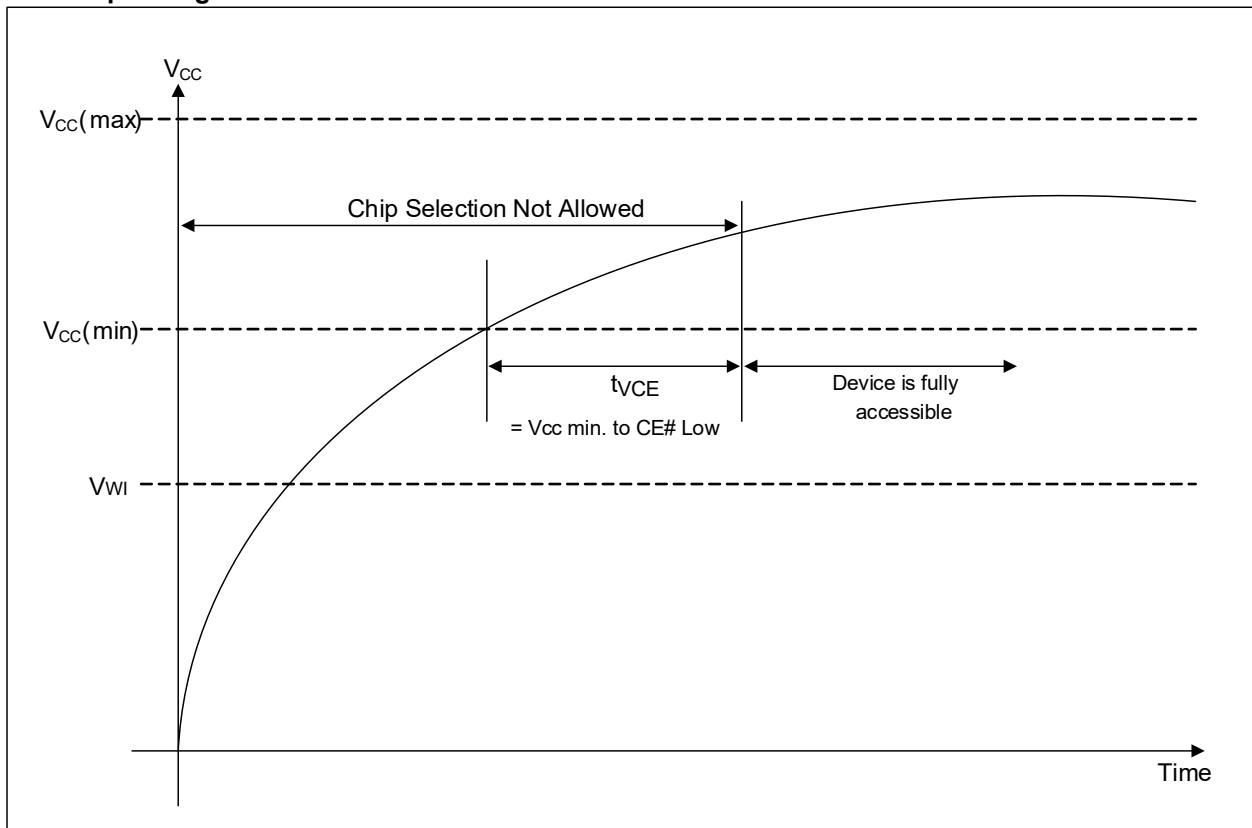

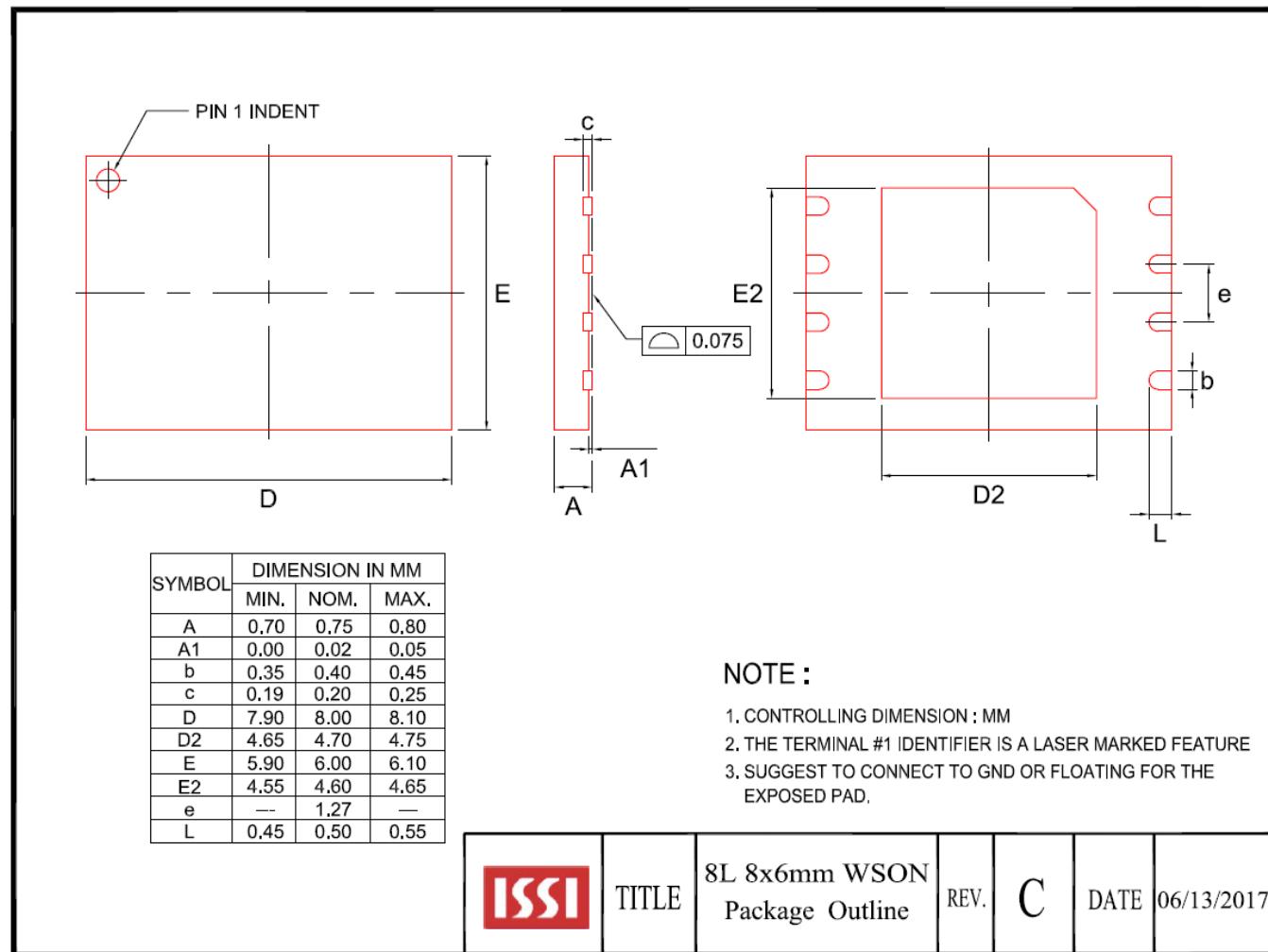

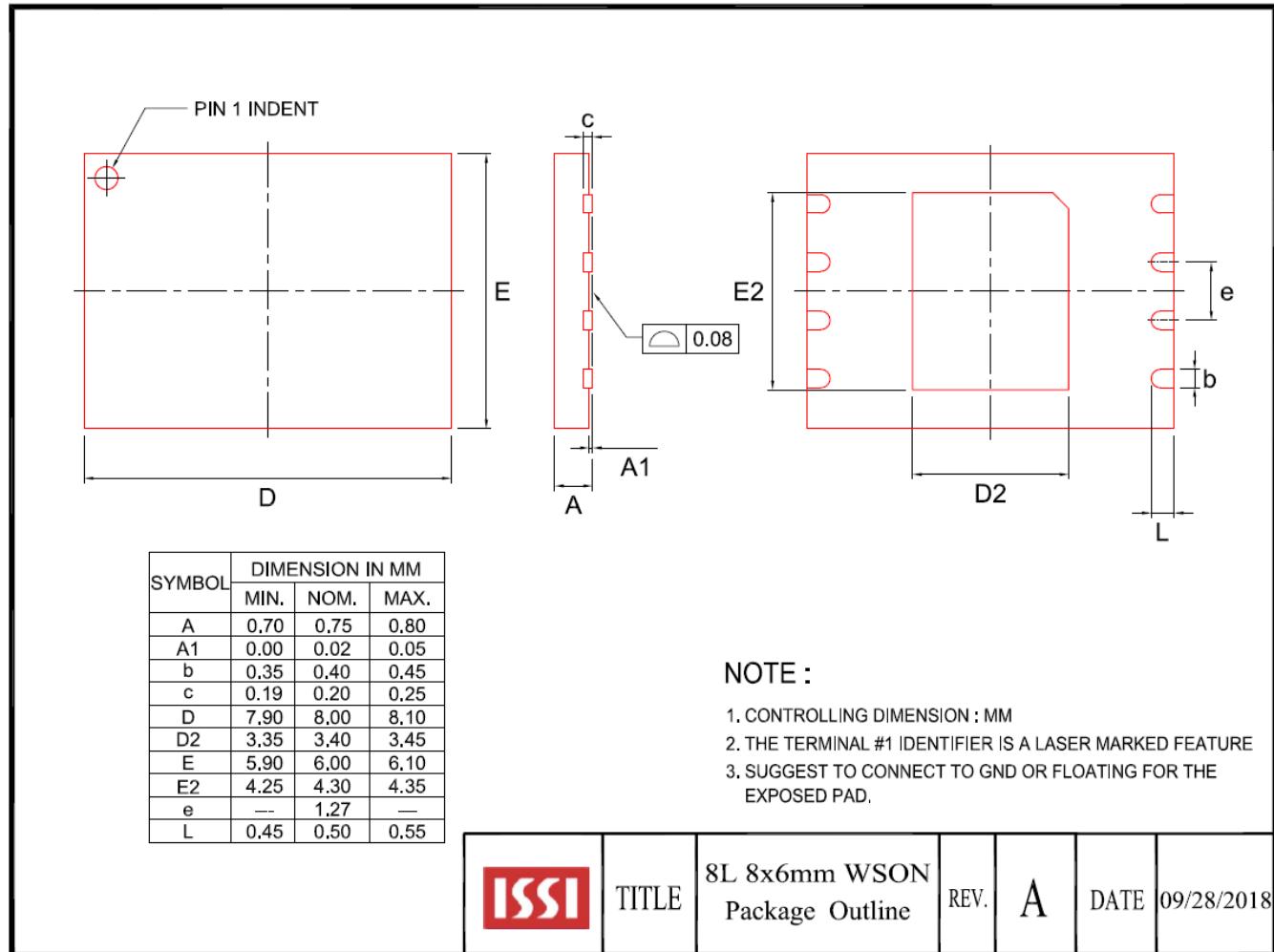

| 12     | 12                            | 166MHz                       | 160MHz                       | 166MHz                    | 166MHz                | 166MHz                    | 160MHz                | 80/80MHz  | 80MHz            | 80MHz      |