# Low Power Software Defined Radio (SDR) Tuner

D/918/2.0 January 2026

## DATASHEET

## Provisional

## Features

- Low power multi-mode SDR Tuner

- Tuning Range 150 kHz to 108 MHz

- LF/MF/HF/VHF band optimised RF inputs

- High spurious free dynamic range tuner

- Analogue and Digital Modulation support

- Software configurable autonomous AGC

- Integrated VCO with low phase noise and fast lock

- Low-IF architecture

- Selectable optimised IF bandwidths

- Standard digital interfaces (SPI, I2C, I2S)

- 5 x 5mm VQFN32 package for low-cost PCB design

- 2.9 V to 3.6 V supply

## Applications

- Battery-powered SDR receivers

- IF processor for professional receivers

- Smartphone accessories

- In-car entertainment

## 1 Brief Description

The CMX918 is a flexible RF Front-End Processor designed for small form factor, low-power software-defined radio (SDR) receiver solutions. Supporting a very wide frequency range from LF through to VHF Band II, the device is suitable for a diverse range of analogue and digital communication applications.

The processor offers general coverage operation from 150 kHz to 108 MHz, featuring frequency-optimised front-end inputs and a highly configurable receive path. Key features include variable gain settings, adjustable IF bandwidths, and programmable IF centre frequencies. This level of configuration allows the device to be precisely tailored to various air interfaces and challenging RF environments. External component requirements are kept to a minimum. Support for Ferrite rod antennas is provided for the LF and MF bands.

The CMX918 is designed to provide robust 'real-world' signal reception. The device's digital output is ready for further processing by a suitable DSP or FPGA platform, which implements the specific demodulation, protocol decoding, and audio processing functions required by the application. This architecture is ideal for SDR implementation, allowing for reception modes such as AM, FM, DRM, DRM+, as well as specialised protocols like SSB, NAVDAT, and others, to be implemented purely in software. A compact, versatile, high-performance, low-power receiver with extended battery life can therefore be realised at low cost.

Programmable power management is included to allow unused circuit blocks to be power saved when not in use, effectively minimizing overall current consumption for extended battery life. The CMX918 is controlled and programmed via a serial port which can be operated as either the industry-standard I<sup>2</sup>C or SPI/C-BUS. The device operates from a single supply of 2.9 to 3.6 V and is supplied in a 32-pin VQFN package with a central ground tab.

Contact CML Sales ([cmlmicro.com](mailto:cmlmicro.com)) for access to additional documentation describing the device register settings.

## CONTENTS

|          |                                                   |           |

|----------|---------------------------------------------------|-----------|

| <b>1</b> | <b>Brief Description .....</b>                    | <b>1</b>  |

| <b>2</b> | <b>Recommended External Components .....</b>      | <b>5</b>  |

| <b>3</b> | <b>Pin and Signal List .....</b>                  | <b>7</b>  |

| <b>4</b> | <b>Functional Description .....</b>               | <b>9</b>  |

| 4.1      | Modulation Modes .....                            | 10        |

| 4.2      | RF Path .....                                     | 10        |

| 4.2.1    | LF / MF Path .....                                | 11        |

| 4.2.2    | HF / VHF Path .....                               | 11        |

| 4.3      | IF path description .....                         | 12        |

| 4.4      | Gain Control .....                                | 12        |

| 4.5      | ADC description .....                             | 16        |

| 4.6      | Local Oscillator / Synthesizer .....              | 16        |

| 4.6.1    | PLL programming .....                             | 17        |

| 4.6.2    | VCO Tuning .....                                  | 18        |

| 4.6.3    | Clock / Crystal Oscillator .....                  | 18        |

| 4.6.4    | PFD, charge pump, lock detector .....             | 18        |

| 4.6.5    | Integer boundary spur avoidance .....             | 19        |

| 4.7      | Signal filtering and down conversion .....        | 19        |

| 4.8      | Digital Processing Block .....                    | 20        |

| 4.8.1    | Digital processing operating modes .....          | 22        |

| 4.8.2    | Output data interface .....                       | 25        |

| 4.8.3    | IQ Calibration .....                              | 26        |

| 4.9      | IF Filter bandwidth calibration .....             | 27        |

| <b>5</b> | <b>Operational Guidelines .....</b>               | <b>28</b> |

| 5.1      | Initial settings .....                            | 28        |

| 5.2      | Reference Frequency Configuration .....           | 28        |

| 5.3      | PLL Reconfiguration .....                         | 29        |

| 5.4      | Noise Figure Improvement .....                    | 29        |

| 5.5      | DRM Operation Table .....                         | 30        |

| 5.6      | Worked examples for specific frequencies .....    | 31        |

| 5.7      | LF/MF band Input and Antennas .....               | 32        |

| 5.8      | AGC and Bandwidth Settings .....                  | 34        |

| 5.9      | Other Features .....                              | 35        |

| 5.9.1    | Pilot PLL .....                                   | 35        |

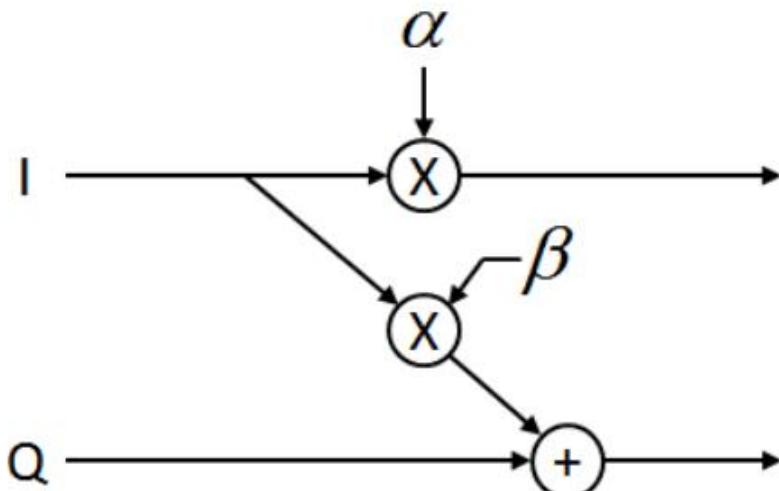

| 5.9.2    | I/Q Amplitude and Phase Compensation .....        | 35        |

| <b>6</b> | <b>Performance Specification .....</b>            | <b>40</b> |

| 6.1      | Electrical Performance .....                      | 40        |

| 6.1.1    | Absolute Maximum Ratings – Typical figures .....  | 40        |

| 6.1.2    | Operating Limits .....                            | 41        |

| 6.1.3    | Operating Characteristics .....                   | 41        |

| 6.1.4    | SPI/C-BUS/I2C Control Interface Description ..... | 56        |

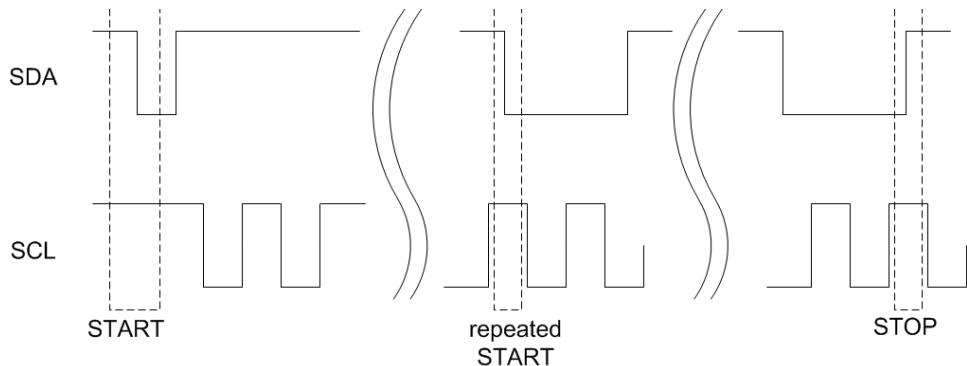

| 6.2      | I2C description .....                             | 56        |

| 6.2.1    | Start and stop conditions .....                   | 57        |

| 6.2.2    | ACK and NACK conditions .....                     | 57        |

| 6.2.3    | Slave address .....                               | 57        |

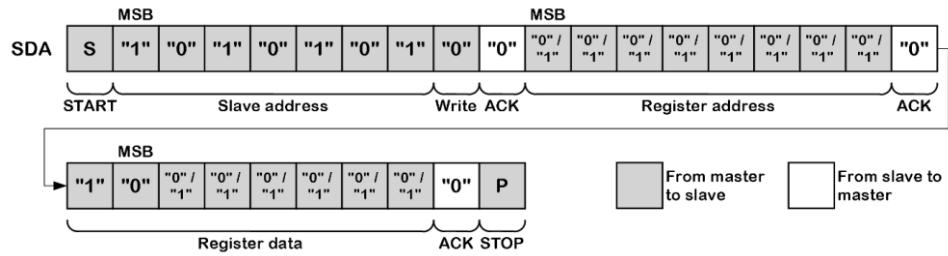

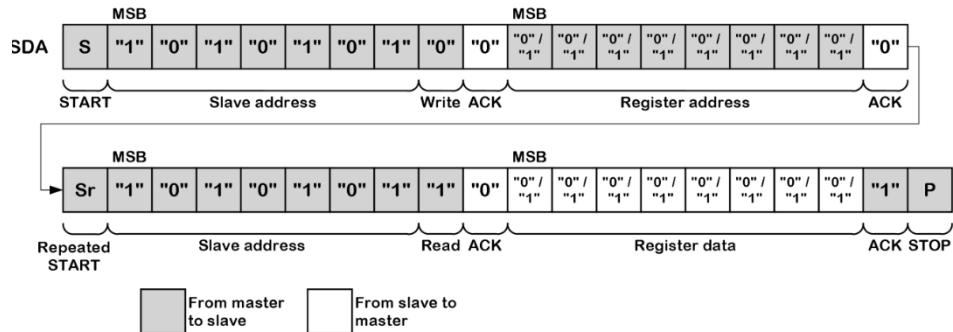

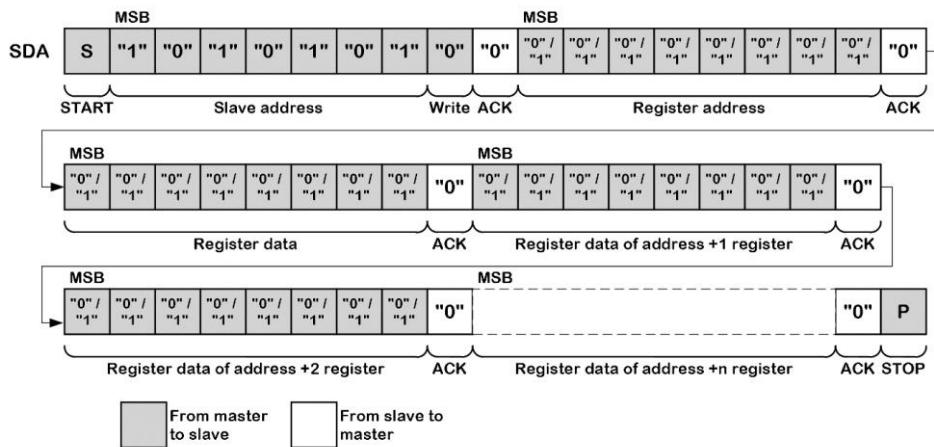

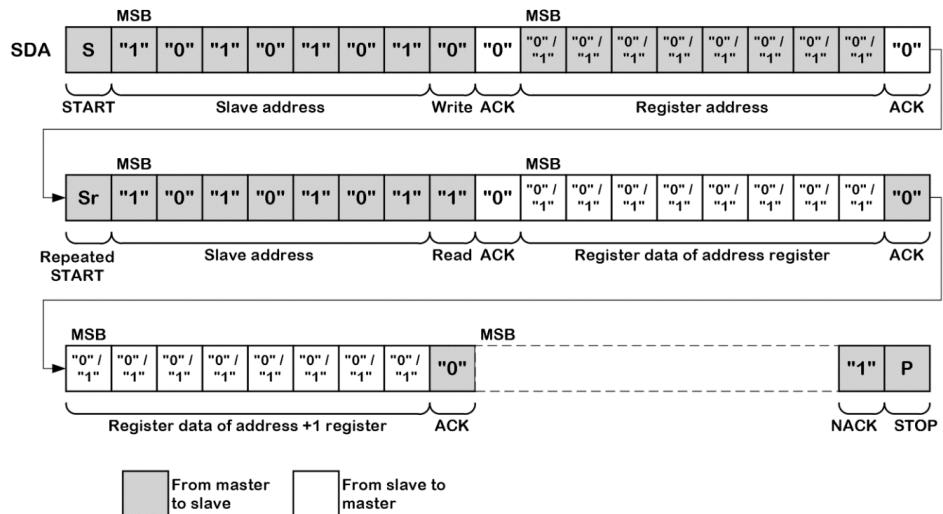

| 6.2.4    | Command format .....                              | 57        |

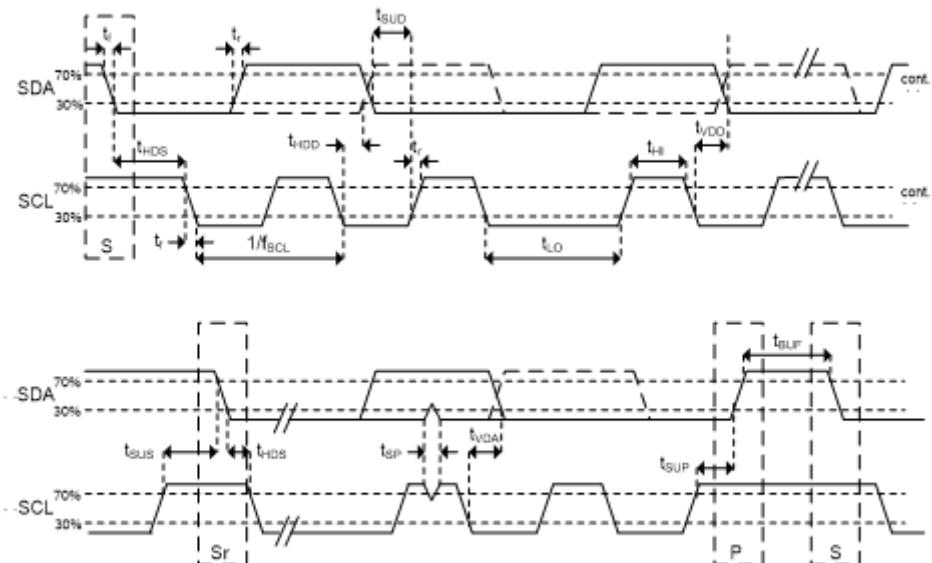

| 6.2.5    | Timing diagram .....                              | 59        |

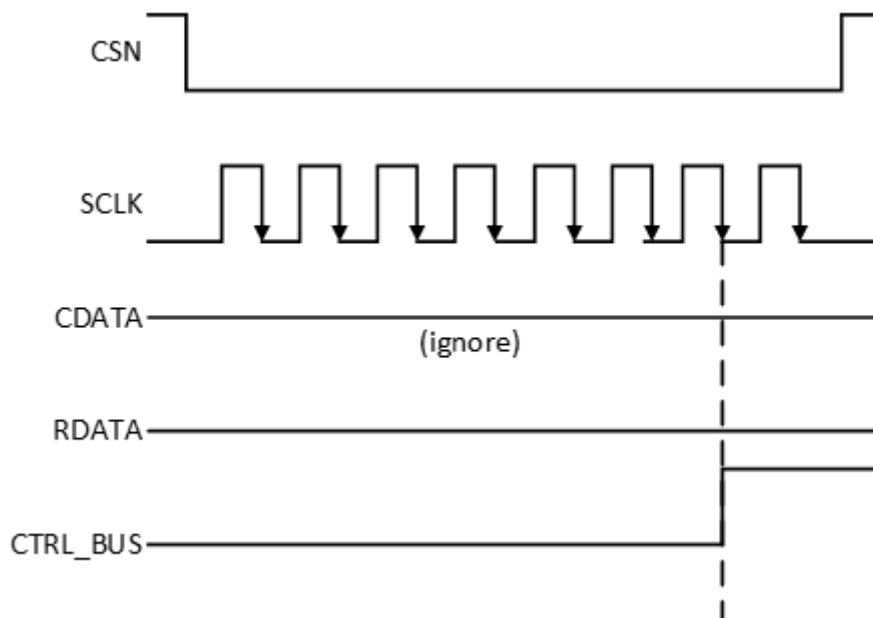

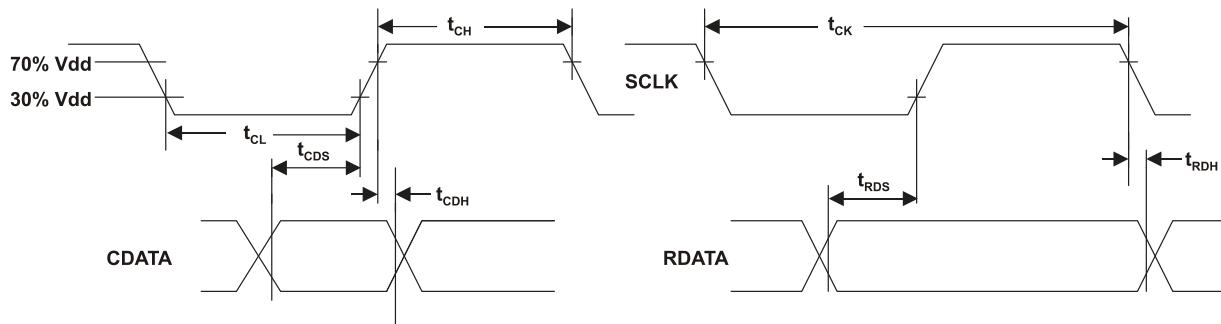

| 6.3      | SPI/C-BUS description .....                       | 60        |

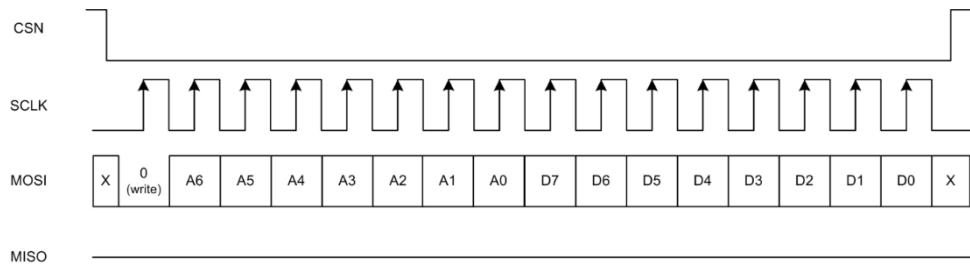

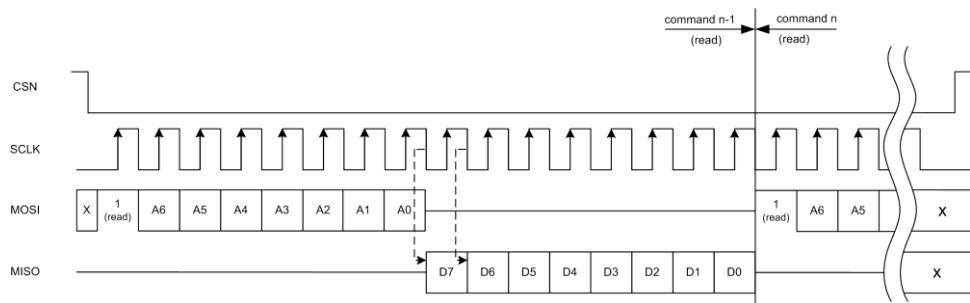

| 6.3.1    | Writing to register .....                         | 61        |

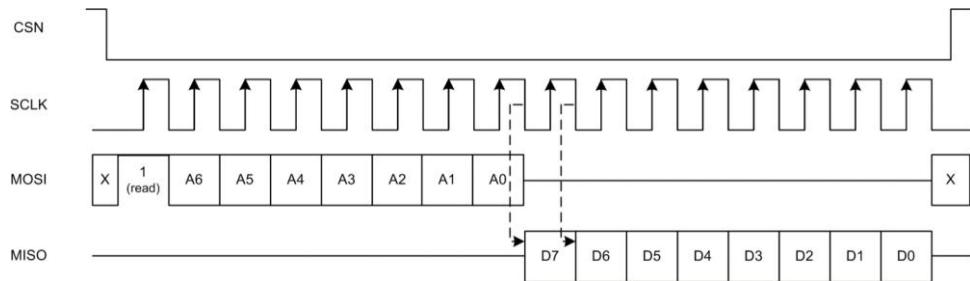

| 6.3.2    | Reading from register .....                       | 61        |

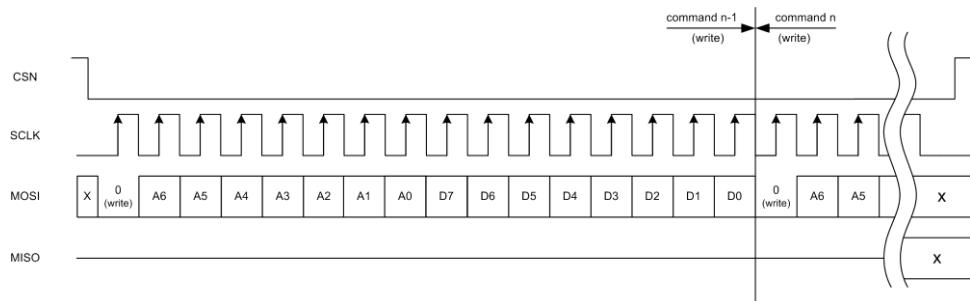

| 6.3.3    | Burst data transfer .....                         | 62        |

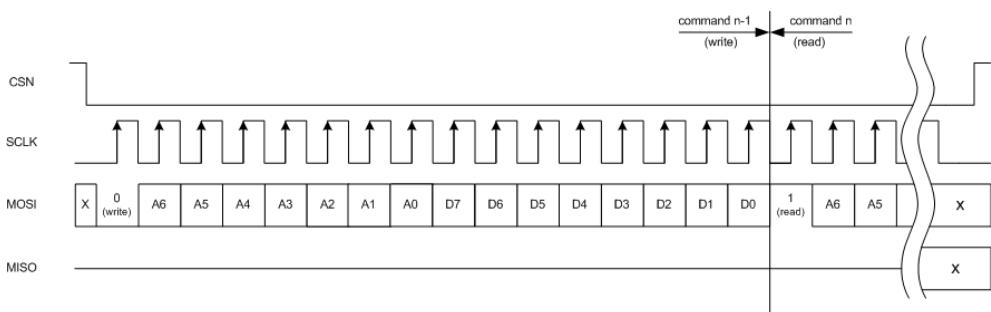

| 6.3.4    | SPI/C-BUS Timing .....                            | 63        |

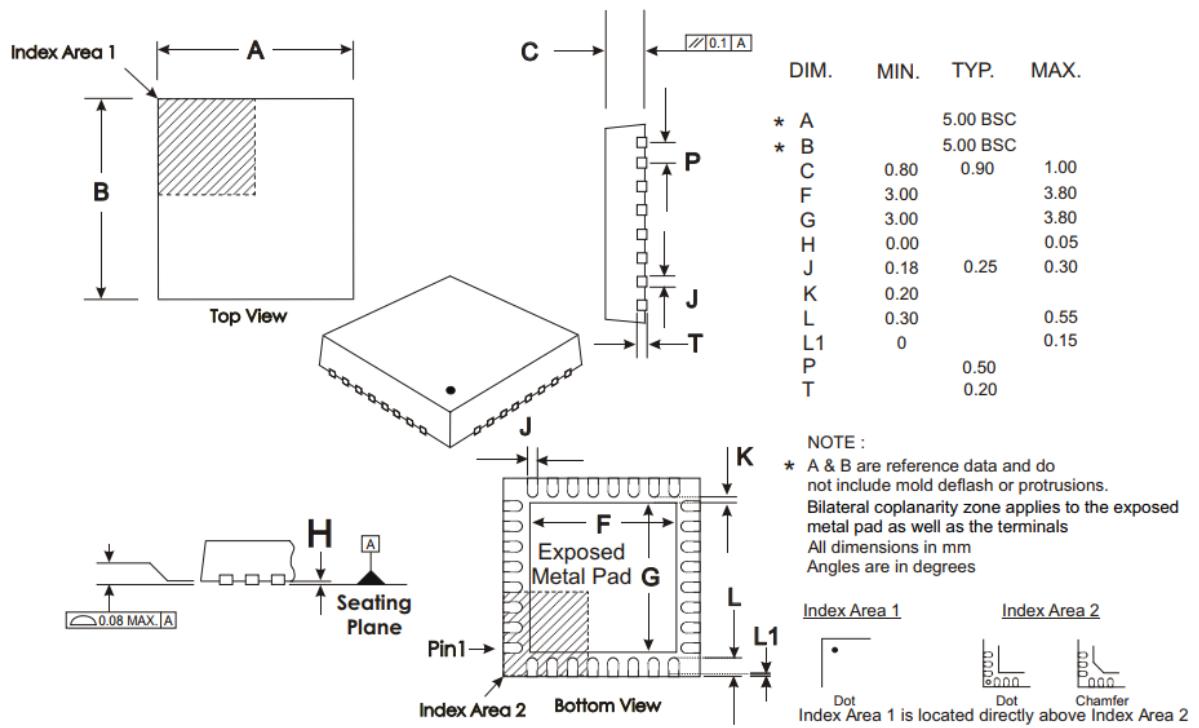

| <b>7</b> | <b>Packaging .....</b>                            | <b>64</b> |

| <u>Table</u>                                                                                             | <u>Page</u> |

|----------------------------------------------------------------------------------------------------------|-------------|

| Table 1 - Recommended External Components (typical example) .....                                        | 5           |

| Table 2 - IF Modes.....                                                                                  | 10          |

| Table 3 - Frequency Synthesizer Tuning in all Frequency Bands .....                                      | 18          |

| Table 4 - Pre ADC Analogue 'roofing' Filter Operating Configurations when used in DRM applications ..... | 19          |

| Table 5 - Default FIR coefficients .....                                                                 | 21          |

| Table 6 - Output Data Rate Configuration .....                                                           | 22          |

| Table 7 - Filter frequency response .....                                                                | 24          |

| Table 8 - Output data interface pins.....                                                                | 25          |

| Table 9 - R-divider recommended values .....                                                             | 30          |

| Table 10 - Loop filter recommended settings.....                                                         | 30          |

| Table 11 - Pilot Signal Coefficients.....                                                                | 37          |

| Table 12 - I2C Timing (Fast mode) .....                                                                  | 60          |

| <u>Figure</u>                                                       | <u>Page</u> |

|---------------------------------------------------------------------|-------------|

| Figure 1 - CMX918 Recommended External Components.....              | 5           |

| Figure 2 - Block Diagram .....                                      | 9           |

| Figure 3 - LF/MF Input Path .....                                   | 11          |

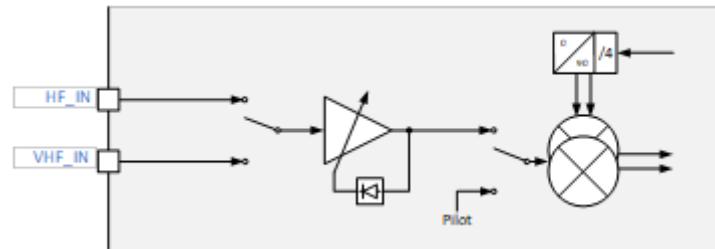

| Figure 4 - HF/ VHF input path .....                                 | 11          |

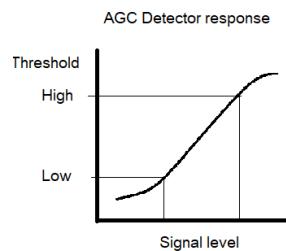

| Figure 5 - AGC Response .....                                       | 13          |

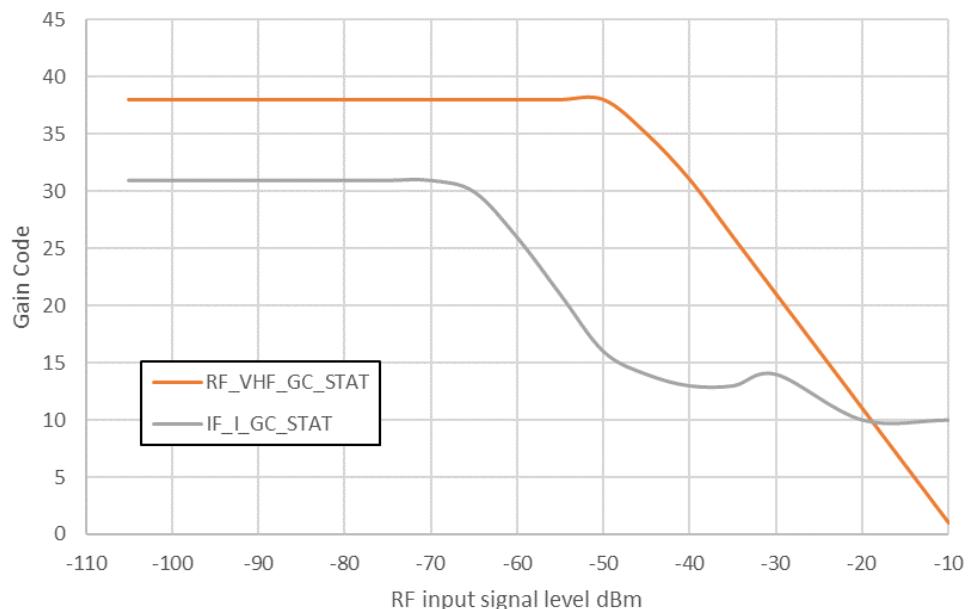

| Figure 6 - Typical HF AGC gain variation with signal level .....    | 13          |

| Figure 7 - LF/MF AGC System .....                                   | 14          |

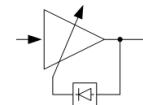

| Figure 8 - HF/VHF AGC System .....                                  | 15          |

| Figure 9 - Synthesizer PLL block diagram .....                      | 16          |

| Figure 10 - Digital Processing Block Diagram .....                  | 20          |

| Figure 11 - DPB Channel Filter response @ BW=10 kHz.....            | 24          |

| Figure 12 - I2S Data Format .....                                   | 25          |

| Figure 13 - SPI Data Format .....                                   | 26          |

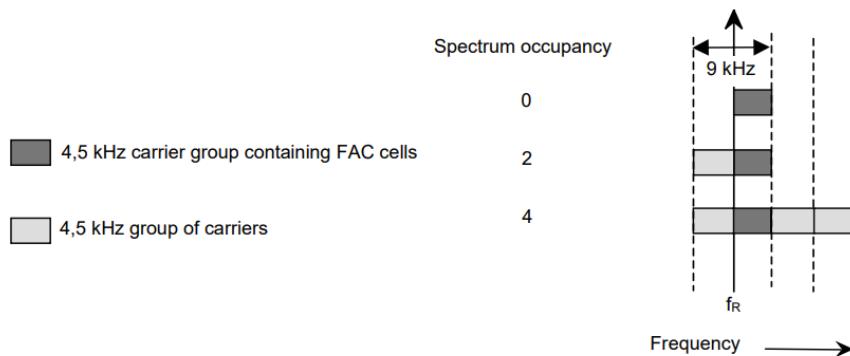

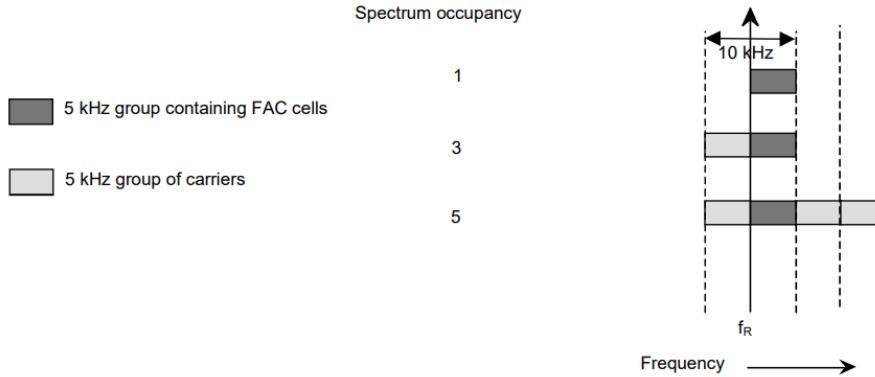

| Figure 14 - Spectrum occupancy for 4.5 kHz modes.....               | 30          |

| Figure 15 - Spectrum occupancy for 5 kHz modes.....                 | 31          |

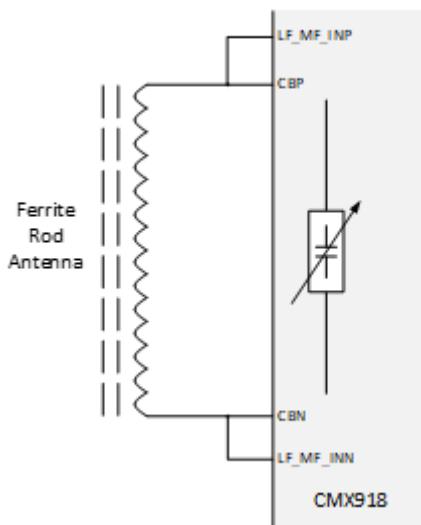

| Figure 16 - Ferrite Rod Antenna - Programmable Capacitor Bank ..... | 32          |

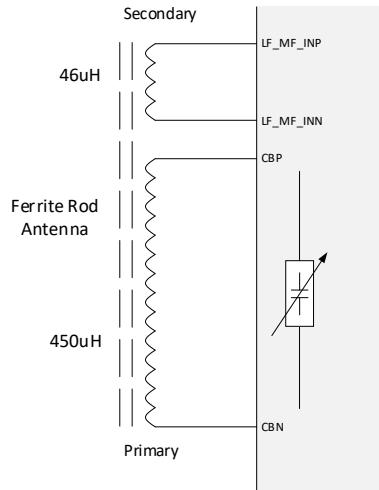

| Figure 17 - Use of ferrite rod antenna with dual windings.....      | 33          |

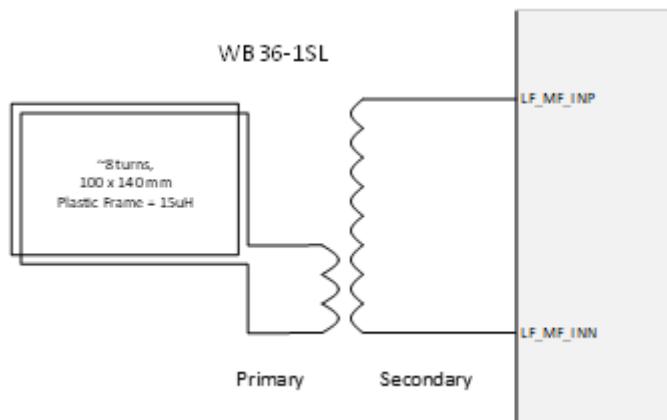

| Figure 18 - Typical Air Loop Antenna .....                          | 33          |

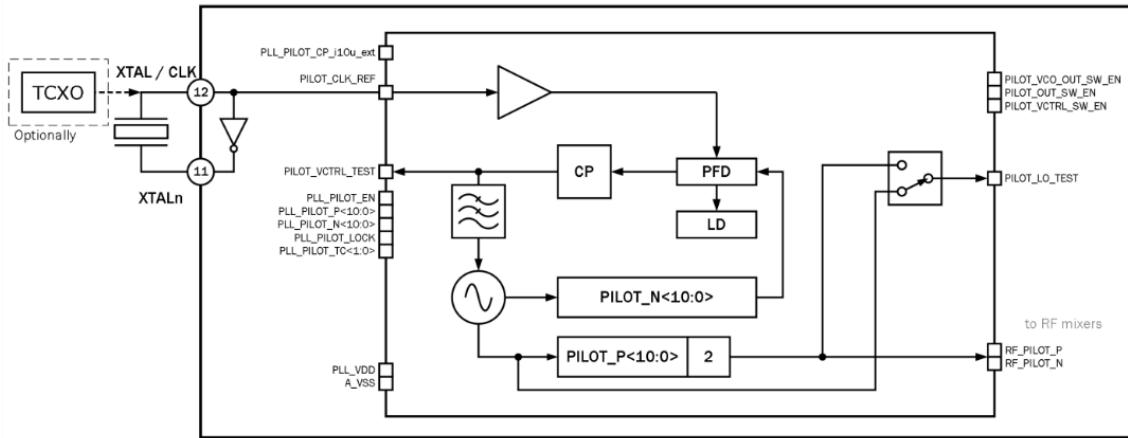

| Figure 19 - Pilot PLL block diagram .....                           | 35          |

| Figure 20 - Calculation of Correction Factors .....                 | 36          |

| Figure 21 – SPI/C-BUS interface selection command .....             | 56          |

| Figure 22 - I2C Start and Stop Conditions .....                     | 57          |

| Figure 23 - Individual Registers Data Writing .....                 | 58          |

| Figure 24 - Individual Register Data Reading .....                  | 58          |

| Figure 25 - Continuous Register Data Writing .....                  | 58          |

| Figure 26 - Continuous Register Data Reading .....                  | 59          |

| Figure 27 - I2C Timing Diagram.....                                 | 59          |

| Figure 28 - Individual Register Writing .....                       | 61          |

| Figure 29 - Single Register Reading.....                            | 61          |

| Figure 30 - Burst Data Writing .....                                | 62          |

| Figure 31 - Burst Data Reading .....                                | 62          |

| Figure 32 - Burst Data Writing and Reading .....                    | 62          |

| Figure 33 – SPI/C-BUS Timing .....                                  | 63          |

| Figure 34 - Q5 Mechanical Outline .....                             | 64          |

**History**

| <b>Version</b> | <b>Changes</b>                               | <b>Date</b>   |

|----------------|----------------------------------------------|---------------|

| 1.0            | First full release – Provisional Information | December 2023 |

| 2.0            | Updated for product launch                   | January 2026  |

## 2 Recommended External Components

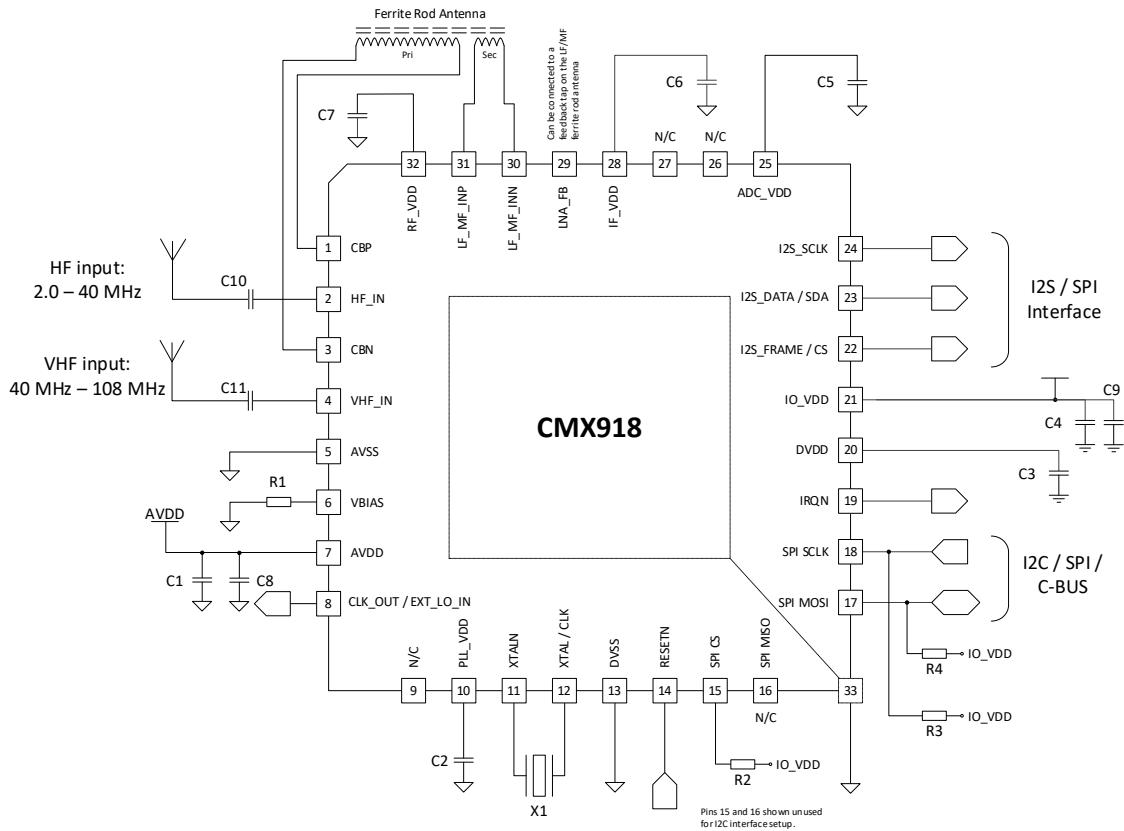

Figure 1 - CMX918 Recommended External Components

Table 1 - Recommended External Components (typical example)

| Component | Value            | Tolerance | Notes                                      |

|-----------|------------------|-----------|--------------------------------------------|

| C1        | 10 nF >10 V X7R  | ±10 %     | AVDD Supply voltage filter capacitor       |

| C8        | 1 µF >10 V X5R   | ±10 %     | AVDD Supply voltage filter capacitor       |

| C2        | 1 µF >10 V X5R   | ±10 %     | PLL_VDD LDO regulator filter capacitor     |

| C3        | 1 µF >10 V X5R   | ±10 %     | DVDD LDO regulator filter capacitor        |

| C4        | 10 nF >10 V X7R  | ±10 %     | IO_VDD Supply voltage filter capacitor     |

| C9        | 1 µF >10 V X5R   | ±10 %     | IO_VDD Supply voltage filter capacitor     |

| C5        | 1 µF >10 V X5R   | ±10 %     | ADC_VDD LDO regulator filter capacitor     |

| C6        | 1 µF >10 V X5R   | ±10 %     | IF_VDD LDO regulator filter capacitor      |

| C7        | 1 µF >10 V X5R   | ±10 %     | RF_VDD LDO regulator filter capacitor      |

| X1        | 38.4 MHz         | ±20 ppm * | 38.4 MHz GSX-223/X SM Crystal 6 pF MP10435 |

| R1        | 61.9 kOhm        | ± 1 %     | Reference resistor                         |

| R2        | 47 kOhm          | ± 1 %     | Pull-up resistor                           |

| R3-R4     | 4.7 kOhm         | ± 1 %     | Pull-up resistor                           |

| C10       | 100 nF >16 V X7R | ± 10 %    | HF input dc blocking capacitor             |

| C11       | 22 nF >16 V X7R  | ± 10 %    | VHF input dc blocking capacitor            |

## Notes (applicable to Figure 1 / Table 1):

1. X1 can be a crystal or an external clock source (e.g. TCXO); this will depend on the application. The tracks between the crystal and the device pins should be as short as possible to achieve maximum stability and best start up performance. By default, operation with a 38.4 MHz crystal is selected.

2. Crystal oscillator tolerance depends on demodulator requirements

3. The above shows connections for I2C control mode. For SPI / C-BUS operation, omit R2, R3 and R4. Pins 15 & 16 are then also included in the control interface.

4. Nominal values of pull up resistors R3-R4 depend on the total capacitance on the bus and operating frequency.

5. Recommended R & C component size is 0402 (Imperial).

6. For the parallel combinations of C1/C8 (AVDD) and C4/C9 (IO\_VDD), the smaller value should be located closest to the IC pin. It is recommended that a larger bulk decoupler ( $>10 \mu\text{F}$ ) is also implemented on each of these supplies (i.e. at the output of a voltage regulator).

Pins 5 and 33 (Centre tab, AVSS) must both be connected to analogue ground in the PCB layout. They are not connected together within the CMX918.

### 3 Pin and Signal List

| Pin No. | Signal Name        | Type | DC level (V) | Description                                                                                                                                            |

|---------|--------------------|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CBP                | AO   | -            | Capacitor bank positive output                                                                                                                         |

| 2       | HF_IN              | AI   | 0.8          | HF band amplifier input                                                                                                                                |

| 3       | CBN                | AO   | -            | Capacitor bank negative output                                                                                                                         |

| 4       | VHF_IN             | AI   | 0.8          | VHF band amplifier input                                                                                                                               |

| 5       | AVSS               | G    | 0            | The negative supply rail (ground) for the analogue on-chip circuits                                                                                    |

| 6       | VBIAS              | AO   | 1.2          | External reference resistor connection for generating reference currents for internal blocks                                                           |

| 7       | AVDD               | P    | 3.3          | The positive 3.3 V supply rail for the analogue on-chip circuits. This pin should be decoupled to AVSS by capacitors mounted close to the device pins. |

| 8       | CLK_OUT /EXT_LO_IN | AIO  | -            | Clock frequency output (19.2 MHz) / Input for external LO or VCO                                                                                       |

| 9       | N/C                |      |              | Not connected                                                                                                                                          |

| 10      | PLL_VDD            | P    | 1.8          | Fractional-N PLL LDO output voltage to external filtering capacitor                                                                                    |

| 11      | XTALN              | AIO  | 0.7          | The output of the on-chip crystal oscillator inverter.                                                                                                 |

| 12      | XTALP/CLK          | AIO  | 0.7          | The input to the oscillator inverter from the crystal circuit or external clock source.                                                                |

| 13      | DVSS               | G    | 0            | The negative supply rail (ground) for the digital on-chip circuits.                                                                                    |

| 14      | RESETN             | DI   | -            | Chip reset to default state (pull low for > 1µs to 'reset') Requires external pull-up to IO_VDD                                                        |

| 15      | SPI CS             | DI   | -            | SPI chip select (active low), used to enable an SPI data read or write operation on the chip. Pull high at start-up for I2C port operation             |

| 16      | SPI MISO           | DO   | -            | SPI serial data 3-state output to host                                                                                                                 |

| 17      | SPI MOSI           | DIO  | -            | SPI serial data input from the host / I2C data input / output.                                                                                         |

| 18      | SPI SCLK           | DI   | -            | SPI clock input from the host / I2C clock input.                                                                                                       |

| 19      | IRQN               | DO   | -            | Interrupt Request (active low). This is driven high internally to IO_VDD.                                                                              |

| 20      | DVDD               | P    | 1.8          | Digital circuits LDO output voltage to external filtering capacitor                                                                                    |

| 21      | IO_VDD             | P    | 1.8 – 3.3    | Supply to SPI / C-BUS / I2C digital interface circuits                                                                                                 |

| Pin No.                                   | Signal Name    | Type | DC level (V)     | Description                                                                   |

|-------------------------------------------|----------------|------|------------------|-------------------------------------------------------------------------------|

| <b>22</b>                                 | I2S_FRAME / CS | DO   | -                | Data Interface: I <sup>2</sup> S frame output / SPI master chip select output |

| <b>23</b>                                 | I2S_DATA / SDA | DO   | -                | Data Interface: I <sup>2</sup> S data output / SPI master data output         |

| <b>24</b>                                 | I2S_SCLK       | DO   | -                | Data Interface: I <sup>2</sup> S clock output / SPI master clock output       |

| <b>25</b>                                 | ADC_VDD        | P    | 1.8              | ADC LDO output voltage to external filtering capacitor                        |

| <b>26</b>                                 | N/C            |      |                  | Not connected                                                                 |

| <b>27</b>                                 | N/C            |      |                  | Not connected                                                                 |

| <b>28</b>                                 | IF_VDD         | P    | 2.7              | IFA LDO output voltage to external filtering capacitor                        |

| <b>29</b>                                 | LNA_FB         | AO   | 1.5 <sup>1</sup> | LF / MF amplifier feedback                                                    |

| <b>30</b>                                 | LF_MF_INN      | AI   | 1.5              | LF / MF band amplifier input – negative                                       |

| <b>31</b>                                 | LF_MF_INP      | AI   | 1.5              | LF / MF band amplifier input – positive                                       |

| <b>32</b>                                 | RF_VDD         | P    | 2.5              | LNA & Mixer LDO output voltage to external filtering capacitor                |

| <b>33<br/>(central<br/>metal<br/>pad)</b> | AVSS           | G    | 0                | Analogue ground                                                               |

Key: AI – analogue input; AO – analogue output; AIO – analogue input/output; DI – digital input; DO – digital push/pull output; DIO – digital input/output; D/AO – digital/analogue output; P – power; G – ground.

<sup>1</sup>If RF\_LNA\_FB\_EN = “1” and RF\_LNA\_FB\_MUX= “0”

## 4 Functional Description

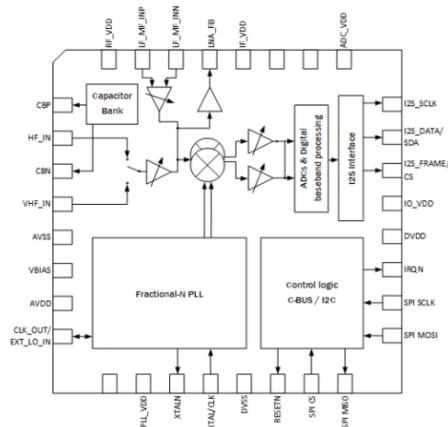

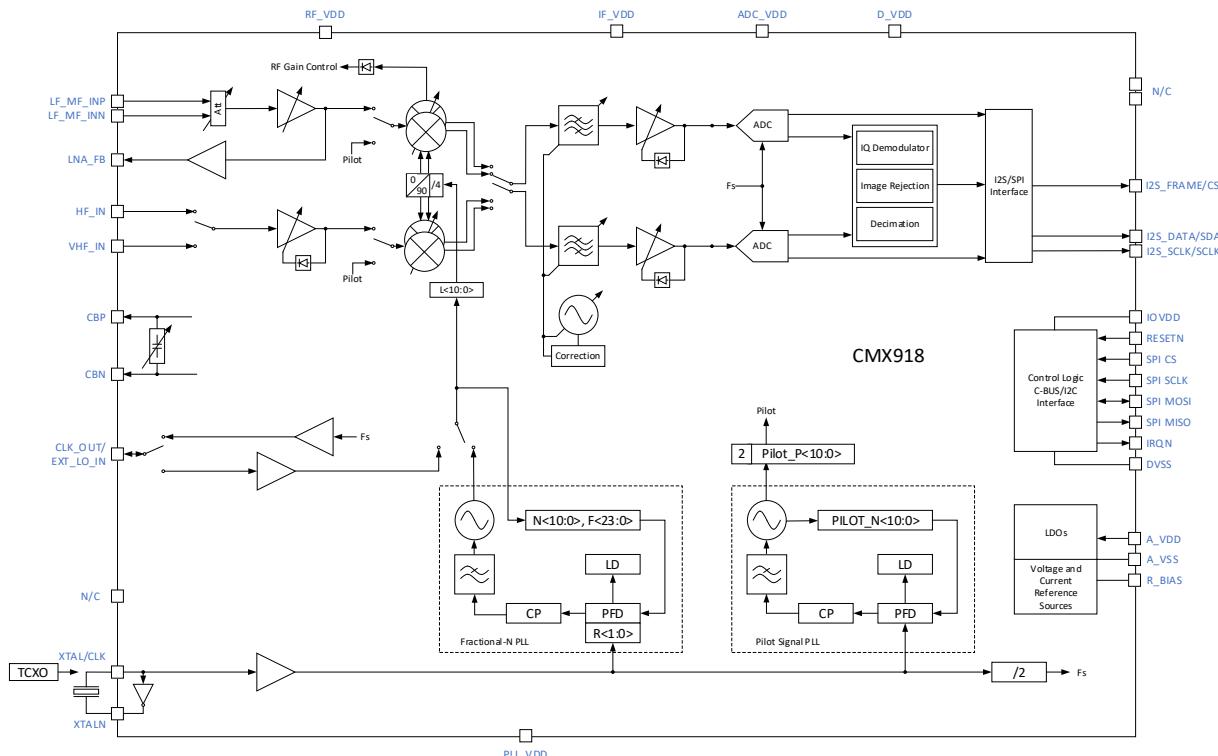

**Figure 2 - Block Diagram**

The CMX918 tuner IC includes the following functional blocks: -

Separate signal inputs with configurable gain settings / AGC for

- LF/MF (150 kHz to 2 MHz) operation (high impedance)

- HF (2 to 40 MHz)

- VHF (40 to 108 MHz)

Frequency mixers convert the signal to a low-IF (96 or 120 kHz) as I/Q channels.

The RF, IF and mixer stages again have configurable gain settings / AGC and filtering.

The IQ channels are then sampled by ADCs after which there is further channel filtering and signal processing within the Digital Processing Block (DPB). The DPB provides a number of features such as RSSI and IQ image rejection optimisation. The signal is converted to digital baseband (zero IF) IQ outputs for further processing and demodulation by an external processor. The digital baseband signal data interface is configurable, further information on this interface can be found in section 4.8.2.

An on chip, flexible fractional-N PLL and VCO provide the receive local oscillator including automatic calibration and spur avoidance functions. A separate integer-N 'Pilot' PLL may be used to generate test signals.

A reference input supports either crystal (default) or TCXO operation.

On-chip voltage regulators are provided for each system block for low noise operation and minimising external component count.

The IC is highly configurable via the control logic block, providing multiple control and monitoring functions via the extensive register functions. Basic operation however requires few register writes.

#### 4.1 Modulation Modes

The CMX918 supports multi-mode operation, including AM and all the modes of DRM30, via its digital baseband output. In addition, WBFM (including Stereo-WBFM, RDS etc.) and DRM+ are supported at VHF.

The receiver RF front ends (LNA + IQ Mixer) are followed by low-IF filters and programmable gain amplifiers (IFPGA) centred on either 96 kHz or 120 kHz. Suggested options are:

**Table 2 - IF Modes**

| Mode          | IF Frequency (kHz) | Filter bandwidth (kHz) |

|---------------|--------------------|------------------------|

| AM / DRM30    | 96                 | 5/10/20                |

| AM / DRM30    | 120                | 5/10/20                |

| FM / DRM+     | 96                 | 100                    |

| FM / DRM+     | 120                | 100                    |

| Analogue WBFM | 120                | 200                    |

When used in DRM30 and DRM+ broadcasting applications, a choice of different bandwidths are available:

- LF/MF 4.5 kHz – Allows a simulcast with the lower-sideband of a 9 kHz raster channel used for AM, with a 4.5 kHz DRM signal occupying the area traditionally taken by the upper-sideband

- LF/MF 5 kHz - Allows a simulcast with the lower-sideband of a 10 kHz raster channel used for AM, with a 5.0 kHz DRM signal occupying the area traditionally taken by the upper-sideband

- LF/MF 9 kHz – DRM uses a standard bandwidth of an ITU region 1 or 3 broadcast channel, may be used as digital only or with an analogue simulcast

- LF/MF 10 kHz- DRM uses a standard bandwidth of an ITU region 2 broadcast channel, may be used as digital only or with an analogue simulcast

- HF 10kHz DRM uses a full worldwide broadcast channel on a 5kHz channel raster

- LF/MF 18 kHz - a double bandwidth region 1 or 3 channel, offers highest audio quality (for DRM30) and multichannel broadcast ability

- LF/MF 20 kHz - a double bandwidth region 2 channel, offers highest audio quality (for DRM30) and multichannel broadcast ability

- VHF 100 kHz for DRM+ allows four multiplexed audio channels or one low-definition video channel

- VHF 200 kHz - analogue FM. The channel is capable of supporting Stereo WBFM, RDS and any other sub-carrier information systems deployed in legacy broadcasting systems on VHF around the world.

The CMX918 supports 5, 10, 20, 100 and 200 kHz bandwidths. 4.5, 9 and 18 kHz channels require additional digital filtering to be implemented in the external DSP or baseband demodulation system.

#### 4.2 RF Path

The RF path is intended to receive signals at LF, MF, HF and VHF bands using three inputs:

- A differential, high impedance input for the LF/MF bands (LF\_MF\_INP, LF\_MF\_INN inputs)

- An HF band input (HF\_IN)

- A VHF band input (VHF\_IN).

The HF and VHF bands share the same LNA and mixer but have switched RF inputs. The correct input is selected automatically from entry of the wanted receive frequency, though this can also be manually controlled. The subsequent IF path is then common regardless of operating frequency.

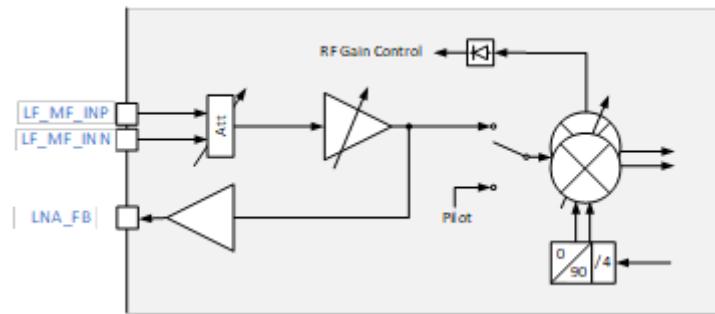

#### 4.2.1 LF / MF Path

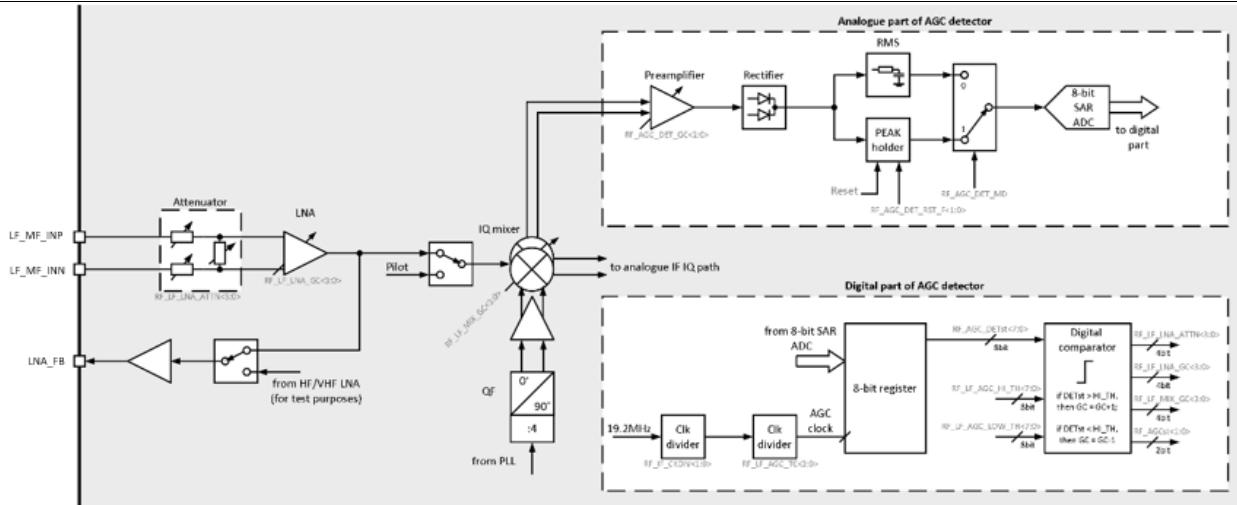

Figure 3 - LF/MF Input Path

The LF/MF RF path consists of following sections:

- LF/MF band LNA attenuator

- LF/MF band LNA

- LF/MF band LNA feedback follower

- LF/MF band quadrature Mixer

- LF/MF band AGC detector

- LF/MF band LO quadrature formers and LO buffers

Each stage in the LF/MF path has switchable gains, as a result there are wide opportunities for optimising the gain/noise/linearity. An attenuator is available at the input of LNA which extends gain control range in the low gain region. An integrated AGC loop can be widely configured in both the amplitude and time domain. Each block can be individually set to automatic or manual control mode (refer to the register description).

An embedded tuneable capacitor bank is intended to tune an external resonant ferrite rod antenna, as an alternative to using the broadband feedback winding configuration. This capacitance is connected between outputs CBP and CBN. The LF/MF LNA is designed with a high input impedance.

#### 4.2.2 HF / VHF Path

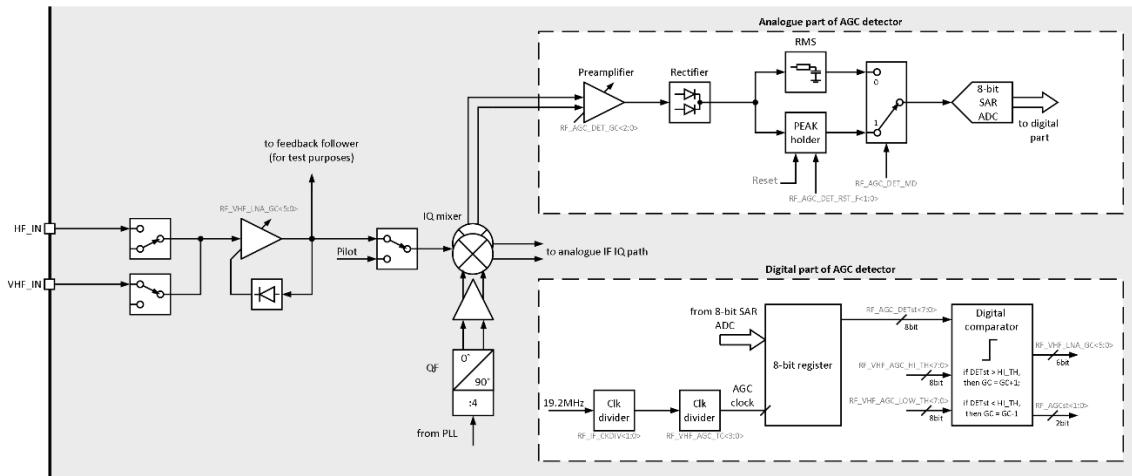

Figure 4 - HF/ VHF input path

The HF/VHF RF path consists of following sections:

- Separate HF/ VHF inputs to allow filter selection

- HF/VHF band LNA

- HF/VHF band quadrature mixer

- HF/VHF band LNA AGC detector

- HF/VHF band LO quadrature former and LO buffers

The HF/VHF LNA has programmable gain, with the mixer having a fixed gain setting. A HF/VHF band dedicated mixer is used to increase system linearity. The AGC loop is constructed around the LNA only. The detection point of the AGC is at the output of the LNA. The AGC can be widely configured in both amplitude and time domain and can be set to automatic or

manual gain control modes. There is an input multiplexer integrated into the LNA gain switching scheme, which is intended to select the input to the LNA: HF\_IN or VHF\_IN. The inputs are designed for a nominal 50 Ohm input impedance, although use with 75 Ohm antenna system will result in minimal loss.

The outputs of the LF/MF and HF/VHF mixers are multiplexed according to the selected operating band. A large tuneable capacitor bank at output of the mixers creates a first order pole to filter out of band noise and interference. The Quadrature LO signal is also multiplexed to the corresponding mixer input in accordance with the selected frequency band.

The RF section contains a dedicated LDO regulator and bias current source.

#### 4.3 IF path description

The Intermediate frequency (IF) path is intended to amplify the down converted differential signals from the IQ mixer and to filter out-of-band components. The IF path has two channels, an 'I' channel and a 'Q' channel; each channel consists of two stages of programmable gain amplifier (PGA) each with a tuneable upper cut-off frequency, an amplitude detector, and a DC offset compensation block. See register description document and 6.1.3 Operating Characteristics for filter details.

The voltage gain in the respective channel is regulated in the range from -1.6 to 29.3 dB in 1 dB steps.

The DC offset compensation (DCOC) system is an analogue RC high-pass filter and is intended to eliminate flicker noise in the I and Q channels. The analogue DCOC system works continuously, and it is recommended that this it is always enabled.

The IF section contains a dedicated LDO regulator and bias current source.

#### 4.4 Gain Control

Gain control is provided to optimise the dynamic range of the system and prevent over-ranging of the ADC at the output of the analogue stages. Two modes are available: manual gain via the SPI/I2C control interface and automatic mode. In automatic mode there is a two-control loop automatic gain control system (AGC).

- For the LF/MF input, loop one has an attenuator, low-noise amplifier (LNA) and mixer AGC system with a detector connected to the mixer output, in order to monitor the peak amplitude of the mixer output voltage. The LNA and mixer gain is then adjusted to achieve the required mixer output voltage amplitude peak threshold. In this case the AGC is intended to prevent IF stage overload.

- For the HF/VHF input, loop one has a low-noise amplifier (LNA) wideband AGC system with a detector connected to the LNA output / mixer input in order to monitor the peak amplitude of the LNA output voltage. The LNA gain is then adjusted to achieve the required LNA output voltage amplitude peak threshold. LNA AGC is intended to prevent mixer overload.

- Loop two is a pair of intermediate frequency, programmable gain amplifiers (IFPGA) in an AGC system with a detector connected to each IFPGA output / ADC input to monitor amplitude of each IFPGA output voltage (one for the I path, the other for the Q path). The two have essentially identical characteristics but can be controlled independently. The IFPGA gain settings are then adjusted to achieve the required IFPGA output voltage amplitude peak threshold. IFPGA AGC is intended to prevent ADC overload.

Each AGC loop has a temperature compensated diode detector with a typical characteristic as follows; if the output detector level is higher than the high threshold, the gain is reduced. If the output detector level is lower than the low threshold, the gain is increased. This continues until the signal remains between the thresholds. The thresholds should be set with a suitably wide separation to avoid any amplitude modulation content changing the gain yet remaining within the linear range of the detectors. Below a certain input level, the gain will be at maximum, and the low threshold will be exceeded.

**Figure 5 - AGC Response**

For most users, the AGC system can be left in its default automatic mode. The default thresholds however may require adjustment dependent on the modulation mode/type being received, the out of band conditions of the system and specifications trying to be met. A typical characteristic for the reported AGC gain status for HF / VHF operation is shown below, with the RF and IF gains reducing at high RF input levels.

**Figure 6 - Typical HF AGC gain variation with signal level**

Note: The \$1E - IF\_Q\_GC\_STAT response will be similar to that of the I channel.

In manual mode the gains of both the LNA output and IFPGA AGC peak thresholds are programmable via the SPI/I2C control interface. The triggering of the upper or lower threshold for each loop is indicated by separate status bits in the AGC status register. The AGC detector levels can be read directly if required.

The AGC loops are widely configurable (for details refer to the register description).

Figure 7 - LF/MF AGC System

The following settings and statuses are available for the LF/MF signal path:

- Automatic or manual gain control mode (register \$0C – RF\_GC\_CTL provides separate control bits for attenuator, LNA and mixer; by default this is set to automatic mode for the LNA and mixer, and manual mode for the attenuator). If a block is in manual mode, then the AGC skips it during operation.

- The order of gain switching stages (register \$3C – RF\_LF\_AGC\_CTL)

- Each stage has its min/max gain code selection limits in automatic mode (registers \$3D – RF\_LF\_ATTN for the attenuator, \$3E – RF\_LF\_LNA\_GTH for the LNA and \$3F – RF\_LF\_MIX\_GTH for the mixer). The gain of the block is changed only after the preceding block has reached GMIN or GMAX. Only one block is being regulated at the time.

- Programmable high and low thresholds (registers \$11 – RF\_LF\_AGC\_HI\_TH and \$12 – RF\_LF\_AGC\_LOW\_TH)

- Programmable detector type (register \$3C – RF\_LF\_AGC\_CTL, peak or RMS) and gain (register \$41 – RF\_AGC\_DET\_GC)

- Peak detector reset time and reset force (register \$A1 – RF\_AGC\_DET\_CTL)

- Detector value status (register \$3B – RF\_DET\_STAT) – the value compared to the selected thresholds.

- AGC status (register \$19 – RF\_AGC\_STAT) indicates whether a signal is between thresholds / gain to be decreased / gain to be increased / AGC threshold fault.

- AGC clock frequency (register \$40 – RF\_LF\_AGC\_TC for time constant adjustment and \$45 for clock division ratio)

- Status of gain selected by AGC (registers \$17 – RF\_LF\_ATTN\_STAT for attenuator, \$18 – RF\_LF\_GC\_STAT for LNA and mixer)

- Pause mode (register \$0C – RF\_GC\_CTL). Detector output is being updated, but the gain control codes are frozen in the last state.

- In manual gain control mode the AGC detector can be disabled for power saving (register \$9F – RF\_AGC\_CTL\_1)

- Gain control in manual mode (registers \$16 – LF\_ATTN\_GC for attenuator gain, \$13 – RF\_LF\_GC for LNA gain, \$0C – RF\_GC\_CTL for mixer gain).

Figure 8 - HF/VHF AGC System

The following settings and statuses are available for the HF/VHF signal path:

- Automatic or manual gain control mode (register \$0C – RF\_GC\_CTL, LNA only)

- Min/max gain code selection limits in automatic mode (registers \$37 – RF\_VHF\_LNA\_GMAX and \$38 – RF\_VHF\_LNA\_GMIN)

- Programmable high and low thresholds (registers \$0D – RF\_VHF\_AGC\_HI\_TH and \$0E – RF\_VHF\_AGC\_LOW\_TH)

- Programmable detector type (register \$3C – RF\_LF\_AGC\_CTL, peak or RMS) and gain (register \$41 – RF\_AGC\_DET\_GC)

- Peak detector reset time and reset force (register \$A1 – RF\_AGC\_DET\_CTL)

- Detector value status (register \$3B – RF\_DET\_STAT) – the value compared to selected thresholds.

- AGC status (register \$19 – RF\_AGC\_STAT) indicates whether signal is between thresholds / gain to be decreased / gain to be increased / AGC threshold fault.

- AGC clock frequency (register \$39 – RF\_VHF\_AGC\_TC for time constant adjustment and \$45 for clock division ratio)

- Status of gain selected by AGC (register \$10 – RF\_VHF\_GC\_STAT)

- Pause mode (register \$0C – RF\_GC\_CTL). The detector output continues to be updated, but the gain control code is frozen in the last state.

- In manual gain control mode, the AGC detector can be disabled for power saving (register \$9F – RF\_AGC\_CTL\_1).

- Gain control in manual mode (register \$0F – RF\_VHF\_LNA\_GC).

The following settings and statuses are available for the IFPGA stages:

- Automatic or manual gain control mode (register \$1A – IF\_GC\_CTL)

- Min/max gain code selection limits in automatic mode (registers \$43 – IF\_AGC\_GMAX and \$44 – IF\_AGC\_GMIN)

- Programmable high and low thresholds (registers \$1B – IF\_AGC\_HI\_TH and \$1C – IF\_AGC\_LOW\_TH)

- Programmable detector type (register \$42 – IF\_AGC\_CTL, peak or RMS)

- Peak detector reset time and reset force (register \$A8 – IF\_AGC\_DET\_CTL)

- Detector value status (registers \$46 – IF\_I\_DET\_STAT and \$47 – IF\_Q\_DET\_STAT) – the value compared to selected thresholds.

- AGC mode (register \$42 – IF\_AGC\_CTL). By default, both I and Q channels are tracked and the minimum result for gain control is applied for both channels. It is also possible to select one channel to be tracked, while the result will be applied for both channels, or to regulate gain independently for I and Q channels.

- AGC status (register \$1F – IF\_AGC\_STAT) indicates whether a signal is between thresholds / gain to be decreased / gain to be increased / AGC threshold fault.

- AGC clock frequency (register \$45 – IF\_AGC\_TC for clock division ratio and time constant adjustment).

- Status of gain selected by AGC (registers \$1D – IF\_I\_GC\_STAT and \$1E – IF\_Q\_GC\_STAT)

- Pause mode (register \$1A – IF\_GC\_CTL). Detector output is being updated, but the gain control codes are frozen in the last state.

- In manual gain control mode, the AGC detector can be disabled for power saving (register \$A6 – IF\_AGC\_CTL\_1)

- Gain control in manual mode (registers \$20 – IF\_I\_GC and \$21 – IF\_Q\_GC)

#### 4.5 ADC description

The CMX918 contains a quadrature IF path, with a dual channel (I and Q) sigma-delta ADC. ADC sampling occurs at 19.2 MHz frequency with a 38.4 MHz reference.

The ADC section contains a dedicated LDO and bias current source.

#### 4.6 Local Oscillator / Synthesizer

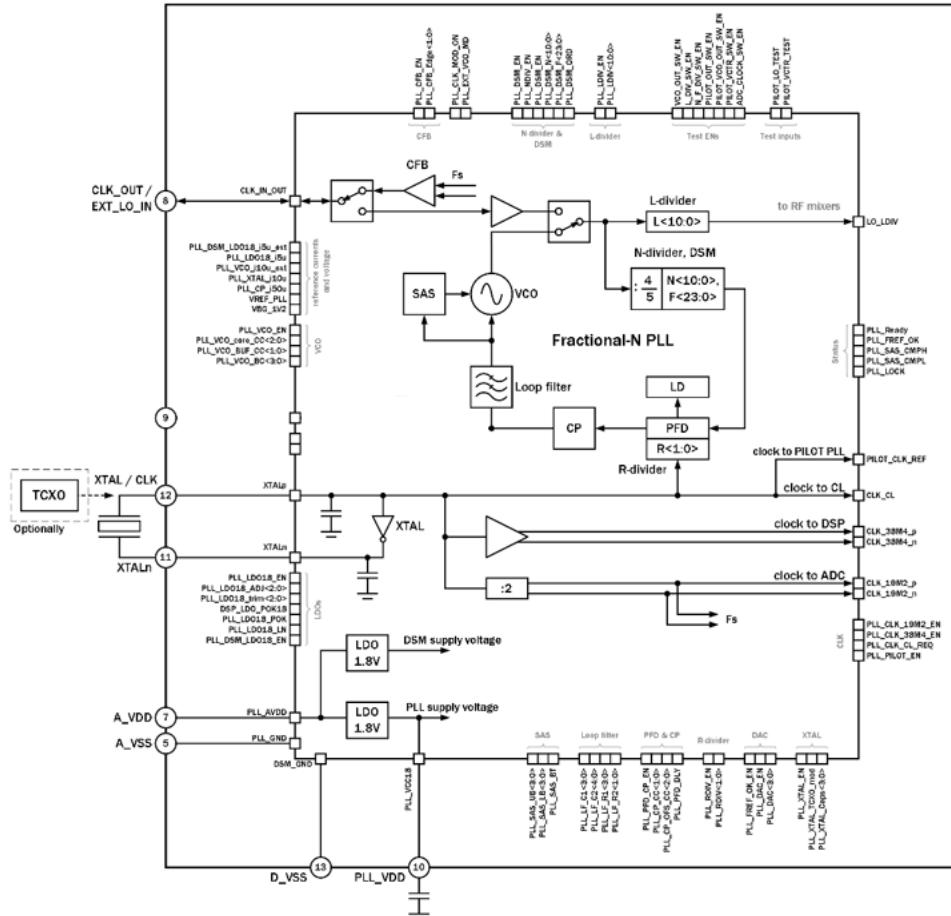

Figure 9 - Synthesizer PLL block diagram

The local oscillator for the mixer is provided by a Fractional-N phase-locked loop frequency synthesizer (PLL). This includes a fully integrated 1.5 – 1.9 GHz Voltage Controlled Oscillator with low tuning gain and good phase noise performance. Optionally, an external LO source can be applied. The PLL operates with a reference frequency of 38.4 MHz, provided from a crystal (with an internal amplifier and tuneable feedback capacitors for frequency adjustment), or an external TCXO source.

The PLL comparison frequency is derived from the reference, dividing by 1, 2, 3 or 4. The feedback N-divider from the VCO to the phase / frequency detector has an integer range of 16 to 2047 and can work in integer mode or in 24-bit fractional mode (fractional range defined as 0-1).

The VCO output is then routed to the quadrature mixer via the L-divider, with a range of 4 to 2047. The mixer has an in-built division by 4 to obtain accurate quadrature outputs (the Quadrature Former). The phase-frequency detector has a built-in digital lock detector circuit. The charge pump has adjustable output current and offset current. There is an

integrated 3<sup>rd</sup> order loop filter, with a nominal loop bandwidth of 200 kHz; adjustable values of resistance and capacitance are available to optimize the loop phase-noise response.

The PLL block consists of:

- A dedicated PLL 1.8 V LDO

- A separate 1.8 V LDO for DSM

- Programmable XTAL oscillator / TCXO input

- Reference-divider (RDIV)

- Reference frequency indicator (FREF\_OK)

- Voltage-controlled oscillator (VCO)

- N-divider (including prescaler) and Fractional Delta-Sigma Modulator (NDIV + DSM)

- Phase-Frequency Detector, charge pump and lock detector (PFD + CP + LD)

- Loop filter

- L-divider (LDIV)

- Voltage detector for SAS (VCO Sub-band Auto-selection System)

- CLK\_BUFS – Clock buffers to other circuit blocks

- Clock frequency buffer (CFB)

The default settings of the CMX918 PLL system are sufficient for the majority of users and many parameters can be configured automatically. All that is required is to program all PLL parameters is to enter the receive frequency into the Fc registers and execute the PLL\_CALC function. Full access to the more detailed PLL parameters is available via the registers for more advanced users (for details refer to the user manual).

#### 4.6.1 PLL programming

To reconfigure the PLL, the following procedure is recommended:

- Select normal operation mode: \$03 – IC\_MODE, Mode<2:0> = "3"

- Select the IF frequency sign: write \$08 – Fc\_2<7>, Fif\_SIGN = "0" or Fif\_SIGN = "1" to the IC registers

- Write the IF frequency value (Fif, 96 kHz or 120 kHz) to the IC registers: \$08 – Fc\_2<6>, Fif = "0" or Fif = "1"

- Write the Carrier frequency (Fc, value in 0.1 kHz) to the IC registers: Fc 2, Fc 1 and Fc 0 <20:0>

- Execute the LO PLL tuning procedure: set PLL\_CALC\_EXE = "1" in register \$29 – AUTO\_EXE, (\$29 – AUTO\_EXE<1> PLL\_SAS\_EXE will be executed automatically along with PLL\_CALC\_EXE). Wait until PLL\_CALC\_EXE and PLL\_SAS\_EXE are reset to "0".

All the advanced features of the PLL are then automatically calculated and configured (e.g. the N, fractional F and L divider values, along with VCO calibration). The resulting N, F and L values can be read back if required via the applicable registers (for details refer to the user manual).

Note that the LO must be operated above the wanted frequency (Fif\_SIGN = 1) for 150 - 281 kHz reception.

To reconfigure PLL in manual mode the following procedure is recommended:

- Select normal operation mode: \$03 – IC\_MODE, Mode<2:0> = "3".

- Select the IF frequency sign: write \$08 – Fc\_2<7>, Fif\_SIGN = "0" or Fif\_SIGN = "1" to the IC registers

- Write the IF frequency value (Fif, 96kHz or 120kHz) to the IC registers: \$08 – Fc\_2<6>, Fif = "0" or Fif = "1"

- Write the Receive Carrier frequency (Fc, value in 0.1 kHz) to the registers: Fc 2, Fc 1 and Fc 0 <20:0>

- Calculate the values of N, F, L and R coefficients according to the formula:

$$F_{LO} = F_c \pm F_{IF} = (F_{REF} * (N + F/2^{24})) / (4 * L * R)$$

Where:

Fref = Reference frequency (38.4 MHz)

R = Reference divider (RDIV) value

L = L divider value

N, F = Integer and fractional parts of the overall feedback divider value.

The /4 term is fixed and denotes the action of the Quadrature Former in the mixer.

- Write \$2A - PLL\_CTRL<1>, PLL\_LDIV\_MD = "0".

- Disable the DSM if F divider value = 0: write \$2A - PLL\_CTRL<0>, PLL\_DSM\_EN = "0".

The values of N, F, L and R can then be written to the IC registers: \$2B/2C (PLL\_DSM\_N<10:0>), \$2D/2E/2F (PLL\_DSM\_F<23:0>), \$31/32 (PLL\_LDIV\_reg<10:0>), \$30 (PLL\_RDIV<1:0>).

#### 4.6.2 VCO Tuning

The integrated VCO has a tuning range of 1500 to 1900 MHz and is coarse tuned to one of 16 bands (SAS - Sub-band Auto-select System) via a switched fixed capacitor bank. Fine PLL adjustment over a sub-band uses a built-in varactor diode.

**Table 3 - Frequency Synthesizer Tuning in all Frequency Bands**

| VCO frequency (MHz) | Quadrature former (mixer) division ratio | L divider division ratio | Local oscillator frequency (MHz) |

|---------------------|------------------------------------------|--------------------------|----------------------------------|

| 1530 - 1848         | 4                                        | 920 - 2040               | 0.19 - 0.5                       |

| 1512 - 1892         | 4                                        | 180 - 760                | 0.5 - 2.30                       |

| 1520 - 1872         | 4                                        | 10 - 167                 | 2.3 - 43                         |

| 1504 - 1880         | 4                                        | 4 - 10                   | 40 - 108.07                      |

A voltage detector within the SAS compares the VCO control voltage with upper and lower thresholds and generates status flags if out of range. The type of threshold is selected by the PLL\_SAS\_BT bit. The voltages of the upper and lower thresholds are selected by PLL\_SAS\_UB<3:0> and PLL\_SAS\_LB<3:0> respectively. If Vctrl is higher than the upper threshold PLL\_SAS\_CMPL = "1". If Vctrl is lower than the lower threshold PLL\_SAS\_CMPL = "1". The PLL\_SAS\_EXE routine can then be reactivated, or the sub-band selection can then be manually incremented appropriately. The purpose of this is to reduce VCO phase noise and to compensate for temperature drift in the VCO.

#### 4.6.3 Clock / Crystal Oscillator

The input reference frequency is 38.4 MHz, chosen to be above the LF/MF/HF bands, but also avoiding harmonics within the VHF broadcast band. Use of other input reference frequencies is not supported. The crystal oscillator uses a Pierce architecture optimized for low power consumption. It also can operate as a buffer for an external TCXO input.

The crystal oscillator has integrated adjustable feedback capacitors to optimise performance. The Reference frequency indicator (PLL\_FREFOK) returns "0" when reference signal frequency is too low or is absent. The recommended crystal is a 38.4MHz GSX-223/X SM Crystal 6pF (Techpoint Golledge MP10435). Alternatively, a recommended TCXO is a 38.4 MHz, 1.8 V GTXO-203 (Techpoint Golledge MP07688). Use of a TCXO gives improved close-in phase noise performance. This TCXO can be supplied from the on-chip 1.8 V regulator output (PLL\_VDD).

The CLK\_BUFBLOCK provides reference clocks for other IC functions such as the ADC, DPB (digital processing block) and CFB (clock frequency buffer). Reference frequencies are:

- $F_{DPB} = F_{REF}$  (38.4 MHz)

- $F_{ADC} = F_{REF}/2$  (19.2 MHz)

- $F_{CFB} = F_{REF}/2$  (19.2 MHz)

Dividing the reference frequency by 2 provides the clock for ADC delta-sigma data sampling at 19.2 Ms/s (Million samples per second). The 16-bit post-decimated sample rate is 19.2 Ms/s  $\div 2^n$ .

The Clock frequency buffer (CFB) is a block which optionally provides an output clock which may be used by the demodulator IC. The output clock frequency is  $F_{CFB} = F_{REF}/2$ . The clock output type is CMOS to the AVDD supply and PLL\_CFB\_edge<1:0> controls the clock output edge speed.

#### 4.6.4 PFD, charge pump, lock detector

The Phase-frequency detector (PFD) and Charge pump (CP) together with the loop filter form a control loop for VCO tuning. The PFD has a built-in digital lock detector.

#### 4.6.5 Integer boundary spur avoidance

An internal routine (\$29 – AUTO\_EXE<0>, PLL\_CALC\_EXE) calculates the appropriate PLL values, including the L divider, automatically from entry of the wanted receive frequency. Within this, if an integer boundary is within 300 kHz of the calculated VCO frequency, the original value of L is changed to L + 1 and N and F recalculated. The values of L are also chosen in such a way as to prevent  $F_{VCO} = F_{LO} \times 4 \times (L + 1)$  being out of the VCO range 1500-1900 MHz.

As  $F_{VCO} = \frac{F_{REF} \times (N+F/2^{24})}{R}$  and  $F_{VCO} = F_{LO} \times 4 \times L$ , for some combinations of FLO and L the result is a small fractional value F that can lead to boundary spurs.

For the chosen FLO and L, a spur offset frequency can be calculated:

$$F_{spur} = F_{REF} \times F/2^{24}.$$

For  $F_{LO} > 52$ MHz however, the flexibility to change the L divide value is unavailable while remaining within the VCO frequency range. The automatic spur avoidance calculation is therefore not applied in this instance.

For operation at VHF, changing between high and low side mixing (IF\_SIGN bit) is an effective method of boundary spur avoidance. This can be implemented by reading the calculated PLL fractional value and checking if this is sufficiently close to zero or one. If it is, the IF\_SIGN can be changed and the PLL values recalculated.

#### 4.7 Signal filtering and down conversion

The wanted signal (Fw) is down converted to the first intermediate frequency (IF = 96 kHz or 120 kHz) and is then filtered by analogue filter blocks. The IF path provides pre-filtering and ADC anti-alias frequency suppression.

The output lower cut-off frequency (Fl) is determined by the DC offset compensation time constant (~6 dB/octave).

The output upper cut-off frequency (Fh) is determined by three RC adjustable poles: one after the mixer and two in the IFPGA (~6 dB/octave each pole). The ADC passband is approximately 220 kHz.

**Table 4 - Pre ADC Analogue ‘roofing’ Filter Operating Configurations when used in DRM applications**

| Configuration                         | Low $F_{cut}$ max (kHz) | IF <sub>centre</sub> (kHz) | High $F_{cut}$ max (kHz) | Channel Bandwidth (kHz) |

|---------------------------------------|-------------------------|----------------------------|--------------------------|-------------------------|

| AM and DRM modes A,B,C,D for LF/MF/HF | 86                      | 96                         | 106                      | 5, 10, 20               |

| AM and DRM modes A,B,C,D for LF/MF/HF | 110                     | 120                        | 130                      | 5, 10, 20               |

| DRM mode E for VHF                    | 46                      | 96                         | 146                      | 100                     |

| DRM mode E for VHF                    | 70                      | 120                        | 170                      | 100                     |

| Stereo WBFM for VHF                   | 20                      | 120                        | 220                      | 200                     |

## 4.8 Digital Processing Block

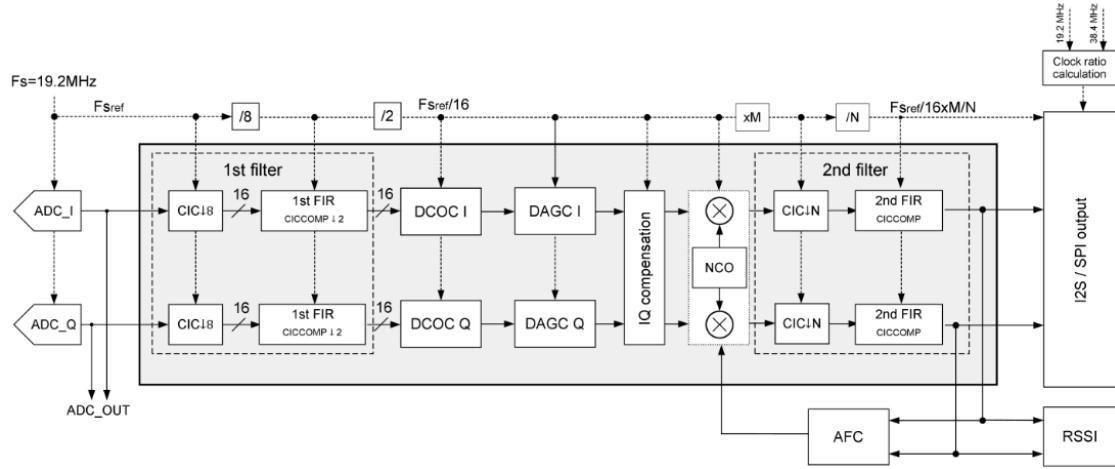

The DPB (digital processing block) implements further decimation and signal filtering from the delta-sigma IQ ADC output. The input is two-channel (I and Q), each channel having a signed bitstream.

**Figure 10 - Digital Processing Block Diagram**

The digital IF filter bandwidth is programmable to 5, 10, 20, 100 or 200 kHz. The image frequency  $F_{\text{Image}}$  is suppressed in the digital domain. The wanted signal is down converted to a zero intermediate frequency ( $F_{\text{IF2}} = 0$  Hz). This is presented as a composite IQ data stream at the I2S/SPI data interface.

All necessary clock signals are formed from the sampling clock  $F_s$  of 19.2MHz. The ADC output signal is filtered and decimated by 8 allowing further processing. The signal then passes through a filter, DC Offset Compensation (DCOC) system and digital automatic gain control amplifier (DAGC).

The first digital filter is implemented as a cascade connection of the filter-decimator (CIC) with a decimation factor of 8 and the FIR filter-compensator (CICCOMP) with a decimation factor of 2.

The DC offset is automatically compensated in the DCOC block. The DPB\_DCOC\_ON register (\$BA - DPB\_CTL\_1<1>) is used to enable the DCOC system (enabled by default). DPB\_DCOC\_MAN (\$C2 - DPB\_DCOC\_CTL<1>) is used to select manual control mode. In manual control mode correction coefficients should be written to DPB\_DCOC\_MAN\_OFS\_I<15:0> (\$C3, \$C4) and DPB\_DCOC\_MAN\_OFS\_Q<15:0> (\$C5, \$C6).

Gain control, as a part of the DPB (DAGC) block, is enabled by DPB\_AGC\_ON (\$BA - DPB\_CTL\_1<0>) and operates in automatic or manual mode (DPB\_AGC\_GC\_MD). DAGC precision and speed are programmable (DPB\_AGC\_GC\_PREC<1:0> and DPB\_AGC\_GC\_GSCL<2:0>). In manual control mode the gain at the input of I and Q channels of the demodulator is set by the \$BC & \$BD - DPB\_AGC\_MAN\_G\_I<10:0> and \$BE & \$BF DPB\_AGC\_MAN\_G\_Q<10:0> registers respectively. Manual mode with 0 dB gain is recommended and is the default mode of operation.

After IQ compensation, the signal is then down converted to the second intermediate frequency ( $F_{\text{IF2}}=0$ ). A second filter after digital down conversion is determined by the pair of filter-decimators (CIC) with programmable decimation factor (N) and FIR filter-compensator (CICCOMP). Further adjustment of the output rate is given by the upsample factor (M) which is applied by repeating sample values into the second stage filter. The final signal is then output as 16-bit words via the data port to the host processor for further filtering and demodulation.

The coefficients for the first and second FIR filters are reprogrammable using \$D7 - DPB\_FIR\_MEM\_ADDR<5:0> (index pointer), \$D8 - DPB\_FIR\_MEM\_DATA\_1<7:0> (coefficient MSB) and \$D9 - DPB\_FIR\_MEM\_DATA\_0<7:0> (coefficient LSB). Coefficients are loaded as signed 16-bit values and the internal memory for each coefficient is updated when the LSB is written. They can be accessed in any order and can also be read back, but the index pointer does not increment automatically so must be explicitly written for every access.

Both filters must have symmetrical impulse responses, with further restrictions as given below. Only the first half of each set of coefficients should be loaded and they are then mirrored internally to form the complete sets. The first FIR has a polyphase architecture and requires its coefficients to be de-interleaved into two phases for loading.

- First FIR: 31 coefficients

- Load first 16 only in polyphase order using \$D7 - DPB\_FIR\_MEM\_ADDR = 0 to 7 (1st phase) and 8 to 15 (2nd phase)

- To obtain 0 dB DC gain, scaling should be such that the sum of the full set (31 coefficients) =  $2^{15}$

- Second FIR: 80 coefficients

- Load first 40 only in conventional form using \$D7 - DPB\_FIR\_MEM\_ADDR = 16 to 55

- Absolute values of the first 20 coefficients must be less than  $2^{12}$

- Absolute values of the second 20 coefficients must be less than  $2^{14}$

- To obtain 0 dB DC gain, scaling should be such that the sum of the full set (80 coefficients) =  $2^{16}$

The default FIR coefficients can be reloaded from the table below.

**Table 5 - Default FIR coefficients**

|         |        |        |        |       |        |        |        |       |

|---------|--------|--------|--------|-------|--------|--------|--------|-------|

| A[56] = | -13,   | -137,  | -56,   | 573,  | -60,   | -1824, | 1284,  | 8378, |

|         | -61,   | -173,  | 249,   | 562,  | -1113, | -1190, | 4998,  | 9744, |

|         | 28,    | 44,    | 54,    | 38,   | -11,   | -82,   | -146,  | -163, |

|         | -107,  | 16,    | 157,   | 244,  | 211,   | 43,    | -201,  | -402, |

|         | -435,  | -236,  | 142,   | 531,  | 716,   | 545,   | 28,    | -629, |

|         | -1092, | -1057, | -424,  | 602,  | 1551,  | 1876,  | 1229,  | -310, |

|         | -2162, | -3410, | -3145, | -870, | 3214,  | 8185,  | 12674, | 15332 |

## 4.8.1 Digital processing operating modes

Table 6 - Output Data Rate Configuration

| Bandwidth (kHz) | N  | M | Over sampling | Sample rate (ks/s) | Clock rate     | Data and clock rate (kb/s) | Frame rate (ks/s) |

|-----------------|----|---|---------------|--------------------|----------------|----------------------------|-------------------|

| 5               | 50 | 1 | 4.8           | 24                 | 2 (decreased)  | 1920                       | 48                |

|                 |    |   |               |                    | 4 (normal)     | 3840                       | 96                |

|                 |    |   |               |                    | 10 (increased) | 9600                       | 240               |

|                 |    |   | 2.4           | 12                 | 4 (decreased)  | 1920                       | 48                |

|                 |    |   |               |                    | 8 (normal)     | 3840                       | 96                |

|                 |    |   |               |                    | 20 (increased) | 9600                       | 240               |

| 10              | 25 | 1 | 4.8           | 48                 | 1 (decreased)  | 1920                       | 48                |

|                 |    |   |               |                    | 2 (normal)     | 3840                       | 96                |

|                 |    |   |               |                    | 5 (increased)  | 9600                       | 240               |

|                 |    |   | 2.4           | 24                 | 2 (decreased)  | 1920                       | 48                |

|                 |    |   |               |                    | 4 (normal)     | 3840                       | 96                |

|                 |    |   |               |                    | 10 (increased) | 9600                       | 240               |

| Bandwidth (kHz) | N  | M | Over sampling | Sample rate (ks/s) | Clock rate      | Data and clock rate (kb/s) | Frame rate (ks/s) |

|-----------------|----|---|---------------|--------------------|-----------------|----------------------------|-------------------|

| 20              | 25 | 2 | 4.8           | 96                 | 0.5 (decreased) | 1920                       | 48                |

|                 |    |   |               |                    | 1 (normal)      | 3840                       | 96                |

|                 |    |   |               |                    | 5 (increased)   | 19200                      | 480               |

|                 | 5  | 2 | 2.4           | 48                 | 1 (decreased)   | 1920                       | 48                |

|                 |    |   |               |                    | 2 (normal)      | 3840                       | 96                |

|                 |    |   |               |                    | 5 (increased)   | 9600                       | 240               |

| 100             | 5  | 2 | 4.8           | 480                | 0.5 (decreased) | 9600                       | 240               |

|                 |    |   |               |                    | 1 (normal)      | 19200                      | 480               |

|                 | 5  | 4 | 2.4           | 240                | 0.5 (decreased) | 4800                       | 120               |

|                 |    |   |               |                    | 1 (normal)      | 9600                       | 240               |

| 200             | 5  | 4 | 4.8           | 960                | 0.5 (decreased) | 19200                      | 480               |

|                 |    |   |               |                    | 1 (normal)      | 38400                      | 960               |

|                 | 5  | 4 | 2.4           | 480                | 0.5 (decreased) | 9600                       | 240               |

|                 |    |   |               |                    | 1 (normal)      | 19200                      | 480               |

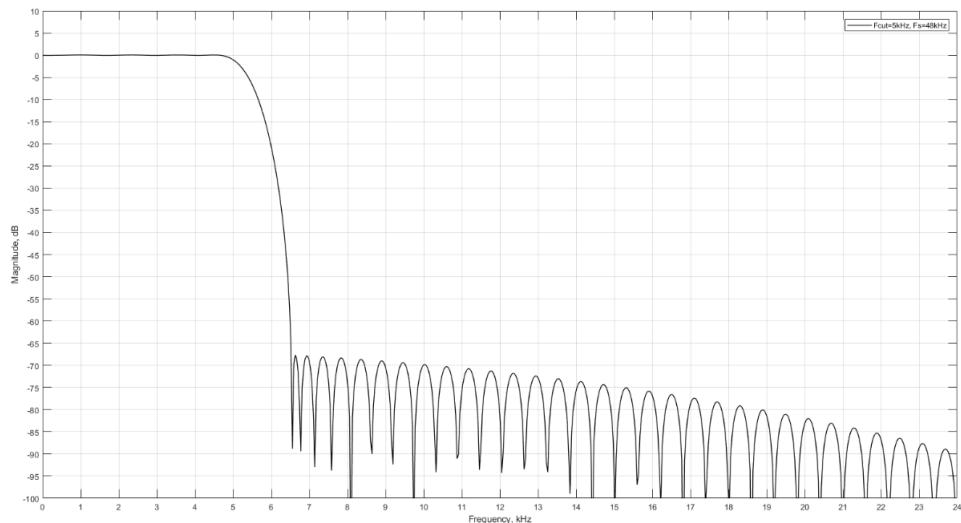

**Figure 11 - DPB Channel Filter response @ BW=10 kHz**

**Table 7 - Filter frequency response**

| Bandwidth (kHz) | Target rejection (dB) | Frequency point (kHz) |

|-----------------|-----------------------|-----------------------|

| 5               | -1                    | 2.5                   |

|                 | -50                   | 3.22                  |

| 10              | -1                    | 5                     |

|                 | -50                   | 6.44                  |

| 20              | -1                    | 10                    |

|                 | -50                   | 12.88                 |

| 100             | -1                    | 50                    |

|                 | -50                   | 64.4                  |

| 200             | -1                    | 100                   |

|                 | -50                   | 128.8                 |

The source of the input data for the RSSI (Received Signal Strength Indicator) system is the output signal of the decimation filter stage; the power measurement is therefore carried out within the output filter band. The measured value of the signal power is presented in “dB” in the DPB\_RSSI\_STAT\_1(0) registers \$D0/D1. A correction offset can be added for the HF/VHF bands in DPB\_RSSI\_REF\_HF\_1(0) in registers \$CE/CF and for the LF/MF bands in DPB\_RSSI\_REF\_LF\_1(0) in registers \$DD/DE.

The AFC system is enabled by DPB\_AFC\_ON. The AFC structure is based on a CORDIC-based frequency discriminator and an integral loop filter in the feedback path. The output of the last FIR is used as input to the AFC system. Correction is done by adding the loop filter output to the frequency controlling word of the digital mixer. Its correction range and precision / speed can be adjusted in the registers.

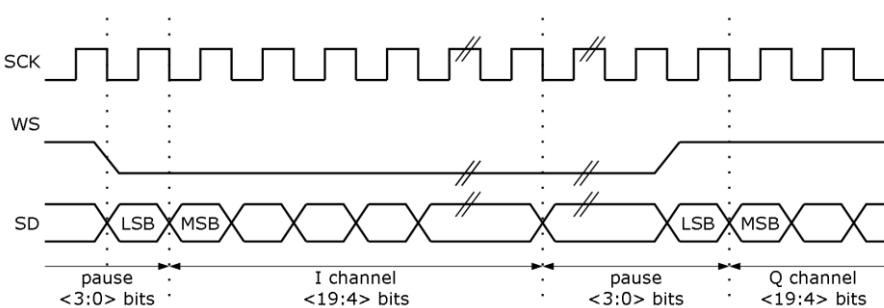

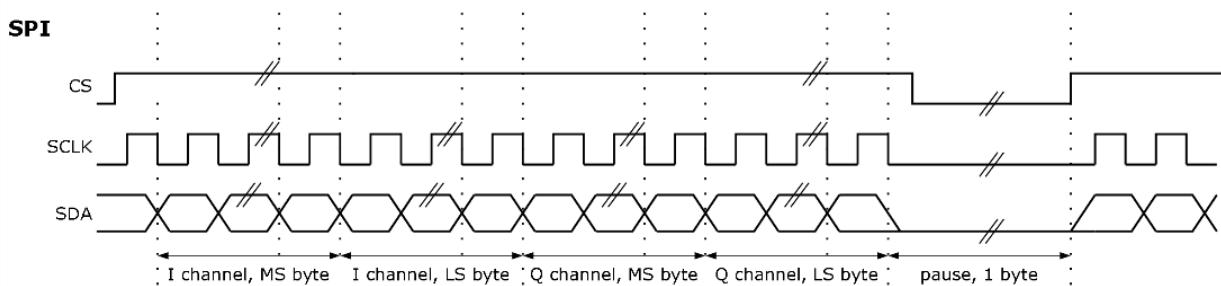

#### 4.8.2 Output data interface

The DRM Tuner IC outputs 16-bit I and Q data using the I2S (master) or SPI (master) interfaces. I and Q data may be allocated to either channel (\$28:b6).

- I2S standard data interface is optimized for streaming PCM data and requires 3 serial bus lines:

- WS: word select (0=left channel, 1=right channel);

- SD: serial interface output data, two time-multiplexed data channels;

- SCK: serial interface clock.

- Standard Serial Peripheral Interface requires 3 serial bus lines:

- CS: serial interface chip select signal with programmable polarity;

- SDA: serial interface output data, two time-multiplexed data channels;

- SCLK: serial interface clock.

**Table 8 - Output data interface pins**

| Pin # | I2S | SPI  |

|-------|-----|------|

| 22    | WS  | CS   |

| 23    | SD  | SDA  |

| 24    | SCK | SCLK |

#### I2S

|                  |                                                                                   |

|------------------|-----------------------------------------------------------------------------------|

| Data word length | 16 bits data + 4 fixed (pause) bits                                               |

| Polarity of WS   | Left channel WS = 0 = I data<br>Right channel WS = 1 = Q data                     |

| Delay            | First CK falling edge after WS transition is valid data                           |

| Data format      | Two's complement, MSB sent first                                                  |

| Transition       | SD and WS change on the falling edge of CLK<br>SD valid on the rising edge of CLK |

| Data transfer    | On the falling edge of SCK                                                        |

| Data reception   | On the rising edge of SCK                                                         |

#### I2S

**Figure 12 - I2S Data Format**

**SPI**

|                  |                                                                              |

|------------------|------------------------------------------------------------------------------|

| Data word length | 16 bits                                                                      |

| CS polarity      | Programmable (low or high active level)                                      |

| Data sequence    | I channel data first, then - Q channel data                                  |

| Data format      | Two's complement, MS byte sent first                                         |

| Transition       | SDA change on the falling edge of CLK<br>SDA valid on the rising edge of CLK |

| Data transfer    | On the falling edge of SCLK                                                  |

| Data reception   | On the rising edge of SCLK                                                   |

**Figure 13 - SPI Data Format****4.8.3 IQ Calibration**

The amplitude and phase balance of the I/Q mixer system requires calibration in order to achieve optimum image rejection.

- Select normal, ECO or boost mode using \$03 – IC\_Mode, Mode<2:0> setting

- Write Carrier frequency (Fc, value in 0.1 kHz) to the IC registers: Fc\_2, Fc\_1 & Fc\_0, Fc<20:0>

- Write IF frequency value (Fif1, 96 kHz or 120 kHz) to the IC registers: \$08 – Fc\_2<6>, Fif = "0" or Fif = "1"

- Select IF frequency sign: write \$08 – Fc\_2<7>, Fif\_SIGN = "0" or Fif\_SIGN = "1" to the IC registers

- Select channel bandwidth \$0B – BANDWIDTH (BW<2:0>)

- Execute IF filter bandwidth calibration procedure: \$29 – AUTO\_EXE<2>, IF\_BW\_ACS\_EXE="1". Wait until IF\_BW\_ACS\_EXE is reset to "0".

- Execute LO PLL tuning procedure: \$29 – AUTO\_EXE<0>, PLL\_CALC\_EXE="1", \$29 – AUTO\_EXE<1>, PLL\_SAS\_EXE will be executed automatically along with PLL\_CALC\_EXE. Wait until PLL\_CALC\_EXE and PLL\_SAS\_EXE are reset to "0".

- Write DPB\_CTRLS<2>="1" to enable improved "running" mode and DPB\_CTRLS<6:4>="110" to enhance accuracy. IQ calibration will be continuously running until the pause command is written or "running" mode is turned off.

- "Running" mode can be set to pause (write DPB\_CTRLS<3> = "1" to set pause and DPB\_CTRLS<3> = "0" to end pause).

- Write DPB\_CTRLS<2> = "0" to disable "running" mode.

- No calibration coefficients are available in this mode (DPB\_IQ\_COMP\_CORR\_I\_VAL<15:0>, DPB\_IQ\_COMP\_CORR\_Q\_VAL<15:0>).

Alternative methods are available, see section 5.9.2

#### 4.9 IF Filter bandwidth calibration

The IF filter bandwidth calibration procedure is intended to compensate for process variation and temperature dependence on the filter characteristics.

The initial bandwidth code (\$4D – IF\_BW\_ACS\_IN <4:0>dec = “20” for Fif = 96 kHz and BW = 100kHz by default) is used to control an RC-oscillator and its oscillation frequency is compared to the expected cut-off frequency (159.7 kHz by default). This RC-oscillator is built on the same components used in the IF filter design, which allows correlation between oscillation frequency and IF filter cut-off frequency to be achieved.

This code is then adjusted by a state machine (step polarity is programmable, BW\_ACS\_STEP\_PLR) until the oscillation frequency and expected frequency have the minimum error.

The lower the cut-off frequency, the longer the calibration time. For the lowest cut-off frequency, IF\_BW calibration may take up to 520 us (310 us typical). The calibration time for higher cut-off frequencies however is faster, typically around 50 us.

The obtained BW code is used as calibration output and is applied to the IF analogue bandwidth controls in separate registers (\$4E – RF\_MIX\_BW, \$4F – IF\_I\_BW and \$50 – IF\_Q\_BW) and can be read by the controller. If the calibration procedure is not executed, BW control registers (RF\_MIX\_BW, IF\_I\_BW and IF\_Q\_BW) should be configured manually. \$0B – BANDWIDTH must be also written.

The bandwidth calibration procedure must be executed (BW\_ACS\_EXE = “1” in \$29 – AUTO\_EXE) after device activation and if the Fif (\$08 – Fc\_2, b6) or \$0B – BANDWIDTH settings are changed.

Bit 4 in the \$05 – IRQ\_MASK and \$06 – STATUS registers (IF\_BW\_ACS\_OK) indicates whether the bandwidth calibration completed successfully or with error/was not executed.

Application of an input signal does not affect IF\_BW calibration.

## 5 Operational Guidelines

### 5.1 Initial settings

After power-on and once out of reset, the CMX918 is in standby mode: the reference voltage and currents sources and internal regulators (for RF, IF, PLL, ADC and DPB) and XTAL will be enabled.

The receive carrier frequency can be set from 150 kHz to 108 MHz with 100 Hz step size using  $Fc<20:0>$  bits (registers \$08 to \$0A). All 21-bits should be rewritten when  $Fc$  is changed. Writing the 8 least significant bits implements the change in value (but does not execute PLL changes). The default carrier frequency is 94.9 MHz.

The Intermediate frequency (Fif) can be set to 96 kHz (Fif = "0", default) or 120 kHz (Fif = "1") via bit6 of register \$08 FC\_2. The default IF frequency polarity corresponds to  $Flo-Fc=Fif$  conversion (Fif\_SIGN = "0") and can be changed to low-side mixing by writing Fif\_SIGN = "1" ( $Fc-Flo=Fif$ ). This is bit 7 of register \$08 FC\_2.

The channel bandwidth can be set to 5 kHz, 10 kHz, 20 kHz, 100 kHz (default) or 200 kHz using \$0B – BANDWIDTH BW<2:0> setting.

If the default settings of  $Fc$ ,  $Fif$  and  $BW$  are acceptable and IQ calibration is not required, a simplified start-up procedure is as described below:

- Select Normal mode: \$03 – IC\_Mode, Mode<2:0> = "3"

- Execute IF filter bandwidth calibration procedure: \$29 – AUTO\_EXE<2>, IF\_BW\_ACS\_EXE = "1"

- Wait until IF\_BW\_ACS\_EXE is reset to "0"

- Execute LO PLL tuning procedure: \$29 – AUTO\_EXE<0>, PLL\_CALC\_EXE = "1" (\$29 – AUTO\_EXE<1>, PLL\_SAS\_EXE will be executed automatically along with PLL\_CALC\_EXE). Wait until PLL\_CALC\_EXE and PLL\_SAS\_EXE have completed and are reset to "0"

These EXE commands are accessed via the AUTO\_EXE register \$29 (for details refer to the register description).

The following procedure is recommended if  $Fc$ ,  $Fif$  and  $BW$  need to be changed:

- Select Normal mode in register: \$03 – IC\_Mode, Mode<2:0> = "3"

- Select the Carrier frequency ( $Fc$ , value in 0.1 kHz)  $Fc_2$ ,  $Fc_1$  &  $Fc_0$ ,  $Fc<20:0>$ , select the IF frequency value (Fif1, 96 kHz or 120 kHz) : \$08 –  $Fc_2<6>$ , Fif = "0" or Fif = "1" and select the IF frequency sign: write \$08 –  $Fc_2<7>$ , Fif\_SIGN = "0" or Fif\_SIGN = "1"

- Select the channel bandwidth \$0B – BANDWIDTH (BW<2:0>)

- Execute the IF filter bandwidth calibration procedure: \$29 – AUTO\_EXE<2>, IF\_BW\_ACS\_EXE = "1". Wait until IF\_BW\_ACS\_EXE is reset to "0"

- Execute LO PLL tuning procedure: \$29 – AUTO\_EXE<0>, PLL\_CALC\_EXE = "1", \$29 – AUTO\_EXE<1>, PLL\_SAS\_EXE will be executed automatically along with PLL\_CALC\_EXE. Wait until PLL\_CALC\_EXE and PLL\_SAS\_EXE have completed and are reset to "0". These can be run by writing 0x05 to AUTO\_EXE register \$29

### 5.2 Reference Frequency Configuration

The IC is preconfigured to operate with 38.4 MHz reference frequency. The default reference frequency input source is an on-chip oscillator using a crystal connected across pins 11 and 12 (PLL\_XTAL\_TCXO\_MD bit in \$07 – CLK\_CTL is set to "0"). Service register \$97 – PLL\_XTAL\_CTL allows control of internal capacitors to tune the crystal oscillator frequency in XTAL mode.

As an option, the reference frequency input source can be switched to use a TCXO by writing PLL\_XTAL\_TCXO\_MD = "1". In this case TCXO must be connected to pin 12, while pin 11 is then connected to ground. The TCXO power supply can be sourced from +1.8 V available at pin 10 (PLL\_VDD).

The PLL comparison frequency is set by default to use the input 38.3 MHz reference frequency, however this can be divided by 2, 3, or 4, set using PLL\_RDIV<1:0> (register \$30 – PLL\_RDIV). In this case the PLL must be reconfigured according to procedure described in section 5.3 PLL Reconfiguration. The PLL is preconfigured according to the default  $Fc$  and  $Fif$  settings.

### 5.3 PLL Reconfiguration

To reconfigure the PLL the following procedure is recommended:

- Select normal operation mode: \$03 – IC\_Mode, Mode<2:0> = “3”

- Select the Carrier frequency (Fc, value in 0.1 kHz) Fc\_2, Fc\_1 & Fc\_0, Fc<20:0>, select the IF frequency value (Fif1, 96 kHz or 120 kHz): \$08 – Fc\_2<6>, Fif = “0” or Fif = “1” and select the IF frequency sign: write \$08 – Fc\_2<7>, Fif\_SIGN = “0” or Fif\_SIGN = “1”

- Write these values to the IC registers \$08 to \$0A (FC\_2/1/0)

- Execute the LO PLL tuning procedure: \$29 – AUTO\_EXE<0>, PLL\_CALC\_EXE = “1” (\$29 – AUTO\_EXE<1>, PLL\_SAS\_EXE will be executed automatically along with PLL\_CALC\_EXE)

Wait until PLL\_CALC\_EXE and PLL\_SAS\_EXE have completed and are reset to “0”.

In automatic mode, when the user executes the PLL dividers ratio calculation by writing PLL\_CALC\_EXE = “1”, internal control logic will calculate and change values of PLL\_DSM\_N<7:0> (registers \$2B/2C), PLL\_DSM\_F<23:0> (registers \$2D-2F) and PLL\_LDIV<7:0> (registers \$31/32) appropriately. The values of the fractional N value PLL\_DSM\_F<23:0> will be changed simultaneously after calculation is finished.

To reconfigure the PLL in manual mode (for advanced users) the following procedure is recommended:

- Select normal operation mode: \$03 – IC\_Mode, Mode<2:0> = “3”

- Select the Carrier frequency (Fc, value in 0.1 kHz) Fc\_2, Fc\_1 & Fc\_0, Fc<20:0>, select the IF frequency value (Fif1, 96 kHz or 120 kHz): \$08 – Fc\_2<6>, Fif = “0” or Fif = “1” and select the IF frequency sign: write \$08 – Fc\_2<7>, Fif\_SIGN = “0” or Fif\_SIGN = “1”

- Write these values to the IC registers \$08 to \$0A (FC\_2/1/0)

- Calculate values of N, F, L and R coefficients according to the formula:

- $F_{lo} = F_{c} \pm F_{if1} = (F_{ref} * (N + F / 2^{24})) / (4 * L * R)$

- Write PLL\_LDIV\_MD = “0” (bit 1 of register \$2A)

- Disable the DSM if F divider value = 0: write PLL\_DSM\_EN = “0” (bit 0 of register \$2A)

- Write the values of N, F, L and R coefficients to the IC registers: PLL\_DSM\_N<10:0>, PLL\_DSM\_F<23:0>, PLL\_LDIV\_reg<10:0>, PLL\_RDIV<1:0> (registers \$2B to \$30)

In manual mode, the values of \$2C - PLL\_DSM\_N<7:0>, \$2D & \$2E PLL\_DSM\_F<23:0> and \$32 - PLL\_LDIV<7:0> are updated via the control interface separately by 8bit registers. They are always “applied” if the PLL is active, so intermediate values will be used while user rewrites them register by register.

A PLL lock indicator (PLL\_LOCK) is available in register \$06 – STATUS, bit 3. Crossing of the VCO voltage comparator lower threshold (PLL\_SAS\_CMPL) will be indicated by bit 1 of the \$06 - STATUS register, crossing of upper threshold (PLL\_SAS\_CMPH) – by bit 2.

The IC includes an integrated 3rd order low-pass loop filter with adjustable values of resistance and capacitance for loop tuning with the aim of best phase-noise performance. The loop filter components can be tuned using \$8F – PLL\_LF\_CTL\_0, PLL\_LF\_R1<3:0>, \$90 - PLL\_LF\_CTL\_1, PLL\_LF\_R2<1:0>, \$8F - PLL\_LF\_CTL\_0, PLL\_LF\_C1<3:0> and \$91 – PLL\_LF\_CTL\_2, PLL\_LF\_C2<4:0> settings in service section of the registers map (\$8F – PLL\_LF\_CTL\_0 onwards).

If an external LO source is to be used with the device, PLL\_EXT\_VCO\_MD must be set to “1” (b2 in \$2A – PLL\_CTL). Note that this input is before the PLL L divider.

### 5.4 Noise Figure Improvement

Changing the R-divider value allows improved noise figure performance over VHF frequency range. Recommended values are given in table overleaf.

**Table 9 - R-divider recommended values**

| F <sub>c</sub><br>(MHz) | F <sub>ref</sub><br>(MHz) | R-divider<br>value | F <sub>pf</sub><br>(MHz) |

|-------------------------|---------------------------|--------------------|--------------------------|

| 2 - 86                  | 38.4                      | 1                  | 38.4                     |

| 86 - 92                 | 38.4                      | 3                  | 12.8                     |

| 92 - 100                | 38.4                      | 2                  | 19.2                     |

| 100 - 110               | 38.4                      | 3                  | 12.8                     |

If R=2 or 3 is selected and written (PLL\_RDIV = "01" or "10" in register \$30 – PLL\_RDIV), execute the LO PLL tuning procedure: set \$29 – AUTO\_EXE<0>, PLL\_CALC\_EXE = "1", (\$29 – AUTO\_EXE<1>, PLL\_SAS\_EXE will be executed automatically along with PLL\_CALC\_EXE). Wait until PLL\_CALC\_EXE and PLL\_SAS\_EXE are reset to "0".

In addition to R-divider value changes, PLL loop filter adjustment can be applied for in-band phase noise reduction in trade off to out of band phase noise.

**Table 10 - Loop filter recommended settings**

| R-divider<br>value | PLL_LF_C1<3:0><br>(dec) | PLL_LF_C2<4:0><br>(dec) | PLL_LF_R1<3:0><br>(dec) | PLL_LF_R2<1:0><br>(dec) |

|--------------------|-------------------------|-------------------------|-------------------------|-------------------------|