# BGM240P Wireless Gecko Bluetooth Module Datasheet

The BGM240P is a secure, high-performance wireless module optimized for the needs of battery and line-powered IoT devices running on Bluetooth networks.

Based on the Series 2 EFR32BG24 SoC, it enables Bluetooth® Low Energy connectivity, delivering exceptional RF performance and energy efficiency, industry-leading Secure Vault® technology, and future-proofing capabilities.

The BGM240P is a complete solution offered with robust and fully-upgradeable software stacks, global regulatory certifications, advanced development and debugging tools, and documentation that simplifies and minimizes the development cycle of your end-product, helping to accelerate its time-to-market.

The BGM240P is targeted for a broad range of applications, including:

- Smart Home Devices

- Lighting

- Gateways and Digital Assistants

- Building Automation and Security

## KEY FEATURES

- Bluetooth Low Energy 5.4 and Bluetooth Mesh connectivity

- Built-in antenna or RF pin

- +10 or +20 dBm TX output power

- -98.5 dBm BLE 1M RX sensitivity

- 32-bit ARM® Cortex®-M33 core at 78 MHz

- 1536/256 kB of flash/RAM memory

- Vault High or Vault Mid security

- Rich set of analog and digital peripherals

- 26 GPIO pins

- -40 to 105 °C

- 12.9 x 15.0 mm

## 1. Features

### • Supported Protocols

- Bluetooth Low Energy (BLE) 5.4

- Bluetooth Mesh

- Matter-ready Smart Home Connectivity

### • Wireless System-on-Chip

- 2.4 GHz radio

- TX power up to +20 dBm

- 32-bit ARM Cortex®-M33 with DSP instruction and floating-point unit for efficient signal processing

- 1536 kB flash program memory

- 256 kB RAM data memory

- Embedded Trace Macrocell (ETM) for advanced debugging

### • Receiver Sensitivity

- -106.5 dBm (0.1% BER) at 125 kbps GFSK

- -102.2 dBm (0.1% BER) at 500 kbps GFSK

- -98.5 dBm (0.1% BER) at 1 Mbps GFSK

- -95.7 dBm (0.1% BER) at 2 Mbps GFSK

### • Current Consumption

- 4.5 mA RX current at 1 Mbps GFSK

- 4.8 mA TX current at 0 dBm (BGM240Px22)

- 18.8 mA TX current at 10 dBm (BGM240Px22)

- 154.8 mA TX current at 19.6 dBm (BGM240Px32)

- 33.4  $\mu$ A/MHz in Active Mode (EM0) at 39.0 MHz

- 1.3  $\mu$ A EM2 DeepSleep current (16 kB RAM retention and RTC running from LFRCO)

### • Regulatory Certifications

- CE (EU)

- UKCA (UK)

- FCC (USA)

- ISED (Canada)

- MIC (Japan)

- KC (South Korea)

### • Operating Range

- 1.8 to 3.8 V

- -40 to +105 °C

### • Dimensions

- 12.9 x 15.0 mm

### • Security

- Secure Boot with Root of Trust and Secure Loader (RTSL)

- Hardware Cryptographic Acceleration with DPA counter-measures for AES128/256, SHA-1, SHA-2 (up to 256-bit), ECC (up to 256-bit), ECDSA, and ECDH

- True Random Number Generator (TRNG) compliant with NIST SP800-90 and AIS-31

- ARM® TrustZone®

- Secure Debug Interface lock/unlock

- Secure Key Management with PUF

- Anti-Tamper

- Secure Attestation

### • MCU Peripherals

- Analog to Digital Converter (ADC)

- 12-bit @ 1 Msps

- 16-bit @ 76.9 ksps

- 2 × Analog Comparator (ACMP)

- 2 × Digital to Analog Converter (VDAC)

- Up to 26 General Purpose I/O pins with output state retention and asynchronous interrupts

- 8 Channel DMA Controller

- 16 Channel Peripheral Reflex System (PRS)

- 3 × 16-bit Timer/Counter with 3 Compare/Capture/PWM channels

- 2 × 32-bit Timer/Counter with 3 Compare/Capture/PWM channels

- 2 × 32-bit Real Time Counter (SYSRTC/BURTC)

- 24-bit Low Energy Timer for waveform generation (LETIMER)

- 16-bit Pulse Counter with asynchronous operation (PCNT)

- 2 × Watchdog Timer (WDOG)

- 1 × Universal Synchronous/Asynchronous Receiver/Transmitter (USART), supporting UART/SPI/SmartCard (ISO 7816)/IrDA/I<sup>2</sup>S

- 2 × Enhanced Universal Synchronous/Asynchronous Receiver/Transmitter (EUSART) supporting UART/SPI/DALI/IrDA

- 2 × I<sup>2</sup>C interface with SMBus support

- Low-Frequency RC Oscillator with precision mode to replace 32 kHz sleep crystal (LFRCO)

- Keypad scanner supporting up to 6x8 matrix (KEYSCAN)

- Die temperature sensor with +/- 1.5 °C accuracy after single-point calibration

**Note:** Sensitivity values above are for +10 dBm parts (BGM240x22).

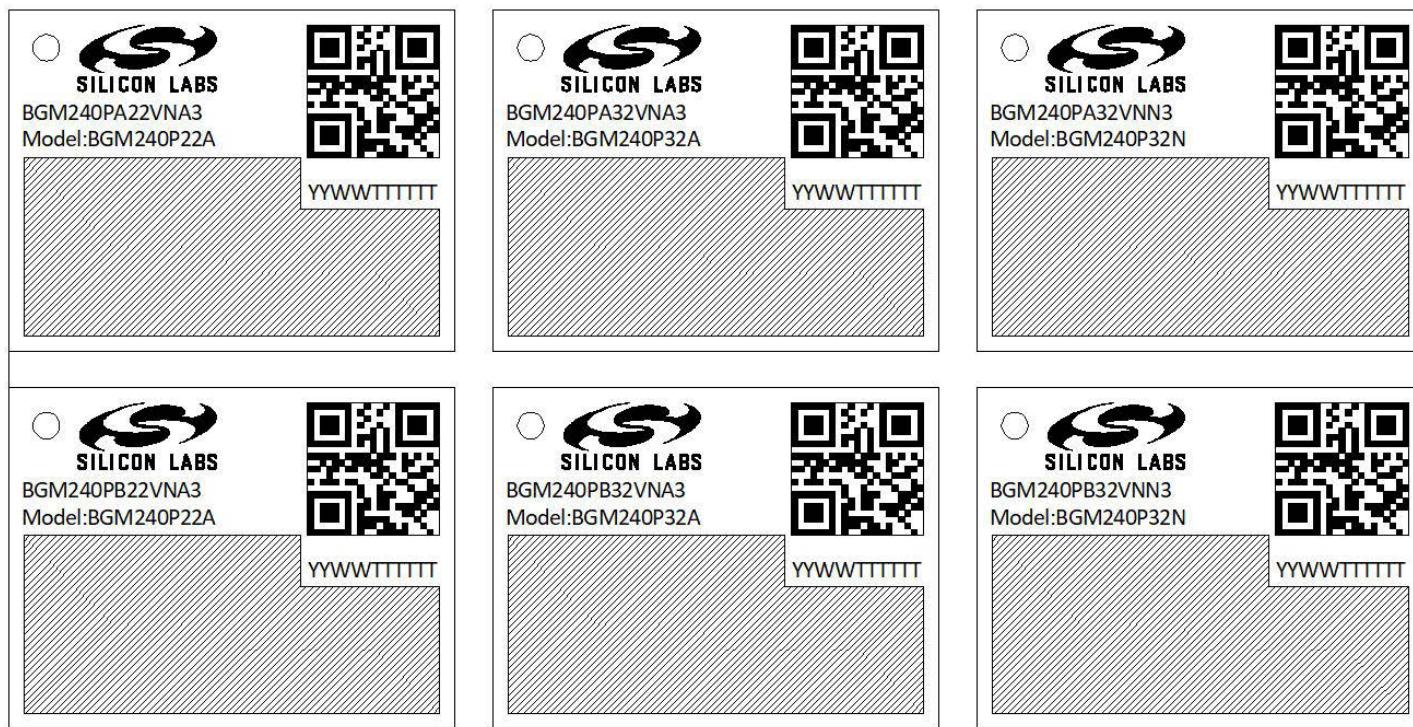

## 2. Ordering Information

Table 2.1. Ordering Information

| Ordering Code   | Protocol Stack                                                                                     | Max TX Power | Security   | Antenna  | Flash (kB) | RAM (kB) | GPIO | Temp Range    | Carrier  |

|-----------------|----------------------------------------------------------------------------------------------------|--------------|------------|----------|------------|----------|------|---------------|----------|

| BGM240PA22VNA3  | <ul style="list-style-type: none"> <li>Bluetooth Low Energy 5.4</li> <li>Bluetooth Mesh</li> </ul> | +10 dBm      | Vault Mid  | Built-in | 1536       | 256      | 26   | -40 to 105 °C | Cut Tape |

| BGM240PA22VNA3R | <ul style="list-style-type: none"> <li>Bluetooth Low Energy 5.4</li> <li>Bluetooth Mesh</li> </ul> | +10 dBm      | Vault Mid  | Built-in | 1536       | 256      | 26   | -40 to 105 °C | Reel     |

| BGM240PB22VNA3  | <ul style="list-style-type: none"> <li>Bluetooth Low Energy 5.4</li> <li>Bluetooth Mesh</li> </ul> | +10 dBm      | Vault High | Built-in | 1536       | 256      | 26   | -40 to 105 °C | Cut Tape |

| BGM240PB22VNA3R | <ul style="list-style-type: none"> <li>Bluetooth Low Energy 5.4</li> <li>Bluetooth Mesh</li> </ul> | +10 dBm      | Vault High | Built-in | 1536       | 256      | 26   | -40 to 105 °C | Reel     |

| BGM240PA32VNA3  | <ul style="list-style-type: none"> <li>Bluetooth Low Energy 5.4</li> <li>Bluetooth Mesh</li> </ul> | +20 dBm      | Vault Mid  | Built-in | 1536       | 256      | 26   | -40 to 105 °C | Cut Tape |

| BGM240PA32VNA3R | <ul style="list-style-type: none"> <li>Bluetooth Low Energy 5.4</li> <li>Bluetooth Mesh</li> </ul> | +20 dBm      | Vault Mid  | Built-in | 1536       | 256      | 26   | -40 to 105 °C | Reel     |

| BGM240PA32VNN3  | <ul style="list-style-type: none"> <li>Bluetooth Low Energy 5.4</li> <li>Bluetooth Mesh</li> </ul> | +20 dBm      | Vault Mid  | RF Pin   | 1536       | 256      | 26   | -40 to 105 °C | Cut Tape |

| BGM240PA32VNN3R | <ul style="list-style-type: none"> <li>Bluetooth Low Energy 5.4</li> <li>Bluetooth Mesh</li> </ul> | +20 dBm      | Vault Mid  | RF Pin   | 1536       | 256      | 26   | -40 to 105 °C | Reel     |

| BGM240PB32VNA3  | <ul style="list-style-type: none"> <li>Bluetooth Low Energy 5.4</li> <li>Bluetooth Mesh</li> </ul> | +20 dBm      | Vault High | Built-in | 1536       | 256      | 26   | -40 to 105 °C | Cut Tape |

| BGM240PB32VNA3R | <ul style="list-style-type: none"> <li>Bluetooth Low Energy 5.4</li> <li>Bluetooth Mesh</li> </ul> | +20 dBm      | Vault High | Built-in | 1536       | 256      | 26   | -40 to 105 °C | Reel     |

| BGM240PB32VNN3  | <ul style="list-style-type: none"> <li>Bluetooth Low Energy 5.4</li> <li>Bluetooth Mesh</li> </ul> | +20 dBm      | Vault High | RF Pin   | 1536       | 256      | 26   | -40 to 105 °C | Cut Tape |

| BGM240PB32VNN3R | <ul style="list-style-type: none"> <li>Bluetooth Low Energy 5.4</li> <li>Bluetooth Mesh</li> </ul> | +20 dBm      | Vault High | RF Pin   | 1536       | 256      | 26   | -40 to 105 °C | Reel     |

**Note:**

1. BGM240P modules operate in the 2.4 GHz ISM frequency band.

2. The maximum RF TX power allowed by different regional regulatory authorities may differ from the maximum output power a module can produce. End-product manufacturers must then verify that the module is configured to meet the regulatory limits for each region in accordance with the local rules and the formal certification test reports.

3. Throughout this document, the modules may be referred to by their product family/marketing name (e.g. BGM240P), by their model names (BGM240P32A, BGM240P22A or BGM240P32N), or by their full ordering codes as seen in the table above.

4. Radio boards **xGM240-RB4316A** (+10 dBm) and **xGM240-RB4317A** (+20 dBm) are available for BGM240P evaluation and development.

5. Devices are pre-programmed with BGAPI UART DFU bootloader version 2.1.0.2, which uses the pin configuration in Section [5. Reference Diagrams](#).

# Table of Contents

|                                                                                                  |    |

|--------------------------------------------------------------------------------------------------|----|

| <b>1. Features</b>                                                                               | 2  |

| <b>2. Ordering Information</b>                                                                   | 3  |

| <b>3. System Overview</b>                                                                        | 7  |

| 3.1 Block Diagram                                                                                | 7  |

| 3.2 EFR32BG24 SoC                                                                                | 8  |

| 3.3 Antenna                                                                                      | 8  |

| 3.4 Power Supply                                                                                 | 8  |

| 3.5 General Purpose Input/Output (GPIO)                                                          | 9  |

| 3.6 Security                                                                                     | 9  |

| 3.6.1 Secure Boot with Root of Trust and Secure Loader (RTSL)                                    | 10 |

| 3.6.2 Cryptographic Accelerator                                                                  | 10 |

| 3.6.3 True Random Number Generator                                                               | 10 |

| 3.6.4 Secure Debug with Lock/Unlock                                                              | 10 |

| 3.6.5 DPA Countermeasures                                                                        | 10 |

| 3.6.6 Secure Key Management with PUF                                                             | 11 |

| 3.6.7 Anti-Tamper                                                                                | 11 |

| 3.6.8 Secure Attestation                                                                         | 11 |

| <b>4. Electrical Specifications</b>                                                              | 12 |

| 4.1 Absolute Maximum Ratings                                                                     | 12 |

| 4.2 General Operating Conditions                                                                 | 13 |

| 4.3 MCU Current Consumption at 3.0 V                                                             | 14 |

| 4.4 Radio Current Consumption with 3.0 V Supply                                                  | 15 |

| 4.5 RF Transmitter General Characteristics for the 2.4 GHz Band                                  | 16 |

| 4.6 RF Receiver General Characteristics for the 2.4 GHz Band                                     | 17 |

| 4.7 RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 1 Mbps Data Rate    | 18 |

| 4.8 RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 2 Mbps Data Rate    | 20 |

| 4.9 RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 500 kbps Data Rate  | 22 |

| 4.10 RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 125 kbps Data Rate | 24 |

| 4.11 High-Frequency Crystal                                                                      | 25 |

| 4.12 Low Frequency Crystal Oscillator                                                            | 26 |

| 4.13 Precision Low Frequency RC Oscillator (LFRCO)                                               | 27 |

| 4.14 GPIO Pins                                                                                   | 28 |

| 4.15 Microcontroller Peripherals                                                                 | 29 |

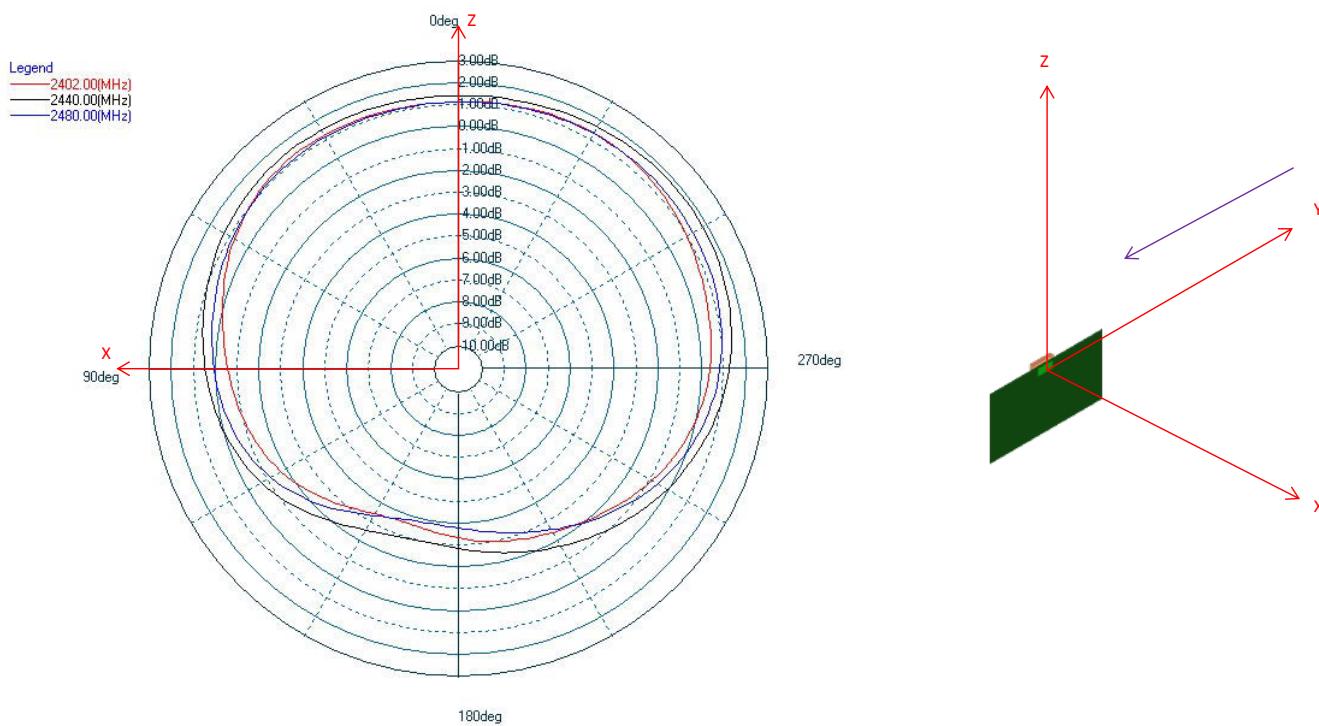

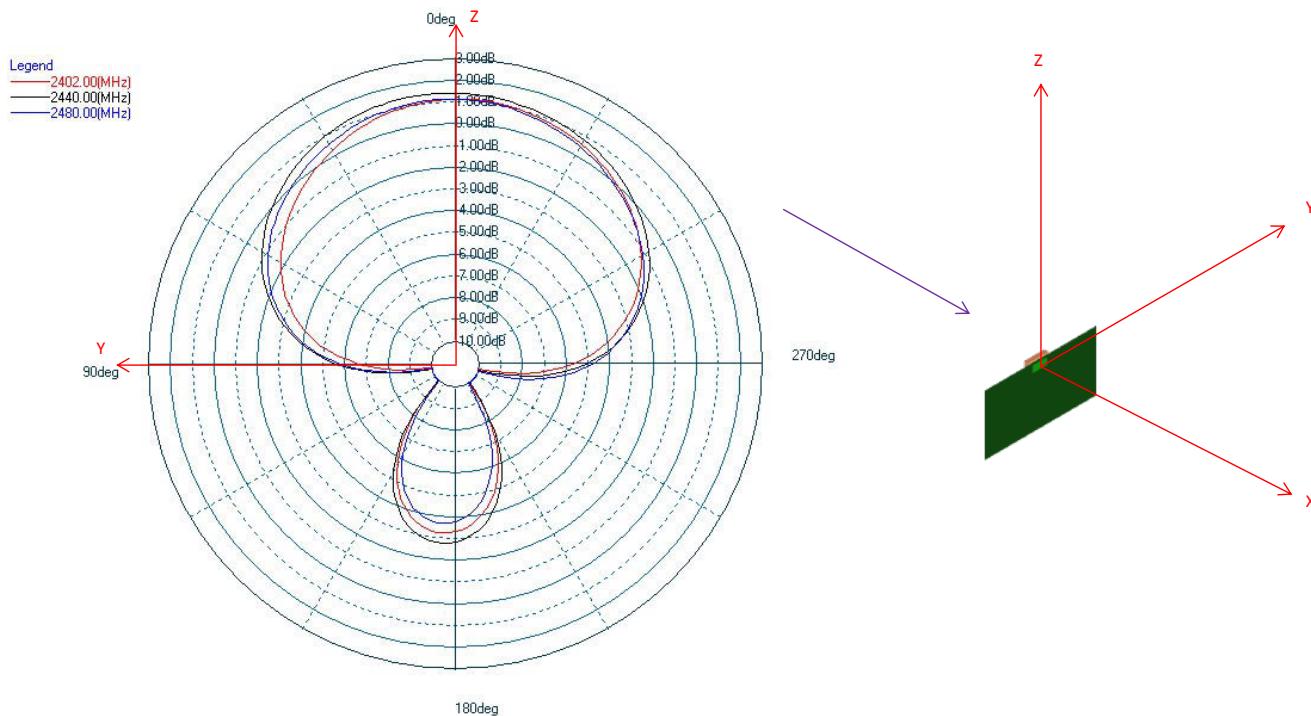

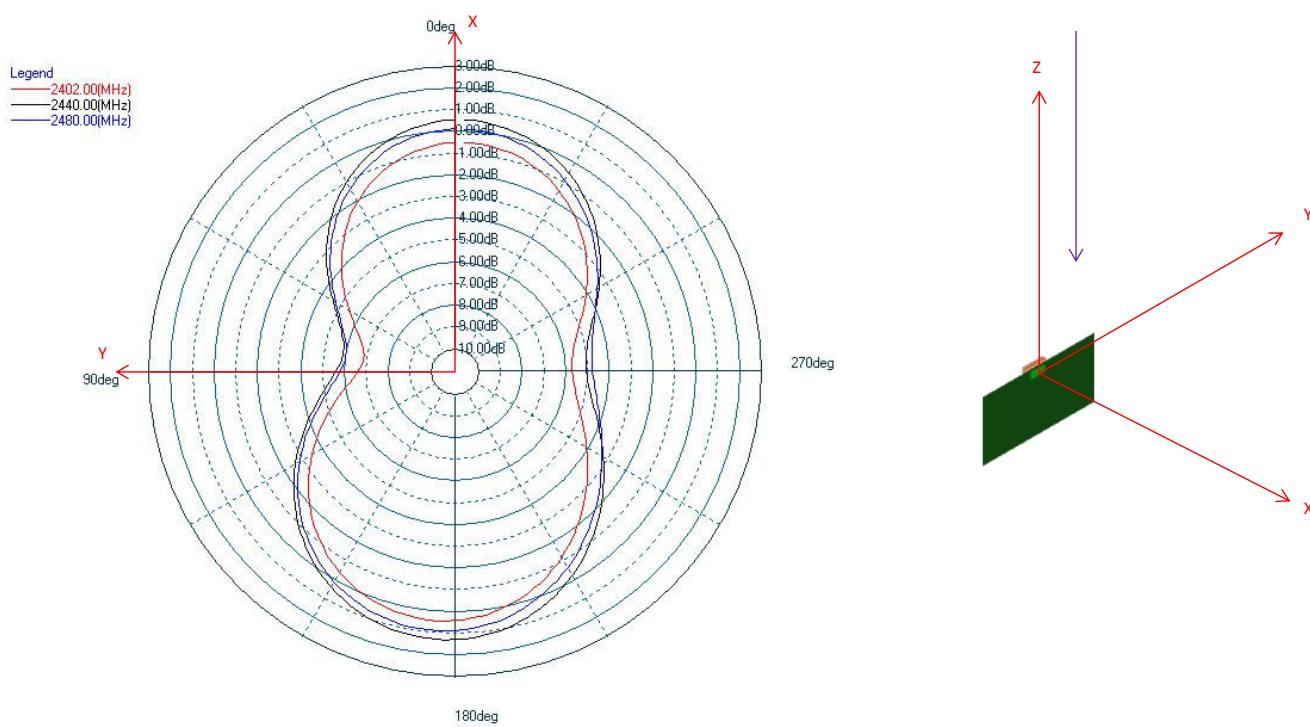

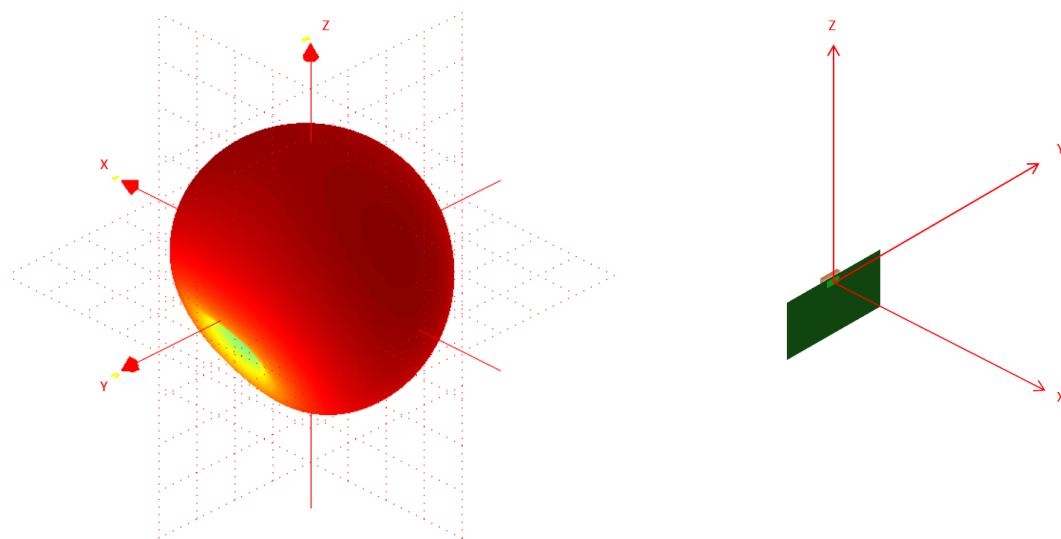

| 4.16 Antenna Radiation and Efficiency                                                            | 30 |

| <b>5. Reference Diagrams</b>                                                                     | 33 |

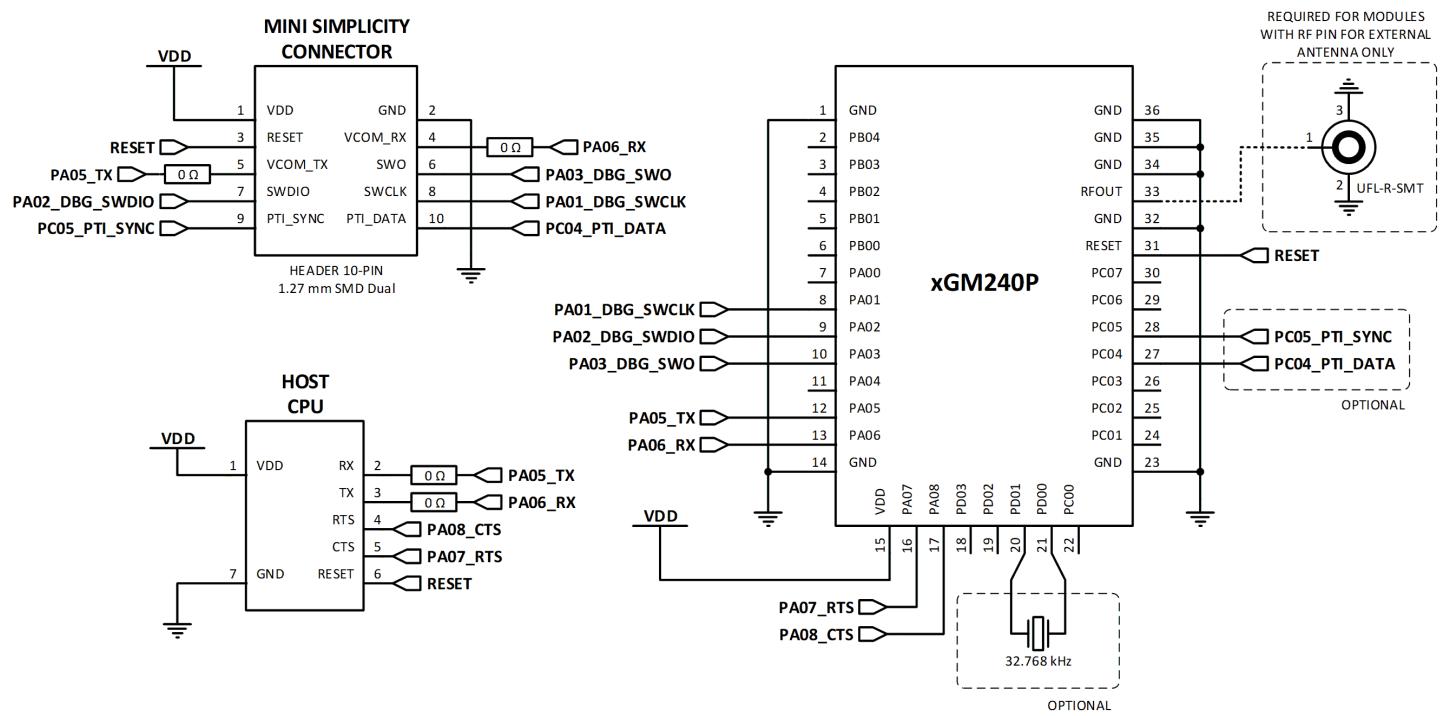

| 5.1 Network Co-Processor (NCP) Application with UART Host                                        | 33 |

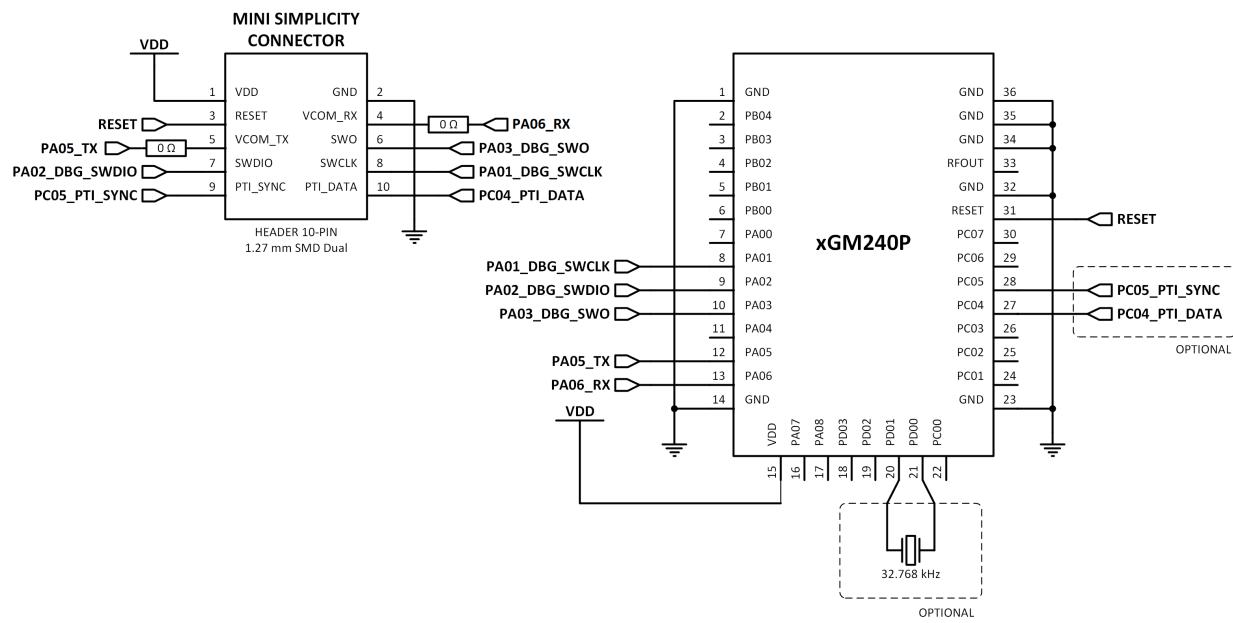

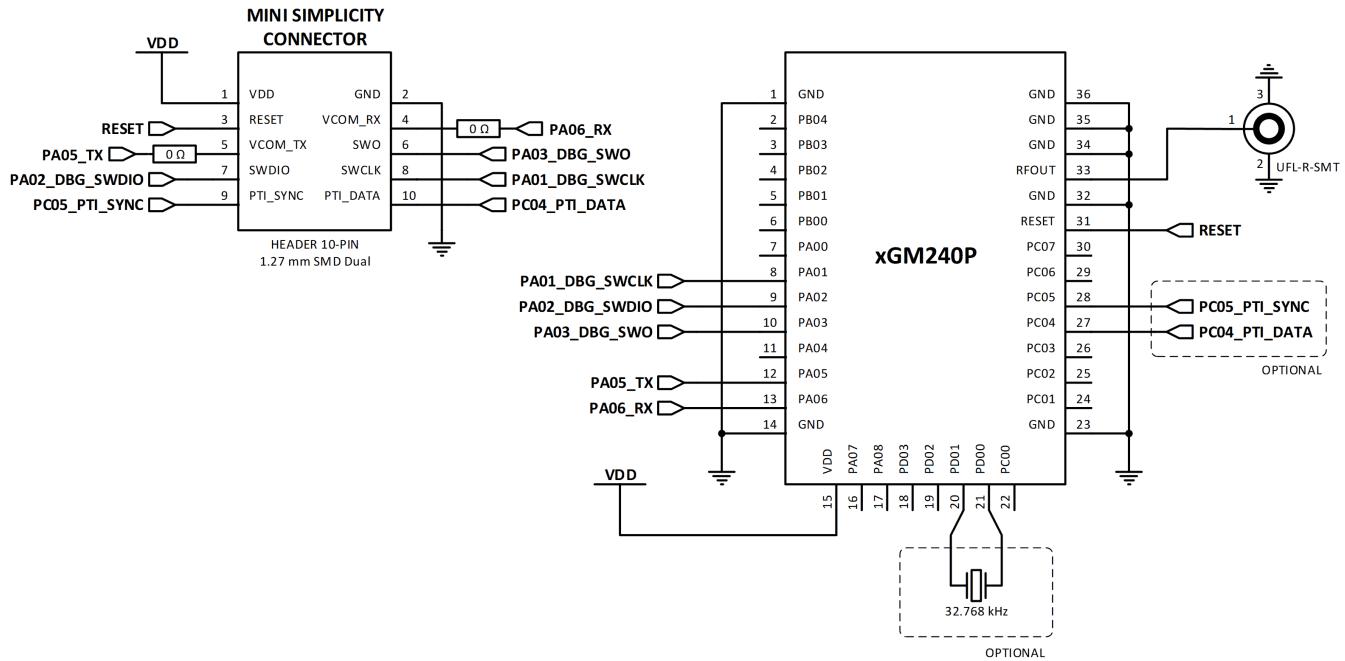

| 5.2 SoC Application                                                                              | 34 |

|                                     |           |

|-------------------------------------|-----------|

| <b>6. Pin Definitions</b>           | <b>35</b> |

| 6.1 Module Pinout                   | .35       |

| 6.2 Alternate Pin Functions         | .37       |

| 6.3 Analog Peripheral Connectivity  | .38       |

| 6.4 Digital Peripheral Connectivity | .39       |

| <b>7. Design Guidelines</b>         | <b>43</b> |

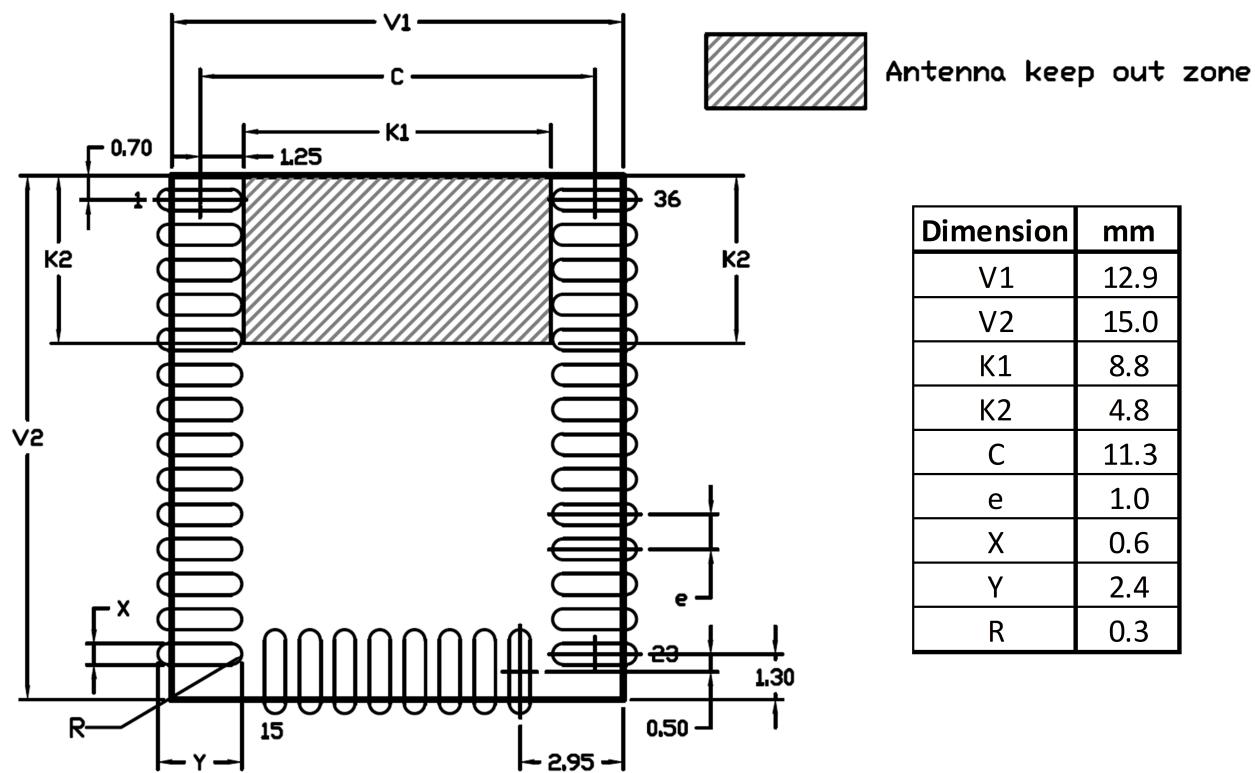

| 7.1 Layout and Placement            | .43       |

| 7.2 Proximity to Other Materials    | .45       |

| 7.3 Proximity to Human Body         | .45       |

| 7.4 Reset                           | .45       |

| 7.5 Debug                           | .45       |

| 7.6 Packet Trace Interface (PTI)    | .46       |

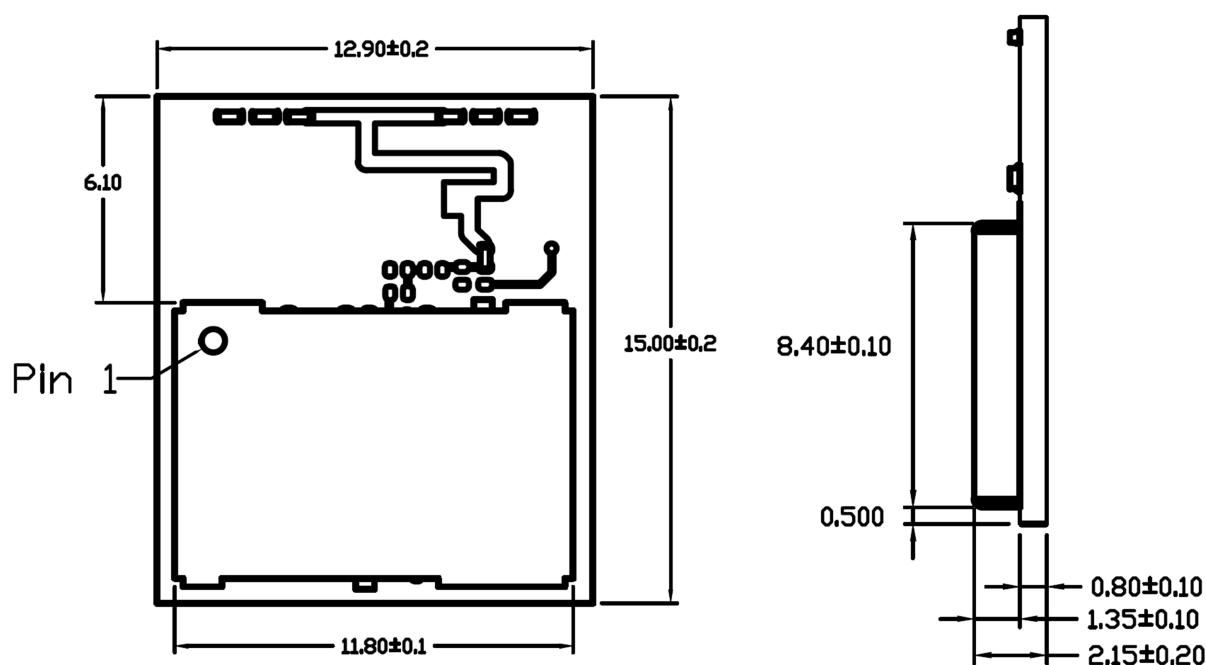

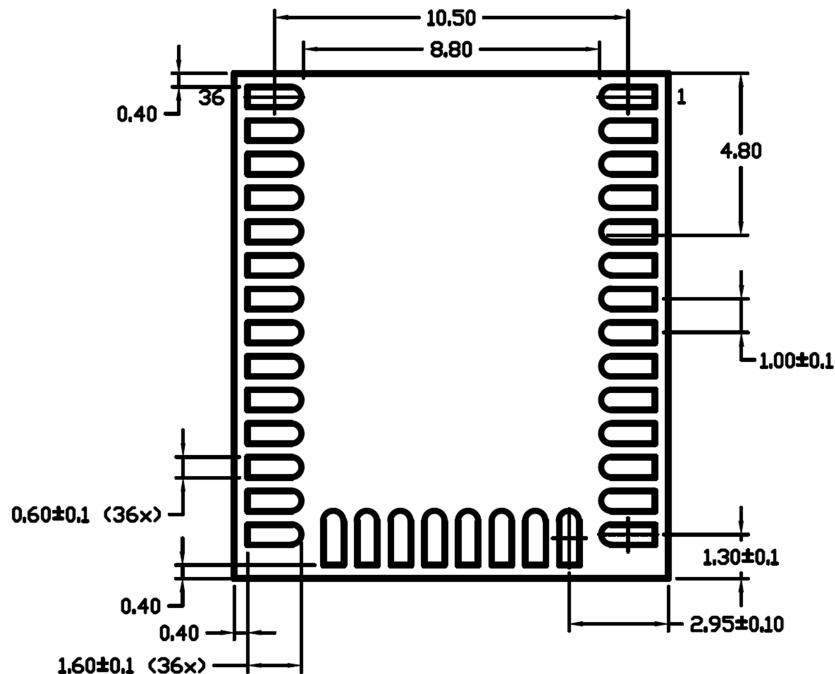

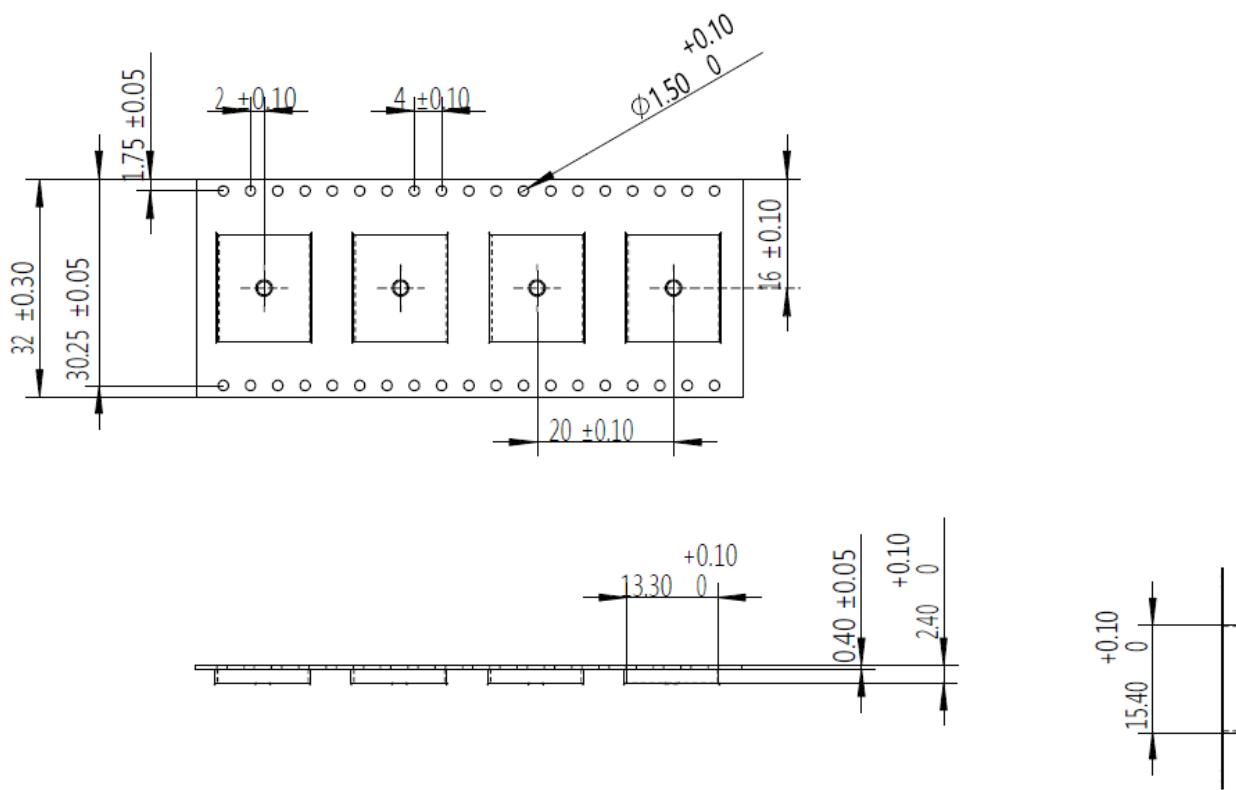

| <b>8. Package Specifications</b>    | <b>47</b> |

| 8.1 Package Outline                 | .47       |

| 8.2 PCB Land Pattern                | .48       |

| 8.3 Package Marking                 | .49       |

| <b>9. Soldering Recommendations</b> | <b>50</b> |

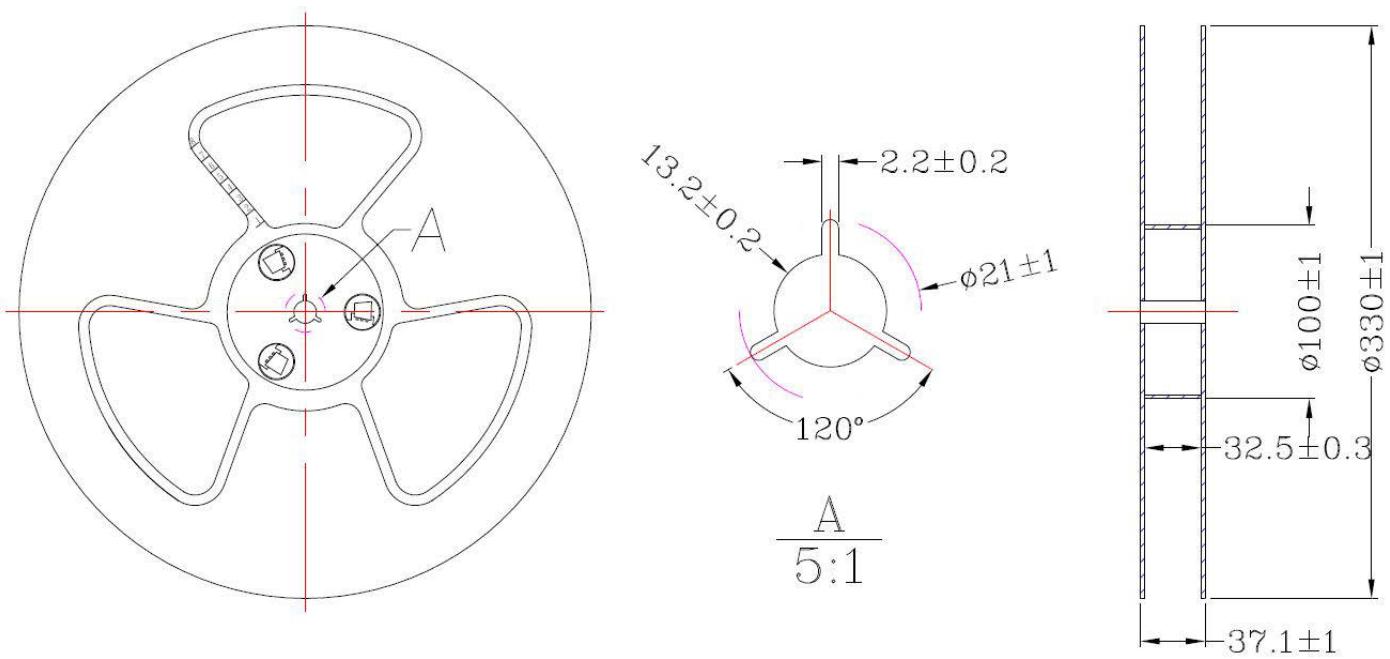

| <b>10. Tape and Reel</b>            | <b>51</b> |

| <b>11. Certifications</b>           | <b>52</b> |

| 11.1 Qualified Antennas             | .52       |

| 11.2 CE and UKCA - EU and UK        | .53       |

| 11.3 FCC - USA                      | .53       |

| 11.4 ISED - Canada                  | .56       |

| 11.5 MIC - Japan                    | .58       |

| 11.6 KC - South Korea               | .59       |

| 11.7 Human Body Proximity           | .60       |

| 11.8 Bluetooth Qualification        | .60       |

| <b>12. Revision History</b>         | <b>61</b> |

### 3. System Overview

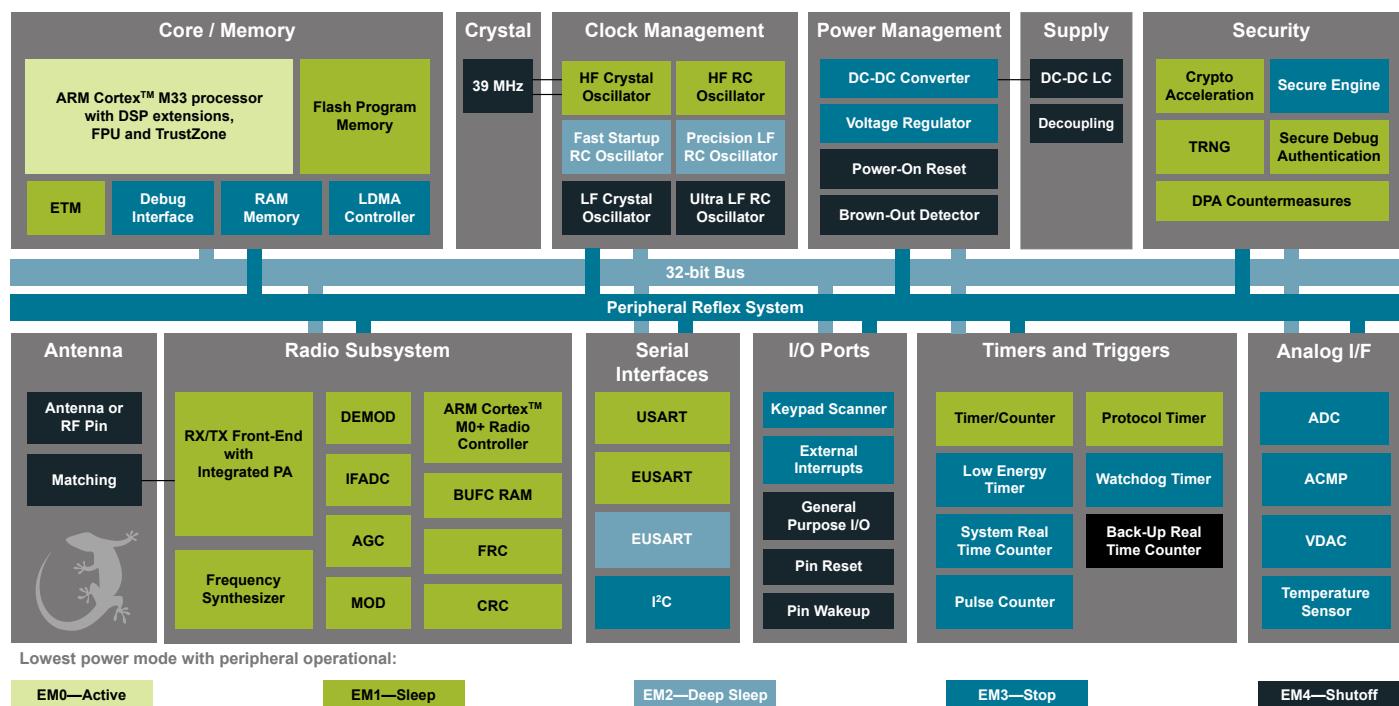

#### 3.1 Block Diagram

The BGM240P module is a highly-integrated, high-performance system with all the hardware components needed to enable 2.4 GHz wireless connectivity and support robust networking capabilities via multiple wireless protocols.

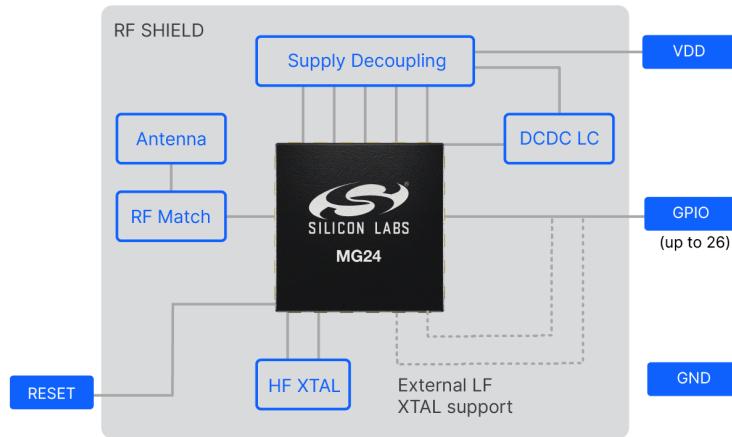

Built around the EFR32BG24 Wireless SoC, the BGM240P includes a built-in antenna, an RF matching network (optimized for transmit power efficiency), supply decoupling and filtering components, an LC tank for DC-DC conversion, a 39 MHz reference crystal, and an RF shield. Also, it supports the use of an external 32 kHz crystal as a low frequency reference signal via GPIO pins for use cases demanding maximum energy efficiency.

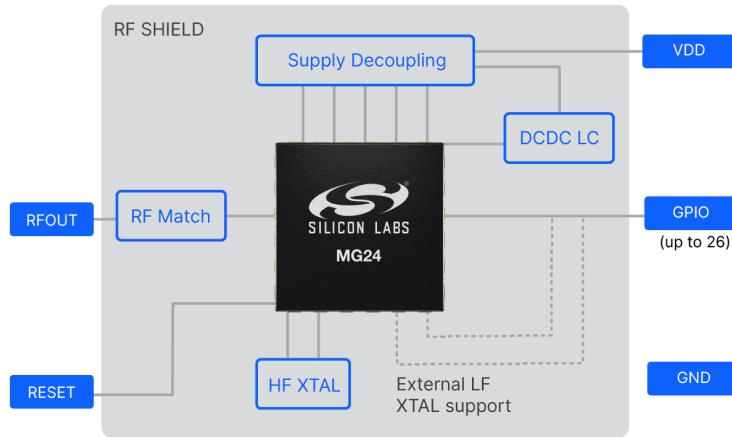

For designs where an external antenna solution may be beneficial, a module variant with a  $50\ \Omega$ -matched RF pin instead of the built-in antenna is available (for 20 dBm TX power only).

Because the RF matching network is optimized for transmit power efficiency, modules rated for +20 dBm will show non-optimal current consumption and performance when operated at a lower output power (e.g., +10 or 0 dBm).

Figure 3.1. BGM240P Block Diagram - Built-in Antenna Variant

Figure 3.2. BGM240P Block Diagram - RF Pin Variant

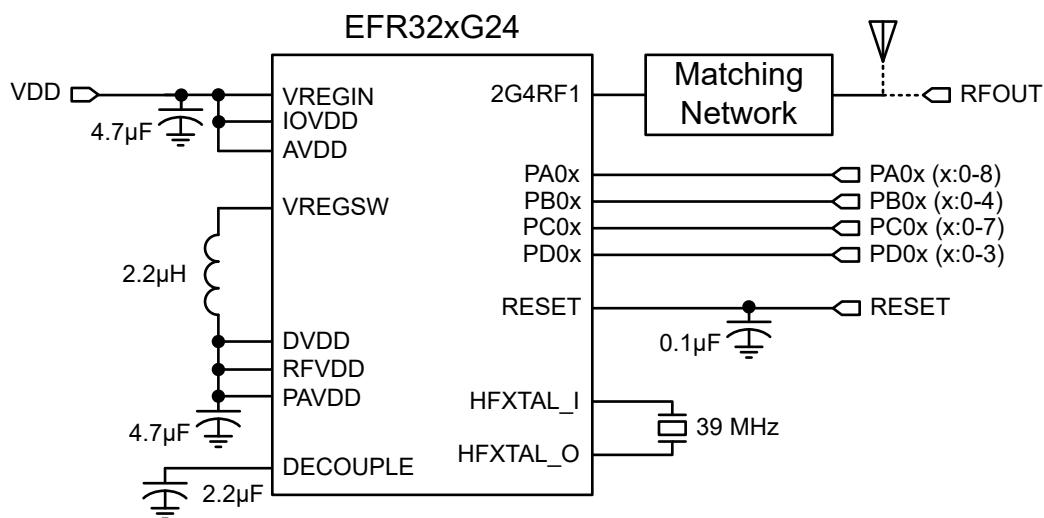

A simplified internal schematic for the BGM240P module is shown in [Figure 3.3 BGM240P Module Schematic on page 8](#).

**Figure 3.3. BGM240P Module Schematic**

### 3.2 EFR32BG24 SoC

The EFR32BG24 SoC features a 32-bit ARM Cortex M33 core, a 2.4 GHz high-performance radio, 1536 kB of Flash memory, 256 kB of RAM, a dedicated core for security, a rich set of MCU peripherals, and various clock management and serial interfacing options. See the [EFR32xG24 Reference Manual](#) and [EFR32BG24 Data Sheet](#) for details.

### 3.3 Antenna

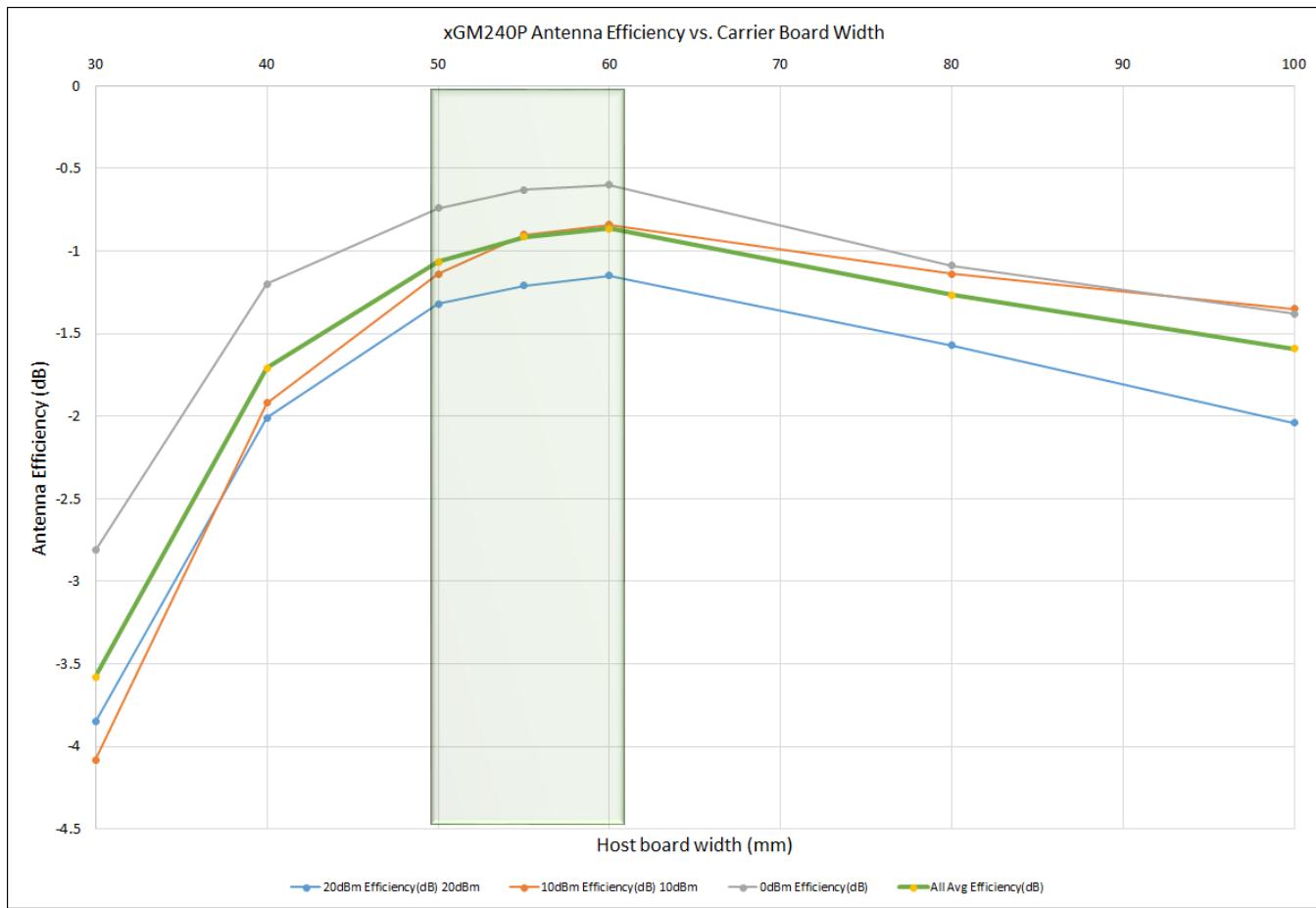

BGM240P modules come with two antenna solution variants: A built-in antenna or a 50  $\Omega$ -matched RF pin to support an external antenna. Typical performance characteristics for the built-in antenna are detailed in the table below. See [4.16 Antenna Radiation and Efficiency](#) and [11.1 Qualified Antennas](#) for other relevant details.

**Table 3.1. Antenna Efficiency and Peak Gain**

| Parameter  | With optimal layout | Note                                                                                                                                                                                                                                |

|------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Efficiency | -1 dB               | Antenna efficiency, gain, and radiation pattern are highly dependent on the application PCB layout and mechanical design. Refer to <a href="#">7. Design Guidelines</a> for recommendations to achieve optimal antenna performance. |

| Peak gain  | 1.82 dBi            |                                                                                                                                                                                                                                     |

### 3.4 Power Supply

The BGM240P requires a single nominal supply level (VDD) to operate and supports an operating range of 1.8 to 3.8 V. The nominal level needed for +10 dBm devices (Model: BGM240P22A) is 3.0 V whereas +20 dBm devices (Model: BGM240P32A, BGM240P32N) require 3.3 V to achieve higher TX output power. All necessary decoupling, filtering, and DC-DC-related components are included in the module.

**Note:** The power amplifier for +10 dBm modules is supplied through an internal LDO, and thus is independent of the VDD supply. Respectively, the power amplifier for +20 dBm modules is supplied through the VDD pin with a target level of 3.3 V.

### 3.5 General Purpose Input/Output (GPIO)

The BGM240P has up to 26 General Purpose Input/Output pins. Each GPIO pin can be individually configured as either an output or input. More advanced configurations including open-drain, open-source, and glitch-filtering can be configured for each individual GPIO pin. The GPIO pins can be overridden by peripheral connections, like SPI communication. Each peripheral connection can be routed to several GPIO pins on the device. The input value of a GPIO pin can be routed through the Peripheral Reflex System to other peripherals. The GPIO subsystem supports asynchronous external pin interrupts.

All of the pins on port A and port B are EM2 capable. These pins may be used by Low-Energy peripherals in EM2/3 and may also be used as EM2/3 pin wake-ups. Pins on ports C and D are latched/retained in their current state when entering EM2 until EM2 exit upon which internal peripherals could once again drive those pads.

A few GPIOs also have EM4 wake functionality. These pins are listed in the [Table 6.2 GPIO Alternate Functions Table on page 37](#).

### 3.6 Security

BGM240P modules support one of two levels in the Security Portfolio offered by Silicon Labs: Secure Vault Mid or Secure Vault High.

Secure Vault is a collection of technologies that deliver state-of-the-art security and upgradability features to protect and future-proof IoT devices against costly threats, attacks, and tampering. A dedicated security CPU enables the Secure Vault functions and isolates cryptographic functions and data from the Cortex-M33 core. BGM240PB part numbers support Secure Vault High and BGM240PA part numbers support Secure Vault Mid.

**Table 3.2. Secure Vault Features**

| Feature                                                 | Secure Vault Mid                                                                                                                   | Secure Vault High                                                                                                                                    |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| True Random Number Generator (TRNG)                     | Yes                                                                                                                                | Yes                                                                                                                                                  |

| Secure Boot with Root of Trust and Secure Loader (RTSL) | Yes                                                                                                                                | Yes                                                                                                                                                  |

| Secure Debug with Lock/Unlock                           | Yes                                                                                                                                | Yes                                                                                                                                                  |

| DPA Countermeasures                                     | Yes                                                                                                                                | Yes                                                                                                                                                  |

| Anti-Tamper                                             |                                                                                                                                    | Yes                                                                                                                                                  |

| Secure Attestation                                      |                                                                                                                                    | Yes                                                                                                                                                  |

| Secure Key Management                                   |                                                                                                                                    | Yes                                                                                                                                                  |

| Symmetric Encryption                                    | <ul style="list-style-type: none"> <li>AES 128 / 192 / 256 bit</li> <li>ECB, CTR, CBC, CFB, CCM, GCM, CBC-MAC, and GMAC</li> </ul> | <ul style="list-style-type: none"> <li>AES 128 / 192 / 256 bit</li> <li>ECB, CTR, CBC, CFB, CCM, GCM, CBC-MAC, and GMAC</li> <li>ChaCha20</li> </ul> |

| Public Key Encryption - ECDSA / ECDH / EdDSA            | <ul style="list-style-type: none"> <li>p192 and p256</li> </ul>                                                                    | <ul style="list-style-type: none"> <li>p192, p256, p384 and p521</li> <li>Curve25519 (ECDH)</li> <li>Ed25519 (EdDSA)</li> </ul>                      |

| Key Derivation                                          | <ul style="list-style-type: none"> <li>ECJ-PAKE p192 and p256</li> </ul>                                                           | <ul style="list-style-type: none"> <li>ECJ-PAKE p192, p256, p384, and p521</li> <li>PBKDF2</li> <li>HKDF</li> </ul>                                  |

| Hashes                                                  | <ul style="list-style-type: none"> <li>SHA-1</li> <li>SHA-2 256, 384, and 512</li> </ul>                                           | <ul style="list-style-type: none"> <li>SHA-1</li> <li>SHA-2 256, 384, and 512</li> <li>Poly1305</li> </ul>                                           |

### 3.6.1 Secure Boot with Root of Trust and Secure Loader (RTSL)

The Secure Boot with RTSL authenticates a chain of trusted firmware that begins from an immutable memory (ROM).

It prevents malware injection, prevents rollback, ensures that only authentic firmware is executed, and protects Over The Air updates.

For more information about this feature, see [AN1218: Series 2 Secure Boot with RTSL](#).

### 3.6.2 Cryptographic Accelerator

The Cryptographic Accelerator is an autonomous hardware accelerator with Differential Power Analysis (DPA) countermeasures to protect keys.

It supports AES encryption and decryption with 128/192/256-bit keys, ChaCha20 encryption, and Elliptic Curve Cryptography (ECC) to support public key operations and hashes.

Supported block cipher modes of operation for AES include:

- Electronic Code Book (ECB)

- Counter Mode (CTR)

- Cipher Block Chaining (CBC)

- Cipher Feedback (CFB)

- Galois Counter Mode (GCM)

- Counter with CBC-MAC (CCM)

- Cipher Block Chaining Message Authentication Code (CBC-MAC)

- Galois Message Authentication Code (GMAC)

The Cryptographic Accelerator accelerates Elliptic Curve Cryptography and supports the National Institute of Standards and Technology (NIST) recommended curves including P-192, P-256, P-384, and P-521 for Elliptic Curve Diffie-Hellman (ECDH) key derivation, and Elliptic Curve Digital Signature Algorithm (ECDSA) sign and verify operations. Also supported is the non-NIST Curve25519 for ECDH and Ed25519 for Edwards-curve Digital Signature Algorithm (EdDSA) sign and verify operations.

Secure Vault also supports Elliptic Curve variant of Password Authenticated Key Exchange by Juggling (ECJ-PAKE) and Password-Based Key Derivation Function 2 (PBKDF2).

Supported hashes include SHA-1, SHA-2/256/384/512 and Poly1305.

This implementation provides a fast and energy efficient solution to state of the art cryptographic needs.

### 3.6.3 True Random Number Generator

The TRNG module is a non-deterministic random number generator that harvests entropy from a thermal energy source. It includes start-up health tests for the entropy source as required by NIST SP800-90B and AIS-31, as well as online health tests required for NIST SP800-90C.

The TRNG is suitable for periodically generating entropy to seed an approved pseudo random number generator.

### 3.6.4 Secure Debug with Lock/Unlock

For obvious security reasons, it is critical for a product to have its debug interface locked before being released in the field.

Secure Vault also provides a secure debug unlock function that allows authenticated access based on public key cryptography. This functionality is particularly useful for supporting failure analysis while maintaining confidentiality of IP and sensitive end-user data.

For more information about this feature, see [AN1190: Series 2 Secure Debug](#).

### 3.6.5 DPA Countermeasures

The AES and ECC accelerators have Differential Power Analysis (DPA) countermeasures support. This makes it very expensive from a time and effort standpoint to use DPA to recover secret keys.

### 3.6.6 Secure Key Management with PUF

Key material in Secure Vault High products is protected by "key wrapping" with a standardized symmetric encryption mechanism. This method has the advantage of protecting a virtually unlimited number of keys, limited only by the storage that is accessible by the Cortex-M33, which includes off-chip storage as well. The symmetric key used for this wrapping and unwrapping must be highly secure because it can expose all other key materials in the system. The Secure Vault Key Management system uses a Physically Unclonable Function (PUF) to generate a persistent device-unique seed key on power up to dynamically generate this critical wrapping/unwrapping key which is only visible to the AES encryption engine and is not retained when the device loses power.

### 3.6.7 Anti-Tamper

Secure Vault High devices provide internal tamper protection which monitors parameters such as voltage, temperature, and electromagnetic pulses as well as detecting tamper of the security sub-system itself. Additionally, 8 external configurable tamper pins support external tamper sources, such as enclosure tamper switches.

For each tamper event, the user is able to select the severity of the tamper response ranging from an interrupt, to a reset, to destroying the PUF reconstruction data which will make all protected key materials un-recoverable and effectively render the device inoperable. The tamper system also has an internal resettable event counter with programmable trigger threshold and refresh periods to mitigate false positive tamper events.

For more information about this feature, see [AN1247: Anti-Tamper Protection Configuration and Use](#).

### 3.6.8 Secure Attestation

Secure Vault High products support Secure Attestation, which begins with a secure identity that is created during the Silicon Labs manufacturing process. During device production, each device generates its own public/private keypair and securely stores the wrapped private key into immutable OTP memory and this key never leaves the device. The corresponding public key is extracted from the device and inserted into a binary DER-encoded X.509 device certificate, which is signed into a Silicon Labs CA chain and then programmed back into the chip into an immutable OTP memory.

The secure identity can be used to authenticate the chip at any time in the life of the product. The production certification chain can be requested remotely from the product. This certification chain can be used to verify that the device was authentically produced by Silicon Labs. The device unique public key is also bound to the device certificate in the certification chain. A challenge can be sent to the chip at any point in time to be signed by the device private key. The public key in the device certificate can then be used to verify the challenge response, proving that the device has access to the securely-stored private key, which prevents counterfeit products or impersonation attacks.

For more information about this feature, see [AN1268: Authenticating Silicon Labs Devices Using Device Certificates](#).

## 4. Electrical Specifications

All electrical parameters in all tables are specified under the following conditions, unless stated otherwise:

- Typical values are based on  $T_A=25\text{ }^{\circ}\text{C}$  and VDD supply at 3.0 V, by production test and/or technology characterization.

- Radio performance numbers are measured in conducted mode, based on Silicon Laboratories reference designs using output power-specific external RF impedance-matching networks for interfacing to a  $50\text{ }\Omega$  antenna.

- Minimum and maximum values represent the worst conditions across supply voltage, process variation, and operating temperature, unless stated otherwise.

### 4.1 Absolute Maximum Ratings

**Table 4.1. Absolute Maximum Ratings**

| Parameter                                                                                                                                                                                                                                                                 | Symbol          | Test Condition | Min  | Typ | Max             | Unit                   |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|------|-----|-----------------|------------------------|--|

| Storage temperature range                                                                                                                                                                                                                                                 | $T_{STG}$       |                | -40  | —   | +105            | $^{\circ}\text{C}$     |  |

| Voltage on any supply pin                                                                                                                                                                                                                                                 | $V_{DDMAX}$     |                | -0.3 | —   | 3.8             | V                      |  |

| Voltage ramp rate on any supply pin                                                                                                                                                                                                                                       | $V_{DDRAMPMAX}$ |                | —    | —   | 1.0             | $\text{V}/\mu\text{s}$ |  |

| DC voltage on any GPIO pin                                                                                                                                                                                                                                                | $V_{DIGPIN}$    |                | -0.3 | —   | $V_{VDD} + 0.3$ | V                      |  |

| DC voltage on RESETn pin <sup>1</sup>                                                                                                                                                                                                                                     | $V_{RESETn}$    |                | -0.3 | —   | 3.8             | V                      |  |

| Absolute voltage on RFOUT pin                                                                                                                                                                                                                                             | $V_{MAX2G4}$    |                | -0.3 | —   | $V_{VDD} + 0.3$ | V                      |  |

| Total current into VDD pin                                                                                                                                                                                                                                                | $I_{VDDMAX}$    | Source         | —    | —   | 200             | mA                     |  |

| Total current into GND pin                                                                                                                                                                                                                                                | $I_{VSSMAX}$    | Sink           | —    | —   | 200             | mA                     |  |

| Current per I/O pin                                                                                                                                                                                                                                                       | $I_{IOMAX}$     | Sink           | —    | —   | 50              | mA                     |  |

|                                                                                                                                                                                                                                                                           |                 | Source         | —    | —   | 50              | mA                     |  |

| Current for all I/O pins                                                                                                                                                                                                                                                  | $I_{IOALLMAX}$  | Sink           | —    | —   | 200             | mA                     |  |

|                                                                                                                                                                                                                                                                           |                 | Source         | —    | —   | 200             | mA                     |  |

| <b>Note:</b>                                                                                                                                                                                                                                                              |                 |                |      |     |                 |                        |  |

| 1. The RESETn pin has a pull-up device to the internal DVDD supply. For minimum leakage, RESETn should not exceed the voltage at DVDD, which is generated by the DC-DC converter. DVDD is equal to 1.8 V when DC-DC is active and bypassed to VDD when DC-DC is inactive. |                 |                |      |     |                 |                        |  |

## 4.2 General Operating Conditions

Table 4.2. General Operating Conditions

| Parameter                           | Symbol                   | Test Condition                     | Min | Typ  | Max  | Unit |

|-------------------------------------|--------------------------|------------------------------------|-----|------|------|------|

| Operating ambient temperature range | $T_A$                    |                                    | -40 | —    | +105 | °C   |

| VDD operating supply voltage        | V <sub>VDD</sub>         | 10 dBm Module, DC-DC in regulation | 2.2 | 3.0  | 3.8  | V    |

|                                     |                          | 20 dBm Module, DC-DC in regulation | 2.2 | 3.3  | 3.8  | V    |

|                                     |                          | 10 dBm Module, DC-DC in bypass     | 1.8 | 3.0  | 3.8  | V    |

|                                     |                          | 20 dBm Module, DC-DC in bypass     | 1.8 | 3.3  | 3.8  | V    |

| HCLK and SYSCLK frequency           | f <sub>HCLK</sub>        | VSCALE2, MODE = WS1                | —   | —    | 78   | MHz  |

|                                     |                          | VSCALE2, MODE = WS0                | —   | —    | 40   | MHz  |

| EM01 Group A clock frequency        | f <sub>EM01GRPACLK</sub> | VSCALE2                            | —   | —    | 78   | MHz  |

|                                     |                          | VSCALE1                            | —   | —    | 40   | MHz  |

| EM01 Group C clock frequency        | f <sub>EM01GRPCCLK</sub> | VSCALE2                            | —   | —    | 78   | MHz  |

|                                     |                          | VSCALE1                            | —   | —    | 40   | MHz  |

| Radio HCLK frequency                | f <sub>RHCLK</sub>       | VSCALE2 or VSCALE1                 | —   | 39.0 | —    | MHz  |

#### 4.3 MCU Current Consumption at 3.0 V

Unless otherwise indicated, typical conditions are: VDD = 3.0 V, DC-DC in regulation. Voltage scaling level = VSCALE1. TA = 25 °C. Minimum and maximum values in this table represent the worst conditions across process variation at TA = 25 °C.

**Table 4.3. MCU Current Consumption at 3.0 V**

| Parameter                                                     | Symbol              | Test Condition                                                                                  | Min | Typ  | Max | Unit   |

|---------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0 mode with all peripherals disabled | I <sub>ACTIVE</sub> | 78 MHz HFRCO w/ DLL referenced to 39 MHz crystal, CPU running Prime from flash, VSCALE2         | —   | 33.3 | —   | µA/MHz |

|                                                               |                     | 78 MHz HFRCO w/ DLL referenced to 39 MHz crystal, CPU running while loop from flash, VSCALE2    | —   | 32.8 | —   | µA/MHz |

|                                                               |                     | 78 MHz HFRCO w/ DLL referenced to 39 MHz crystal, CPU running CoreMark loop from flash, VSCALE2 | —   | 49.1 | —   | µA/MHz |

|                                                               |                     | 39 MHz crystal, CPU running Prime from flash                                                    | —   | 33.9 | —   | µA/MHz |

|                                                               |                     | 39 MHz crystal, CPU running while loop from flash                                               | —   | 33.4 | —   | µA/MHz |

|                                                               |                     | 39 MHz crystal, CPU running CoreMark loop from flash                                            | —   | 49.4 | —   | µA/MHz |

|                                                               |                     | 38 MHz HFRCO, CPU running while loop from flash                                                 | —   | 28.1 | —   | µA/MHz |

| Current consumption in EM1 mode with all peripherals disabled | I <sub>EM1</sub>    | 78 MHz HFRCO w/ DLL referenced to 39 MHz crystal, VSCALE2                                       | —   | 22.6 | —   | µA/MHz |

|                                                               |                     | 39 MHz crystal                                                                                  | —   | 24.4 | —   | µA/MHz |

|                                                               |                     | 38 MHz HFRCO                                                                                    | —   | 19.0 | —   | µA/MHz |

| Current consumption in EM2 mode, VSCALE0                      | I <sub>EM2_VS</sub> | 256 kB RAM and full Radio RAM retention, RTC running from LFXO <sup>1</sup>                     | —   | 2.9  | —   | µA     |

|                                                               |                     | 256 kB RAM and full Radio RAM retention, RTC running from LFRCO <sup>1</sup>                    | —   | 2.9  | —   | µA     |

|                                                               |                     | 16 kB RAM and full Radio RAM retention, RTC running from LFXO <sup>1</sup>                      | —   | 1.3  | —   | µA     |

|                                                               |                     | 16 kB RAM and full Radio RAM retention, RTC running from LFRCO <sup>1</sup>                     | —   | 1.3  | —   | µA     |

|                                                               |                     | 16 kB RAM and full Radio RAM retention, RTC running from LFRCO in precision mode <sup>1</sup>   | —   | 1.9  | —   | µA     |

| Parameter                                                | Symbol              | Test Condition                                                                | Min | Typ  | Max | Unit |

|----------------------------------------------------------|---------------------|-------------------------------------------------------------------------------|-----|------|-----|------|

| Current consumption in EM3 mode, VSCALE0                 | I <sub>EM3_VS</sub> | 256 kB RAM and full Radio RAM retention, RTC running from ULFRCO <sup>1</sup> | —   | 2.7  | —   | µA   |

|                                                          |                     | 16 kB RAM and full Radio RAM retention, RTC running from ULFRCO <sup>1</sup>  | —   | 1.1  | —   | µA   |

| Current consumption in EM4 mode                          | I <sub>EM4</sub>    | No BURTC, no LF oscillator                                                    | —   | 0.27 | —   | µA   |

|                                                          |                     | BURTC with LFXO                                                               | —   | 0.64 | —   | µA   |

| Current consumption during reset                         | I <sub>RST</sub>    | Hard pin reset held                                                           | —   | 467  | —   | µA   |

| <b>Note:</b>                                             |                     |                                                                               |     |      |     |      |

| 1. CPU cache retained, EM0/1 peripheral states retained. |                     |                                                                               |     |      |     |      |

#### 4.4 Radio Current Consumption with 3.0 V Supply

RF current consumption measured with MCU in EM1 and all MCU peripherals disabled. Unless otherwise indicated, typical conditions are: VDD = 3.0 V, DC-DC in regulation. T<sub>A</sub> = 25 °C.

**Table 4.4. Radio Current Consumption with 3.0 V Supply**

| Parameter                                                                                                                         | Symbol                 | Test Condition                                                 | Min | Typ   | Max | Unit |  |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------------------------|-----|-------|-----|------|--|

| Current consumption in receive mode, active packet reception, VSCALE1, EM1P                                                       | I <sub>RX_ACTIVE</sub> | 125 kbit/s, 2GFSK, f = 2.4 GHz                                 | —   | 4.8   | —   | mA   |  |

|                                                                                                                                   |                        | 500 kbit/s, 2GFSK, f = 2.4 GHz                                 | —   | 4.9   | —   | mA   |  |

|                                                                                                                                   |                        | 1 Mbit/s, 2GFSK, f = 2.4 GHz                                   | —   | 4.5   | —   | mA   |  |

|                                                                                                                                   |                        | 2 Mbit/s, 2GFSK, f = 2.4 GHz                                   | —   | 5.2   | —   | mA   |  |

| Current consumption in receive mode, listening for packet, VSCALE1, EM1P                                                          | I <sub>RX_LISTEN</sub> | 125 kbit/s, 2GFSK, f = 2.4 GHz                                 | —   | 4.8   | —   | mA   |  |

|                                                                                                                                   |                        | 500 kbit/s, 2GFSK, f = 2.4 GHz                                 | —   | 4.8   | —   | mA   |  |

|                                                                                                                                   |                        | 1 Mbit/s, 2GFSK, f = 2.4 GHz                                   | —   | 4.5   | —   | mA   |  |

|                                                                                                                                   |                        | 2 Mbit/s, 2GFSK, f = 2.4 GHz                                   | —   | 5.2   | —   | mA   |  |

| Current consumption in transmit mode                                                                                              | I <sub>TX</sub>        | f = 2.4 GHz, CW, 20 dBm output power, VDD = 3.3 V <sup>1</sup> | —   | 154.8 | —   | mA   |  |

|                                                                                                                                   |                        | f = 2.4 GHz, CW, 10 dBm output power                           | —   | 18.8  | —   | mA   |  |

|                                                                                                                                   |                        | f = 2.4 GHz, CW, 0 dBm output power                            | —   | 4.8   | —   | mA   |  |

| <b>Note:</b>                                                                                                                      |                        |                                                                |     |       |     |      |  |

| 1. The maximum output power for Bluetooth Low Energy is limited to 19.6 dBm for compliance with the Bluetooth Core Specification. |                        |                                                                |     |       |     |      |  |

**4.5 RF Transmitter General Characteristics for the 2.4 GHz Band**

Unless otherwise indicated, typical conditions are: VDD = 3.0 V, DC-DC in regulation. RF center frequency 2.45 GHz. TA = 25 °C.

**Table 4.5. RF Transmitter General Characteristics for the 2.4 GHz Band**

| Parameter                                                                | Symbol                | Test Condition                                                 | Min  | Typ   | Max  | Unit |

|--------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------|------|-------|------|------|

| RF tuning frequency range                                                | F <sub>RANGE</sub>    |                                                                | 2402 | —     | 2480 | MHz  |

| Maximum TX power <sup>1</sup>                                            | POUT <sub>MAX</sub>   | 20 dBm, VDD = 3.3 V <sup>2</sup>                               | —    | 19.6  | —    | dBm  |

|                                                                          |                       | 10 dBm                                                         | —    | 10    | —    | dBm  |

|                                                                          |                       | 0 dBm                                                          | —    | -0.3  | —    | dBm  |

| Minimum active TX power                                                  | POUT <sub>MIN</sub>   | 20 dBm, VDD = 3.3 V                                            | —    | -33.7 | —    | dBm  |

|                                                                          |                       | 10 dBm                                                         | —    | -30   | —    | dBm  |

|                                                                          |                       | 0 dBm                                                          | —    | -24   | —    | dBm  |

| Output power step size                                                   | POUT <sub>STEP</sub>  | 0 dBm                                                          | 0.1  | 0.7   | 9.9  | dB   |

|                                                                          |                       | 10 dBm, -5 dBm < Output power < 0 dBm                          | 0.6  | 1.1   | 1.8  | dB   |

|                                                                          |                       | 10 dBm, 0 dBm < Output power < 10 dBm                          | 0.1  | 0.3   | 0.8  | dB   |

|                                                                          |                       | 20 dBm, VDD = 3.3 V, Output power < 0 dBm                      | 0.9  | 3.6   | 14.4 | dB   |

|                                                                          |                       | 20 dBm, 0 dBm < Output power < 20 dBm                          | 0.1  | 0.2   | 1.3  | dB   |

| Output power variation vs supply voltage variation, frequency = 2450 MHz | POUT <sub>VAR_V</sub> | 20 dBm output power with VDD voltage swept from 1.8 V to 3.8 V | —    | 5.4   | —    | dB   |

|                                                                          |                       | 10 dBm output power with VDD voltage swept from 1.8 V to 3.8 V | —    | 0.05  | —    | dB   |

|                                                                          |                       | 0 dBm output power with VDD voltage swept from 1.8 V to 3.8 V  | —    | 0.01  | —    | dB   |

| Output power variation vs temperature, Frequency = 2450 MHz              | POUT <sub>VAR_T</sub> | 20 dBm, VDD = 3.3 V, (-40 to +105 °C)                          | —    | 0.2   | —    | dB   |

|                                                                          |                       | 10 dBm, (-40 to +105 °C)                                       | —    | 0.3   | —    | dB   |

|                                                                          |                       | 0 dBm, (-40 to +105 °C)                                        | —    | 1.0   | —    | dB   |

| Output power variation over the RF tuning frequency range                | POUT <sub>VAR_F</sub> | 20 dBm, VDD = 3.3 V                                            | —    | 0.2   | —    | dB   |

|                                                                          |                       | 10 dBm                                                         | —    | 0.2   | —    | dB   |

|                                                                          |                       | 0 dBm                                                          | —    | 0.2   | —    | dB   |

**Note:**

1. Supported transmit power levels are determined by the ordering part number (OPN). Transmit power ratings for all devices covered in this datasheet can be found in the TX Power column of the Ordering Information Table.

2. The maximum output power for Bluetooth Low Energy is limited to 19.6 dBm for compliance with the Bluetooth Core Specification.

#### 4.6 RF Receiver General Characteristics for the 2.4 GHz Band

Unless otherwise indicated, typical conditions are: VDD = 3.0 V, DC-DC in regulation. RF center frequency 2.45 GHz. TA = 25 °C.

**Table 4.6. RF Receiver General Characteristics for the 2.4 GHz Band**

| Parameter                 | Symbol             | Test Condition | Min  | Typ | Max  | Unit |

|---------------------------|--------------------|----------------|------|-----|------|------|

| RF tuning frequency range | F <sub>RANGE</sub> |                | 2402 | —   | 2480 | MHz  |

**4.7 RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 1 Mbps Data Rate**

Unless otherwise indicated, typical conditions are: VDD = 3.0 V, DC-DC in regulation. RF center frequency 2.45 GHz. TA = 25 °C.

**Table 4.7. RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 1 Mbps Data Rate**

| Parameter                              | Symbol              | Test Condition                                                                               | Min | Typ   | Max | Unit |

|----------------------------------------|---------------------|----------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Max usable receiver input level        | SAT                 | Signal is reference signal <sup>1</sup>                                                      | —   | 10    | —   | dBm  |

| Sensitivity                            | SENS                | 10 dBm module. Signal is reference signal, 37 byte payload <sup>1</sup>                      | —   | -98.5 | —   | dBm  |

|                                        |                     | 10 dBm module. Signal is reference signal, 255 byte payload <sup>1</sup>                     | —   | -96.9 | —   | dBm  |

|                                        |                     | 10 dBm module with non-ideal signals <sup>2 1</sup>                                          | —   | -96.5 | —   | dBm  |

|                                        |                     | 20 dBm module. Signal is reference signal, 37 byte payload <sup>1</sup>                      | —   | -97.6 | —   | dBm  |

|                                        |                     | 20 dBm module. Signal is reference signal, 255 byte payload <sup>1</sup>                     | —   | -96   | —   | dBm  |

|                                        |                     | 20 dBm module with non-ideal signals <sup>2 1</sup>                                          | —   | -95.6 | —   | dBm  |

| Signal to co-channel interferer        | C/I <sub>CC</sub>   | (see notes) <sup>1 3</sup>                                                                   | —   | 8.7   | —   | dB   |

| N ± 1 Adjacent channel selectivity     | C/I <sub>1</sub>    | Interferer is reference signal at +1 MHz offset <sup>1 4 3 5</sup>                           | —   | -5.4  | —   | dB   |

|                                        |                     | Interferer is reference signal at -1 MHz offset <sup>1 4 3 5</sup>                           | —   | -5.3  | —   | dB   |

| N ± 2 Alternate channel selectivity    | C/I <sub>2</sub>    | Interferer is reference signal at +2 MHz offset <sup>1 4 3 5</sup>                           | —   | -40.9 | —   | dB   |

|                                        |                     | Interferer is reference signal at -2 MHz offset <sup>1 4 3 5</sup>                           | —   | -39.7 | —   | dB   |

| N ± 3 Alternate channel selectivity    | C/I <sub>3</sub>    | Interferer is reference signal at +3 MHz offset <sup>1 4 3 5</sup>                           | —   | -45.5 | —   | dB   |

|                                        |                     | Interferer is reference signal at -3 MHz offset <sup>1 4 3 5</sup>                           | —   | -45.7 | —   | dB   |

| Selectivity to image frequency         | C/I <sub>IM</sub>   | Interferer is reference signal at image frequency with 1 MHz precision <sup>1 5</sup>        | —   | -23.3 | —   | dB   |

| Selectivity to image frequency ± 1 MHz | C/I <sub>IM_1</sub> | Interferer is reference signal at image frequency +1 MHz with 1 MHz precision <sup>1 5</sup> | —   | -40.9 | —   | dB   |

|                                        |                     | Interferer is reference signal at image frequency -1 MHz with 1 MHz precision <sup>1 5</sup> | —   | -5.4  | —   | dB   |

| Intermodulation performance            | IM                  | n = 3 (see note <sup>6</sup> )                                                               | —   | -17.3 | —   | dBm  |

| Parameter                                                                                                                                                                                                                                                                                                                                                               | Symbol | Test Condition | Min | Typ | Max | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|-----|-----|-----|------|

| <b>Note:</b>                                                                                                                                                                                                                                                                                                                                                            |        |                |     |     |     |      |

| 1. 0.017% Bit Error Rate.<br>2. With non-ideal signals as specified in Bluetooth Test Specification RF-PHY.TS.5.0.1 section 4.7.1.<br>3. Desired signal -67 dBm.<br>4. Desired frequency $2402 \text{ MHz} \leq F_c \leq 2480 \text{ MHz}$ .<br>5. With allowed exceptions.<br>6. As specified in Bluetooth Core specification version 5.1, Vol 6, Part A, Section 4.4. |        |                |     |     |     |      |

**4.8 RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 2 Mbps Data Rate**

Unless otherwise indicated, typical conditions are: VDD = 3.0 V, DC-DC in regulation. RF center frequency 2.45 GHz. TA = 25 °C.

**Table 4.8. RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 2 Mbps Data Rate**

| Parameter                              | Symbol              | Test Condition                                                                               | Min | Typ   | Max | Unit |

|----------------------------------------|---------------------|----------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Max usable receiver input level        | SAT                 | Signal is reference signal <sup>1</sup>                                                      | —   | 10    | —   | dBm  |

| Sensitivity                            | SENS                | 10 dBm module. Signal is reference signal, 37 byte payload <sup>1</sup>                      | —   | -95.7 | —   | dBm  |

|                                        |                     | 10 dBm module. Signal is reference signal, 255 byte payload <sup>1</sup>                     | —   | -94.2 | —   | dBm  |

|                                        |                     | 10 dBm module with non-ideal signals <sup>2 1</sup>                                          | —   | -93.9 | —   | dBm  |

|                                        |                     | 20 dBm module. Signal is reference signal, 37 byte payload <sup>1</sup>                      | —   | -94.8 | —   | dBm  |

|                                        |                     | 20 dBm module. Signal is reference signal, 255 byte payload <sup>1</sup>                     | —   | -93.3 | —   | dBm  |

|                                        |                     | 20 dBm module with non-ideal signals <sup>2 1</sup>                                          | —   | -93.1 | —   | dBm  |

| Signal to co-channel interferer        | C/I <sub>CC</sub>   | (see notes) <sup>1 3</sup>                                                                   | —   | 8.6   | —   | dB   |

| N ± 1 Adjacent channel selectivity     | C/I <sub>1</sub>    | Interferer is reference signal at +2 MHz offset <sup>1 4 3 5</sup>                           | —   | -5.3  | —   | dB   |

|                                        |                     | Interferer is reference signal at -2 MHz offset <sup>1 4 3 5</sup>                           | —   | -5.8  | —   | dB   |

| N ± 2 Alternate channel selectivity    | C/I <sub>2</sub>    | Interferer is reference signal at +4 MHz offset <sup>1 4 3 5</sup>                           | —   | -42.2 | —   | dB   |

|                                        |                     | Interferer is reference signal at -4 MHz offset <sup>1 4 3 5</sup>                           | —   | -44.2 | —   | dB   |

| N ± 3 Alternate channel selectivity    | C/I <sub>3</sub>    | Interferer is reference signal at +6 MHz offset <sup>1 4 3 5</sup>                           | —   | -48.1 | —   | dB   |

|                                        |                     | Interferer is reference signal at -6 MHz offset <sup>1 4 3 5</sup>                           | —   | -50.2 | —   | dB   |

| Selectivity to image frequency         | C/I <sub>IM</sub>   | Interferer is reference signal at image frequency with 1 MHz precision <sup>1 5</sup>        | —   | -22.8 | —   | dB   |

| Selectivity to image frequency ± 2 MHz | C/I <sub>IM_1</sub> | Interferer is reference signal at image frequency +2 MHz with 1 MHz precision <sup>1 5</sup> | —   | -42.2 | —   | dB   |

|                                        |                     | Interferer is reference signal at image frequency -2 MHz with 1 MHz precision <sup>1 5</sup> | —   | -5.3  | —   | dB   |

| Intermodulation performance            | IM                  | n = 3 (see note <sup>6</sup> )                                                               | —   | -18.3 | —   | dBm  |

| Parameter                                                                                                                                                                                                                                                                                                                                                               | Symbol | Test Condition | Min | Typ | Max | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|-----|-----|-----|------|

| <b>Note:</b>                                                                                                                                                                                                                                                                                                                                                            |        |                |     |     |     |      |

| 1. 0.017% Bit Error Rate.<br>2. With non-ideal signals as specified in Bluetooth Test Specification RF-PHY.TS.5.0.1 section 4.7.1.<br>3. Desired signal -64 dBm.<br>4. Desired frequency $2402 \text{ MHz} \leq F_c \leq 2480 \text{ MHz}$ .<br>5. With allowed exceptions.<br>6. As specified in Bluetooth Core specification version 5.1, Vol 6, Part A, Section 4.4. |        |                |     |     |     |      |

**4.9 RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 500 kbps Data Rate**

Unless otherwise indicated, typical conditions are: VDD = 3.0 V, DC-DC in regulation. RF center frequency 2.45 GHz. TA = 25 °C.

**Table 4.9. RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 500 kbps Data Rate**

| Parameter                              | Symbol              | Test Condition                                                                               | Min | Typ    | Max | Unit |

|----------------------------------------|---------------------|----------------------------------------------------------------------------------------------|-----|--------|-----|------|

| Max usable receiver input level        | SAT                 | Signal is reference signal <sup>1</sup>                                                      | —   | 10     | —   | dBm  |

| Sensitivity                            | SENS                | 10 dBm module. Signal is reference signal, 37 byte payload <sup>1</sup>                      | —   | -102.2 | —   | dBm  |

|                                        |                     | 10 dBm module. Signal is reference signal, 255 byte payload <sup>1</sup>                     | —   | -101   | —   | dBm  |

|                                        |                     | 10 dBm module with non-ideal signals <sup>2 1</sup>                                          | —   | -100   | —   | dBm  |

|                                        |                     | 20 dBm module. Signal is reference signal, 37 byte payload <sup>1</sup>                      | —   | -101.4 | —   | dBm  |

|                                        |                     | 20 dBm module. Signal is reference signal, 255 byte payload <sup>1</sup>                     | —   | -100   | —   | dBm  |

|                                        |                     | 20 dBm module with non-ideal signals <sup>2 1</sup>                                          | —   | -99    | —   | dBm  |

| Signal to co-channel interferer        | C/I <sub>CC</sub>   | (see notes) <sup>1 3</sup>                                                                   | —   | 2.7    | —   | dB   |

| N ± 1 Adjacent channel selectivity     | C/I <sub>1</sub>    | Interferer is reference signal at +1 MHz offset <sup>1 4 3 5</sup>                           | —   | -7.1   | —   | dB   |

|                                        |                     | Interferer is reference signal at -1 MHz offset <sup>1 4 3 5</sup>                           | —   | -7.4   | —   | dB   |

| N ± 2 Alternate channel selectivity    | C/I <sub>2</sub>    | Interferer is reference signal at +2 MHz offset <sup>1 4 3 5</sup>                           | —   | -46.8  | —   | dB   |

|                                        |                     | Interferer is reference signal at -2 MHz offset <sup>1 4 3 5</sup>                           | —   | -49.7  | —   | dB   |

| N ± 3 Alternate channel selectivity    | C/I <sub>3</sub>    | Interferer is reference signal at +3 MHz offset <sup>1 4 3 5</sup>                           | —   | -49.4  | —   | dB   |

|                                        |                     | Interferer is reference signal at -3 MHz offset <sup>1 4 3 5</sup>                           | —   | -54.5  | —   | dB   |

| Selectivity to image frequency         | C/I <sub>IM</sub>   | Interferer is reference signal at image frequency with 1 MHz precision <sup>1 5</sup>        | —   | -49    | —   | dB   |

| Selectivity to image frequency ± 1 MHz | C/I <sub>IM_1</sub> | Interferer is reference signal at image frequency +1 MHz with 1 MHz precision <sup>1 5</sup> | —   | -49.4  | —   | dB   |

|                                        |                     | Interferer is reference signal at image frequency -1 MHz with 1 MHz precision <sup>1 5</sup> | —   | -46.8  | —   | dB   |

| Parameter                                                                                                                                                                                                                                                                   | Symbol | Test Condition | Min | Typ | Max | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|-----|-----|-----|------|

| <b>Note:</b>                                                                                                                                                                                                                                                                |        |                |     |     |     |      |

| 1. 0.017% Bit Error Rate.<br>2. With non-ideal signals as specified in Bluetooth Test Specification RF-PHY.TS.5.0.1 section 4.7.1.<br>3. Desired signal -72 dBm.<br>4. Desired frequency $2402 \text{ MHz} \leq F_c \leq 2480 \text{ MHz}$ .<br>5. With allowed exceptions. |        |                |     |     |     |      |

**4.10 RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 125 kbps Data Rate**

Unless otherwise indicated, typical conditions are: VDD = 3.0 V, DC-DC in regulation. RF center frequency 2.45 GHz. TA = 25 °C.

**Table 4.10. RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 125 kbps Data Rate**

| Parameter                              | Symbol              | Test Condition                                                                               | Min | Typ    | Max | Unit |

|----------------------------------------|---------------------|----------------------------------------------------------------------------------------------|-----|--------|-----|------|

| Max usable receiver input level        | SAT                 | Signal is reference signal <sup>1</sup>                                                      | —   | 10     | —   | dBm  |

| Sensitivity                            | SENS                | 10 dBm module. Signal is reference signal, 37 byte payload <sup>1</sup>                      | —   | -106.5 | —   | dBm  |

|                                        |                     | 10 dBm module. Signal is reference signal, 255 byte payload <sup>1</sup>                     | —   | -106.1 | —   | dBm  |

|                                        |                     | 10 dBm module with non-ideal signals <sup>2 1</sup>                                          | —   | -105.7 | —   | dBm  |

|                                        |                     | 20 dBm module. Signal is reference signal, 37 byte payload <sup>1</sup>                      | —   | -105.6 | —   | dBm  |

|                                        |                     | 20 dBm module. Signal is reference signal, 255 byte payload <sup>1</sup>                     | —   | -105.3 | —   | dBm  |

|                                        |                     | 20 dBm module with non-ideal signals <sup>2 1</sup>                                          | —   | -104.8 | —   | dBm  |

| Signal to co-channel interferer        | C/I <sub>CC</sub>   | (see notes) <sup>1 3</sup>                                                                   | —   | 0.9    | —   | dB   |

| N ± 1 Adjacent channel selectivity     | C/I <sub>1</sub>    | Interferer is reference signal at +1 MHz offset <sup>1 4 3 5</sup>                           | —   | -12.4  | —   | dB   |

|                                        |                     | Interferer is reference signal at -1 MHz offset <sup>1 4 3 5</sup>                           | —   | -12.8  | —   | dB   |

| N ± 2 Alternate channel selectivity    | C/I <sub>2</sub>    | Interferer is reference signal at +2 MHz offset <sup>1 4 3 5</sup>                           | —   | -52.6  | —   | dB   |

|                                        |                     | Interferer is reference signal at -2 MHz offset <sup>1 4 3 5</sup>                           | —   | -55.5  | —   | dB   |

| N ± 3 Alternate channel selectivity    | C/I <sub>3</sub>    | Interferer is reference signal at +3 MHz offset <sup>1 4 3 5</sup>                           | —   | -53.8  | —   | dB   |

|                                        |                     | Interferer is reference signal at -3 MHz offset <sup>1 4 3 5</sup>                           | —   | -60    | —   | dB   |

| Selectivity to image frequency         | C/I <sub>IM</sub>   | Interferer is reference signal at image frequency with 1 MHz precision <sup>1 5</sup>        | —   | -53    | —   | dB   |

| Selectivity to image frequency ± 1 MHz | C/I <sub>IM_1</sub> | Interferer is reference signal at image frequency +1 MHz with 1 MHz precision <sup>1 5</sup> | —   | -53.8  | —   | dB   |

|                                        |                     | Interferer is reference signal at image frequency -1 MHz with 1 MHz precision <sup>1 5</sup> | —   | -52.6  | —   | dB   |

| Parameter                                                                                             | Symbol | Test Condition | Min | Typ | Max | Unit |

|-------------------------------------------------------------------------------------------------------|--------|----------------|-----|-----|-----|------|

| <b>Note:</b>                                                                                          |        |                |     |     |     |      |

| 1. 0.017% Bit Error Rate.                                                                             |        |                |     |     |     |      |

| 2. With non-ideal signals as specified in Bluetooth Test Specification RF-PHY.TS.5.0.1 section 4.7.1. |        |                |     |     |     |      |

| 3. Desired signal -79 dBm.                                                                            |        |                |     |     |     |      |

| 4. Desired frequency 2402 MHz $\leq$ Fc $\leq$ 2480 MHz.                                              |        |                |     |     |     |      |

| 5. With allowed exceptions.                                                                           |        |                |     |     |     |      |

#### 4.11 High-Frequency Crystal

Table 4.11. High-Frequency Crystal

| Parameter                   | Symbol           | Test Condition                     | Min | Typ  | Max | Unit |

|-----------------------------|------------------|------------------------------------|-----|------|-----|------|

| Crystal frequency           | $f_{HFXTAL}$     |                                    | —   | 39   | —   | MHz  |

| Initial calibrated accuracy | $ACC_{HFXTAL}$   |                                    | -10 | +/-5 | 10  | ppm  |

| Temperature drift           | $DRIFT_{HFXTAL}$ | Across specified temperature range | -20 | —    | 20  | ppm  |

## 4.12 Low Frequency Crystal Oscillator

Table 4.12. Low Frequency Crystal Oscillator

| Parameter                                                      | Symbol          | Test Condition                                                            | Min  | Typ    | Max  | Unit |

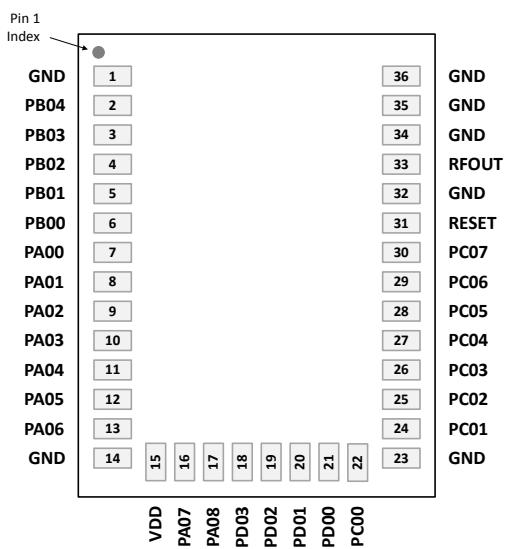

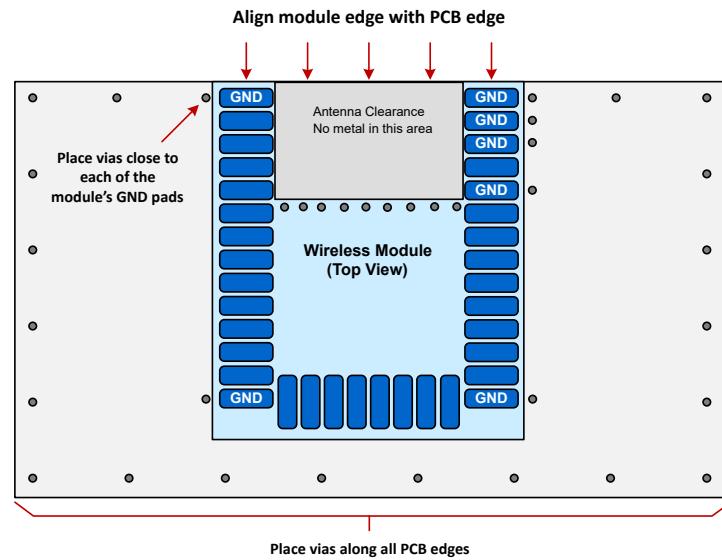

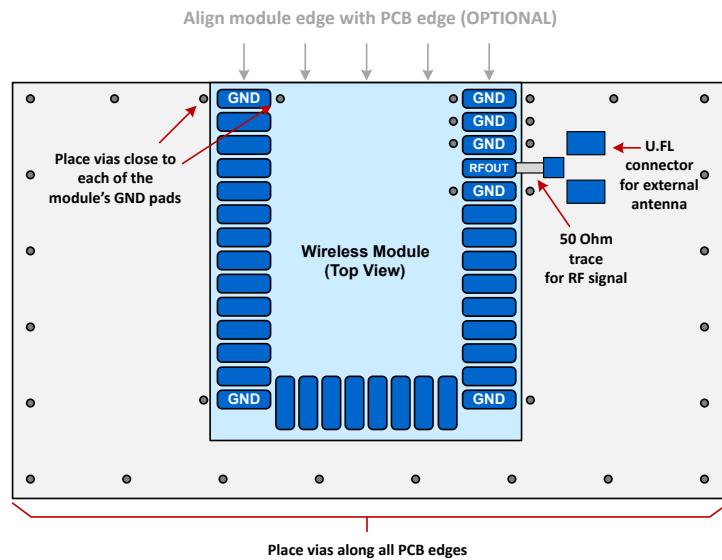

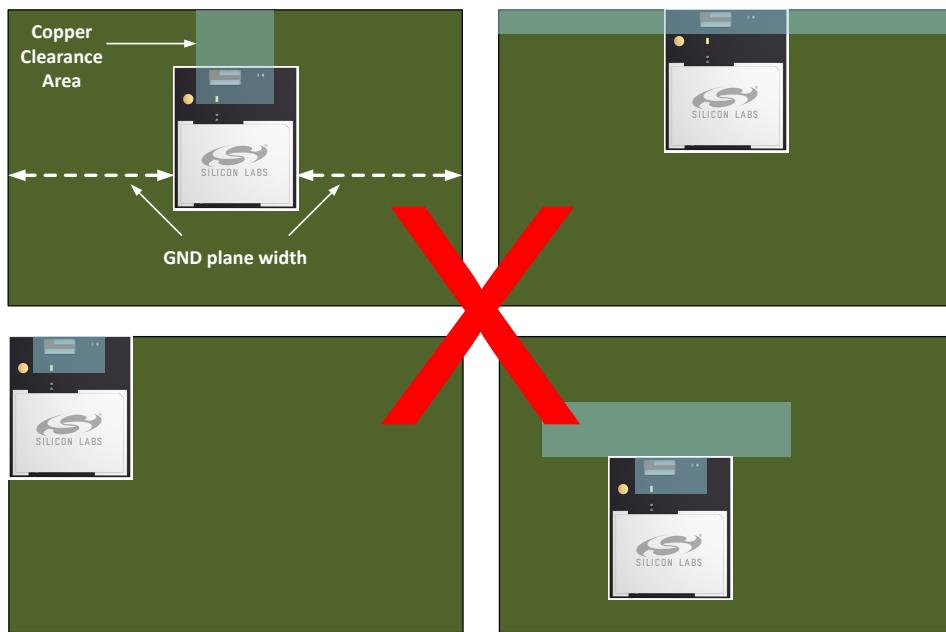

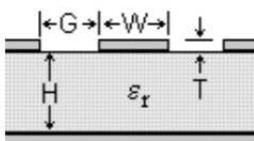

|----------------------------------------------------------------|-----------------|---------------------------------------------------------------------------|------|--------|------|------|