## Industrial Dual Channel USB 3.2 Gen 1 Reclocker/Redriver

### Features

- Extending the reach of USB 3.2 Gen 1 (SuperSpeed) up to 16m

- Cable types supported are STP (Shielded Twisted Pair) and Coax

- Cable lengths supported

- Up to 5m when USB 2.0 signaling included in cable

- Up to 16m when USB 3.2 only

- EyeOpen*™ technology automatically performs cable compensation 0 to 24 dB with 1 dB steps

- MarginLink*™ integrated signal integrity test capability

- CDR (Clock-Data Recovery) restores signal timing integrity in both directions

- Reference Clock-free operation (no crystal or clock needed)

- Internal terminations for low external component count

- Transparent for all USB 3.2 SuperSpeed signaling including LFPS and electrical-idle

- Dual Channel Single Lane

- 20 pin 4 mm QFN package with wettable flanks

- Low power consumption / single supply @ 1.2V

- Ultra low power sleep mode when link is idle for a sustained period

- Industrial temperature range

### Applications

- Extended reach for video conference systems

- Extended reach cable for VR gaming applications

- Extending active USB 3.2 cables

- Extending USB3 Vision™ systems

### General Description

The EQCO5X31 is a fully qualified single chip USB 3.2 SuperSpeed Reclocker/Redriver with *EyeOpen*™ and *MarginLink*™ technology for the industrial and commercial market segments. The EQCO5X31 will reclock and drive a USB 3.2 SuperSpeed signal over a cable up to 16m reliably. Furthermore, the EQCO5X31 extends max cable length from a recommended 1m to 5m to meet the maximum length of USB2.0 and up to 16m for USB 3.2 links for longer reach applications. Now designers can easily create applications to support both USB 2.0 and USB 3.2 up to 5 meters and USB 3.2 only up to 16m meters in cable length.

The EQCO5X31 is a single chip (equalizer, driver, reclocker) that repeats high speed data signals with a rate of 5 Gbps. From a cable or PCB trace pair, the signal is received by an auto-adaptive equalizer that compensates for higher-frequency losses in the preceding channel. A reference-less clock-data recovery (CDR) subsequently resets jitter back to meet USB 3.2 specifications for maintaining signal integrity. A cable driver launches this clean signal back onto a cable or PCB trace pair. When placed in series as a repeater, a signal can travel through several EQCO5X31 devices to the destination. The EQCO5X31 CDR restores signal timing integrity at each link along the way.

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at [docerrors@microchip.com](mailto:docerrors@microchip.com). We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

<http://www.microchip.com>

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; <http://www.microchip.com>

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### Customer Notification System

Register on our web site at [www.microchip.com](http://www.microchip.com) to receive the most current information on all of our products.

## Conventions

The following abbreviations and symbols are used to improve readability.

| Example                | Description                                                                                                                                                                       |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>BIT</b>             | Name of a single bit within a field                                                                                                                                               |

| <b>FIELD.BIT</b>       | Name of a single bit (BIT) in FIELD                                                                                                                                               |

| x...y                  | Range from x to y, inclusive                                                                                                                                                      |

| <b>BITS[m:n]</b>       | Groups of bits from m to n, inclusive                                                                                                                                             |

| <b>PIN</b>             | Pin Name                                                                                                                                                                          |

| <b>SIGNAL</b>          | Signal Name                                                                                                                                                                       |

| msb, lsb               | Most significant bit, least significant bit                                                                                                                                       |

| MSB, LSB               | Most significant byte, least significant byte                                                                                                                                     |

| zzzzb                  | Binary number (value zzzz)                                                                                                                                                        |

| 0xzzz                  | Hexadecimal number (value zzz)                                                                                                                                                    |

| zzh                    | Hexadecimal number (value zz)                                                                                                                                                     |

| rsvd                   | Reserved memory location. Must write 0, read value indeterminate                                                                                                                  |

| code                   | Instruction code, or API function or parameter                                                                                                                                    |

| <i>Multi Word Name</i> | Used for multiple words that are considered a single unit, such as: <i>Resource Allocate</i> message, or <i>Connection Label</i> , or <i>Decrement Stack Pointer</i> instruction. |

| <i>Section Name</i>    | Emphasis, Reference, Section or Document name.                                                                                                                                    |

| <b>VAL</b>             | Over-bar indicates active low pin or register bit                                                                                                                                 |

| x                      | Don't care                                                                                                                                                                        |

| <Parameter>            | <> indicate a Parameter is optional or is only used under some conditions                                                                                                         |

| {,Parameter}           | Braces indicate Parameter(s) that repeat one or more times.                                                                                                                       |

| [Parameter]            | Brackets indicate a nested Parameter. This Parameter is not real and actually decodes into one or more real parameters.                                                           |

# EQCO5X31

---

---

## TABLE OF CONTENTS

|   |                                   |    |

|---|-----------------------------------|----|

| 1 | OVERVIEW .....                    | 5  |

| 2 | EQCO5X31 PINOUT .....             | 6  |

| 3 | EQCO5X31 CIRCUIT CONNECTION ..... | 7  |

| 4 | ELECTRICAL SPECIFICATIONS .....   | 9  |

| 5 | APPLICATION INFORMATION .....     | 10 |

| 6 | PACKAGING INFORMATION .....       | 17 |

|   | APPENDIX A REFERENCES .....       | 21 |

|   | APPENDIX B REVISION HISTORY ..... | 21 |

|   | Ordering Information .....        | 23 |

## 1.0 OVERVIEW

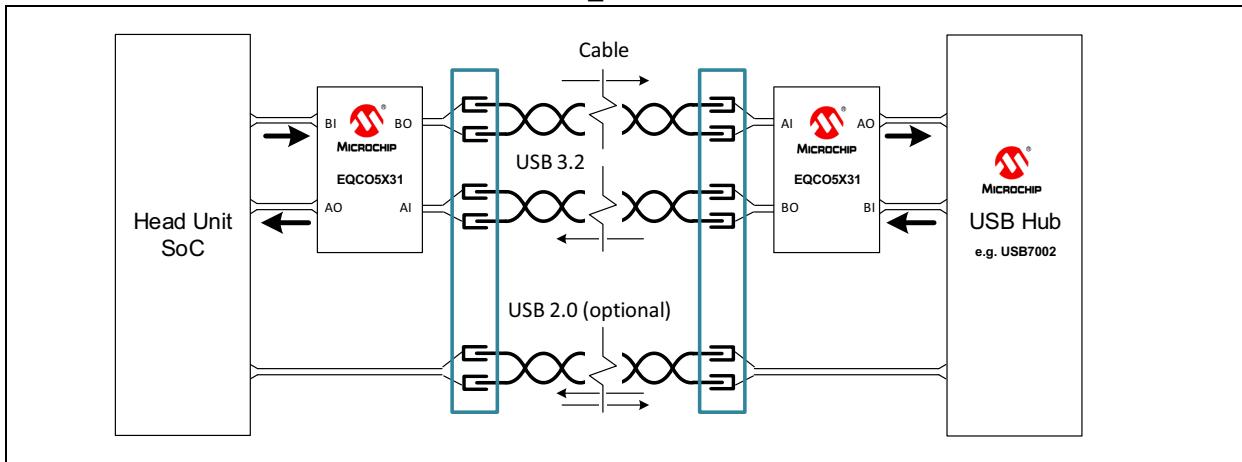

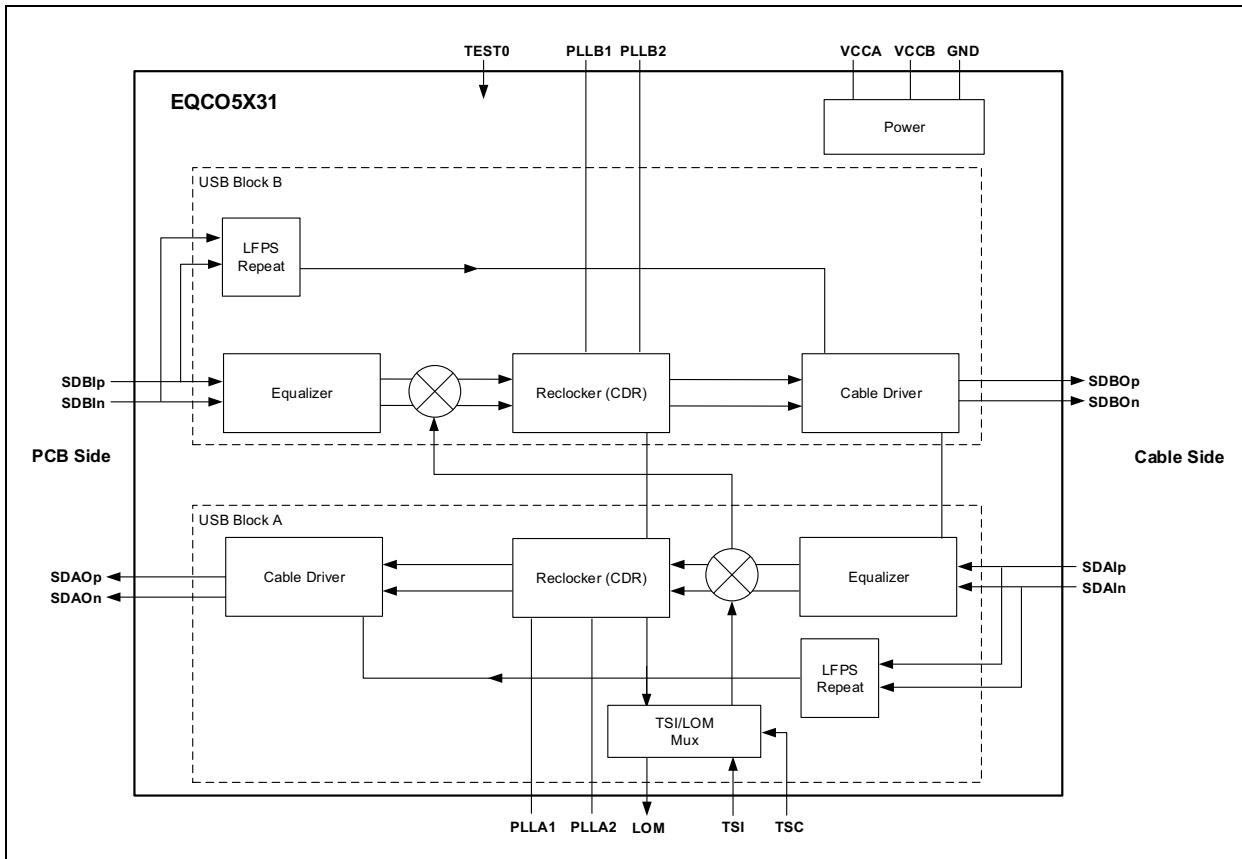

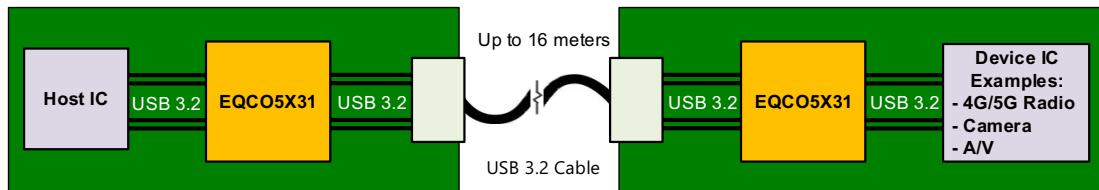

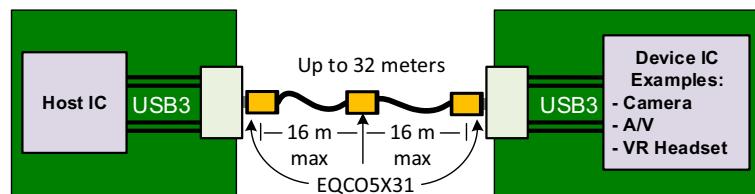

The EQCO5X31 is a USB Reclocker/Redriver intended to increase the cable distances of USB 3.2 SuperSpeed ports in industrial environments. A typical EQCO5X31 Link Set-up is shown in [Figure 1-1](#) along with an internal block diagram showing pin connections in [Figure 1-2](#). See the Section 5.0 of the Data Sheet for additional use-case scenarios. Other use-case scenarios are shown in [Section 5.0 “Application Information”](#).

FIGURE 1-1: TYPICAL EQCO5X31 LINK SET\_UP

**FIGURE 1-2: EQCO5X31 BLOCK DIAGRAM SHOWING PIN CONNECTIONS**

**Note:** The EQCO5X31 has two sides: the Cable side, which is typically routed to a cable connector, and the PCB side which is typically routed on a PCB to an IC. The cores in each direction are identical and each can drive cable or PCB traces.

# EQCO5X31

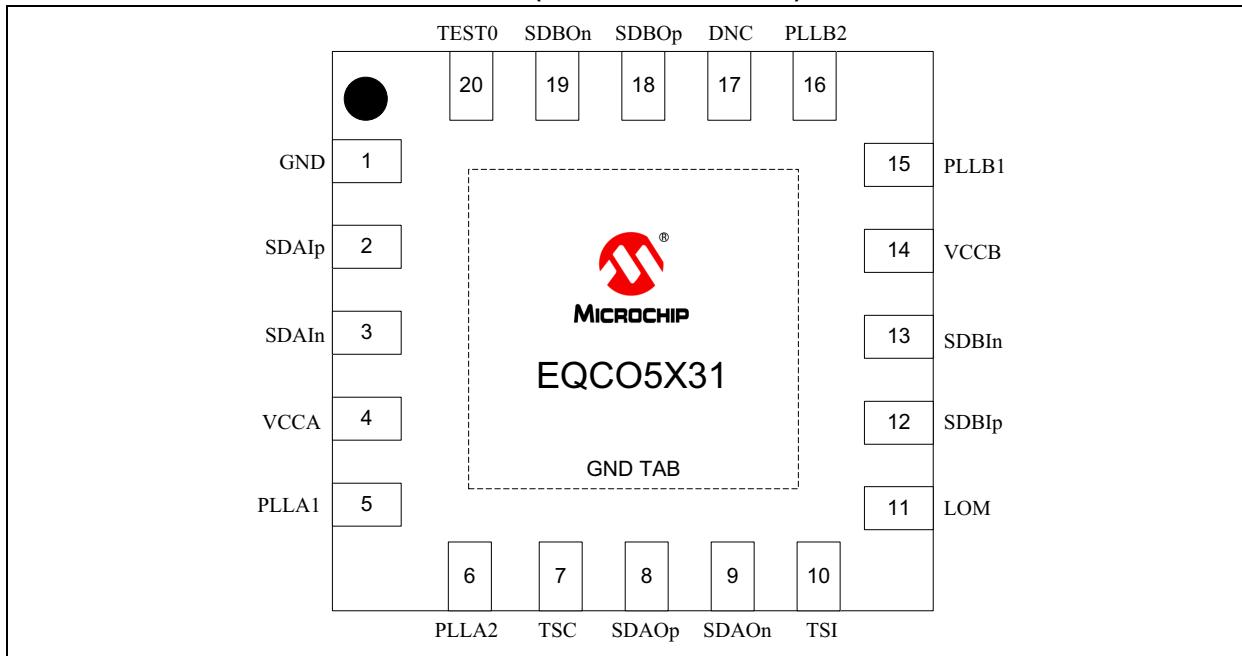

## 2.0 EQCO5X31 PINOUT

FIGURE 2-1: EQCO5X31 PIN DIAGRAM (VIEWED FROM TOP)

TABLE 2-1: EQCO5X31 PIN DESCRIPTIONS TABLE

| Pin Number | Name               | Type                | Description                                                                                                                                                                                                                                         |

|------------|--------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (TAB)      | <b>GND</b>         | Power               | Connect to Ground. This pad should be connected to ground with in-pad vias.                                                                                                                                                                         |

| 1          | <b>GND</b>         | Power               | Connect to GND TAB directly.                                                                                                                                                                                                                        |

| 2,3        | <b>SDAIp/SDAIn</b> | Differential Input  | USB Cable side differential serial input pair.                                                                                                                                                                                                      |

| 4          | <b>VCCA</b>        | Power               | Connect to +1.2V of power supply.                                                                                                                                                                                                                   |

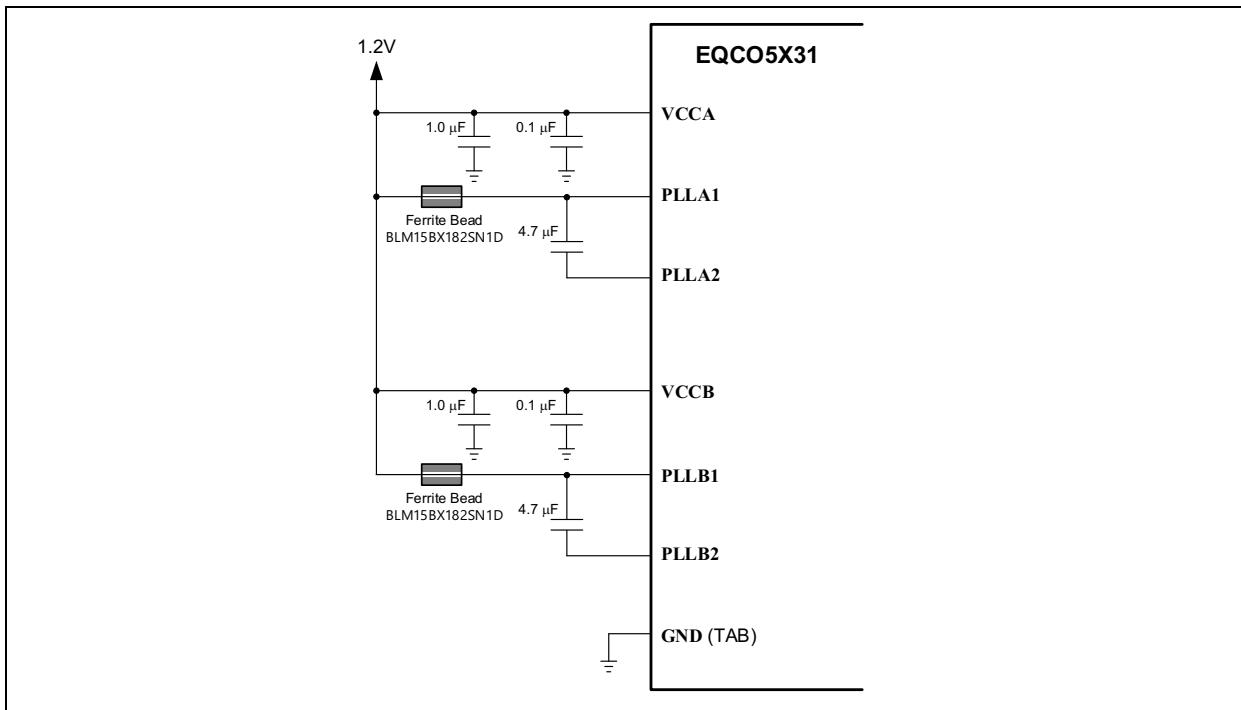

| 5          | <b>PLLA1</b>       | Power               | Connect to +1.2V of power supply through a ferrite bead.                                                                                                                                                                                            |

| 6          | <b>PLLA2</b>       | Power               | Connect to PLLA1 through a capacitor.                                                                                                                                                                                                               |

| 7          | <b>TSC</b>         | Digital Input       | Test Select Channel input. This pin selects the channel (A or B) that the TSI and LOM pins are associated with, High = Chan A, Low = Chan B. See <a href="#">Section 5.4</a> for further details on how to use this pin.                            |

| 8,9        | <b>SDAOp/SDAOn</b> | Differential Output | PCB side differential serial output pair.                                                                                                                                                                                                           |

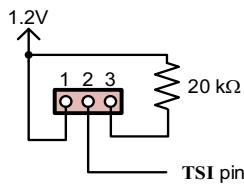

| 10         | <b>TSI</b>         | Analog Input        | Test Signal Integrity input for channel A or channel B (selected by TSC pin). This pin has a weak internal pull down (20 kΩ) so it can be left unconnected if not used. See <a href="#">Section 5.4</a> for further details on how to use this pin. |

| 11         | <b>LOM</b>         | Digital Output      | Low Margin. A low to high pulse indicates when a bit error is detected on channel A or channel B (selected by TSC pin). See <a href="#">Section 5.4</a> for further details on how to use this pin.                                                 |

| 12,13      | <b>SDBIp/SDBIn</b> | Differential Input  | PCB side differential serial input pair.                                                                                                                                                                                                            |

| 14         | <b>VCCB</b>        | Power               | Connect to +1.2V of power supply.                                                                                                                                                                                                                   |

| 15         | <b>PLLBI</b>       | Power               | Connect to +1.2V of power supply through a ferrite bead.                                                                                                                                                                                            |

| 16         | <b>PLL2</b>        | Power               | Connect to PLLB1 through a capacitor.                                                                                                                                                                                                               |

| 17         | <b>DNC</b>         | -                   | Do Not Connect. The pin must be left floating externally.                                                                                                                                                                                           |

| 18,19      | <b>SDBOp/SDBOn</b> | Differential Output | USB Cable side differential serial output pair.                                                                                                                                                                                                     |

| 20         | <b>TEST0</b>       | Input               | Must be low. Either tie directly to GND or if compliance mode support is needed, tie to GND with a 0Ω resistor, and add a test point on the pin. See <a href="#">Section 5.5</a> for more information about compliance mode.                        |

## 3.0 EQCO5X31 CIRCUIT CONNECTION

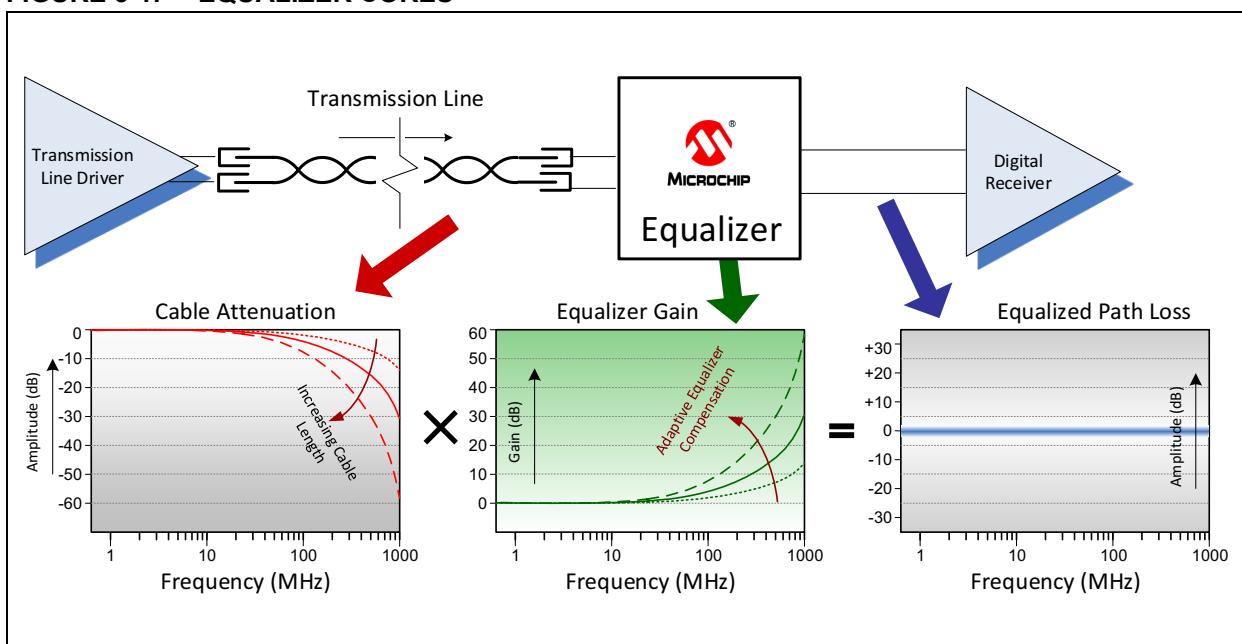

### 3.1 EyeOpen™ Equalizer Cores

The EQCO5X31 has an integrated receiver / equalizer in each direction with the following characteristics.

- Auto-adaptive

The equalizer controls a multiple pole analog filter which compensates for attenuation of the cable, as illustrated in [Figure 3-1](#). The filter frequency response needed to restore the signal is automatically determined by the device using a time-continuous feedback loop that measures the frequency components in the signal. Upon the detection of a valid signal, the control loop converges within a few microseconds.

- Variable gain

The EQCO5X31 equalizer has variable gain to compensate for low frequency attenuation through the cable and variations in transmit amplitude.

- Single speed

The EQCO5X31 equalizer cores work at a data rate of 5 Gbps (USB 3.2 SuperSpeed).

- Integrated termination

The EQCO5X31 receiver includes on-chip termination, no external termination components are required.

**FIGURE 3-1: EQUALIZER CORES**

### 3.2 Reclocker Cores

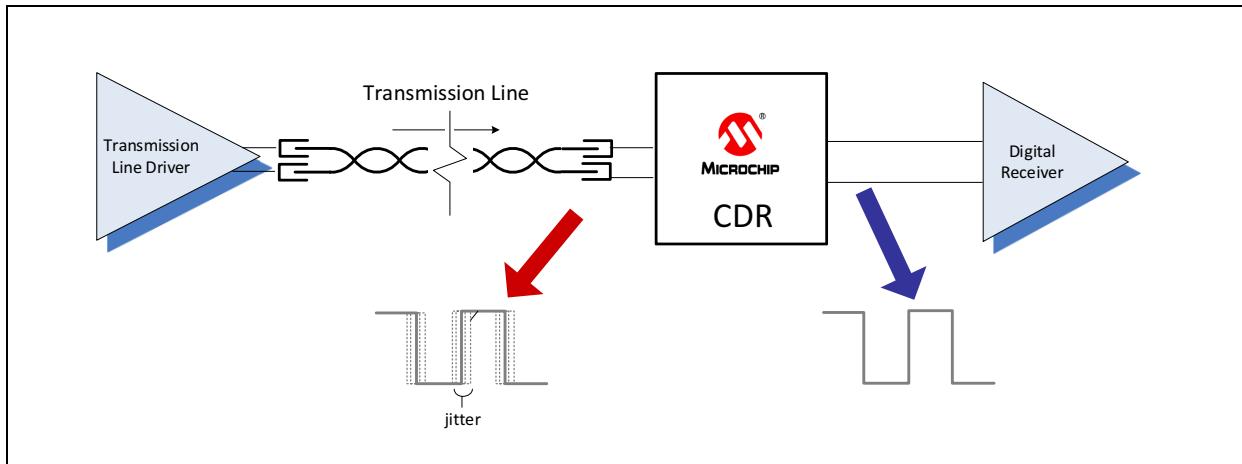

The EQCO5X31 has an integrated reclocker (CDR) in each data direction. The reference-less clock-data recovery subsequently resets the jitter back to a low value for maintaining signal timing integrity, as illustrated in [Figure 3-2](#).

- Reference-clock free operation

The reclocker cores do not require any external reference clock or crystal.

- Single speed

The EQCO5X31 reclocker cores work at a data rate of 5 Gbps (USB 3.2 SuperSpeed).

- Analog VCC and GND

For best performance the reclocker cores have their own analog power pins along with external filter components. This provides a clean supply rail for the internal PLL. For more details see the [Section 5.7 "Power Connectivity"](#).

# EQCO5X31

- Integrated signal integrity testing

For purposes of testing and verification, impairment can be added to the signal path just before the reclocker, via the **TSI** pin and results measured via the **LOM** pin. This added impairment has similar effects as adding extra cable length and thus provides a quick way to test a design for adequate margin. See [Section 5.4 "MarginLink™ Signal Integrity Pins \(TSI, LOM and TSC\)"](#) for more information on how **TSI** and **LOM** can be used.

**FIGURE 3-2: RECLKER CORES**

**Note:** The high speed data sent over the USB 3.2 SuperSpeed ports MUST be 8b/10b encoded.

## 3.3 Cable Driver Cores

The EQCO5X31 has integrated cable driver cores in each direction with the following characteristics:

- Cable Driver Operation

The cable driver drives the digital signals onto the **SDxOp/SDxOn** pins and is designed to work with single-ended or differential interfaces. The cable driver takes its output to electrical idle (squench) when there is no high frequency or LFPS input at the **SDxIp/SDxIn** pins. The cable driver also includes circuits which determine the presence of RX termination on the remote side in accordance with the standard.

- Single speed

The EQCO5X31 cable driver cores work at a single speed of 5 Gbps (USB 3.2 SuperSpeed).

- Integrated termination

The EQCO5X31 cable driver includes on-chip termination, no external termination components are required.

## 3.4 LFPS Repeat Cores

The EQCO5X31 has integrated LFPS (Low Frequency Periodic Signaling) repeat cores in each direction. The LFPS Repeat cores detect LFPS at the input, condition the LFPS timing and send to the output. Spread Spectrum modulation is applied to the LFPS signal output to reduce EMI.

## 3.5 Sleep Mode

The power block takes the EQCO5X31 to a low power state when both directions are in sustained idle.

## 4.0 ELECTRICAL SPECIFICATIONS

Specifications are subject to change without notice.

### 4.1 Absolute Maximum Ratings

TABLE 4-1: ABSOLUTE MAXIMUM RATINGS

| Parameter <sup>1</sup>   | Conditions    | Min  | Typ | Max  | Unit |

|--------------------------|---------------|------|-----|------|------|

| Storage Temperature      |               | -65  |     | +150 | °C   |

| Ambient Temperature      | Power Applied | -55  |     | +125 | °C   |

| Supply Voltage to Ground |               | -0.5 |     | +1.4 | V    |

| DC Input Voltage         |               | -0.5 |     | +1.6 | V    |

| DC Voltage to Outputs    |               | -0.5 |     | +1.6 | V    |

| Current into Outputs     | Outputs Low   |      |     | 90   | mA   |

**Note 1:** Stresses above those listed in this table may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions may affect device reliability.

### 4.2 Electrical Characteristics

Over the Operating  $V_{CC}$  and temperature range. All pertinent USB Gen 1 electrical parameters from the [USB 3.2 Specifications \[1\]](#) have been validated.

TABLE 4-2: ELECTRICAL CHARACTERISTICS

| Parameter                                                                               | Description                                         | Min  | Typ | Max                       | Unit |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------|------|-----|---------------------------|------|

| <b>Temperature (see additional package thermal data in <a href="#">Section 6.2</a>)</b> |                                                     |      |     |                           |      |

| $T_a$                                                                                   | Ambient Temperature                                 | -40  |     | 85                        | °C   |

| <b>Power Supply</b>                                                                     |                                                     |      |     |                           |      |

| $V_{CC}$                                                                                | Supply Voltage                                      | 1.14 | 1.2 | 1.26                      | V    |

| $I_s$ (operational)                                                                     | Supply current, both directions operating at 5 Gbps |      | 100 | 145 @ 1.2V<br>168 @ 1.26V | mA   |

| $I_s$ (sleep)                                                                           | Supply Current in sleep mode                        |      |     | 210 @ 25C<br>600 @ 85C    | µA   |

| <b>LOM Output</b>                                                                       |                                                     |      |     |                           |      |

| $V_{oh}$                                                                                | Output High Voltage                                 | 1.0  | 1.2 |                           | V    |

| $V_{ol}$                                                                                | Output Low Voltage                                  |      | GND | 0.1                       | V    |

| $t_{LOM}$                                                                               | High Pulse Width                                    | 18   | 36  | 60                        | ns   |

| <b>TSC Input</b>                                                                        |                                                     |      |     |                           |      |

| $V_{ih}$                                                                                | Input High Voltage                                  | 1.0  | 1.2 |                           | V    |

| $V_{il}$                                                                                | Input Low Voltage                                   |      | GND | 0.15                      | V    |

| <b>TSI Input</b>                                                                        |                                                     |      |     |                           |      |

| $V_i$                                                                                   | Input Voltage                                       | GND  |     | $V_{CC}$                  | V    |

# EQCO5X31

## 5.0 APPLICATION INFORMATION

### 5.1 Usage Diagrams

The following figures show examples of how the EQCO5X31 can be used in different scenarios. Other applications that need extension of USB 3.2 signaling are also possible. One example of this would be USB3 Vision™.

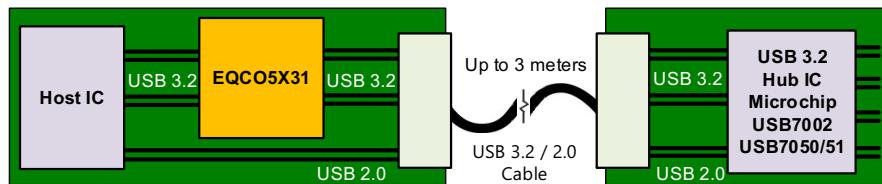

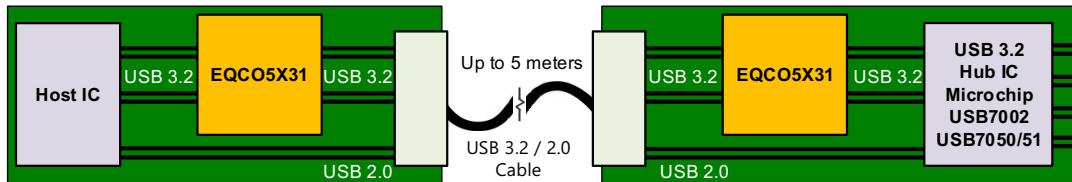

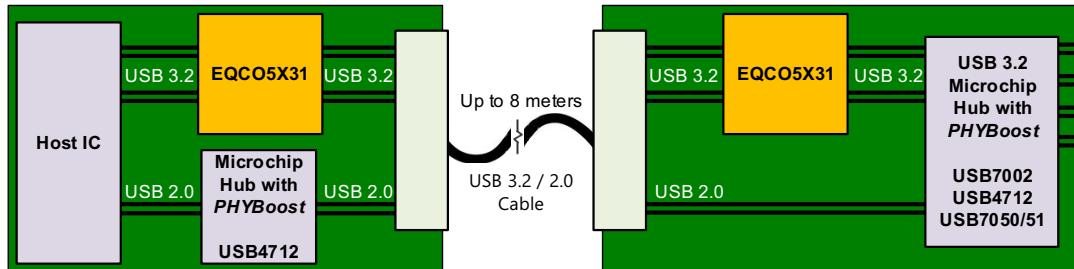

#### 5.1.1 USB 3.2 WITH USB 2.0 CO-EXISTENCE

For extending USB 3.2 connections that include USB 2.0, cables up to 8 meters can be supported. For cable lengths up to 3 meters, a single EQCO5X31 can be used to provide extra margin and reliability over standard 3-meter links (see [Figure 5-1](#)). For cable lengths up to 5 meters, two EQCO5X31 parts are required, one on each end (see [Figure 5-2](#)). For cable lengths up to 8 meters, the USB 2.0 signals can also be extended by using a Microchip hub with *PHYboost* technology (see [Figure 5-3](#)). Some example use cases are shown below.

**FIGURE 5-1: IMPROVED INTEGRITY / RELIABILITY AT USB 3.2 STANDARD LENGTHS**

**FIGURE 5-2: EXTENDING USB 3.2 TO MATCH USB 2.0 STANDARD LENGTHS**

**FIGURE 5-3: EXTENDING USB 3.2 AND USB 2.0**

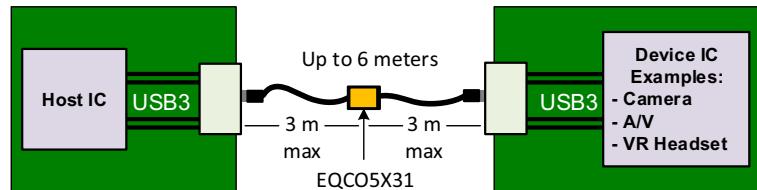

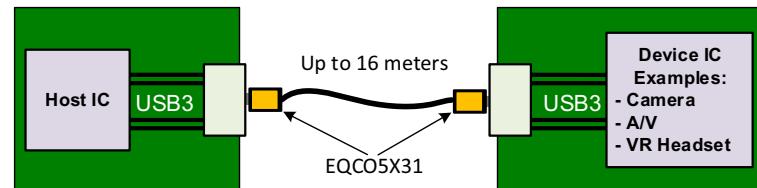

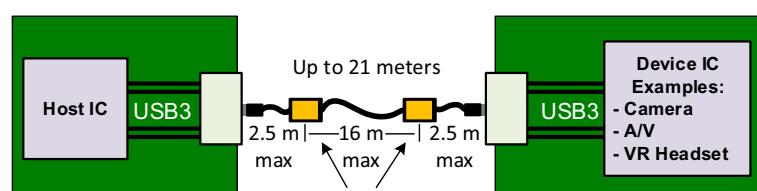

## 5.1.2 LONGER CABLES FOR USB 3.2 ONLY

For extending USB 3.2 connections that do not include USB 2.0, longer cables can be supported. For cable lengths beyond 5 meters, upgraded connectors and cables might be required that have improved crosstalk and loss parameters. Please see [Section 5.2](#) for more information on cable lengths. Some example use-cases are shown below.

**FIGURE 5-4: EXTENDING USB 3.2 ONLY CONNECTIONS**

**FIGURE 5-5: EXTENDING USB 3.2 ACTIVE CABLE USING ONE CENTER PLACED EQCO5X31**

**FIGURE 5-6: EXTENDING USB 3.2 ACTIVE CABLE USING TWO END PLACED EQCO5X31**

**FIGURE 5-7: EXTENDING USB 3.2 ACTIVE CABLE USING TWO NEAR-END PLACED EQCO5X31**

# EQCO5X31

**FIGURE 5-8: EXTENDING USB 3.2 ACTIVE CABLE USING THREE EQCO5X31**

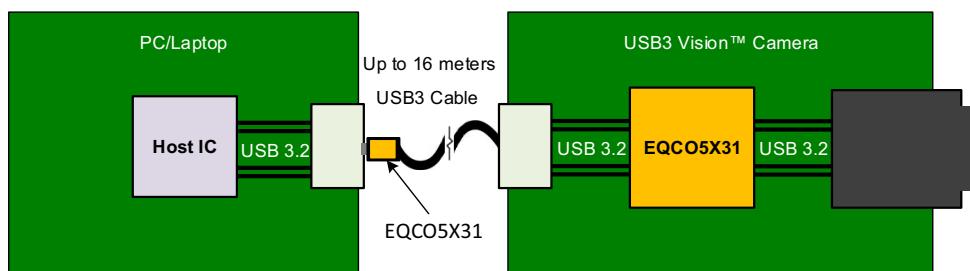

### 5.1.3 LONGER CABLES FOR USB3 VISION™

USB3 Vision™ is an interface standard for industrial cameras. It describes a specification on top of the USB standard, with a particular focus on supporting high-performance cameras based on USB 3.0. An example use-case for USB3 Vision™ shown in [Figure 5-9](#), illustrates how the EQCO5X31 can be integrated into the camera to provide a superior differentiated product.

**FIGURE 5-9: EXTENDING FOR USB3 VISION™ APPLICATIONS**

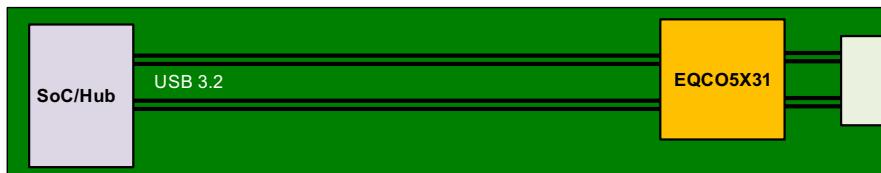

### 5.1.4 RESTORING PCB LOSSES

Sometimes the USB controller/SoC cannot be physically near the USB connector on the PCB or is located on a separate board entirely. In these cases the EQCO5X31 can be located near the USB connector, restoring the signal integrity lost through the PCB traces/connector. Please see [Section 5.2](#) for more information on cable lengths. An example use case is shown below.

**FIGURE 5-10: EXTENDING EXTRA LONG PCB TRACES AND/OR BOARD-TO-BOARD/BACKPLANE CONNECTIONS**

## 5.2 Cable Information

### 5.2.1 CABLE LENGTH

Because the EQCO5X31 is intended to work with lossier channels than defined in the [USB 3.2 Specifications \[1\]](#), it was designed to provide a minimum of 24 dB of compensation at the Nyquist frequency (2.5 GHz) using its *EyeOpen*™ technology. That figure is a conservative minimum taking account factors such as temperature, cable aging and industrial environmental noise. Using that figure then, a maximum cable length can be determined that should work in an industrial environment. To determine the maximum cable length when an EQCO5X31 device is present at both ends of the cable, the following equations should be used:

1. IL (Insertion Loss)  $\leq 24$  dB

2. SNR (Signal to Noise Ratio)  $\geq 16$  dB, where  $\text{SNR} = \text{NEXT} (\text{Near End Crosstalk}) - \text{IL}$

For example, a cable with an IL of 2 dB/m can achieve up to 12 meters length. At that length, the cable + connector with a NEXT of 40 dB or greater would be required to achieve the SNR. In the same way, PCB maximum trace lengths can be calculated by knowing the IL of the trace.

Insertion Loss is largely a matter of the cables AWG rating, long cables would need to have smaller AWG (thicker wire) ratings to achieve lower IL. NEXT is largely a matter of the quality of the cable and connector, the wire arrangement, wire shielding and wire attachment method.

### 5.2.2 OTHER CABLE TYPES

Although the EQCO5X31 was primarily designed for  $90\Omega$  or  $100\Omega$  STP (Shielded Twisted Pair), it has also been designed to work with  $50\Omega$  coaxial cable, and has been tested to a limited extent.

To obtain further application information pertaining to other cable types and required circuit changes, please contact Microchip support via the Microchip support portal.

## 5.3 Guidelines for Design and Layout

### 5.3.1 GENERAL RULES

Below are the general rules that should be used in the schematic and PCB layout. These rules have been implemented in our reference designs. It is best to follow these rules by copying our reference designs as closely as possible. In addition, customer designs should be reviewed by Microchip before building product. This is done through our EQCOcheck process. We highly encourage our customers to send in their designs for review as significant issues are often found during this review. Please contact Microchip support via the Microchip support portal.

1. The 1.2V supply for the EQCO5X31 should be supplied by a low ripple LDO regulator with a high PSRR at the switching frequencies that might be present at its input. Please see our reference design for suggested part selection. For boards with multiple EQCO5X31's, each should have its own regulator.

2. Place and route decoupling capacitors for VCCA and VCCB power pins using low inductance techniques, such as short and wide traces and multiple vias to planes. Microchip recommends placing the decoupling capacitors on the opposite side of the board from the EQCO5X31 so that the ground side of the capacitors can attach directly to a center GND pad via, as is done on our reference designs.

3. Differential PCB traces should be as short as possible and routed as  $90\Omega$  or  $100\Omega$  (as preferred). The two traces of the pair should be as symmetrical as possible to each other (to reduce mode conversions) and should be routed next to a continuous plane. Copper features such as vias and copper co-planar pours should be kept away from the traces by a distance of 3-4x the trace width. Crosstalk between the RX and TX pairs should be reduced as much as possible, this implies keeping these trace routes as far away from each other as practical. Other crosstalk mitigation techniques such as using different non-adjacent layers and orthogonal routing can also be used.

### 5.3.2 USB DE-EMPHASIS

The [USB 3.2 Specifications \[1\]](#) allows transmit de-emphasis to be used as a method of equalization to compensate for long cable losses. The EQCO5X31 receive equalizer operates equally well when receiving signals that were launched with or without de-emphasis. The EQCO5X31 does not apply de-emphasis on its transmit outputs. If transmit de-empha-

sis is desired, it is something that can be easily implemented with a few external passive components. Microchip can provide more details on an external circuit to implement transmit de-emphasis. Please contact Microchip support via the Microchip support portal.

### 5.3.3 ESD GUIDELINES

The EQCO5X31 has extremely strong and robust ESD protection built into the device, so it is generally not required to add external ESD protection in most applications. If the application must be further hardened, external ESD diodes can be added on each differential pair signal located nearest the USB connector. Microchip has the following guidelines with regards to the ESD diode selection:

- a. Low capacitance (< 1 pF or preferably < 0.5 pF)

- b. TLP voltages in both directions less than 9V at a TLP current of 15A,

- c. A dual diode part (or quad) in a single package is better than individual diodes for best matching

- d. The diodes should be placed in-line with the differential routes, so stubs are reduced as much as possible.

## 5.4 *MarginLink™* Signal Integrity Pins (TSI, LOM and TSC)

USB links typically operate with a very low Bit-Error-Rate (BER). Unfortunately, there is usually no mechanism to determine if there is sufficient operational BER system margin. It is possible that the BER might be low but near a cliff that with just a small additional impairment might result in a much higher BER. This impairment, resulting in increased jitter and eye-opening degradations, can be caused by many factors including but not limited to long cables, damaged cables/ connectors and poor PCB layout.

The Test Signal Integrity (**TSI**) pin and Low Margin (**LOM**) pin of the EQCO5X31 are therefore introduced to allow run-time evaluation of the integrity of the whole signal path. When an analog voltage is applied to the **TSI** pin, a controlled level of signal impairment (both timing and amplitude) is intentionally added to the signal just before the reclocker (CDR). Hence, the high frequency jitter margin of the EQCO5X31 will be reduced for a given BER. In case too little margin is present, this will be noticeable by a substantial rise in bit errors. The **LOM** pin output can then be used to detect these bit errors.

The **TSI** pin is an analog input with an internal pull-down to ground of  $20\text{ k}\Omega$ . This allows an external resistor to form a voltage divider with the internal resistor and thus generate the desired voltage and impairment level. From 300 mV ( $\pm 100\text{ mV}$ ) onwards, signal impairment is added. At the power supply voltage (1.2V) there is 100% of the maximum allowed impairment, likewise at 50% of the power supply voltage, there is 50% of maximum allowed impairment. For typical applications it is advised to test with 50% level, and for safety critical applications 100% is advised. For example, the jumper configuration as shown in [Figure 5-11](#) could be added to a board design. In this way three different impairment values can be configured manually.

The **LOM** pin is a digital output that indicates when a bit error is detected. Although **LOM** is usually used in conjunction with **TSI**, the function is independent of **TSI**, which means it can be used as a general error indicator. The **LOM** output is normally low but when a bit error is detected, it will output a high (1.2V) pulse. Note that if multiple errors occur during the high pulse width, only one error will be reported.

There are several potential ways to monitor the **LOM** pin output including but not limited to:

1. Counting: A digital counter would count on each rising edge seen. A pass/fail test can be implemented by counting total errors per unit of time. FPGA's and most microcontrollers have counter functions fast enough for this purpose.

2. Integration: A capacitor could be used to integrate the pulses and provide an analog voltage that could be used as input to an ADC or comparator. A pass/fail test can be made by measuring the analog voltage does not exceed a defined threshold.

3. Pulse stretching: This might be done to provide a longer pulse that would drive a visual indicator such as an LED. The LED flashing on would indicate an error occurred, or multiple errors could be roughly measured via the intensity of the LED.

FIGURE 5-11: EQCO5X31 - TSI TEST JUMPER

- No jumper installed = no impairment added

- Jumper 2-3 would provide approximately 50% of maximum allowed impairment

- Jumper 1-2 would provide approximately 100% of maximum allowed impairment

The connection to TSI pin should be short and kept away from other signals.

The **TSC** pin is a digital input that selects the channel (A or B, see [Figure 1-2](#)) that **TSI** and **LOM** are associated with, High = Chan A, Low = Chan B. For example, if **TSC** is high, channel A will be selected so that **TSI** will impair the channel A receiver, and **LOM** will indicate errors on Channel A receiver. Conversely, if **TSC** is low, **TSI** and **LOM** are associated with Channel B. For most customers, **TSI** and **LOM** should be associated with channel A, because that is the cable side channel input, and it is usually more important to check the margin of the cable side connections.

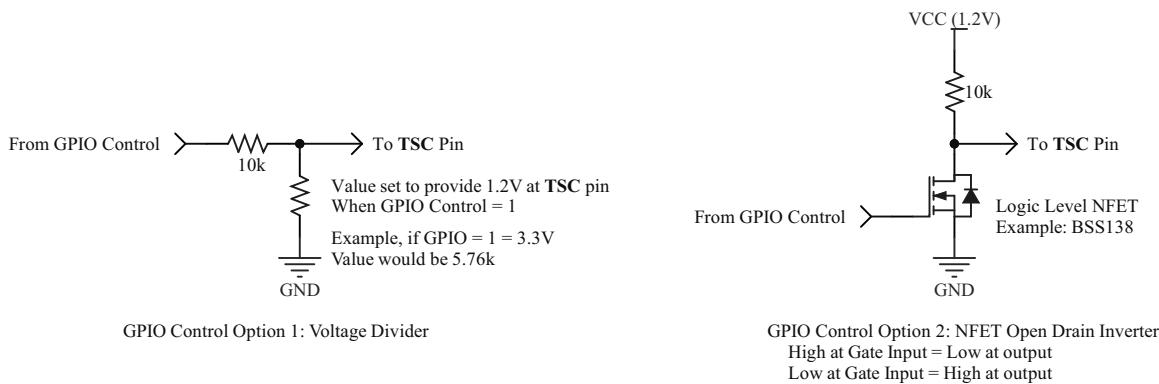

The **TSC** input can be set high or low using the following methods.

1. Resistor Pullup or Pulldown. To tie the **TSC** pin low, a direct tie to ground or a  $0\Omega$  resistor to ground is recommended. To tie the **TSC** pin high, a  $10\text{ k}\Omega$  resistor to **VCC** is recommended. Do not tie the **TSC** pin directly to **VCC** or leave floating.

2. Controlled from GPIO. See [Figure 5-12](#) for two options to set or clear the **TSC** pin from a GPIO.

FIGURE 5-12: EQCO5X31 - SET OR CLEAR THE TSC PIN FROM A GPIO

## 5.5 TEST0 Pin and Compliance Mode

Link partners (Host or Device) are required to support USB 3.2 Compliance Mode [\[4\]](#). This is a special test mode used to generate test patterns that would enable physical measurements to be made at the transmitter (such as scope measurements, eye diagrams, etc.). As the EQCO5X31 is not a Host or Device, it does not by default support Compliance mode, nor does it normally pass these special test patterns through the device. However, it is possible to enable the EQCO5X31 to pass through and re-drive CP0 and CP1 patterns needed for electrical compliance testing by programming the EQCO5X31 through its **TEST0** pin. This is detailed in [AN1686: EQCO5X31 Compliance with USB 3.2 Gen 1 Application Note \[5\]](#).

# EQCO5X31

## 5.6 Data Pins (SDxOp/SDxOn and SDxIp/SDxIn)

The connection to these pins should follow the general rules in [Section 5.3.1](#). The transmit outputs (**SDxOp/SDxOn**) must include DC blocking capacitors with a value between 75-265 nF. Microchip recommends 100 nF / 50V as these can be readily obtained in 0402 (1005 metric) size. The USB specifications do not require capacitors on the receiver inputs (**SDxIp/SDxIn**), but for reasons of industrial safety and protection, it is recommended. If receiver capacitors are used, the value must be between 297-363 nF. Microchip recommends 330 nF / 50V..

## 5.7 Power Connectivity

[Figure 5-13](#) illustrates the power configuration for the EQCO5X31 with recommended filtering and decoupling. The EQCO5X31 requires only a single 1.2V power supply, which must supply both VCC pins (VCCA and VCCB must be connected together). It is important to power each EQCO5X31 from a low ripple LDO regulator with a high PSRR at the switching frequencies that might be present at its input. Ripple on the power supply adversely affects CDR operation, signal integrity, and cable distance that can be supported.

**FIGURE 5-13: POWER CONNECTIVITY**

## 5.8 Microchip EQCO5X31 Reference Designs

Microchip offers the following reference designs and evaluation boards for the EQCO5X31.

1. EQCO5X31 Evaluation Board, AIS20001

2. EV40G35A EVB-EQCO5X31-TYPE-C EXTENDER

3. EV23B43A EVB-EQCO5X31-TYPE-C REPEATER

Design files and evaluation boards are available upon request. Please contact Microchip support via the Microchip support portal.

It is highly recommended to start with a Microchip reference design before beginning a new project. Customer designs should be reviewed by Microchip before building product. This is done through our EQCOcheck process. We highly encourage our customers to send in their designs for review. Significant issues are often found during this review. Please contact Microchip support via the Microchip support portal.

## 6.0 PACKAGING INFORMATION

### 6.1 Package Marking

FIGURE 6-1: EQCO5X31 TOP MARKING

### 6.2 Package Thermal Characteristics

TABLE 6-1: EQCO5X31 20 LEAD PLASTIC QUAD FLAT, NO LEAD PACKAGE (6N)

| Parameter                   | Symbol        | Value | Unit |

|-----------------------------|---------------|-------|------|

| Typical Junction to Ambient | $\Theta_{JA}$ | 43.9  | °C/W |

| Typical Junction to Case    | $\Theta_{JC}$ | 28.5  | °C/W |

| Typical Junction to Board   | $\Theta_{JB}$ | 20.43 | °C/W |

# EQCO5X31

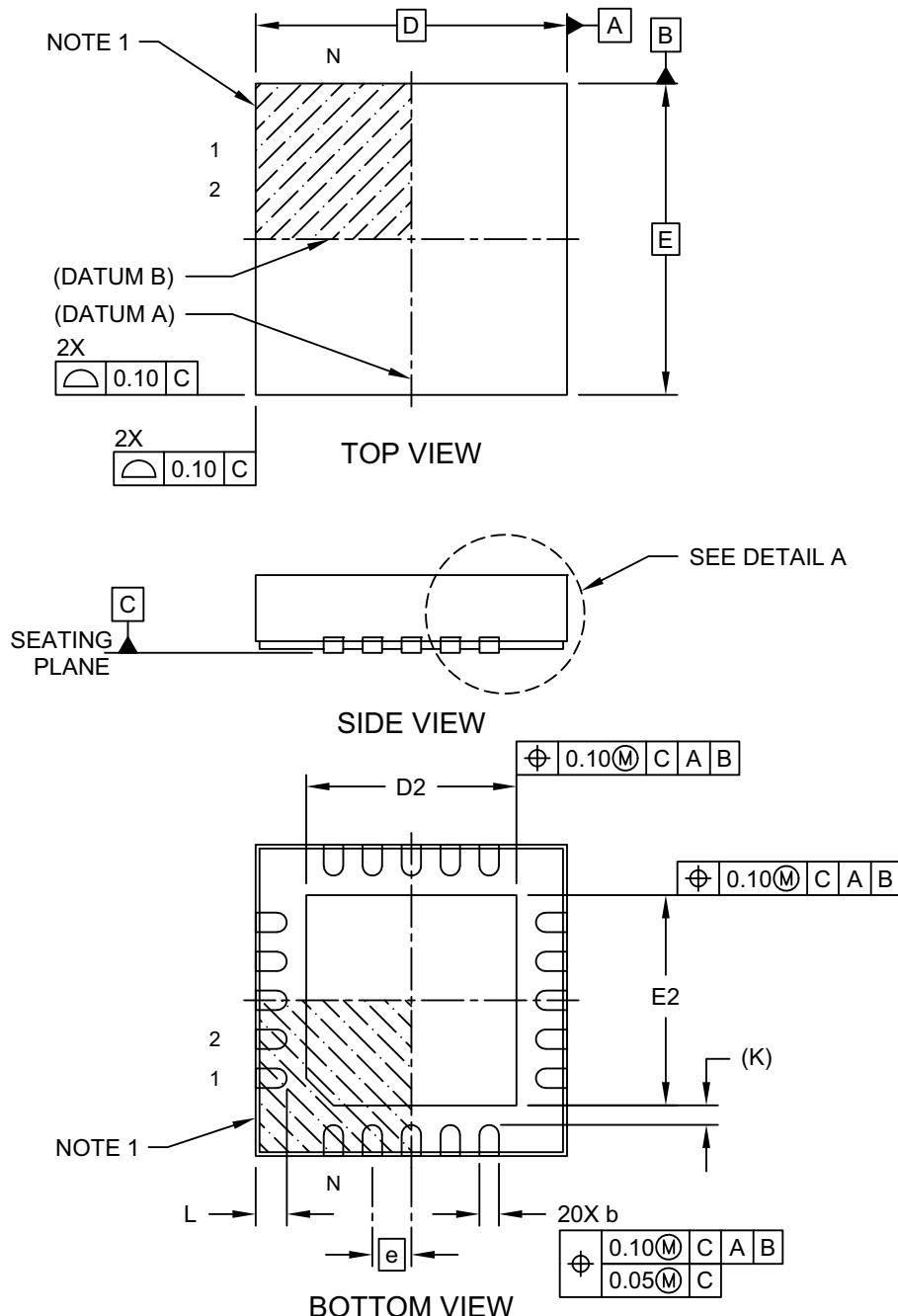

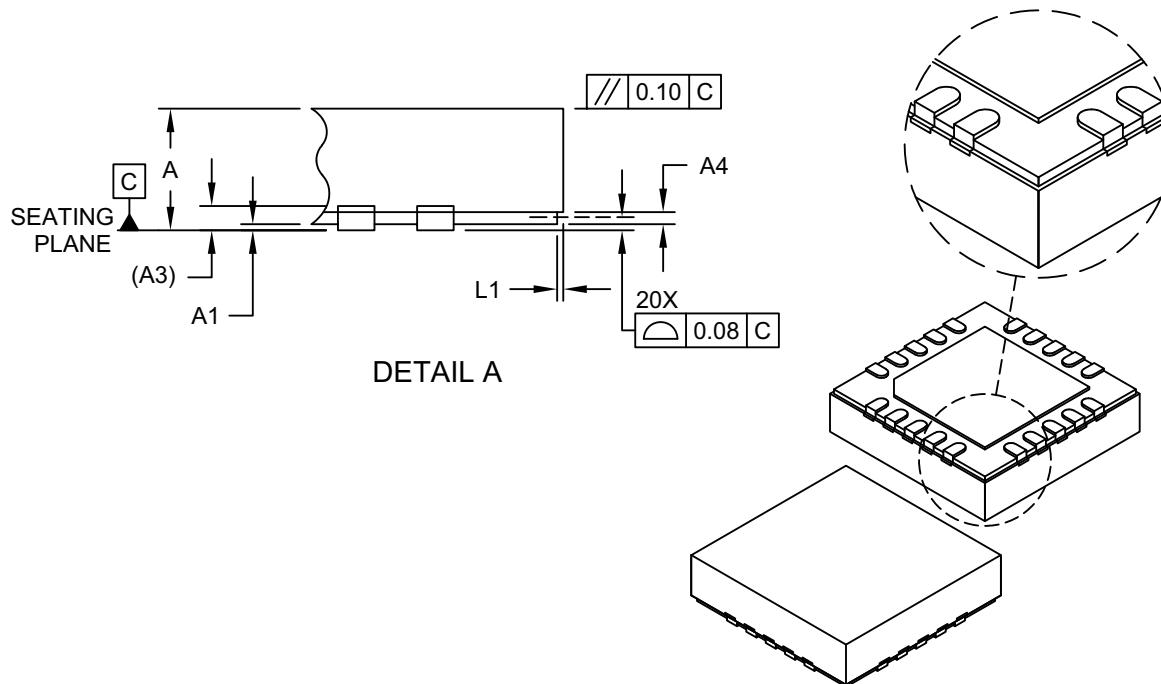

## 6.3 Package Drawings

### 20-Lead Plastic Quad Flat, No Lead Package (6N,6NX) - 4x4x1.0 mm Body [VQFN] Wettable Flanks (Stepped), 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at <http://www.microchip.com/packaging>

Microchip Technology Drawing C04-402E Sheet 1 of 2

**20-Lead Plastic Quad Flat, No Lead Package (6N,6NX) - 4x4x1.0 mm Body [VQFN]

Wettable Flanks (Stepped), 0.40 mm Terminal Length**

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at <http://www.microchip.com/packaging>

| Dimension               | Limits | Units |       |       | MILLIMETERS |     |     |

|-------------------------|--------|-------|-------|-------|-------------|-----|-----|

|                         |        | MIN   | NOM   | MAX   | MIN         | NOM | MAX |

| Number of Terminals     | N      |       | 20    |       |             |     |     |

| Pitch                   | e      |       | 0.50  | BSC   |             |     |     |

| Overall Height          | A      | 0.80  | 0.90  | 1.00  |             |     |     |

| Standoff                | A1     | 0.00  | 0.02  | 0.05  |             |     |     |

| Terminal Thickness      | A3     |       | 0.20  | REF   |             |     |     |

| Step Height             | A4     | 0.10  | —     | 0.19  |             |     |     |

| Overall Width           | E      |       | 4.00  | BSC   |             |     |     |

| Exposed Pad Width       | E2     | 2.60  | 2.70  | 2.80  |             |     |     |

| Overall Length          | D      |       | 4.00  | BSC   |             |     |     |

| Exposed Pad Length      | D2     | 2.60  | 2.70  | 2.80  |             |     |     |

| Terminal Width          | b      | 0.20  | 0.25  | 0.30  |             |     |     |

| Terminal Length         | L      | 0.30  | 0.40  | 0.50  |             |     |     |

| Step Length             | L1     | 0.035 | 0.060 | 0.085 |             |     |     |

| Terminal-to-Exposed Pad | K      |       | 0.25  | REF   |             |     |     |

**Notes:**

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

# EQCO5X31

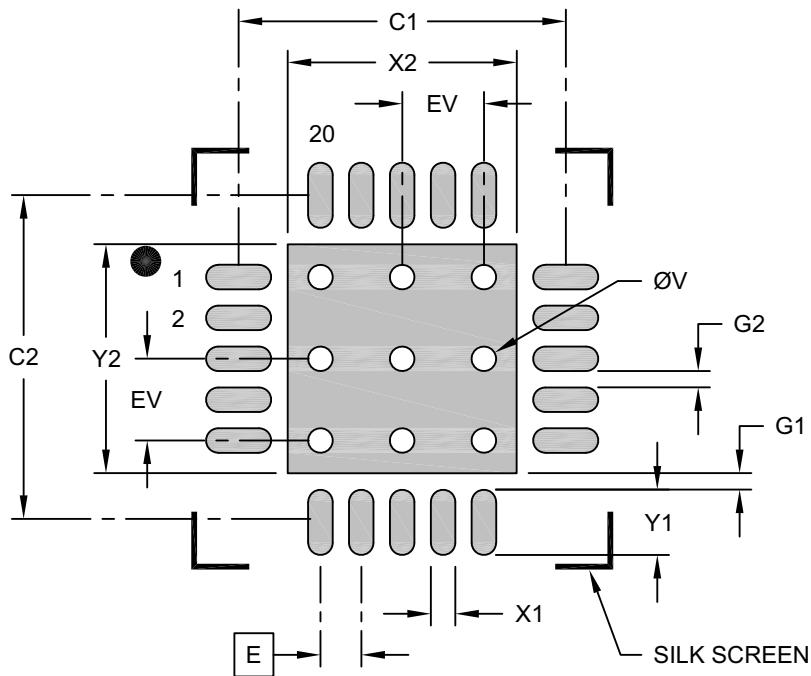

## 20-Lead Plastic Quad Flat, No Lead Package (6N,6NX) - 4x4x1.0 mm Body [VQFN] Wettable Flanks (Stepped), 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at <http://www.microchip.com/packaging>

### RECOMMENDED LAND PATTERN

| Dimension Limits                 | Units | MILLIMETERS |          |      |

|----------------------------------|-------|-------------|----------|------|

|                                  |       | MIN         | NOM      | MAX  |

| Contact Pitch                    | E     |             | 0.50 BSC |      |

| Optional Center Pad Width        | X2    |             |          | 2.80 |

| Optional Center Pad Length       | Y2    |             |          | 2.80 |

| Contact Pad Spacing              | C1    |             | 4.00     |      |

| Contact Pad Spacing              | C2    |             | 4.00     |      |

| Contact Pad Width (X20)          | X1    |             |          | 0.30 |

| Contact Pad Length (X20)         | Y1    |             |          | 0.80 |

| Contact Pad to Center Pad (X20)  | G1    | 0.25        |          |      |

| Contact Pad to Contact Pad (X16) | G2    | 0.20        |          |      |

| Thermal Via Diameter             | V     |             | 0.30     |      |

| Thermal Via Pitch                | EV    |             | 1.00     |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2402E

© 2023 Microchip Technology Inc.

## APPENDIX A: REFERENCES

Documents listed below and referenced within this publication are current as of the release of this publication and may have been reissued with more current information. To obtain the latest releases of Microchip documentation please visit the Microchip website. Please note, some Microchip documentation may require approval. Contact information can be found at [www.microchip.com](http://www.microchip.com).

All non-Microchip documentation should be retrieved from the applicable website locations listed below. Microchip is not responsible for the update, maintenance or distribution of non-Microchip documentation.

Because the Internet is a constantly changing environment, all Internet links mentioned below and throughout this document are subject to change without notice.

[1] USB 3.2 Specifications

<https://www.usb.org/>

[2] Patents: US7894515B2 & EP2182688B1

[3] Patents & Patents Pending: US10277340 (B1)

[4] Universal Serial Bus 3.2 Specification. Revision 1.1 June 2022 - Section 7.5.5

[5] AN1686: EQCO5X31 Compliance with USB 3.2 Gen 1 Application Note

## APPENDIX B: REVISION HISTORY

### B.1 Current Revision

#### DS60001668E (July 2024)

- Updated section 2.0 Pinout

- Added section 5.5 TEST0 Pin and Compliance Mode

### B.2 Previous Revision

#### DS60001668D (August 2023)

- Updated section 6.3 Package Drawings

#### DS60001668C (March 2023)

- Updated section 2.0 Pinout

- Updated section 4.2 Electrical Characteristics

- Updated section 5.3.3 ESD guidelines

- Updated section 5.7 Microchip EQCO5X31 Reference Designs

#### DS60001668B (December 2021)

- Updated entire document for new pins TSC, TEST2 and TEST3

- Updated Table 4-2 to add digital pins LOM, TSC and Analog pin TSI to electrical table

- Updated section 5.1 Usage Diagrams, added USB2 extension Figure and USB3 Vision™ Figure

- Updated section 5.3.2 regarding de-emphasis

- Added section 5.3.3 ESD Guidelines.

#### DS60001668A (December 2020)

- Initial document release.

# EQCO5X31

---

## THE MICROCHIP WEBSITE

Microchip provides online support via our website at <https://www.microchip.com>. This website is used to make files and information easily available to customers. Some of the available content includes:

- **Product Support** – Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, the latest software releases and archived software

- **General Technical Support** – Frequently Asked Questions (FAQs), technical support requests, online discussion groups and a Microchip design partner program member listing

- **Business of Microchip** – Product selector and ordering guides, the latest Microchip press releases, a listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Embedded Solutions Engineer (ESE)

- Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

**Technical support is available through the website at:**

<https://www.microchip.com/support>

## PRODUCT CHANGE NOTIFICATION

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notifications whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to <https://www.microchip.com/pcn> and follow the registration instructions.

## ORDERING INFORMATION

### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office

| <u>PART NO.</u>              | <u>R</u>         | <u>P</u>       | <u>G</u>                                   | <u>M</u>       |

|------------------------------|------------------|----------------|--------------------------------------------|----------------|

| Device                       | Silicon Revision | Package Option | Grade                                      | MCHP Package # |

| Device                       | EQCO5X31         |                |                                            |                |

| Silicon Revision             | <b>R</b>         | rr             | = Designates Silicon Revision (example C0) |                |

| Packing Option               | <b>P</b>         | T              | = Tape and Reel                            |                |

|                              |                  | Blank          | = Tray                                     |                |

| Grade                        | <b>G</b>         | I              | = Industrial                               |                |

| MCHP Internal Package Number | <b>M</b>         | 6NX            | = QFN Package                              |                |

**ORDERING INFORMATION**

- a. EQCO5X31rr-I/6NX

- b. EQCO5X31rrT-I/6NX

# EQCO5X31

---

---

## NOTES:

**Note the following details of the code protection feature on Microchip products:**

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is "unbreakable" Code protection is constantly evolving. Microchip is committed to continuously improving the code protection features of our products.

---

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <https://www.microchip.com/en-us/support/design-help/client-support-services>.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

**Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-B4, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, TimeCesium, TimeHub, TimePictra, TimeProvider, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, EyeOpen, GridTime, IdealBridge, iGAT, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, MarginLink, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mSiC, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, Power MOS IV, Power MOS 7, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQL, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, Turing, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2024 Microchip Technology Inc. and its subsidiaries

All Rights Reserved.

ISBN: 978-1-6683-4915-1

For information regarding Microchip's Quality Management Systems, please visit [www.microchip.com/quality](https://www.microchip.com/quality).

**MICROCHIP**

---

## Worldwide Sales and Service

---

### AMERICAS

**Corporate Office**

2355 West Chandler Blvd.

Chandler, AZ 85224-6199

Tel: 480-792-7200

Fax: 480-792-7277

Technical Support:

<http://www.microchip.com/support>

Web Address:

[www.microchip.com](http://www.microchip.com)

**Atlanta**

Duluth, GA

Tel: 678-957-9614

Fax: 678-957-1455

**Austin, TX**

Tel: 512-257-3370

**Boston**

Westborough, MA

Tel: 774-760-0087

Fax: 774-760-0088

**Chicago**

Itasca, IL

Tel: 630-285-0071

Fax: 630-285-0075

**Dallas**

Addison, TX

Tel: 972-818-7423

Fax: 972-818-2924

**Detroit**

Novi, MI

Tel: 248-848-4000

**Houston, TX**

Tel: 281-894-5983

**Indianapolis**

Noblesville, IN

Tel: 317-773-8323

Fax: 317-773-5453

Tel: 317-536-2380

**Los Angeles**

Mission Viejo, CA

Tel: 949-462-9523

Fax: 949-462-9608

Tel: 951-273-7800

**Raleigh, NC**

Tel: 919-844-7510

**New York, NY**

Tel: 631-435-6000

**San Jose, CA**

Tel: 408-735-9110

Tel: 408-436-4270

**Canada - Toronto**

Tel: 905-695-1980

Fax: 905-695-2078

### ASIA/PACIFIC

**Australia - Sydney**

Tel: 61-2-9868-6733

**China - Beijing**

Tel: 86-10-8569-7000

**China - Chengdu**

Tel: 86-28-8665-5511

**China - Chongqing**

Tel: 86-23-8980-9588

**China - Dongguan**

Tel: 86-769-8702-9880

**China - Guangzhou**

Tel: 86-20-8755-8029

**China - Hangzhou**

Tel: 86-571-8792-8115

**China - Hong Kong SAR**

Tel: 852-2943-5100

**China - Nanjing**

Tel: 86-25-8473-2460

**China - Qingdao**

Tel: 86-532-8502-7355

**China - Shanghai**

Tel: 86-21-3326-8000

**China - Shenyang**

Tel: 86-24-2334-2829

**China - Shenzhen**

Tel: 86-755-8864-2200

**China - Suzhou**

Tel: 86-186-6233-1526

**China - Wuhan**

Tel: 86-27-5980-5300

**China - Xian**

Tel: 86-29-8833-7252

**China - Xiamen**

Tel: 86-592-2388138

**China - Zhuhai**

Tel: 86-756-3210040

### ASIA/PACIFIC

**India - Bangalore**

Tel: 91-80-3090-4444

**India - New Delhi**

Tel: 91-11-4160-8631

**India - Pune**

Tel: 91-20-4121-0141

**Japan - Osaka**

Tel: 81-6-6152-7160

**Japan - Tokyo**

Tel: 81-3-6880-3770

**Korea - Daegu**

Tel: 82-53-744-4301

**Korea - Seoul**

Tel: 82-2-554-7200

**Malaysia - Kuala Lumpur**

Tel: 60-3-7651-7906

**Malaysia - Penang**

Tel: 60-4-227-8870

**Philippines - Manila**

Tel: 63-2-634-9065

**Singapore**

Tel: 65-6334-8870

**Taiwan - Hsin Chu**

Tel: 886-3-577-8366

**Taiwan - Kaohsiung**

Tel: 886-7-213-7830

**Taiwan - Taipei**

Tel: 886-2-2508-8600

**Thailand - Bangkok**

Tel: 66-2-694-1351

**Vietnam - Ho Chi Minh**

Tel: 84-28-5448-2100

### EUROPE

**Austria - Wels**

Tel: 43-7242-2244-39

Fax: 43-7242-2244-393

**Denmark - Copenhagen**

Tel: 45-4485-5910

Fax: 45-4485-2829

**Finland - Espoo**

Tel: 358-9-4520-820

**France - Paris**

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

**Germany - Garching**

Tel: 49-8931-9700

**Germany - Haan**

Tel: 49-2129-3766400

**Germany - Heilbronn**

Tel: 49-7131-72400

**Germany - Karlsruhe**

Tel: 49-721-625370

**Germany - Munich**

Tel: 49-89-627-144-0

Fax: 49-89-627-144-44

**Germany - Rosenheim**

Tel: 49-8031-354-560

**Israel - Hod Hasharon**

Tel: 972-9-775-5100

**Italy - Milan**

Tel: 39-031-742611

Fax: 39-0331-466781

**Italy - Padova**

Tel: 39-049-7625286

**Netherlands - Drunen**

Tel: 31-416-690399

Fax: 31-416-690340

**Norway - Trondheim**

Tel: 47-7288-4388

**Poland - Warsaw**

Tel: 48-22-3325737

**Romania - Bucharest**

Tel: 40-21-407-87-50

**Spain - Madrid**

Tel: 34-91-708-08-90

Fax: 34-91-708-08-91

**Sweden - Gothenberg**

Tel: 46-31-704-60-40

**Sweden - Stockholm**

Tel: 46-8-5090-4654

**UK - Wokingham**

Tel: 44-118-921-5800

Fax: 44-118-921-5820