## USB 48V EPR Port Protector for CC & SBU

### Features

- CC Switches: 1.25A, 300mΩ, 50pF, 180MHz

- ▶ Automatic 5.1kΩ dead battery pull-down

- SBU Switches: 4.5Ω, 9pF, 900MHz

- ▶ Thunderbolt™ Compatible

- USB PD3.0 SPR & PD3.1 48V EPR Compatible

- ▶ 63V<sub>DC</sub> Short-to-VBUS on CC1/2, SBU1/2

- ▶ 1x/0.42x VBUS Level Shift for 48V → 20V

- ▶ VBUS EPR Blocking via external NFET

- Overvoltage Protection

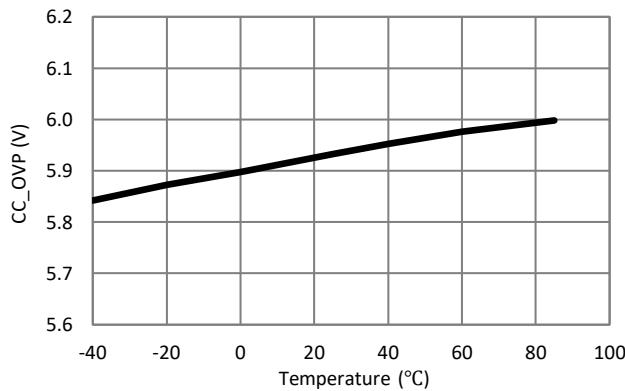

- ▶ CC1/2 OVP = 5.9V

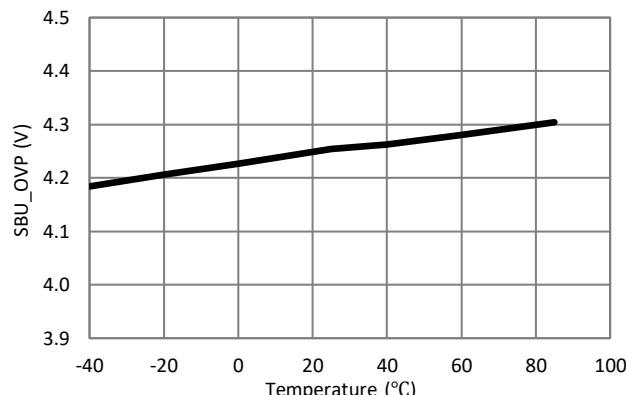

- ▶ SBU1/2 OVP = 4.2V

- ▶ Fast 60ns Response Time

- IEC61000-4-5 Surge Protection

- ▶ +90V Surge Tolerance on CC1/2

- ▶ +90V Surge Tolerance on SBU1/2

- IEC61000-4-2 ESD Protection

- ▶ ±15kV air gap on CC1/2, SBU1/2

- ▶ ±8kV contact on CC1/2, SBU1/2

- ▶ ±2kV HBM on all pins (JEDEC JS-001-2017)

- 2.7V to 4.5V Operating Supply Voltage Range

- -40°C to 85°C Operating Temperature Range

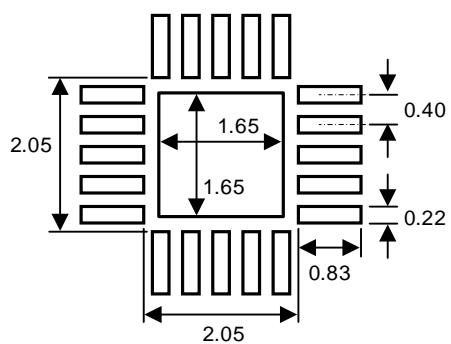

- 20-pin WQFN 3mmx3mm (0.4mm pitch)

- ▶ Pin-to-Pin Drop-In with TPD4S480

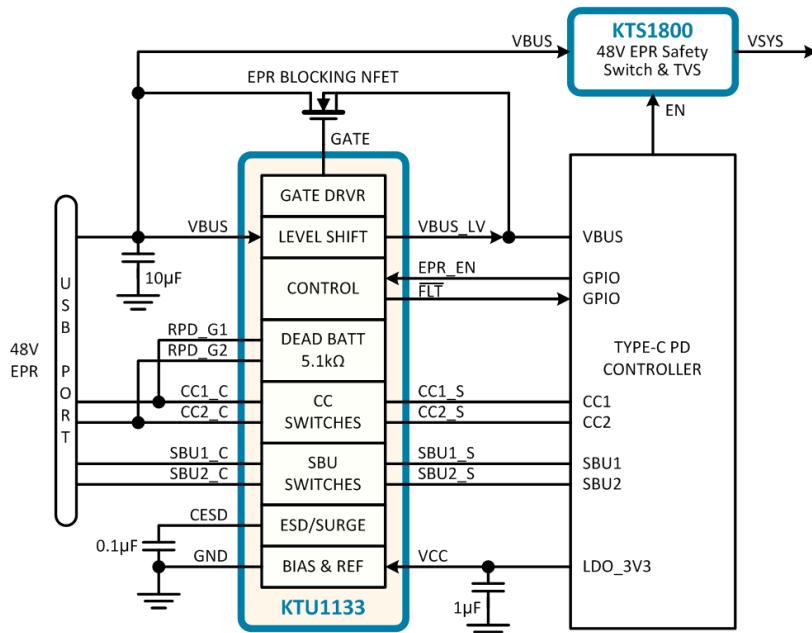

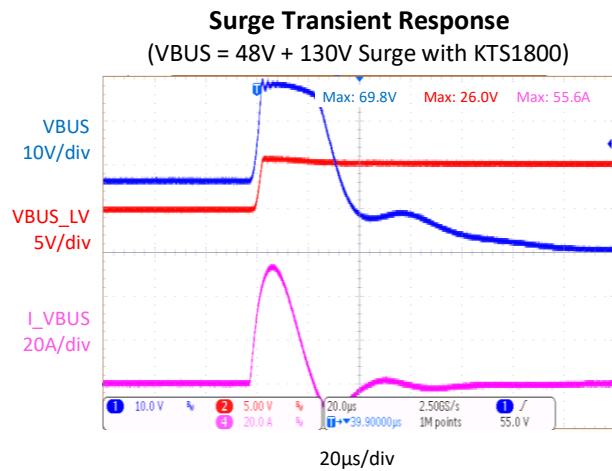

### Typical Application

### Brief Description

The KTU1133 provides safety management for USB PD3.1 48V EPR ports with comprehensive protection of the CC and SBU data lines. All four data lines include 63V<sub>DC</sub> withstand for short-to-VBUS fault events in the connector and integrated transient voltage suppression (TVS) for IEC surge protection and IEC level-4 ESD protection. Fast over-voltage protection (OVP) isolates downstream system circuits during fault events.

The integrated VBUS level shift circuit and external blocking NFET gate driver allow SPR-rated PD controllers to safely operate in EPR systems.

The CC1/2 switches have low on-resistance for passing V<sub>CONN</sub> power up to 1.25A. During dead battery conditions, optional-use internal 5.1kΩ resistors automatically pull down on CC1/2 to ensure that the up-stream source provides 5V on VBUS.

The KTU1133 is packaged in RoHS and Green compliant 20-pin 3mm x 3mm WQFN package.

### Applications

- Desktop PC, Workstation & Gaming Notebooks

- Monitors, Docking Stations, Conferencing Systems

## Ordering Information

| Part Number    | Marking <sup>1</sup> | Operating Temperature | Package   |

|----------------|----------------------|-----------------------|-----------|

| KTU1133EUAJ-TD | UWYWZ<br>aaaaaaaa    | -40°C to +85°C        | WQFN33-20 |

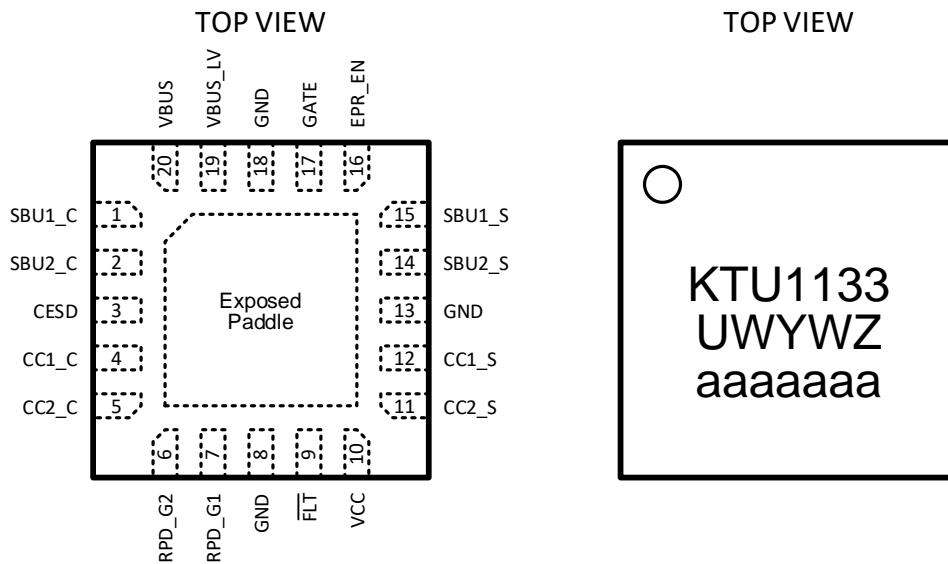

## Pinout Diagram

WQFN33-20

20-pin 3mm x 3mm x 0.75mm WQFN Package, 0.4mm pitch

### Top Mark

UW = Device ID, YW = Date Code, Z = Serial Number

aaaaaaaa = Assembly Lot Tracking Number

1. UW = Device ID, YW = Date Code, Z = Serial Number, aaaaaaaaa = Assembly Lot Tracking Number.

## Pin Descriptions

| Pin #     | Name    | Function                                                                                                                                                                    |

|-----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12        | CC1_S   | System side of CC1 switch                                                                                                                                                   |

| 11        | CC2_S   | System side of CC2 switch                                                                                                                                                   |

| 4         | CC1_C   | Connector side of CC1 switch                                                                                                                                                |

| 5         | CC2_C   | Connector side of CC2 switch                                                                                                                                                |

| 1         | SBU1_C  | Connector side of SBU1 switch – alternatively, use to protect the USB2.0 D+/- path.                                                                                         |

| 2         | SBU2_C  | Connector side of SBU2 switch – alternatively, use to protect the USB2.0 D+/- path.                                                                                         |

| 15        | SBU1_S  | System side of SBU1 switch – alternatively, use to protect the USB2.0 D+/- path.                                                                                            |

| 14        | SBU2_S  | System side of SBU2 switch – alternatively, use to protect the USB2.0 D+/- path.                                                                                            |

| 7         | RPD_G1  | Dead battery pull-down resistor – connect to CC1_C if needed; connect to GND if not required.                                                                               |

| 6         | RPD_G2  | Dead battery pull-down resistor – connect to CC2_C if needed; connect to GND if not required.                                                                               |

| 9         | FLT     | Active-low, open-drain fault flag output to alert system to an OVP fault condition – connect to GND if not required.                                                        |

| 8, 13, 18 | GND     | Ground – connect to PCB ground plane.                                                                                                                                       |

| 3         | CESD    | Capacitor connection for ESD/surge protection – connect a 0.1µF capacitor from CESD to GND.                                                                                 |

| 10        | VCC     | Device supply input – connect to a 2.5V to 4.5V power source.                                                                                                               |

| 20        | VBUS    | VBUS level shifter input – connect to VBUS on the connector.                                                                                                                |

| 19        | VBUS_LV | VBUS level shifter output – 1x pass-through output is enabled in SPR mode; 0.42x divider output is enabled in EPR mode.                                                     |

| 16        | EPR_EN  | EPR mode enable input – logic 0 = SPR mode; logic 1 = EPR mode.                                                                                                             |

| 17        | GATE    | Gate drive output to optional VBUS NFET – gate drive is enabled in SPR mode; gate drive is disabled in EPR mode to block high VBUS voltage from reaching the PD controller. |

| EP        | EP      | Exposed paddle – connect to GND pins and to PCB ground plane for thermal conduction.                                                                                        |

## Absolute Maximum Ratings<sup>2</sup>

| Symbol                                               | Description                                                           | Value       | Units |

|------------------------------------------------------|-----------------------------------------------------------------------|-------------|-------|

| $V_{CC}$                                             | $V_{CC}$ to GND                                                       | -0.3 to 5   | V     |

| $V_{LOGIC}$                                          | EPR_EN to GND                                                         | -0.3 to 3.6 | V     |

|                                                      | FLT to GND                                                            | -0.3 to 6   |       |

| $V_{BUS}$                                            | VBUS to GND (continuous)                                              | -0.3 to 63  | V     |

|                                                      | VBUS to GND (during IEC61000-4-5 surge event with external TVS)       | -4 to 70    |       |

| $V_{BUS\_LV}$                                        | VBUS_LV to GND (continuous)                                           | -0.3 to 24  | V     |

| $V_{GATE}$                                           | GATE to GND                                                           | -0.3 to 30  | V     |

| $V_{RPD\_G1/2}$<br>$V_{CC1/2\_C}$<br>$V_{SBU1/2\_C}$ | RPD_G1, RPD_G2 to GND<br>CC1_C, CC2_C to GND<br>SBU1_C, SBU2_C to GND | -0.3 to 63  | V     |

| $V_{CESD}$                                           | CESD to GND                                                           | -0.3 to 63  | V     |

| $V_{CC1/2\_S}$<br>$V_{SBU1/2\_S}$                    | CC1_S, CC2_S to GND<br>SBU1_S, SBU2_S to GND                          | -0.3 to 6   | V     |

| $I_{CC1/2}$                                          | CC1_C to CC1_S, CC2_C to CC2_S Continuous Current                     | $\pm 1.25$  | A     |

| $I_{SBU1/2}$                                         | SBU1_C to SBU1_S, SBU2_C to SBU2_S Continuous Current                 | $\pm 100$   | mA    |

| $T_J$                                                | Die Junction Operating Temperature Range                              | -40 to 125  | °C    |

| $T_S$                                                | Storage Temperature Range                                             | -55 to 150  | °C    |

| $T_{LEAD}$                                           | Maximum Soldering Temperature (at leads, 10 sec)                      | 260         | °C    |

## ESD and Surge Ratings<sup>3</sup>

| Symbol         | Description                                                   | Value     | Units |

|----------------|---------------------------------------------------------------|-----------|-------|

| $V_{ESD\_HBM}$ | JEDEC JS-001-2017 Human Body Model (all pins)                 | $\pm 2$   | kV    |

| $V_{ESD\_CDM}$ | JEDEC JESD22-C101 Charged Device Model (all pins)             | $\pm 500$ | V     |

| $V_{ESD\_CD}$  | IEC61000-4-2 Contact Discharge (CC1_C, CC2_C, SBU1_C, SBU2_C) | $\pm 8$   | kV    |

| $V_{ESD\_AGD}$ | IEC61000-4-2 Air Gap Discharge (CC1_C, CC2_C, SBU1_C, SBU2_C) | $\pm 15$  | kV    |

| $V_{SURGE}$    | IEC61000-4-5 Surge (CC1_C, CC2_C)                             | +90       | V     |

|                | IEC61000-4-5 Surge (SBU1_C, SBU2_C)                           | +90       | V     |

## Thermal Capabilities<sup>4</sup>

| Symbol                | Description                                                                               | Value | Units |

|-----------------------|-------------------------------------------------------------------------------------------|-------|-------|

| $\Theta_{JA}$         | Thermal Resistance – Junction to Ambient                                                  | 60    | °C/W  |

| $P_D$                 | Maximum Power Dissipation at $T_A \leq 25^\circ\text{C}$ ( $T_J \leq 125^\circ\text{C}$ ) | 1.67  | W     |

| $\Delta P_D/\Delta T$ | Derating Factor Above $T_A = 25^\circ\text{C}$                                            | -16.7 | mW/°C |

---

2. Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

3. ESD and Surge Ratings conform to JEDEC and IEC industry standards. Some pins may actually have higher performance. Surge ratings apply with chip enabled, disabled, or unpowered, unless otherwise noted.

4. Junction to Ambient thermal resistance is highly dependent on PCB layout. Values are based on thermal properties of the device when soldered to a PCB with thermal vias from the exposed paddle to the ground plane.

## Recommended Operating Conditions<sup>5</sup>

| Symbol          | Description                              | Value         | Units   |

|-----------------|------------------------------------------|---------------|---------|

| $V_{CC}$        | $V_{CC}$ Operating Voltage               | 2.7 to 4.5    | V       |

| $V_{LOGIC}$     | EPR_EN Input Voltage                     | 0 to $V_{CC}$ | V       |

|                 | FLT Output Pull-Up Voltage               | 2.7 to 5.5    |         |

| $V_{BUS}$       | VBUS Input Voltage                       | 0 to 55       | V       |

| $V_{BUS\_LV}$   | VBUS_LV Voltage                          | 0 to 23       | V       |

| $V_{RPD\_G1/2}$ | RPD_G1, RPD_G2 Input Voltage             | 0 to 5.9      | V       |

| $V_{CC1/2\_C}$  | CC1_C, CC2_C Input/Output Voltage        | 0 to 5.9      | V       |

| $V_{SBU1/2\_C}$ | SBU1_C, SBU2_C Input/Output Voltage      | 0 to 4.2      | V       |

| $V_{CC1/2\_S}$  | CC1_S, CC2_S Input/Output Voltage        | 0 to 5.9      | V       |

| $V_{SBU1/2\_S}$ | SBU1_S, SBU2_S Input/Output Voltage      | 0 to 4.2      | V       |

| $I_{CC1/2}$     | CC1_C to CC1_S, CC2_C to CC2_S Current   | $\pm 1.25$    | A       |

| $T_A$           | Ambient Operating Temperature Range      | -40 to 85     | °C      |

| $T_J$           | Die Junction Operating Temperature Range | -40 to 125    | °C      |

| $C_{VCC}$       | $V_{CC}$ External Capacitor              | 1             | $\mu F$ |

|                 |                                          | 6.3           | V       |

| $R_{FLT}$       | FLT External Pull-Up Resistor            | 1.7 to 300    | kΩ      |

| $C_{VBUS}$      | VBUS External Capacitor                  | 1 to 10       | $\mu F$ |

|                 |                                          | 100           | V       |

| $C_{VBUS\_LV}$  | VBUS_LV External Capacitor               | 0.1           | $\mu F$ |

|                 |                                          | 25            | V       |

| $C_{ESD}$       | CESD External Capacitor                  | 0.1           | $\mu F$ |

|                 |                                          | 100           | V       |

5. The recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Kinetic does not recommend exceeding them or designing to Absolute Maximum Rating.

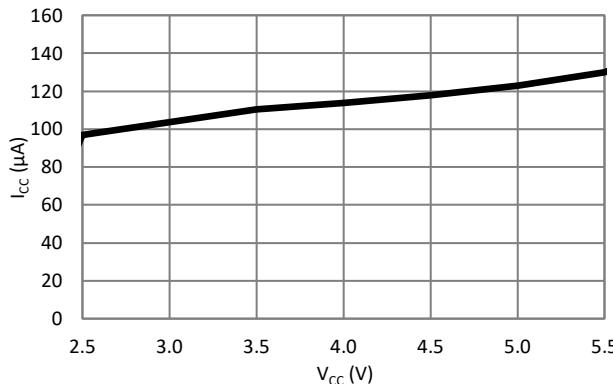

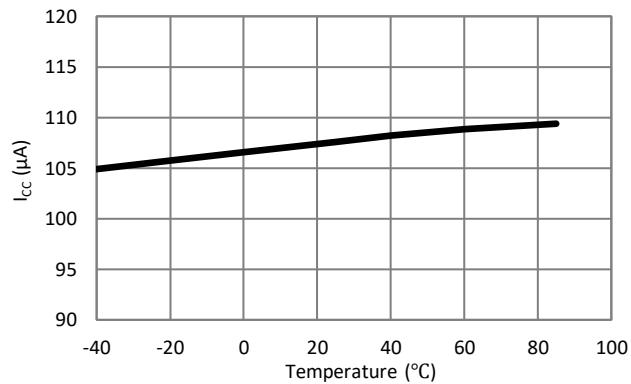

## Electrical Characteristics<sup>6</sup>

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation range of  $T_A = -40^\circ\text{C}$  to  $+85^\circ\text{C}$  with  $V_{CC} = 2.7\text{V}$  to  $4.5\text{V}$ . Typical values are specified at  $T_A = +25^\circ\text{C}$  with  $V_{CC} = 3.3\text{V}$ .

### Supply Specifications

| Symbol     | Description                                     | Conditions                                                                                                                | Min | Typ | Max  | Units         |

|------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----|-----|------|---------------|

| $V_{CC}$   | VCC Supply Operating Voltage Range <sup>7</sup> |                                                                                                                           | 2.7 |     | 4.5  | V             |

| $V_{UVLO}$ | VCC Under-Voltage Lockout                       | Rising threshold                                                                                                          | 2.1 | 2.3 | 2.65 | V             |

|            |                                                 | Hysteresis                                                                                                                |     | 100 |      | mV            |

| $I_{CC}$   | VCC No-Load Supply Current                      | $V_{CC} = 3.3\text{ V}$ (typical), $V_{CC} = 4.5\text{ V}$ (maximum). $-40^\circ\text{C} \leq T_J \leq +85^\circ\text{C}$ |     | 110 | 140  | $\mu\text{A}$ |

### Logic Pin Specifications

| Symbol                      | Description                                             | Conditions                        | Min            | Typ  | Max            | Units            |

|-----------------------------|---------------------------------------------------------|-----------------------------------|----------------|------|----------------|------------------|

| $V_I$                       | Input Logic Threshold (EPR_EN)                          | Rising                            |                |      | 0.73* $V_{CC}$ | V                |

|                             |                                                         | Falling                           | 0.27* $V_{CC}$ |      |                |                  |

| $R_{I\_PD}$                 | Input Logic Pull-Down (EPR_EN)                          |                                   |                | 1    |                | $\text{M}\Omega$ |

| $V_{OL}$                    | Output Logic Low ( $\overline{\text{FLT}}$ )            | $I_{O\_SINK} = 1\text{mA}$        |                | 0.01 | 0.2            | V                |

|                             |                                                         | $I_{O\_SINK} = 3\text{mA}$        |                |      | 0.4            |                  |

| $I_{O\_LK}$                 | Output Logic High-Z Leakage ( $\overline{\text{FLT}}$ ) | $V_O = 5\text{V}$                 | -1             |      | 1              | $\mu\text{A}$    |

| $t_{\overline{\text{FLT}}}$ | $\overline{\text{FLT}}$ Flag Response Time              | Assertion                         |                | 20   |                | $\mu\text{s}$    |

|                             |                                                         | Deassertion debounce <sup>8</sup> |                | 5    |                | ms               |

### Over-Temperature Protection (OTP) Specifications

| Symbol    | Description                           | Conditions                                                      | Min              | Typ        | Max | Units |

|-----------|---------------------------------------|-----------------------------------------------------------------|------------------|------------|-----|-------|

| $T_{OTP}$ | Over-Temperature Protection Threshold | $T_J$ rising threshold<br>$T_J$ falling threshold<br>Hysteresis | 150<br>130<br>35 | 175<br>140 |     | °C    |

### TVS Surge Clamp Specifications

| Symbol          | Description             | Conditions            | Min  | Typ | Max | Units |

|-----------------|-------------------------|-----------------------|------|-----|-----|-------|

| $V_{TVS\_WRK}$  | Clamp Working Voltage   |                       | -0.3 |     | 60  | V     |

| $V_{TVS\_CLMP}$ | Clamp Breakdown Voltage | $I_{IN} = 1\text{mA}$ |      | 64  |     | V     |

(continued next page)

6. Device is guaranteed to meet performance specifications over the  $-40^\circ\text{C}$  to  $+85^\circ\text{C}$  operating temperature range by design, characterization, and correlation with statistical process controls.

7. To guarantee normal startup logical operation, the minimum ramp up time of VCC from 0V to  $>V_{UVLO}$  shall be longer than 0.5ms.

8. CC and SBU channels turn on before the  $\overline{\text{FLT}}$  flag is deasserted and the dead battery resistors are turned off.

## Electrical Characteristics (continued)<sup>9</sup>

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation range of  $T_A = -40^\circ\text{C}$  to  $+85^\circ\text{C}$  with  $V_{CC} = 2.7\text{V}$  to  $4.5\text{V}$ . Typical values are specified at  $T_A = +25^\circ\text{C}$  with  $V_{CC} = 3.3\text{V}$ .

### CC OVP Switch Specifications

| Symbol           | Description                                        | Conditions                                                                                                                                         | Min | Typ | Max | Units            |

|------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------------------|

| $R_{ON\_CC}$     | CC On-Resistance                                   | $V_{CCx\_C} = 0$ to $5.5\text{V}$ , $T_J \leq +85^\circ\text{C}$                                                                                   |     | 300 | 420 | $\text{m}\Omega$ |

| $I_{LK\_CC}$     | CC Off-Leakage Current                             | $V_{CC} = 0\text{V}$ , $V_{CCx\_C} = 5.5\text{V}$ , $V_{CCx\_S} = 0\text{V}$ , $T_A = +25^\circ\text{C}$ , measure current out of $CCx\_S$         |     | 0.1 | 5   | $\mu\text{A}$    |

| $I_{LK\_CC-GND}$ | CC ON-Leakage Current to GND                       | $V_{CC} = 3.3\text{V}$ , $V_{CCx\_C} = 3.6\text{V}$ , $V_{CCx\_S} = \text{floating}$ , $T_A = +25^\circ\text{C}$ , measure current into $CCx\_C$   |     | 1   | 5   | $\mu\text{A}$    |

| $C_{ON\_CC}$     | CC On-Capacitance <sup>10</sup>                    | From $CCx\_C$ or $CCx\_S$ to GND when device is powered, $V_{CCx\_C}$ or $V_{CCx\_S} = 0\text{V}$ to $1.2\text{V}$ , $f = 400\text{kHz}$           |     | 50  |     | $\text{pF}$      |

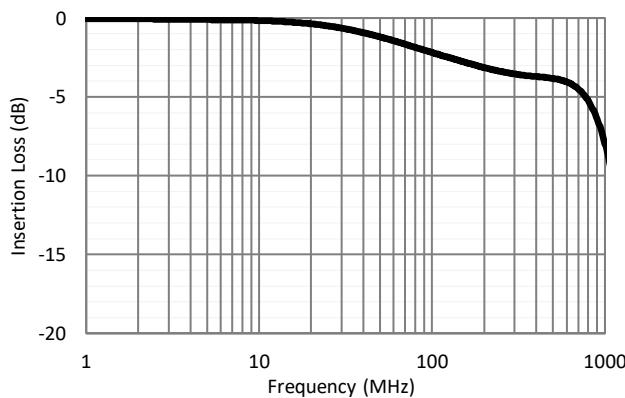

| $BW_{ON\_CC}$    | CC On-Bandwidth <sup>10</sup>                      | -3dB bandwidth from $CCx\_C$ to $CCx\_S$ , single-ended, $50\Omega$ system, $V_{CM} = 0.1\text{V}$ to $1.2\text{V}$                                |     | 180 |     | $\text{MHz}$     |

| $V_{STBUS\_CC}$  | $CCx\_C$ Short-to-VBUS Tolerance <sup>10</sup>     | Hot-plug $CCx\_C$ with 1m USB type-C cable, $30\Omega$ load on $CCx\_S$                                                                            |     |     | 55  | $\text{V}$       |

| $V_{OVP\_CC}$    | $CCx\_C$ OVP Threshold Voltage                     | Rising threshold                                                                                                                                   | 5.6 | 5.9 | 6.2 | $\text{V}$       |

|                  |                                                    | Hysteresis                                                                                                                                         |     | 200 |     | $\text{mV}$      |

| $t_{OVP\_CC}$    | $CCx\_C$ OVP Response Time <sup>10</sup>           | Rising                                                                                                                                             |     | 60  |     | $\text{ns}$      |

|                  |                                                    | Falling debounce                                                                                                                                   |     | 0.9 |     | $\text{ms}$      |

| $V_{MAX\_CC}$    | $CCx\_S$ Rising Maximum Voltage <sup>10</sup>      | During $V_{STBUS\_CC}$ or surge event                                                                                                              | 7   |     |     | $\text{V}$       |

| $t_{ON\_CC}$     | CC Turn-On Time                                    | $V_{CC}$ rising $> V_{UVLO}$                                                                                                                       |     | 1.3 | 3.5 | $\text{ms}$      |

| $t_{OFF\_CC}$    | CC Turn-Off Time <sup>10</sup>                     | $V_{CC}$ falling $< V_{UVLO}$                                                                                                                      |     | 5   |     | $\mu\text{s}$    |

| $R_{DB}$         | Dead Battery Pull-Down Resistance                  | $V_{CC} < V_{UVLO}$ , $V_{CCx\_C} = 2.6\text{V}$                                                                                                   | 4.1 | 5.1 | 6.1 | $\text{k}\Omega$ |

| $V_{DB}$         | RPD_Gx Dead Battery Threshold Voltage              | $V_{CC} < V_{UVLO}$ , $I_{CCx\_C} = 80\ \mu\text{A}$                                                                                               | 0.5 | 0.9 | 1.2 | $\text{V}$       |

| $t_{OFF\_DB}$    | Dead Battery Resistor Turn-Off Delay <sup>11</sup> | $V_{CC}$ rising $> V_{UVLO}$ debounce                                                                                                              |     | 5.7 | 9.5 | $\text{ms}$      |

|                  |                                                    | $V_{CCx\_C}$ falling $< V_{OVP\_CC}$ debounce                                                                                                      |     | 5   |     |                  |

| $I_{LK\_CCOVP}$  | CC OVP Leakage Current                             | $V_{CC} = 0$ or $3.3\text{V}$ , $V_{CCx\_C} = 55\text{V}$ , $V_{CCx\_S} = 0\text{V}$ , $T_A = +25^\circ\text{C}$ , measure current into $CCx\_C$   |     |     | 200 | $\mu\text{A}$    |

|                  |                                                    | $V_{CC} = 0$ or $3.3\text{V}$ , $V_{CCx\_C} = 55\text{V}$ , $V_{CCx\_S} = 0\text{V}$ , $T_A = +25^\circ\text{C}$ , measure current out of $CCx\_S$ |     |     | 1   |                  |

(continued next page)

9. Device is guaranteed to meet performance specifications over the  $-40^\circ\text{C}$  to  $+85^\circ\text{C}$  operating temperature range by design, characterization, and correlation with statistical process controls.

10. Guaranteed by characterization and/or simulation.

11. CC and SBU channels turn on before the  $\overline{FLT}$  flag is deasserted and the dead battery resistors are turned off.

## Electrical Characteristics (continued)<sup>12</sup>

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation range of  $T_A = -40^\circ\text{C}$  to  $+85^\circ\text{C}$  with  $V_{CC} = 2.7\text{V}$  to  $4.5\text{V}$ . Typical values are specified at  $T_A = +25^\circ\text{C}$  with  $V_{CC} = 3.3\text{V}$ .

### SBU OVP Switch Specifications

| Symbol             | Description                                     | Conditions                                                                                                                                                                                                  | Min | Typ | Max | Units         |

|--------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| $R_{ON\_SBU}$      | SBU On-Resistance                               | $V_{SBUXC} = 0$ to $3.6\text{V}$ , $T_J \leq +85^\circ\text{C}$                                                                                                                                             |     | 4.5 | 6.5 | $\Omega$      |

| $I_{LK\_SBU}$      | SBU Off-Leakage Current                         | $V_{CC} = 0\text{V}$ , $V_{SBUX\_C} = 3.6\text{V}$ , $V_{SBUX\_S} = 0\text{V}$ , $T_A = +25^\circ\text{C}$ , measure current out of $SBUX\_S$                                                               |     | 0.1 | 3   | $\mu\text{A}$ |

| $I_{LK\_SBU\_GND}$ | SBU On-Leakage Current to GND                   | $V_{CC} = 3.3\text{V}$ , $V_{SBUX\_C} = 3.6\text{V}$ , $V_{SBUX\_S} = \text{floating}$ , $T_A = +25^\circ\text{C}$ , measure current into $SBUX\_C$                                                         |     | 1   | 3   | $\mu\text{A}$ |

| $C_{ON\_SBU}$      | SBU On-Capacitance <sup>13</sup>                | From $SBUX\_C$ or $SBUX\_S$ to GND when device is powered, $V_{SBUX\_C}$ or $V_{SBUX\_S} = 0.3\text{V}$ to $3.6\text{V}$ , $f = 400\text{kHz}$                                                              |     | 9   |     | $\text{pF}$   |

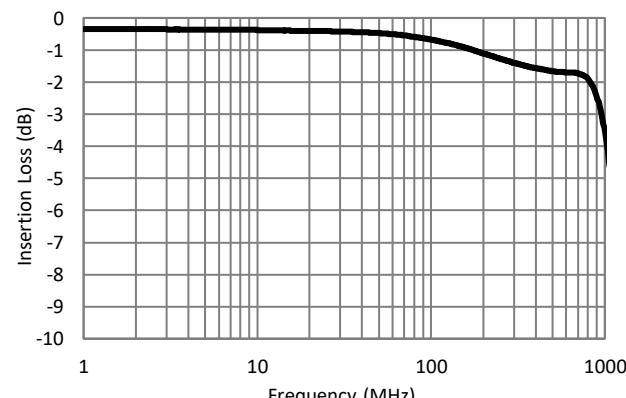

| $BW_{ON\_SBU}$     | SBU On-Bandwidth <sup>13</sup>                  | -3dB bandwidth from $SBUX\_C$ to $SBUX\_S$ , single-ended, $50\Omega$ system, $V_{CM} = 0.1\text{V}$ to $3.6\text{V}$                                                                                       |     | 900 |     | $\text{MHz}$  |

| $X_{TALK\_SBU}$    | SBU Crosstalk <sup>13</sup>                     | From $SBUX1\_S$ to $SBUX2\_C$ or $SBUX2\_S$ to $SBUX1\_C$ when device is powered, $V_{CM1} = 3.6\text{V}$ , $V_{CM2} = 0.3\text{V}$ to $3.6\text{V}$ , $f = 1\text{MHz}$ , $50\Omega$ open side termination |     | -70 |     | $\text{dB}$   |

| $V_{STBUS\_SBU}$   | $SBUX\_C$ Short-to-VBUS Tolerance <sup>13</sup> | Hot-plug $SBUX\_C$ with 1m USB type-C cable, $30\Omega$ load on $SBUX\_S$                                                                                                                                   |     |     | 55  | $\text{V}$    |

| $V_{OVP\_SBU}$     | $SBUX\_C$ OVP Threshold Voltage                 | Rising threshold                                                                                                                                                                                            | 4.0 | 4.2 | 4.4 | $\text{V}$    |

|                    |                                                 | Hysteresis                                                                                                                                                                                                  |     | 100 |     | $\text{mV}$   |

| $t_{OVP\_SBU}$     | $SBUX\_C$ OVP Response Time <sup>13</sup>       | Rising                                                                                                                                                                                                      |     | 60  |     | $\text{ns}$   |

|                    |                                                 | Falling debounce                                                                                                                                                                                            |     | 0.6 |     | $\text{ms}$   |

| $V_{MAX\_SBU}$     | $SBUX\_S$ Rising Maximum Voltage <sup>13</sup>  | During $V_{STBUS\_SBU}$ or surge event                                                                                                                                                                      |     | 6.5 |     | $\text{V}$    |

| $t_{ON\_SBU}$      | SBU Turn-On Time                                | $V_{CC}$ rising $> V_{UVLO}$                                                                                                                                                                                |     | 1.3 | 3.5 | $\text{ms}$   |

| $t_{OFF\_SBU}$     | SBU Turn-Off Time <sup>13</sup>                 | $V_{CC}$ falling $< V_{UVLO}$                                                                                                                                                                               |     | 4   |     | $\mu\text{s}$ |

| $I_{LK\_SBUOVP}$   | SBU OVP Leakage Current                         | $V_{CC} = 0$ or $3.3\text{V}$ , $V_{SBUX\_C} = 55\text{V}$ , $V_{SBUX\_S} = 0\text{V}$ , $T_A = +25^\circ\text{C}$ , measure current into $SBUX\_C$                                                         |     |     | 200 | $\mu\text{A}$ |

|                    |                                                 | $V_{CC} = 0$ or $3.3\text{V}$ , $V_{SBUX\_C} = 55\text{V}$ , $V_{SBUX\_S} = 0\text{V}$ , $T_A = +25^\circ\text{C}$ , measure current out of $SBUX\_S$                                                       |     |     | 1   |               |

(continued next page)

12. Device is guaranteed to meet performance specifications over the  $-40^\circ\text{C}$  to  $+85^\circ\text{C}$  operating temperature range by design, characterization, and correlation with statistical process controls.

13. Guaranteed by characterization and/or simulation.

## Electrical Characteristics (continued)<sup>14</sup>

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation range of  $T_A = -40^\circ\text{C}$  to  $+85^\circ\text{C}$  with  $V_{CC} = 2.7\text{V}$  to  $4.5\text{V}$ . Typical values are specified at  $T_A = +25^\circ\text{C}$  with  $V_{CC} = 3.3\text{V}$ .

### EPR Level Shifter Specifications

| Symbol            | Description                                                | Conditions                                                                                            | Min | Typ  | Max  | Units |

|-------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| $V_{BUS\_DIV}$    | VBUS_LV to VBUS Divider Ratio<br>( $V_{BUS\_LV}/V_{BUS}$ ) | SPR Mode: EPR_EN = 0, $V_{BUS} = 4.5\text{V}$ to $21\text{V}$ , $I_{V_{BUS\_LV}} \leq 20\text{mA}$    |     | 1    |      | V/V   |

|                   |                                                            | EPR Mode: EPR_EN = 1, $V_{BUS} = 26.6\text{V}$ to $50.4\text{V}$ , $I_{V_{BUS\_LV}} \leq 20\text{mA}$ |     | 0.42 |      |       |

| $I_{V_{BUS\_LV}}$ | VBUS_LV Output Load Current                                |                                                                                                       |     |      | 20   | mA    |

| $V_{F\_VBUSLV}$   | VBUS to VBUS_LV Forward Voltage Drop <sup>15</sup>         | EPR_EN = 0, $V_{BUS} = 4.5\text{V}$ , $I_{V_{BUS\_LV}} = 20\text{mA}$                                 |     |      | 100  | mV    |

|                   |                                                            | EPR_EN = 0, $V_{BUS} = 22\text{V}$ , $I_{V_{BUS\_LV}} = 20\text{mA}$                                  |     |      | 100  |       |

| $V_{EPR\_VBUS}$   | Automatic EPR Mode Threshold Voltage                       | $V_{BUS}$ rising                                                                                      |     |      | 24.5 | V     |

|                   |                                                            | $V_{BUS}$ falling                                                                                     | 22  |      |      |       |

### EPR Blocking Gate Driver Specifications

| Symbol          | Description                | Conditions                                                                         | Min | Typ | Max | Units         |

|-----------------|----------------------------|------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| $V_{EPR\_GATE}$ | GATE Output Driver Voltage | $0 \leq V_{BUS} \leq 22\text{V}$                                                   | 5   |     | 12  | V             |

| $I_{EPR\_GATE}$ | GATE Output Driver Current | $0 \leq (V_{GATE} - V_{BUS}) \leq 5\text{V}$ ,<br>$0 \leq V_{BUS} \leq 22\text{V}$ |     | 4   |     | $\mu\text{A}$ |

14. Device is guaranteed to meet performance specifications over the  $-40^\circ\text{C}$  to  $+85^\circ\text{C}$  operating temperature range by design, characterization, and correlation with statistical process controls.

15.  $V_{F\_VBUSLV} = (V_{BUS\_DIV} \times V_{BUS}) - V_{BUS\_LV}$ .

## Typical Characteristics

$V_{CC} = 3.3V$  and  $T_A = +25^\circ C$  unless otherwise noted.

**VCC Supply Current Vs.  $V_{CC}$  Voltage**

**VCC Supply Current Vs. Temperature**

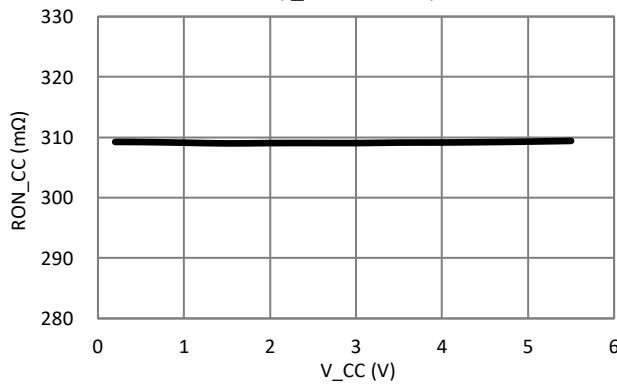

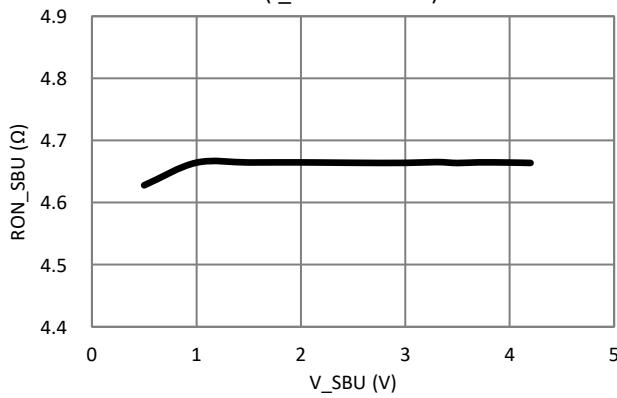

**CC Switch  $R_{ON}$  VS. Switch Voltage

( $I_{CC} = 200mA$ )**

**CC Switch  $R_{ON}$  VS. Switch Voltage**

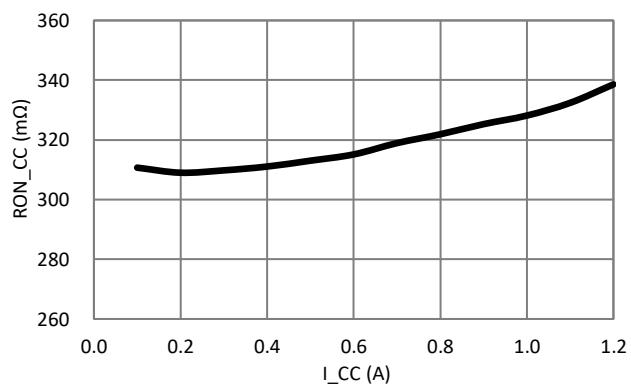

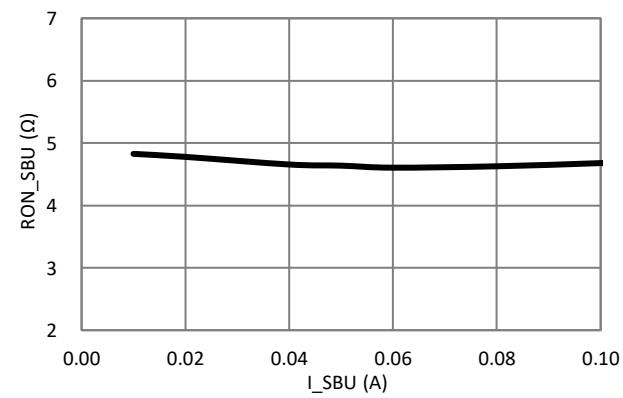

**SBU Switch  $R_{ON}$  VS. Switch Voltage

( $I_{SBU} = 100mA$ )**

**SBU Switch  $R_{ON}$  VS. Switch Voltage**

(continued next page)

## Typical Characteristics

$V_{CC} = 3.3V$  and  $T_A = +25^\circ C$  unless otherwise noted.

**CC Switch OVP VS. Temperature**

**CC Switch OVP Level VS. Temperature**

**CC Switch OVP VS. Temperature**

**SBUx Switch Bandwidth**

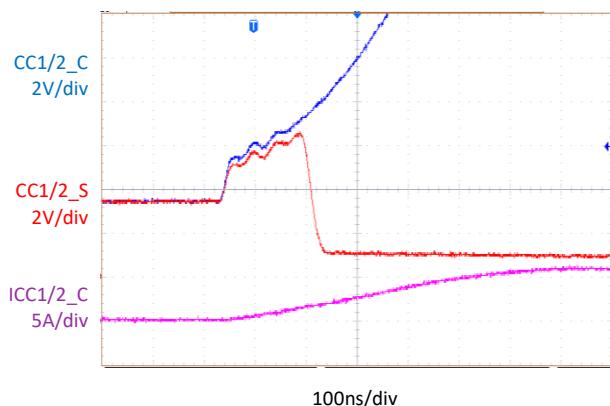

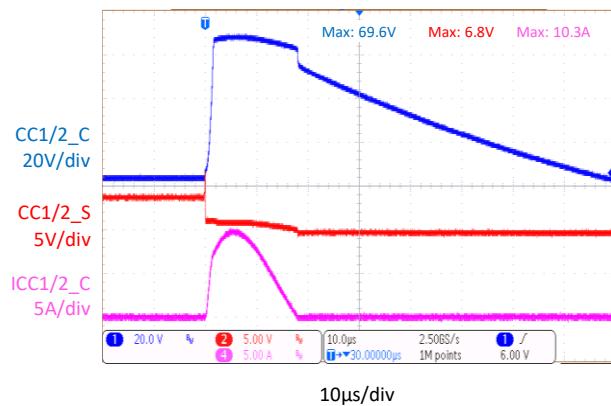

**CCx\_C Short-to-VBUS 48V**

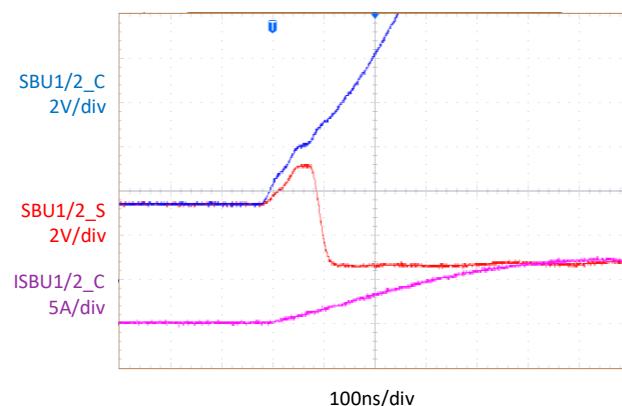

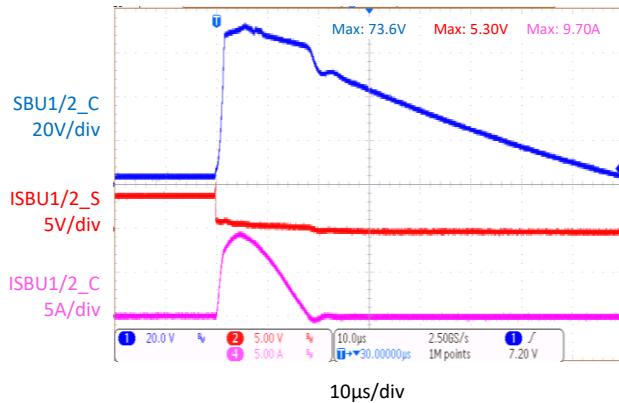

**SBUx\_C Short-to-VBUS 48V**

(continued next page)

## Typical Characteristics

$V_{CC} = 3.3V$  and  $T_A = +25^\circ C$  unless otherwise noted.

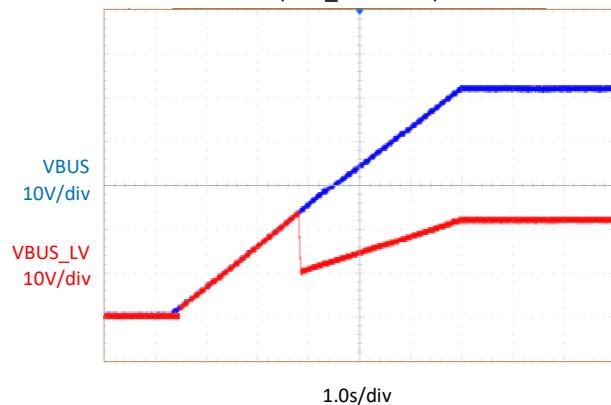

### EPR Level Shifter

(EPR\_EN = Low)

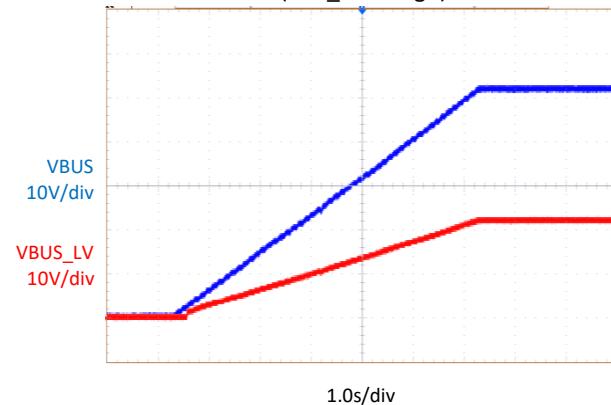

### EPR Level Shifter

(EPR\_EN = High)

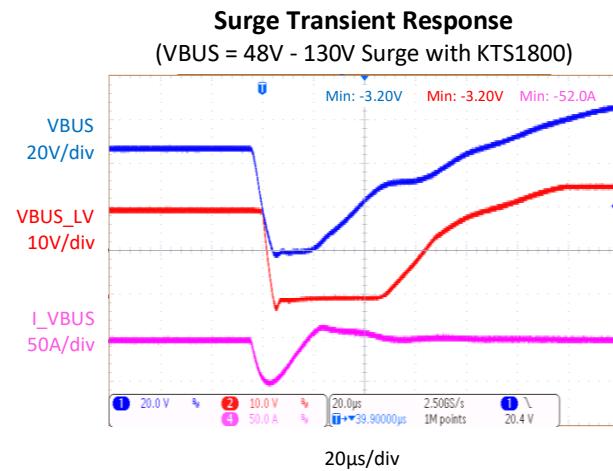

### CC OVP during + 90V Surge Event

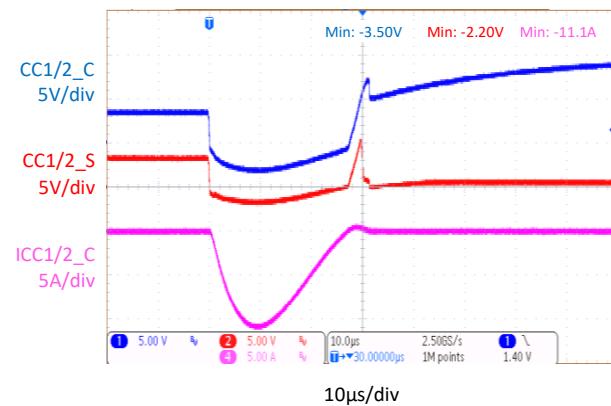

### CC -30V Surge Event

### SBU OVP during + 90V Surge Event

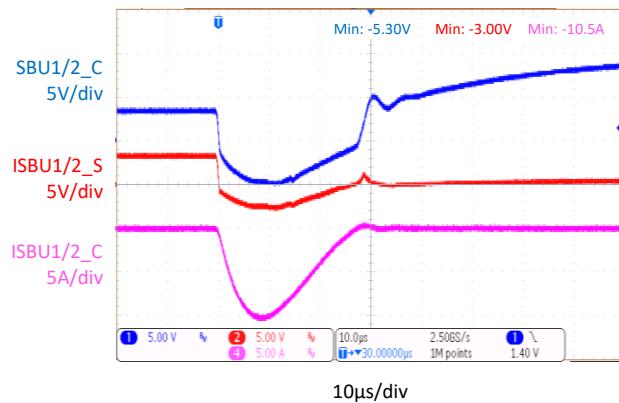

### SBU -30V Surge Event

(continued next page)

## Typical Characteristics

$V_{CC} = 3.3V$  and  $T_A = +25^\circ C$  unless otherwise noted.

## Functional Block Diagram

**Figure 1. Functional Block Diagram**

## Functional Description

### Overview

The KTU1133 provides comprehensive, single-chip protection for USB type-C PD3.1 extended power range (EPR) ports for the CC and SBU pins, as well as the VBUS path specifically to the PD controller. (See the KTS1800 for protecting the VBUS power path to the charger and/or system.) The KTU1133 enables the use of a 20V (nominal) PD controller in EPR systems that support up to 48V (nominal). It is a pin-to-pin alternate source for the TPD4S480.

### Short-to-VBUS Protection

Although the CC and SBU data channels operate at low voltages, these pins are adjacent to VBUS in the type-C connector and vulnerable to short-to-VBUS fault events. Short-to-VBUS events may occur due to mechanical contact, debris, or moisture in the local-side connector or the connector at the other end of the USB cable. With relatively low capacitance on the CC and SBU lines and up to 10uF capacitance on VBUS that may be pre-charged to 48V<sub>DC</sub>, the voltage on CC1/2 or SBU1/2 rises very rapidly during short-to-48V<sub>BUS</sub> events. When coupled with cable and trace inductance, the voltage typically overshoots 48V by many volts. If not controlled and isolated, these high voltages go well beyond the absolute maximum ratings of PD controllers and other circuits within the system. With the KTU1133, the high voltages are contained and isolated from the system.

To protect the system from short-to-VBUS, the KTU1133 includes four channels (for CC1, CC2, SBU1, and SBU2 data-lines) of high-voltage transient-voltage-suppression (TVS) shunt clamping to contain overshoot and four in-line (series-connected) isolation switches to isolate the system. The TVS and switches are designed to work together and provide 63V<sub>DC</sub> tolerance with dynamic short-to-VBUS protection up to 48V + 15% = 55V. During short-to-55V<sub>BUS</sub> events, the KTU1133 turns off the switches very quickly in just 70ns to isolate the system from high voltage. The CC1\_S and CC2\_S system-side is contained to 5.9V<sub>DC</sub> and 7V<sub>PEAK</sub> transient during short-to-55V<sub>BUS</sub>. The SBU1\_S and SBU2\_S system-side is contained to 4.2V<sub>DC</sub> and 6.5V<sub>PEAK</sub> transient during short-to-55V<sub>BUS</sub>.

### ESD Protection

The KTU1133's four channels of TVS provide IEC61000-4-2 level 4 ESD protection for the CC1/2 and SBU1/2 data-lines. Level 4 is defined as  $\pm 8\text{kV}$  contact and  $\pm 15\text{kV}$  air-gap ESD tolerance without damage. ESD events are generally caused by static electricity jumping from an end-user to the exposed contacts within the USB port.

### Surge Protection

The KTU1133's four channels of TVS also provide IEC61000-4-5 surge protection. Surge events are generally caused by lightning strikes or cloud-to-cloud lightning coupling into the power grid, passing through the USB wall adapter and USB cable, and entering the system through the USB port. Other surge events include failure of grid equipment (such as a transformer failure) or sudden loading and inductive surges by other appliances on the local AC lines. Usually, most surge power enters the USB port via VBUS. However, some surge energy may enter from the CC and SBU lines, as well. The KTU1133 provides 90V surge tolerance on CC1/2 and 90V surge tolerance on SBU1/2.

### Over-Voltage Protection (OVP)

If an OVP event occurs on any CC or SBU channel, the KTU1133 turns off all channels at once and pulls FLAG low to indicate there is a fault. After the OVP is removed, the channels recover and FLAG automatically returns to high-Z.

## Over-Temperature Protection (OTP)

If the KTU1133 die junction temperature rises above the thermal shutdown threshold, the KTU1133 turns off all channels at once and pulls  $\overline{\text{FLAG}}$  low to indicate there is a fault. Once the die temperature cools sufficiently, the channels recover and  $\overline{\text{FLAG}}$  automatically returns to high-Z.

## FLT Output Flag

The  $\overline{\text{FLT}}$  pin indicates the fault status. The  $\overline{\text{FLT}}$  open-drain output requires an external pull-up resistor with recommended value in the  $1.7\text{k}\Omega$  to  $300\text{k}\Omega$  range. During OVP and OTP fault conditions, the  $\overline{\text{FLT}}$  flag is active low. When there is no fault, the  $\overline{\text{FLT}}$  flag is high-Z and pulled up via the external resistor.

## DP/DM (D+/D-) Protection

For systems that do not utilize the SBU1/2 data-lines, the SBU1/2 channels in the KTU1133 may be used to protect the DP/DM data-lines. The KTU1133's SBU bandwidth and channel-to-channel isolation support USB data rates up to 900Mbps.

## VCONN Power

Once the CC channel is identified by the system's PD controller as either CC1 or CC2, the unused CCn channel becomes available as VCONN power to support USB active cables, dongles, port-expanders, and other VCONN-powered devices. To support any VCONN device, the KTU1133's CC1/2 switches are rated to pass up to 1.25A continuous current.

## Dead Battery 5.1k $\Omega$ Pull-Down Option

For systems that contain a battery, the KTU1133 includes optional-use circuitry to wake the system in the event of a dead battery. Unlike USB type-A and type-B ports where 5V VBUS power is always present, the type-C port has VBUS turned off before a connection is established. Without VBUS power, the dead battery cannot be charged to wake the system. For this reason, a connection must first be established via a  $5.1\text{k}\Omega$  pull-down on both CC1 and CC2 to accommodate cable-flip, as the CC line may connect at either terminal in the port. Once the upstream AC wall-adapter or other USB current source sees the CC line  $5.1\text{k}\Omega$  pull-down from the KTU1133, the connection is established and VBUS is turned on to 5V, enabling the system to wake.

The PD controller includes  $5.1\text{k}\Omega$  pull-down resistors; however, the KTU1133 protection is inserted between the port and PD controller and is turned off due to lack of system power. Therefore, to enable the dead battery  $5.1\text{k}\Omega$  pull-down option in the KTU1133, connect the RPD\_G1 and RPD\_G2 pins to the CC1\_C and CC2\_C pins, respectively. The KTU1133 presents the  $5.1\text{k}\Omega$  pull-down to the port when:

- 1) KTU1133 is unpowered ( $\text{VCC} < \text{V}_{\text{UVLO}}$ ), and...

- 2) KTU1133 RPD\_G1/2 pins are optionally tied to the CC1/2\_C pins, and...

- 3) CC line in the USB cable is pulled up via a pull-up resistor or current source within the upstream AC wall-adapter or other USB current source.

Once a connection is established, VBUS is turned on, and the system can awake and charge its battery. Then, system power is restored and the KTU1133 receives power at its VCC pin. With power, the CC and SBU switches turn on, but the  $5.1\text{k}\Omega$  pull-downs remain active for an additional 5.7ms to give sufficient time for the PD controller to take over with its internal  $5.1\text{k}\Omega$  pull-downs. Without this important delay, a USB detach event may trigger, causing the upstream AC wall-adapter or other USB current source to turn off VBUS, disrupting system power. After 5.7ms, the KTU1133 pull-downs are disabled.

For applications that do not require the dead battery  $5.1\text{k}\Omega$  pull-downs in the KTU1133, connect the RPD\_G1 and RPD\_G2 pins to ground.

## Extended Power Range (EPR) Adapter

Compared to other CC/SBU protection ICs that target USB standard power range (SPR) up to 20V, the KTU1133 is designed to support EPR systems up to 48V/5A/240W nominal. For this reason, the CC1/2\_C and SBU1/2\_C voltage tolerances have been raised above 48V to survive short-to-VBUS fault events. Additionally, the KTU1133's TVS maximum working voltage, breakdown voltage, and clamping voltage are raised above 48V.

Furthermore, the KTU1133 includes two additional circuits to enable the use of a 20V SPR PD controller in a 48V EPR system. These two circuits are the *VBUS Level Shifter* and the *EPR Blocking FET Gate Driver*, as described below. The two circuits are enabled for EPR Mode via the EPR\_EN active-high logic input **or** whenever the VBUS pin rises over 24V<sub>MAX</sub>. The KTU1133 returns to SPR Mode whenever the EPR\_EN input is logic 0 **and** VBUS falls below 22V<sub>MIN</sub>.

### VBUS Level Shifter

The VBUS level shifter provides a lower-voltage version of VBUS during EPR Mode so an SPR-rated PD controller can safely monitor the VBUS voltage. In EPR Mode, the VBUS\_LV output is proportionally scaled to 0.42x VBUS. Therefore, 48V at the VBUS input is shifted to 20V at VBUS\_LV output. In SPR Mode, the VBUS level shifter enters 1x VBUS "pass through" operation.

### EPR Blocking FET Gate Driver

The EPR blocking FET gate driver controls an external n-channel MOSFET. In SPR Mode, the MOSFET is turned ON so that the PD controller can source VBUS to the USB port to power other devices within the SPR range from 5V\*0.5A=2.5W up to 20V\*5A=100W (as well as the full USB PPS range), depending upon the system capabilities. In EPR Mode, the MOSFET is turned OFF to block high EPR VBUS voltages that would otherwise damage the SPR-rated PD controller. Instead, the PD controller can safely monitor the voltage via the 0.42x VBUS level shifter output at VBUS\_LV.

### EPR-Rated UFP/DFP/DRP with KTU1133 + KTS1800 + 20V SPR PD Controller

The KTU1133 enables 20V SPR-rated PD controllers to be used in USB 36V/48V EPR upstream facing power ports (UFP), downstream facing power ports (DFP), and dual-role power ports (DRP). However, additional EPR-rated VBUS OVP load switches, such as the KTS1800, are required to safely route the EPR VBUS sink and/or source power within the system. The KTS1800 can operate as a current sink or current source switch. It integrates a plethora of fast protection features, including an integrated high-voltage transient voltage suppressor (TVS) for IEC surge and ESD protection. The active TVS in the KTS1800 also provides superior protection for the VBUS pin of the KTU1133, as they are designed to work together.

## Functional Tables

Table 1. EPR/SPR Mode Control

| Mode     | Inputs |                          | Outputs                       |                    |

|----------|--------|--------------------------|-------------------------------|--------------------|

|          | EPR_EN | VBUS                     | VBUS_LV                       | GATE               |

| SPR Mode | 0      | $V_{BUS} < V_{EPR\_BUS}$ | $V_{BUS\_LV} = 1x V_{BUS}$    | Enabled (FET On)   |

| EPR Mode | 1      | X                        | $V_{BUS\_LV} = 0.42x V_{BUS}$ | Disabled (FET Off) |

| EPR Mode | X      | $V_{BUS} > V_{EPR\_BUS}$ | $V_{BUS\_LV} = 0.42x V_{BUS}$ | Disabled (FET Off) |

Table 2. Device Operating State

| Mode                    | Inputs      |                |                 |                  |                | Outputs |       |        |                 |                |       |

|-------------------------|-------------|----------------|-----------------|------------------|----------------|---------|-------|--------|-----------------|----------------|-------|

|                         | VCC         | CCn_C          | SBUn_C          | RPD_Gn           | T <sub>J</sub> | FLT     | CCn_S | SBUn_S | VBUS_LV         | GATE           | 5.1kΩ |

| No Dead Battery Support | $<V_{UVLO}$ | X              | X               | Connect to GND   | X              | high-Z  | Off   | Off    | $1x V_{BUS}$    | Disable        | Off   |

| Dead Battery Support    | $<V_{UVLO}$ | $>V_{DB}$      | X               | Connect to CCn_C | X              | high-Z  | Off   | Off    | $1x V_{BUS}$    | Disable        | On    |

| SPR Mode                | $>V_{UVLO}$ | $<V_{OVP\_CC}$ | $<V_{OVP\_SBU}$ | X                | $<T_{OTP}$     | high-Z  | On    | On     | $1x V_{BUS}$    | Enable         | Off   |

| EPR Mode                | $>V_{UVLO}$ | $<V_{OVP\_CC}$ | $<V_{OVP\_SBU}$ | X                | $<T_{OTP}$     | high-Z  | On    | On     | $0.42x V_{BUS}$ | Disable        | Off   |

| OTP Fault               | $>V_{UVLO}$ | X              | X               | X                | $>T_{OTP}$     | 0       | Off   | Off    | Maintain State  | Maintain State | Off   |

| CC OVP Fault            | $>V_{UVLO}$ | $>V_{OVP\_CC}$ | X               | X                | $<T_{OTP}$     | 0       | Off   | Off    | Maintain State  | Maintain State | Off   |

| SBU OVP Fault           | $>V_{UVLO}$ | X              | $>V_{OVP\_SBU}$ | X                | $<T_{OTP}$     | 0       | Off   | Off    | Maintain State  | Maintain State | Off   |

## Applications Information

### VCC Bypass Capacitor Selection

Place a  $1.0\mu\text{F}/6.3\text{V}$  (or higher) ceramic capacitor between the VCC pin and ground. X5R or X7R dielectric ceramic capacitors are preferred for input supply bypass applications as they maintain better capacitance value and tolerance over operating voltage and temperature ranges when compared to lower cost Y5V dielectric type ceramic capacitors.

### ESD Capacitor Selection

KTU1133 utilizes an ESD support capacitor to meet ESD protection requirements. The ESD support capacitor should be placed between the CESD pin and ground. The CC1/2\_C and SBU1/2\_C inputs can have as much as 65V applied during a short-to-VBUS event with overshoot and the KTU1133's TVS clamping. Therefore, a  $0.1\mu\text{F}/100\text{V}$  X5R or X7R dielectric ceramic capacitor is recommended for this application.

### VBUS Capacitor Selection

Although the KTU1133 does not require much capacitance on VBUS, most USB applications connect a  $1\mu\text{F}$  to  $10\mu\text{F}$  ceramic capacitor from VBUS to GND. Per USB specifications, a maximum of  $10\mu\text{F}$  total is allowed on the VBUS port/connector node. 100V rated capacitors with X5R or better dielectric are recommended for EPR applications. If using the KTU1133 and KTS1800 together, they can share the same VBUS capacitor. For optimal surge and ESD performance with the KTS1800,  $10\mu\text{F}$  is preferred.

### Recommended PCB Layout

Place the bypass capacitors as close as possible to the VCC pin, and ESD protection capacitor as close as possible to the CESD pin. Capacitors must be attached to a solid ground. This minimizes voltage disturbances during transient events such as short-to-VBUS and ESD strikes.

The SBU lines must be routed as straight as possible, and any sharp bends must be minimized. Eliminate any sharp corners on the SBU1\_C, SBU2\_C, SBU1\_S, and SBU2\_S traces by using rounded corners with the largest radii possible.

Standard ESD recommendations apply to the CC1\_C, CC2\_C, SBU1\_C, and SBU2\_C. Route these protected traces as straight as possible. The optimum placement for the device is as close to the connector as possible. EMI during an ESD event can couple from the trace being struck to other nearby unprotected traces, resulting in early system failures. The PCB designer must minimize the possibility of EMI coupling by keeping any unprotected traces away from the protected traces which are between the KTU1133 and the connector.

For the VBUS connection of the KTU1133, the trace should first route from the VBUS terminal of the connector directly to a VBUS capacitor and an appropriate TVS (such as the one integrated within the KTS1800), and then to the KTU1133.

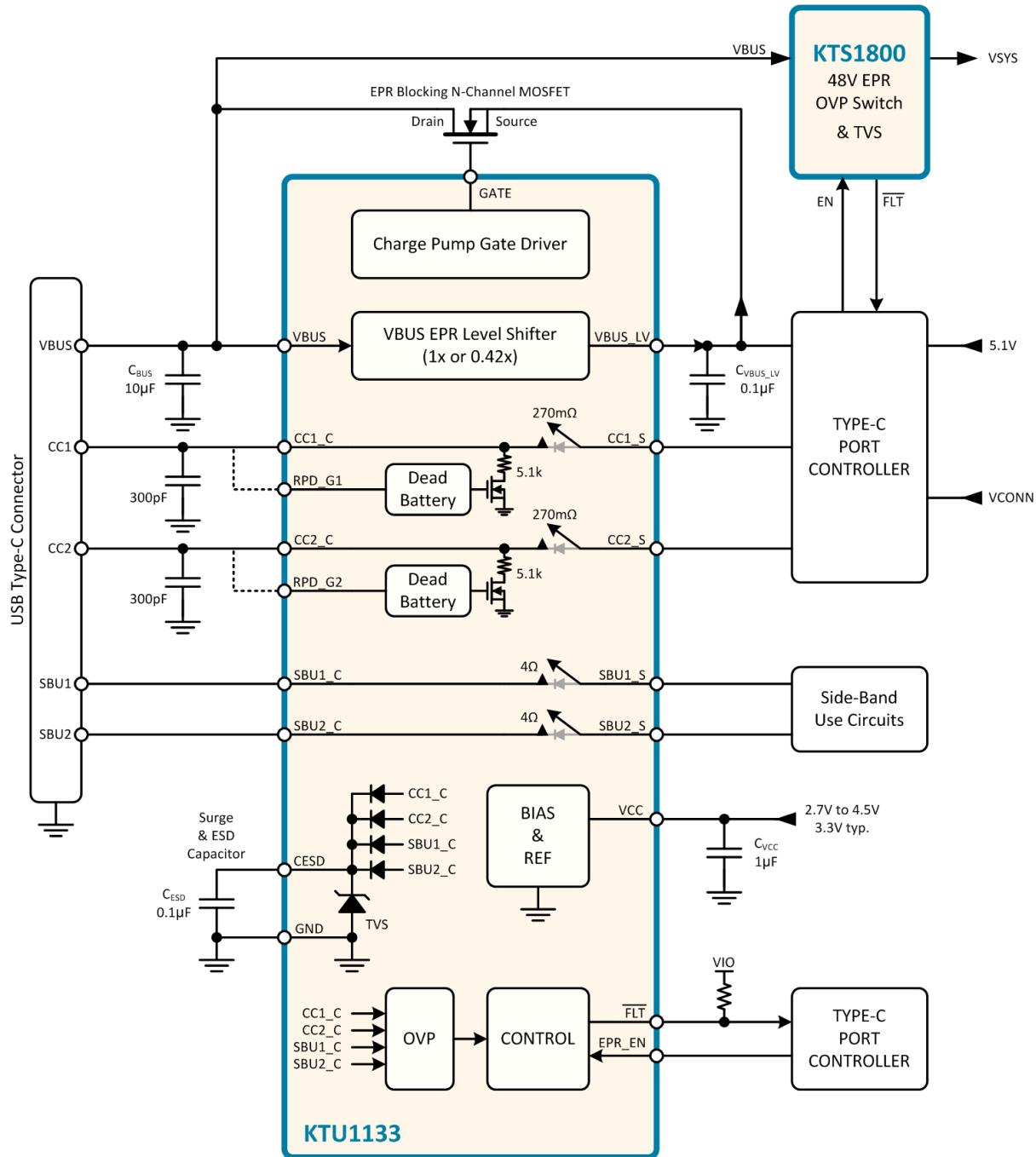

## Packaging Information

WQFN33-20 (3.00mm x 3.00mm x 0.75mm)

| Dimension    | mm   |      |      |

|--------------|------|------|------|

|              | Min. | Typ. | Max. |

| A            | 0.70 | 0.75 | 0.80 |

| A1           | 0.00 | 0.02 | 0.05 |

| A3 0.203 REF |      |      |      |

| b            | 0.15 | 0.20 | 0.25 |

| D            | 2.90 | 3.00 | 3.10 |

| D1           | 1.60 | 1.65 | 1.70 |

| E            | 2.90 | 3.00 | 3.10 |

| E1           | 1.60 | 1.65 | 1.70 |

| e 0.40 BSC   |      |      |      |

| K            | 0.20 | —    | —    |

| L            | 0.30 | 0.40 | 0.50 |

| M            | —    | 0.10 | —    |

| N            | —    | 0.10 | —    |

## Recommended Footprint

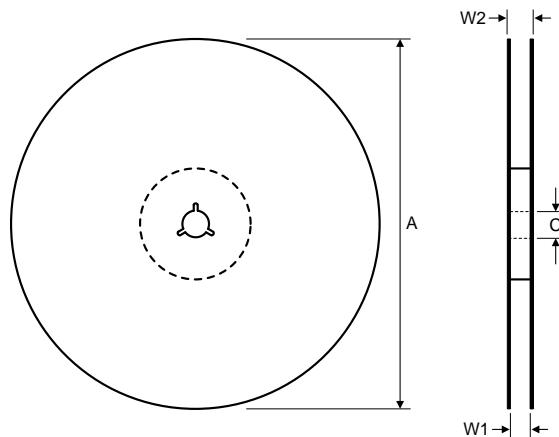

## Packing Material Information

### Reel Dimensions

| Dimension | mm   |      |      |

|-----------|------|------|------|

|           | Min. | Typ. | Max. |

| A         | 328  | 330  | 332  |

| C         | 12.8 | 13.0 | 13.5 |

| W1        | 12.4 | 12.8 | 14.4 |

| W2        | —    | —    | 18.4 |

43-00003-021

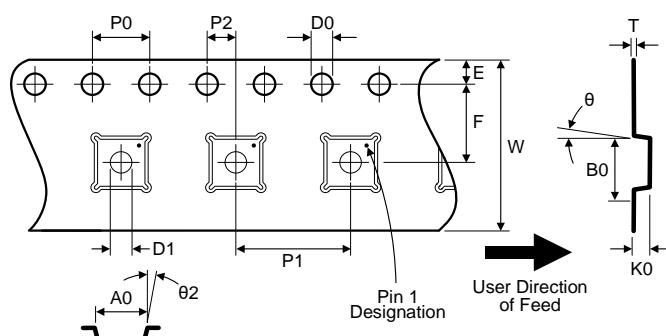

### Carrier Tape Dimensions

### Cover Tape Dimensions

| Dimension | mm        |       |       |

|-----------|-----------|-------|-------|

|           | Min.      | Typ.  | Max.  |

| A0        | —         | 3.30  | —     |

| B0        | —         | 3.30  | —     |

| K0        | —         | 1.10  | —     |

| P0        | 3.98      | 4.00  | 4.02  |

| P1        | —         | 8.00  | —     |

| P2        | 1.95      | 2.00  | 2.05  |

| D0        | 1.50      | 1.50  | 1.60  |

| D1        | 1.50      | —     | —     |

| E         | 1.65      | 1.75  | 1.85  |

| F         | 5.45      | 5.50  | 5.55  |

| 10P0      | 39.8      | 40.0  | 40.2  |

| W         | 11.70     | 12.00 | 12.30 |

| T         | 0.25      | 0.30  | 0.35  |

| θ         | 0°        |       | 5°    |

| θ2        | 0°        |       | 5°    |

| Quantity  | 5000 each |       |       |

43-010X2-306

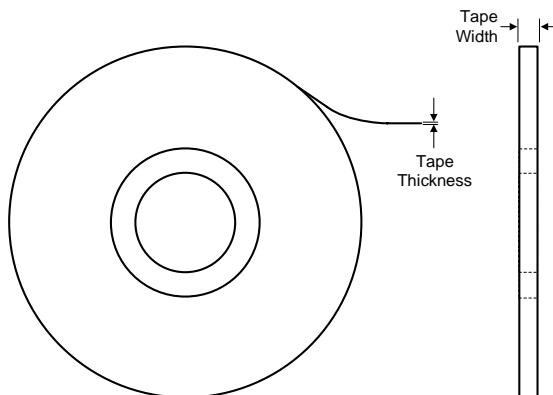

| Dimensions | Dimension      | mm    |       |       |

|------------|----------------|-------|-------|-------|

|            |                | Min.  | Typ.  | Max.  |

|            | Tape Thickness | 0.047 | 0.052 | 0.057 |

| 12mm       | Tape Width     | 9.2   | 9.3   | 9.4   |

43-00002-061

Kinetic Technologies cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Kinetic Technologies product. No intellectual property or circuit patent licenses are implied. Kinetic Technologies reserves the right to change the circuitry and specifications without notice at any time.