## Ideal Diode and Load Switch Controller with Reverse Input Protection

### Features

- 4V to 60V Wide Input Operating Range

- Reverse Voltage Protection to -60V Requirements with a Suitable TVS Diode

- AEC-Q100 Qualified Over -40°C to 125°C Ambient Operating Temp Range

- ESD Ratings

- ▶ HBM, per AEC Q100-002:  $\pm 2\text{kV}$

- ▶ CDM, per AEC Q100-011:  $\pm 750\text{V}$

- Meets Automotive ISO7637 Transient Requirements with a Suitable External TVS Diode

- Internal Charge Pump for External High-Side N-Channel MOSFET Driving

- Controller and MOSFET Driver Suitable for:

- ▶ Single MOSFET for Reverse Protection

- ▶ Two Back-to-Back MOSFETs, one for

- Reverse Protection and the other for Load

- Switching and Inrush Control

- 1.5A/15 $\mu\text{A}$  Sink/Source Current Capability of MOSFET Gate Driver

- EN Pin to Enable/Disable the Controller

- 1 $\mu\text{A}$  Shutdown Current

- 110 $\mu\text{A}$  Operating Quiescent Current

- 230ns Reverse Protection Response Time

- Small 6 Pin SOT23 Package (2.9mm x 1.6mm)

### Applications

- Automotive Battery and Digital Unit Protection

- Automotive Camera System

- Reverse Power Supply Protection

- Telecom/Server/Networking Systems

- Redundant Power Systems

- Industrial and Medical Systems

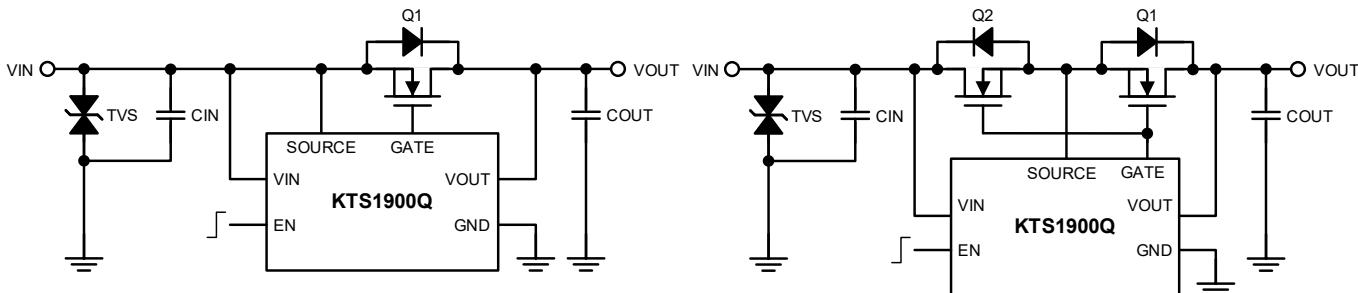

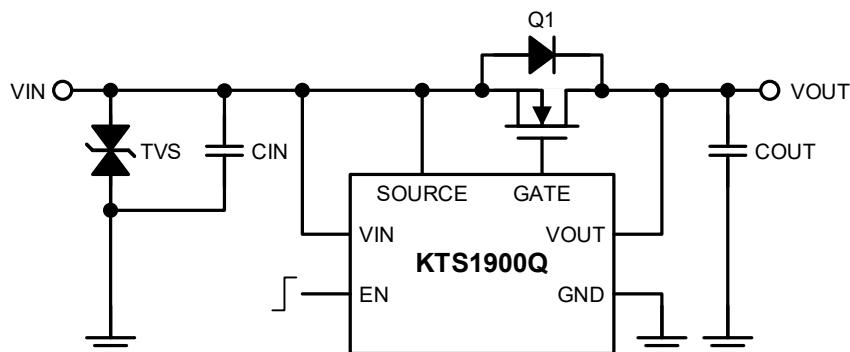

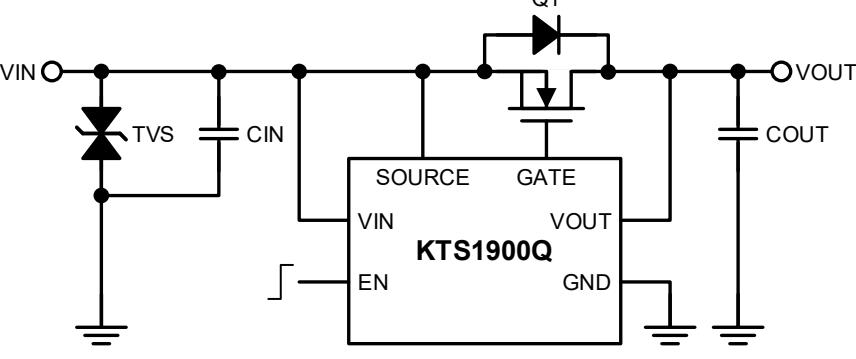

### Typical Application

**Figure 1. (a) Ideal Diode Controller Application (b) Load Switch Controller Application**

## Ordering Information

| Part Number     | Marking <sup>1</sup> | Operating Temperature | Package  |

|-----------------|----------------------|-----------------------|----------|

| KTS1900QGXAA-TA | ZMYWZ<br>aaaaaaaa    | -40°C to +125°C       | SOT23-6L |

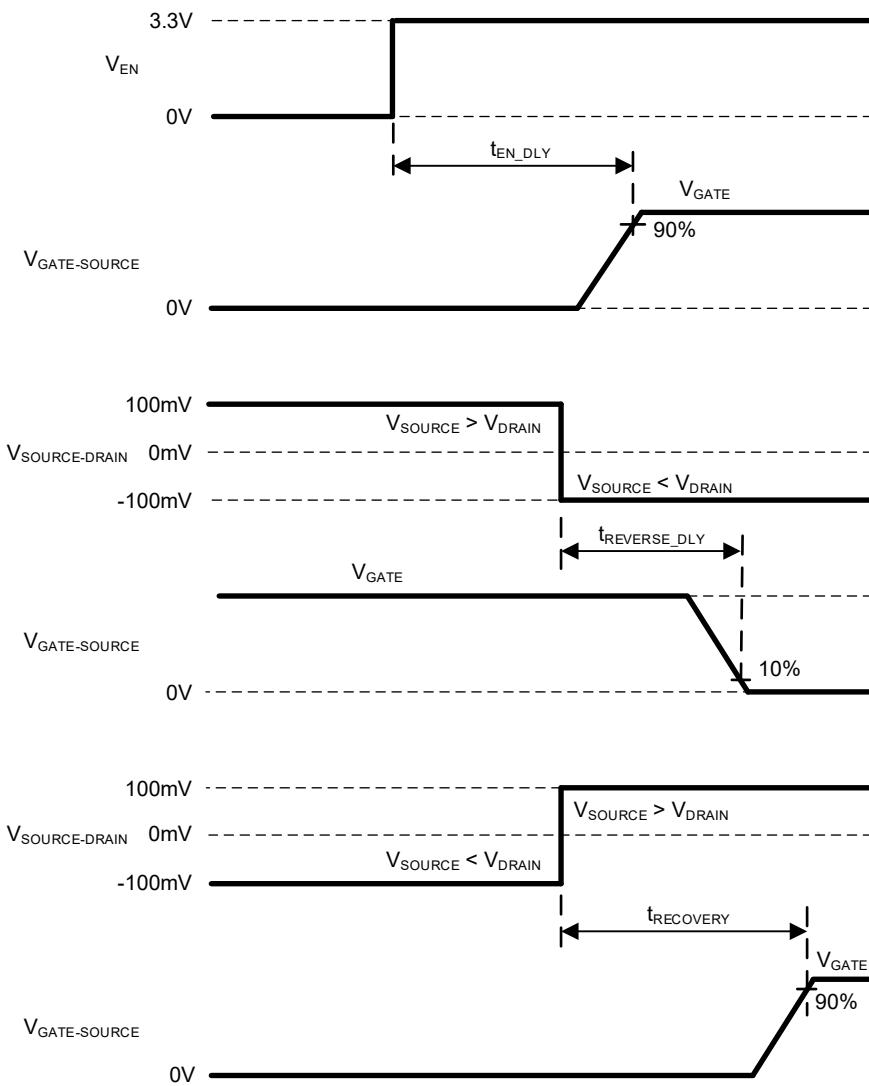

## Pin Descriptions

### Top View

SOT23-6 2.9mm x 1.6mm x 1.45mm

SOT23 Package

### Top Mark

XX = Device Code, YW = Date Code, Z = Serial Number

aaaaaaaa = Assembly Lot Tracking Number

| Pin # | Name   | Function                                                                                                                                                                                                          |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VIN    | Supply voltage input. Connect pin to supply voltage VIN with a 2.2µF capacitor to ground. The VIN pin must be connected to the SOURCE pin in Ideal Diode mode. See the typical application schematic for details. |

| 2     | GND    | Device ground.                                                                                                                                                                                                    |

| 3     | EN     | Enable control pin. EN pin is used to enable and disable the controller. EN pin can be also connected to VIN directly to enable the controller.                                                                   |

| 4     | VOUT   | Output voltage sense pin. Connect to the drain of the external N-channel MOSFET. Use 2.2µF from VOUT to ground                                                                                                    |

| 5     | GATE   | Gate drive. Connect to the gate of the external N-Channel MOSFETs.                                                                                                                                                |

| 6     | SOURCE | Source pin. Connect to the source of the external N-Channel MOSFETs in Load Switch mode. SOURCE pin is also connected to VIN pin in single MOSFET application.                                                    |

1. ZM = Device Code, YW = Date Code, Z = Serial Number, aaaaaaaaa = Assembly Lot Tracking Number

## Absolute Maximum Ratings<sup>2</sup>

(T<sub>A</sub> = 25°C unless otherwise noted)

| Symbol            | Description                                                           | Min. | Max. | Units |

|-------------------|-----------------------------------------------------------------------|------|------|-------|

| V <sub>IN</sub>   | V <sub>IN</sub> , EN, SOURCE to GND                                   | -65  | 65   | V     |

| V <sub>OUT</sub>  | V <sub>OUT</sub> to GND                                               | -0.3 | 65   | V     |

| V <sub>OUT</sub>  | V <sub>OUT</sub> to V <sub>IN</sub>                                   | -65  | 80   | V     |

| V <sub>I-S</sub>  | V <sub>IN</sub> to SOURCE                                             | -0.3 | 80   | V     |

| V <sub>O-S</sub>  | V <sub>OUT</sub> to SOURCE                                            | -0.3 | 80   | V     |

| V <sub>GS</sub>   | GATE to SOURCE                                                        | -0.3 | 20   | V     |

| T <sub>J</sub>    | Operating Junction Temperature Range (T <sub>J</sub> )                | -40  | 150  | °C    |

| T <sub>S</sub>    | Storage Temperature Range (T <sub>S</sub> )                           | -55  | 150  | °C    |

| T <sub>LEAD</sub> | Maximum Soldering Temperature (at leads, 10 sec) (T <sub>LEAD</sub> ) | -    | 250  | °C    |

## ESD Ratings<sup>3</sup>

| Symbol                               | Description                                            | Value | Units |

|--------------------------------------|--------------------------------------------------------|-------|-------|

| V(ESD)<br>Electrostatic<br>discharge | Human body model (HBM), per AEC Q100-002, all pins     | ±2000 | V     |

|                                      | Charged device model (CDM), per AEC Q100-011, all pins | ±750  | V     |

## Thermal Capabilities<sup>4</sup>

| Symbol              | Description                                                           | Value | Units |

|---------------------|-----------------------------------------------------------------------|-------|-------|

| Θ <sub>JA</sub>     | Thermal Resistance – Junction to Ambient                              | 120   | °C/W  |

| P <sub>D</sub>      | Maximum Continuous Power Dissipation at 25°C (T <sub>J</sub> = 125°C) | 833   | mW    |

| ΔP <sub>D</sub> /ΔT | Derating Factor Above T <sub>A</sub> = 25°C                           | -8.3  | mW/°C |

## Recommended Operating Conditions<sup>5</sup>

| Symbol           | Description                                            | Min. | Max. | Units |

|------------------|--------------------------------------------------------|------|------|-------|

| V <sub>IN</sub>  | V <sub>IN</sub> to GND                                 | -60  | 60   | V     |

| V <sub>EN</sub>  | EN to GND                                              | -60  | 60   | V     |

| V <sub>OUT</sub> | V <sub>OUT</sub> to GND                                | -0.3 | 60   | V     |

| T <sub>J</sub>   | Operating Junction Temperature Range (T <sub>J</sub> ) | -40  | 125  | °C    |

-

2. Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

3. ESD conform to JEDEC and IEC industry standards. Some pins may have higher performance.

4. Junction to Ambient thermal resistance is highly dependent on PCB layout. Values are based on thermal properties of the device when soldered to an EV board.

5. The recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Kinetic does not recommend exceeding them or designing to Absolute Maximum Rating.

## Electrical Characteristics<sup>6</sup>

Typical values correspond to  $T_A = 25^\circ\text{C}$ . *Minimum* and *Maximum* specs are applied over the full operation junction temperature range of  $-40^\circ\text{C}$  to  $125^\circ\text{C}$ , unless otherwise noted. SOURCE pin tied to VIN pin, VIN = 12V,  $V_{EN} = 12\text{V}$  unless otherwise noted.

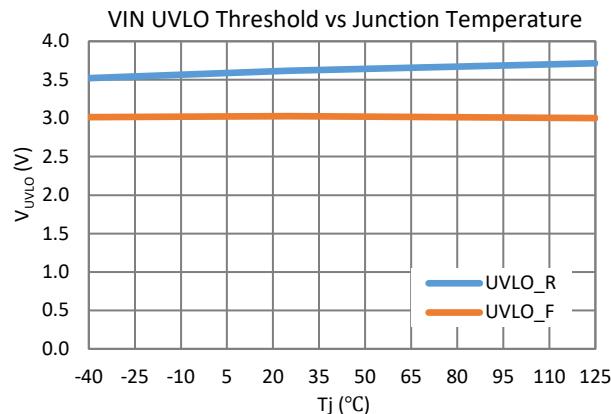

### Supply and Enable

| Symbol     | Description                   | Conditions  | Min. | Typ. | Max. | Units         |

|------------|-------------------------------|-------------|------|------|------|---------------|

| $V_{IN}$   | Operating Input Voltage Range |             | 4    |      | 60   | V             |

|            | VIN Undervoltage Threshold    | VIN Rising  |      | 3.6  | 3.95 | V             |

|            |                               | VIN Falling | 2.65 | 3    |      | V             |

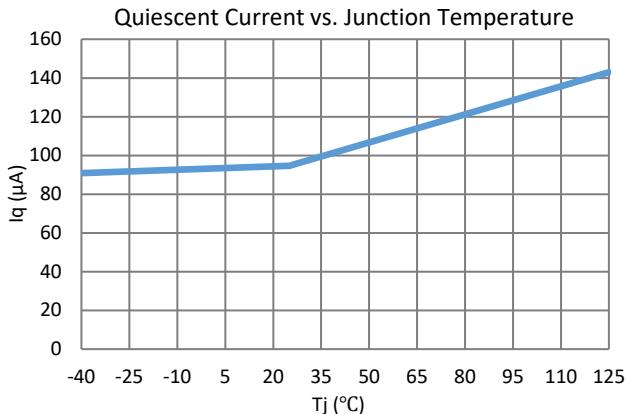

| $I_Q$      | Operating Quiescent Current   | EN = 12V    |      | 110  | 180  | $\mu\text{A}$ |

| $I_{SHDN}$ | Shutdown Supply Current       | EN = 0V     |      | 1    | 4    | $\mu\text{A}$ |

| $EN$       | EN Logic High Threshold       | EN Rising   |      | 1.24 | 1.32 | V             |

|            | EN Logic Low Threshold        | EN Falling  | 0.7  | 1.14 |      | V             |

| $I_{EN}$   | EN Pin Sink Current           | EN = 12V    |      | 3    | 5    | $\mu\text{A}$ |

### Gate Driver

| Symbol             | Description                                                        | Conditions                                                      | Min. | Typ. | Max. | Units         |

|--------------------|--------------------------------------------------------------------|-----------------------------------------------------------------|------|------|------|---------------|

| $V_{GATE}$         | Gate Drive Voltage (GATE to SOURCE)                                | Full Conduction Mode,<br>$V_{SOURCE} - V_{VOUT} = 100\text{mV}$ | 10   | 12   | 15   | V             |

| $I_{GATE}$         | Gate Peak Source Current                                           |                                                                 |      | 15   |      | $\mu\text{A}$ |

|                    | Gate Peak Sink Current <sup>7</sup>                                |                                                                 |      | 1.5  |      | A             |

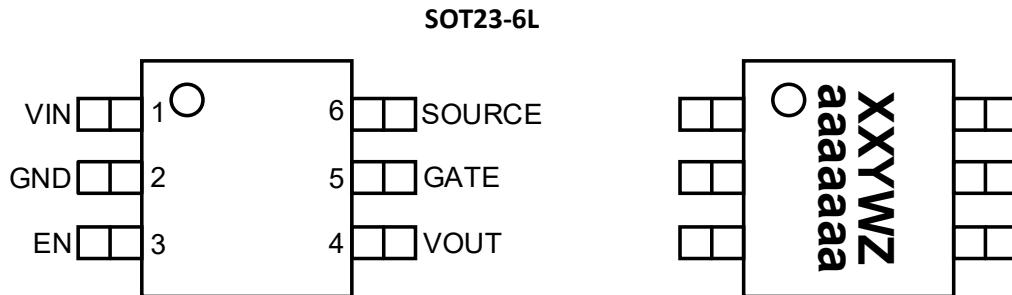

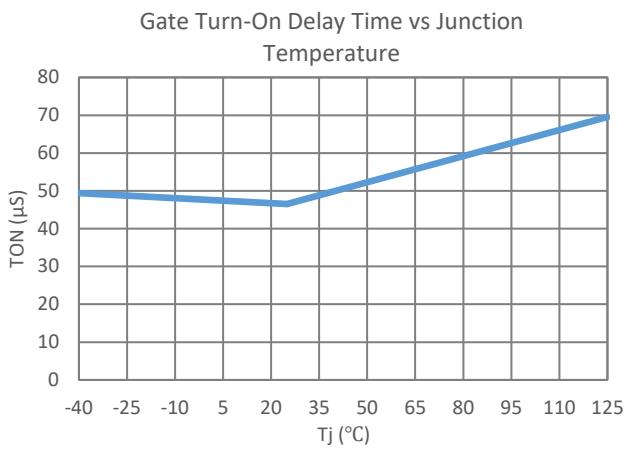

| $T_{EN\_DLY}$      | Gate Turn-On Delay Time                                            |                                                                 |      | 60   | 100  | $\mu\text{s}$ |

| $T_{REVERSE\_DLY}$ | Gate Turn-Off Delay Time                                           |                                                                 |      | 230  |      | ns            |

| $T_{RECOVERY}$     | Recovery Delay from Forward Detection to Gate Turn On <sup>7</sup> |                                                                 |      | 5    |      | $\mu\text{s}$ |

### Source to Drain Voltage

| Symbol      | Description                                                    | Conditions | Min. | Typ. | Max. | Units |

|-------------|----------------------------------------------------------------|------------|------|------|------|-------|

| $V_{SDREG}$ | Regulated Source to Drain Voltage (SOURCE-VOUT)                |            | 25   | 45   | 70   | mV    |

| $V_{SDREV}$ | Source to Drain Voltage Threshold for Reverse Current Blocking |            | -24  | -15  | -2   | mV    |

### VOUT and Source Pin Current

| Symbol       | Description                          | Conditions                | Min. | Typ. | Max. | Units         |

|--------------|--------------------------------------|---------------------------|------|------|------|---------------|

| $I_{VOUT}$   | VOUT Pin Sink Current                | $V_{OUT} = 12\text{V}$    |      | 1.5  | 2    | $\mu\text{A}$ |

| $I_{SOURCE}$ | SOURCE Pin Sink Current <sup>7</sup> | $V_{SOURCE} = 12\text{V}$ |      | 5    | 10   | $\mu\text{A}$ |

6. Device is guaranteed to meet performance specifications over the  $-40^\circ\text{C}$  to  $+125^\circ\text{C}$  operating temperature range by design, characterization and correlation with statistical process controls.

7. Guaranteed by design, characterization and statistical process control methods; not production tested.

## Timing Diagrams

**Figure 2. Timing Definition**

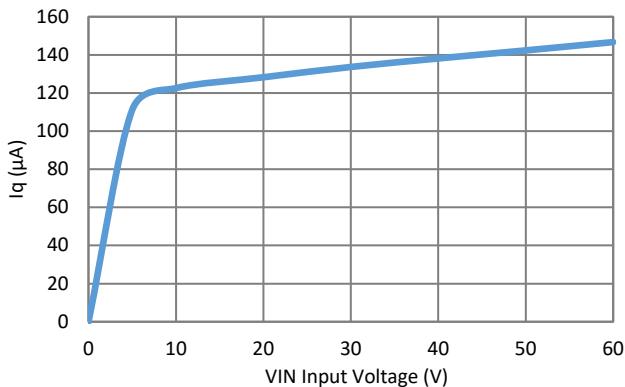

## Typical Characteristics

$V_{IN} = 12V$ ,  $T_A = 25^\circ C$ , unless otherwise specified.

Input Operating Quiescent Current vs. Vin

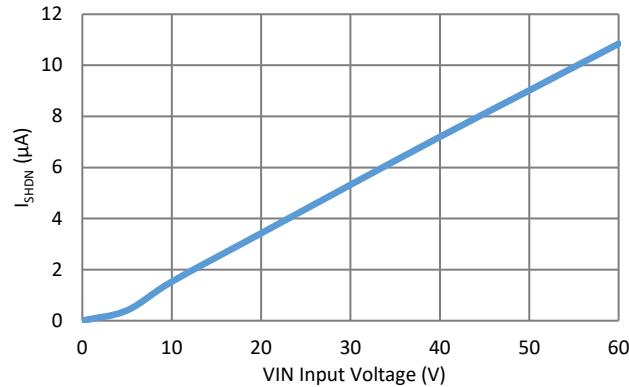

Input Shutdown Current vs. Vin

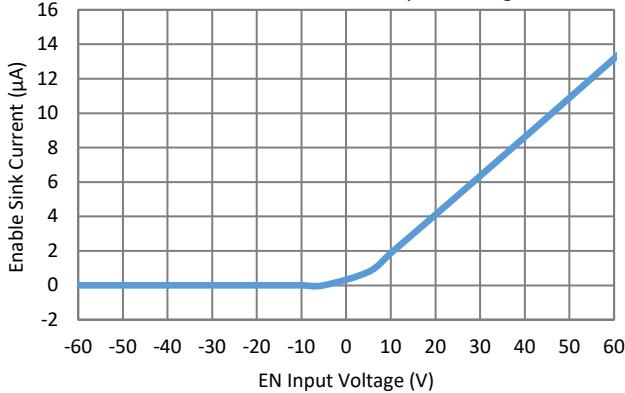

Enable Sink Current vs. EN Input Voltage

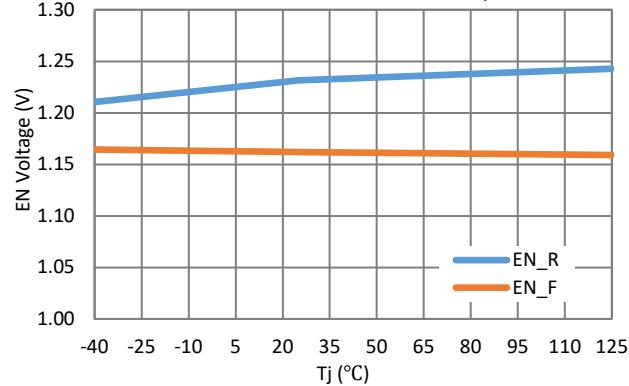

Enable Threshold vs. Junction Temperature

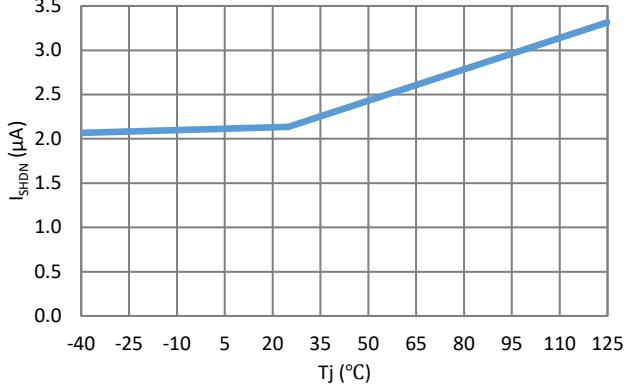

Input Shutdown Current vs. Temperature

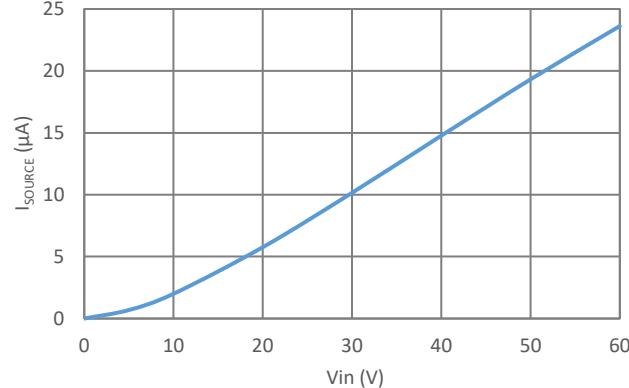

SOURCE Current in Shutdown vs Vin

## Typical Characteristics

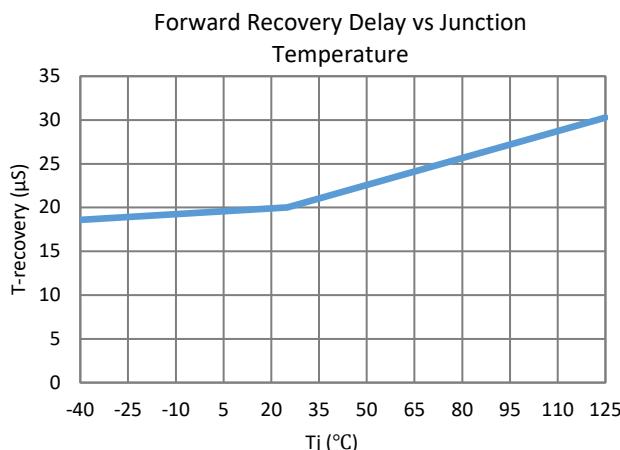

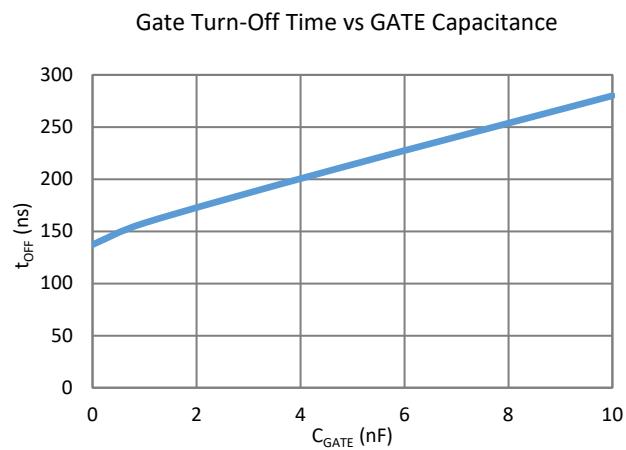

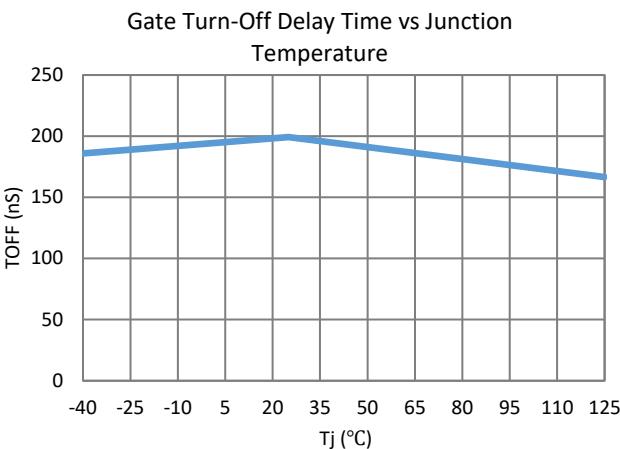

$V_{IN} = 12V$ ,  $T_A = 25^\circ C$ , unless otherwise specified.

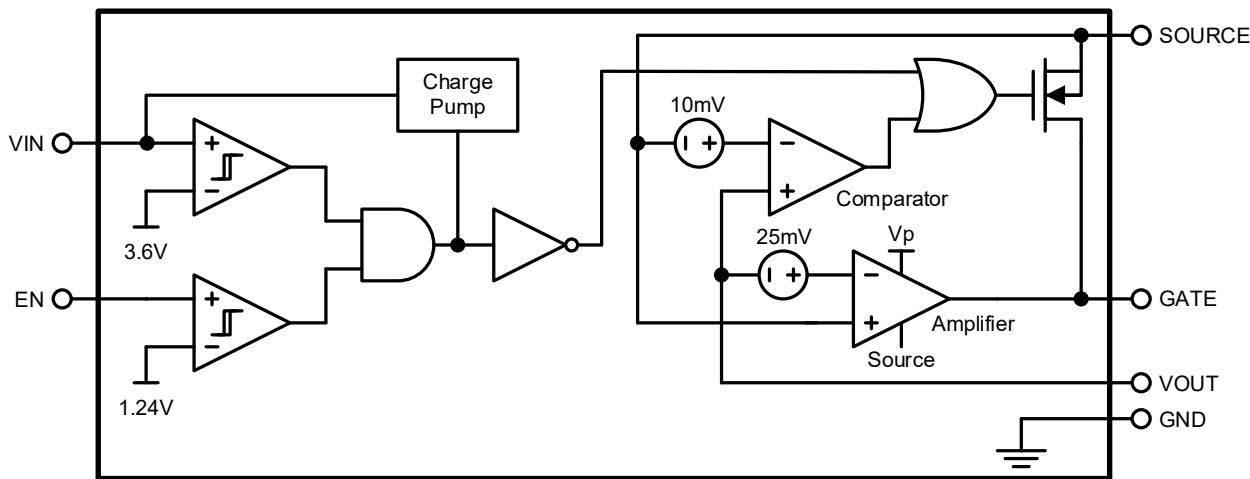

## Functional Block Diagram

**Figure 3. Functional Block Diagram**

## Application Information

### Overview

To achieve an ideal diode function the KTS1900Q controls an external N-MOSFET. An internal charge pump is used to supply NMOSFET gate driver turn on voltage. This ideal diode controller integrates a fast reverse current protection circuit. This protects the system from reverse current when there is a short or reverse polarity at VIN. In forward mode the KTS1900Q also senses the source to drain voltage drop of the NMOSFET. The device linearly increases the GATE voltage to regulate the forward voltage drop to 40mV at light load. To keep the power loss at a minimum the GATE voltage increases with load current. This makes the KTS1900Q ideal diode solution more efficient compared to traditional a Schottky diode. The forward voltage drop is regulated to avoid oscillation at light loads and minimize the power dissipation at higher currents. The KTS1900Q also detects reverse current through the MOSFET. If the threshold is reached the MOSFET is turned off with a 1.5 Amp GATE pull down. The EN pin is also available to turn off the MOSFETs and minimize the current drawn by the controller down to 1 $\mu$ A.

**Figure 4. Typical Application**

### Linear Regulation Control

The table below shows that at light load the gate drive is reduced to regulate the source to drain voltage. At higher currents the MOSFET is driven to its lowest resistance. This results in a soft turn on and the lowest R<sub>ON</sub> at higher currents as listed in Table 1.

**Table 1. Linear Regulation Control as Output Current Increases**

| I <sub>OUT</sub><br>(A) | V <sub>GS</sub><br>(V) | R <sub>ON</sub><br>(mΩ) | PLOSS<br>(mW) |

|-------------------------|------------------------|-------------------------|---------------|

| 0.1                     | 2.195                  | 476.00                  | 4.8           |

| 1                       | 2.611                  | 48.70                   | 48.7          |

| 2                       | 2.854                  | 24.80                   | 99.2          |

| 3                       | 3.073                  | 16.87                   | 151.8         |

| 4                       | 3.310                  | 12.90                   | 206.4         |

| 5                       | 3.603                  | 10.52                   | 263.0         |

| 6                       | 3.998                  | 8.98                    | 323.4         |

| 7                       | 4.583                  | 7.90                    | 387.1         |

| 8                       | 5.480                  | 7.15                    | 457.6         |

| 9                       | 6.832                  | 6.61                    | 535.5         |

| 10                      | 8.790                  | 6.27                    | 627.0         |

| 11                      | 11.260                 | 6.08                    | 735.9         |

| 12                      | 13.870                 | 6.05                    | 871.2         |

| 13                      | 13.890                 | 6.2                     | 1047.8        |

Notes: V<sub>GS</sub> is the MOSFET GATE to SOURCE voltage. PLOSS is the MOSFET power loss.

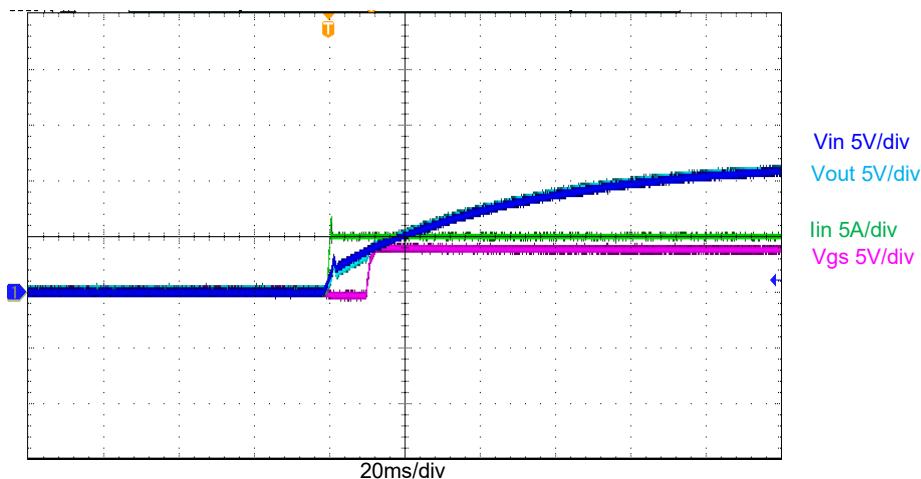

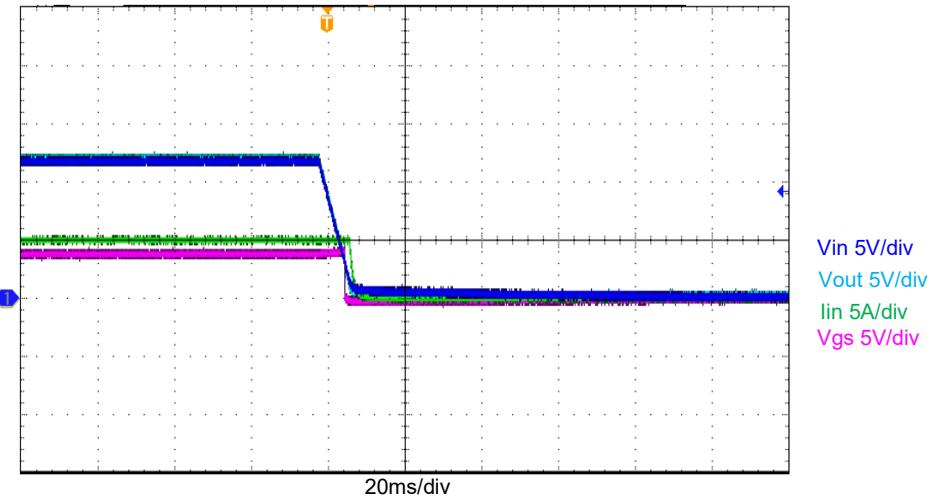

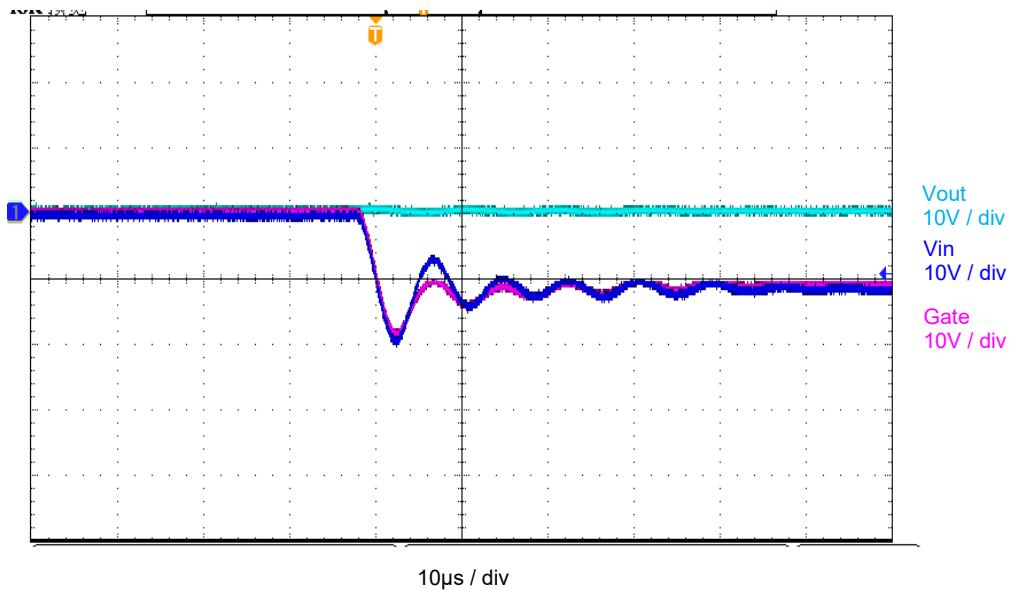

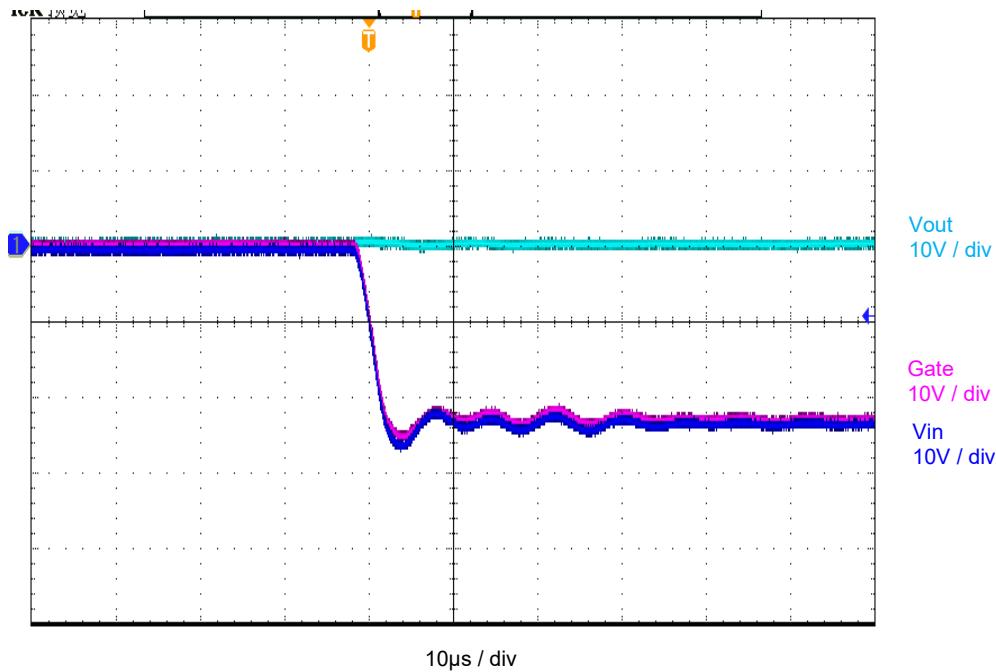

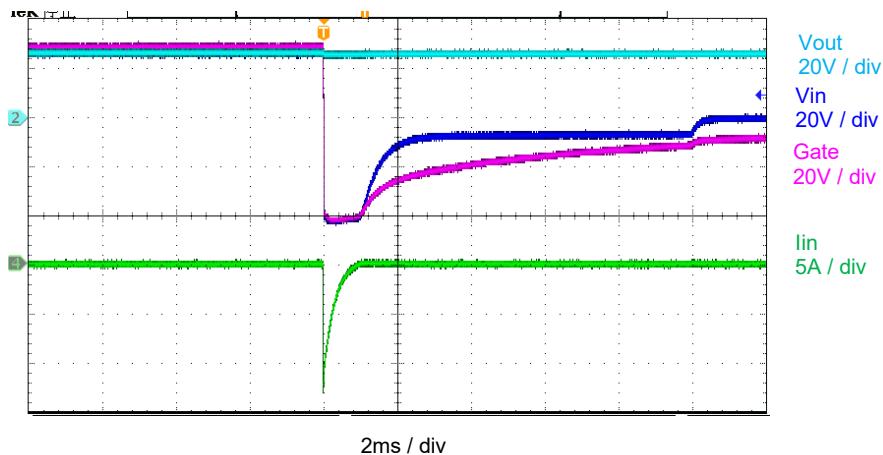

### Operational Waveform

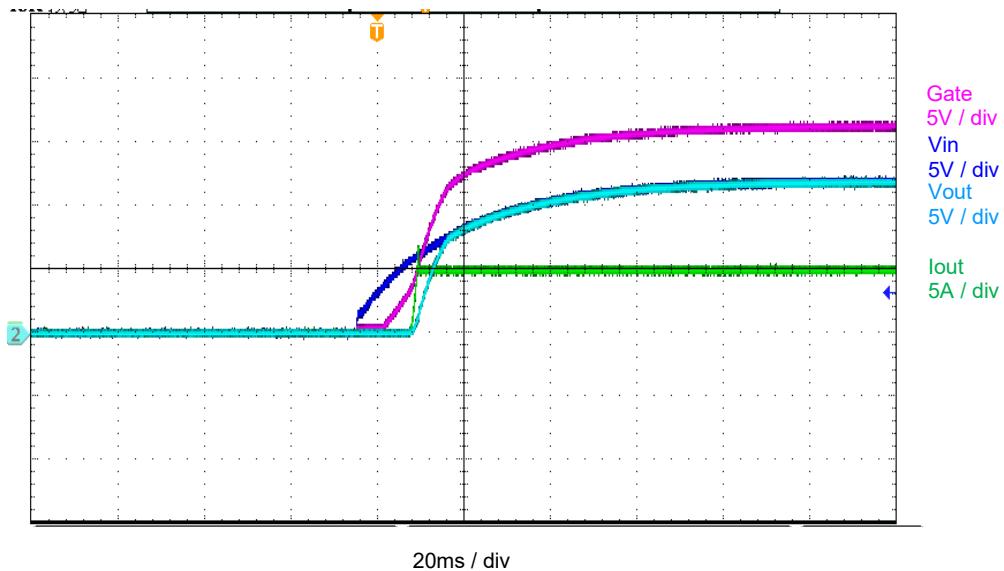

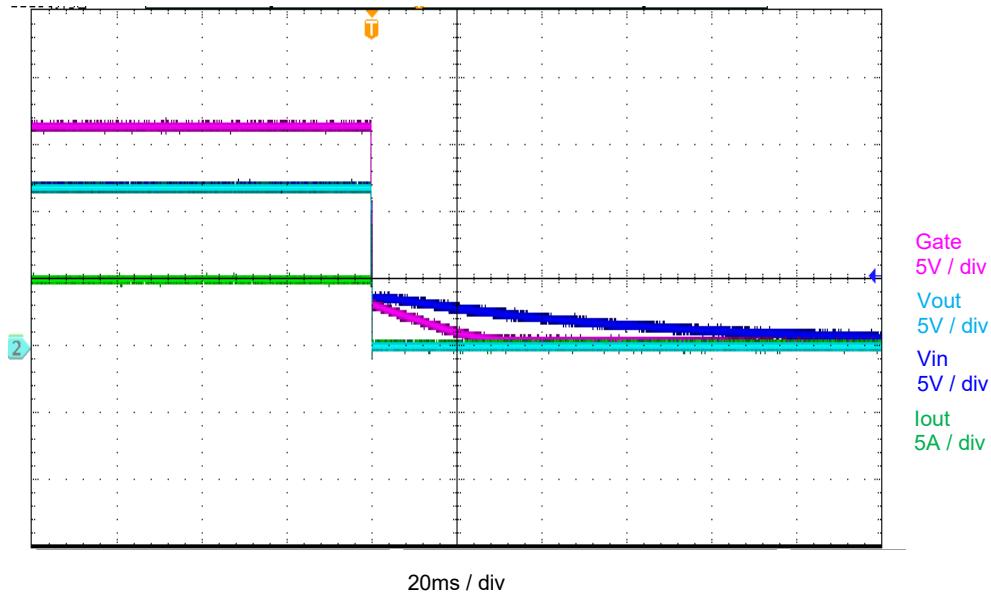

The normal startup and shut down waveforms for ideal diode configuration with 12V input are shown in Figure 5 and Figure 6.

**Figure 5. Start up at 12V Vin, and 5A Load**

**Figure 6. Turn off at 12V Vin, and 5A Load**

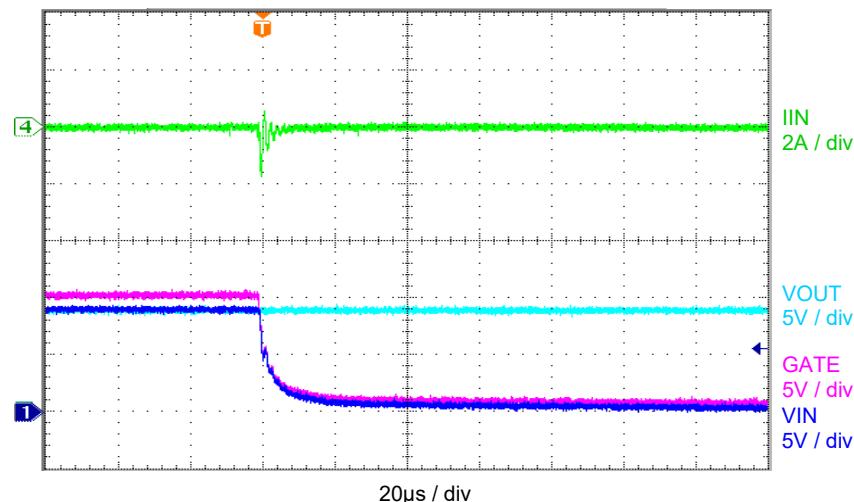

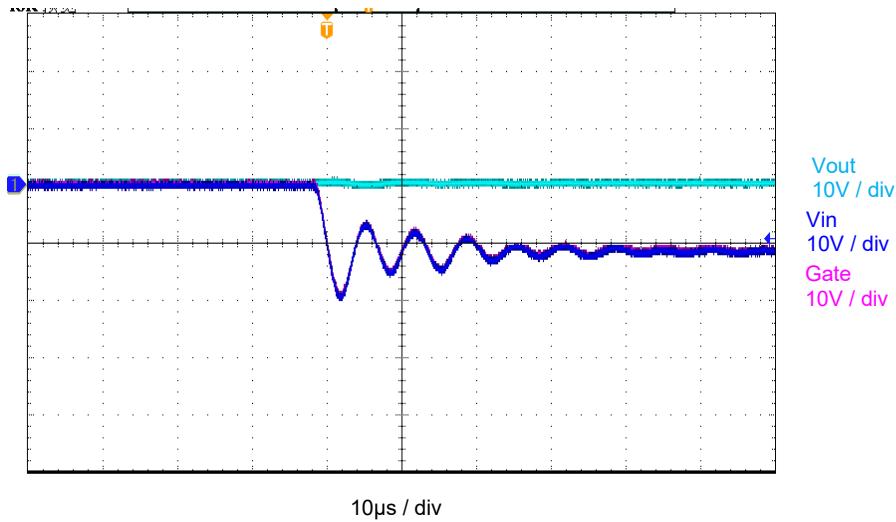

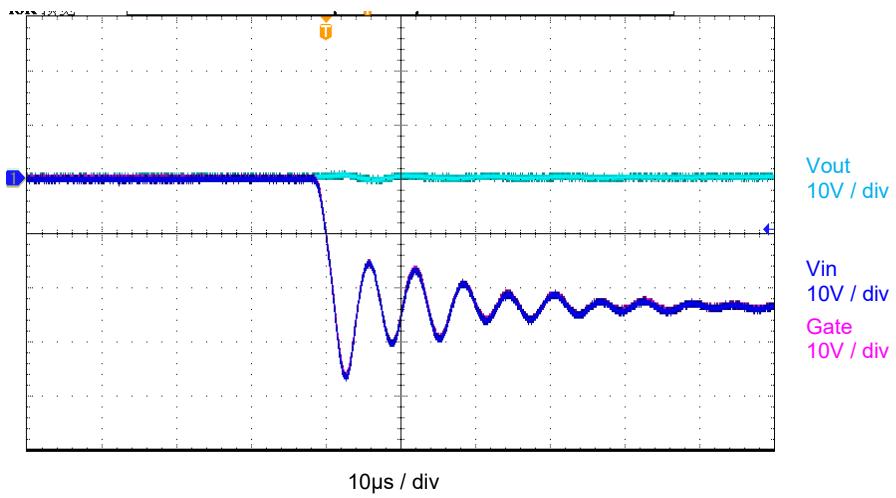

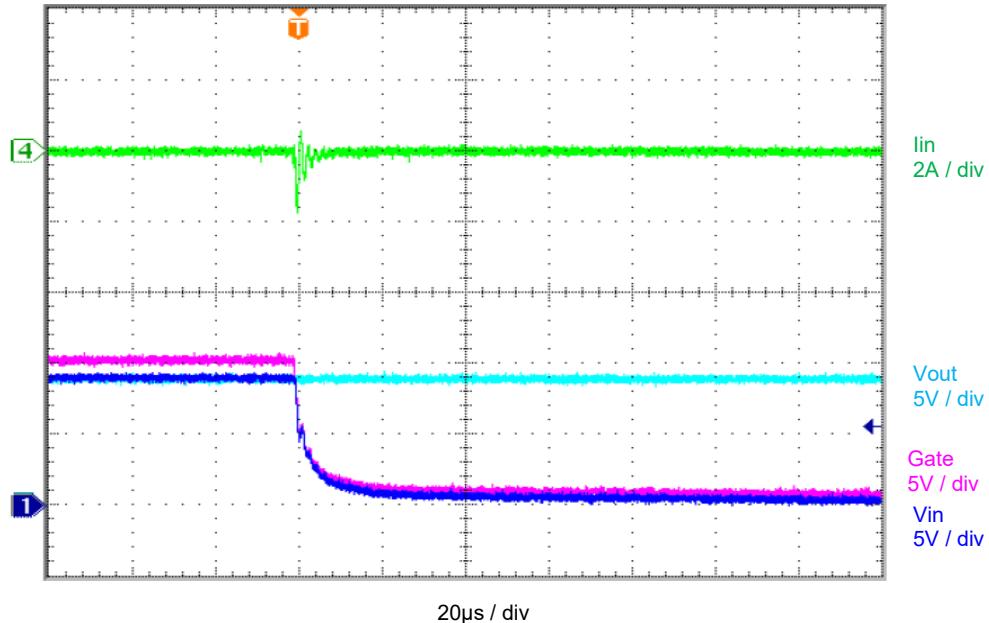

### Reverse Blocking

During input supply failure or micro-short conditions, huge reverse currents can flow in reverse, discharging the load capacitors used for VOUT holdup. KTS1900Q features a very fast reverse current comparator and a strong gate driver to pull down the gate and turn off the MOSFET. The internal reverse current comparator monitors the voltage across source and drain and if it exceeds the reverse current threshold, the GATE is pulled down to source with a fast response. Reverse current comparator delay, gate pulldown current and total gate capacitance determine how fast the MOSFET can be turned off. Figure 7 shows the fast reverse blocking when an input short happens. Once the MOSFET drain to source voltage exceeds the 15mV threshold the device is turned off. With the MOSFET off the voltage on the body diode increases well beyond the 15mV latching the circuit off. This is shown in Figure 7. The circuit will remain off until the source to drain voltage is above 40mV on the body diode. This prevents the holdup capacitors on VOUT from discharging into the shorted input rail. The IIN trace in Figure 7 shows very little reverse let through current. This keeps the power supplies on the back-end circuits stable.

**Figure 7. Reverse Blocking During Input Short**

### Reverse Polarity Protection

During maintenance of the battery or jump start of the vehicle, the battery can be connected in reverse polarity during reinstallation. If a battery is connected with a reversed polarity, the KTS1900Q is rapidly turned off to protect the downstream circuits and components from damage. Figure 8 and Figure 9 show the VOUT stability when a reverse battery connection of -12V or -24V is applied at its VIN.

**Figure 8. VIN Switch from 0V to -12V**

**Figure 9. VIN Switch from 0V to -24V**

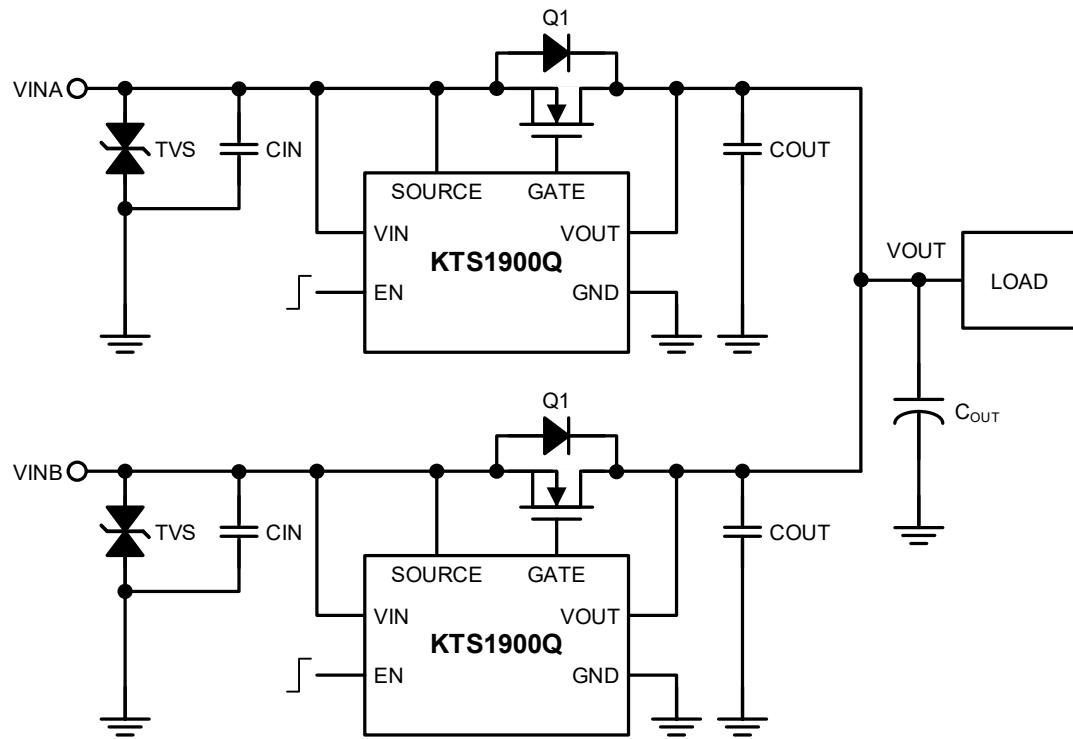

## OR-ing Power Supplies Application

In OR-ing power supplies application, two or more power supplies are needed to increase system redundancy or increase power capacity or both. Typically, in the N+1 configuration, more than one power supply source is paralleled with ideal diodes. A minimum 'N' supplies are required to power the load and additional supplies are added for redundancy in case of failed power supplies. The power supply with higher voltage provides most or all the current required by the load. To share loads equally, the power supplies DC set point is adjusted to match other units closely.

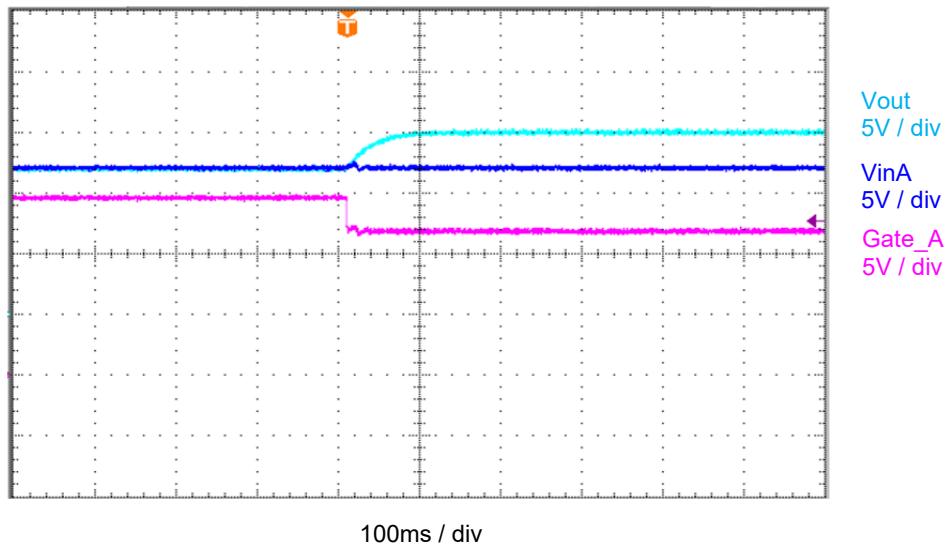

With external N-Channel MOSFETs, KTS1900Q can be used in an OR-ing solution as Figure 10 shows. When an input supply failure happens, the KTS1900Q quickly detects the reverse current and quickly pulls down the MOSFET gate, leaving the body diode of the MOSFET to block the reverse current flow. Redundant power supplies can then service the load.

**Figure 10. Typical OR-ing Application (Redundant Power Supplies)**

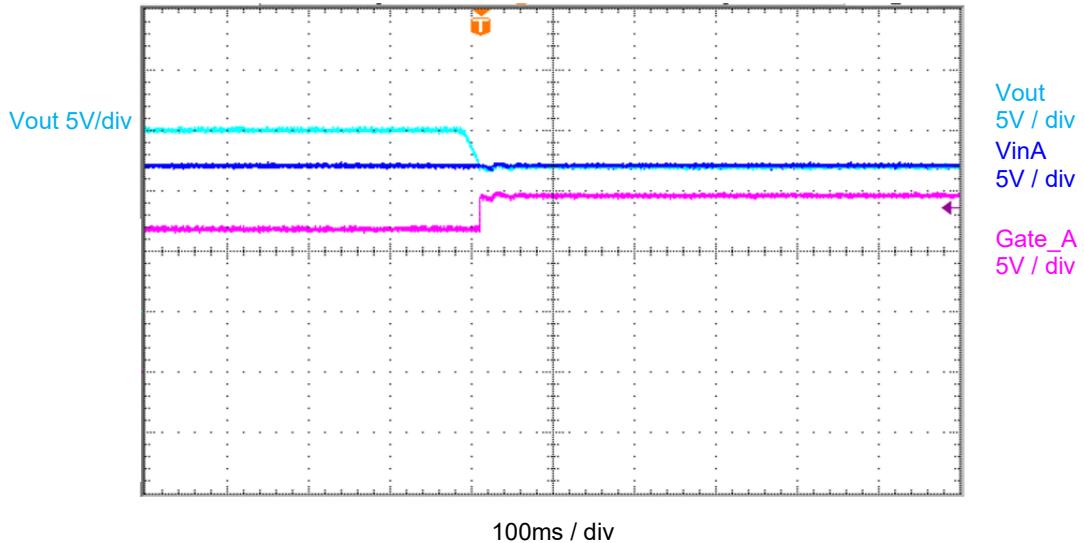

**Figure 11. OR-Ing Performance  $VINA = 12V$**

**Figure 12. OR-Ing Performance  $VINA = 12V$  turns off When  $VINB = 15V$**

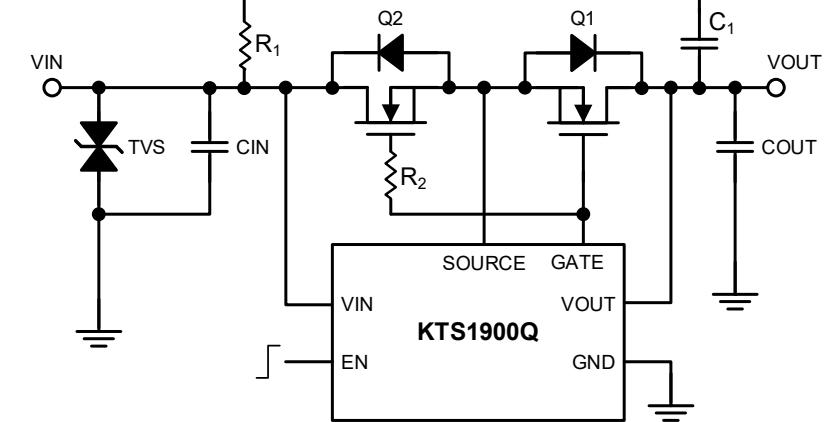

## Load Switch Configuration

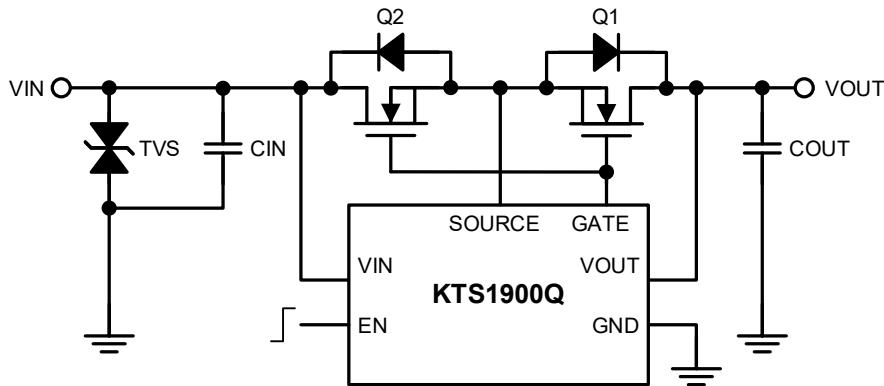

In load switch configuration, an additional MOSFET (Q2) can be used in KTS1900Q circuit to shut down the current to the load. In this case, Q1 acts as the ideal diode, while Q2 acts as a switch to control forward current flow. The circuit is shown in Figure 13. In addition, the back-to-back body diodes of two MOSFETs prohibit current flow, in both directions, when the MOSFETs are off. The turn on is inherently slow due to the low charge pump current of 15 $\mu$ A and the total gate capacitance.

**Figure 13. Load Switch Circuit Configuration with two MOSFETs**

## Operational Waveform

The normal turn on and off waveforms are shown in Figure 14 and Figure 15.

**Figure 14. Start up at 12V Vin, and 5A Load**

**Figure 15. Turn off at 12V Vin, and 5A Load**

### Reverse Polarity Protection

To test the dynamic input reverse protection a  $-12V$  or  $-24V$  source is connected to the input of the KTS1900Q. Figure 16 and Figure 17 show that the  $V_{OUT}$  remains at a constant  $0V$  in this situation. This test shows that the KTS1900Q can protect the load from negative input voltage.

**Figure 16. VIN Switch from 0V to -12V Reverse Protection**

**Figure 17. VIN Switch from 0V to -24V Reverse Protection**

### Input Voltage Short Protection

For input voltage short protection, VIN is switched from 12V to 0V, and VOUT keeps stable, with low reverse current as shown in Figure 18.

**Figure 18. VIN Switch from 12V to 0V Short Protection**

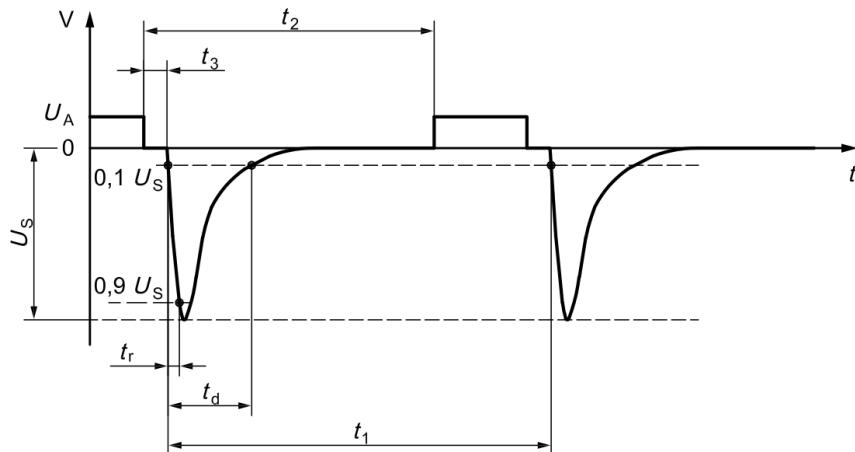

## ISO7637-2 Pulse Test

To ensure the compatibility of KTS1900Q to conducted electrical transients for automotive applications; ISO7637-2 Pulse test is used as the reference with 12V or 24V electrical systems. This test is a simulation of transients due to supply disconnection from inductive loads. The test waveform details, and the related parameters are shown in Figure 19 and Table 2.

During dynamic reverse polarity conditions specified in ISO 7637-2 for 12 volt systems, a negative voltage transient is applied at the 12V battery supply line (VIN). A -150 volt transient is generated from a  $10\Omega$  generator impedance for 2ms. The 24 Volt system is hit with a -600V,  $50\Omega$  generator for 1ms. When the ISO 7637-2 test pulse is applied to VIN, the load current starts to reverse quickly and tries to pull the VOUT negative. KTS1900Q detects the reverse current and turns OFF the MOSFET to block reverse current and prevent the VOUT from dropping. Downstream, bulk holdup capacitors, provide energy to the rest of the module during such transients. With a bi-direction TVS, the input voltage is clamped from exceeding the absolute maximum ratings of KTS1900Q and N-MOSFET.

**Figure 19. Test Pulse 1 Reference Waveform Details in ISO7637-2 Pulse Test Standard**

**Table 2. Parameters for Test Pulse 1 in ISO7637-2 Standard**

| Parameters | Nominal 12V System | Nominal 24V System |

|------------|--------------------|--------------------|

| $U_S$      | -75V to -150V      | -300V to -600V     |

| $t_d$      | 2ms                | 1ms                |

| $t_r$      | $\sim 1\mu s$      | $\sim 3\mu s$      |

| $t_1$      |                    | $\geq 0.5s$        |

| $t_2$      |                    | 200ns              |

| $t_3$      |                    | $< 100\mu s$       |

$t_1$  shall be chosen such that it is the minimum time for the DUT to be correctly initialized before the application of the next pulse.

$t_3$  is the smallest possible time necessary between the disconnection of the supply source and the application of the pulse.

Figure 20 shows the result of KTS1900Q for -600V transient pulse test that can be used as the reference for 24V system. The large current spike seen in the lin trace is the conduction of the TVS diode. The Vin trace shows the input voltage is clamped to -65 Volts during the lin current spike.

**Figure 20. -600V Transient Results Based on ISO7367-2 Pulse Test**

## Typical Application Circuits

| Ideal Diode Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BOM                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  <p>The schematic shows a TVS diode connected between VIN and ground. A capacitor CIN is connected between VIN and SOURCE. A MOSFET (Q1) is connected between SOURCE and VOUT. The MOSFET's gate is connected to VOUT through a diode and to GND through a resistor. The KTS1900Q IC is connected between VIN and VOUT, with its EN pin connected to ground. A capacitor COUT is connected between VOUT and GND.</p>                                                                                                                                                       | <p>TVS = SMBJ33CA-13-F<br/>     DIODE, TVS, Bi, 33V, SMB<br/>     Q1 = DMT6007LFG-13<br/>     MOSFET, N-CH, 60V, 15A<br/>     CIN = 2.2μF, 100V, ±10%, X7R, 1210<br/>     COUT = 2.2μF, 100V, ±10%, X7R, 1210</p>                                                                                                                            |

| Load Switch Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BOM                                                                                                                                                                                                                                                                                                                                          |

|  <p>The schematic shows a TVS diode connected between VIN and ground. A resistor R1 is connected between VIN and SOURCE. A resistor R2 is connected between SOURCE and GND. A MOSFET (Q2) is connected between VIN and SOURCE. A MOSFET (Q1) is connected between SOURCE and VOUT. The MOSFETs' gates are connected to VOUT through diodes and to GND through resistors. The KTS1900Q IC is connected between VIN and VOUT, with its EN pin connected to ground. A capacitor C1 is connected between VOUT and GND. A capacitor COUT is connected between VOUT and GND.</p> | <p>TVS = SMBJ33CA-13-F<br/>     DIODE, TVS, Bi, 33V, SMB<br/>     Q1 and Q2 = IPB027N10N3GATMA1<br/>     MOSFET, N-CH, 100V 120A<br/>     CIN = 2.2μF, 100V, ±10%, X7R, 1210<br/>     COUT = 2.2μF, 100V, ±10%, X7R, 1210<br/>     C1 = 10nF, 500V, ±20%, X7R, 1206<br/>     R1 = 100Ω, 1/2W, 5%, 1210<br/>     R2 = 10Ω, 1/8W, 5%, 0805</p> |

## Recommended PCB Layout

The recommended KTS1900 PCB layout is optimized for low EMI, and good performance and follows the below PCB layout recommendations.

1. Connect a 2.2μF capacitor CIN as close as possible to the VIN and GND pins using wide metal traces and ground plane.

2. Connect the VIN, SOURCE and VOUT pins as close as possible to the MOSFET source and drain pins. With short and wide traces to minimize resistive losses.

3. Place surge suppressors and transient protection components as close as possible to the input of KTS1900Q with short lead lengths.

4. Connect a 2.2μF capacitor, COUT, as close as possible to the GND and VOUT pins.

5. Check the creepage and clearance details and guidelines to determine spacing between high voltage (VIN) and other nearby traces.

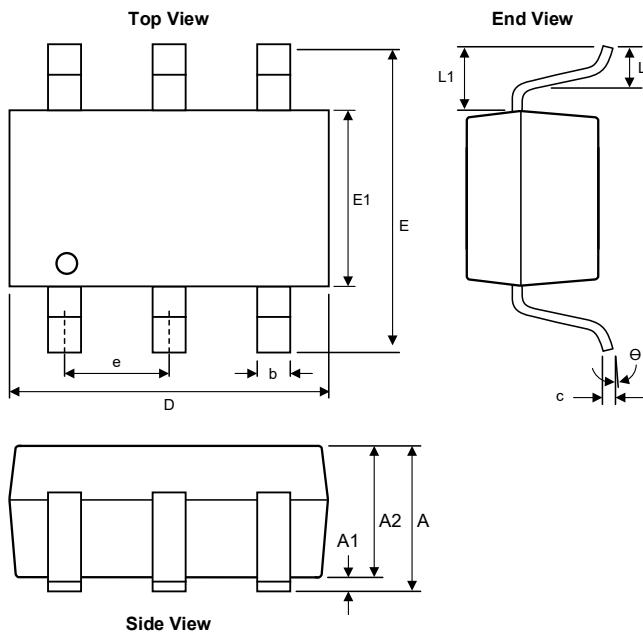

## Packaging Information

SOT23-6 (2.90mm x 1.60mm x 1.45mm)

| Dimension | mm       |      |      |

|-----------|----------|------|------|

|           | Min.     | Typ. | Max. |

| A         | —        | —    | 1.45 |

| A1        | 0        | —    | 0.15 |

| A2        | 0.90     | 1.15 | 1.30 |

| b         | 0.30     | —    | 0.50 |

| c         | 0.08     | —    | 0.22 |

| D         | 2.90 BSC |      |      |

| E         | 2.80 BSC |      |      |

| E1        | 1.60BSC  |      |      |

| e         | 0.95 BSC |      |      |

| L         | 0.30     | 0.45 | 0.60 |

| L1        | 0.60 BSC |      |      |

| θ°        | 0        | 4    | 8    |

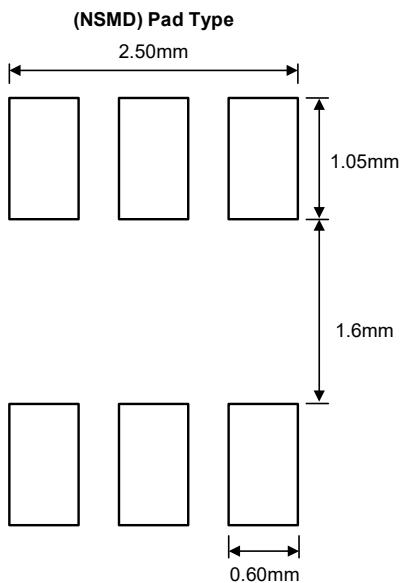

## Recommended Footprint

Kinetic Technologies cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Kinetic Technologies product. No intellectual property or circuit patent licenses are implied. Kinetic Technologies reserves the right to change the circuitry and specifications without notice at any time.