## Description

The AP74701Q is an automotive AEC-Q100 qualified ideal diode controller, which operates in conjunction with an external n-channel MOSFET as an ideal diode for minimum loss reverse-polarity protection with a 20mV forward voltage drop. The AP74701Q is suitable for input protection of 12V automotive systems. The 3.2V input-voltage support is particularly well suited for severe cold crank requirements in automotive systems.

The device controls the GATE of the MOSFET to regulate the forward voltage drop at 20mV. The regulation scheme enables immediate turn-off of the MOSFET during a reverse current event and ensures zero DC reverse current flow. Immediate response (< 0.75µs) to reverse current blocking makes the device suitable for systems with output voltage hold-up requirements during ISO7637 pulse testing as well as power fail and input micro-short conditions. The AP74701Q has a built-in Vds clamp feature which enables users to achieve "TVS Less" input polarity protection solution and save on average a typical 60% of PCB space in constrained automotive systems.

The AP74701Q controller provides a charge pump gate drive for an external n-channel MOSFET. With the enable pin low, the controller is off and draws approximately 1µA of current.

The AP74701Q is available in the SOT28 package.

## Applications

- Automotive infotainment systems – head units, telematics, control units

- Automotive ADAS systems - cameras

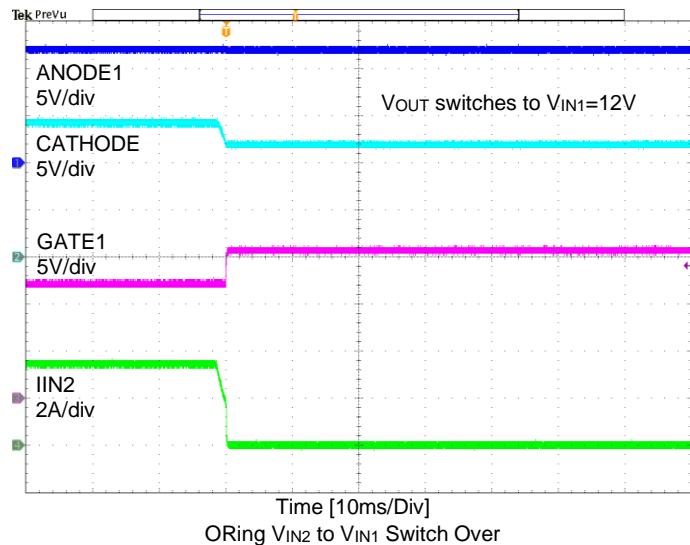

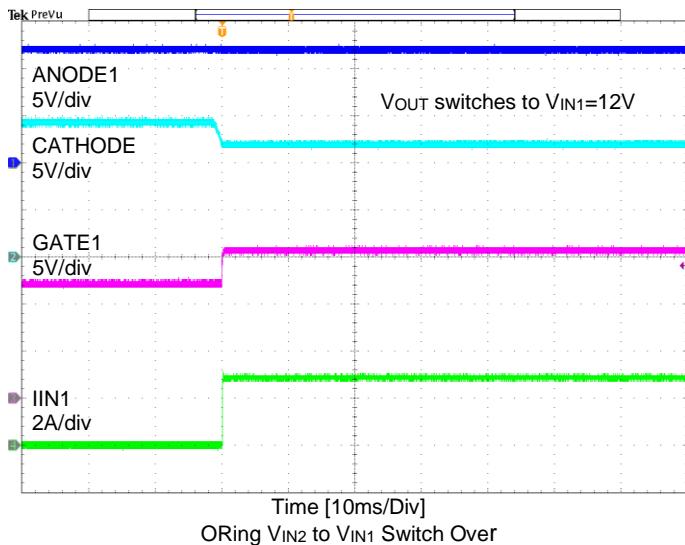

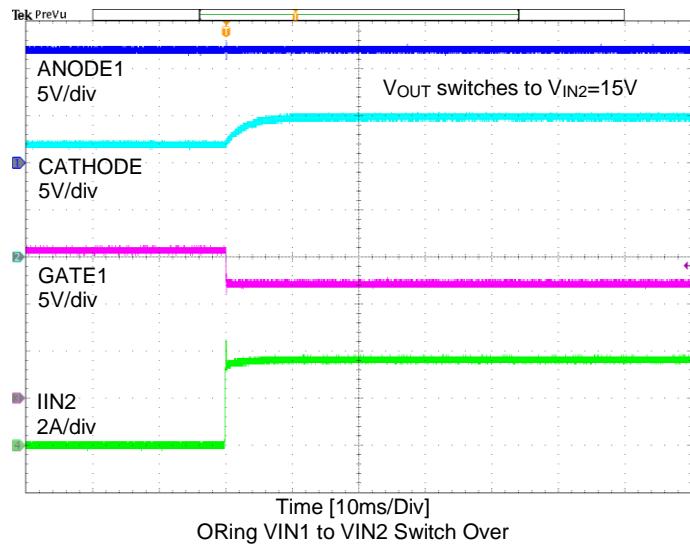

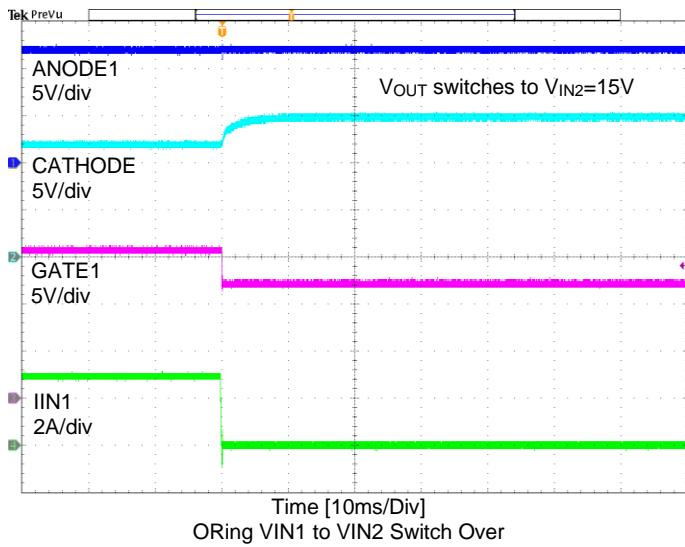

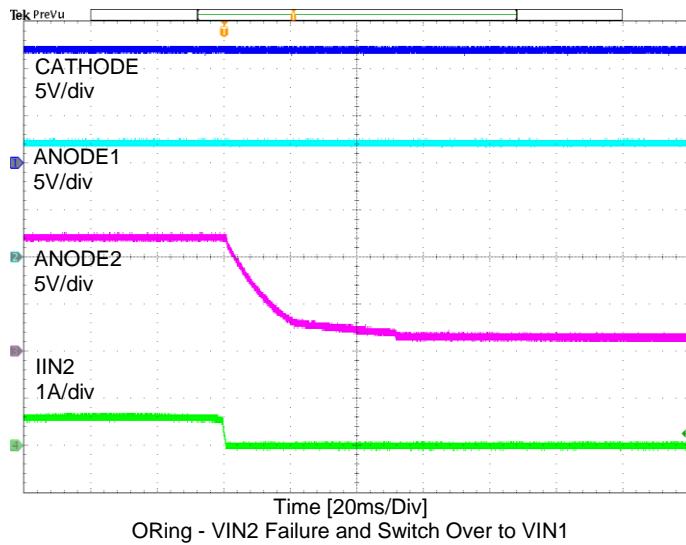

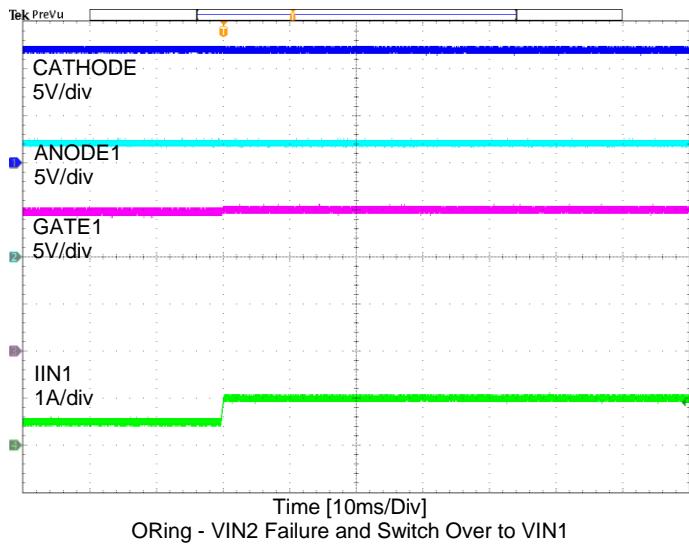

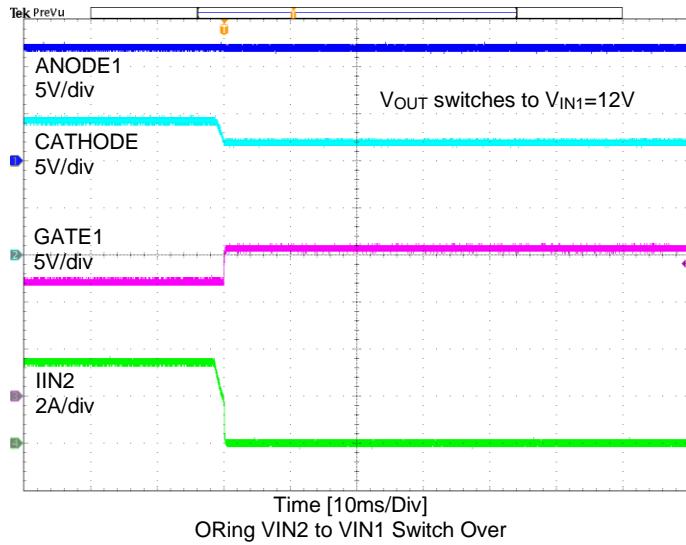

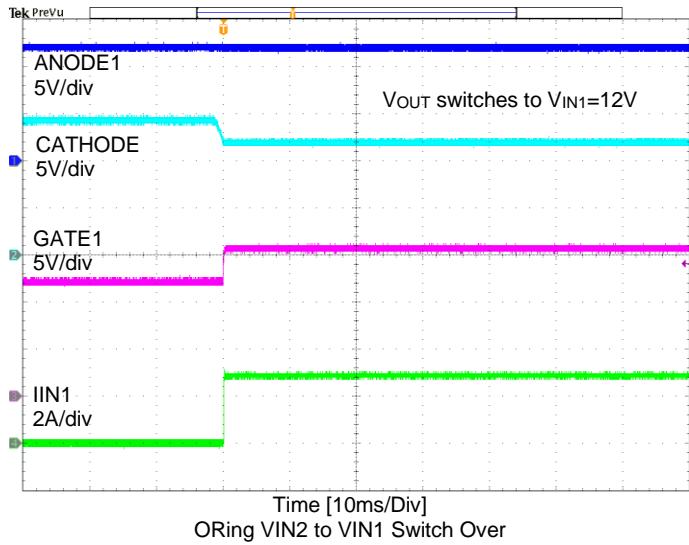

- Active power ORing for redundant power

- Power of industrial automation such as PLC

- Enterprise power supplies

- Input Voltage Ranges from 3.2V to 65V (3.9V Startup)

- 33V Reverse-Battery Voltage

- Charge Pump for External N-Channel Power MOSFET

- 20mV ANODE to CATHODE Forward Voltage Drop Control

- Low Shutdown Current of 1µA when Disabled

- Low Quiescent Current of 80µA when Enabled

- Fast Reverse Current Block Response Time of < 0.75µs

- 2.3A Peak Gate Turn-Off Current

- Active High Operation

- Integrated Battery Voltage Monitoring Switch (SW)

- Meet Automotive ISO7637 Transient Requirements Without Additional Input TVS Diodes (TVS Less)

- ESD Protection: 2kV of HBM and 750V of CDM

- AEC-Q100 Qualification Compliance with Device Temperature Grade 1 (-40°C to +125°C Ambient Operating Temperature Range)

- 8-Pin SOT28 Package

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)**

- Halogen and Antimony Free. "Green" Device (Note 3)**

- The AP74701Q is suitable for automotive applications requiring specific change control; this part is AEC-Q100 qualified, PPAP capable, and manufactured in IATF 16949 certified facilities.**

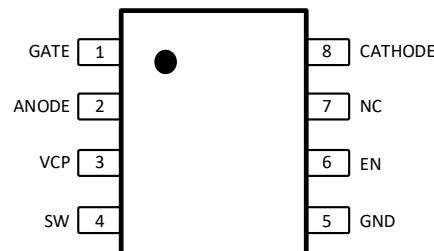

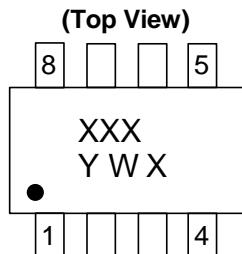

## Pin Assignments

(Top View)

SOT28

## Features

Notes:

- No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- See <https://www.diodes.com/quality/lead-free/> for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

---

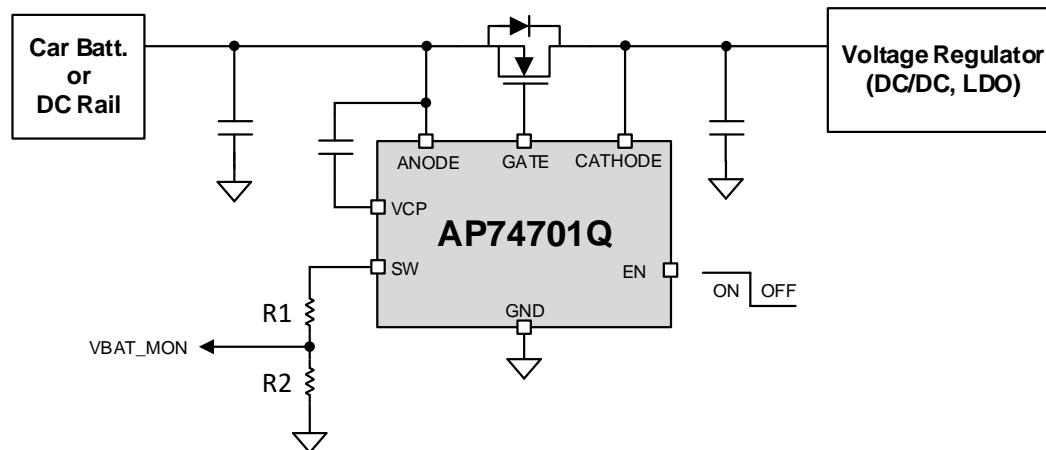

**Typical Applications Circuit**

---

---

**Pin Descriptions**

---

| Pin Name | Pin Number | Function                                                                                                                                                                                                                                                                                                                           |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GATE     | 1          | Gate driver out pin. Connects to gate of external nMOSFET                                                                                                                                                                                                                                                                          |

| ANODE    | 2          | Input supply and ANODE of Ideal diode. Connects to the source of external nMOSFET                                                                                                                                                                                                                                                  |

| VCP      | 3          | Charge pump voltage output pin. Connect to external capacitor.                                                                                                                                                                                                                                                                     |

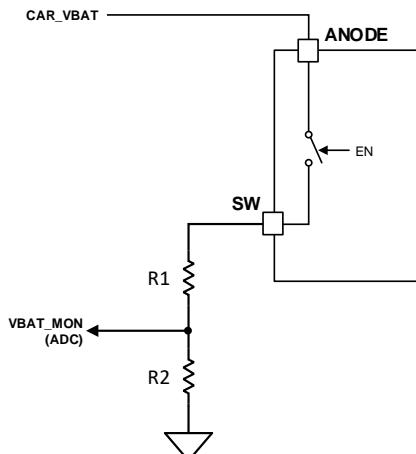

| SW       | 4          | Voltage sensing switch terminal. Internal switch is ON connecting ANODE to SW when EN is high. A resistor divider from this pin to GND can be used to for adjustment for ADC full-scale range. When EN is low, the switch is OFF disconnecting the resistor divider from the battery line thereby eliminating the leakage current. |

| GND      | 5          | Ground pin                                                                                                                                                                                                                                                                                                                         |

| EN       | 6          | Enable pin. Active high                                                                                                                                                                                                                                                                                                            |

| NC       | 7          | No Connect. Leave this pin float                                                                                                                                                                                                                                                                                                   |

| CATHODE  | 8          | CATHODE pin. Connects to the drain of external nMOSFET                                                                                                                                                                                                                                                                             |

---

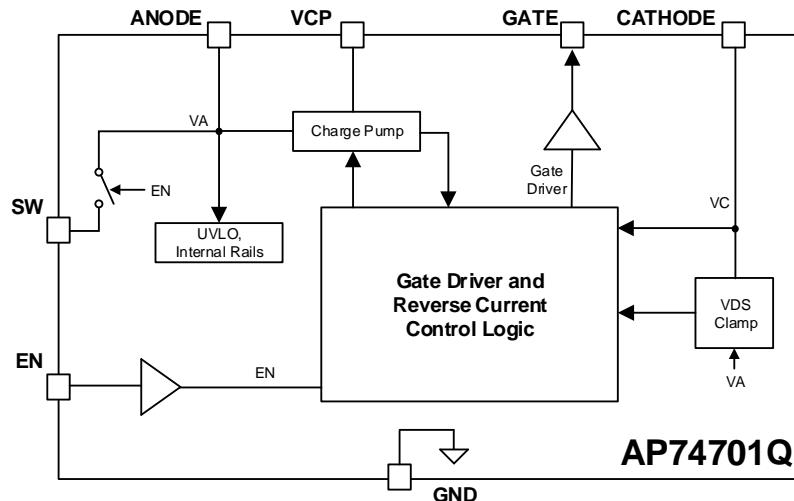

**Functional Block Diagram**

---

Absolute Maximum Ratings (@ $T_A = +25^\circ\text{C}$ , unless otherwise specified.) (Note 4)

| Symbol                     | Parameter                                             | Ratings                                                 | Unit                      |

|----------------------------|-------------------------------------------------------|---------------------------------------------------------|---------------------------|

| ESD HBM                    | Human Body ESD Protection                             | $\pm 2$                                                 | kV                        |

| ESD CDM                    | Charged Device Model ESD Protection                   | $\pm 750$                                               | V                         |

| ANODE to GND               | Input Voltage at ANODE                                | -( $V_{\text{CLAMP}} - 1$ ) to +65                      | V                         |

| SW and EN to GND           | Voltage at SW and EN, $V_{\text{ANODE}} > 0\text{V}$  | -0.3 to +65                                             | V                         |

| EN to GND                  | Voltage at EN, $V_{\text{ANODE}} \leq 0\text{V}$      | $V_{\text{ANODE}} \text{ to } (V_{\text{ANODE}} + 65)$  | V                         |

| SW to GND                  | Voltage at SW, $V_{\text{ANODE}} \leq 0\text{V}$      | $V_{\text{ANODE}} \text{ to } (V_{\text{ANODE}} + 0.3)$ | V                         |

| $I_{\text{SW}}$            | SW Switch Current                                     | -1 to 3mA                                               | A                         |

| GATE to ANODE              | Gate to Anode Voltage                                 | -0.3 to +15                                             | V                         |

| VCP to ANODE               | Charge Pump Voltage                                   | -0.3 to +15                                             | V                         |

| CATHODE to ANODE           | CATHODE to ANODE Voltage                              | -5 to $V_{\text{CLAMP}}$                                | V                         |

| $T_{\text{J(max)}}$        | Maximum Junction Temperature                          | -40 to +150                                             | $^\circ\text{C}$          |

| $T_{\text{STG}}$           | Storage Temperature                                   | -40 to +150                                             | $^\circ\text{C}$          |

| $R_{\theta\text{JA}}$      | Junction-to-Ambient Thermal Resistance (Note 5)       | 176.9                                                   | $^\circ\text{C}/\text{W}$ |

| $R_{\theta\text{JC(top)}}$ | Junction-to-Case (Top) Thermal Resistance (Note 5)    | 122.0                                                   | $^\circ\text{C}/\text{W}$ |

| $R_{\theta\text{JB}}$      | Junction-to-Board Thermal Resistance (Note 5)         | 46.0                                                    | $^\circ\text{C}/\text{W}$ |

| $\Psi_{\text{JT}}$         | Junction-to-Top Characterization Parameter (Note 5)   | 10.2                                                    | $^\circ\text{C}/\text{W}$ |

| $\Psi_{\text{JB}}$         | Junction-to-Board Characterization Parameter (Note 5) | 44.9                                                    | $^\circ\text{C}/\text{W}$ |

Notes:

- Stresses greater than the *Absolute Maximum Ratings* specified above can cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions exceeding those indicated in this specification is not implied. Device reliability can be affected by exposure to absolute maximum rating conditions for extended periods of time.

- $R_{\theta\text{JA}}$  and  $R_{\theta\text{JC}}$  are measured at  $T_A = +25^\circ\text{C}$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.

Recommended Operating Conditions (@ $T_A = +25^\circ\text{C}$ , unless otherwise specified.)

| Symbol                              | Parameter                            | Min                  | Max  | Unit             |

|-------------------------------------|--------------------------------------|----------------------|------|------------------|

| ANODE to GND                        | Input Voltage at ANODE               | -33                  | +60  | V                |

| CATHODE to GND                      | Input Voltage at CATHODE             | —                    | +60  | V                |

| EN to GND                           | Voltage at Enable Pin                | -33                  | +60  | V                |

| ANODE to CATHODE                    | ANODE to CATHODE Voltage             | - $V_{\text{CLAMP}}$ | 5    | V                |

| GATE to ANODE                       | Gate to Anode Voltage                | 0                    | +15  | V                |

| VCP to ANODE                        | Charge Pump Voltage                  | 0                    | +15  | V                |

| CATHODE to ANODE                    | CATHODE to ANODE Voltage             | —                    | 70   | V                |

| Anode Cap                           | Input Capacitor (Note 6)             | 0.1                  | 1    | $\mu\text{F}$    |

| VCP to Anode Cap                    | Charge Pump Cap (Note 6)             | 0.1                  | —    | $\mu\text{F}$    |

| External MOSFET $V_{\text{GS max}}$ | Gate to Anode (Note 6)               | 15                   | —    | V                |

| $T_{\text{J}}$                      | Operating Junction Temperature Range | -40                  | +125 | $^\circ\text{C}$ |

Note: 6. Refer to the typical application circuit.

**Electrical Characteristics** ( $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$ ,  $V_{\text{ANODE}} = 12\text{V}$ ,  $C_{\text{VCP}} = 0.1\mu\text{F}$ ,  $V_{\text{EN}} = 3.3\text{V}$ , typical values are at  $T_J = +25^\circ\text{C}$ , unless otherwise specified.)

| Symbol                                        | Parameter                                               | Conditions                                                                                                      | Min  | Typ  | Max  | Unit            |

|-----------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|------|------|-----------------|

| <b>VANODE Supply</b>                          |                                                         |                                                                                                                 |      |      |      |                 |

| VCLAMP                                        | V <sub>CATHODE</sub> – V <sub>ANODE</sub> Clamp Voltage | —                                                                                                               | 34   | —    | 43   | V               |

| V <sub>ANODE</sub>                            | Operating Input Voltage                                 | —                                                                                                               | 4    | —    | 60   | V               |

| V <sub>UVLO_ANODE</sub>                       | ANODE UVLO Rising Threshold                             | —                                                                                                               | —    | —    | 3.9  | V               |

|                                               | ANODE UVLO Falling Threshold                            | —                                                                                                               | 2.2  | 2.8  | 3.1  | V               |

| V <sub>UVLO_ANODE_HYS</sub>                   | ANODE UVLO Hysteresis                                   | —                                                                                                               | 440  | —    | 800  | mV              |

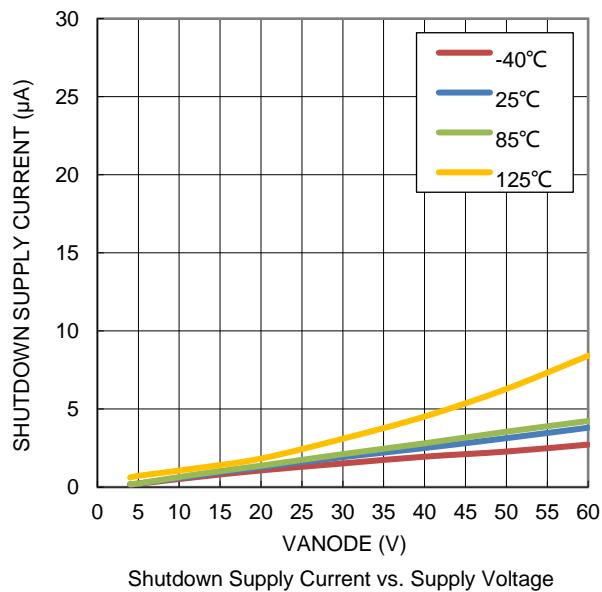

| I <sub>ANODE_OFF</sub>                        | Shutdown Supply Current                                 | $V_{\text{EN}} = 0\text{V}$                                                                                     | —    | 0.6  | 1.5  | $\mu\text{A}$   |

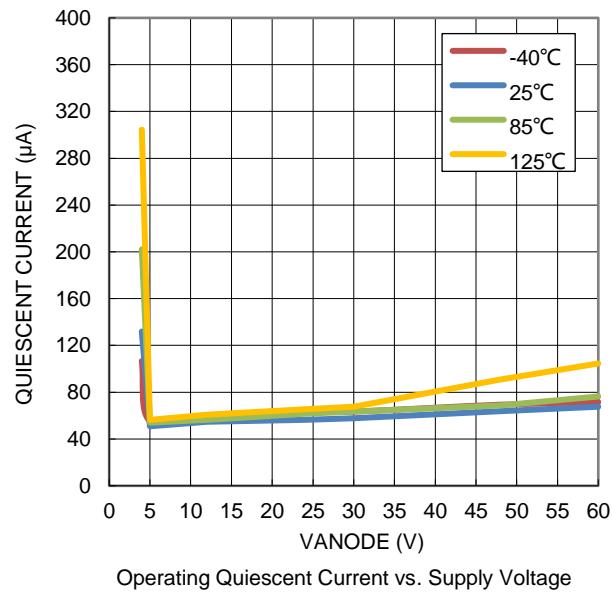

| I <sub>ANODE_Q</sub>                          | Operating Quiescent Current                             | —                                                                                                               | —    | 65   | 100  | $\mu\text{A}$   |

| <b>EN Input</b>                               |                                                         |                                                                                                                 |      |      |      |                 |

| V <sub>IIL_EN</sub>                           | Enable Input Low Threshold                              | —                                                                                                               | 0.5  | 0.9  | 1.22 | V               |

| V <sub>IIL_EN</sub>                           | Enable Input High Threshold                             | —                                                                                                               | 1.06 | 2    | 2.6  | V               |

| V <sub>hys_EN</sub>                           | Enable Hysteresis                                       | —                                                                                                               | 0.52 | —    | 1.35 | V               |

| I <sub>EN</sub>                               | Enable Sink Current                                     | $V_{\text{EN}} = 12\text{V}$                                                                                    | —    | 3    | 5    | $\mu\text{A}$   |

| <b>VANODE and VCATHODE by Operation Modes</b> |                                                         |                                                                                                                 |      |      |      |                 |

| V <sub>ACTIVE_REG</sub>                       | Regulated Forward Threshold                             | —                                                                                                               | 13   | 24   | 34   | mV              |

| V <sub>ACTIVE_FULL</sub>                      | Threshold for Full Conduction Mode                      | —                                                                                                               | 40   | 55   | 67   | mV              |

| V <sub>ACTIVE_REV</sub>                       | Threshold for Reverse Current Blocking                  | —                                                                                                               | -17  | -11  | -2   | mV              |

| G <sub>m</sub>                                | Regulation Error AMP Transconductance (Note 7)          | —                                                                                                               | 1200 | 1800 | 3100 | $\mu\text{A/V}$ |

| <b>SW Switch</b>                              |                                                         |                                                                                                                 |      |      |      |                 |

| R <sub>SW</sub>                               | Resistance of Battery Sensing Isolation Switch          | $4\text{V} < V_{\text{ANODE}} \leq 60\text{V}$                                                                  | 25   | 46   | 90   | $\Omega$        |

| <b>Gate Drive</b>                             |                                                         |                                                                                                                 |      |      |      |                 |

| I <sub>GATE</sub>                             | Peak Source Current                                     | $V_{\text{ANODE}} - V_{\text{CATHODE}} = 100\text{mV}$ ,<br>$V_{\text{GATE}} - V_{\text{ANODE}} = 5\text{V}$    | 3    | 11   | —    | mA              |

|                                               | Peak Sink Current                                       | $V_{\text{ANODE}} - V_{\text{CATHODE}} = -20\text{mV}$ ,<br>$V_{\text{GATE}} - V_{\text{ANODE}} = 5\text{V}$    | —    | 2370 | —    | mA              |

|                                               | Regulation Max Sink Current                             | $V_{\text{ANODE}} - V_{\text{CATHODE}} = 0\text{V}$ ,<br>$V_{\text{GATE}} - V_{\text{ANODE}} = 5\text{V}$       | 2    | 16   | —    | $\mu\text{A}$   |

| R <sub>DIS</sub>                              | Discharge Switch Resistance                             | $V_{\text{ANODE}} - V_{\text{CATHODE}} = -20\text{mV}$ ,<br>$V_{\text{GATE}} - V_{\text{ANODE}} = 100\text{mV}$ | 0.4  | —    | 2    | $\Omega$        |

Note: 7. Parameter guaranteed by design and characterization

**Electrical Characteristics** ( $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$ ,  $V_{\text{ANODE}} = 12\text{V}$ ,  $C_{\text{VCP}} = 0.1\mu\text{F}$ ,  $V_{\text{EN}} = 3.3\text{V}$ , typical values are at  $T_J = +25^\circ\text{C}$ , unless otherwise specified.) (continued)

| Symbol                                | Parameter                                                          | Conditions                                                                      | Min  | Typ  | Max | Unit |

|---------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------|------|------|-----|------|

| <b>Charge Pump</b>                    |                                                                    |                                                                                 |      |      |     |      |

| I <sub>VCP</sub>                      | Charge Pump Source Current (Charge Pump On)                        | V <sub>VCP</sub> – V <sub>ANODE</sub> = 7V                                      | 160  | 220  | 600 | µA   |

|                                       | Charge Pump Sink Current (Charge Pump Off)                         | V <sub>VCP</sub> – V <sub>ANODE</sub> = 14V                                     | —    | 5    | 10  | µA   |

| V <sub>VCP</sub> – V <sub>ANODE</sub> | Charge Pump Voltage at V <sub>ANODE</sub> = 3.2V                   | I <sub>VCP</sub> ≤ 30µA                                                         | 8    | —    | —   | V    |

|                                       | Charge Pump Turn-On Voltage                                        | —                                                                               | 10.3 | 11.6 | 13  | V    |

|                                       | Charge Pump Turn-Off Voltage                                       | —                                                                               | 11   | 13   | 14  | V    |

|                                       | Charge Pump Enable Comparator Hysteresis                           | —                                                                               | 0.4  | 1    | 1.8 | V    |

| V <sub>VCP_UVLO</sub>                 | V <sub>VCP</sub> – V <sub>ANODE</sub> UV Release at Rising Edge    | V <sub>ANODE</sub> – V <sub>CATHODE</sub> = 100mV                               | 5.41 | 6.5  | 7.5 | V    |

|                                       | V <sub>VCP</sub> – V <sub>ANODE</sub> UV Threshold at Falling Edge | V <sub>ANODE</sub> – V <sub>CATHODE</sub> = 100mV                               | 4.21 | 5.3  | 6   | V    |

| <b>CATHODE</b>                        |                                                                    |                                                                                 |      |      |     |      |

| I <sub>CATHODE</sub>                  | CATHODE Sink Current                                               | V <sub>ANODE</sub> = 12V,<br>V <sub>ANODE</sub> – V <sub>CATHODE</sub> = -100mV | —    | 1.7  | 2   | µA   |

|                                       |                                                                    | V <sub>ANODE</sub> – V <sub>CATHODE</sub> = 100mV                               | —    | 1.2  | 2.5 | µA   |

|                                       |                                                                    | V <sub>ANODE</sub> = -14V, V <sub>DRAIN</sub> = 0V                              | —    | —    | 2   | µA   |

|                                       |                                                                    | V <sub>ANODE</sub> = -16V, V <sub>CATHODE</sub> = 16V                           | —    | —    | 24  | µA   |

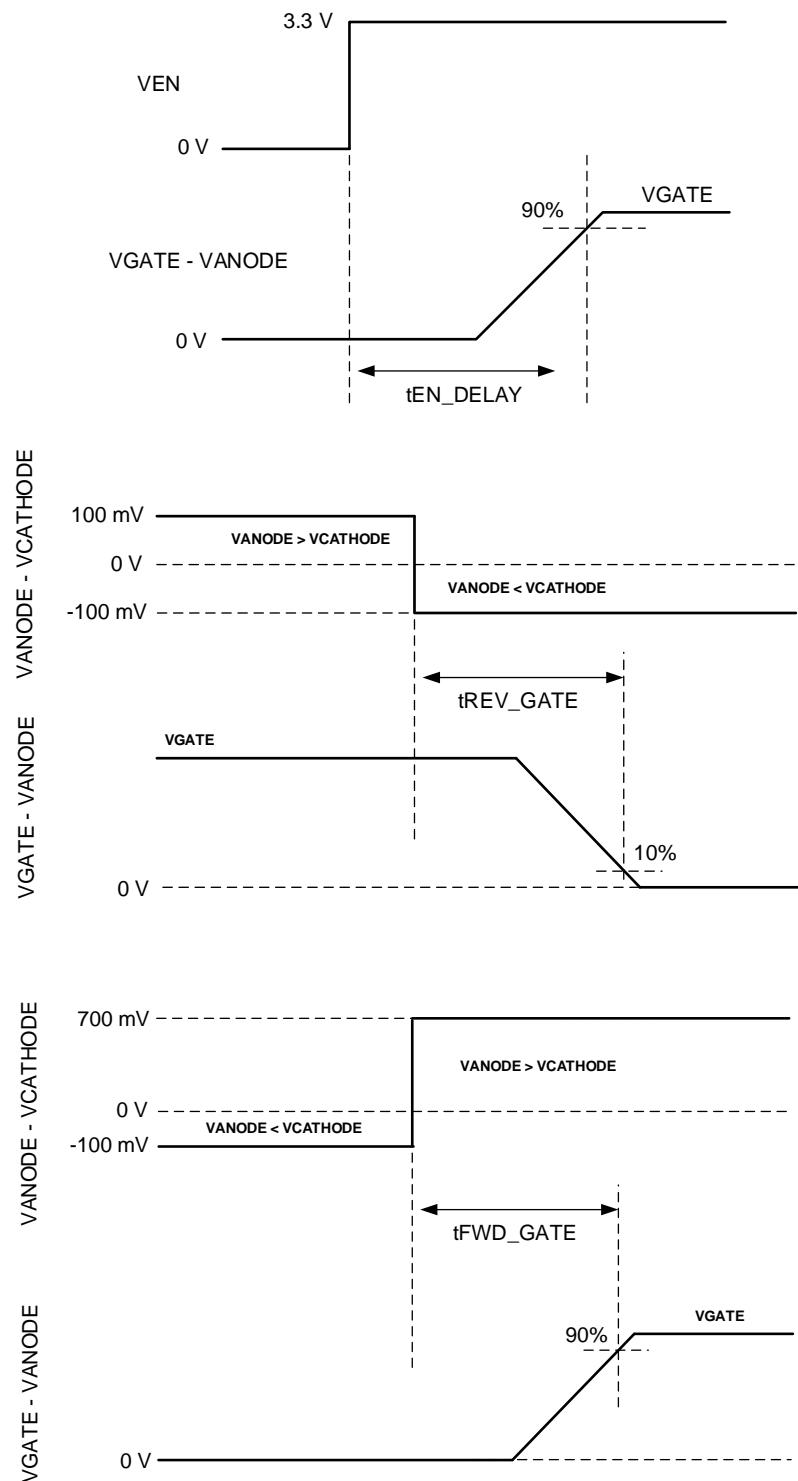

**Switching Characteristics** ( $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$ ,  $V_{\text{ANODE}} = 12\text{V}$ ,  $C_{\text{VCP}} = 0.1\mu\text{F}$ ,  $V_{\text{EN}} = 3.3\text{V}$ , typical values are at  $T_J = +25^\circ\text{C}$ , unless otherwise specified.)

| Symbol                           | Parameter                                                           | Conditions                                                  | Min | Typ  | Max  | Unit |

|----------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------|-----|------|------|------|

| <b>Switching Characteristics</b> |                                                                     |                                                             |     |      |      |      |

| t <sub>EN_DELAY</sub>            | Delay from Enable Switching High to Gate Turn On                    | V <sub>VCP</sub> > V <sub>VCP_UVLO</sub>                    | —   | 75   | 110  | µs   |

| t <sub>REV_GATE</sub>            | Gate Turn-Off Time when Reverse Voltage is Detected (Note 8)        | V <sub>ANODE</sub> – V <sub>CATHODE</sub> = 100mV to -100mV | —   | 0.45 | 0.75 | µs   |

| t <sub>FWD_GATE</sub>            | Gate Turn-On Time when Forward Conducting Voltage Detected (Note 8) | V <sub>ANODE</sub> – V <sub>CATHODE</sub> = -100mV to 700mV | —   | 1.4  | 2.6  | µs   |

Note: 8. Parameter guaranteed by bench characterization

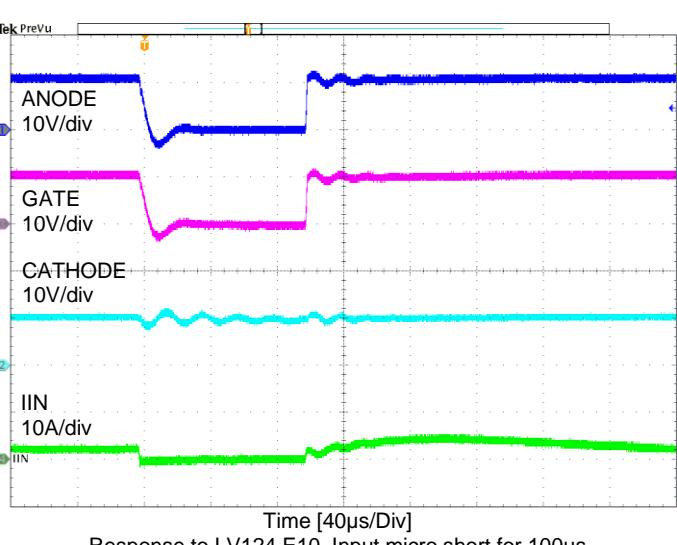

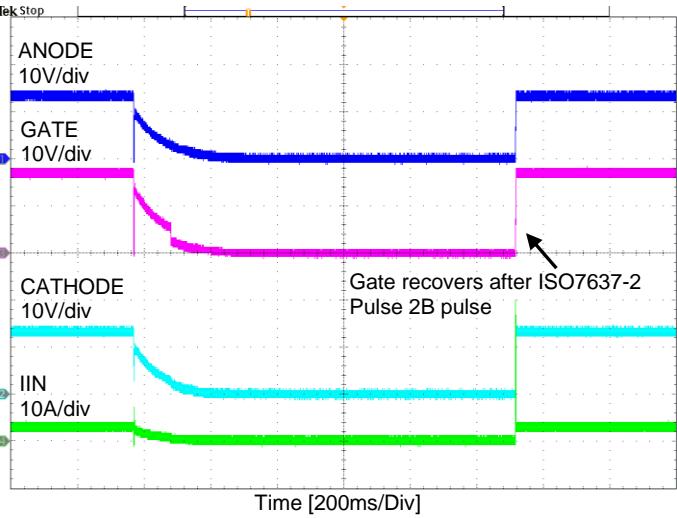

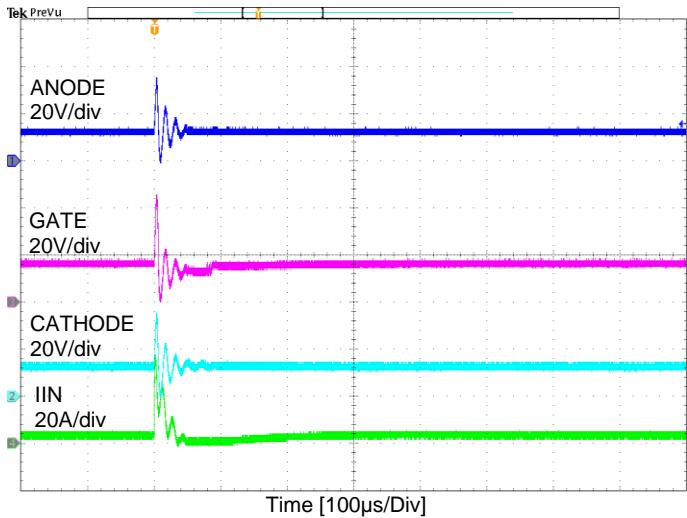

## Switching Waveforms

## Detailed Description

### Overview

The AP74701Q ideal diode controller has all the features necessary to implement an efficient and fast reverse-polarity protection circuit while minimizing the number of external components. This ideal diode controller is paired with an external n-channel MOSFET to replace other reverse-polarity schemes such as a p-channel MOSFET or a Schottky diode. An internal charge pump is used to drive the external n-channel MOSFET to a maximum gate drive voltage of approximately 12V. The voltage drop across the MOSFET is continuously monitored between the ANODE and CATHODE pins, and the GATE to ANODE voltage is adjusted as needed to regulate the forward voltage drop at 20mV. This closed loop regulation scheme enables graceful turn-off of the MOSFET during a reverse current event and ensures zero DC reverse current flow. A fast reverse current condition is detected when the voltage across ANODE and CATHODE pins reduces below -11mV, resulting in the GATE pin being internally connected to the ANODE pin turning off the external n-channel MOSFET, and using the body diode to block any of the reverse current. An enable pin, EN, is available to place the AP74701Q in shutdown mode disabling the n-channel MOSFET and minimizing the quiescent current. When the device is enabled, an internal switch between SW and ANODE pin enables input-voltage monitoring using an external resistor divider connected to SW pin. The device integrates V<sub>DS</sub> clamp feature which enables input "TVS Less" reverse-polarity protection.

### Input Voltage

The ANODE pin is used to power the AP74701Q's internal circuitry, typically drawing 80 $\mu$ A when enabled and 1 $\mu$ A when disabled. If the ANODE pin voltage is greater than the POR rising threshold, then AP74701Q operates in either shutdown mode or conduction mode in accordance with the EN pin voltage. The voltage from ANODE to GND is designed to vary from 65V to -33V, allowing the AP74701Q to withstand negative voltage input.

### Charge Pump

The charge pump supplies the voltage necessary to drive the external n-channel MOSFET. An external charge pump capacitor is placed between VCAP and ANODE pins to provide energy to turn on the external MOSFET. In order for the charge pump to supply current to the external capacitor the EN pin voltage must be above the specified input high threshold, V(EN\_IH). When enabled, the charge pump sources a charging current of 300 $\mu$ A typical. If EN pins is pulled low, then the charge pump remains disabled. To ensure that the external MOSFET can be driven above its specified threshold voltage, the VCAP to ANODE voltage must be above the undervoltage lockout threshold, typically 6.5V, before the internal gate driver is enabled. The initial gate driver enable delay can be calculated by following equation:

$$T_{DRV\_EN} = 75\mu\text{s} + C_{VCP} \times \frac{V_{VCP\_UVLO}}{300\mu\text{A}}$$

where,

C<sub>VCP</sub> is the charge pump capacitance connected across ANODE and VCP pins

V<sub>VCP\_UVLO</sub> = 6.5V (typical)

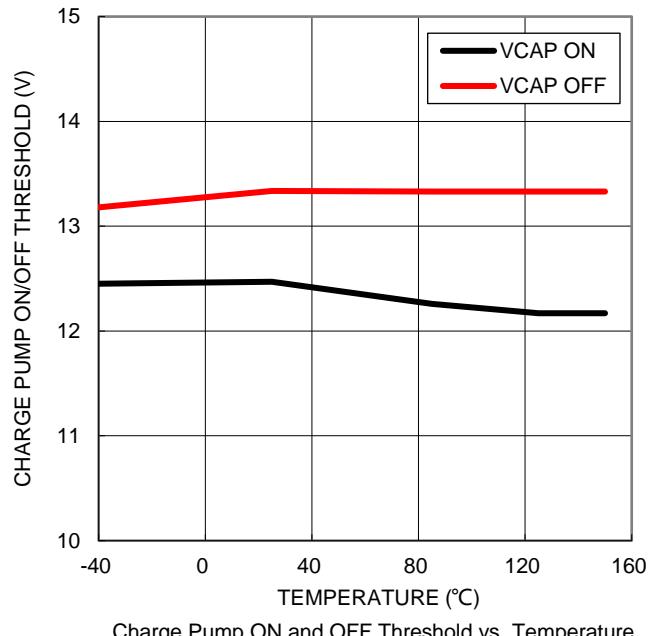

To remove any chatter on the gate drive, approximately 800mV of hysteresis is added to the VCAP undervoltage lockout. The charge pump remains enabled until the VCAP to ANODE voltage reaches 12.4V, typically, at which point the charge pump is disabled decreasing the current draw on the ANODE pin. The charge pump remains disabled until the VCAP to ANODE voltage is below to 11.6V typically at which point the charge pump is enabled. The voltage between VCAP and ANODE continue to charge and discharge between 11.6V and 12.4V. By enabling and disabling the charge pump, the operating quiescent current of the AP4701Q is reduced. When the charge pump is disabled, it sinks 5 $\mu$ A typically.

## Detailed Description (continued)

### Gate Driver

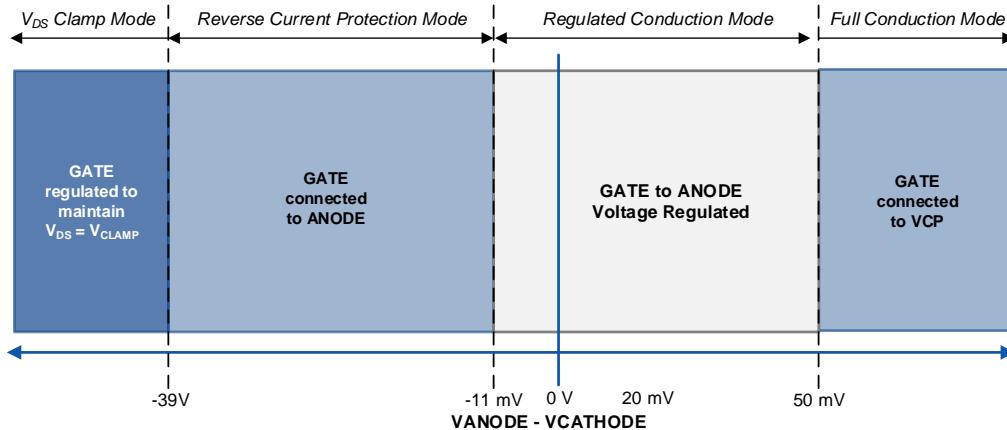

The gate driver is used to control the external n-channel MOSFET by setting the GATE to ANODE voltage to the corresponding mode of operation. There are four defined modes of operation that the gate driver operates under forward regulation, full conduction mode, reverse current protection and V<sub>DS</sub> clamp mode according to the ANODE to CATHODE voltage. The following figure depicts how the modes of operation vary according to the ANODE to CATHODE voltage of the AP74701Q. The threshold between forward regulation mode and conduction mode is when the ANODE to CATHODE voltage is 50mV. The threshold between forward regulation mode and reverse current protection mode is when the ANODE to CATHODE voltage is -11mV. The threshold between reverse current protection mode and V<sub>DS</sub> clamp mode is when the ANODE to CATHODE voltage is -39V typical.

Before the gate driver is enabled following three conditions must be achieved:

- The EN pin voltage must be greater than the specified input high voltage.

- The VCAP to ANODE voltage must be greater than the undervoltage lockout voltage.

- The ANODE voltage must be greater than VANODE POR rising threshold.

If the above conditions are not achieved, then the GATE pin is internally connected to the ANODE pin, assuring that the external MOSFET is disabled. Once these conditions are achieved the gate driver operates in the correct mode depending on the ANODE to CATHODE voltage.

### Enable

The AP74701Q has an enable pin, EN. The enable pin allows for the gate driver to be either enabled or disabled by an external signal. If the EN pin voltage is greater than the rising threshold, the gate driver and charge pump operates as described in *Gate Driver* and *Charge Pump* sections. If the enable pin voltage is less than the input low threshold, the charge pump and gate driver are disabled placing the AP74701Q in shutdown mode. The EN pin can withstand a voltage as large as 65V and as low as -33V. This allows for the EN pin to be connected directly to the ANODE pin if enable functionality is not needed. In conditions where EN is left floating, the internal sink current of 1 $\mu$ A pulls EN pin low and disables the device.

### SW Switch

The AP74701Q has "SW" pin to enable battery voltage monitoring in automotive systems. When the device is enabled, an internal switch connects SW pin to ANODE. This enables monitoring battery voltage using an external resistor divider connected from SW pin to GND. When AP74701Q is put in shutdown mode by pulling down the EN pin to ground, an internal switch between SW and ANODE pin is disconnected. This eliminates leakage current by the resistor divider when system is in shutdown state. When not used, "SW" pin should be left floating.

## Detailed Description (continued)

### Operations

The AP74701Q has shutdown, regulated conduction, full conduction, reverse current protection mode and  $V_{DS}$  clamping mode in operation. Details are as follows.

| VANODE      | EN                    | V <sub>CP</sub> - VANODE | VANODE - V <sub>CATHODE</sub> | V <sub>CP</sub> | V <sub>GATE</sub> | AP74701Q Mode                     |

|-------------|-----------------------|--------------------------|-------------------------------|-----------------|-------------------|-----------------------------------|

| < -39V      |                       |                          | < -39V                        | OFF             | Regulated         | $V_{DS}$ Clamping Mode            |

| -39V to 0V  | Don't Care            | Don't Care               | Reverse Voltage               |                 | NA                | OFF (No Power)                    |

| 0V to UVLO  |                       |                          |                               | OFF             |                   | Shutdown                          |

| UVLO to 60V | < VEN <sub>IL</sub>   |                          | Forward Voltage               |                 | ANODE             | V <sub>CP</sub> Charging          |

|             | < VCP <sub>UVLO</sub> |                          |                               |                 | Regulated         | $V_{DS}$ Clamping Mode            |

|             | > VEN <sub>IH</sub>   | > VCP <sub>UVLO</sub>    | < -39V                        |                 | ANODE             | Reverse Current Protection        |

|             |                       |                          | -39V to -11mV                 |                 | Regulated         | Regulated Conduction (Light Load) |

|             |                       |                          | -11mV to 50mV                 | ON              |                   |                                   |

|             |                       |                          | > 50mV                        |                 | VCP               | Full Conduction (Heavy Load)      |

### Shutdown Mode

The AP74701Q enters shutdown mode when the EN pin voltage is below the specified input low threshold  $V_{IL\_EN}$ . Both the gate driver and the charge pump are disabled in shutdown mode. During shutdown mode the AP74701Q enters low IQ operation with the ANODE pin only sinking 1 $\mu$ A. When the AP74701Q is in shutdown mode, forward current flow through the external MOSFET is not interrupted but is conducted through the MOSFET's body diode.

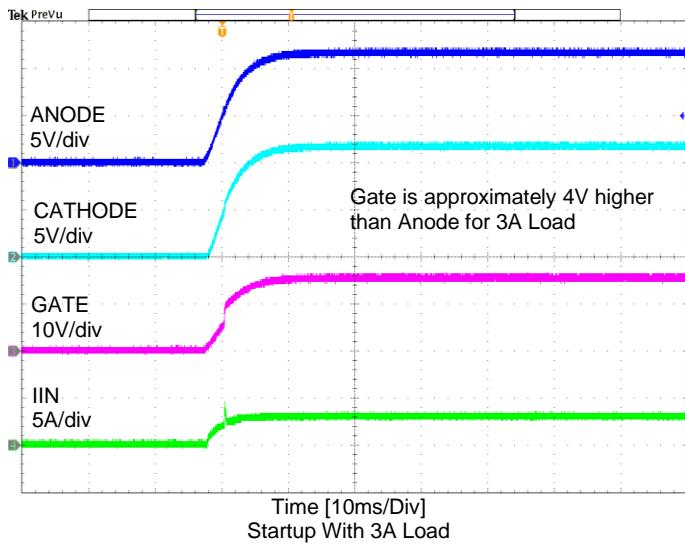

### Regulated Conduction Mode

For the AP74701Q to operate in regulated conduction mode, the gate driver must be enabled and the current from source to drain of the external MOSFET must be within the range to result in an ANODE to CATHODE voltage drop of -11mV (typ) to 50mV (typ). During forward regulation mode the ANODE to CATHODE voltage is regulated to 20mV (typ) by adjusting the GATE to ANODE voltage. This regulation enables turn-off of the MOSFET at very light loads and ensures no DC reverse current flow.

### Full Conduction Mode

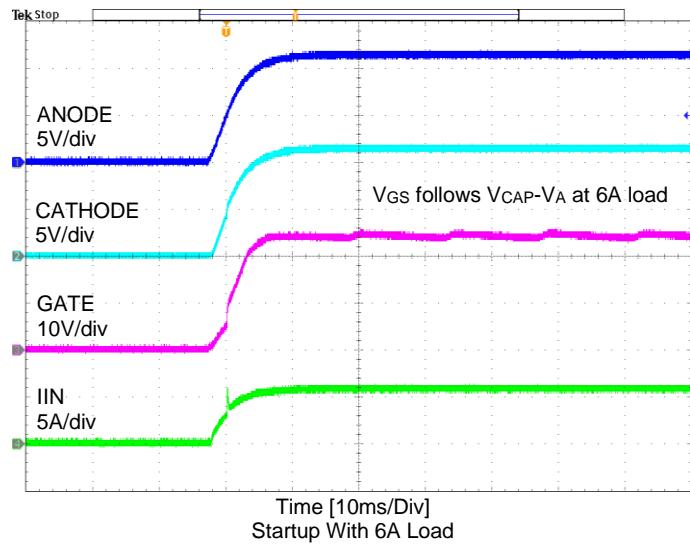

For the AP74701Q to operate in full conduction mode, the gate driver must be enabled and the current from source to drain of the external MOSFET must be large enough to result in an ANODE to CATHODE voltage drop of greater than 50mV (typ). If these conditions are achieved the GATE pin is internally connected to the V<sub>CP</sub> pin resulting in the GATE to ANODE voltage being approximately the same as the V<sub>CP</sub> to ANODE voltage. By connecting V<sub>CP</sub> to GATE, the external MOSFET's  $R_{DS(ON)}$  is minimized reducing the power loss of the external MOSFET when forward currents are large.

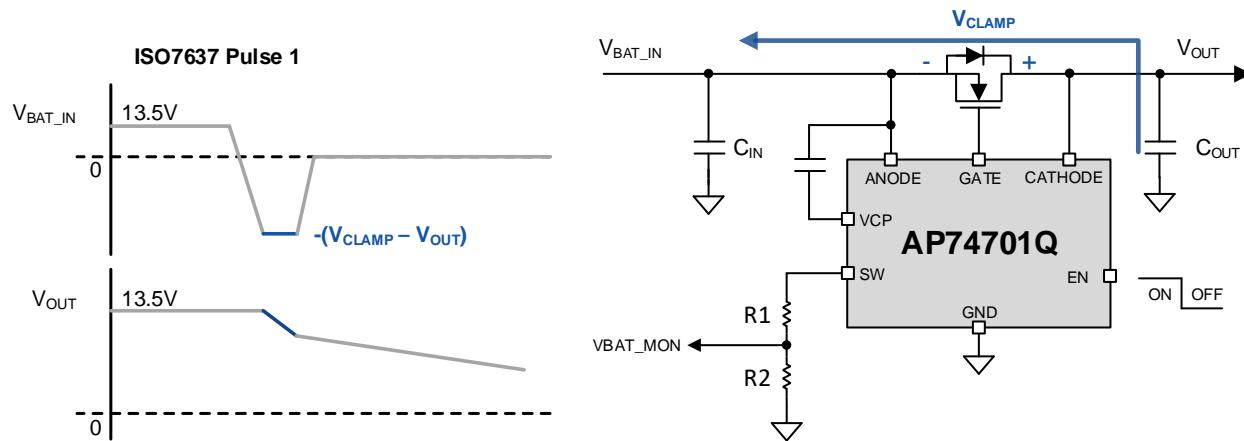

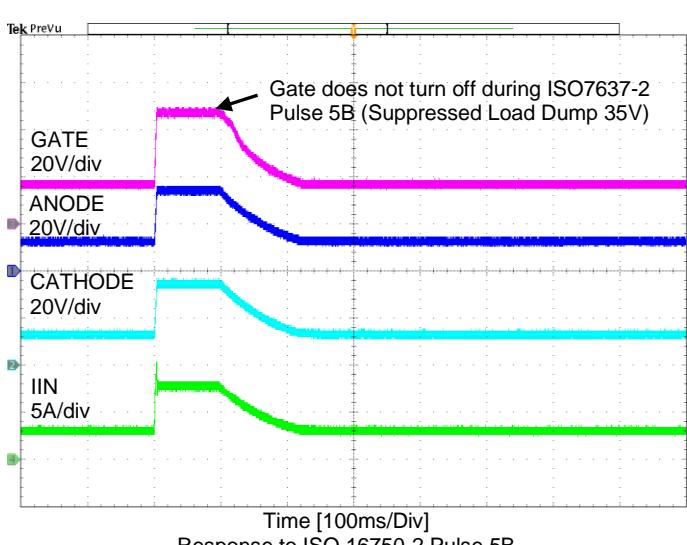

### $V_{DS}$ Clamping mode

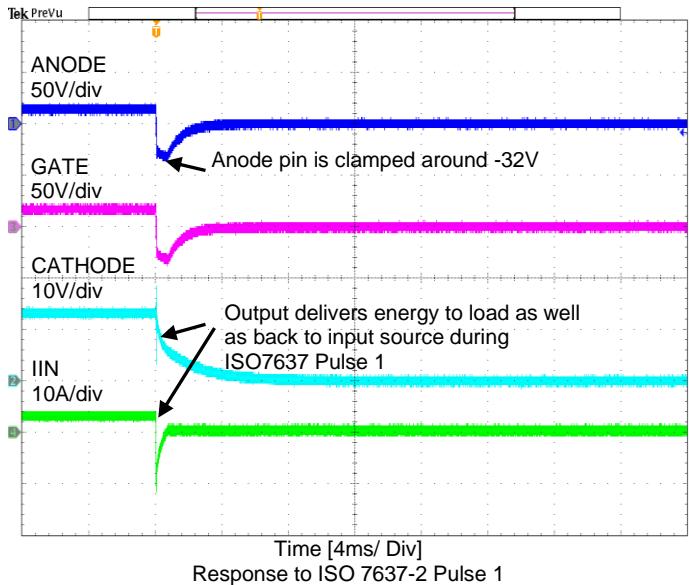

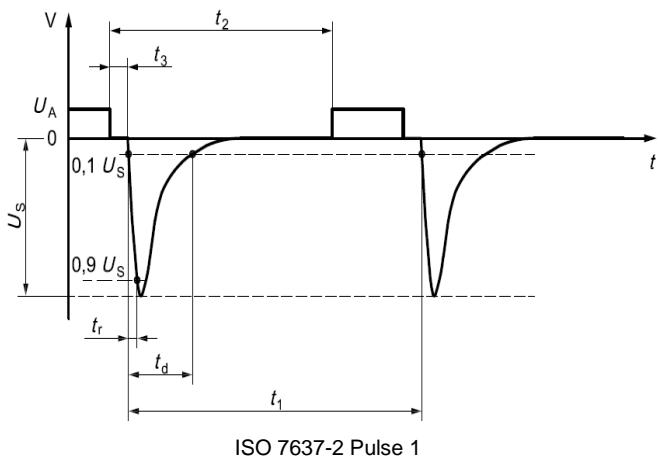

The AP74701Q features an integrated  $V_{DS}$  clamp that operates the external MOSFET as an active clamp element to dissipate automotive EMC transients such as ISO7637-2 pulse 1 transient where there is no output voltage hold-up requirement and system is allowed to turn off during such EMC transients.  $V_{DS}$  clamp threshold is selected such that the AP74701Q does not engage into  $V_{DS}$  clamp operation, thereby ensuring the FET remains OFF during the RCB state for the system level EMC tests where output voltage hold-up is required such as input short interruptions/micro cuts (LV124 E-10, ISO16750-2).

When the ISO7637 pulse 1 is applied at the input of AP74701Q:

1. Device GATE goes low and turns OFF the MOSFET once the voltage drop across ANODE to CATHODE reaches  $V_{ACTIVE\_REV}$  threshold.

2. Once the voltage across drain and source of the MOSFET reaches  $V_{CLAMP}$  level (34V min), GATE is turned ON back in the saturation region, operating external MOSFET as an active clamp and dissipates the ISO7637 pulse 1 energy.

Note that the reverse current flows from V<sub>OUT</sub> back to input during the ISO7637 pulse 1 transient event, thus discharging V<sub>OUT</sub> capacitor. The AP74701Q CATHODE pin can handle negative voltage. However, if application circuit connected to the output of AP74701Q cannot handle negative voltage, then the output filter should be designed to ensure that V<sub>OUT</sub> does not go negative during ISO7637 pulse 1 test. For all the other ISO7637 pulses (i.e. pulse 2a, 2b, 3a, 3b), which are short duration transients, the input and output filter components filtering effect suppresses these pulses.

**Detailed Description** (continued)

The Typical Circuit Operation of AP74701Q During Vds Clamp at ISO7637 Pulse 1

**Reverse Current Protection Mode**

For the AP74701Q to operate in reverse current protection mode, the gate driver must be enabled and the current of the external MOSFET must be flowing from the drain to the source. When the ANODE to CATHODE voltage is less than -11mV (typ), reverse current protection mode is entered and the GATE pin is internally connected to the ANODE pin. The connection of the GATE to ANODE pin disables the external MOSFET. The body diode of the MOSFET blocks any reverse current from flowing from the drain to source.

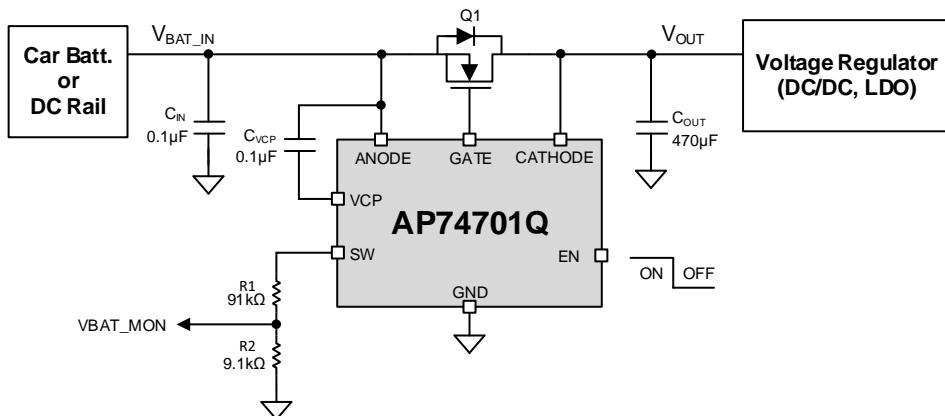

**Application Information**

The AP74701Q is used with n-channel MOSFET to achieve a typical reverse-polarity protection solution. The schematic for the 12V battery protection application is shown below where the AP74701Q is used to drive n-channel MOSFET Q1 in series with a battery. The V<sub>DS</sub> clamp feature integrated into AP74701Q enables input TVS-less operation. The output capacitor C<sub>OUT</sub> is recommended to protect the immediate output voltage collapse as a result of line disturbance, and to make sure output remains positive during all system EMC transient tests.

**Design Example**

| Design Parameter           | Example Value                                                                                                            |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------|

| V <sub>VBAT_IN</sub> Range | 12V car battery, 12V nominal with 3.2V cold crank and 35V load dump                                                      |

| V <sub>OUT</sub>           | 3.2V during cold crank to 35V load dump                                                                                  |

| I <sub>OUT</sub>           | 3A nominal and 5A maximum                                                                                                |

| C <sub>OUT</sub>           | 1μF min, 470μF typical hold-up cap                                                                                       |

| Automotive EMC Compliance  | ISO 7637-2 (-100V, Pulse 1, Pulse 2a, Pulse 2b), ISO 16750-2 (Suppressed load dump 35V), LV124, E-10 (Input Micro Short) |

## Application Information (continued)

### MOSFET Selection

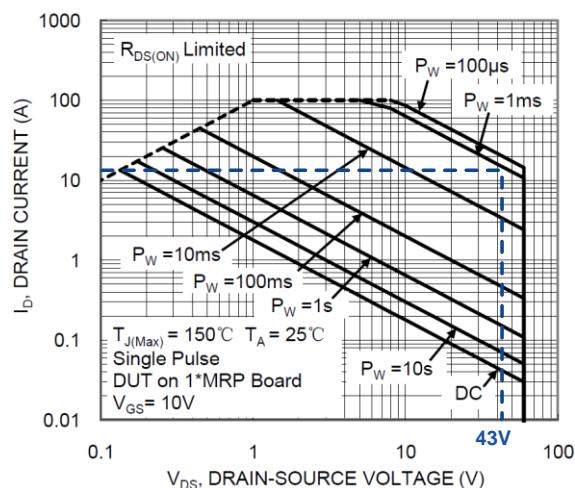

For selecting the blocking MOSFET Q1, important electrical parameters are the maximum continuous drain current ID, the maximum drain-to-source voltage  $V_{DS\_MAX}$ , the maximum drain-to-source voltage  $V_{GS\_MAX}$ , safe operating area (SOA), the maximum source current through body diode and the drain-to-source ON resistance  $R_{DS(ON)}$ .

The maximum continuous drain current (ID) rating must exceed the maximum continuous load current.

To reduce the MOSFET conduction losses, MOSFET with the lowest possible  $R_{DS(ON)}$  is preferred, but selecting a MOSFET based on low  $R_{DS(ON)}$  may not be beneficial always. Higher  $R_{DS(ON)}$  will provide increased voltage information to AP74701Q's reverse current comparator at a lower reverse current. Reverse current detection is better with increased  $R_{DS(ON)}$ . Choosing a MOSFET with forward voltage drop of less than 50mV at maximum current is a good starting point.

The maximum drain-to-source voltage,  $V_{DS\_MAX}$ , must be high enough to withstand the highest differential voltage seen in the application. With AP74701Q, the maximum differential voltage across the MOSFET is  $V_{CLAMP\_MAX}$  of 43V. A minimum of 60V  $V_{DS}$  rated is recommended. This would include all the automotive transient events and any anticipated fault conditions.

During the ISO7637 Pulse 1, the maximum  $V_{DS}$  seen by the external MOSFET Q1 is  $V_{DSCLAMP\_MAX}$  that is 43V. The peak current during ISO7637-2 pulse 1 can be calculated following equation:

$$I_{ISO\_PEAK} = (V_{ISO} + V_{OUT} - V_{DSCLAMP\_MAX}) / R_s$$

Where

- $V_{ISO}$  is the negative peak of the ISO7637-2 pulse 1

- $V_{OUT}$  is the initial level of the VBAT before ISO pulse is applied

- $V_{DSCLAMP}$  is maximum  $V_{CLAMP}$  threshold of AP74701Q

- $R_s$  is the ISO7637 pulse generator input impedance (10Ω)

For ISO7637-2 pulse 1 with amplitude of -100V,  $V_{OUT}$  nominal voltage of 13.5V the peak current seen by MOSFET Q1 comes around 7A.

The current profile tapers down from 7A to 0A from the peak of 7A as shown in response to ISO 7637-2 Pulse 1. The resulting average current ( $I_{ISO\_AVG}$ ) can be approximated as one third of the peak current that is around 2.4A. The  $V_{DS}$  clamp operation lasts for about 1msec (max). Selecting a MOSFET with SOA characteristics covering the load line of 43V which can support drain current greater than ( $I_{ISO\_PEAK}/2$ ) for 1 msec is a good starting point. For this particular design example, MOSFET which can support greater than 3.5A of drain current at 43V  $V_{DS}$  on SOA curve is suitable.

The following curve shows typical SOA characteristics plot of Diodes Incorporated's DMT6007LFGQ highlighting maximum drain current supported by the MOSFET for the duration of 1msec. MOSFET datasheet SOA curves are typically plotted at ambient temperature, so consider sufficient margin over MOSFET parameters calculated values to ensure safe operation over desired operating temperature range.

Safe Operation Area of DMT6007LFGQ, N-CHANNEL ENHANCEMENT MODE MOSFET

## Application Information (continued)

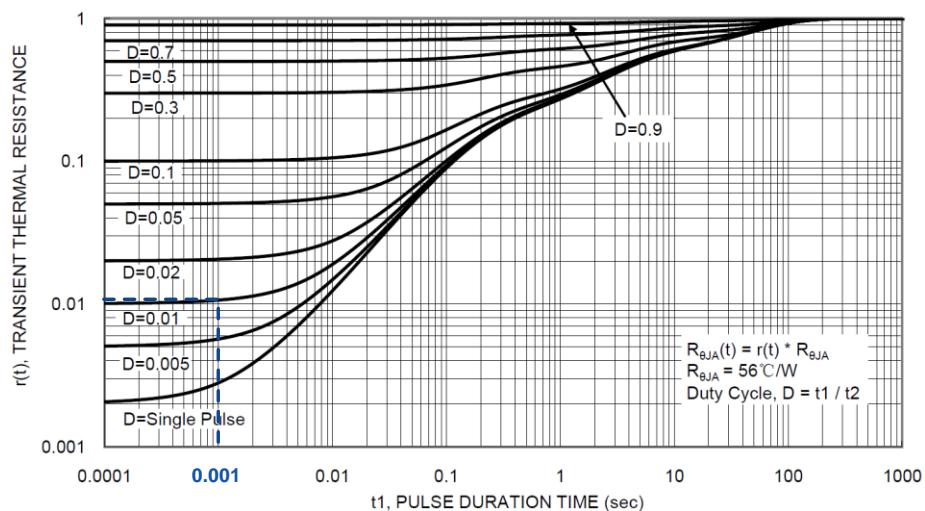

As external MOSFET dissipates ISO7637-2 pulse 1 energy, a special attention should be given while calculating maximum power dissipation and effective temperature rise. An average power dissipation across the MOSFET can be calculated by following equation:

$$P_{D\_AVG} = V_{DSCLAMP\_MAX} \times I_{ISO\_AVG}$$

For given design example, average power dissipation comes around.

$$P_{D\_AVG} = 43V \times 2.4A = 103.2W$$

Typical ISO7637-2 pulse 1 transient lasts for 2ms with total time period of 200ms between two consecutive pulses (duty cycle of 1%). The effective temperature rise due to power dissipation across MOSFET during ISO7637-2 pulse 1 event can be calculated by looking at transient thermal impedance curve in a MOSFET datasheet. The following curve shows an example of how to estimate transient thermal impedance of a MOSFET for ISO7637-2 pulse 1 event.

Transient Thermal Resistance of DMT6007LFGQ, N-CHANNEL ENHANCEMENT MODE MOSFET

The maximum  $V_{GS}$  AP74701Q can drive is 13.9V, so a MOSFET with 15V minimum  $V_{GS}$  rating should be selected.

### Charge Pump C\_CP and Input Capacitance CIN

Minimum required capacitance for charge pump VCP and input/output capacitance are:

- $C_{VCP}$ : Minimum 0.1 $\mu$ F is required; recommended value of  $V_{CP}$  [ $\mu$ F]  $\geq 10 \times C_{iss\_MOSFET}$  [ $\mu$ F]

- $C_{IN}$ : Minimum 0.1 $\mu$ F of input capacitance is required, recommended to place close to ANODE pin

### Output Capacitance COUT

The AP74701Q CATHODE pin is capable of handling negative voltage. However, if applications connected to AP74701Q output are not capable of handling negative voltage, then sufficient output capacitor is required to ensure output does not swing negative during ISO7637-2 pulse 1 operation. The required output capacitor during ISO7637-2 pulse 1 to ensure output does not swing negative can be calculated using following equation:

$$C_{OUT} = (I_{LOAD} + I_{ISO\_AVG}) \times 1ms / \Delta V_{OUT} \quad (5)$$

Where  $\Delta V_{OUT}$  is difference between  $V_{OUT}$  at the start and the end of ISO7637-2 pulse 1.

## Application Curves

## Application Curves (continued)

**Application Curves (continued)**

**Application Curves (continued)**

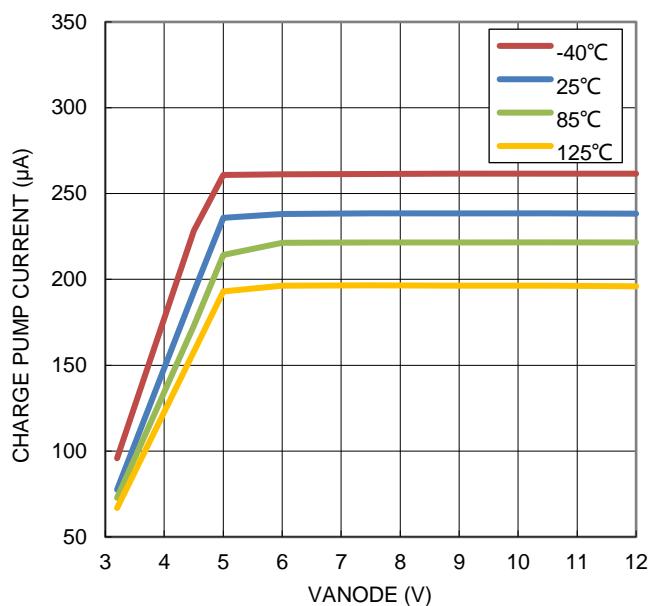

Charge Pump Current vs. Supply Voltage at  $V_{CAP} = 6V$

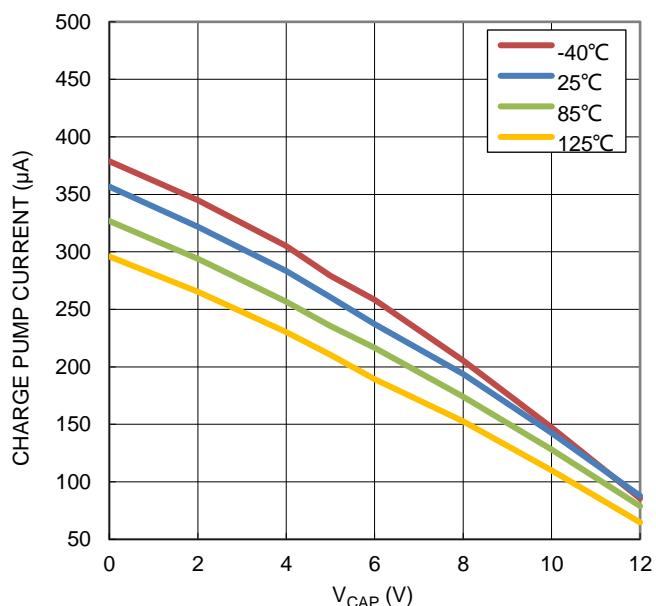

Charge Pump V-I Characteristics at  $VANODE >= 12V$

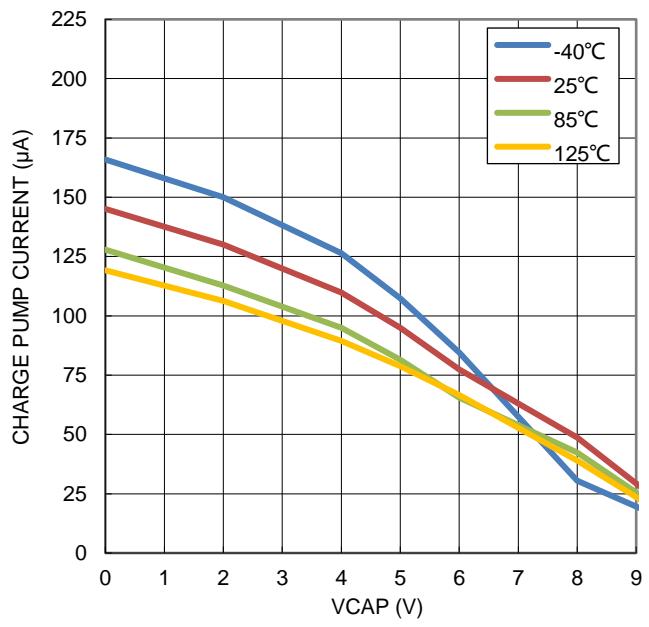

Charge Pump V-I Characteristics at  $VANODE = 3.2V$

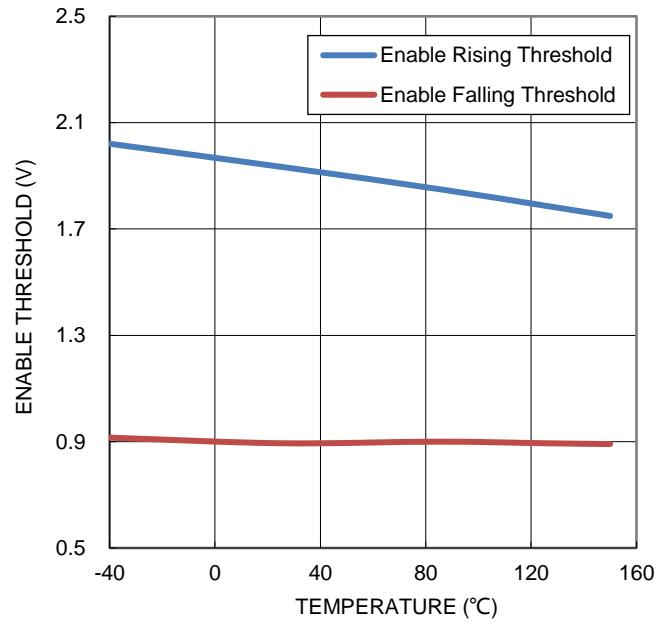

Enable Threshold vs. Temperature

**Application Curves (continued)**

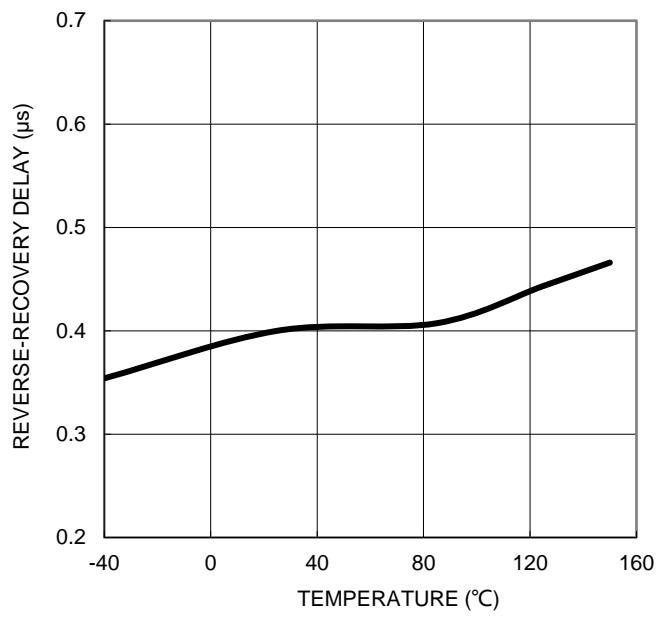

Reverse Current Blocking Delay vs. Temperature

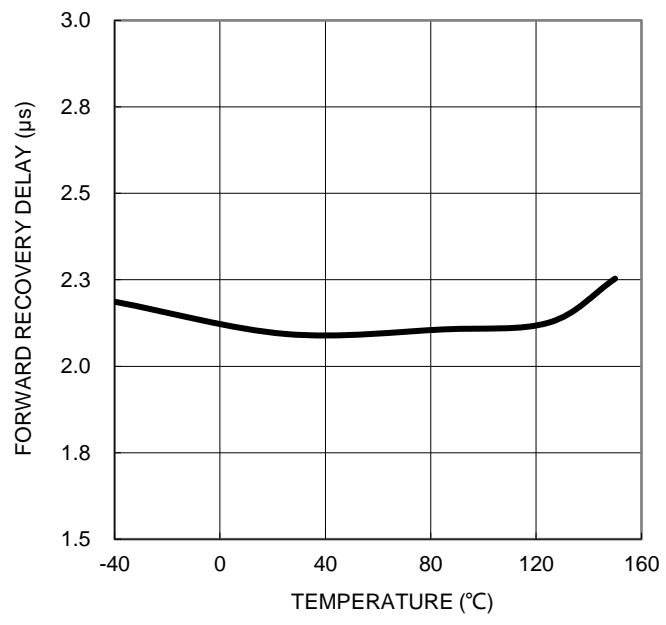

Forward Recovery Delay vs. Temperature

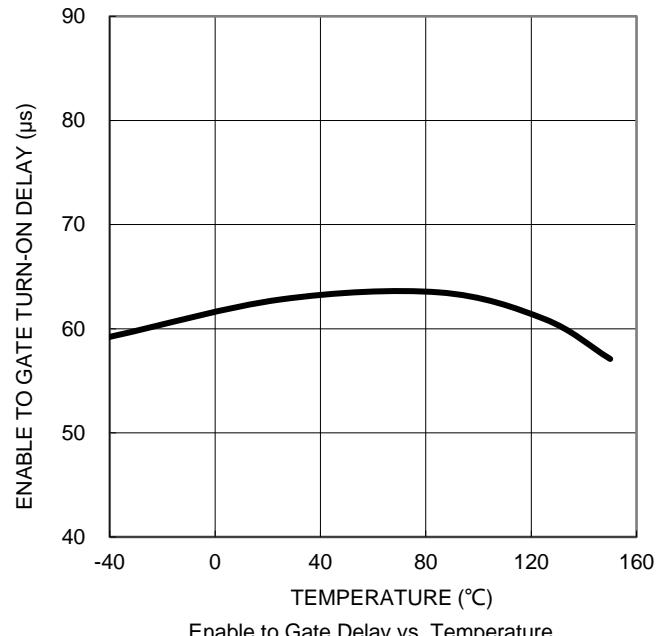

Enable to Gate Turn-On Delay vs. Temperature

Charge Pump ON and OFF Threshold vs. Temperature

**Application Curves (continued)**

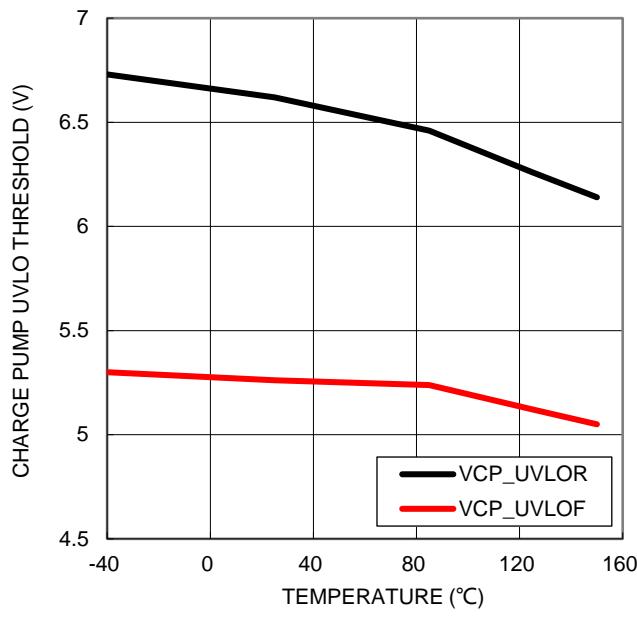

Charge Pump UVLO Threshold vs. Temperature

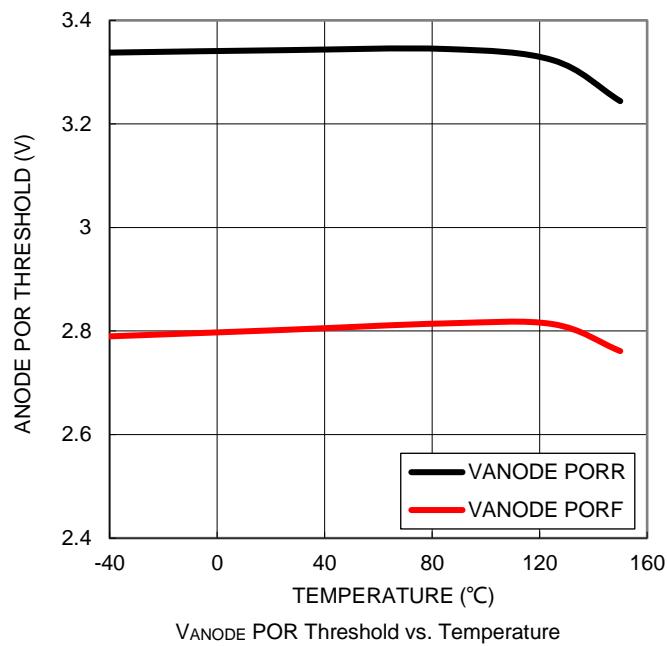

Vanode POR Threshold vs. Temperature

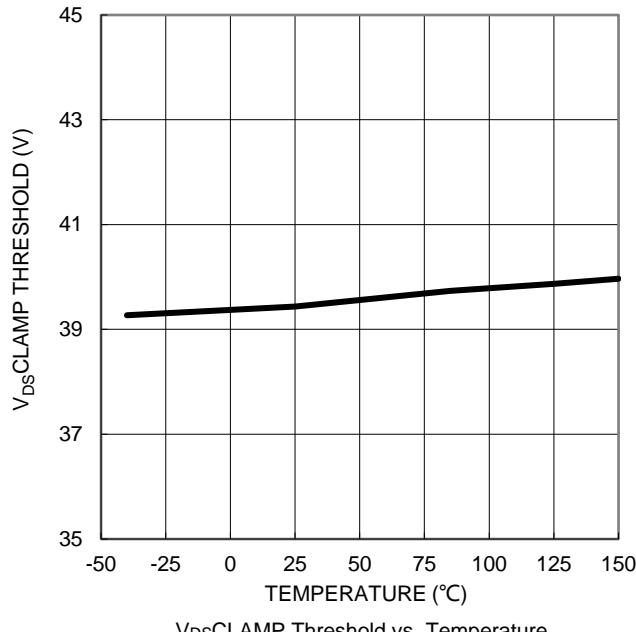

VDsCLAMP Threshold vs. Temperature

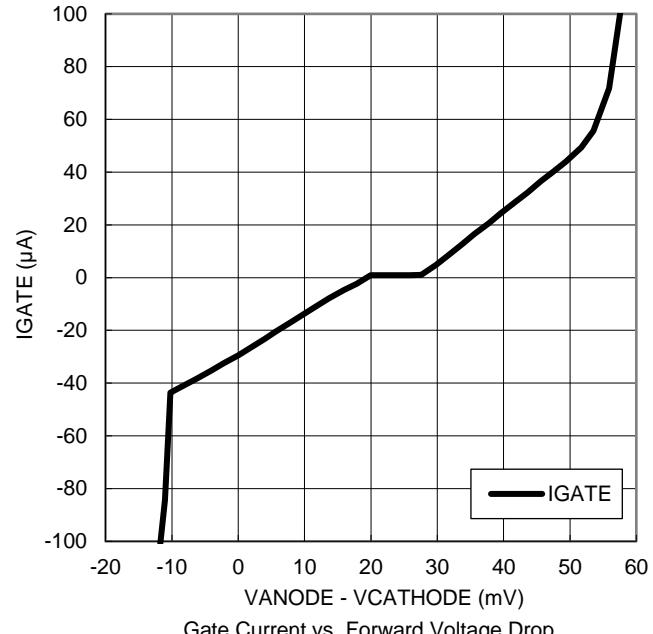

Gate Current vs. Forward Voltage Drop

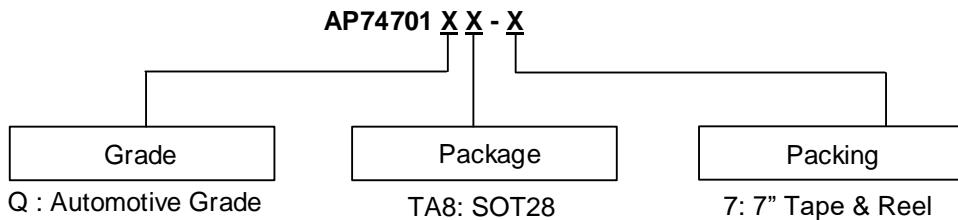

## Ordering Information

| Orderable Part Number | Enable Active | Package Code | Package | Packing |                  |

|-----------------------|---------------|--------------|---------|---------|------------------|

|                       |               |              |         | Qty.    | Carrier          |

| AP74701QTA8-7         | High          | TA8          | SOT28   | 3000    | 7" Tape and Reel |

## Marking Information

SOT28

XXX : Identification Code

Y : Year 0 to 9

W : Week : A to Z : 1 to 26 week;

a to z : 27 to 52 week; z represents

52 and 53 week

X : Internal Code

| Orderable Part Number | Package | Identification Code |

|-----------------------|---------|---------------------|

| AP74701QTA8-7         | SOT28   | T9Q                 |

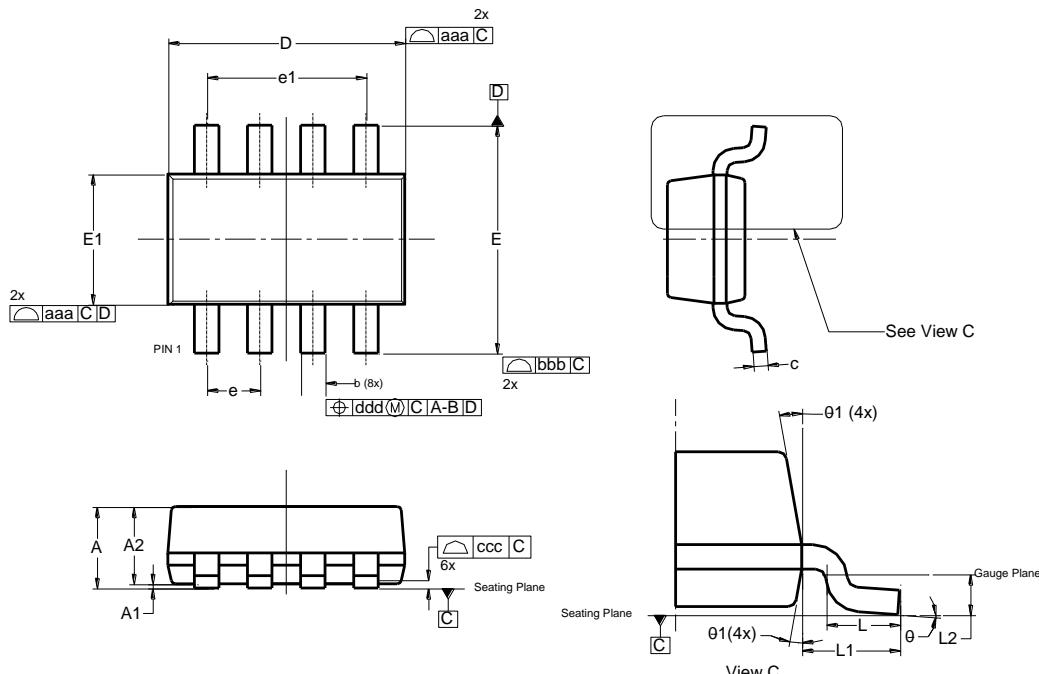

## Package Outline Dimensions

Please see <http://www.diodes.com/package-outlines.html> for the latest version.

SOT28

## Suggested Pad Layout

Please see <http://www.diodes.com/package-outlines.html> for the latest version.

SOT28

| Dimensions | Value (in mm) |

|------------|---------------|

| <b>C</b>   | 0.950         |

| <b>G</b>   | 1.600         |

| <b>X</b>   | 0.700         |

| <b>Y</b>   | 0.900         |

| <b>Y1</b>  | 3.400         |

**Note:** The suggested land pattern dimensions have been provided for reference only, as actual pad layouts may vary depending on application. These dimensions may be modified based on user equipment capability or fabrication criteria. A more robust pattern may be desired for wave soldering and is calculated by adding 0.2 mm to the 'Z' dimension. For further information, please reference document IPC-7351A, Naming Convention for Standard SMT Land Patterns, and for International grid details, please see document IEC, Publication 97.

**Note:** For high voltage applications, the appropriate industry sector guidelines should be considered with regards to creepage and clearance distances between device Terminals and PCB tracking.

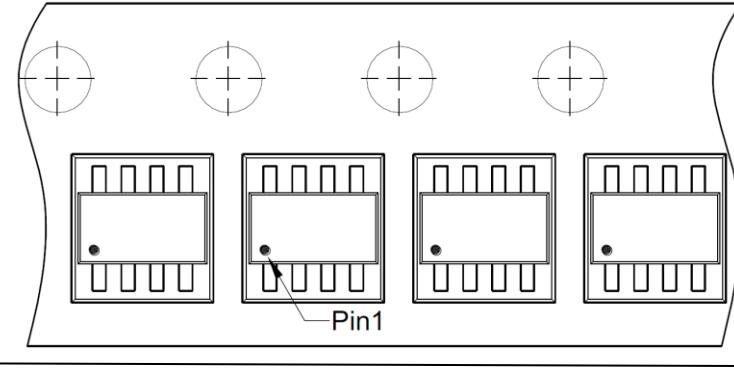

## Device Taping Orientation

Package Type: SOT28

| Tape Width | Part Number Suffix | Tape Orientation                                                                                            |

|------------|--------------------|-------------------------------------------------------------------------------------------------------------|

| 8mm        | -7                 |  <p>Direction of feed</p> |

Note: For part marking, refer to *Marking Information*.

Note: Tape and package drawings are not to scale and are shown for device tape orientation only.

Note: The taping orientation of the other package type can be found on our website at <https://www.diodes.com/assets/Packaging-Support-Docs/AP02007.pdf>.

## Mechanical Data

- Surface-Mount Package

- Moisture Sensitivity: Level 1 per J-STD-020

- Package Material: Molded Plastic, UL Flammability Classification Rating 94V-0

- Terminals: Finish – Matte Tin Plated Leads, Solderable per MIL-STD-202, Method 208<sup>③</sup>

- Weight: 0.016 grams (Approximate)

- Max Soldering Temperature +260°C for 30 secs as per JEDEC J-STD-020

**IMPORTANT NOTICE**

1. DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products for their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

5. Diodes' products are provided subject to Diodes' Standard Terms and Conditions of Sale (<https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/>) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

6. Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

9. This Notice may be periodically updated with the most recent version available at <https://www.diodes.com/about/company/terms-and-conditions/important-notice>

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries.

All other trademarks are the property of their respective owners.

© 2025 Diodes Incorporated. All Rights Reserved.

[www.diodes.com](http://www.diodes.com)