## Table of Contents

|                                                                 |           |

|-----------------------------------------------------------------|-----------|

| <b>Chapter 1. Introduction .....</b>                            | <b>3</b>  |

| <b>Chapter 2. AP33772S Sink Controller .....</b>                | <b>3</b>  |

| 2.1    Package Outline .....                                    | 3         |

| 2.2    Pin Descriptions .....                                   | 4         |

| <b>Chapter 3. EVB Hardware Details .....</b>                    | <b>5</b>  |

| 3.1    EVB TOP View .....                                       | 5         |

| 3.2    EVB Block Diagram.....                                   | 5         |

| 3.3    EVB Schematics.....                                      | 6         |

| 3.4    Board Outline .....                                      | 6         |

| 3.5    EVB System BOM .....                                     | 7         |

| <b>Chapter 4. EVB Quick Setup and Function Description.....</b> | <b>8</b>  |

| 4.1    Quick Setup Guide .....                                  | 8         |

| 4.2    Application Circuit Description .....                    | 11        |

| <b>Chapter 5. I2C Command/Register Summary .....</b>            | <b>13</b> |

| 5.1    I2C Command Format .....                                 | 13        |

| 5.2    I2C Operation.....                                       | 13        |

| 5.3    Register Summary.....                                    | 13        |

| 5.4    Register Description .....                               | 15        |

| <b>Chapter 6. Function Description.....</b>                     | <b>23</b> |

| 6.1    I2C Request Message .....                                | 23        |

| 6.2    Support EPR / AVS.....                                   | 23        |

| 6.3    VOUT MOS Switch.....                                     | 23        |

| 6.4    LED Indication .....                                     | 24        |

| 6.5    Interrupt .....                                          | 24        |

| 6.6    CC Flip Indication.....                                  | 24        |

| 6.7    Legacy Type A Charger with Type A-to-C Cable.....        | 24        |

| 6.8    Temperate Estimate .....                                 | 25        |

|                                                             |           |

|-------------------------------------------------------------|-----------|

| <b>Chapter 7. Protection .....</b>                          | <b>26</b> |

| 7.1    Overvoltage Protection (OVP) .....                   | 26        |

| 7.2    Overcurrent Protection (OCP) .....                   | 26        |

| 7.3    Undervoltage Protection (UVP) .....                  | 26        |

| 7.4    Overtemperature Protection (OTP) and De-Rating ..... | 27        |

| 7.5    Moisture Detection.....                              | 27        |

| <b>Chapter 8. Firmware Flow.....</b>                        | <b>28</b> |

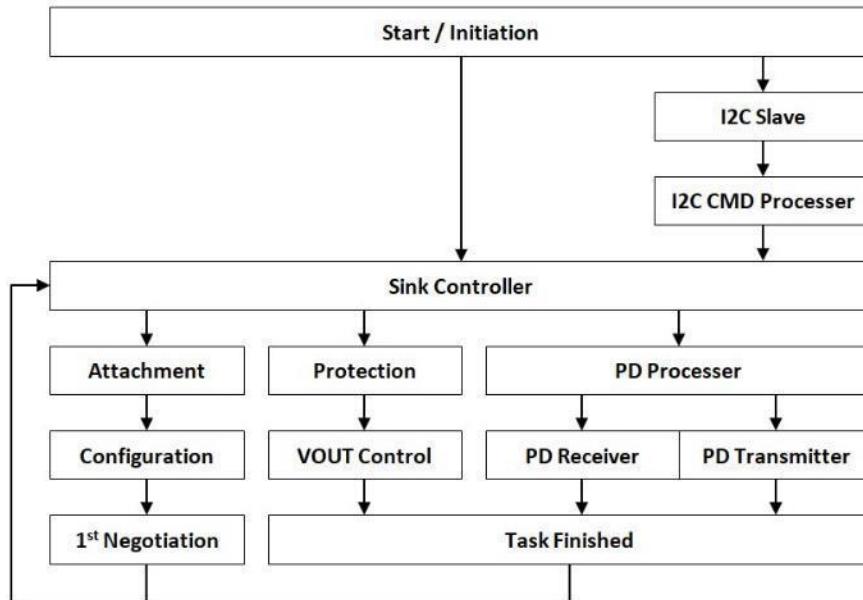

| 8.1    Firmware Block Diagram .....                         | 28        |

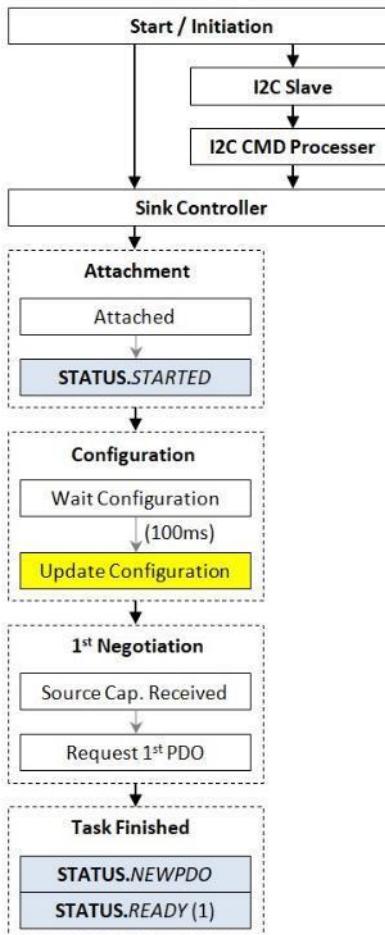

| 8.2    Firmware Startup Process .....                       | 29        |

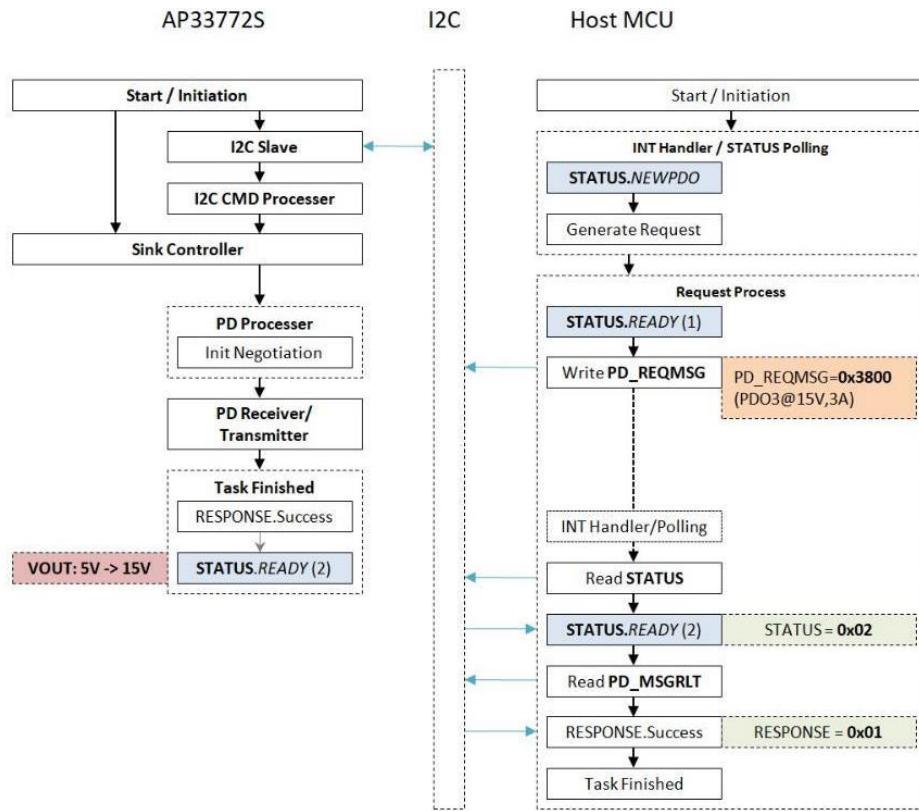

| 8.3    Request Process .....                                | 30        |

| 8.4    Initial Configuration .....                          | 31        |

| <b>Chapter 9. Compliance Test .....</b>                     | <b>32</b> |

| <b>Chapter 10. Revision History.....</b>                    | <b>33</b> |

## Chapter 1. Introduction

The growing popularity of standard USB PD3.1 chargers for mobile phones and notebook PCs spurs the demand for leveraging standard PD3.1 chargers to replace purposely and individually built chargers for battery-power electronic devices to reduce E-Waste.

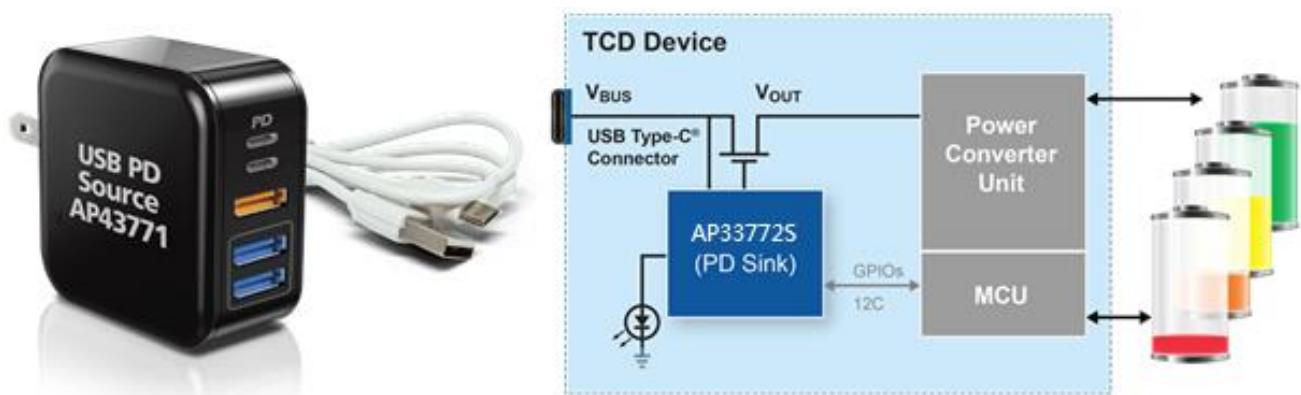

The AP33772S Evaluation Board (EVB) is intended to be used as an evaluation vehicle for charging applications between a Type C Connector-equipped Device (**TCD**, Energy Sink) and a Type C Connector-equipped PD3.1 compliance Charger or Adaptor (**PDC**, Energy Source).

Figure 1 illustrates a TCD, embedded with a PD3.1 Sink controller IC (AP33772S). This is physically connected to a PDC, embedded with a USB PD3.1 decoder (AP43771) through a Type-C to Type-C cable. Based on the built-in USB PD3.1 compliant firmware, the AP33772S and AP43771 pair can go through the USB PD3.1 standard attachment procedure to establish a suitable PD3.1 charging state.

The AP33772S Evaluation Board (EVB) User Guide explains a flexible I2C setting arrangement (I2C Interface Pin, I2C Register Map, and Operations) to request the desired input voltage and input power for a typical TCD. Various system protection functions and system status checks can also be performed by accessing the relevant I2C register contents by the TCD's host MCU device.

Figure 1 – A typical TCD uses the AP33772S PD Sink Controller with I2C Interface to request power from a USB Type-C PD3.1/PPS Compliance Source Adaptor

## Chapter 2. AP33772S Sink Controller

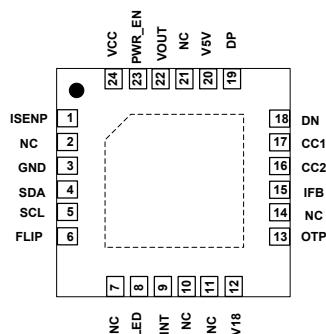

### 2.1 Package Outline

Figure 2 – AP33772S Package Outline

### 2.2 Pin Descriptions

| Pin No | Pin Name | Type (Notes) | Pin Function                                                                                                                                                                                                       |

|--------|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

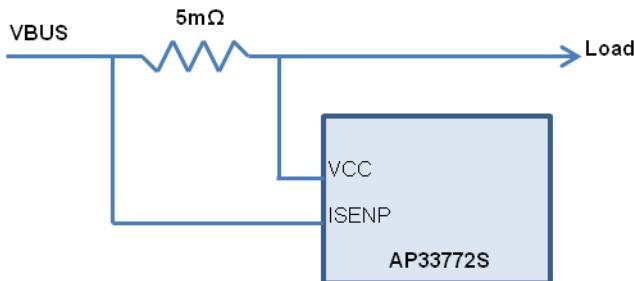

| 1      | ISENP    | AHV          | Current Sense Positive Node, connect to the positive node of the external current sensing resistor                                                                                                                 |

| 2      | NC       | -            | No Connection                                                                                                                                                                                                      |

| 3      | GND      | GND          | Ground                                                                                                                                                                                                             |

| 4      | SDA      | DIO          | I2C Data, need to be pulled up externally                                                                                                                                                                          |

| 5      | SCL      | DI           | I2C Clock, need to be pulled up externally                                                                                                                                                                         |

| 6      | FLIP     | DO           | Flip indicator of Type-C plug. LOW: CC1 detected; HIGH: CC2 detected                                                                                                                                               |

| 7      | NC       | -            | No Connection                                                                                                                                                                                                      |

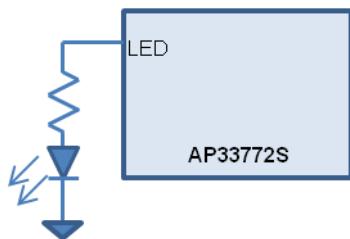

| 8      | LED      | DO           | LED Indicator Pin, refer to Table 13 for detailed description                                                                                                                                                      |

| 9      | INT      | DO           | Interrupt pin is used to inform external MCU. LOW: normal; HIGH: interrupt occurred                                                                                                                                |

| 10     | NC       | -            | No Connection                                                                                                                                                                                                      |

| 11     | NC       | -            | No Connection                                                                                                                                                                                                      |

| 12     | V18      | DP           | 1.8V LDO output for internal use only. Connect a 100nF cap to GND. This pin cannot drive external load.                                                                                                            |

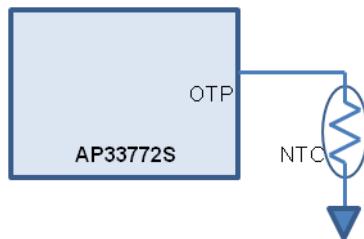

| 13     | OTP      | AIO          | 100uA Current Source output for NTC connected to ground; this NTC is used to monitor temperature variation                                                                                                         |

| 14     | NC       | -            | No Connection                                                                                                                                                                                                      |

| 15     | IFB      | AI           | For current measurement, a 100nF cap to Ground is suggested                                                                                                                                                        |

| 16     | CC2      | AIO          | Type-C Configuration Channel 2 (CC2); the CC2 pin detects, configures, and manages the connections across a USB Type-C cable                                                                                       |

| 17     | CC1      | AIO          | Type-C Configuration Channel 1 (CC1); the CC1 pin detects, configures, and manages the connections across a USB Type-C cable                                                                                       |

| 18     | DN       | AIO          | DN of Type-C Connector                                                                                                                                                                                             |

| 19     | DP       | AIO          | DP of Type-C Connector                                                                                                                                                                                             |

| 20     | V5V      | AP           | Output of the internal LDO with VCC as input; a 1μF cap is required to connect this pin to GND. When VCC is off, V5V pin can be an alternative power path for the AP33772S when provided with a 5V external power. |

| 21     | NC       | -            | No Connection                                                                                                                                                                                                      |

| 22     | VOUT     | AHV          | Terminal for VOUT monitoring                                                                                                                                                                                       |

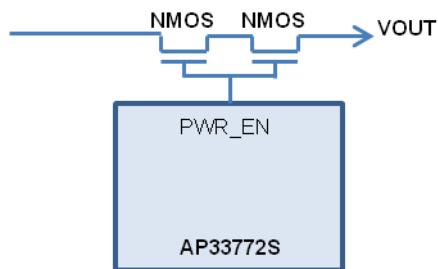

| 23     | PWR_EN   | AHV          | NMOS Switch gate control to switch the NMOS on or off                                                                                                                                                              |

| 24     | VCC      | AHV          | The power supply of the IC; a 1μF cap is required to connect this pin to GND pin                                                                                                                                   |

| -      | EPAD     | GND          | Exposed pad is suggested to connect to Ground for improved thermal dissipation                                                                                                                                     |

Table 1 – Pin Descriptions of the AP33772S PD Sink Controller

Notes:

- AHV – Analog High Voltage pin

- AP – Power for Analog Circuit and Analog I/O pins, 5.0V operation

- AI – Analog Input pin

- DP – Power for Digital Circuit operation

- AIO – Analog I/O pin with 5.0V operation; CC1/CC2 pins are 3.3V operation

- DIO – Digital I/O pin; all are 5.0V operation

- DI – Digital input pin; all are 5.0V operation

- DO – Digital output pin; all are 5.0V operation

## Chapter 3. EVB Hardware Details

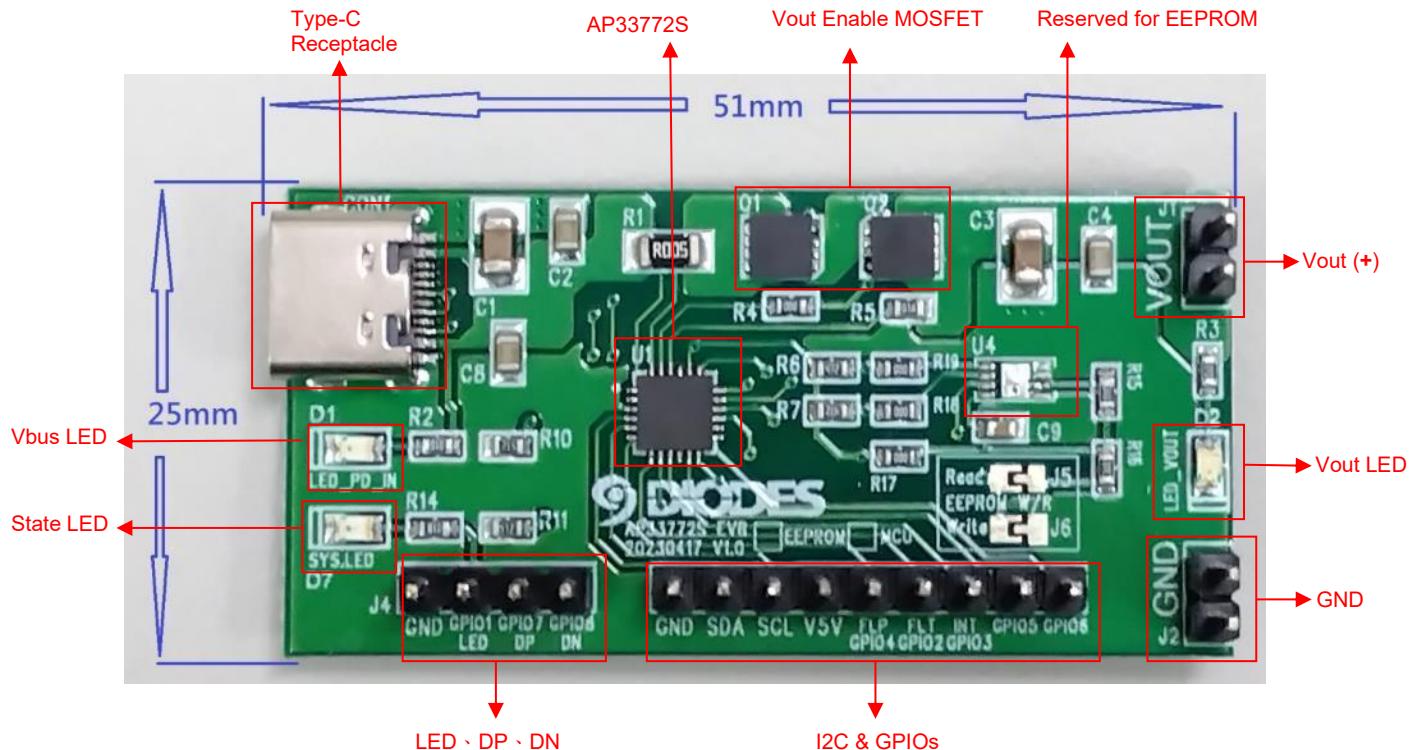

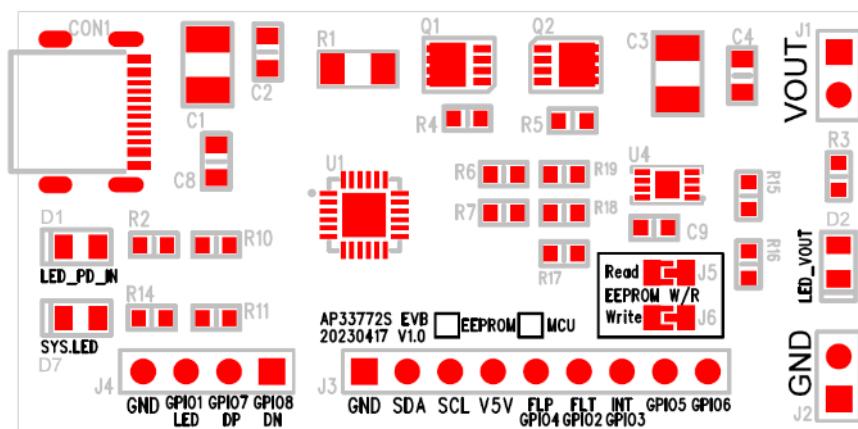

### 3.1 EVB TOP View

Figure 3 – AP33772S Evaluation Board top view and its key portions

### 3.2 EVB Block Diagram

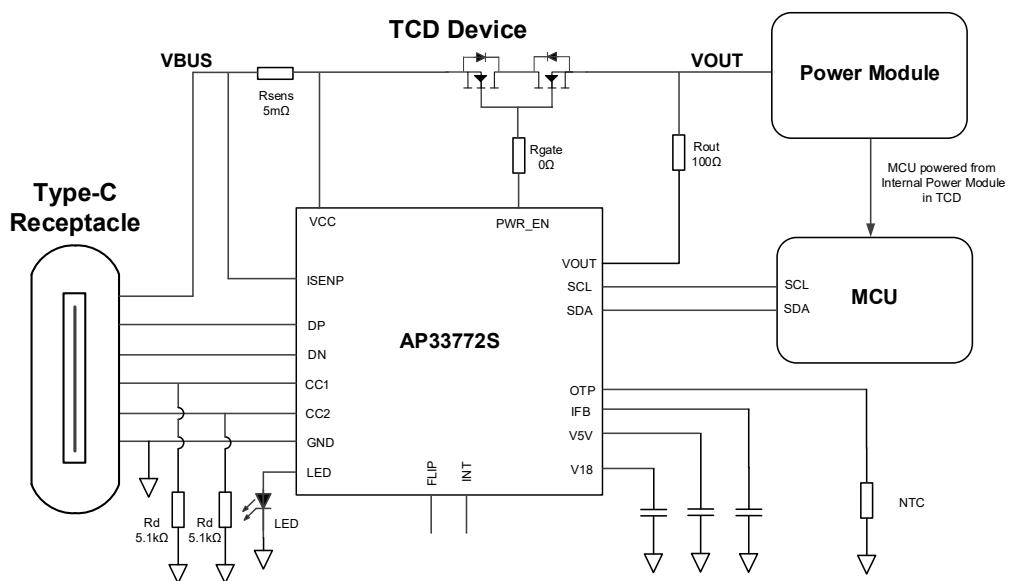

Figure 4 – AP33772S Evaluation Board Block Diagram

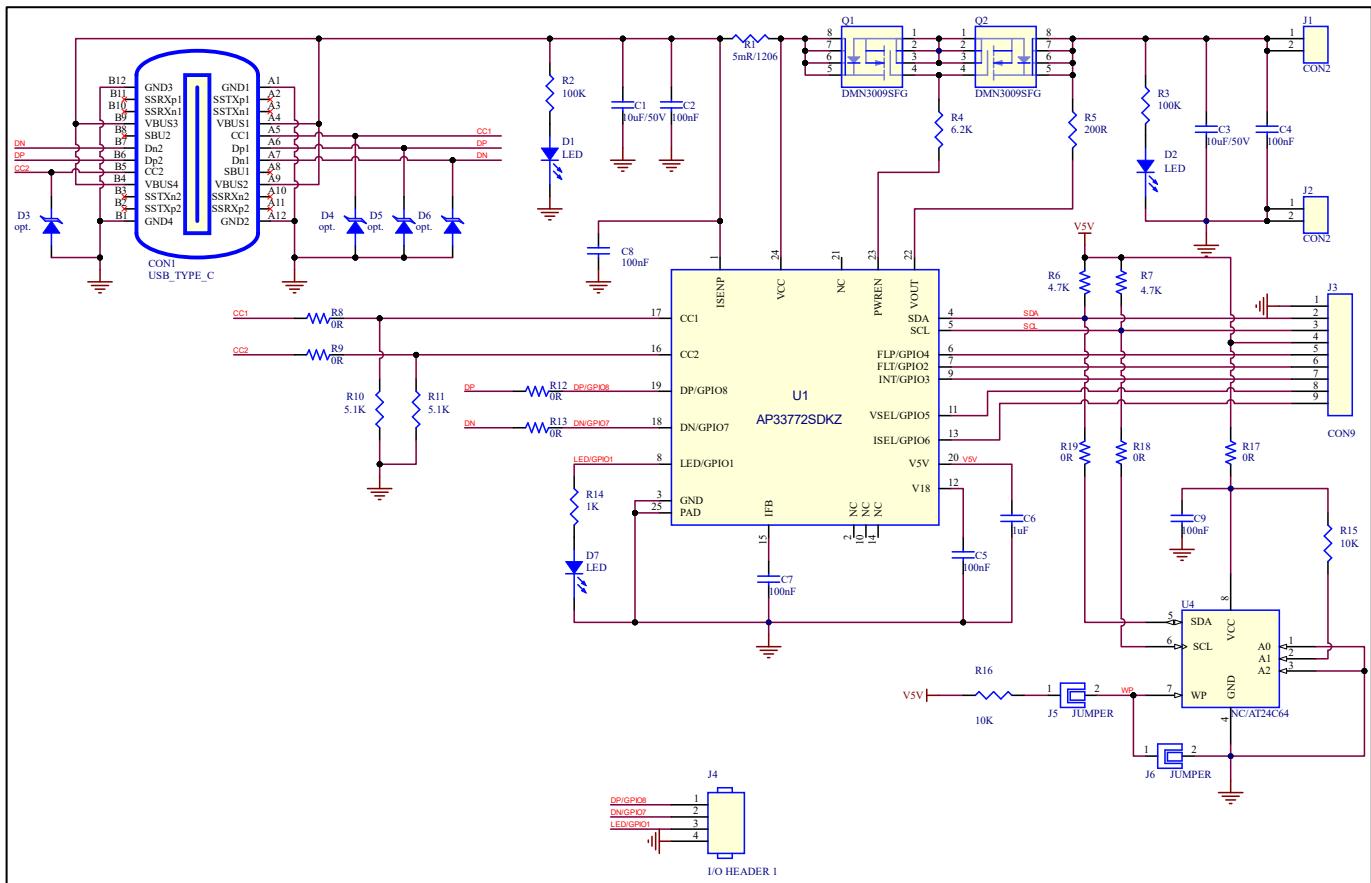

### 3.3 EVB Schematics

Figure 5 –Schematic of the AP33772S Evaluation Board

### 3.4 Board Outline

The AP33772S EVB outline and floor plan are shown in Figure 6, and the connector and jumper location are listed in Table 2.

Figure 6 – Connector and jumper locations

| Location | Function                               |

|----------|----------------------------------------|

| J1, J2   | VOUT and Load Connector                |

| J3       | I <sup>2</sup> C Bus & other test pins |

| J4       | DP, DN & other test pins               |

Table 2 – Jumpers and functions of the Evaluation Board

### 3.5 EVB System BOM

| Item | Quantity | Reference                       | Description                                     | Manufacturer Part Number | Manufacturer        |

|------|----------|---------------------------------|-------------------------------------------------|--------------------------|---------------------|

| 1    | 2        | C1, C3                          | 10 $\mu$ /50V                                   | -                        | -                   |

| 2    | 6        | C2, C4, C5, C7, C8, C9          | 0.1 $\mu$ /50V                                  | -                        | -                   |

| 3    | 1        | C6                              | 1 $\mu$ /50V                                    | -                        | -                   |

| 4    | 7        | R8, R9, R12, R13, R17, R18, R19 | 0R                                              | -                        | -                   |

| 5    | 1        | R4                              | 6.2K                                            |                          |                     |

| 6    | 1        | R5                              | 200R                                            | -                        | -                   |

| 7    | 1        | R14                             | 1K                                              | -                        | -                   |

| 8    | 2        | R6, R7                          | 4.7K                                            | -                        | -                   |

| 9    | 2        | R10, R11                        | 5.1K                                            | -                        | -                   |

| 10   | 2        | R15, R16                        | 10K                                             | -                        | -                   |

| 11   | 2        | R2, R3                          | 100K                                            | -                        | -                   |

| 12   | 1        | R1                              | 5mR/1W 1206                                     | SMD12A1FR005T            | SART Inc.           |

| 13   | 3        | D1, D2, D7                      | LED                                             | -                        | -                   |

| 14   | 2        | Q1, Q2                          | 30V/45A/4.4m $\Omega$ N-CH PowerDI3333-8        | DMN3009SFG               | Diodes Incorporated |

| 15   | 1        | U1                              | USB PD3.1 Sink Controller With I <sup>2</sup> C | AP33772S QFN-24          | Diodes Incorporated |

| 16   | 1        | U4                              | Reserved EEPROM solder location                 | N/A                      | N/A                 |

| 17   | 1        | CON1                            | USB Type-C Receptacle                           | -                        | -                   |

| 18   | 2        | J1, J2                          | VOUT & GND                                      | -                        | -                   |

| 19   | 2        | J3, J4                          | DP, DN, I <sup>2</sup> C, & other test pins     | -                        | -                   |

| 20   | 4        | D3~D6                           | Zener Diode (option)                            | N/A                      | N/A                 |

Table 3 – BOM list of the AP33772S EVB's schematics

## Chapter 4. EVB Quick Setup and Function Description

The AP33772S EVB provides users a convenient and flexible way to use power profile settings, as well as various status monitoring functions by the host MCU in the TCD through simple I2C interface pins (SCL and SDA).

### 4.1 Quick Setup Guide

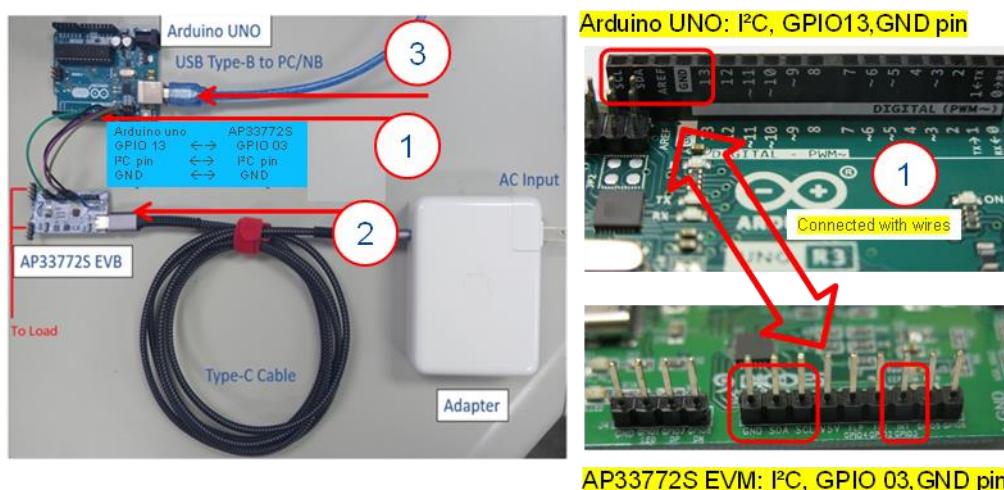

Hardware setup steps are shown in Figure 7.

Step1: Connect a Host System (using Arduino UNO for example) to the AP33772S EVB with the below pins.

|                                 |   |                                 |

|---------------------------------|---|---------------------------------|

| Arduino uno board               | ↔ | AP33772S EVB                    |

| GPIO 13 pin                     | ↔ | GPIO 03 pin                     |

| I <sup>2</sup> C pin (SDA, SCL) | ↔ | I <sup>2</sup> C pin (SDA, SCL) |

| GND pin                         | ↔ | GND pin                         |

Step 2: Connect the AP33772S EVB to a USB PD adaptor with a Type-C cable, and power on the AP33772S EVB.

Step 3: Connect the Arduino UNO board to a PC/NB with a Type-B cable, and power on the Arduino UNO board.

Figure 7 – AP33772S EVB Hardware Setup sequence

When using a Host System (single board computer or MCU-based system) with I2C interface pins (SDA, SCL) to connect to the AP33772S EVB, please make sure to power the AP33772S EVB board first before applying power to the Host System. The AP33772S EVB's power-sequencing requirement (being powered up first) is necessary due to the I2C design for the SDA and SCL pins.

## Step 1: Startup the GUI

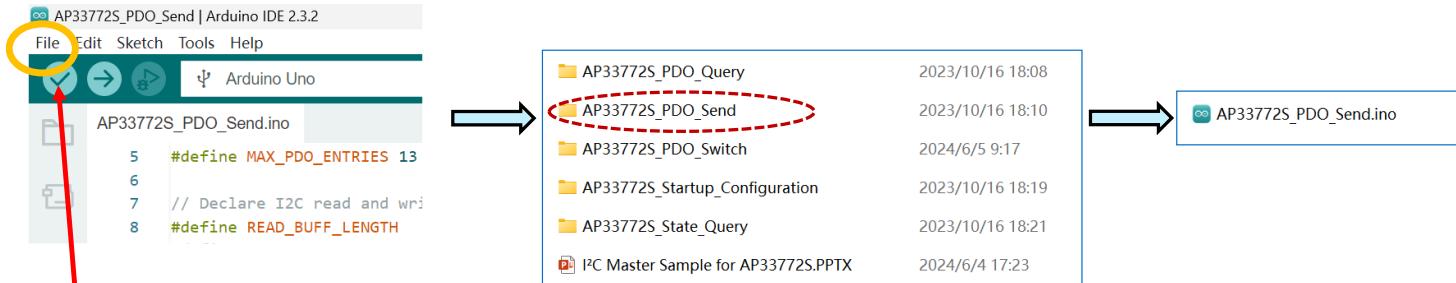

Arduino IDE

double-click the icon of Arduino on computer's desktop

Click "File" -> click "Open" -> click fold "AP33772S PDO\_Send" -> select file "AP33772S PDO\_Send.ino"

## Step 2: load the AP33772S PDO file

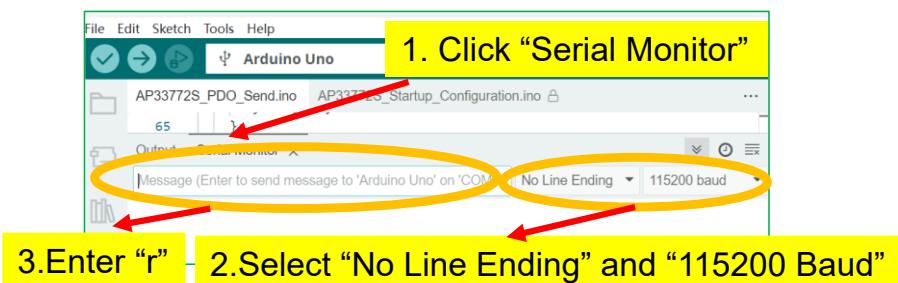

3. Enter "r"

2. Select "No Line Ending" and "115200 Baud"

## Step 3

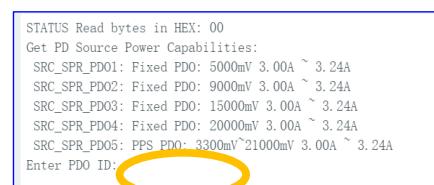

After Entering "r", PD Source Power Capabilities can be selected as above, if you want to choose PDO : 20000mV/3.00A~3.24A, You only need to Enter PDO ID "4"

## Step 4: select PDO

PDO is fixed, then you need to choose output current. If you need a 2.25A current, you can Enter "5". When you complete the confirmation of operating voltage and current, system output will become your target.

Step 5: select current

```

Enter PDO ID:

You entered PDO ID: 4

Operating Current Select:

0: 1.00A

1: 1.25A

2: 1.50A

3: 1.75A

4: 2.00A

5: 2.25A

6: 2.50A

7: 2.75A

8: 3.00A

9: 3.25A

10: 3.50A

11: 3.75A

12: 4.00A

13: 4.25A

14: 4.50A

15: 5.00A

```

```

You entered PDO ID: 4

Operating Current Select:

0: 1.00A

1: 1.25A

2: 1.50A

3: 1.75A

4: 2.00A

5: 2.25A

6: 2.50A

7: 2.75A

8: 3.00A

9: 3.25A

10: 3.50A

11: 3.75A

12: 4.00A

13: 4.25A

14: 4.50A

15: 5.00A

You entered current: 5

I2C_SFR_PDO4 : status=0x02 RESPONSE=Success V=19920mV I=48mA T=0° C

```

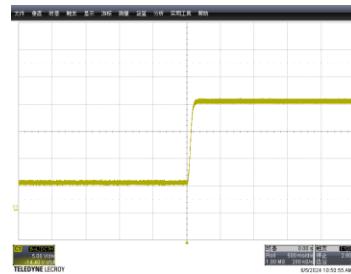

Step 6: output successfully

### 4.2 Application Circuit Description

#### Sensing of Input Current

As shown in the figure above, the sense resistor is connected in series to detect the charging current. The ISENP pin is connected to the input side of the sense resistor, and the VCC pin is connected to the other side. The AP33772S detects the current by measuring the voltage drop across the current sense resistor.

#### Use of Back-to-Back N-MOS Chips

The common-source back-to-back N-MOSFET in the battery-pack protection-circuit module controls charging and plays a protective role in the occurrence of failures that may damage electrical appliances, such as overvoltage, overcurrent, and overtemperature. The back-to-back N-MOSFET control is also used to prevent backward current flows through the system when unplugging the cable from the PD charger.

#### Temperature-Sensing Circuitry

A 10k $\Omega$  NTC (negative temperature coefficient) thermistor is connected to the OTP pin and grounded nearby the potential hot spot. The characteristic data of the NTC thermistor's temperature and resistance values need to be set by the user through I2C. Then the host MCU can read and calculate the temperature and enable OTP (overtemperature protection) and de-rating functions through the I2C interface.

## LED Light Indication Circuitry

The LED light and resistor are used to connect the LED pin and ground. The LED charging indication light starts to breathe at a speed matching the battery's quick-charging pace.

## I2C Support

The AP33772S's supports I2C Interface and is used to communicate with the TCD's host MCU. The I2C pins are listed below in Table 4 and are used to set the AP33772S's register data such as Initialization, PDO, APDO, OCP, OTP, temperature, de-rating, interrupt, and so on. The AP33772S's operating status can also be monitored at the same time.

Meanwhile, INT is used as a fault-report channel to the Interrupt input pin of the host MCU, in case of any fault occurrence requiring immediate action from the host MCU.

For the I2C commands and registers, please refer to Chapter 5.

| Pin No. | Pin Name | Pin Function                       |

|---------|----------|------------------------------------|

| 4       | SDA      | I2C Data                           |

| 5       | SCL      | I2C Clock                          |

| 9       | INT      | Issue an interrupt to the host MCU |

Table 4 – I2C interface pin list

## Chapter 5. I2C Command/Register Summary

As an I2C slave device, the AP33772S's physical address is 0x52. All AP33772S I2C-related control operations and commands are summarized in this chapter.

### 5.1 I2C Command Format

#### Device Address Format

| Bit7     | Bit6     | Bit5     | Bit4     | Bit3     | Bit2     | Bit1     | Bit0 |

|----------|----------|----------|----------|----------|----------|----------|------|

| DevAddr6 | DevAddr5 | DevAddr4 | DevAddr3 | DevAddr2 | DevAddr1 | DevAddr0 | R/W  |

| 1        | 0        | 1        | 0        | 0        | 1        | 0        | 1/0  |

#### Command Format

| Bit7    | Bit6    | Bit5    | Bit4    | Bit3    | Bit2    | Bit1    | Bit0    |

|---------|---------|---------|---------|---------|---------|---------|---------|

| CmdBit7 | CmdBit6 | CmdBit5 | CmdBit4 | CmdBit3 | CmdBit2 | CmdBit1 | CmdBit0 |

#### Data Format

| Bit7     | Bit6     | Bit5     | Bit4     | Bit3     | Bit2     | Bit1     | Bit0     |

|----------|----------|----------|----------|----------|----------|----------|----------|

| DataBit7 | DataBit6 | DataBit5 | DataBit4 | DataBit3 | DataBit2 | DataBit1 | DataBit0 |

## 5.2 I2C Operation

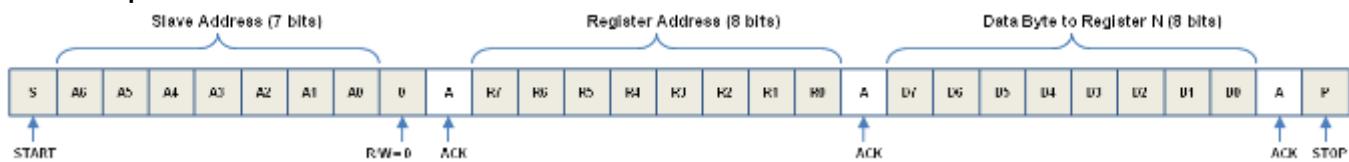

### I2C Write Operation

### I2C Read Operation

## 5.3 Register Summary

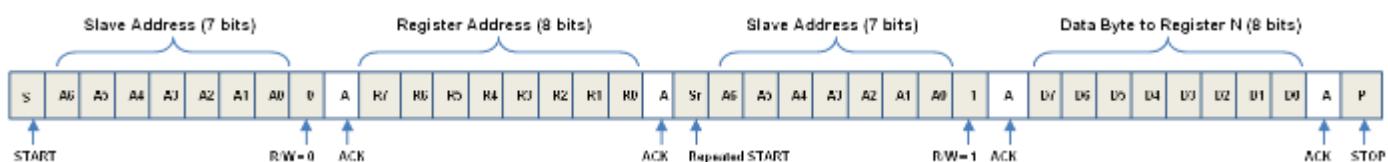

The memory representation of multibyte data types on the AP33772S is in a little-endian byte order: the least significant byte (the "little end") of the data is placed at the byte with the lowest address.

Suppose the integer is stored as 4 bytes, then a variable X with a value of 0x12345678 will be stored as the following.

| Register      | Command | Length | Attribute | Pwr-on  | Description                                                                     |

|---------------|---------|--------|-----------|---------|---------------------------------------------------------------------------------|

| STATUS        | 0x01    | 1      | RC        | 00h     | Status                                                                          |

| MASK          | 0x02    | 1      | RW        | 03h     | Interrupt enable mask                                                           |

| OPMODE        | 0x03    | 1      | RO        | 00h     | Operation mode                                                                  |

| CONFIG        | 0x04    | 1      | RW        | F8h     | System configuration options                                                    |

| PDCONFIG      | 0x05    | 1      | RW        | 03h     | PD mode configuration options                                                   |

| SYSTEM        | 0x06    | 1      | RO/RW     | 10h     | System control and information                                                  |

| TR25          | 0x0C    | 2      | RW        | 2710h   | Thermal Resistance @25°C, Unit: Ω                                               |

| TR50          | 0x0D    | 2      | RW        | 1041h   | Thermal Resistance @50°C, Unit: Ω                                               |

| TR75          | 0x0E    | 2      | RW        | 0788h   | Thermal Resistance @75°C, Unit: Ω                                               |

| TR100         | 0x0F    | 2      | RW        | 03CEh   | Thermal Resistance @100°C, Unit: Ω                                              |

| VOLTAGE       | 0x11    | 2      | RO        | 0000h   | The VOUT Voltage, LSB 80mV                                                      |

| CURRENT       | 0x12    | 1      | RO        | 00h     | The VOUT Current, LSB 24mA                                                      |

| TEMP          | 0x13    | 1      | RO        | 19h     | Temperature, Unit: °C<br>The default value is 19h (25°C).                       |

| VREQ          | 0x14    | 2      | RO        | 0000h   | The latest requested voltage negotiated with the source, LSB 50mV               |

| IREQ          | 0x15    | 2      | RO        | 0000h   | The latest requested current negotiated with the source, LSB 10mA               |

| VSELMIN       | 0x16    | 1      | RW        | 19h     | The Minimum Selection Voltage, LSB 200mV<br>The default value is 19h (5000mV).  |

| UVPTHR        | 0x17    | 1      | RW        | 01h     | UVP Threshold, percentage(%) of VREQ<br>The default value is 01h (80%).         |

| OVPTHR        | 0x18    | 1      | RW        | 19h     | OVP Threshold, offset from VREQ. LSB 80mV<br>The default value is 19h (2000mV). |

| OCPTHR        | 0x19    | 1      | RW        | 00h     | OCP Threshold, LSB 50mA                                                         |

| OTPTHR        | 0x1A    | 1      | RW        | 78h     | OTP Threshold, Unit: °C<br>The default value is 78h (120°C).                    |

| DRTHR         | 0x1B    | 1      | RW        | 78h     | De-Rating Threshold, Unit: °C<br>The default value is 78h (120°C).              |

| SRCPDO        | 0x20    | 26     | RO        | All 00h | Get all PD Source Power Capabilities<br>(SRC_SPR_PDO1 ~ SRC_EPR_PDO13)          |

| SRC_SPR_PDO1  | 0x21    | 2      | RO        | 0000h   | Source SPR PDO1                                                                 |

| SRC_SPR_PDO2  | 0x22    | 2      | RO        | 0000h   | Source SPR PDO2                                                                 |

| SRC_SPR_PDO3  | 0x23    | 2      | RO        | 0000h   | Source SPR PDO3                                                                 |

| SRC_SPR_PDO4  | 0x24    | 2      | RO        | 0000h   | Source SPR PDO4                                                                 |

| SRC_SPR_PDO5  | 0x25    | 2      | RO        | 0000h   | Source SPR PDO5                                                                 |

| SRC_SPR_PDO6  | 0x26    | 2      | RO        | 0000h   | Source SPR PDO6                                                                 |

| SRC_SPR_PDO7  | 0x27    | 2      | RO        | 0000h   | Source SPR PDO7                                                                 |

| SRC_EPR_PDO8  | 0x28    | 2      | RO        | 0000h   | Source EPR PDO8                                                                 |

| SRC_EPR_PDO9  | 0x29    | 2      | RO        | 0000h   | Source EPR PDO9                                                                 |

| SRC_EPR_PDO10 | 0x2A    | 2      | RO        | 0000h   | Source EPR PDO10                                                                |

| SRC_EPR_PDO11 | 0x2B    | 2      | RO        | 0000h   | Source EPR PDO11                                                                |

| SRC_EPR_PDO12 | 0x2C    | 2      | RO        | 0000h   | Source EPR PDO12                                                                |

| SRC_EPR_PDO13 | 0x2D    | 2      | RO        | 0000h   | Source EPR PDO13                                                                |

| PD_REQMSG     | 0x31    | 2      | WO        | 0000h   | Send request message with selected voltage, current and PDO index               |

| PD_CMDSMSG    | 0x32    | 1      | WO        | 00h     | Send specific PD command message                                                |

| PD_MSGRLT     | 0x33    | 1      | RO        | 00h     | Result and status of PD request or command message                              |

Table 5 – AP33772S Register Summary

Attribute Convention

RW: Readable / Writable

RO: Read-Only

RC: Read-Clear

WO: Write-Only

### 5.4 Register Description

#### STATUS

The host MCU, working as an I2C master, can access the status of the AP33772S through the STATUS register. The STATUS register will be reset to 0 after a read operation.

| STATUS  | Bit | Attribute | Pwr-on | Description                                                                          |

|---------|-----|-----------|--------|--------------------------------------------------------------------------------------|

| -       | 7   | RC        | 0h     | Reserved                                                                             |

| OTP     | 6   | RC        | 0h     | 1: OTP status                                                                        |

| OCP     | 5   | RC        | 0h     | 1: OCP status                                                                        |

| OVP     | 4   | RC        | 0h     | 1: OVP status                                                                        |

| UVP     | 3   | RC        | 0h     | 1: UVP status                                                                        |

| NEW PDO | 2   | RC        | 0h     | 1: New source PDOs received (Valid when PDMOD = 1)                                   |

| READY   | 1   | RC        | 0h     | 1: Ready to receive I2C request/command                                              |

| STARTED | 0   | RC        | 0h     | 1: System started. Allow system configuration (register) to be updated within 100ms. |

#### MASK

The AP33772S supports a level-triggered interrupt signal through the INT pin to the host MCU. The MASK register defines the enable and disable of ON and OFF for various STATUS-defined events.

| MASK        | Bit | Attribute | Pwr-on | Description            |

|-------------|-----|-----------|--------|------------------------|

| -           | 7   | RW        | 0h     | Reserved               |

| OTP_MSK     | 6   | RW        | 0h     | 1: OTP status mask     |

| OCP_MSK     | 5   | RW        | 0h     | 1: OCP status mask     |

| OVP_MSK     | 4   | RW        | 0h     | 1: OVP status mask     |

| UVP_MSK     | 3   | RW        | 0h     | 1: UVP status mask     |

| NEW PDO_MSK | 2   | RW        | 0h     | 1: NEW PDO status mask |

| READY_MSK   | 1   | RW        | 1h     | 1: READY status mask   |

| STARTED_MSK | 0   | RW        | 1h     | 1: STARTED status mask |

#### OPMODE

The OPMODE register is defined as the AP33772S's operation mode.

When CCFLIP = 1, the CC2 is connected to the CC line.

When DR = 1, the AP33772S works in de-rating (DR) mode.

When PDMOD = 1, the AP33772S works in PD mode.

When LGCYMOD = 1, the AP33772S works in Legacy mode (non-PD).

| OPMODE  | Bit | Attribute | Pwr-on | Description                                                                         |

|---------|-----|-----------|--------|-------------------------------------------------------------------------------------|

| CCFLIP  | 7   | RO        | 0h     | 0: CC1 is connected to CC line or unattached mode<br>1: CC2 is connected to CC line |

| DR      | 6   | RO        | 0h     | 0: Normal mode<br>1: DR (de-rating) mode                                            |

| -       | 5   | RO        | 0h     | Reserved                                                                            |

| -       | 4   | RO        | 0h     | Reserved                                                                            |

| -       | 3   | RO        | 0h     | Reserved                                                                            |

| -       | 2   | RO        | 0h     | Reserved                                                                            |

| PDMOD   | 1   | RO        | 0h     | 1: PD source connected                                                              |

| LGCYMOD | 0   | RO        | 0h     | 1: Legacy source connected (non-PD)                                                 |

## CONFIG

The CONFIG register is defined as the system configuration options that enable specific modules.

| CONFIG | Bit | Attribute | Pwr-on | Description                      |

|--------|-----|-----------|--------|----------------------------------|

| DR_EN  | 7   | RW        | 1h     | 0/1: Disable/enable DR function  |

| OTP_EN | 6   | RW        | 1h     | 0/1: Disable/enable OTP function |

| OCP_EN | 5   | RW        | 1h     | 0/1: Disable/enable OCP function |

| OVP_EN | 4   | RW        | 1h     | 0/1: Disable/enable OVP function |

| UVP_EN | 3   | RW        | 1h     | 0/1: Disable/enable UVP function |

| -      | 2   | RW        | 0h     | Reserved                         |

| -      | 1   | RW        | 0h     | Reserved                         |

| -      | 0   | RW        | 0h     | Reserved                         |

## PDCONFIG

The PDCONFIG register is defined as the PD mode configuration options that enable specific modules.

| PDCONFIG    | Bit | Attribute | Pwr-on | Description                                     |

|-------------|-----|-----------|--------|-------------------------------------------------|

| -           | 7:4 | RW        | 0h     | Reserved                                        |

| -           | 3   | RW        | 0h     | Reserved                                        |

| -           | 2   | RW        | 0h     | Reserved                                        |

| PPS_AV_S_EN | 1   | RW        | 1h     | 0/1: Disable/Enable sink PPS and AVS capability |

| EPR_MODE_EN | 0   | RW        | 1h     | 0/1: Disable/Enable EPR mode                    |

## SYSTEM

The SYSTEM register is defined as the system information and control options that request specific functions.

By default, the VOUT MOS switches are controlled by the AP33772S. Writing the VOUTCTL parameter can force the VOUT MOS switches to turn OFF/ON.

| SYSTEM  | Bit | Attribute | Pwr-on | Description                                                                                                                                                |

|---------|-----|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -       | 7   | RO        | 0h     | Reserved                                                                                                                                                   |

| -       | 6   | RO        | 0h     | Reserved                                                                                                                                                   |

| CMDVER  | 5:4 | RO        | 1h     | I2C Command Version<br>1: Version 1.0<br>others: Reserved, shall not be used                                                                               |

| -       | 3   | RW        | 0h     | Reserved                                                                                                                                                   |

| -       | 2   | RW        | 0h     | Reserved                                                                                                                                                   |

| VOUTCTL | 1:0 | RW        | 0h     | VOUT control option switch<br>0: Auto VOUT Control (controlled by the AP33772S)<br>1: VOUT force OFF<br>2: VOUT force ON<br>3: Reserved, shall not be used |

## TR25

The TR25 register is defined as the resistance value of the NTC thermistor at 25°C (unit: Ω).

| TR25 | Bit  | Attribute | Pwr-on | Description                                                                                         |

|------|------|-----------|--------|-----------------------------------------------------------------------------------------------------|

| TR25 | 15:0 | RW        | 2710h  | The resistance value of the NTC thermistor at 25°C (unit: Ω)<br>The default value is 2710h (10000Ω) |

## TR50

The TR50 register is defined as the resistance value of the NTC thermistor at 50°C (unit: Ω).

| TR50 | Bit  | Attribute | Pwr-on | Description                                                                                        |

|------|------|-----------|--------|----------------------------------------------------------------------------------------------------|

| TR50 | 15:0 | RW        | 1041h  | The resistance value of the NTC thermistor at 50°C (unit: Ω)<br>The default value is 1041h (4161Ω) |

## TR75

The TR75 register is defined as the resistance value of the NTC thermistor at 75°C (unit: Ω).

| TR75 | Bit  | Attribute | Pwr-on | Description                                                                                        |

|------|------|-----------|--------|----------------------------------------------------------------------------------------------------|

| TR75 | 15:0 | RW        | 0788h  | The resistance value of the NTC thermistor at 75°C (unit: Ω)<br>The default value is 0788h (1928Ω) |

## TR100

The TR100 register is defined as the resistance value of the NTC thermistor at 100°C (unit: Ω).

| TR100 | Bit  | Attribute | Pwr-on | Description                                                                                        |

|-------|------|-----------|--------|----------------------------------------------------------------------------------------------------|

| TR100 | 15:0 | RW        | 03CEh  | The resistance value of the NTC thermistor at 100°C (unit: Ω)<br>The default value is 03CEh (974Ω) |

## VOLTAGE

The VOLTAGE register is defined as the voltage of VOUT. The LSB (least significant bit) is 80mV.

| VOLTAGE | Bit  | Attribute | Pwr-on | Description                   |

|---------|------|-----------|--------|-------------------------------|

| VOLTAGE | 15:0 | RO        | 0000h  | The VOUT voltage; LSB is 80mV |

## CURRENT

The CURRENT register is defined as the current of VOUT. The LSB is 24mA.

| CURRENT | Bit | Attribute | Pwr-on | Description                   |

|---------|-----|-----------|--------|-------------------------------|

| CURRENT | 7:0 | RO        | 00h    | The VOUT current; LSB is 24mA |

## TEMP

The TEMP register is defined as the temperature near the NTC thermistor. The unit is °C. The default value is 19h (25°C).

| TEMP | Bit | Attribute | Pwr-on | Description                                                                       |

|------|-----|-----------|--------|-----------------------------------------------------------------------------------|

| TEMP | 7:0 | RO        | 19h    | Temperature near the NTC thermistor (unit: °C)<br>The default value is 19h (25°C) |

## VREQ

The VREQ register is defined as the latest request voltage, which depends on the PD negotiation result after setting the request message (PD\_REQMSG). The LSB is 50mV.

The Host MCU writes PD\_REQMSG and will initiate a PD negotiation process. If negotiation is successful (PD\_MSGRLT.RESPONSE = 1), VREQ will be updated to the requested voltage (PD\_REQMSG.VOLTAGE\_SEL). If negotiation is unsuccessful, VREQ will not be updated.

| VREQ | Bit  | Attribute | Pwr-on | Description                                                                                                                     |

|------|------|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------|

| VREQ | 15:0 | RO        | 0000h  | The latest requested voltage; LSB 50mV<br>The value depends on the PD negotiation result after setting PD_REQMSG (VOLTAGE_SEL). |

## IREQ

The IREQ register is defined as the latest request current, which depends on the PD negotiation result after setting the request message (PD\_REQMSG). The LSB is 10mA.

If negotiation is successful (PD\_MSGRLT.RESPONSE=1), IREQ will be updated to the requested current (PD\_REQMSG.CURRENT\_SEL). If negotiation is unsuccessful, IREQ will not be updated.

| IREQ | Bit  | Attribute | Pwr-on | Description                                                                                                                     |

|------|------|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------|

| IREQ | 15:0 | RO        | 0000h  | The latest requested current; LSB 10mA<br>The value depends on the PD negotiation result after setting PD_REQMSG (CURRENT_SEL). |

## VSELMIN

The VSELMIN register is defined as the Minimum Selection Voltage. If the VREQ voltage is more than or equal to the VSELMIN voltage, the VOUT MOS switches turn ON after the system is ready (STATUS.READY = 1). The default value for VSELMIN is 19h (5000mV) and the LSB is 200mV.

| VSELMIN | Bit | Attribute | Pwr-on | Description                                                                                                                                                                           |

|---------|-----|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSELMIN | 7:0 | RW        | 19h    | The Minimum Selection Voltage; the LSB is 200mV.<br>If $V_{VREQ} \geq V_{VSELMIN}$ , VOUT MOS switches turn on after system is ready (READY=1).<br>The default value is 19h (5000mV). |

## UVPTHR

The UVPTHR register is defined as the UVP Threshold Voltage that triggers UVP protection function. The UVP Threshold Voltage is the UVPTHR percentage (%) of the VREQ voltage. The default value for the UVPTHR is 01h (80%). Please refer to the “Undervoltage Protection” section for more details.

| UVPTHR | Bit | Attribute | Pwr-on | Description                                                                                                                                                                          |

|--------|-----|-----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -      | 7:4 | RW        | 0h     | Reserved                                                                                                                                                                             |

| UVPTHR | 3:0 | RW        | 1h     | The UVP Threshold Voltage is UVPTHR percentage (%) of VREQ voltage (unit: %)<br>1: 80%<br>2: 75%<br>3: 70%<br>Others: Reserved, shall not be used<br>The default value is 01h (80%). |

## OVPTHR

The OVPTHR register is defined as the OVP Threshold Voltage that triggers OVP protection function. The OVP Threshold Voltage is the VREQ voltage plus the OVPTHR offset voltage (mV). The default value for the OVPTHR is 19h (2000mV) and the LSB is 80mV. Please refer to the “Overvoltage Protection” section for more details.

| OVPTHR | Bit | Attribute | Pwr-on | Description                                                                                                                                                                                                           |

|--------|-----|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OVPTHR | 7:0 | RW        | 19h    | The OVP Threshold Voltage is the VREQ voltage plus OVPTHR offset voltage (mV); the LSB is 80mV.<br>The default value is 19h (2000mV), which means the OVP Threshold Voltage is $V_{VREQ} + 2000\text{mV}$ by default. |

### OCPTHR

The OCPTHR register is defined as the OCP Threshold Current that triggers OCP protection function. The OCP Threshold Current is 110% of the OCPTHR current value. The default value for the OCPTHR is 00h and the LSB is 50mA.

If the OCPTHR is set to 0, the OCP Threshold Current will be updated to 110% of the selected PDO maximum current after successful negotiation with the PD source. Please refer to the “Overcurrent Protection” section for more details.

| OCPTHR | Bit | Attribute | Pwr-on | Description                                                                                                                                                                                                                                  |

|--------|-----|-----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OCPTHR | 7:0 | RW        | 00h    | The OCP Threshold Current is 110% of the OCPTHR current value; the LSB is 50mA.<br>The default value is 00h, which means the OCP Threshold Current will be updated to 110% of the selected PDO maximum current after successful negotiation. |

### OTPTHR

The OTPTHR register is defined as the OTP Threshold Temperature (°C) that triggers OTP protection function. The default value for the OTPTHR is 78h (120°C). Please refer to the “Overtemperature Protection and De-Rating” section for more details.

| OTPTHR | Bit | Attribute | Pwr-on | Description                                                                                                                           |

|--------|-----|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------|

| OTPTHR | 7:0 | RW        | 78h    | OTP Threshold Temperature (unit: °C)<br>The temperature threshold triggers OTP function; the default value for OTPTHR is 78h (120°C). |

### DRTHR

The DRTHR register is defined as the De-Rating Threshold Temperature (°C) that triggers the De-Rating function. The default value for the DRTHR is 78h (120°C). Please refer to the “Overtemperature Protection and De-Rating” section for more details.

| DRTHR | Bit | Attribute | Pwr-on | Description                                                                                                                                      |

|-------|-----|-----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| DRTHR | 7:0 | RW        | 78h    | De-Rating Threshold Temperature (unit: °C)<br>The temperature threshold triggers De-Rating function; the default value for DRTHR is 78h (120°C). |

### SRC PDO

The SRC PDO register can obtain all of the PD Source Power Capabilities and has a total length of 28 bytes.

| SRC PDO       | Byte  | Attribute | Pwr-on | Description                                                      |

|---------------|-------|-----------|--------|------------------------------------------------------------------|

| SRC_EPR_PDO13 | 25:24 | RO        | 0000h  | For data format, refer to<br><b>SRC_EPR_PDO8 ~ SRC_EPR_PDO13</b> |

| SRC_EPR_PDO12 | 23:22 | RO        | 0000h  |                                                                  |

| SRC_EPR_PDO11 | 21:20 | RO        | 0000h  |                                                                  |

| SRC_EPR_PDO10 | 19:18 | RO        | 0000h  |                                                                  |

| SRC_EPR_PDO9  | 17:16 | RO        | 0000h  |                                                                  |

| SRC_EPR_PDO8  | 15:14 | RO        | 0000h  |                                                                  |

| SRC_SPR_PDO7  | 13:12 | RO        | 0000h  | For data format, refer to<br><b>SRC_SPR_PDO1 ~ SRC_SPR_PDO7</b>  |

| SRC_SPR_PDO6  | 11:10 | RO        | 0000h  |                                                                  |

| SRC_SPR_PDO5  | 9:8   | RO        | 0000h  |                                                                  |

| SRC_SPR_PDO4  | 7:6   | RO        | 0000h  |                                                                  |

| SRC_SPR_PDO3  | 5:4   | RO        | 0000h  |                                                                  |

| SRC_SPR_PDO2  | 3:2   | RO        | 0000h  |                                                                  |

| SRC_SPR_PDO1  | 1:0   | RO        | 0000h  |                                                                  |

## SRC\_SPR\_PDO1 ~ SRC\_SPR\_PDO7

The SRC\_SPR\_PDO register can obtain the PD Source SPR PDO of a specific index; each length is 2 bytes. The structure of the SRC\_SPR\_PDO register is as follows:

| SRC_SPR_PDO                       | Bit   | Attribute | Pwr-on | Description                                                                                                                                                                                                                                                                                                                                                      |                                                                                                   |

|-----------------------------------|-------|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| DETECT                            | 15    | RO        | 0h     | 0: Not detected<br>1: Detected                                                                                                                                                                                                                                                                                                                                   |                                                                                                   |

| TYPE                              | 14    | RO        | 0h     | 0: Fixed PDO<br>1: PPS APDO                                                                                                                                                                                                                                                                                                                                      |                                                                                                   |

| CURRENT_MAX                       | 13:10 | RO        | 0h     | 0: 0.00A ~ 1.24A (Less than 1.24A)<br>1: 1.25A ~ 1.49A<br>2: 1.50A ~ 1.74A<br>3: 1.75A ~ 1.99A<br>4: 2.00A ~ 2.24A<br>5: 2.25A ~ 2.49A<br>6: 2.50A ~ 2.74A<br>7: 2.75A ~ 2.99A<br>8: 3.00A ~ 3.24A<br>9: 3.25A ~ 3.49A<br>10: 3.50A ~ 3.74A<br>11: 3.75A ~ 3.99A<br>12: 4.00A ~ 4.24A<br>13: 4.25A ~ 4.49A<br>14: 4.50A ~ 4.99A<br>15: 5.00A ~ (More than 5.00A) |                                                                                                   |

| PEAK_CURRENT<br>or<br>VOLTAGE_MIN | 9:8   | RO        | 0h     | PEAK_CURRENT                                                                                                                                                                                                                                                                                                                                                     | VOLTAGE_MIN                                                                                       |

|                                   |       |           |        | For Fixed PDO (bit[14]=0)<br>Peak Current                                                                                                                                                                                                                                                                                                                        | For PPS APDO (bit[14]=1)<br>0 : Reserved<br>1 : 3.3V<br>2 : 3.3V < VOLTAGE_MIN ≤ 5V<br>3 : others |

| VOLTAGE_MAX                       | 7:0   | RO        | 0h     | If bit[14]=0 (Fixed PDO) :<br>Voltage in 100mV units<br>If bit[14]=1 (PPS APDO) :<br>Maximum Voltage in 100mV units                                                                                                                                                                                                                                              |                                                                                                   |

## SRC\_EPR\_PDO8 ~ SRC\_EPR\_PDO13

The SRC\_EPR\_PDO register can obtain the PD Source EPR PDO of a specific index; each length is 2 bytes. The structure of the SRC\_EPR\_PDO register is as follows:

| SRC_EPR_PDO                       | Bit   | Attribute | Pwr-on | Description                                                                                                                                                                                                                                                                                                                                                      |                                                                                                  |

|-----------------------------------|-------|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| DETECT                            | 15    | RO        | 0h     | 0: Not detected<br>1: Detected                                                                                                                                                                                                                                                                                                                                   |                                                                                                  |

| TYPE                              | 14    | RO        | 0h     | 0: Fixed PDO<br>1: AVS APDO                                                                                                                                                                                                                                                                                                                                      |                                                                                                  |

| CURRENT_MAX                       | 13:10 | RO        | 0h     | 0: 0.00A ~ 1.24A (Less than 1.24A)<br>1: 1.25A ~ 1.49A<br>2: 1.50A ~ 1.74A<br>3: 1.75A ~ 1.99A<br>4: 2.00A ~ 2.24A<br>5: 2.25A ~ 2.49A<br>6: 2.50A ~ 2.74A<br>7: 2.75A ~ 2.99A<br>8: 3.00A ~ 3.24A<br>9: 3.25A ~ 3.49A<br>10: 3.50A ~ 3.74A<br>11: 3.75A ~ 3.99A<br>12: 4.00A ~ 4.24A<br>13: 4.25A ~ 4.49A<br>14: 4.50A ~ 4.99A<br>15: 5.00A ~ (More than 5.00A) |                                                                                                  |

| PEAK_CURRENT<br>or<br>VOLTAGE_MIN | 9:8   | RO        | 0h     | PEAK_CURRENT                                                                                                                                                                                                                                                                                                                                                     | VOLTAGE_MIN                                                                                      |

|                                   |       |           |        | For Fixed PDO (bit[14]=0)<br>Peak Current                                                                                                                                                                                                                                                                                                                        | For AVS APDO (bit[14]=1)<br>0 : Reserved<br>1 : 15V<br>2 : 15V < VOLTAGE_MIN ≤ 20V<br>3 : others |

| VOLTAGE_MAX                       | 7:0   | RO        | 0h     | If bit[14]=0 (Fixed PDO) :<br>Voltage in 200mV units<br>If bit[14]=1 (AVS APDO) :<br>Maximum Voltage in 200mV units                                                                                                                                                                                                                                              |                                                                                                  |

| Bits 9...8 | Description for PEAK_CURRENT                                                                                                                                                                                                                                                                                                                               |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00         | Peak current equals $I_{OC}$ (default)<br>or look at extended Source capabilities                                                                                                                                                                                                                                                                          |

| 01         | Overload Capabilities:<br>1. Peak current equals 150% $I_{OC}$ for 1ms @ 5% duty cycle (low current equals 97% $I_{OC}$ for 19ms)<br>2. Peak current equals 125% $I_{OC}$ for 2ms @ 10% duty cycle (low current equals 97% $I_{OC}$ for 18ms)<br>3. Peak current equals 110% $I_{OC}$ for 10ms @ 50% duty cycle (low current equals 90% $I_{OC}$ for 10ms) |

| 10         | Overload Capabilities:<br>1. Peak current equals 200% $I_{OC}$ for 1ms @ 5% duty cycle (low current equals 95% $I_{OC}$ for 19ms)<br>2. Peak current equals 150% $I_{OC}$ for 2ms @ 10% duty cycle (low current equals 94% $I_{OC}$ for 18ms)<br>3. Peak current equals 125% $I_{OC}$ for 10ms @ 50% duty cycle (low current equals 75% $I_{OC}$ for 10ms) |

| 11         | Overload Capabilities:<br>1. Peak current equals 200% $I_{OC}$ for 1ms @ 5% duty cycle (low current equals 95% $I_{OC}$ for 19ms)<br>2. Peak current equals 175% $I_{OC}$ for 2ms @ 10% duty cycle (low current equals 92% $I_{OC}$ for 18ms)<br>3. Peak current equals 150% $I_{OC}$ for 10ms @ 50% duty cycle (low current equals 50% $I_{OC}$ for 10ms) |

loc: The Operating Current of an RDO (The Operating Current Select parameter of PD\_REQMSG)

For more information, refer to the "Peak Current" section of the USB PD Specification.

## PD\_REQMSG

The PD\_REQMSG register is defined as the request message format to initiate negotiation with the PD source. The request message can select the source PDO index and request the desired voltage and current output. If the selected PDO is a Fixed PDO (TYPE=0), setting the VOLTAGE\_SEL has no meaning (except in VOLTAGE\_SEL=FFh).

| PD_REQMSG                                                                                                                                  | Bit   | Attribute | Pwr-on | Description                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PDO_INDEX                                                                                                                                  | 15:12 | WO        | 0h     | Source PDO index select<br>[1] ~ [7]: For SRC_SPR_PDO1 ~ SRC_SPR_PDO7 selection,<br>if its corresponding PDO is detected<br>[8] ~ [13]: For SRC_EPR_PDO8 ~ SRC_EPR_PDO13 selection,<br>if its corresponding PDO is detected<br>Others: Reserved, Shall Not be used                         |

| CURRENT_SEL                                                                                                                                | 8:11  | WO        | 0h     | Operating Current Select<br>0: 1.00A<br>1: 1.25A<br>2: 1.50A<br>3: 1.75A<br>4: 2.00A<br>5: 2.25A<br>6: 2.50A<br>7: 2.75A<br>8: 3.00A<br>9: 3.25A<br>10: 3.50A<br>11: 3.75A<br>12: 4.00A<br>13: 4.25A<br>14: 4.50A<br>15: 5.00A or Maximum Current <sup>(Note1)</sup>                       |

| VOLTAGE_SEL                                                                                                                                | 7:0   | WO        | 0h     | Output Voltage Select<br>If select SRC_SPR_PDO (PDO1 ~ PDO7): <sup>(Note2)</sup><br>Output Voltage in 100mV units for SPR PPS APDO selected<br>If select SRC_EPR_PDO (PDO8 ~ PDO13):<br>Output Voltage in 200mV units for EPR AVS APDO selected<br>FFh: Maximum Voltage <sup>(Note1)</sup> |

| Note1: If set CURRENT_SEL=Fh and VOLTAGE_SEL=FFh, AP33772S will request the Maximum Current and Maximum Voltage of the selected Source PDO |       |           |        |                                                                                                                                                                                                                                                                                            |

| Note2: Setting VOLTAGE_SEL has no meaning when a Fixed PDO is selected                                                                     |       |           |        |                                                                                                                                                                                                                                                                                            |

The AP33772S provides a special request message to request the maximum current and maximum voltage of the selected source PDO by setting only PDO\_INDEX and keeping CURRENT\_SEL = Fh and VOLTAGE\_SEL = FFh.

For example, if source PDO3 is detected, the AP33772S will write PD\_REQMSG=3FFFh to request the maximum current and maximum voltage of source PDO3.

| PD_REQMSG   | Bit   | Attribute | Pwr-on | Value   |

|-------------|-------|-----------|--------|---------|

| PDO_INDEX   | 15:12 | WO        | 0h     | 1 to 13 |

| CURRENT_SEL | 8:11  | WO        | 0h     | Fh      |

| VOLTAGE_SEL | 7:0   | WO        | 0h     | FFh     |

## PD\_CMDSMSG

The PD\_CMDSMSG register is defined as the command message that issues the specific USB PD command.

| AP33772S | AP33772S | AP33772S | AP33772S | AP33772S                    |

|----------|----------|----------|----------|-----------------------------|

| -        | 7:4      | WO       | 0h       | Reserved                    |

| -        | 3        | WO       | 0h       | Reserved                    |

| -        | 2        | WO       | 0h       | Reserved                    |

| -        | 1        | WO       | 0h       | Reserved                    |

| HRST     | 0        | WO       | 0h       | 1: Issue Hard Reset command |

## PD\_MSGRLT

The PD\_MSGRLT register is defined as the message processing results of PD\_REQMSG and PD\_CMDMSG.

The RESPONSE parameter displays the message response made by the AP33772S, based on the interaction result with the PD source. The response values and meanings are as follows:

| PD_MSGRLT | Bit | Attribute | Pwr-on | Description                                                                                                                                                                                                                      |

|-----------|-----|-----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -         | 7:4 | RO        | 0h     | Reserved                                                                                                                                                                                                                         |

| -         | 3   | RO        | 0h     | Reserved                                                                                                                                                                                                                         |

| RESPONSE  | 2:0 | RO        | 0h     | The message response<br>0: System busy or no response<br>1: Success<br>2: Invalid command or argument<br>3: Command not supported or rejected<br>4: Transaction failed. No GoodCRC is received after sending<br>Others: Reserved |

## Chapter 6. Function Description

### 6.1 I2C Request Message

The I2C request message (PD\_REQMSG) can update the PDO index, Operating Current, and Output Voltage settings during runtime.

- PDO\_INDEX assigns the source PDO index.

- CURRENT\_SEL sets the Operating Current value of RDO.

- VOLTAGE\_SEL sets the Output Voltage value of PPS/AVS RDO, but has no effect for selecting Fixed PDO.

The AP33772S starts to negotiate with the PD source after receiving the PD\_REQMSG. When the PD negotiation completes, the AP33772S sets the STATUS.READY bit and updates the negotiation result in the PD\_MSGRLT.RESPONSE.

### 6.2 Support EPR / AVS

After the first negotiation with the PD source, which supports EPR Mode, the AP33772S will try to enter EPR Mode when PDCONFIG.EPR\_MODE is set to 1. If the AP33772S successfully enters EPR Mode, the device stores the EPR Source Capability in the SRC\_EPR\_PDOx registers and enables the EPR request.

### 6.3 VOUT MOS Switch

When the VREQ voltage is more than or equal to the VSELMIN voltage, the AP33772S enables the associated MOS switches and then VBUS is connected to VOUT.

When overvoltage, undervoltage, overcurrent, or overtemperature protection occurs, the associated VOUT MOS switches are turned off to protect the electrical appliances from possible damage. The host MCU will need to load a new PD\_REQMSG to start the PD negotiation process, resuming quick-charging operation.

By default, the VOUT MOS switches are controlled by the AP33772S. Writing the VOUTCTL parameter of the SYSTEM register can force the VOUT MOS switches to turn OFF/ON.

## 6.4 LED Indication

The AP33772S controls LED lighting through the LED pin. The table below summarizes the LED indication and VOUT in each State.

| State           | LED Indication  | VOUT | Comments                                                          |

|-----------------|-----------------|------|-------------------------------------------------------------------|

| <b>INIT</b>     | N/A             | OFF  | VBUS/Rp attached and AP33772S initialization                      |

| <b>CHARGING</b> | 4-sec Breathing | ON   | Successful negotiation or entering of Non-PD Mode; charging start |

| <b>MISMATCH</b> | Full Light      | OFF  | VSELMIN mismatch ( $V_{VREQ} < V_{VSELMIN}$ )                     |

| <b>MOISTURE</b> | 2-sec Flicker   | OFF  | DN abnormal impedance detected                                    |

| <b>FAULT</b>    | 0.6-sec Flicker | OFF  | OVP, OCP, UVP, or OTP occurs                                      |

## 6.5 Interrupt

The AP33772S supports a level-triggered interrupt signal through the INT pin to the host MCU. The MASK register defines the enable and disable options of ON and OFF for each interruptible event.

Interrupt initialization is required before use. When an interruptible event occurs, the AP33772S will set the INT level high (1) if the relevant event of the MASK register is enabled. Then the host MCU should read STATUS to obtain the status of the AP33772S in real time.

For example, if the OVP\_MSK is set to 1 (MASK = 0x13), INT is to be set high when an OVP event occurs.

## 6.6 CC Flip Indication

The AP33772S uses the FLIP Pin for CC Flip Indication. If CC is non-flipped (CC1 attached), the FLIP output is low. If CC is flipped (CC2 attached), the FLIP output is high.

| CC Flip Indication |              |              |

|--------------------|--------------|--------------|

| CC Detection       | CC1 Attached | CC2 Attached |

| FLIP Output        | Low (0)      | High (1)     |

## 6.7 Legacy Type A Charger with Type A-to-C Cable

When the energy source is from a legacy Type A charger, with a Type A-to-C cable connection to the Type-C Connector-equipped devices (TCD), the AP33772S enters Non-PD Mode after PD negotiation fails. When the VREQ voltage is less than the VSELMIN voltage, the associated VOUT MOS switches are turned off. The table below shows the Non-PD Mode state of the AP33772S.

| Non-PD Mode State |                    |            |

|-------------------|--------------------|------------|

| $V_{VREQ}$        | $V_{VSELMIN}$      | $V_{VOUT}$ |

| $V_{VREQ} = 5V$   | $V_{VSELMIN} = 5V$ | ON         |

| $V_{VREQ} = 5V$   | $V_{VSELMIN} > 5V$ | OFF        |

## 6.8 Temperate Estimate

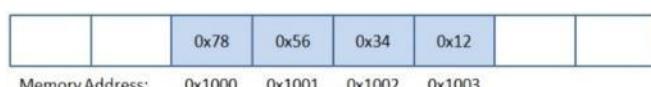

The AP33772S measures and estimates the temperature value based on four User-Entered NTC resistance values vs. temperature (TR25, TR50, TR75, and TR100) in the TCD's practical-usage temperature range.

The AP33772S use Murata NTC NCP03XH103 by default. The table below shows the NTC resistance values vs. temperature.

| Register | Default Value | NTC Resistance (KΩ) | Temperature (°C) |

|----------|---------------|---------------------|------------------|

| TR25     | 2710h         | 10                  | 25               |

| TR50     | 1041h         | 4.161               | 50               |

| TR75     | 0788h         | 1.928               | 75               |

| TR100    | 03CEh         | 0.974               | 100              |

If the calculated NTC resistance value is bounded by TR25 and TR100, the AP33772S uses the "LINEAR INTERPOLATION" of the two bounding TR values to estimate the temperature value, and deposits this estimated temperature value in the I2C register TEMP.

If the calculated NTC resistance value is higher than TR25 value, the AP33772S uses the "LINEAR EXTRAPOLATION" of TR50 and TR25 to estimate the temperature below 25°C. Similarly, if the calculated resistance value is lower than TR100 value, the AP33772S uses the "LINEAR EXTRAPOLATION" of TR75 and TR100 to estimate the temperature above 100°C.

**Calculated Resistance vs. Estimated Temperature**

Ex. The AP33772S calculates that the resistance value of NTC is 2.250kΩ. The near-boundary 50°C is 4.161kΩ; 75°C is 1.925kΩ. Therefore, 2.250kΩ corresponds to:

$$\text{SLOPE} = (1.925\text{k}\Omega - 4.161\text{k}\Omega) / (75^\circ\text{C} - 50^\circ\text{C}) = -0.08944 \text{ k}\Omega/\text{C}$$

$$\text{Temperature} = 50^\circ\text{C} + (2.250\text{k}\Omega - 4.161\text{k}\Omega) / (-0.08944 \text{ k}\Omega/\text{C}) = 71.4^\circ\text{C}$$

So, the TEMP register value is to be set at 47h (71°C).

## Chapter 7. Protection

### 7.1 Overvoltage Protection (OVP)

The AP33772S triggers OVP protection when the VBUS voltage is higher than the OVP Threshold Voltage. The table below summarizes the correspondence between VREQ, OVPTHR, and OVP Threshold Voltage.

| Mode     | Criteria                           | OVP Threshold Voltage   |

|----------|------------------------------------|-------------------------|

| SPR Mode | $(V_{VREQ} + V_{OVPTHR}) \leq 20V$ | $V_{VREQ} + V_{OVPTHR}$ |

|          | $(V_{VREQ} + V_{OVPTHR}) > 20V$    | $V_{VREQ} * 110\%$      |

| EPR Mode | $(V_{VREQ} + V_{OVPTHR}) \leq 40V$ | $V_{VREQ} + V_{OVPTHR}$ |

|          | $(V_{VREQ} + V_{OVPTHR}) > 40V$    | $V_{VREQ} * 110\%$      |

The OVP debounce time mechanism is to prevent false triggering caused by various spurious noises. The OVP debounce time is preset to 30ms. If the VBUS voltage is greater than the OVP threshold voltage after the debounce time (30ms), the STATUS.OVP will be set to 1 and the associated VOUT MOS switches are turned off. The host MCU will need to load a new PD\_CMDMSG to start the PD negotiation process, resuming quick-charging operation.

### 7.2 Overcurrent Protection (OCP)

The AP33772S triggers OCP protection when the charging current is larger than OCP Threshold Current. The table below shows the correspondence between OCPTHR and OCP Threshold Current. The default value of the OCPTHR register is 00h.

If the OCPTHR value is still 00h after successful negotiation with the PD source, the OCP Threshold Current should be updated to 110% of the maximum current ( $I_{MAX}$ ) of the selected PDO/APDO.

If the OCPTHR value has been updated through I2C interface, the OCP Threshold Current should be updated to 110% of the OCPTHR value.

| OCPTHR      | OCP Threshold Current    |

|-------------|--------------------------|

| OCPTHR = 0  | $I_{MAX} * 110\%$ (Note) |

| OCPTHR != 0 | $I_{OCPTHR} * 110\%$     |

Note:  $I_{MAX}$ : The Maximum Current of PDO/APDO

The default OCP debounce time is 30ms. If the charging current is larger than OCP Threshold Current after debounce time (30ms), the STATUS.OCP will be set to 1 and the associated VOUT MOS switches are turned off. The host MCU will need to load a new PD\_CMDMSG to start the PD negotiation process, resuming quick-charging operation.

### 7.3 Undervoltage Protection (UVP)

The AP33772S triggers UVP protection when VBUS voltage is lower than UVP Threshold Voltage. The table below shows the correspondence between UVPTHR and UVP Threshold Voltage.

The default value of the Undervoltage Protection Threshold (UVPTHR) is 80%, which can be modified by writing the UVPTHR command.

| UVPTHR | UVP Threshold Voltage |

|--------|-----------------------|

| 1      | $V_{VREQ} * 80\%$     |

| 2      | $V_{VREQ} * 75\%$     |

| 3      | $V_{VREQ} * 70\%$     |

The default UVP debounce time is 30ms. If VBUS voltage is lower than UVP Threshold Voltage after debounce time (30ms), the STATUS.UVP will be set to 1 and the associated VOUT MOS switches are turned off. The host MCU will need to load a new PD\_CMDMSG to start the PD negotiation process, resuming quick-charging operation.

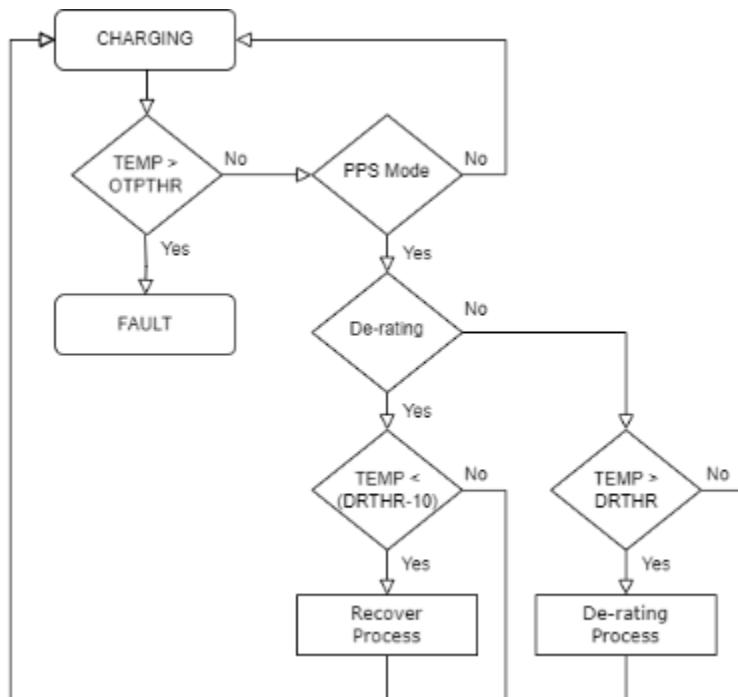

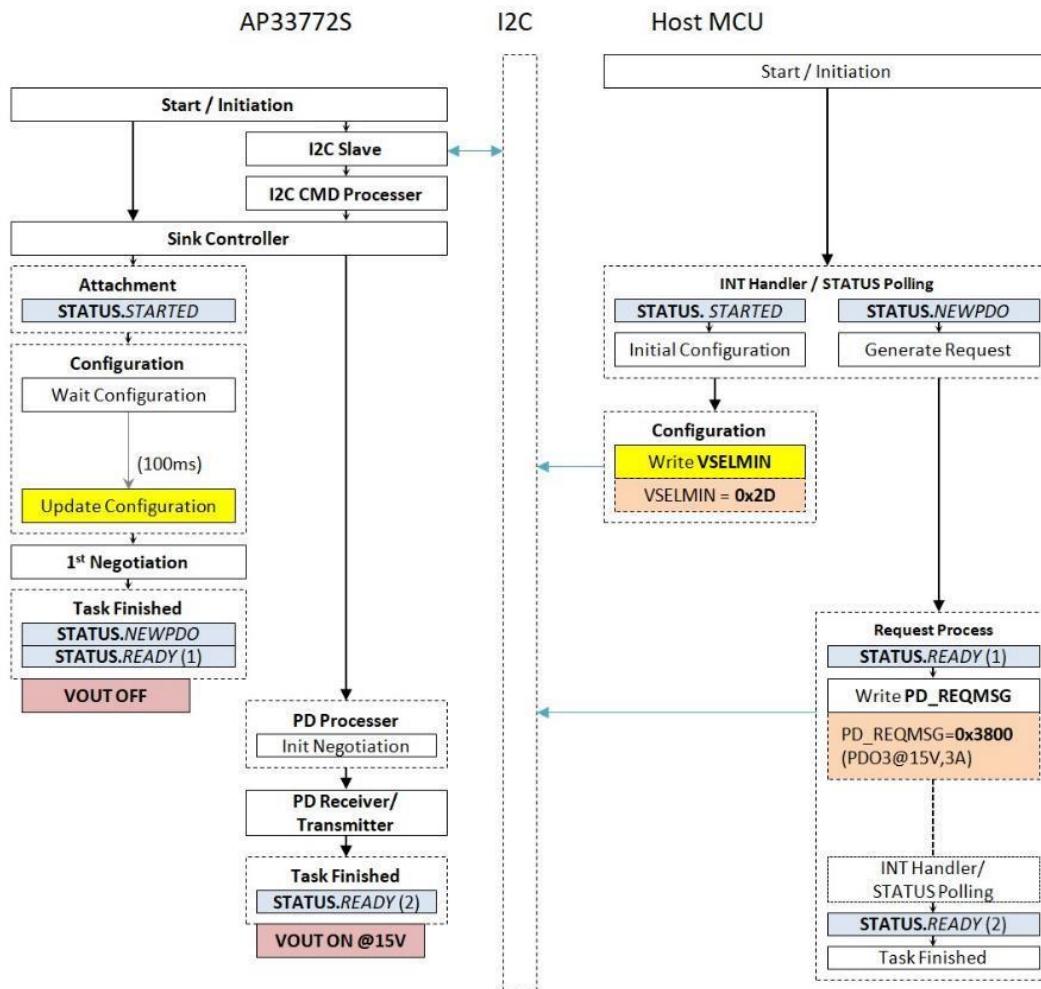

## 7.4 Overtemperature Protection (OTP) and De-Rating