## Description

The AL3565 is a Power Management Integrated Chip (PMIC) with three programmable DC-DC converters via a simple one-wire digital control to the power-supply bias 500mA AMOLED (Active Matrix Organic Light Emitting Diode) panel, requiring three supply rails: V<sub>POS</sub>, V<sub>NEG</sub>, and A<sub>VDD</sub>.

The device integrates a buck-boost converter for V<sub>POS</sub>, an inverting buck-boost converter for V<sub>NEG</sub>, and a boost converter for A<sub>VDD</sub>, which are suitable for power management of portable products operated under lithium-ion battery power.

The PRG (Programming Digital Control) pin allows programming of the V<sub>POS</sub> and V<sub>NEG</sub> output voltage in steps of 100mV, and A<sub>VDD</sub> in steps of 300mV. The AL3565 offers an excellent line and load regulation.

The AL3565 is available in the U-QFN3030-16 (Type B) (3.0mm x 3.0mm) 16-pin package with exposed pad. Please contact us for WL-CSP and other package options.

## Features

- Wide Input Voltage Range: 2.9V to 4.8V

- 40°C to + 85°C Operating Ambient Temperature

- V<sub>POS</sub> – Buck-Boost Converter (Default 4.6V)

- 4.6V to 5.4V, Programmable Output Voltage

- 100mV Step Size

- Up to 500mA Output Current

- 0.5% Accuracy

- A<sub>VDD</sub> – Boost Converter (Default 6.1V)

- 5.8V to 7.9V, Programmable Output Voltage

- 300mV Step Size

- 100mA Output Current

- 0.5% Accuracy

- V<sub>NEG</sub> – Inverting Buck-Boost Converter (Default -2.5V)

- 1.4V to -5.4V, Programmable Negative Voltage

- 100mV Step Size

- Up to 500mA Output Current

- 0.5% Accuracy

- Excellent Line and Transient Regulations

- Short-Circuit Protection (SCP)

- Thermal Shutdown Protection

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)**

- Halogen and Antimony Free. "Green" Device (Note 3)**

- For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/104/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please [contact us](#) or your local Diodes representative.**

<https://www.diodes.com/quality/product-definitions/>

Notes:

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

2. See <https://www.diodes.com/quality/lead-free/> for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

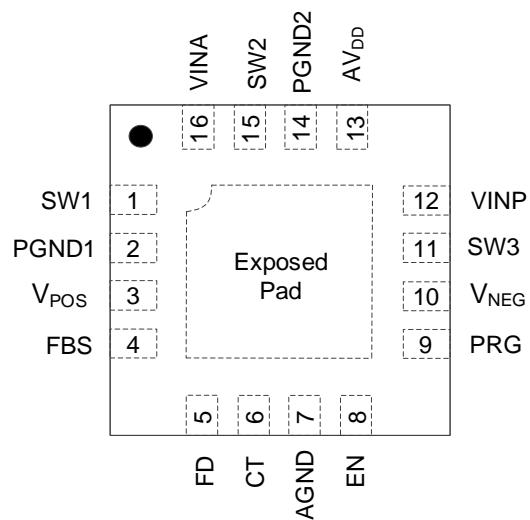

## Pin Assignments

Top View

U-QFN3030-16 (Type B)

## Applications

- AMOLED display-panel power-supply bias

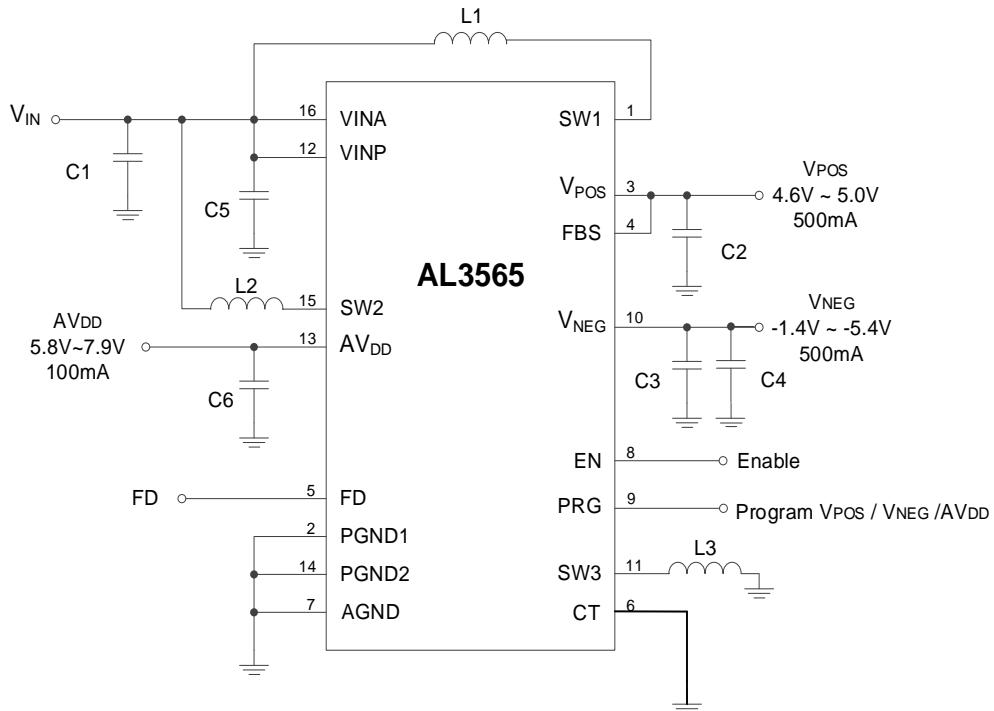

## Typical Applications Circuits

## Pin Descriptions

| Pin Number | Pin Name    | Description                                                                                                                                                  |

|------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | SW1         | Boost converter switch pin                                                                                                                                   |

| 2          | PGND1       | Boost converter power ground                                                                                                                                 |

| 3          | VPOS        | Boost converter output (VPOS)                                                                                                                                |

| 4          | FBS         | Boost converter sense pin                                                                                                                                    |

| 5          | FD          | Fast Discharge circuit function selection. High level enables the fast discharge function; low level sets VPOS, VNEG and AVDD high impedance without output. |

| 6          | CT          | Must tie to ground                                                                                                                                           |

| 7          | AGND        | Analog ground                                                                                                                                                |

| 8          | EN          | Enable boost converter (AVDD)                                                                                                                                |

| 9          | PRG         | Programming control pin, digital control VPOS, VNEG and AVDD output voltage                                                                                  |

| 10         | VNEG        | Inverting buck-boost output (VNEG)                                                                                                                           |

| 11         | SW3         | Inverting buck-boost switching pin                                                                                                                           |

| 12         | VINP        | Inverting buck-boost converter power stage supply voltage                                                                                                    |

| 13         | AVDD        | Boost converter output voltage pin (AVDD)                                                                                                                    |

| 14         | PGND2       | Boost converter power ground                                                                                                                                 |

| 15         | SW2         | Boost converter switching pin                                                                                                                                |

| 16         | VINA        | Supply voltage for the device                                                                                                                                |

| —          | Exposed Pad | Connect to the Ground layers on the PCB                                                                                                                      |

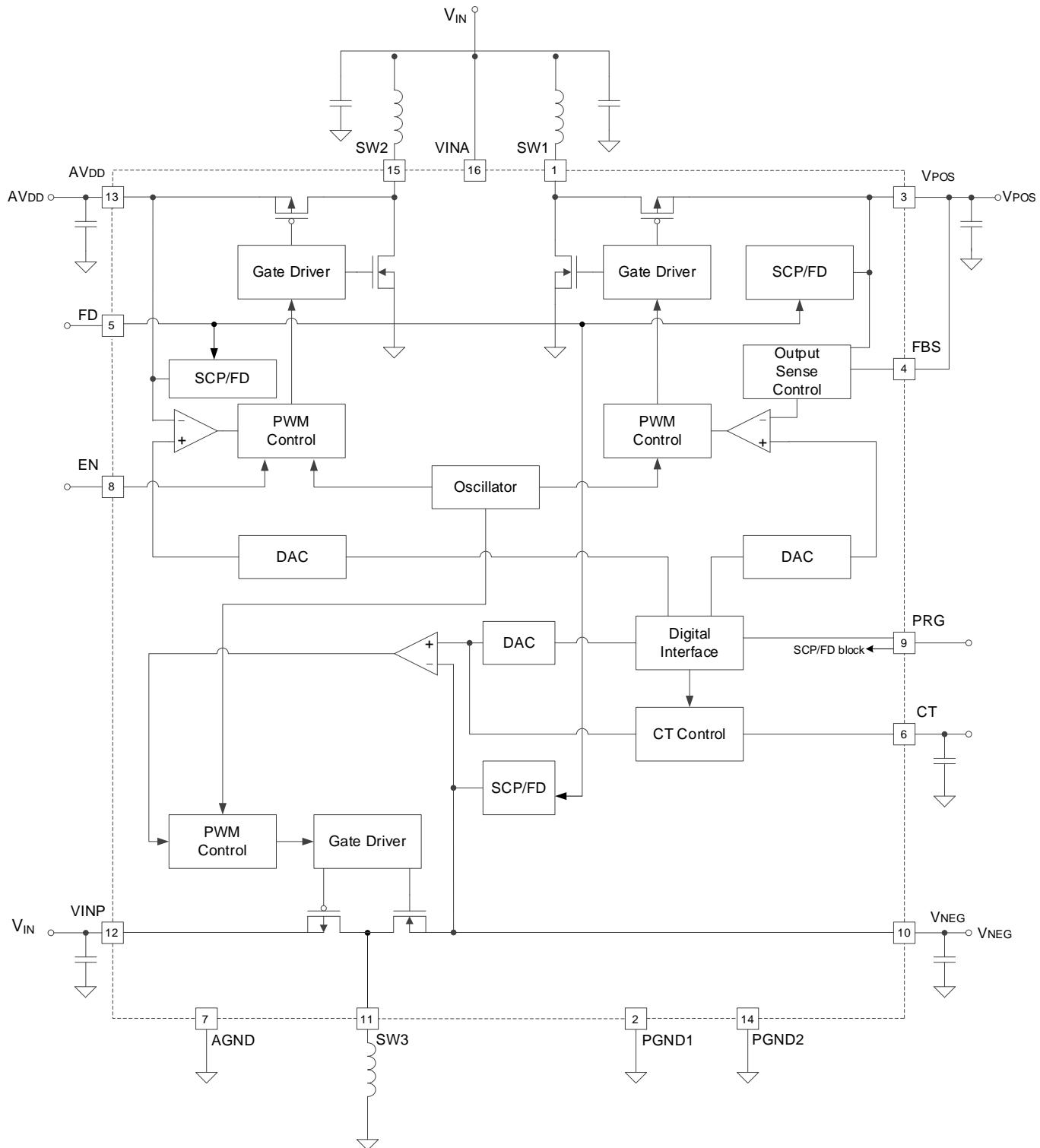

## Functional Block Diagram

## Absolute Maximum Ratings

| Symbol                              | Parameter                               | Ratings      | Unit |

|-------------------------------------|-----------------------------------------|--------------|------|

| V <sub>INP</sub> , V <sub>INA</sub> | Supply pin voltage                      | -0.3 to 6.5  | V    |

| S <sub>W1</sub>                     | Switch pin voltage                      | -0.3 to 6.5  |      |

| F <sub>BS</sub>                     | Feedback sense pin voltage              | -0.3 to 6.5  |      |

| S <sub>W2</sub>                     | Switch pin voltage                      | -0.3 to 12.0 |      |

| V <sub>POS</sub>                    | V <sub>POS</sub> pin voltage            | -0.3 to 6.5  |      |

| A <sub>V<sub>DD</sub></sub>         | A <sub>V<sub>DD</sub></sub> pin voltage | -0.3 to 12.0 |      |

| V <sub>NEG</sub>                    | V <sub>NEG</sub> pin voltage            | -6.5 to 0.3  |      |

| S <sub>W3</sub>                     | Switch pin voltage                      | -6.5 to 6.5  |      |

| PRG, EN, FD                         | PRG, EN, FD pin voltage                 | -0.3 to 6.5  |      |

| C <sub>T</sub>                      | C <sub>T</sub> pin voltage              | -0.3 to 6.5  |      |

| T <sub>J</sub>                      | Operating junction temperature          | -40 to +150  | °C   |

| T <sub>ST</sub>                     | Storage temperature                     | -65 to +150  |      |

Caution: Stresses greater than those listed under *Absolute Maximum Ratings* can cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to *Absolute Maximum Ratings* for extended periods can affect device reliability. Semiconductor devices are ESD sensitive and may be damaged by exposure to ESD events. Suitable ESD precautions should be taken when handling and transporting these devices.

## ESD Ratings

| Symbol           | Parameter               |                                   | Value | Unit |

|------------------|-------------------------|-----------------------------------|-------|------|

| V <sub>ESD</sub> | Electrostatic discharge | Human body model ESD protection   | ±2000 | V    |

|                  |                         | Charge device mode ESD protection | 1000  | V    |

## Package Thermal Data

| Package               | θ <sub>JC</sub><br>Thermal Resistance<br>Junction-to-Case | θ <sub>JA</sub><br>Thermal Resistance<br>Junction-to-Ambient | P <sub>DIS</sub><br>T <sub>A</sub> = +25°C, T <sub>J</sub> = +125°C |

|-----------------------|-----------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------|

| U-QFN3030-16 (Type B) | 3.3°C/W                                                   | 42.9°C/W (Note 4)                                            | 1.5W                                                                |

## Recommended Operating Conditions

| Symbol          | Parameter                           | Min | Max | Unit |

|-----------------|-------------------------------------|-----|-----|------|

| V <sub>IN</sub> | Input supply voltage range          | 2.9 | 4.8 | V    |

| T <sub>A</sub>  | Operating ambient temperature range | -40 | +85 | °C   |

Note: 4. Test condition for U-QFN3030-16 (Type B): device mounted on 25.4mm x 25.4mm FR-4 PCB (10mm x 10mm 1oz copper, minimum recommended pad layout on top layer and thermal vias to bottom layer ground plane). For better thermal performance, larger copper pad for heatsink is needed.

## Electrical Characteristics

( $V_{IN} = 3.7V$ ,  $PRG = 3.7V$ ,  $EN = 3.7V$ ,  $V_{POS} = 4.6V$ ,  $V_{NEG} = -2.5V$ ,  $AV_{DD} = 6.1V$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ , typical values are at  $T_A = +25^\circ C$ , unless otherwise specified.)

| Symbol                                              | Parameter                                      | Conditions                                                                             |                                                | Min  | Typ  | Max  | Unit |

|-----------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------|------|------|------|------|

| <b>Input Supply Section</b>                         |                                                |                                                                                        |                                                |      |      |      |      |

| $V_{IN}$                                            | Input voltage                                  | —                                                                                      | $T_A = -40^\circ C$ to $+85^\circ C$           | 2.9  | 3.7  | 4.8  | V    |

| V <sub>UVLO</sub>                                   | Undervoltage lockout threshold                 | V <sub>IN</sub> falling                                                                | —                                              | 2.7  | —    | 2.8  | V    |

|                                                     |                                                | V <sub>IN</sub> rising                                                                 | —                                              | 2.75 | —    | 2.86 | V    |

| I <sub>SD</sub>                                     | Shutdown current                               | PRG = GND, EN = GND, sum of current flowing into V <sub>INA</sub> and V <sub>INP</sub> |                                                | —    | 0.3  | 1    | µA   |

| <b>V<sub>POS</sub> – Boost/Buck-Boost Converter</b> |                                                |                                                                                        |                                                |      |      |      |      |

| V <sub>VPOS</sub>                                   | V <sub>POS</sub> voltage                       | Default voltage                                                                        | —                                              | —    | 4.6  | —    | V    |

|                                                     |                                                | Output accuracy                                                                        | $T_A = +25^\circ C$ , No load                  | -0.5 | —    | 0.5  | %    |

|                                                     |                                                |                                                                                        | $T_A = -40^\circ C$ to $+85^\circ C$ , No load | -0.8 | —    | 0.8  | %    |

| Output range (100mV/step)                           |                                                | —                                                                                      | 4.6                                            | —    | 5.0  | —    | V    |

| R <sub>DS(on)1N</sub>                               | Switch on-resistance (nMOS)                    | I <sub>(SW1)</sub> = 200mA                                                             | —                                              | —    | 250  | —    | mΩ   |

| R <sub>DS(on)1P</sub>                               | Rectifier on-resistance (pMOS)                 |                                                                                        | —                                              | —    | 350  | —    | mΩ   |

| f <sub>SW1</sub>                                    | Switching frequency                            | I <sub>VPOS</sub> = 500mA                                                              | —                                              | —    | 1.5  | —    | MHz  |

| I <sub>SW1</sub>                                    | Switch current limit                           | Inductor peak current                                                                  | —                                              | 1.1  | 1.4  | 1.8  | A    |

| V <sub>VSCP_VPOS</sub>                              | Short-circuit threshold in operation           | Percentage of V <sub>POS</sub>                                                         | —                                              | —    | 90   | —    | %    |

| t <sub>VSCP_VPOS</sub>                              | Short-circuit detection time in operation      | —                                                                                      | —                                              | —    | 1    | —    | ms   |

| V <sub>T</sub>                                      | FBS sense threshold                            | FBS increasing                                                                         | —                                              | 200  | 300  | 400  | mV   |

|                                                     |                                                | FBS decreasing                                                                         | —                                              | 100  | 200  | 300  | mV   |

| R <sub>DCHG1</sub>                                  | Discharge resistance                           | PRG = GND, FD = V <sub>IN</sub><br>I <sub>VPOS</sub> = 1mA                             | —                                              | —    | 70   | —    | Ω    |

| V <sub>V RIPPLE_VPOS</sub>                          | V <sub>POS</sub> output voltage ripple         | V <sub>IN</sub> = 3.7V, V <sub>POS</sub> = 4.6V<br>I <sub>POS</sub> = 500mA            | —                                              | —    | 20   | —    | mV   |

| I <sub>LEAK_VPOS</sub>                              | V <sub>POS</sub> and FBS leakage, no discharge | FD = GND, PRG = GND                                                                    | V <sub>POS</sub> ≤ V <sub>IN</sub>             | —    | 0.1  | —    | µA   |

| —                                                   | Line regulation                                | I <sub>POS</sub> = 500mA                                                               | —                                              | —    | 0.03 | —    | %/V  |

| —                                                   | Load regulation                                | V <sub>IN</sub> = 3.7V<br>0mA ≤ I <sub>POS</sub> ≤ 500mA                               | 100mA ≤ I <sub>POS</sub> ≤ 500mA               | —    | 0.08 | —    | %/A  |

| —                                                   |                                                |                                                                                        | 0mA ≤ I <sub>POS</sub> ≤ 500mA                 | —    | 0.1  | —    |      |

| <b>AV<sub>DD</sub> – Boost Converter</b>            |                                                |                                                                                        |                                                |      |      |      |      |

| V <sub>AVDD</sub>                                   | V <sub>AVDD</sub> voltage                      | Default voltage                                                                        | —                                              | —    | 7.6  | —    | V    |

|                                                     |                                                | Output accuracy                                                                        | $T_A = +25^\circ C$ , No load                  | -0.5 | —    | 0.5  | %    |

|                                                     |                                                |                                                                                        | $T_A = -40^\circ C$ to $+85^\circ C$ , No load | -1.0 | —    | 1.0  | %    |

| Output range (300mV/step)                           |                                                | —                                                                                      | 5.8                                            | —    | 7.9  | —    | V    |

| R <sub>DS(on)2N</sub>                               | Switch on-resistance (nMOS)                    | I <sub>(SW2)</sub> = 100mA                                                             | —                                              | —    | 300  | —    | mΩ   |

| R <sub>DS(on)2P</sub>                               | Rectifier on-resistance (pMOS)                 |                                                                                        | —                                              | —    | 450  | —    | mΩ   |

| f <sub>SW2</sub>                                    | Switching frequency                            | I <sub>AVDD</sub> = 100mA                                                              | —                                              | —    | 1.5  | —    | MHz  |

| V <sub>VSCP_AVDD</sub>                              | Short-circuit threshold in operation           | Percentage of nominal AV <sub>DD</sub>                                                 | —                                              | —    | 90   | —    | %    |

| t <sub>VSCP_AVDD</sub>                              | Short-circuit detection time in operation      | —                                                                                      | —                                              | —    | 1    | —    | ms   |

| I <sub>SW2</sub>                                    | Switch current limit                           | Inductor peak current                                                                  | —                                              | 0.45 | 0.65 | 0.85 | A    |

| V <sub>V RIPPLE_AVDD</sub>                          | AV <sub>DD</sub> output voltage ripple         | V <sub>IN</sub> = 3.7V, AV <sub>DD</sub> = 7.6V<br>I <sub>AVDD</sub> = 100mA           | —                                              | —    | 20   | —    | mV   |

| I <sub>LEAK_AVDD</sub>                              | AV <sub>DD</sub> leakage, no discharge         | FD = GND, EN = GND                                                                     | AV <sub>DD</sub> ≤ V <sub>IN</sub>             | —    | 0.3  | —    | µA   |

| R <sub>DCHG2</sub>                                  | Discharge resistance                           | EN = GND, FD = V <sub>IN</sub><br>I <sub>AVDD</sub> = 1mA                              | —                                              | —    | 70   | —    | Ω    |

| —                                                   | Line regulation                                | I <sub>AVDD</sub> = 30mA                                                               | —                                              | —    | 0.05 | —    | %/V  |

| —                                                   | Load regulation                                | 0mA ≤ I <sub>AVDD</sub> ≤ 100mA                                                        | 50mA ≤ I <sub>AVDD</sub> ≤ 100mA               | —    | 0.5  | —    | %/A  |

| —                                                   |                                                |                                                                                        | 0mA ≤ I <sub>AVDD</sub> ≤ 100mA                | —    | 0.5  | —    |      |

**Electrical Characteristics** ( $V_{IN} = 3.7V$ ,  $PRG = 3.7V$ ,  $EN = 3.7V$ ,  $V_{POS} = 4.6V$ ,  $V_{NEG} = -2.5V$ ,  $AV_{DD} = 6.1V$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ , typical values are at  $T_A = +25^\circ C$ , unless otherwise specified.) (continued)

| Symbol                                                       | Parameter                                 | Conditions                                                |                                      | Min  | Typ  | Max  | Unit       |

|--------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------|--------------------------------------|------|------|------|------------|

| <b><math>V_{NEG}</math> – Inverting Buck-Boost Converter</b> |                                           |                                                           |                                      |      |      |      |            |

| $V_{VNEG}$                                                   | $V_{VNEG}$ voltage                        | Default voltage                                           | —                                    | —    | -4.0 | —    | V          |

|                                                              |                                           | Output accuracy                                           | $T_A = +25^\circ C$                  | -0.5 | —    | 0.5  | %          |

|                                                              |                                           |                                                           | $T_A = -40^\circ C$ to $+85^\circ C$ | -0.8 | —    | 0.8  | %          |

|                                                              |                                           | Output range (100mV/step)                                 | —                                    | -1.4 | —    | -5.4 | V          |

| $R_{DS(on)3P}$                                               | Switch on-resistance (pMOS)               | $I_{(SW3)} = 200mA$                                       | —                                    | —    | 200  | —    | $m\Omega$  |

| $R_{DS(on)3N}$                                               | Rectifier on-resistance (nMOS)            |                                                           | —                                    | —    | 300  | —    | $m\Omega$  |

| $f_{SW3}$                                                    | Switching frequency                       | $I_{NEG} = 500mA$                                         | —                                    | —    | 1.5  | —    | MHz        |

| $I_{SW3}$                                                    | Switch current limit                      | Inductor peak current                                     | —                                    | 1.5  | 2.0  | 2.75 | A          |

| $V_{SCP\_VNEG}$                                              | Short-circuit threshold in operation      | Voltage increase from nominal $V_{NEG}$                   | —                                    | —    | 530  | —    | mV         |

|                                                              | Short-circuit threshold in startup        | —                                                         | —                                    | —    | 250  | —    | mV         |

| $t_{SCP\_VNEG}$                                              | Short-circuit detection time in operation | —                                                         | —                                    | —    | 1    | —    | ms         |

|                                                              | Short-circuit detection time in startup   | —                                                         | —                                    | —    | 10   | —    | ms         |

| $I_{LEAK\_VNEG}$                                             | $V_{NEG}$ leakage, no discharge           | $FD = GND$ , $EN = GND$                                   | $V_{NEG} = 0V$                       | —    | 0.1  | —    | $\mu A$    |

| $V_{RIPPLE\_VNEG}$                                           | $V_{NEG}$ output voltage ripple           | $V_{IN} = 3.7V$ , $V_{NEG} = -4.0V$<br>$I_{AVDD} = 500mA$ | —                                    | —    | 20   | —    | mV         |

| $R_{DCHG3}$                                                  | Discharge resistance                      | $PRG = GND$ , $FD = V_{IN}$<br>$I_{VNEG} = 1mA$           | —                                    | —    | 70   | —    | $\Omega$   |

| —                                                            | Line regulation                           | $I_{NEG} = 500mA$                                         | —                                    | —    | 0.03 | —    | %/V        |

| —                                                            | Load regulation                           | $V_{NEG} = -5V$<br>$1mA \leq I_{NEG} \leq 500mA$          | $100mA \leq I_{NEG} \leq 500mA$      | —    | 0.16 | —    | %/A        |

| —                                                            |                                           |                                                           | $1mA \leq I_{NEG} \leq 500mA$        | —    | 0.20 | —    |            |

| <b>Logic Interface (PRG, EN, FD)</b>                         |                                           |                                                           |                                      |      |      |      |            |

| $V_{IH}$                                                     | Logic input high level voltage            | —                                                         | —                                    | —    | 1.2  | —    | V          |

| $V_{IL}$                                                     | Logic input low level voltage             | —                                                         | —                                    | —    | —    | 0.4  | V          |

| R                                                            | Pulldown resistance                       | —                                                         | —                                    | 250  | 500  | 900  | $k\Omega$  |

| <b>Other</b>                                                 |                                           |                                                           |                                      |      |      |      |            |

| $T_{SHDN}$                                                   | Thermal shutdown                          | Junction temperature                                      | —                                    | —    | +150 | —    | $^\circ C$ |

| $T_{HYS}$                                                    | Thermal shutdown hysteresis               | —                                                         | —                                    | —    | +10  | —    | $^\circ C$ |

| <b>PRG Timing Interface Section (PRG, EN, FD)</b>            |                                           |                                                           |                                      |      |      |      |            |

| $t_{INIT}$                                                   | Initialization time                       |                                                           |                                      | —    | 300  | —    | $\mu s$    |

| $t_{STORE}$                                                  | Data storage time                         |                                                           |                                      | 30   | —    | 80   | $\mu s$    |

| $t_{LOW}$                                                    | Low-level pulse duration                  |                                                           |                                      | 2    | 10   | 25   | $\mu s$    |

| $t_{HIGH}$                                                   | High-level pulse duration                 |                                                           |                                      | 2    | 10   | 25   | $\mu s$    |

| $t_{OFF}$                                                    | Shutdown time                             |                                                           |                                      | 30   | —    | 80   | $\mu s$    |

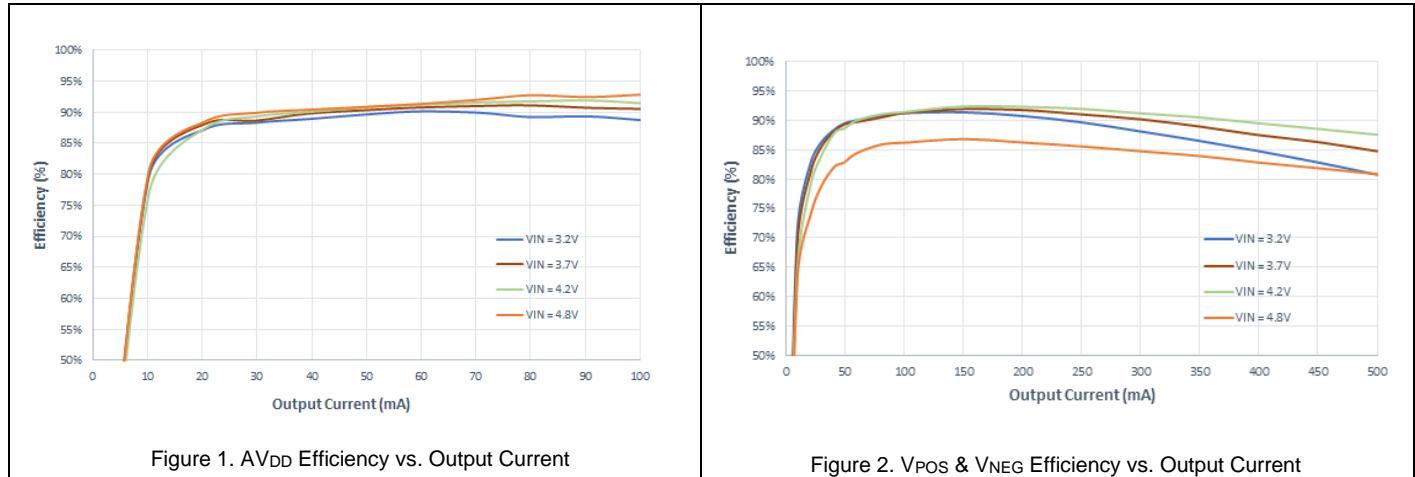

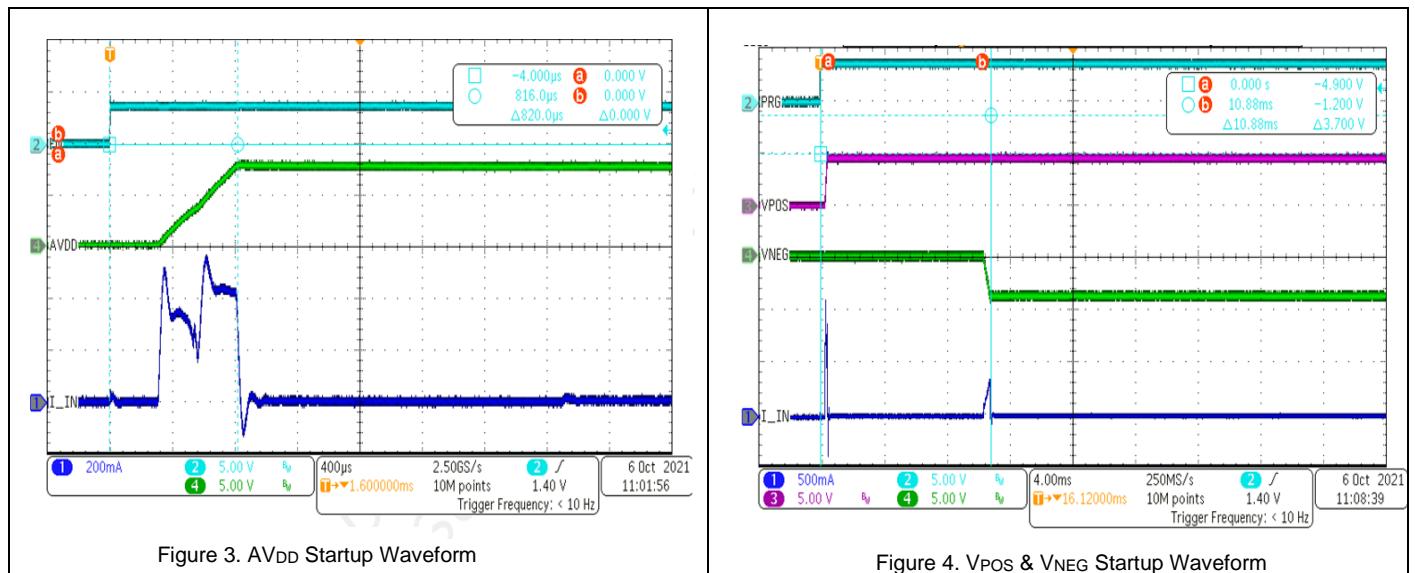

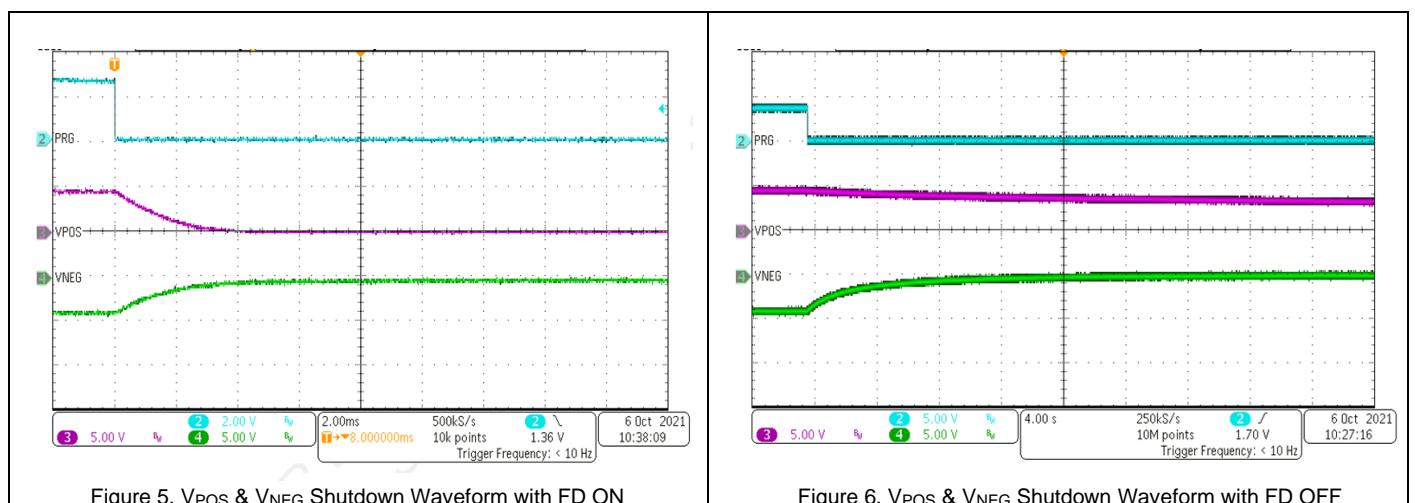

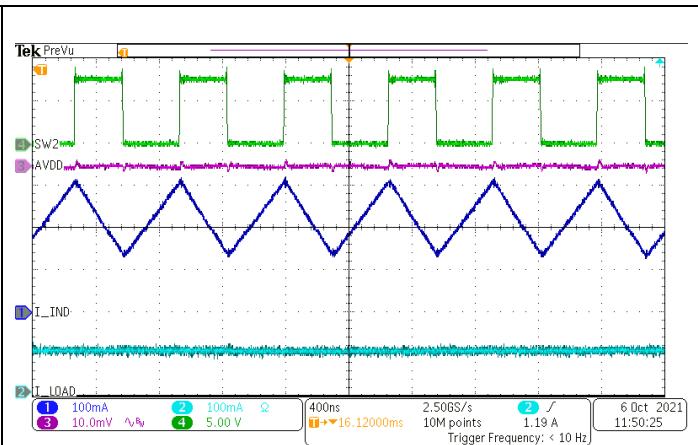

**Performance Characteristics** ( $V_{IN} = 3.7V$ ,  $T_A = +25^\circ C$  with components as Figure 20, unless otherwise specified.)

Test conditions:  $AVDD = 7.6V$ ,  $EN = HIGH$ ,  $PRG = LOW$

$V_{POS} = 4.6V$ ,  $V_{NEG} = -4V$ ,  $EN = LOW$ ,  $PRG = HIGH$

Test conditions:  $V_{IN} = 3.7V$ , No Load,  $PRG = HIGH$ ,  $EN = LOW$

$V_{IN} = 3.7V$ , No Load,  $PRG = LOW$ ,  $EN = HIGH$

Test conditions:  $V_{POS}$   $V_{NEG}$  with Fast Discharge (FD) = OFF

$V_{POS}$   $V_{NEG}$  with Fast Discharge (FD) = ON

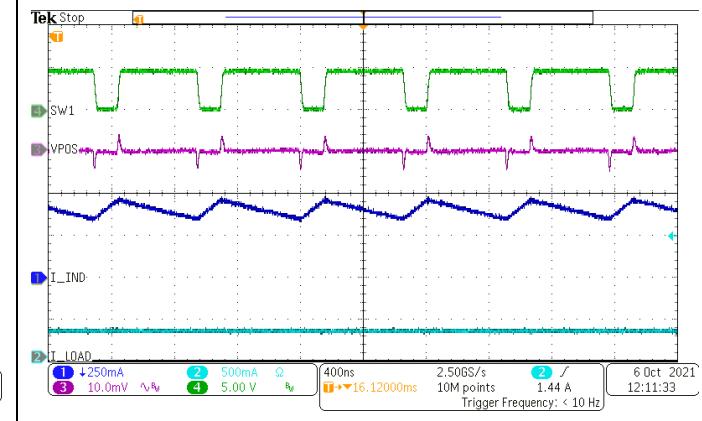

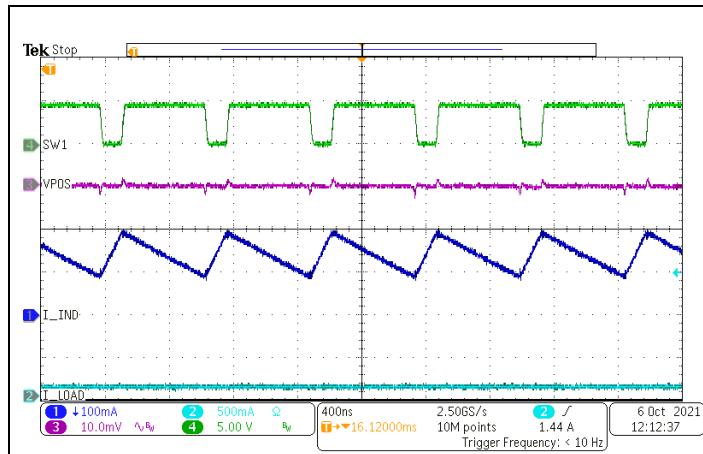

**Performance Characteristics** ( $V_{IN} = 3.7V$ ,  $T_A = +25^\circ C$  with components as Figure 20, unless otherwise specified.) (continued)

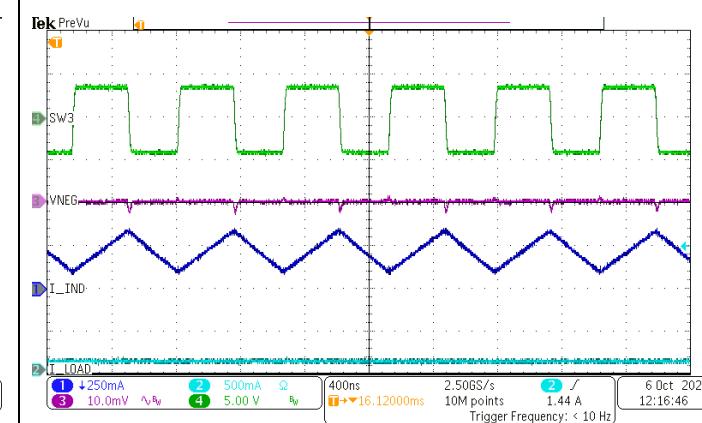

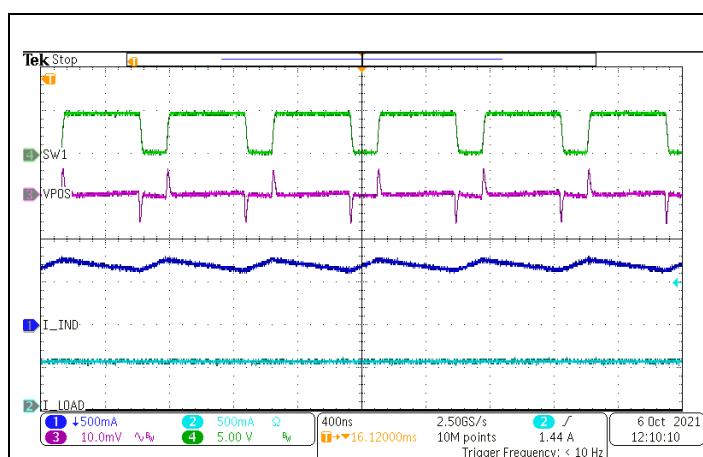

Test conditions:  $V_{POS}$  Boost,  $V_{POS} = 4.6V$  / 100mA load

$V_{POS}$  Boost,  $V_{POS} = 4.6V$  / 300mA load

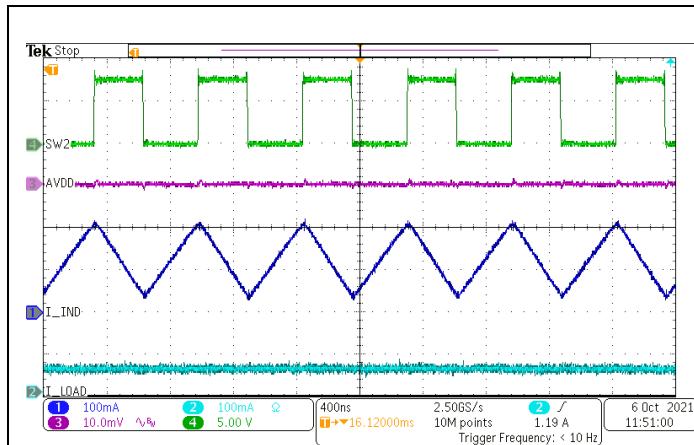

Test conditions:  $V_{POS}$  Boost,  $V_{POS} = 4.6V$  / 500mA load

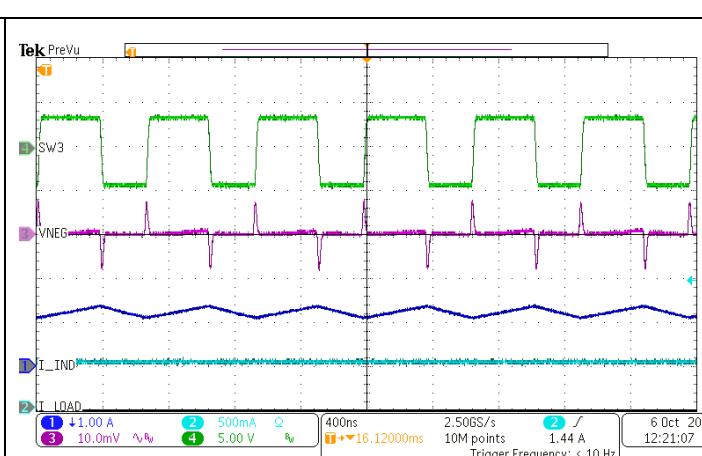

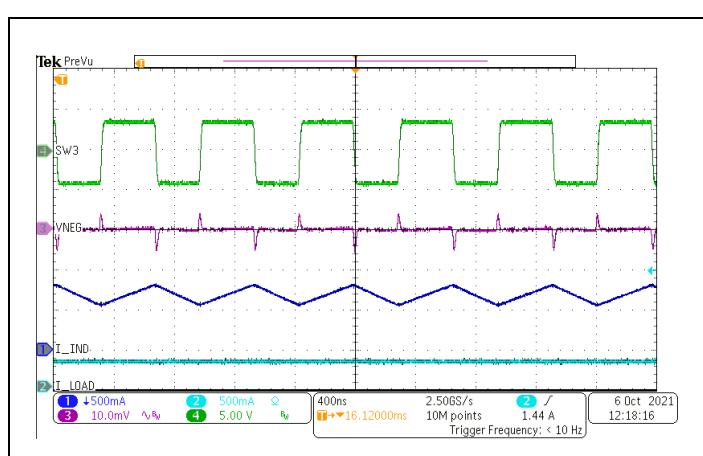

$V_{NEG} = -4.0V$  / 100mA load

Test conditions:  $V_{NEG} = -4.0V$  / 300mA load

$V_{NEG} = -4.0V$  / 500mA load

**Performance Characteristics** ( $V_{IN} = 3.7V$ ,  $T_A = +25^\circ C$  with components as Figure 20, unless otherwise specified.) (continued)

Test conditions:  $AV_{DD} = 7.6V$  / 50mA load

$AV_{DD} = 7.6V$  / 100mA load

## Function Description

The AL3565 consists of two boost converters and an inverting buck-boost converter. The VPOS, VNEG and AVDD outputs are all programmable through the PRG digital pin. The VPOS output range is from 4.6V to 5.0V, default 4.6V. The VNEG output range is from -5.4V to -1.4V, default -2.5V. The AVDD output range is from 5.8V to 7.9V, default 6.1V. Fast discharge function is on/off controlled by FD pin

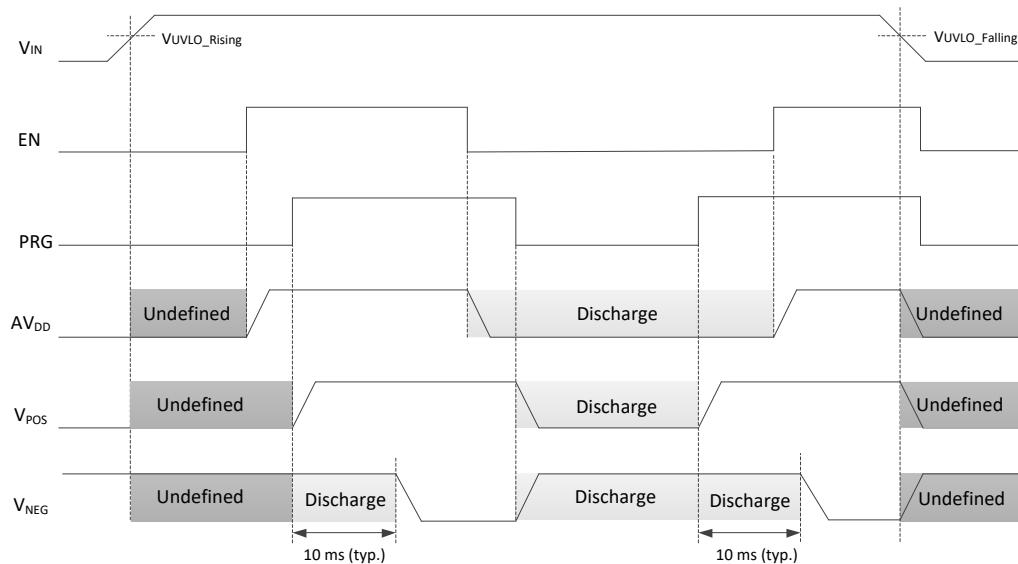

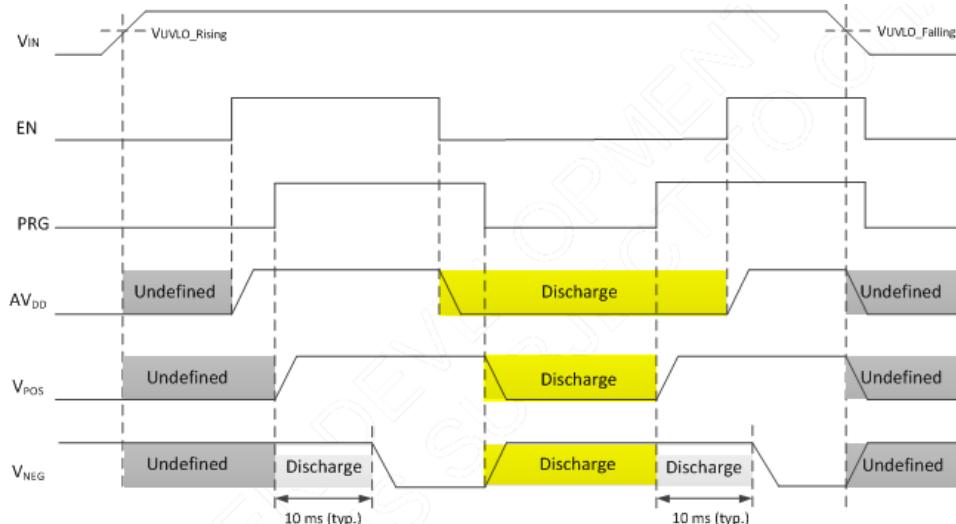

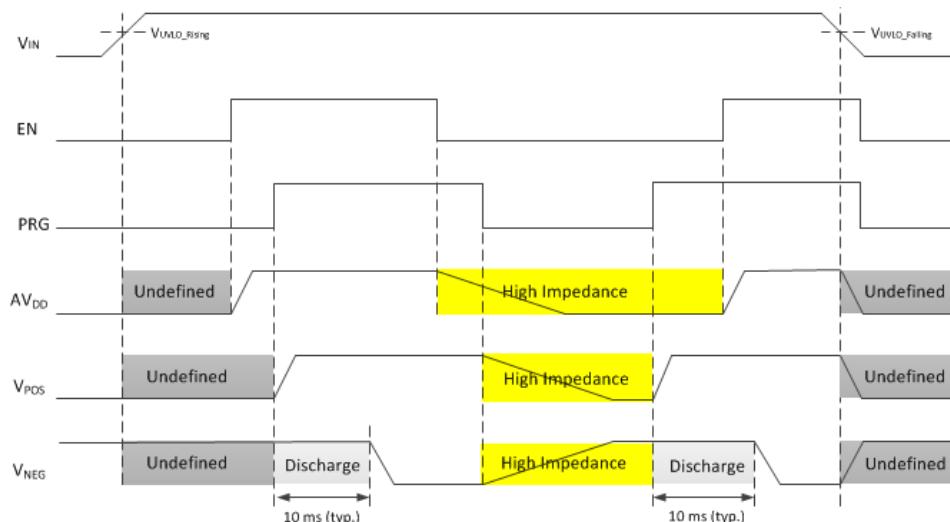

### 1.0 Startup Sequence, Soft-Start and Shutdown

The device features a soft-start function to limit the inrush current. The AVDD boost converter is enabled when EN goes high. When PRG goes high, the VPOS boost/buck-boost converter starts and 10ms later the inverting buck-boost converter (VNEG) starts with its default value. The typical startup sequence with fast discharge is shown in Figure 15. The AVDD boost converter, and the VPOS boost converter operate independently. The AVDD boost converter does not require the VPOS boost converter to be in regulation in order for it to start.

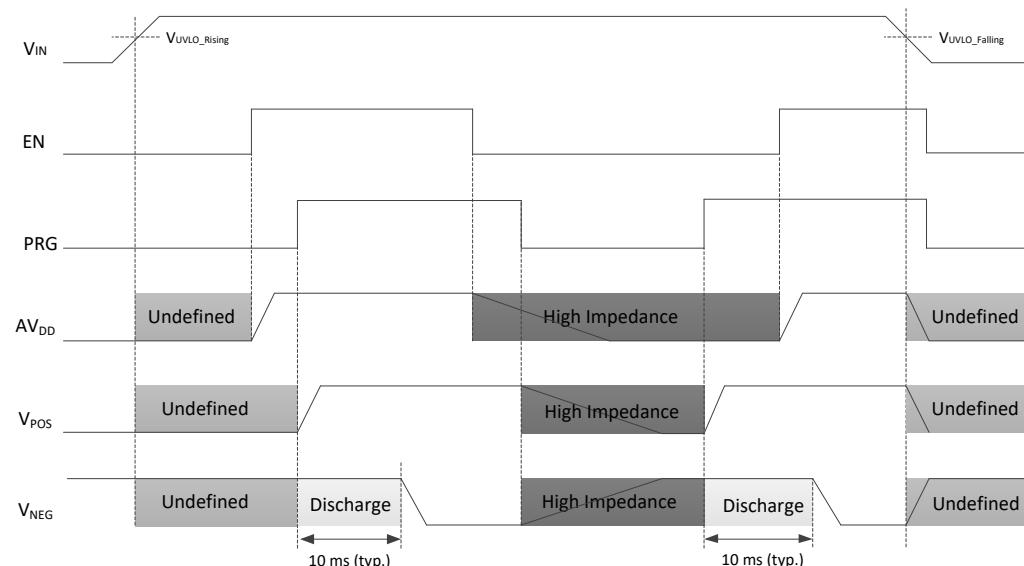

Before the first startup, the output discharge is undefined and the output discharge is activated by PRG rising edge, following the FD configuration. When the converters shut down, the outputs are discharged if FD function is enabled or the outputs are high impedance if FD function is disabled.

Figure 15. Startup and Shutdown Sequence with Fast Discharge

Figure 16. Startup and Shutdown Sequence Without Fast Discharge

## Function Description (continued)

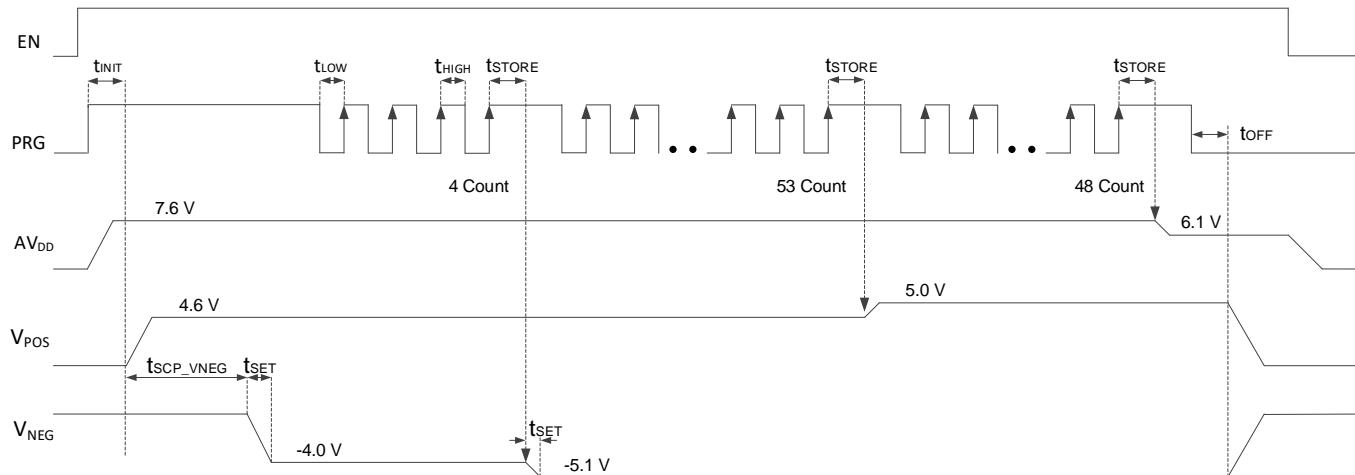

### 1.1 Programming V<sub>POS</sub>, V<sub>NEG</sub> and AV<sub>DD</sub> Output Voltage through PRG Pin

All the output voltage of AL3565 can be programmed through PRG pin. If programming is not required the PRG pin can also be used as a standard enable pin. Once the device is enabled, AL3565 starts with its default values. The interface counts the rising edges applied to the PRG pin and sets the new values. Table 1 to 3 listed the mapping for the rising edge numbers and the corresponding the output voltage.

The settings are stored in a volatile memory, they are reset as follows:

- A power cycle resets all settings to default values.

- Enabling the V<sub>POS</sub> boost/buck-boost converter sets the output discharge. (The output discharge function is controlled by FD pin.)

- If PRG is low for a min. t<sub>OFF</sub>, V<sub>NEG</sub> will be reset to default value and V<sub>POS</sub> will be reset to default value.

- If EN and PRG are low at the same time for min. t<sub>OFF</sub>, AV<sub>DD</sub> will be reset to its default value. If EN is low and PRG is high, AV<sub>DD</sub> retains its programmed value.

Figure 17. Digital Interface Using PRG Pin

---

**Function Description** (continued)**2.0 VPos – Boost/Buck-Boost Converter**

The boost/buck-boost converter VPos uses a fixed-frequency current-mode topology. Its default output voltage VPos is (4.6V) for AL3565. VPos can be programmed through the digital PRG pin. For higher output voltage accuracy, connect the output sense pin (FBS) directly to the positive terminal of the main output capacitor. If not used, the FBS pin shall be tied to ground.

**2.1 Vpos – Asynchronous Buck-Boost Mode**

When VPos is close to VIN, AL3565 enters asynchronous buck-boost mode. In this mode, the high-side power pMOS channel is turned off completely and the power pMOS body diode is used for the conduction.

**2.2 VPos – Boost Converter, Output Sense (FBS pin)**

The positive output boost circuitry has a dedicated output pin (FBS). If FBS is floating or tied to ground, the positive output boost circuitry senses the output through the VPos pin.

**2.3 VPos Voltage Control by PRG Pin**

When the PRG pin is pulled high while the device is enabled, VPos will rise to its default voltage of 4.6V. While the device is enabled, the digital programming interface counts the number of rising edges applied to the PRG pin. Table 1 shows the pulse count for a corresponding programmed VPos voltage. VPos can be programmed in 100mV steps.

| Bit / Rising Edges | VPos |

|--------------------|------|

| Default            | 4.6V |

| 54                 | 4.7V |

| 55                 | 4.8V |

| 56                 | 4.9V |

| 57                 | 5.0V |

| 64                 | 4.6V |

Table 1. Programing Table for AL3565 VPos

---

**Function Description** (continued)**3.0 AVDD – Boost Converter**

Boost converter uses a fixed-frequency current-mode topology. Its default output voltage AVDD is (6.1V) for AL3565. AVDD can be programmed through the digital PRG pin.

**3.1 AVDD Voltage Control by PRG Pin**

Once the device is enabled using the EN pin, AVDD will rise to its default value. While the device is enabled, the digital programming interface counts the number of rising edges applied to the PRG pin. Table 2 shows the pulse count for a corresponding programmed AVDD voltage. AVDD can be programmed in 300mV steps.

| Bit / Rising Edges | AVDD |

|--------------------|------|

| Default            | 6.1V |

| 42                 | 7.9V |

| 43                 | 7.6V |

| 44                 | 7.3V |

| 45                 | 7.0V |

| 46                 | 6.7V |

| 47                 | 6.4V |

| 48                 | 6.1V |

| 49                 | 5.8V |

Table 2. Programing Table for AL3565 AVDD

---

## Function Description (continued)

---

### 4.0 V<sub>NEG</sub> – Inverting Buck-Boost Converter

The inverting buck-boost converter uses a peak current PWM control topology. Its default output voltage V<sub>NEG</sub> is (-2.5V) for AL3565. V<sub>NEG</sub> can be programmed through the digital PRG pin.

### 4.1 V<sub>NEG</sub> Voltage Control by PRG Pin

When the PRG pin is pulled high while the device is enabled, V<sub>NEG</sub> will fall to its default value. While the device is enabled, the digital programming interface counts the number of rising edges applied to the PRG pin. Table 3 shows the pulse count for a corresponding programmed V<sub>NEG</sub> voltage. V<sub>NEG</sub> can be programmed in 100mV steps.

| Bit / Rising Edges | V <sub>VNEG</sub> | Bit / Rising Edges | V <sub>VNEG</sub> |

|--------------------|-------------------|--------------------|-------------------|

| Default            | -2.5V             | 21                 | -3.4V             |

| 1                  | -5.4 V            | 22                 | -3.3V             |

| 2                  | -5.3 V            | 23                 | -3.2V             |

| 3                  | -5.2 V            | 24                 | -3.1V             |

| 4                  | -5.1V             | 25                 | -3.0V             |

| 5                  | -5.0V             | 26                 | -2.9V             |

| 6                  | -4.9V             | 27                 | -2.8V             |

| 7                  | -4.8V             | 28                 | -2.7V             |

| 8                  | -4.7V             | 29                 | -2.6V             |

| 9                  | -4.6V             | 30                 | -2.5V             |

| 10                 | -4.5V             | 31                 | -2.4V             |

| 11                 | -4.4V             | 32                 | -2.3V             |

| 12                 | -4.3V             | 33                 | -2.2V             |

| 13                 | -4.2V             | 34                 | -2.1V             |

| 14                 | -4.1V             | 35                 | -2.0V             |

| 15                 | -4.0V             | 36                 | -1.9V             |

| 16                 | -3.9V             | 37                 | -1.8V             |

| 17                 | -3.8V             | 38                 | -1.7V             |

| 18                 | -3.7V             | 39                 | -1.6V             |

| 19                 | -3.6V             | 40                 | -1.5V             |

| 20                 | -3.5V             | 41                 | -1.4V             |

Table 3. Programming Table for AL3565 V<sub>NEG</sub>

## Function Description (continued)

### 5.0 FD Control

When PRG is pulled high, the fast discharge (FD) function will be initialized to its default state according to the FD pin. If the FD pin is connected to GND, fast discharge is disabled and all outputs are high impedance. If the FD pin is connected to HIGH (HIGH > 1.2V), fast discharge is enabled and all outputs are discharged.

The fast discharge function can also be controlled through the PRG pin, which would override the FD pin connection setting. Table 4 shows the pulse rising edges count for a corresponding programmed FD function (ON/OFF).

| Bit / Rising Edges | FD Pin | FD  | Comment       |

|--------------------|--------|-----|---------------|

| Default / 0        | HIGH   | ON  | Using FD pin  |

|                    | GND    | OFF | Using FD pin  |

| 50                 | X      | ON  | Using PRG pin |

| 51                 | X      | OFF | Using PRG pin |

Table 4. Programming Table for FD Control

Only in the “Yellow Highlighted” area, we can use pulses applied to PRG pin to disable/enable fast discharge, no matter how FD pin is configured. As shown, V<sub>NEG</sub> always needs Fast Discharge active at power-up.

Figure 18. Fast Discharge sequence with FD = high, but discharge can be disabled by PRG (Table 4) in yellow highlighted area

Figure 19. Without Fast Discharge sequence with FD = low, but discharge can be enabled by PRG (Table 4) in yellow highlighted area

---

**Function Description** (continued)**6.0 Short-Circuit Protection (SCP)**

AL3565 detects short and shuts down in one of the below conditions:

- AVDD falls below 90% of its programmed voltage for more than 1ms after power-up: shutdown VPOS/VNEG/AVDD

- VPOS falls below 90% of its programmed voltage for more than 1ms after power-up: shutdown VPOS/VNEG/AVDD

- VNEG rises above 500mV of its programmed voltage longer than 1ms: shutdown VPOS/VNEG/ AVDD

- VNEG > 200mV (during startup) when VNEG is enabled (10ms after PRG = HIGH): shutdown VPOS and VNEG only

The shutdown state is latched, and the input and outputs are disconnected. To restart the device, VIN must cycle below UVLO or EN and PRG have to be low at the same time for 80 $\mu$ s (t<sub>OFF</sub> max spec) or longer.

See Section 7 – *Inductor/Capacitor Selection* for recommended inductor & capacitor values.

**6.1 Thermal Shutdown**

The AL3565 device enters thermal shutdown if its junction temperature exceeds +150°C (typical). During thermal shutdown none of the device's functions are available, but the programming data is not lost. When the temperature decreases to +140°C (typical), the device automatically restarts performing the startup sequencing with the same voltages and programming as programmed before the thermal shutdown.

## Application Information

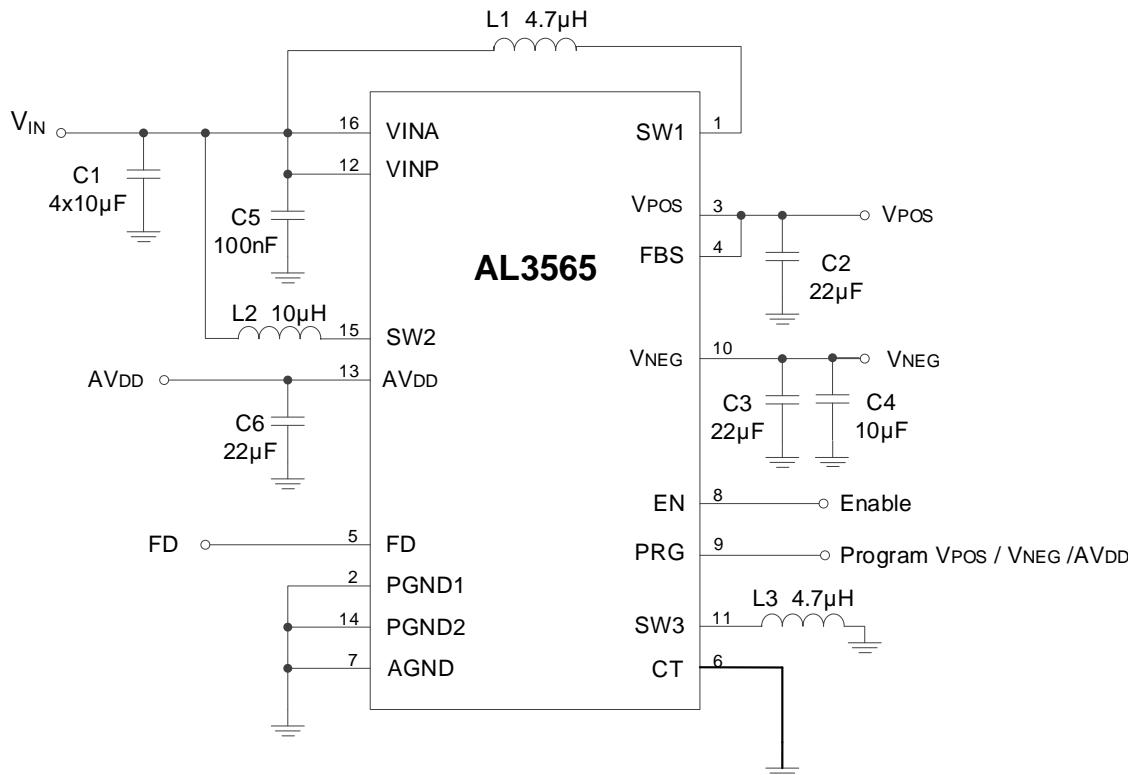

### 7.0 Inductor/Capacitor Selection

The AL3565 is designed for supplying power to AMOLED display in smart phone applications. The circuit inputs power from a single-cell Li-ion battery and generates an adjustable power supply AVDD, an adjustable positive output voltage VPOS and an adjustable negative output voltage VNEG.

The AVDD boost converter typically requires a  $10\mu\text{H}$  inductor, VPOS and VNEG require a  $4.7\mu\text{H}$ . The input and output capacitors are usually ceramic capacitors. Table 5 lists the recommended component for typical circuit configurations. Please contact us for any further components optimizations on either efficiency or sizes.

Figure 20. Typical Application Circuit

The AL3565 is designed to operate with the input voltage ranging from 2.9V to 4.8V. If the input supply is located more than a few centimeters from the AL3565, additional bulk capacitors may be needed. The (4)  $10\mu\text{F}$  (C1) capacitors shown in the typical application circuit are a common choice.

| Component              | Designator | Value                                                                                    | Part Number                          | Manufacturer |

|------------------------|------------|------------------------------------------------------------------------------------------|--------------------------------------|--------------|

| AVDD inductor          | L2         | $10\mu\text{H}\pm20\%$                                                                   | DFE252012C-100M                      | TOKO         |

| VPOS and VNEG inductor | L1, L3     | $4.7\mu\text{H}\pm20\%$                                                                  | DFE252012F-4R7M                      | muRata       |

|                        |            |                                                                                          | DFE252012P-4R7N                      | TOKO         |

|                        |            |                                                                                          | GRM219R61A106ME47                    | muRata       |

| AVDD capacitor         | C6         | $22\mu\text{F}\pm20\% / 25\text{V} / 0805$                                               | CL21A226MPCLRNC                      | muRata       |

| VPOS capacitor         | C2         | $22\mu\text{F}\pm20\% / 25\text{V} / 0805$                                               | CL21A226MPCLRNC                      | muRata       |

| VNEG capacitor         | C3, C4     | $22\mu\text{F}\pm20\% / 25\text{V} / 0805$<br>$10\mu\text{F}\pm20\% / 25\text{V} / 0805$ | CL21A226MPCLRNC<br>GRM219R61A106ME47 | muRata       |

Table 5. Component Selection Table

---

**Application Information** (continued)

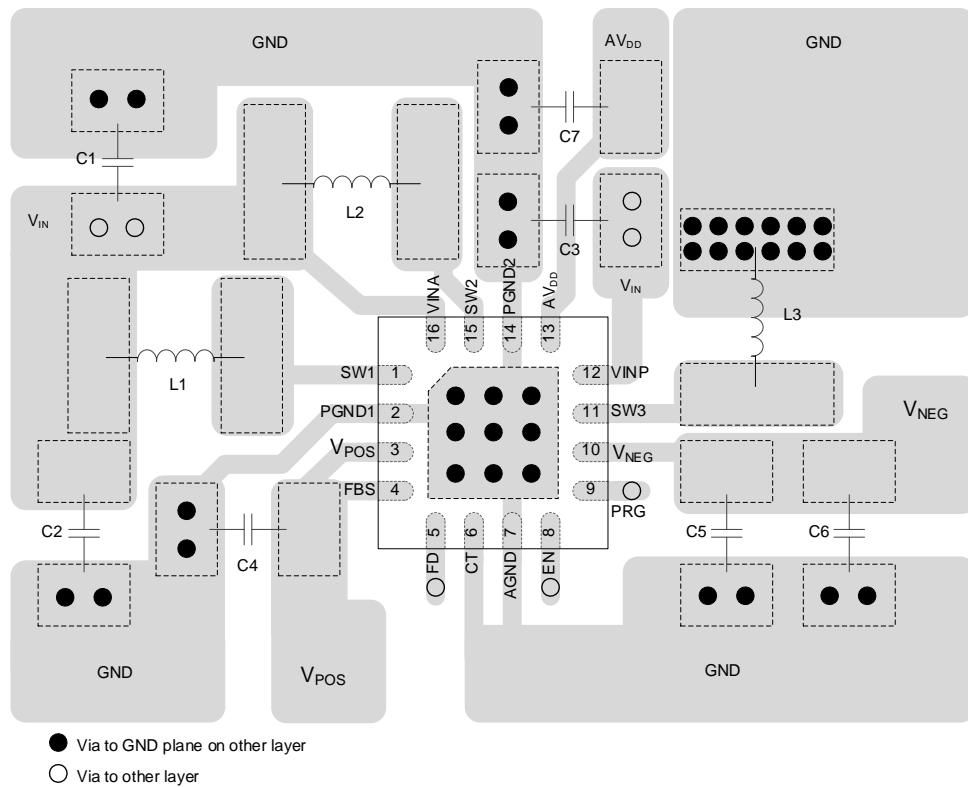

**8.0 Layout Guidelines**

1. Place the input capacitor on  $V_{INP}$  and the output capacitor on  $V_{NEG}$  as close as possible to device. Use short and wide traces to connect the input capacitor on  $V_{INP}$  and the output capacitor on  $V_{NEG}$ .

2. Place the output capacitor on  $V_{POS}$  and  $AV_{DD}$  as close as possible to device. Use short and wide traces to connect the output capacitor on  $V_{POS}$  and  $AV_{DD}$ .

3. Connect the ground of CT capacitor with  $AGND$  (pin 7) directly.

4. Connect input ground and output ground on the same board layer, not through via hole.

5. Connect  $AGND$ ,  $PGND1$  and  $PGND2$  with exposed thermal pad.

**8.1 Layout Example**

Figure 21. Recommended PCB Layout

---

**Design Tools**

- Demo Board

- Calculator

- Demo Board Gerber File of PCB Layout Reference

- PSPICE

---

**Ordering Information**

---

AL3565 DA-7

DA : U-QFN3030-16 (Type B)      7 : Tape &amp; Reel

| Orderable Part Number | Part Number Suffix | Package Code | Package (Note 5)      | Packing |             |

|-----------------------|--------------------|--------------|-----------------------|---------|-------------|

|                       |                    |              |                       | Qty.    | Carrier     |

| AL3565DA-7            | -7                 | DA           | U-QFN3030-16 (Type B) | 1,500   | Tape & Reel |

Note: 5. For packaging details, go to our website at <https://www.diodes.com/design/support/packaging/diodes-packaging/>.

---

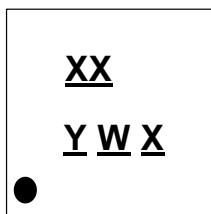

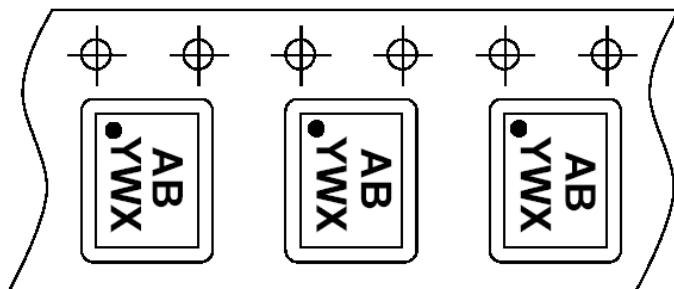

**Marking Information**

---

U-QFN3030-16 (Type B)

(Top View)

XX : Identification Code

Y : Year : 0 to 9 (ex: 3 = 2023)

W : Week : A to Z : week 1 to 26;

a to z : week 27 to 52;

z represents week 52 and 53

X : A to G : Green

| Orderable Part Number | Package               | Identification Code |

|-----------------------|-----------------------|---------------------|

| AL3565DA-7            | U-QFN3030-16 (Type B) | S9                  |

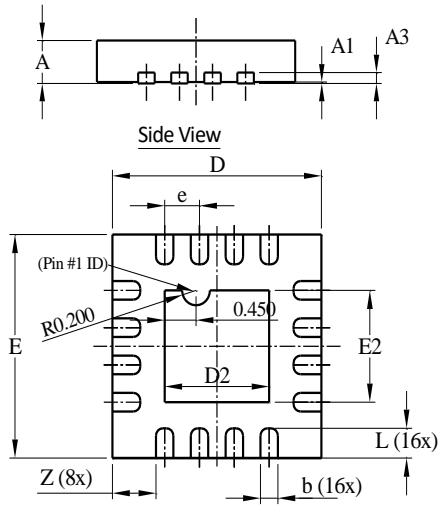

## Package Outline Dimensions

Please see <http://www.diodes.com/package-outlines.html> for the latest version.

U-QFN3030-16 (Type B)

| U-QFN3030-16<br>Type B |      |      |       |

|------------------------|------|------|-------|

| Dim                    | Min  | Max  | Typ   |

| A                      | 0.55 | 0.65 | 0.60  |

| A1                     | 0    | 0.05 | 0.02  |

| A3                     | -    | -    | 0.15  |

| b                      | 0.18 | 0.28 | 0.23  |

| D                      | 2.95 | 3.05 | 3.00  |

| D2                     | 1.40 | 1.60 | 1.50  |

| E                      | 2.95 | 3.05 | 3.00  |

| E2                     | 1.40 | 1.60 | 1.50  |

| e                      | -    | -    | 0.50  |

| L                      | 0.35 | 0.45 | 0.40  |

| Z                      | -    | -    | 0.625 |

All Dimensions in mm

Bottom View

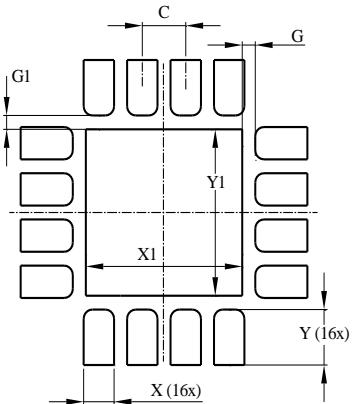

## Suggested Pad Layout

Please see <http://www.diodes.com/package-outlines.html> for the latest version.

U-QFN3030-16 (Type B)

| Dimensions | Value (in mm) |

|------------|---------------|

| C          | 0.500         |

| G          | 0.150         |

| G1         | 0.150         |

| X          | 0.350         |

| X1         | 1.800         |

| Y          | 0.600         |

| Y1         | 1.800         |

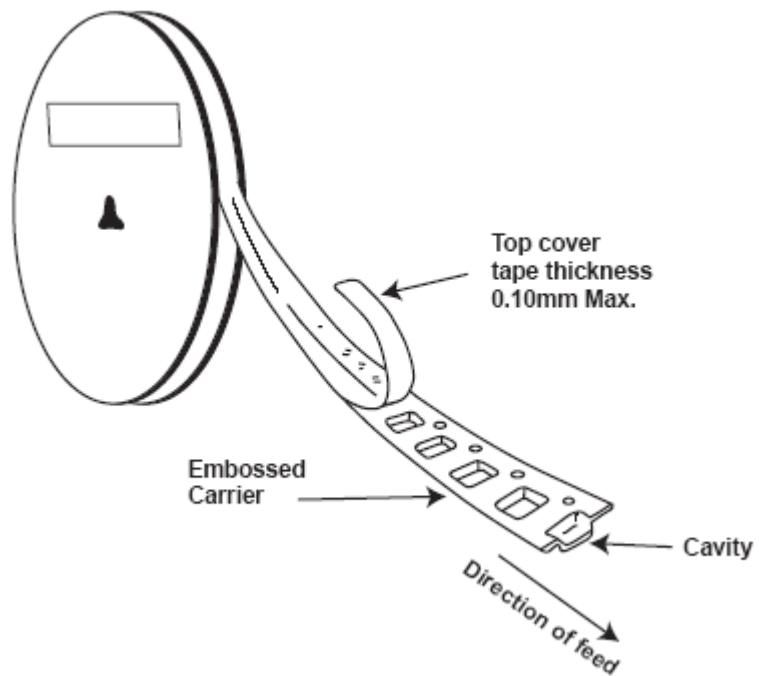

## Mechanical Data

- Moisture Sensitivity: Level 1 per JESD22-A113

- Terminals: Finish - Preplated NiPdAu, Solderable per JESD22-B102 [e4](#)

- Weight: 0.017 grams (Approximate)

## Taping Orientation

The taping orientation of other package type can be found on our website at <https://www.diodes.com/assets/Packaging-Support-Docs/ap02007.pdf>.

**IMPORTANT NOTICE**

1. DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products for their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

5. Diodes' products are provided subject to Diodes' Standard Terms and Conditions of Sale (<https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/>) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

6. Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

9. This Notice may be periodically updated with the most recent version available at <https://www.diodes.com/about/company/terms-and-conditions/important-notice>

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries.

All other trademarks are the property of their respective owners.

© 2025 Diodes Incorporated. All Rights Reserved.

[www.diodes.com](http://www.diodes.com)