## Digital Input Class-D Amplifier with IV Feedback and Brownout Protection

MAX98388/MAX98389

### General Description

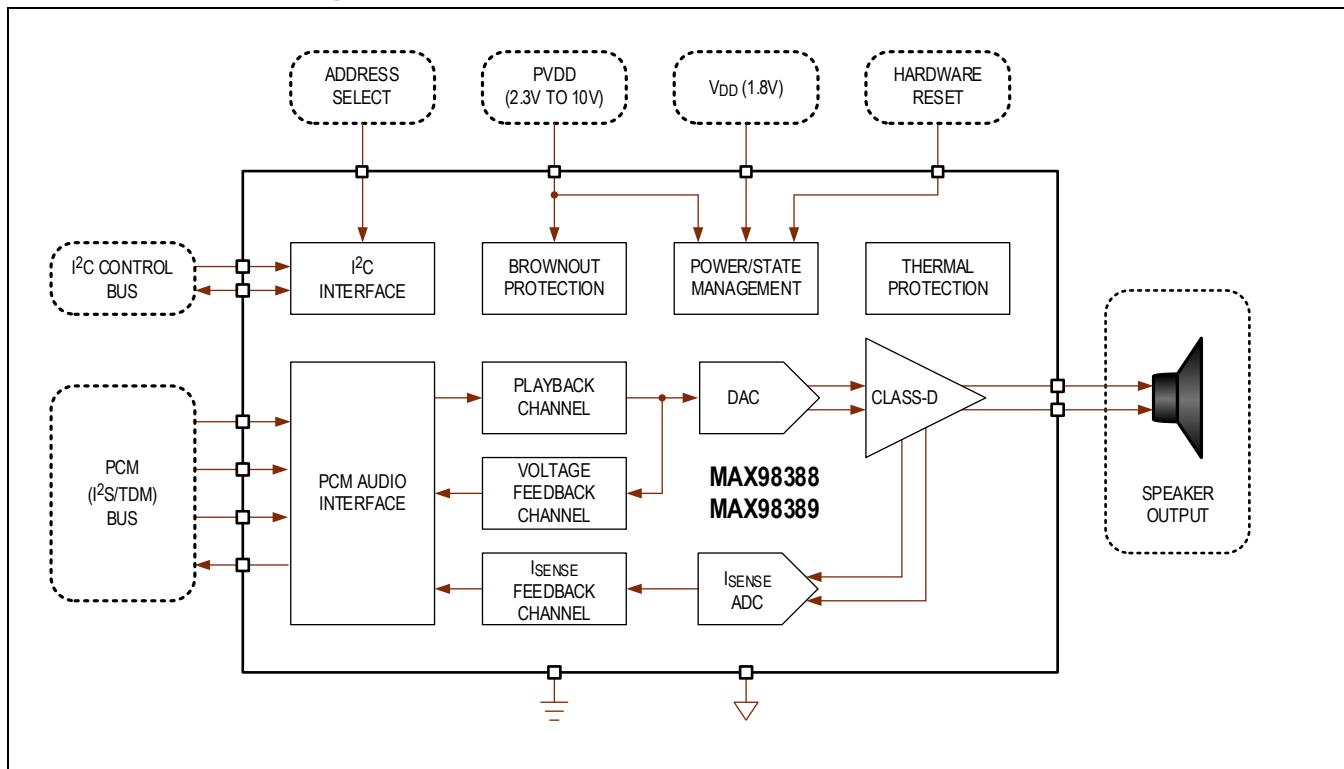

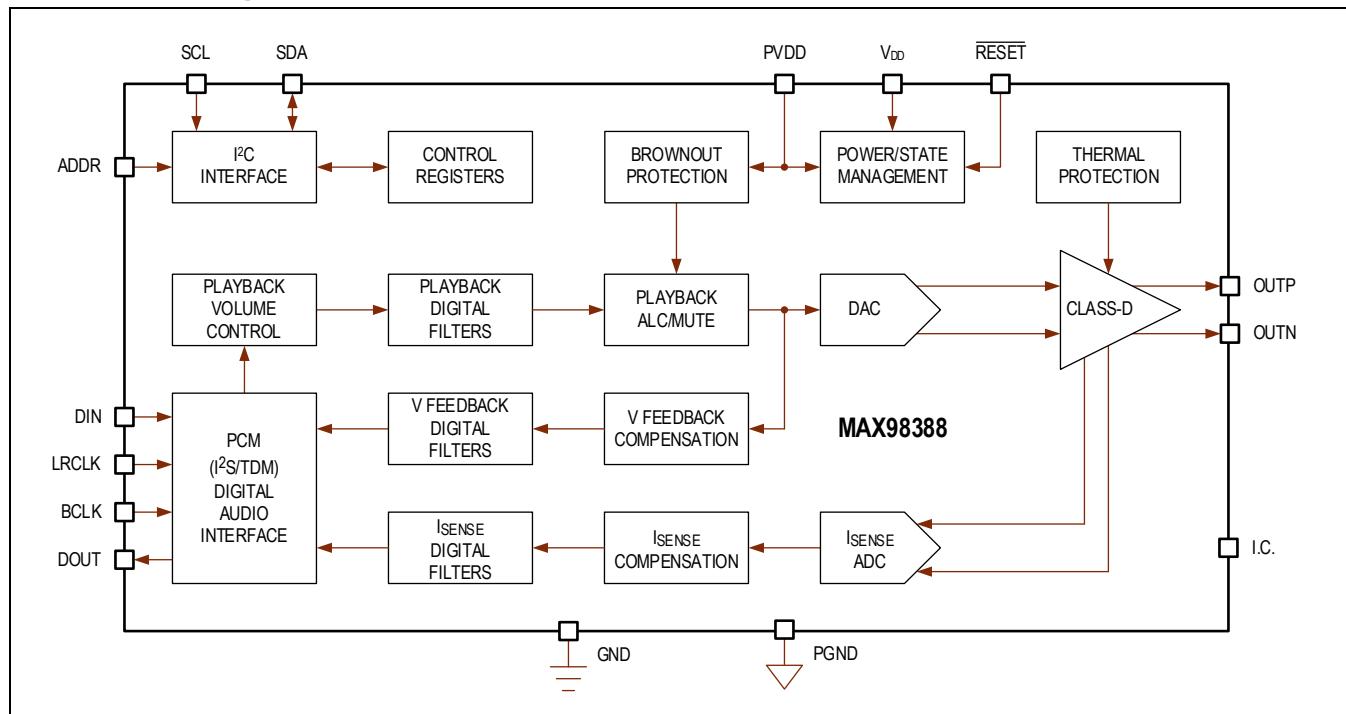

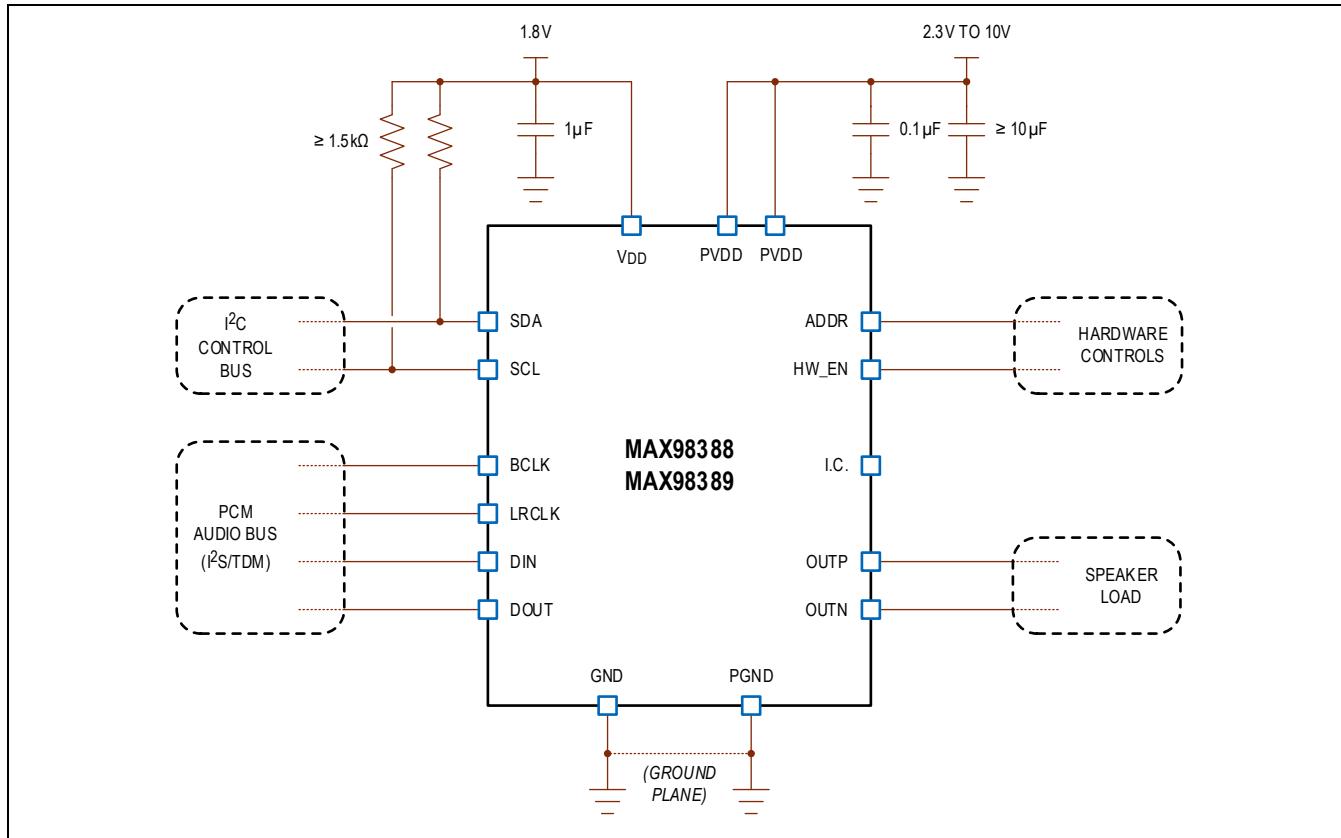

The MAX98388/MAX98389 is a small, cost-effective mono digital input amplifier with integrated IV feedback. The device operates over a wide supply voltage range from 2.3V to 10V. With this supply range, both versions support single-cell, two-cell, and externally regulated/boosted portable applications. MAX98388 is optimized for up to 5.5V applications (single-cell), while MAX98389 is optimized for 5V to 10V cases (two-cell).

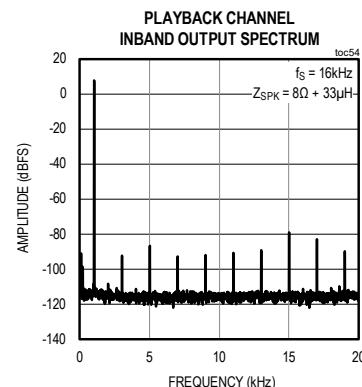

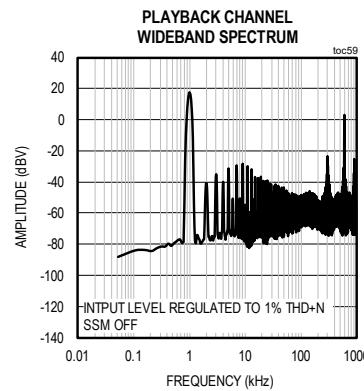

The Class-D playback amplifier pairs Class-AB level audio performance with the efficiency needed to extend battery life in portable applications. Active emissions-limiting (AEL) and edge-rate limiting circuitry combined with a spread-spectrum modulation (SSM) scheme reduces EMI and eliminates the need for the output filtering required for traditional Class-D amplifiers.

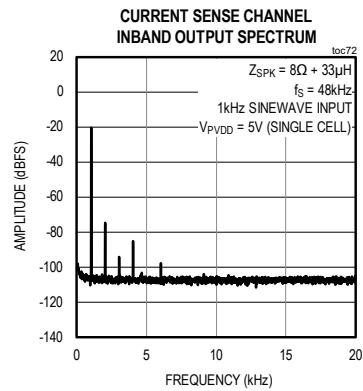

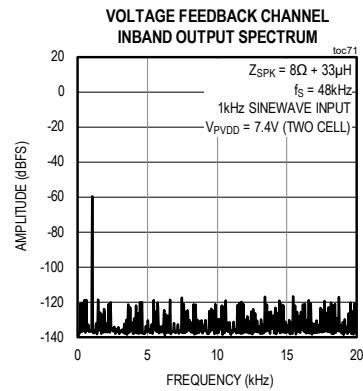

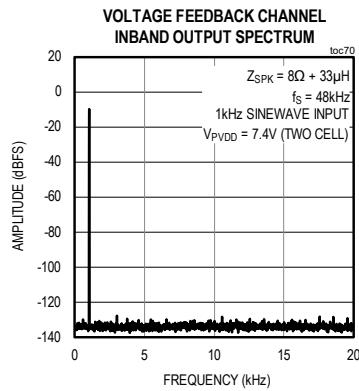

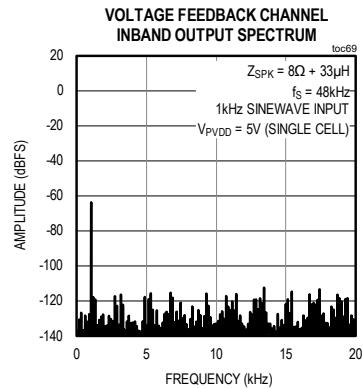

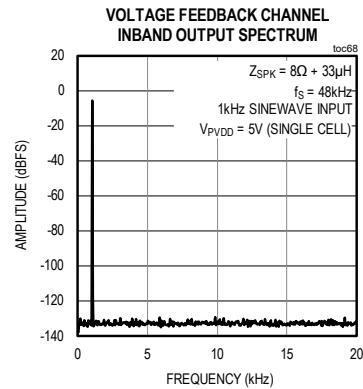

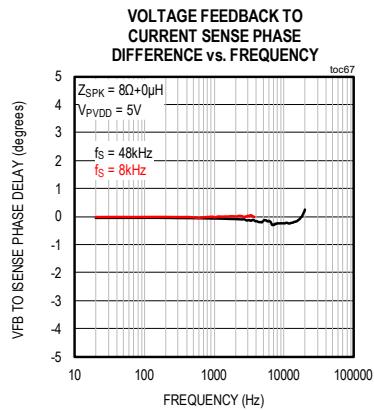

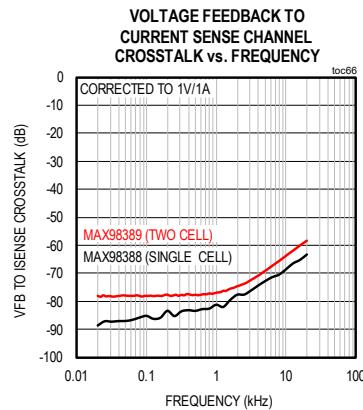

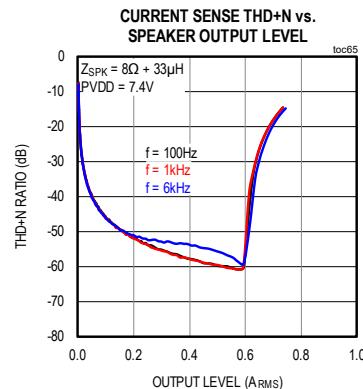

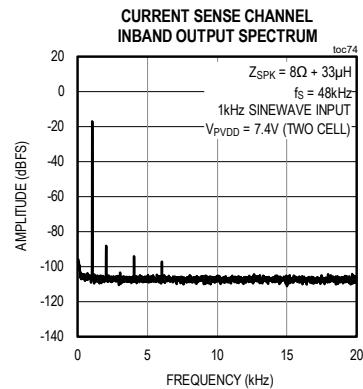

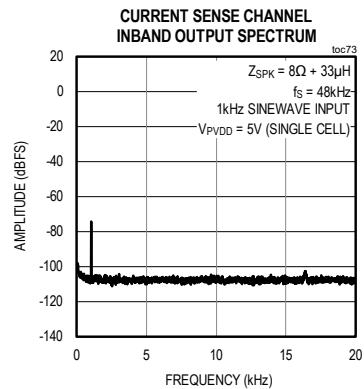

The device provides a precision output current sense channel and an output voltage feedback channel. The data collected by these channels can be transmitted on the audio data output and enables algorithms such as audio enhancement, bass boosting, speaker protection, and haptic functions to be run on the host audio DSP.

The device includes a programmable threshold playback channel ALC that provides brownout protection for batteries in portable systems, and robust thermal and overcurrent protection to prevent device damage.

The device provides a PCM interface for audio playback and IV feedback data and pairs this with a standard I<sup>2</sup>C interface for device control and status readback. The PCM interface supports common audio data formats such as I<sup>2</sup>S, left justified, and TDM timing. A unique clocking structure eliminates the need for an external high-frequency reference clock. In addition to reducing device size and pin count, eliminating this clock saves interface power while reducing the risk of EMI from high-speed switching and potential board coupling issues.

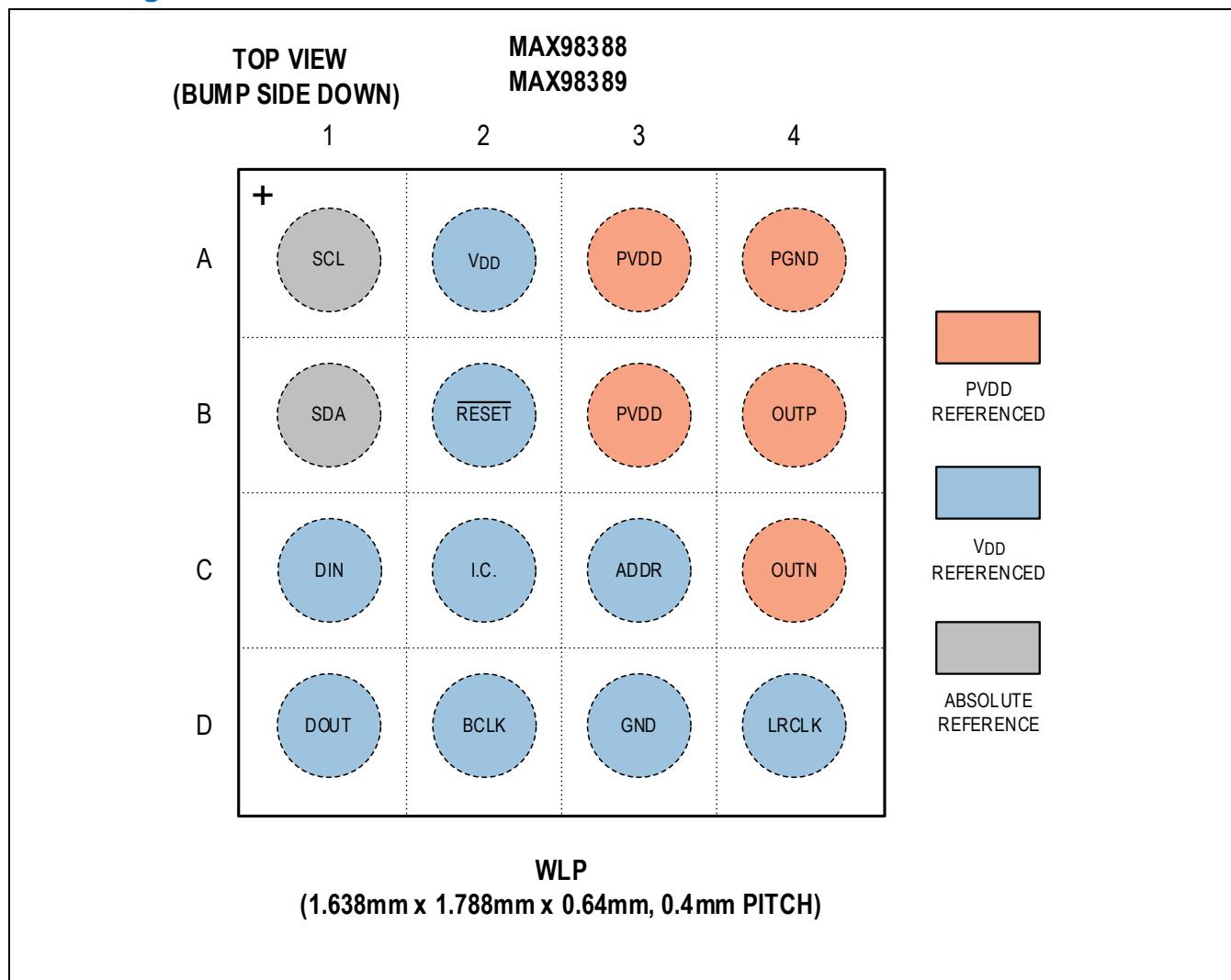

The package connections are designed to only require edge routing, allowing the use of the cost-effective wafer-level package (WLP) with no requirement for expensive bump vias. The device is available in a 0.4mm pitch 16-bump WLP package and is specified over the extended -40°C to +85°C temperature range.

SMBus is a trademark of Intel Corp.

### Benefits and Features

- Wide Amplifier Supply Range (2.3V to 10V)

- Supports Both Single-Cell and Two-Cell Cases

- High-Performance Class-D Amplifier

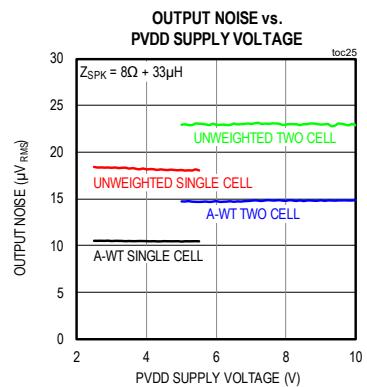

- Up to 111dB Dynamic Range (A-Weighted)

- 10µVRMS Output Noise (Single-Cell Mode)

- 14.5µVRMS Output Noise (Two-Cell Mode)

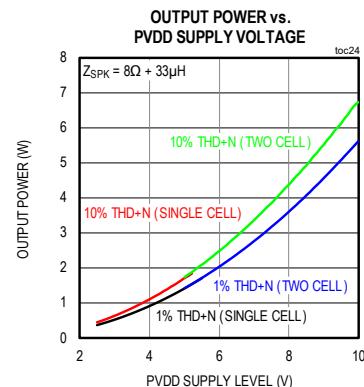

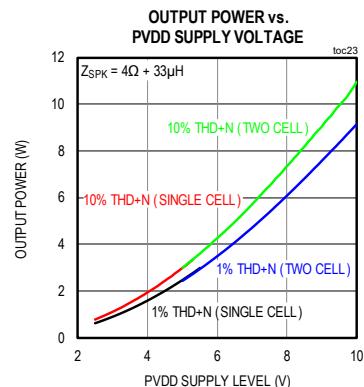

- High Output Power (THD+N ≤ 1%)

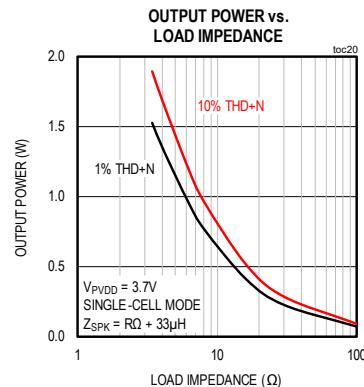

- 1.32W Output Power into 4Ω (V<sub>PVDD</sub> = 3.7V)

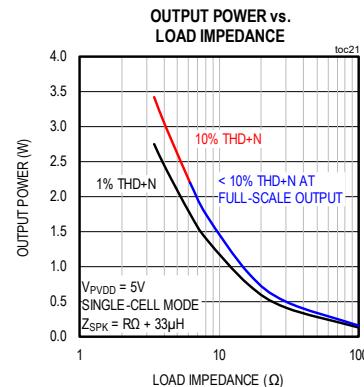

- 2.4W Output Power into 4Ω (V<sub>PVDD</sub> = 5V)

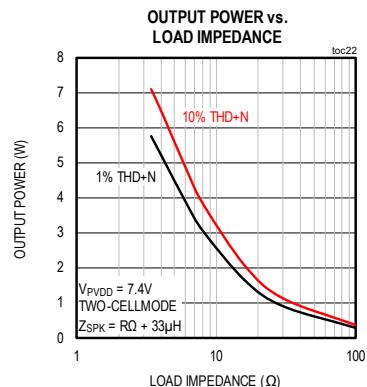

- 5.15W Output Power into 4Ω (V<sub>PVDD</sub> = 7.4V)

- 9.1W Output Power into 4Ω (V<sub>PVDD</sub> = 10V)

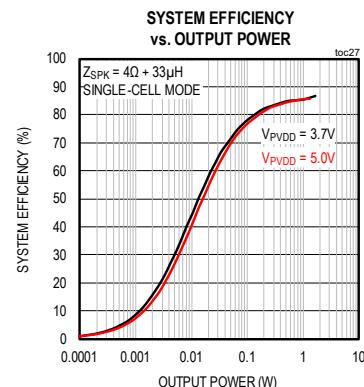

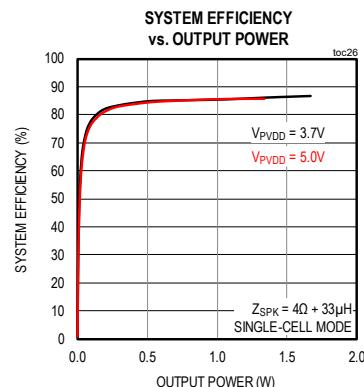

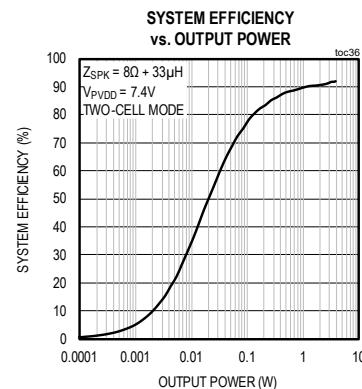

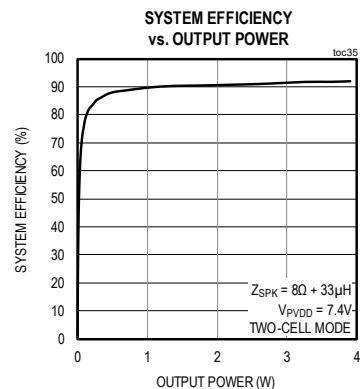

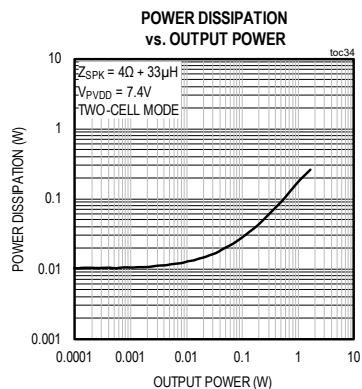

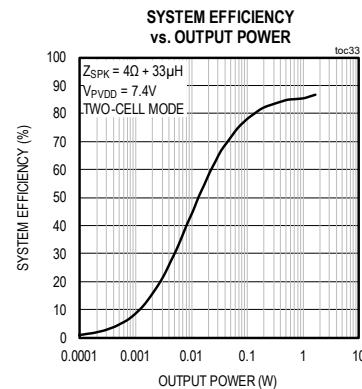

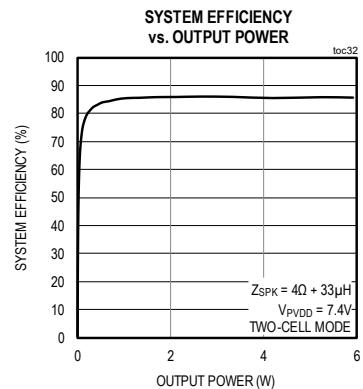

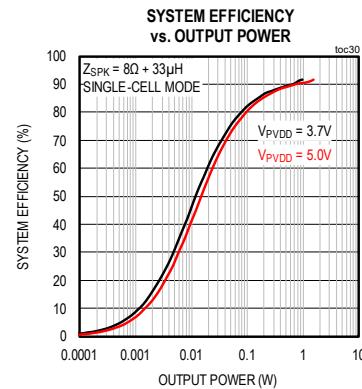

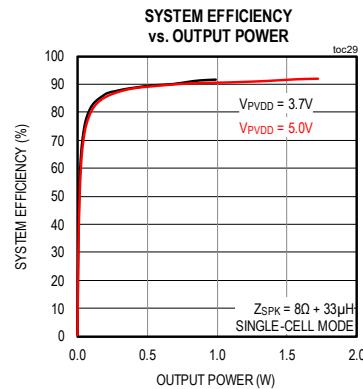

- High Amplifier Efficiency (Playback Only Power)

- 76% Efficiency at 0.1W into 4Ω (V<sub>PVDD</sub> = 5V)

- 85.5% Efficiency at 1W into 4Ω (V<sub>PVDD</sub> = 5V)

- 90% Efficiency at 1W into 8Ω (V<sub>PVDD</sub> = 5V)

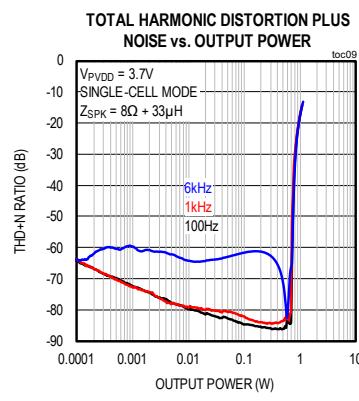

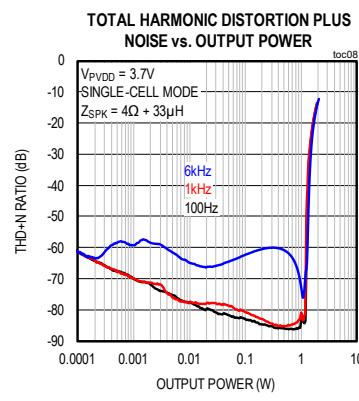

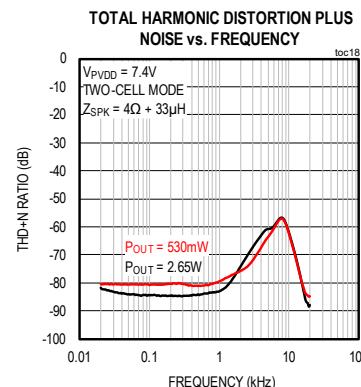

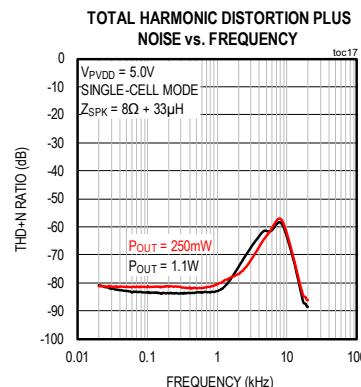

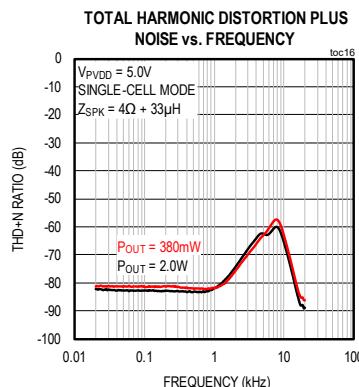

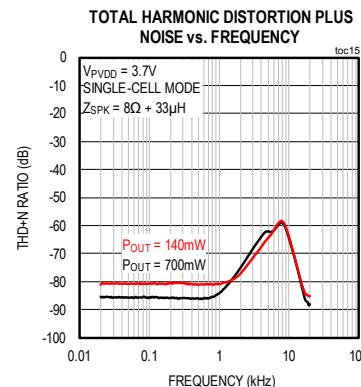

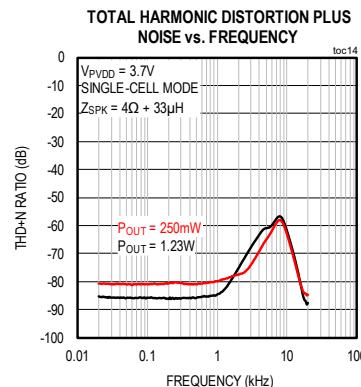

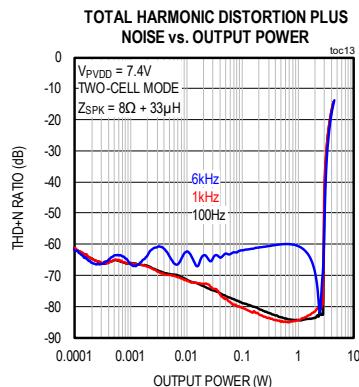

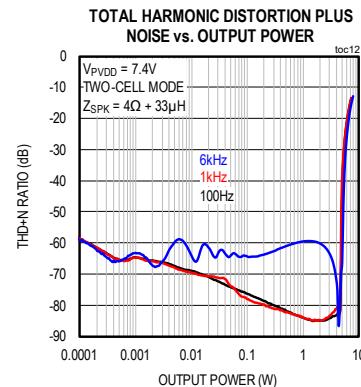

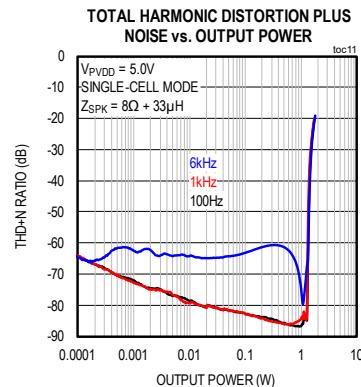

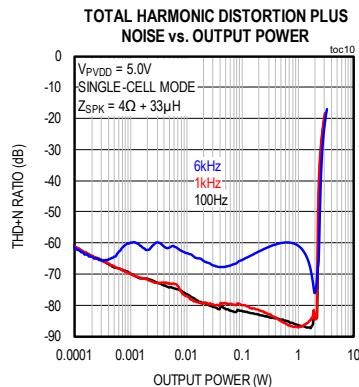

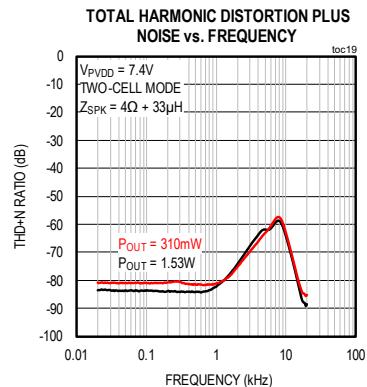

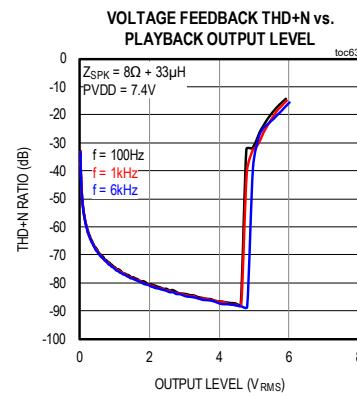

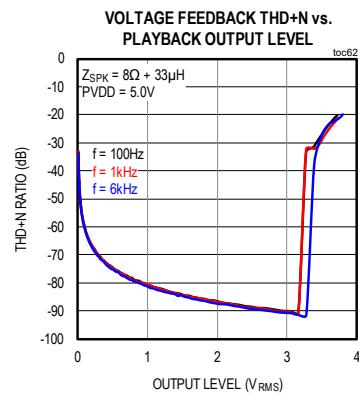

- Peak THD+N Better than -83dB at 1kHz

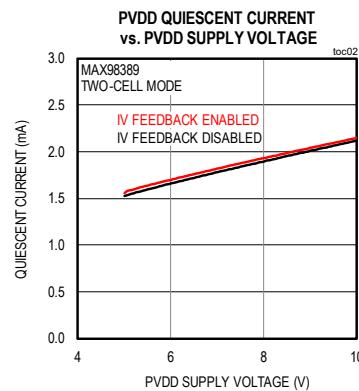

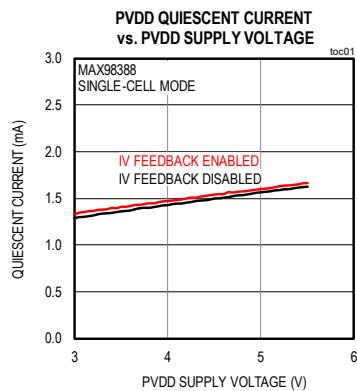

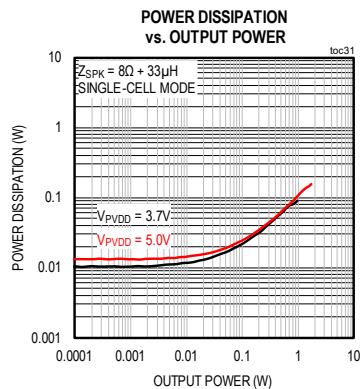

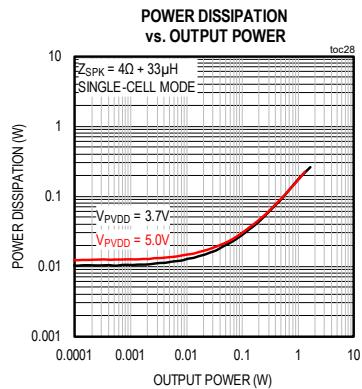

- Low Total Quiescent Power

- 9.3mW (V<sub>PVDD</sub> = 3.7V, IV Feedback Disabled)

- 13.9mW (V<sub>PVDD</sub> = 3.7V, IV Feedback Enabled)

- 16.1mW (V<sub>PVDD</sub> = 5V, IV Feedback Enabled)

- 22.5mW (V<sub>PVDD</sub> = 7.4V, IV Feedback Enabled)

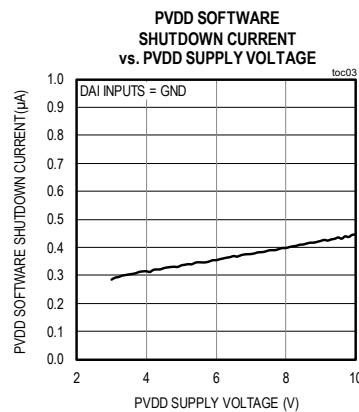

- Low < 5µW Software Shutdown Power

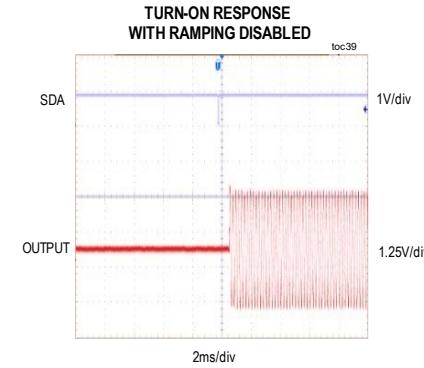

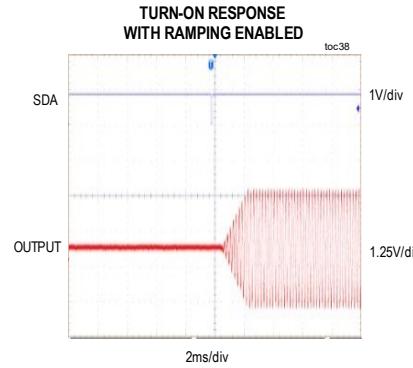

- 1ms Turn-On Time (f<sub>S</sub> = 48kHz, Ramp Disabled)

- Five Sample Playback Delay (f<sub>S</sub> < 50kHz, f<sub>IN</sub> = 1kHz)

- No External Reference Clock Required

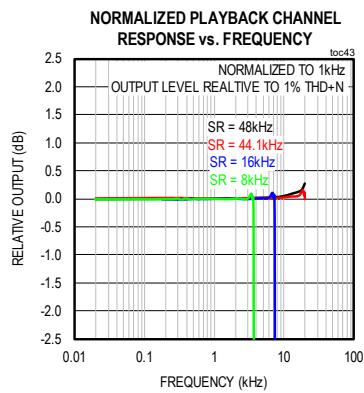

- Playback Sample Rates from 8kHz to 96kHz

- Trimmed Class-D Switching Frequency for EMI Planning

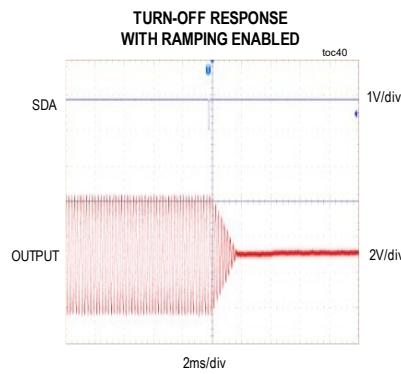

- Extensive Click-and-Pop Reduction Circuitry

- Programmable ALC for Brownout Protection

- Robust Short-Circuit and Thermal Protection

- Available in Space-Saving Package:

- 2.93mm<sup>2</sup>, 16-pin WLP (0.4mm Pitch)

### Applications

- AR/VR Wearables

- LRA Haptic Drive

- Smart Watches and IoT Devices

- Gaming Devices

- Notebooks and Tablets

[Ordering Information](#) appears at end of data sheet.

## Simplified Block Diagram

---

**TABLE OF CONTENTS**

---

|                                                            |    |

|------------------------------------------------------------|----|

| General Description .....                                  | 1  |

| Benefits and Features .....                                | 1  |

| Applications .....                                         | 1  |

| Simplified Block Diagram .....                             | 2  |

| Absolute Maximum Ratings .....                             | 5  |

| Package Information .....                                  | 5  |

| Electrical Characteristics .....                           | 6  |

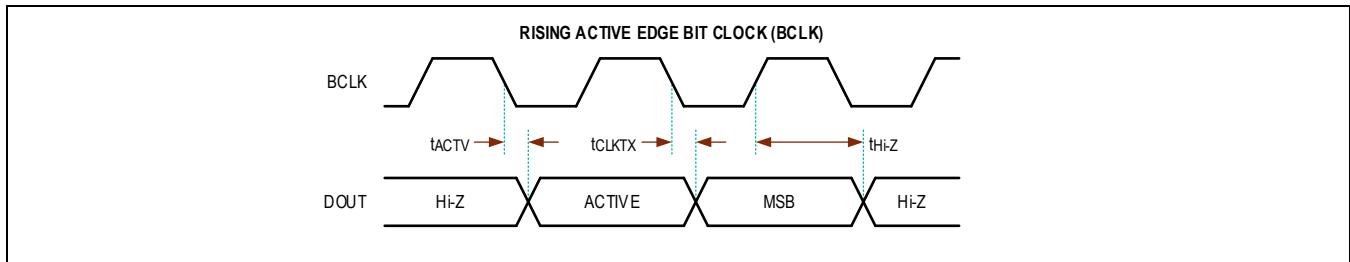

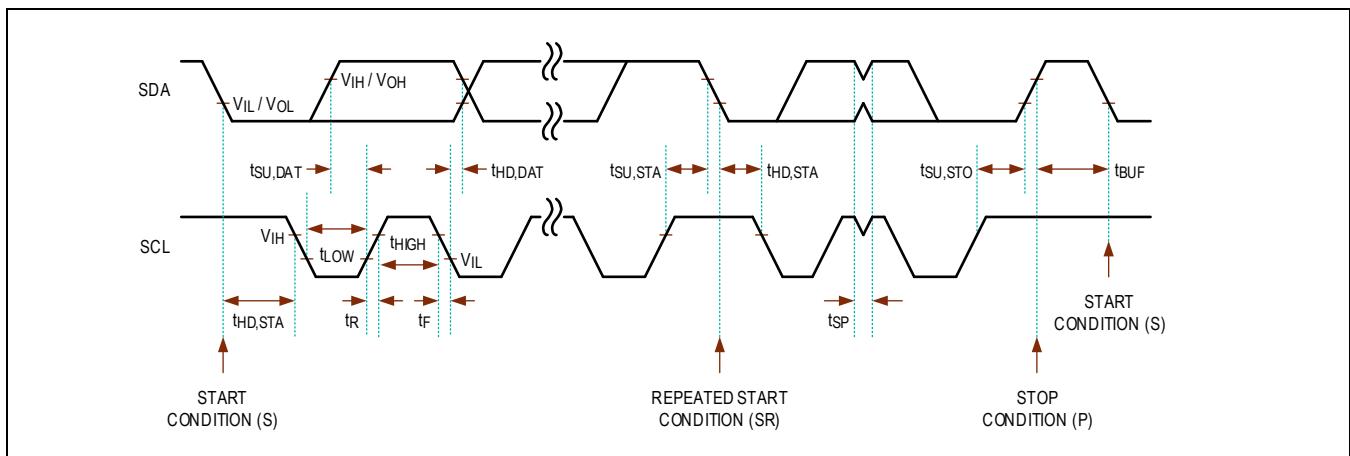

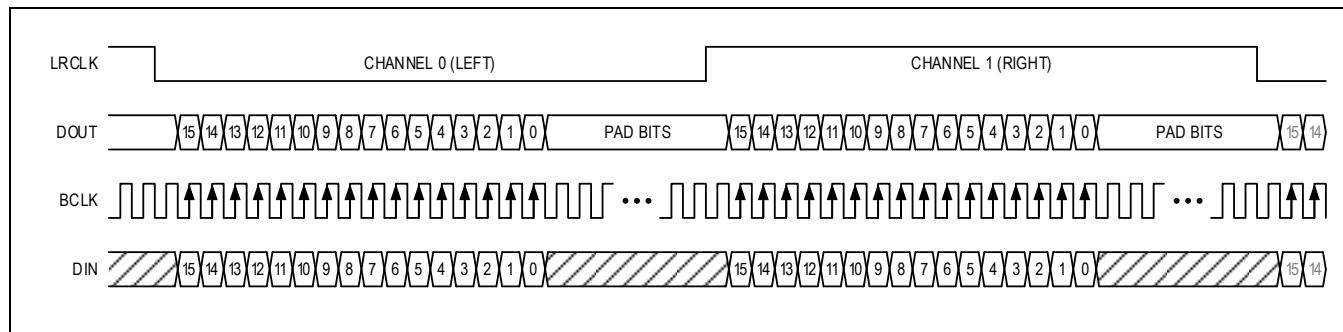

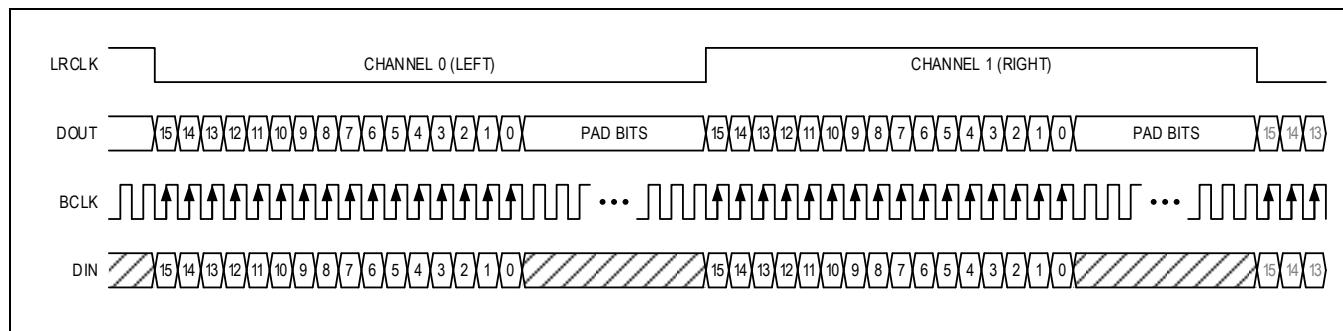

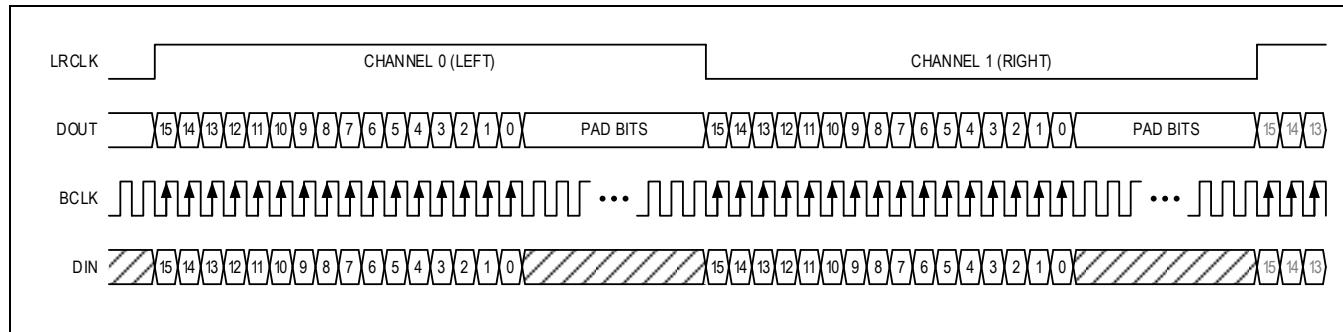

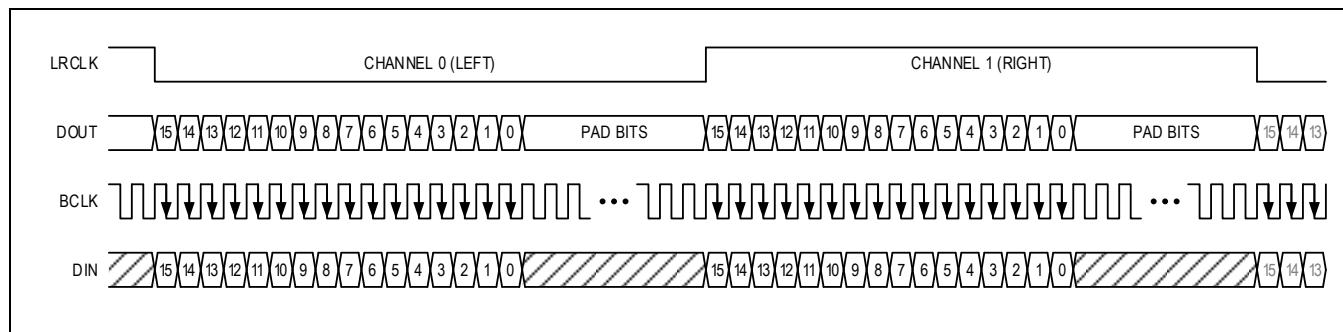

| Timing Diagrams .....                                      | 16 |

| Typical Operating Characteristics .....                    | 18 |

| Pin Configurations .....                                   | 27 |

| Pin Descriptions .....                                     | 27 |

| Functional Diagram .....                                   | 29 |

| Detailed Description .....                                 | 30 |

| Device State Control .....                                 | 30 |

| Hardware-Shutdown State .....                              | 30 |

| Software-Shutdown State .....                              | 30 |

| Active State .....                                         | 30 |

| Power Supply Sequencing .....                              | 30 |

| Device Sequencing .....                                    | 31 |

| Example Device Enable Sequencing .....                     | 31 |

| Example Device Disable Sequencing .....                    | 32 |

| Device Status Event Reporting .....                        | 33 |

| Raw Status (RAW) .....                                     | 33 |

| State Status (STATE) .....                                 | 33 |

| Device Status Event Sources .....                          | 33 |

| PCM Interface .....                                        | 35 |

| PCM Clock Configuration .....                              | 35 |

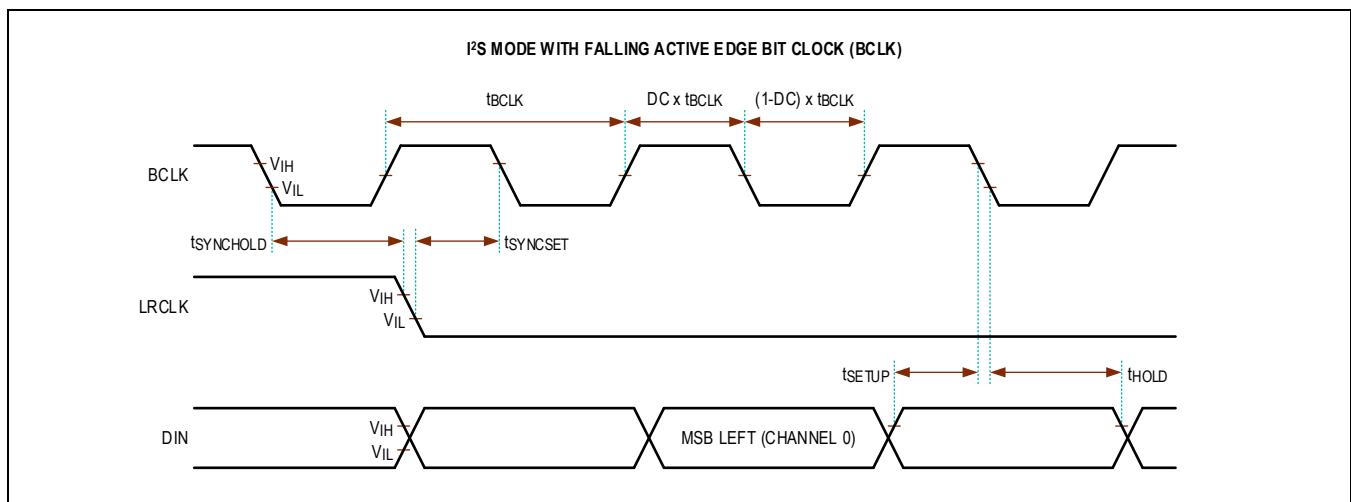

| PCM Data Format Configuration .....                        | 36 |

| I <sup>2</sup> S/Left-Justified Mode .....                 | 36 |

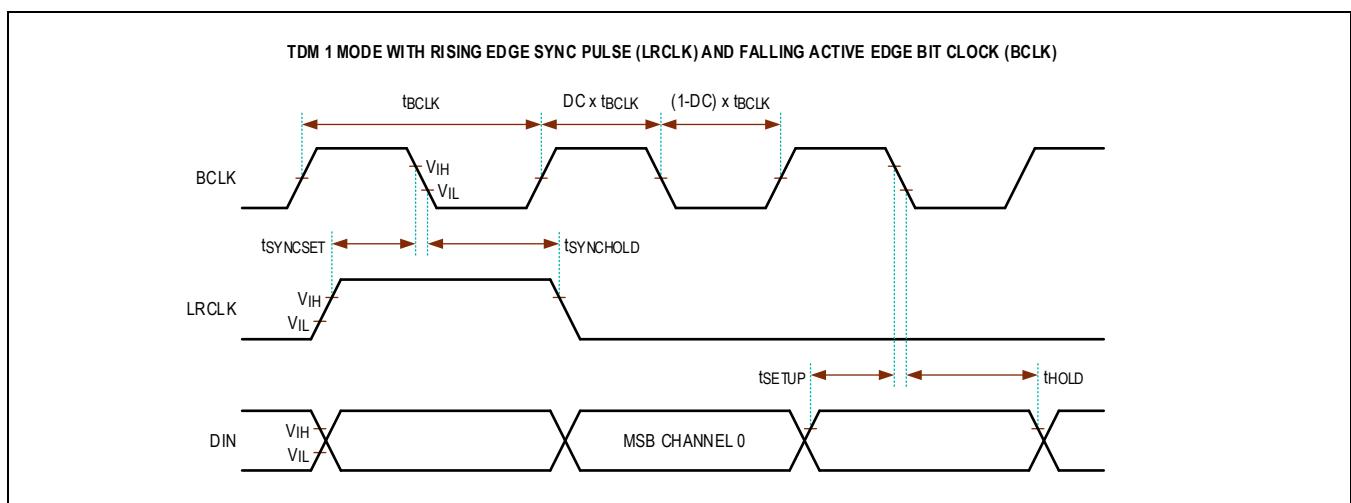

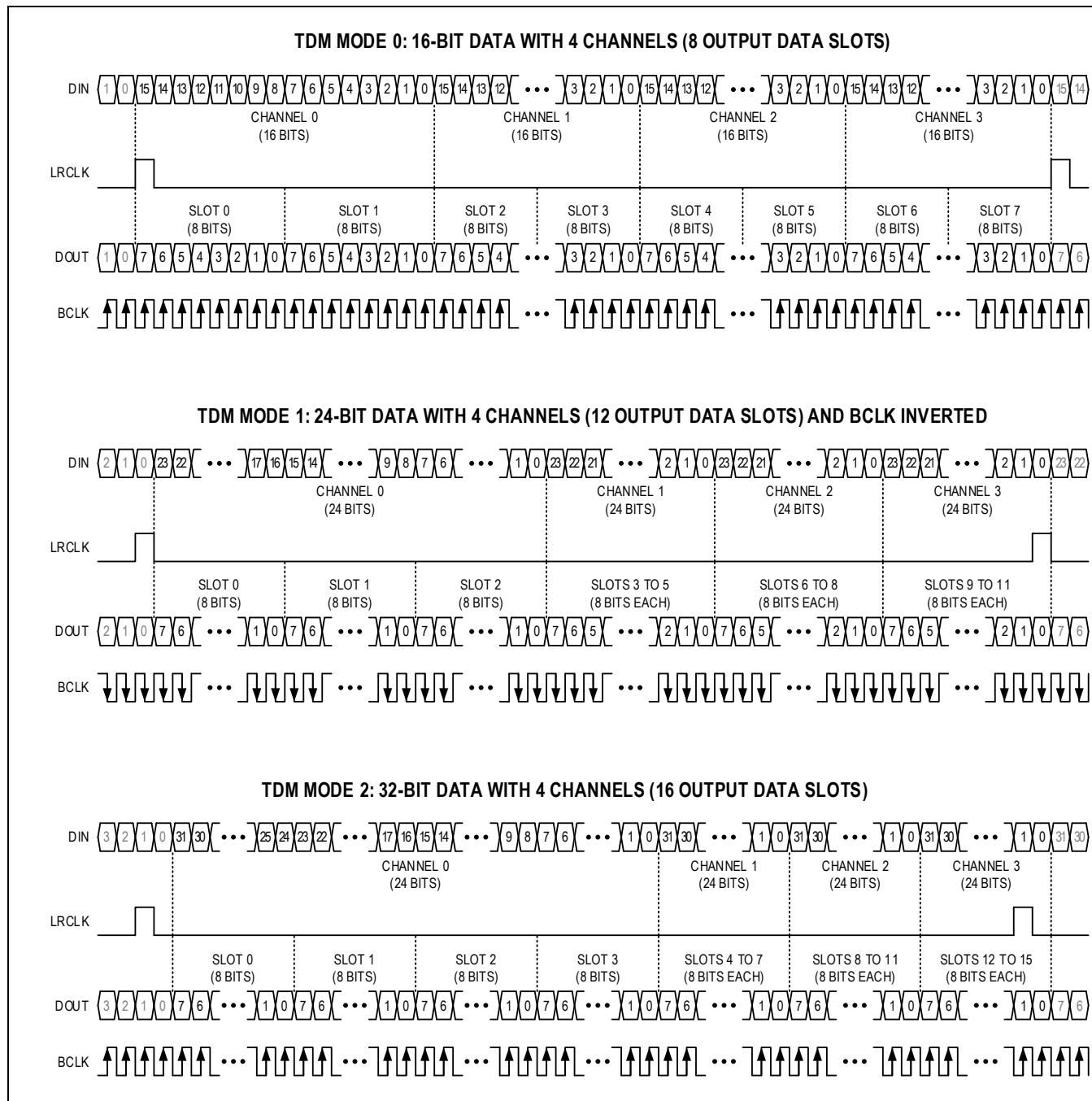

| TDM Modes .....                                            | 37 |

| PCM Data Channel Configuration .....                       | 40 |

| PCM Data Input .....                                       | 40 |

| PCM Data Output .....                                      | 40 |

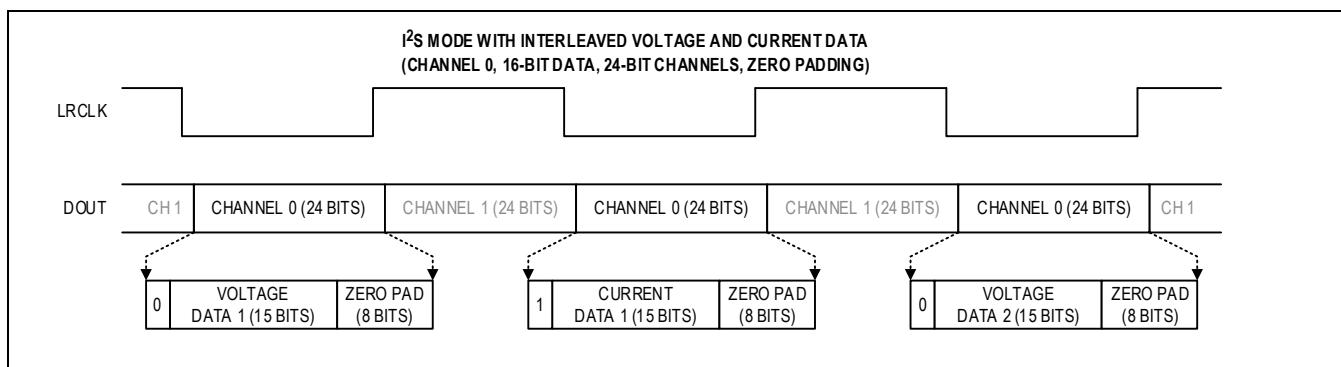

| Data Output Channel-Interleaved I/V Data .....             | 41 |

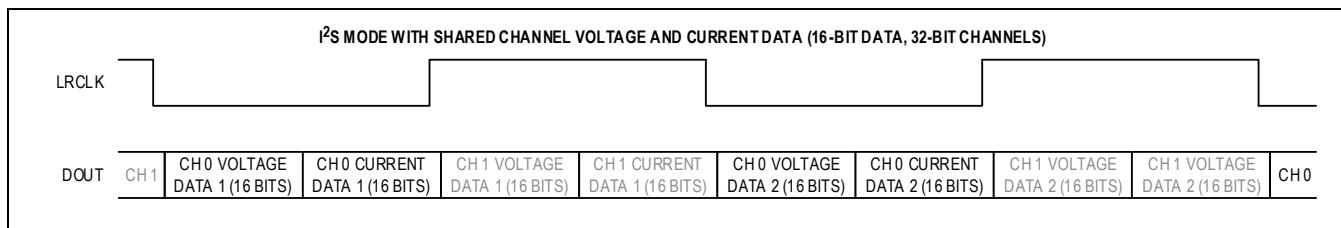

| Data Output Shared Channel I/V Data .....                  | 41 |

| I <sup>2</sup> C Peripheral Serial Control Interface ..... | 42 |

| I <sup>2</sup> C Interface Address .....                   | 42 |

|                                                                          |    |

|--------------------------------------------------------------------------|----|

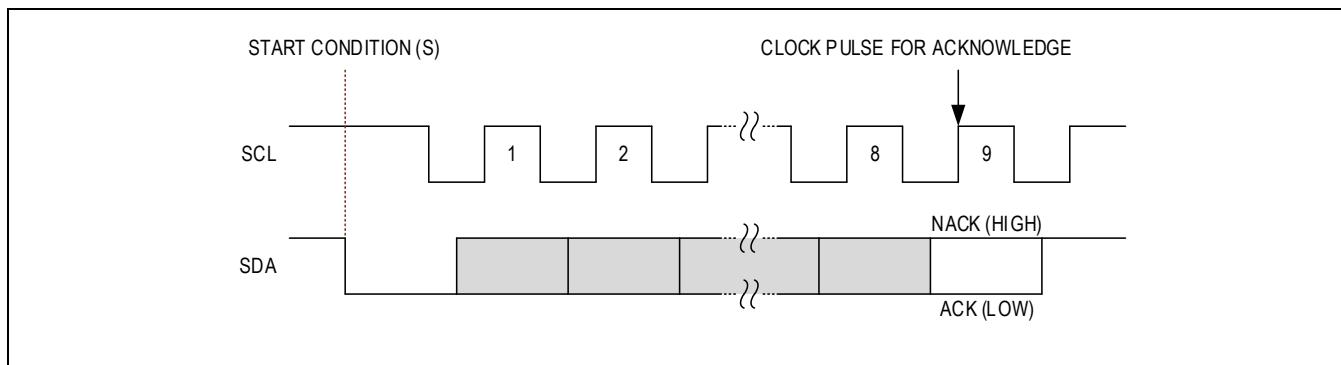

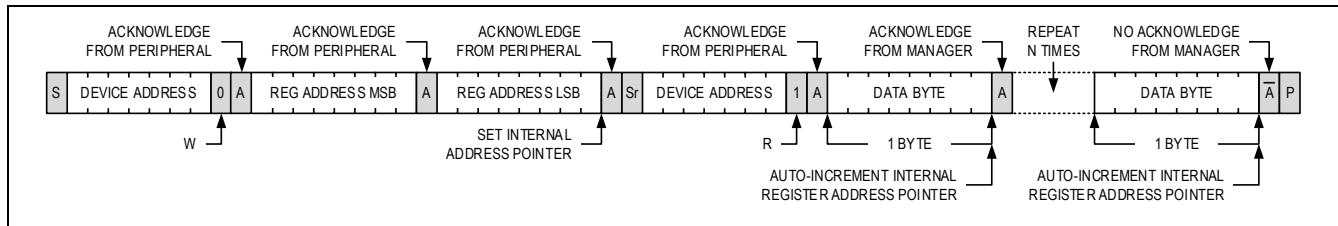

| I <sup>2</sup> C Interface Bit Transfer Protocol .....                   | 42 |

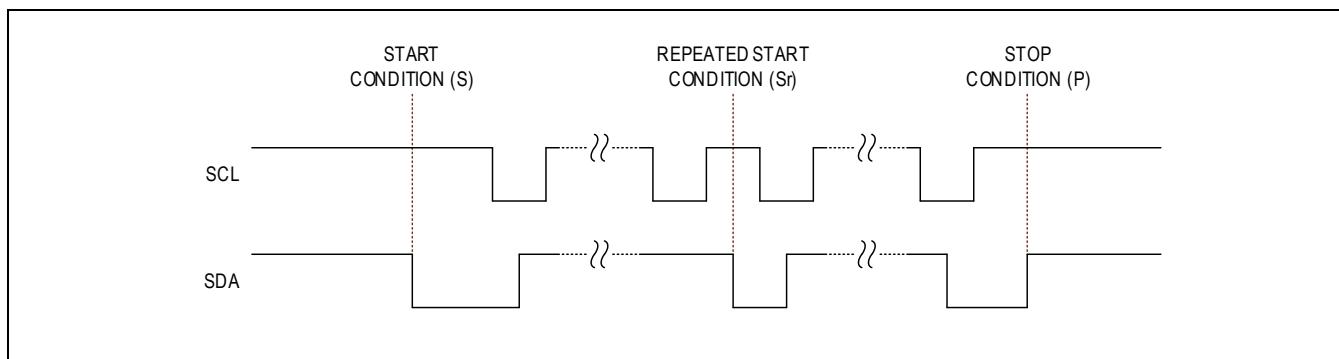

| I <sup>2</sup> C Interface START and STOP Conditions .....               | 42 |

| I <sup>2</sup> C Interface Early STOP Condition .....                    | 43 |

| I <sup>2</sup> C Interface Acknowledge Bit .....                         | 43 |

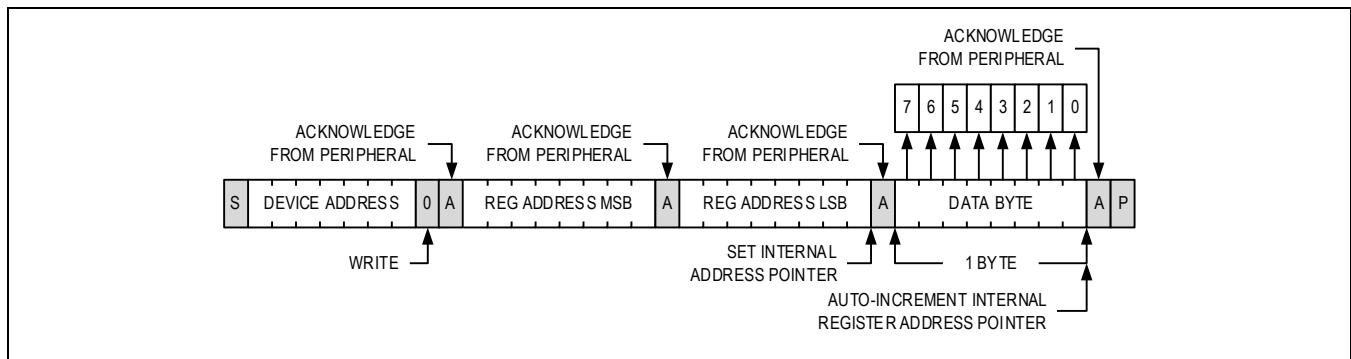

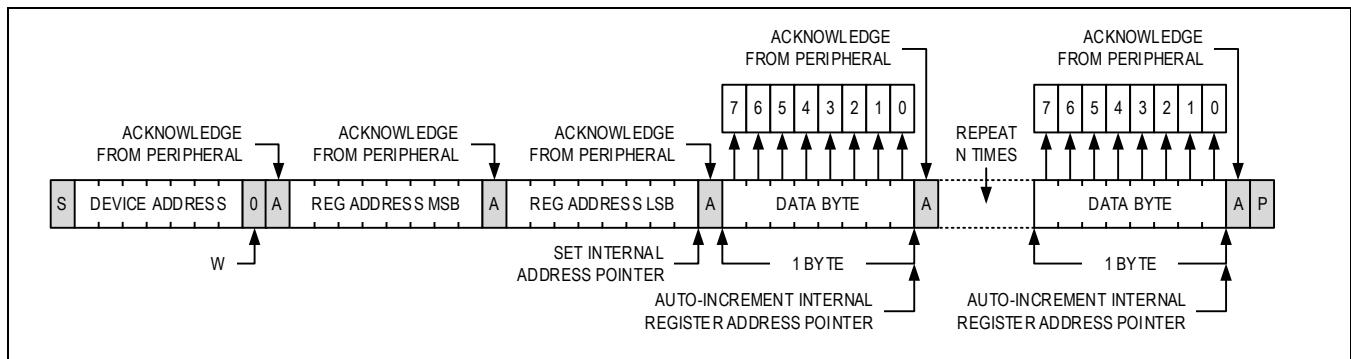

| I <sup>2</sup> C Interface Write Data Format .....                       | 44 |

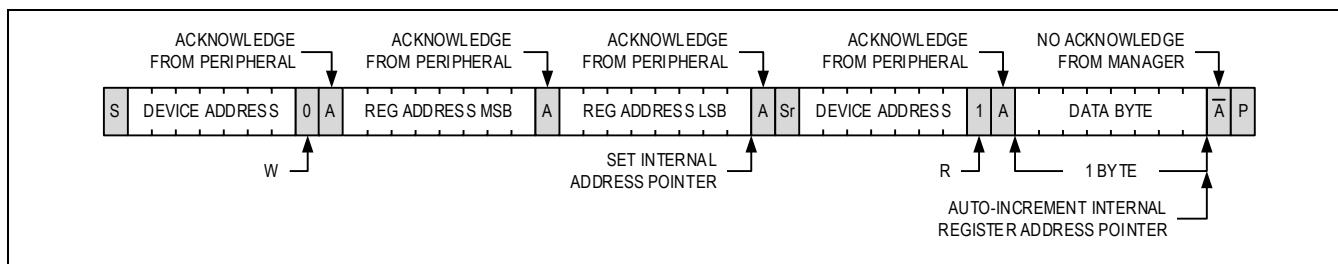

| I <sup>2</sup> C Interface Read Data Format .....                        | 45 |

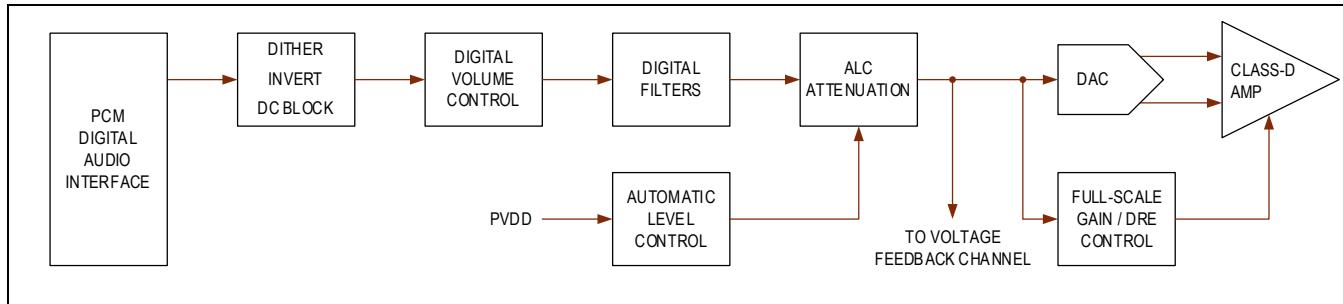

| Speaker Playback Channel .....                                           | 46 |

| Speaker Channel Dither .....                                             | 46 |

| Speaker Channel Data Inversion .....                                     | 46 |

| Speaker Channel DC Blocking Filter .....                                 | 46 |

| Speaker Channel DAC Digital Filters .....                                | 46 |

| Speaker Channel Maximum Peak Output Voltage Scaling .....                | 46 |

| Speaker Channel Digital Volume Control .....                             | 47 |

| Speaker Amplifier .....                                                  | 47 |

| Speaker Amplifier Output Short-Circuit Protection .....                  | 47 |

| Speaker Amplifier Click-and-Pop Suppression .....                        | 47 |

| Speaker Amplifier Ultra-Low EMI Filterless Output .....                  | 47 |

| Speaker Current Sense and Voltage Feedback Channels .....                | 48 |

| Speaker Current Sense and Voltage Feedback Channel Data Format .....     | 48 |

| Clock and Speaker Output Monitors .....                                  | 48 |

| Clock Monitor .....                                                      | 48 |

| Speaker Output Monitor .....                                             | 49 |

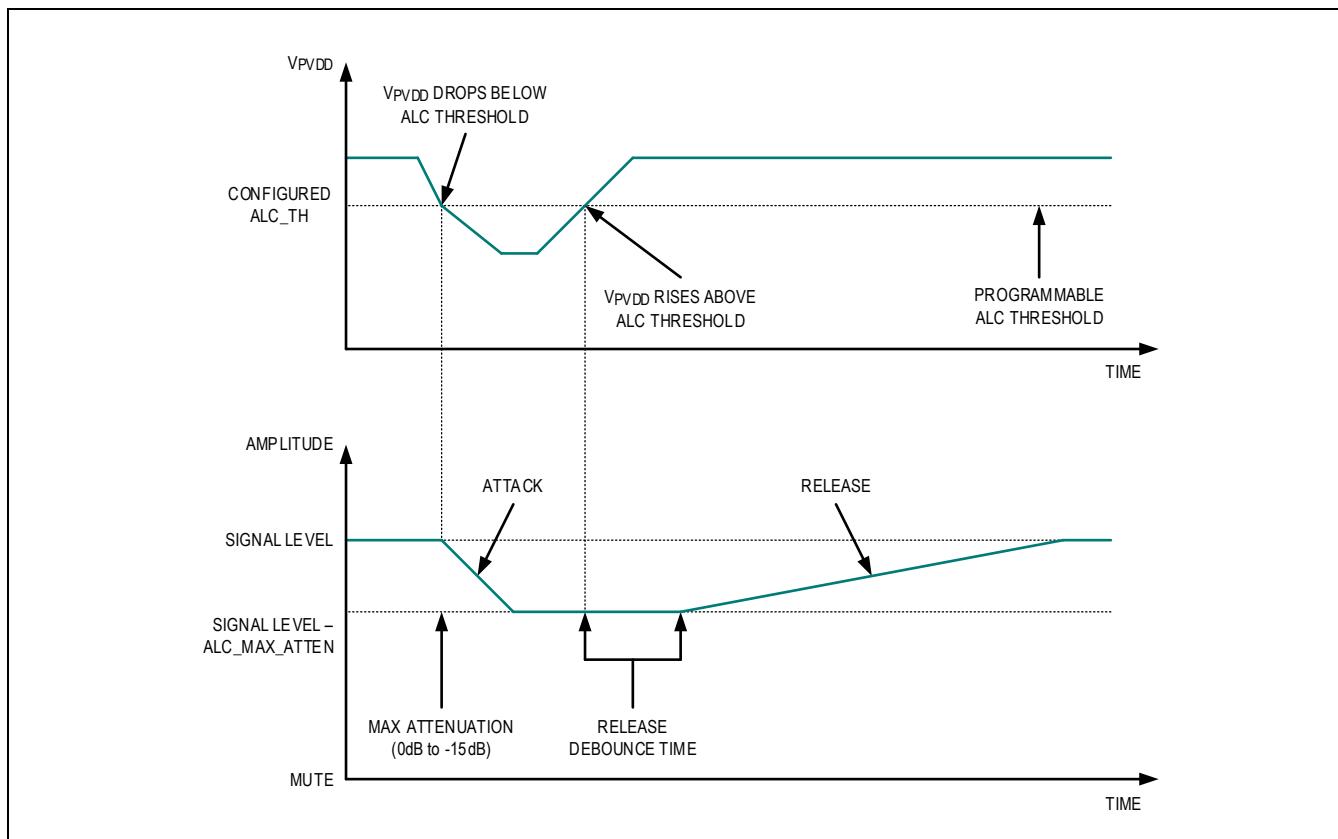

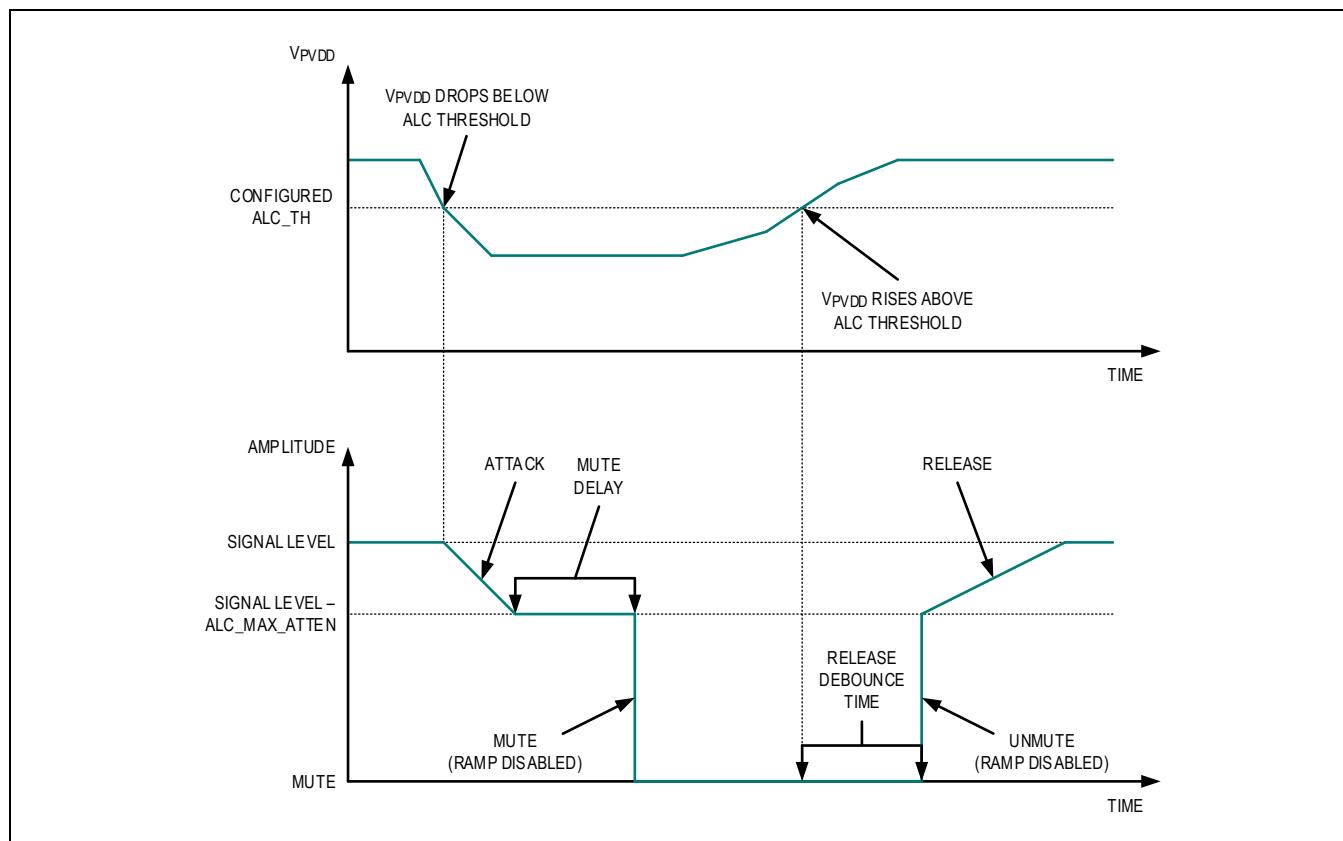

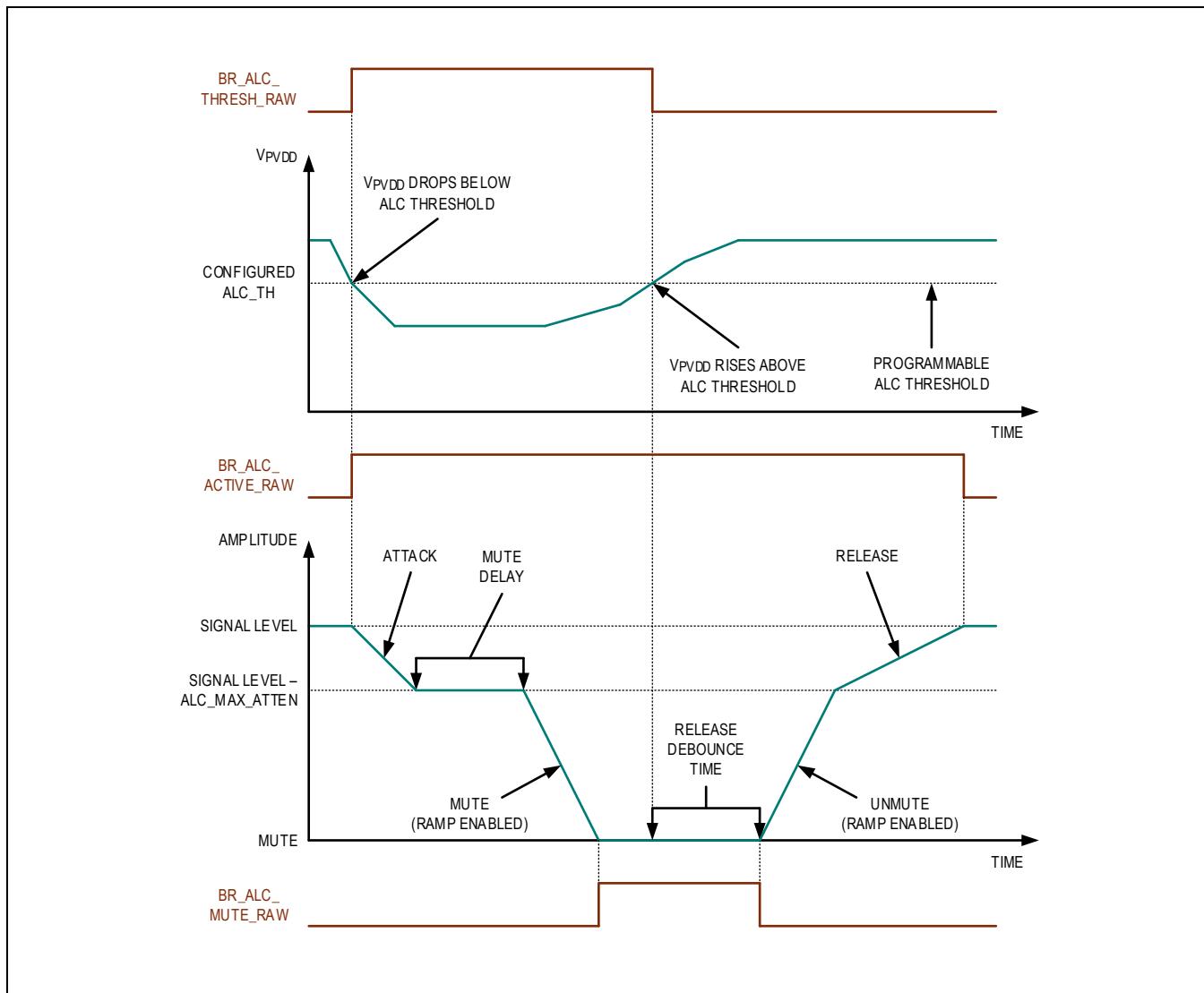

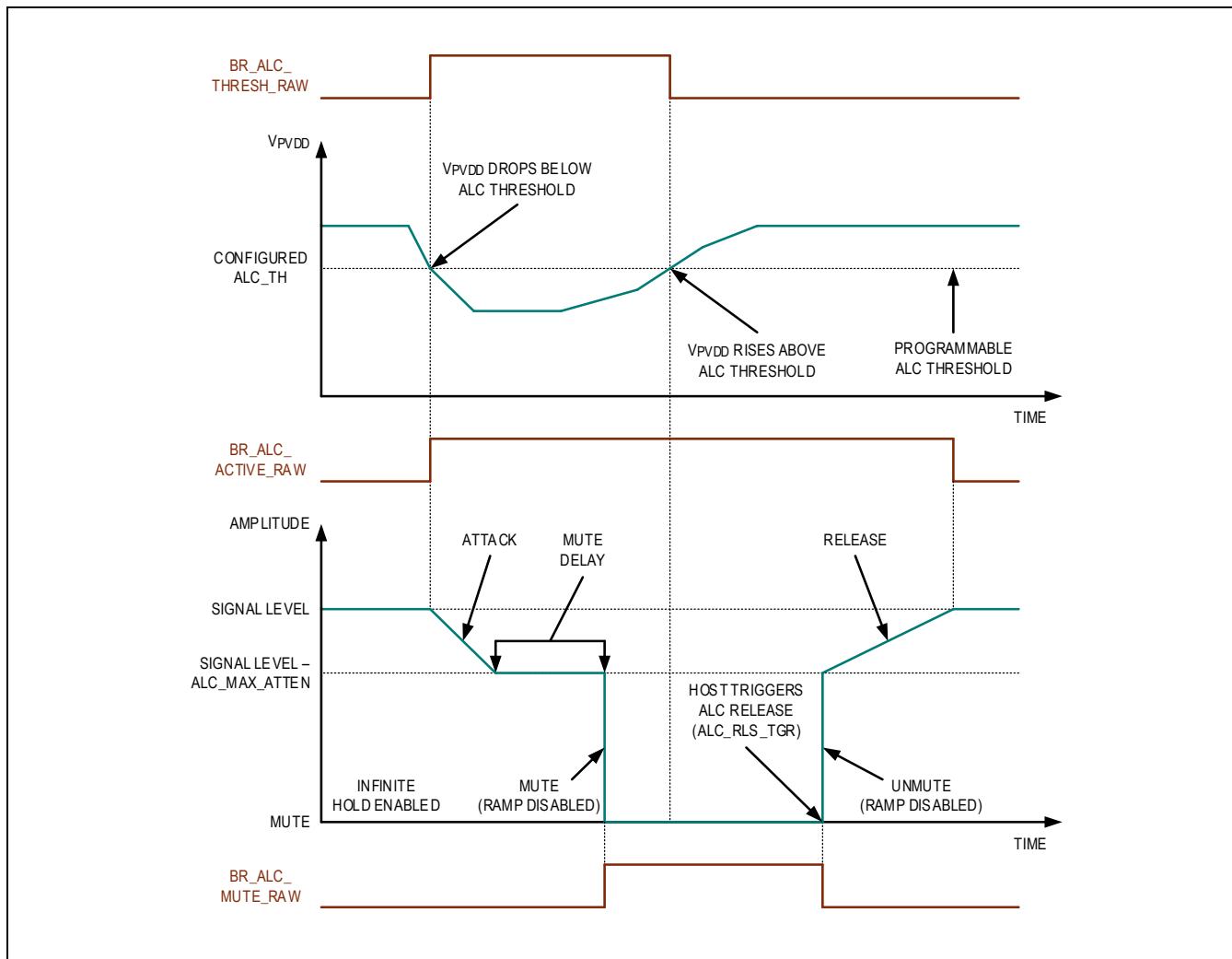

| Brownout Protection Automatic Level Control (ALC) .....                  | 50 |

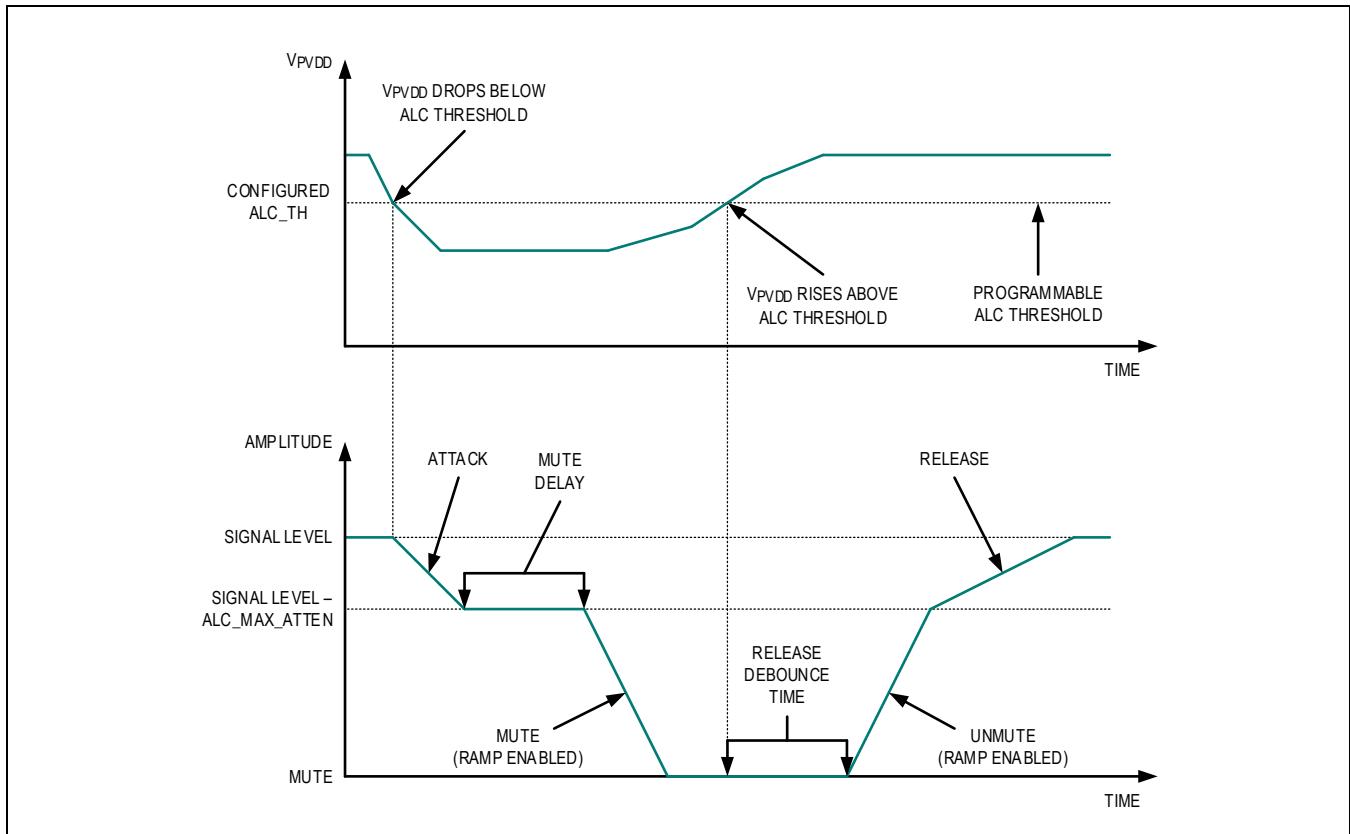

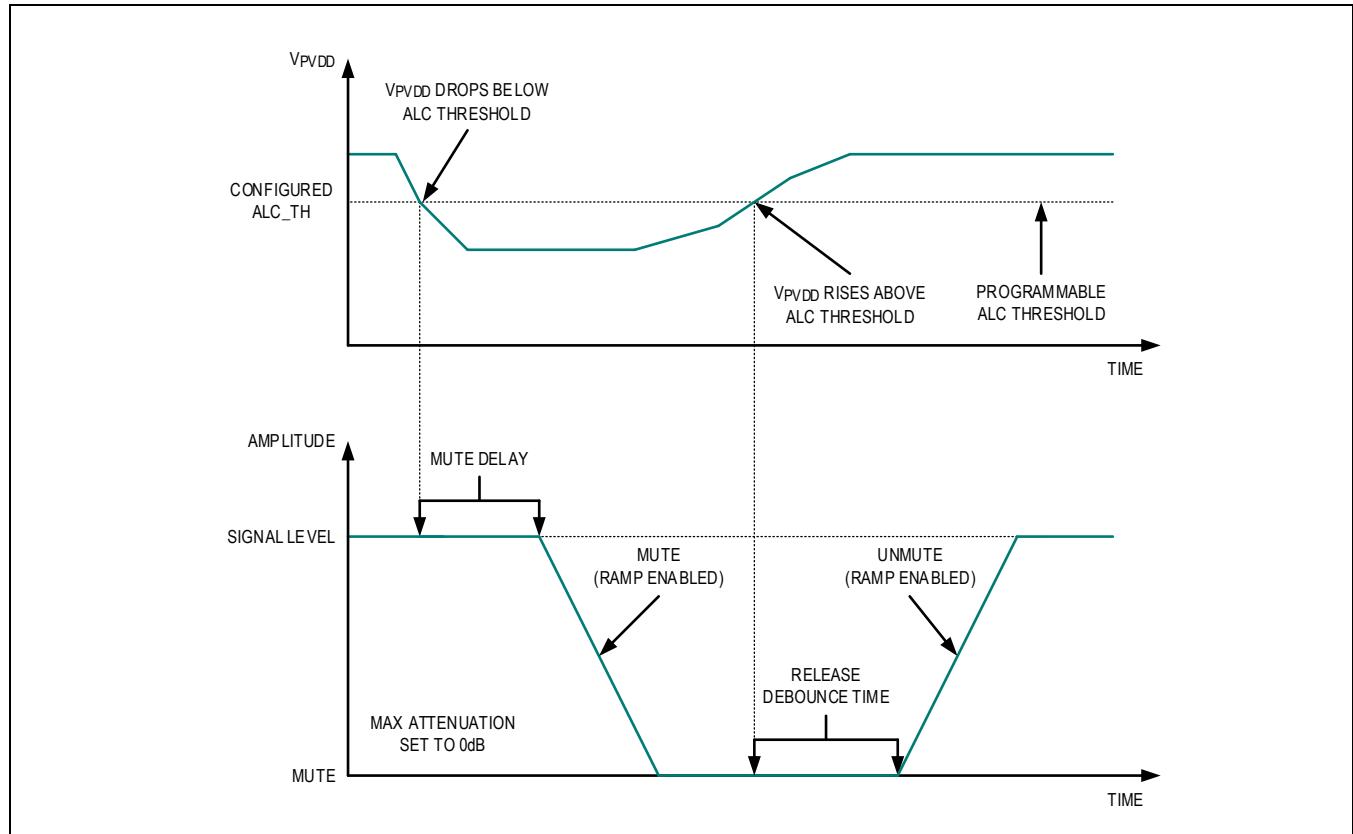

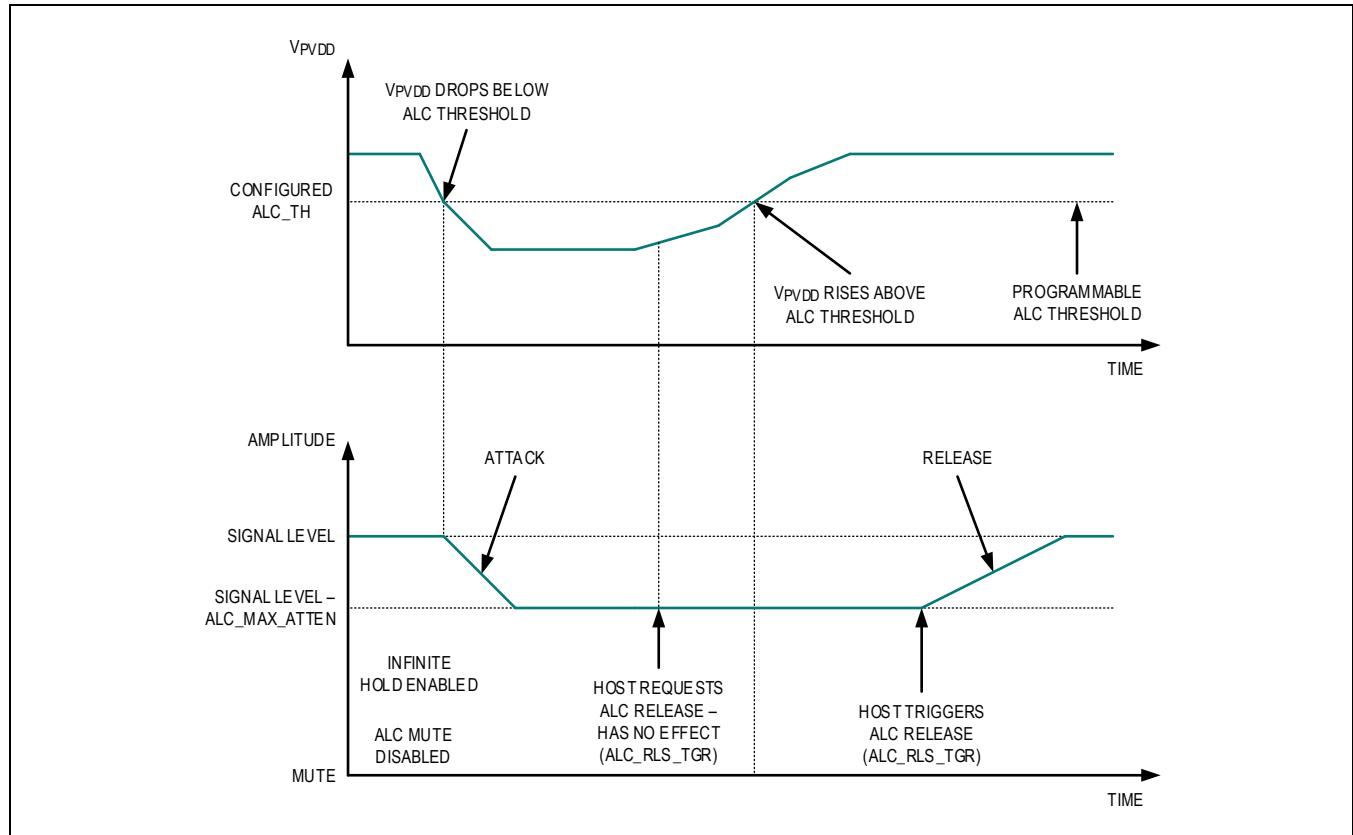

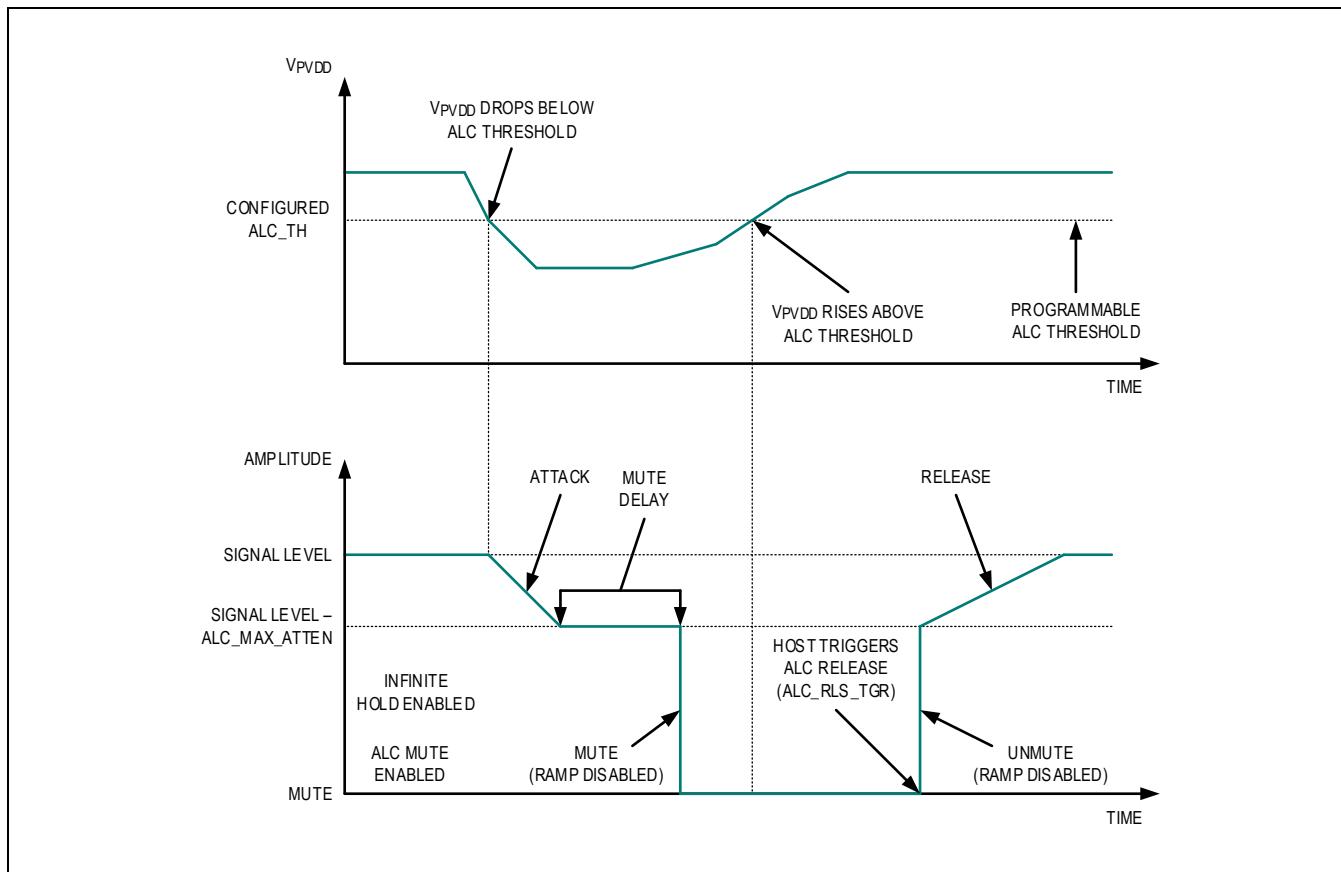

| Brownout Protection ALC Ballistics .....                                 | 50 |

| Brownout Protection ALC Status Reporting .....                           | 55 |

| Thermal Protection .....                                                 | 57 |

| Device Register Map Description .....                                    | 58 |

| Register Default Setting Differences Between MAX98388 and MAX98389 ..... | 58 |

| Control Bit Write Access Restrictions .....                              | 58 |

| Register Map .....                                                       | 59 |

| Typical Application Circuit .....                                        | 89 |

| Ordering Information .....                                               | 89 |

| Chip Information .....                                                   | 89 |

**Absolute Maximum Ratings**

|                                               |                                   |

|-----------------------------------------------|-----------------------------------|

| GND to PGND .....                             | -0.1V to +0.1V                    |

| V <sub>PVDD</sub> to PGND .....               | -0.3V to +12V                     |

| V <sub>DD</sub> to GND .....                  | -0.3V to +2.2V                    |

| OUTP, OUTN to PGND .....                      | -0.3V to V <sub>PVDD</sub> + 0.3V |

| BCLK, LRCLK, DIN, DOUT to GND .....           | -0.3V to V <sub>DD</sub> + 0.3V   |

| ADDR, I.C. to GND .....                       | -0.3V to V <sub>DD</sub> + 0.3V   |

| All Other Pins to GND .....                   | -0.3V to +2.2V                    |

| Duration of short between OUTP and OUTN ..... | Continuous                        |

|                                                                                                       |                 |

|-------------------------------------------------------------------------------------------------------|-----------------|

| Duration of short circuit between OUTP or OUTN and PGND, V <sub>PVDD</sub> , or V <sub>DD</sub> ..... | Continuous      |

| Continuous power dissipation (T <sub>A</sub> = +70°C, derate 13.7mW/°C above +70°C) .....             | 1.38W           |

| Junction temperature .....                                                                            | +150°C          |

| Operating temperature range .....                                                                     | -40°C to +85°C  |

| Storage temperature range .....                                                                       | -65°C to +150°C |

| Soldering temperature (reflow) .....                                                                  | +260°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Package Information****WLP**

|                                                        |                                                |

|--------------------------------------------------------|------------------------------------------------|

| Package Code                                           | W161P1Z+1                                      |

| Outline Number                                         | <a href="#">21-100636</a>                      |

| Land Pattern Number                                    | Refer to <a href="#">Application Note 1891</a> |

| <b>Thermal Resistance, Four Layer Board:</b>           |                                                |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 57.93°C/W                                      |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | N/A                                            |

For the latest package outline information and land patterns (footprints), go to [www.maximintegrated.com/packages](#). Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to [www.maximintegrated.com/thermal-tutorial](#).

**Electrical Characteristics**

( $V_{PVDD} = 5V$  (Single-Cell Mode) or  $7.4V$  (Two-Cell Mode),  $V_{DD} = 1.8V$ ,  $V_{GND} = V_{PGND} = 0V$ ,  $C_{PVDD} = 10\mu F + 0.1\mu F$ ,  $C_{VDD} = 1\mu F$ ,  $f_{BCLK} = 3.072MHz$ ,  $f_{LRCLK} = 48kHz$ ,  $Z_{SPK} = \infty$  between OUTP and OUTN, Single-Cell Mode, AC Measurement Bandwidth = 20Hz to 20kHz,  $T_A = T_{MIN}$  to  $T_{MAX}$ , Typical values are at  $T_A = +25^\circ C$ ) (Note 1)

| PARAMETER                                                      | SYMBOL           | CONDITIONS                                                                                                       |                                      | MIN  | TYP | MAX  | UNITS   |

|----------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------|------|-----|------|---------|

| <b>SYSTEM-LEVEL</b>                                            |                  |                                                                                                                  |                                      |      |     |      |         |

| PVDD Supply Voltage Range                                      | $V_{PVDD}$       | Guaranteed by PSRR test                                                                                          | Two-cell / boosted mode              | 5    | 10  | 10   | V       |

|                                                                |                  |                                                                                                                  | Single-cell mode                     | 3.0  | 5.5 | 5.5  |         |

|                                                                |                  | Guaranteed by PSRR test, single-cell mode, the device is functional but parametric performance is not guaranteed |                                      | 2.3  |     |      |         |

| $V_{DD}$ Supply Voltage Range                                  | $V_{DD}$         | Guaranteed by PSRR test                                                                                          |                                      | 1.71 | 1.8 | 1.89 | V       |

| PVDD Undervoltage Lockout                                      | $V_{UVLO\_PVDD}$ | Single-cell mode                                                                                                 | $V_{PVDD}$ falling                   | 1.9  | 2.2 | 2.2  | V       |

|                                                                |                  | Two-cell mode                                                                                                    | $V_{PVDD}$ falling                   | 4.4  | 4.7 | 4.7  |         |

| PVDD UVLO Hysteresis                                           |                  | Single-cell mode (Note 4)                                                                                        |                                      | 150  | 200 | 200  | mV      |

|                                                                |                  | Two-cell mode (Note 4)                                                                                           |                                      | 120  | 150 | 150  |         |

| $V_{DD}$ Undervoltage Lockout                                  | $V_{UVLO\_VDD}$  | $V_{DD}$ falling                                                                                                 |                                      | 1.3  | 1.6 | 1.6  | V       |

| $V_{DD}$ UVLO Hysteresis                                       |                  | Note 4                                                                                                           |                                      | 20   | 40  | 40   | mV      |

| $V_{DD}$ Supply Ramp Rate                                      |                  |                                                                                                                  |                                      | 0.1  |     |      | V/ms    |

| Thermal Shutdown Temperature                                   |                  | $THERMSHDN\_THRES = 0x2$                                                                                         |                                      |      | 155 | 155  | °C      |

| Thermal Shutdown Hysteresis                                    |                  |                                                                                                                  |                                      |      | 15  | 15   | °C      |

| Thermal Warning Temperature                                    |                  | $THERMWARN\_THRES = 0x2$                                                                                         |                                      |      | 115 | 115  | °C      |

| Thermal Warning Hysteresis                                     |                  |                                                                                                                  |                                      |      | 15  | 15   | °C      |

| <b>POWER CONSUMPTION / QUIESCENT POWER CONSUMPTION</b>         |                  |                                                                                                                  |                                      |      |     |      |         |

| Total Quiescent Power                                          |                  | Both supplies, IV feedback disabled                                                                              | $V_{PVDD} = 3.7V$                    | 9.3  |     |      | mW      |

|                                                                |                  | Both supplies, IV feedback enabled                                                                               | $V_{PVDD} = 3.7V$                    | 13.9 |     |      |         |

|                                                                |                  |                                                                                                                  | $V_{PVDD} = 5V$                      | 16.1 |     |      |         |

|                                                                |                  |                                                                                                                  | $V_{PVDD} = 7.4V$                    | 22.5 |     |      |         |

| PVDD Quiescent Current                                         |                  | IV feedback disabled                                                                                             | $V_{PVDD} = 3.7V$                    | 1.37 |     |      | mA      |

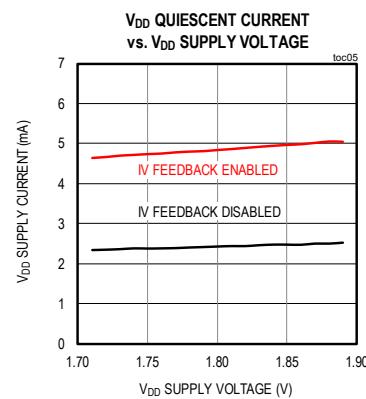

| $V_{DD}$ Quiescent Current                                     |                  | IV feedback disabled                                                                                             |                                      | 2.38 |     |      | mA      |

| PVDD Quiescent Current                                         |                  | IV feedback enabled                                                                                              | $V_{PVDD} = 3.7V$                    | 1.42 | 2   | 2    | mA      |

|                                                                |                  |                                                                                                                  | $V_{PVDD} = 5V$                      | 1.59 | 2.2 | 2.2  |         |

|                                                                |                  |                                                                                                                  | $V_{PVDD} = 7.4V$                    | 1.86 | 2.5 | 2.5  |         |

| $V_{DD}$ Quiescent Current                                     |                  | IV feedback enabled                                                                                              |                                      | 4.83 | 6.8 | 6.8  | mA      |

| <b>POWER CONSUMPTION / SOFTWARE SHUTDOWN POWER CONSUMPTION</b> |                  |                                                                                                                  |                                      |      |     |      |         |

| PVDD Software Shutdown Current                                 | $I_{PVDD\_SWSD}$ | No toggling on PCM interface pins, $T_A = +25^\circ C$                                                           | $V_{PVDD} = 3.7V$ , single-cell mode | 0.3  | 4   | 4    | $\mu A$ |

|                                                                |                  |                                                                                                                  | $V_{PVDD} = 7.4V$ , two-cell mode    | 0.4  | 5   | 5    |         |

( $V_{PVDD} = 5V$  (Single-Cell Mode) or  $7.4V$  (Two-Cell Mode),  $V_{DD} = 1.8V$ ,  $V_{GND} = V_{PGND} = 0V$ ,  $C_{PVDD} = 10\mu F + 0.1\mu F$ ,  $C_{VDD} = 1\mu F$ ,  $f_{BCLK} = 3.072MHz$ ,  $f_{LRCLK} = 48kHz$ ,  $Z_{SPK} = \infty$  between OUTP and OUTN, Single-Cell Mode, AC Measurement Bandwidth = 20Hz to 20kHz,  $T_A = T_{MIN}$  to  $T_{MAX}$ , Typical values are at  $T_A = +25^\circ C$ ) (Note 1)

| PARAMETER                                                                                                              | SYMBOL           | CONDITIONS                                                                                                                                                   | MIN                                            | TYP          | MAX | UNITS   |

|------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------|-----|---------|

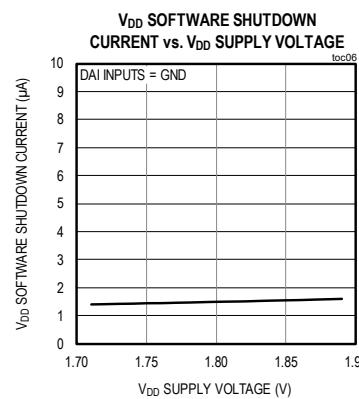

| $V_{DD}$ Software Shutdown Current                                                                                     | $I_{VDD\_SWSD}$  | No toggling on PCM interface pins, $T_A = +25^\circ C$                                                                                                       |                                                | 1.5          | 6   | $\mu A$ |

| <b>POWER CONSUMPTION / HARDWARE SHUTDOWN POWER CONSUMPTION</b>                                                         |                  |                                                                                                                                                              |                                                |              |     |         |

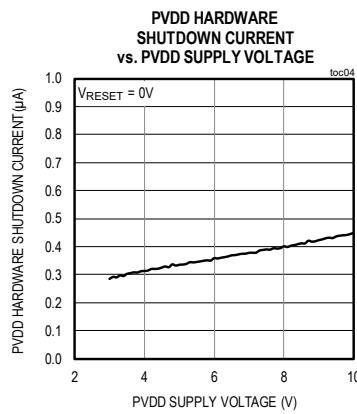

| PVDD Hardware Shutdown Current                                                                                         | $I_{PVDD\_HWSD}$ | $T_A = +25^\circ C$                                                                                                                                          | $V_{PVDD} = 3.7V$ ,<br>single-cell mode        | 0.3          | 4   | $\mu A$ |

|                                                                                                                        |                  |                                                                                                                                                              | $V_{PVDD} = 7.4V$ ,<br>two-cell mode           | 0.4          | 5   |         |

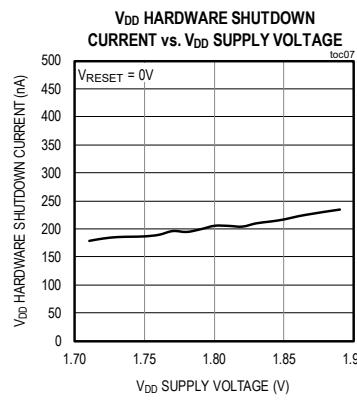

| $V_{DD}$ Hardware Shutdown Current                                                                                     | $I_{VDD\_HWSD}$  | $T_A = +25^\circ C$                                                                                                                                          |                                                | 0.2          | 1   | $\mu A$ |

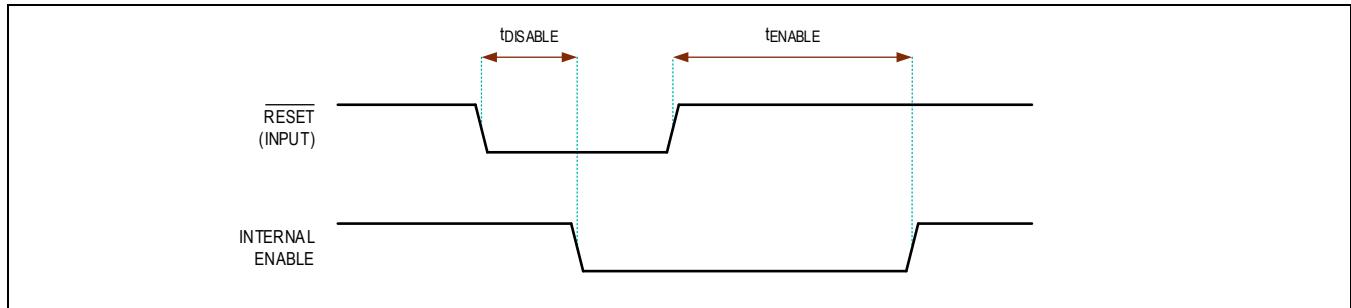

| <b>ENABLE / DISABLE TIMING</b>                                                                                         |                  |                                                                                                                                                              |                                                |              |     |         |

| Turn-On Time                                                                                                           | $t_{ON}$         | Software-shutdown state to active state (device ready to receive audio data)                                                                                 | Volume ramp disabled, $f_S \geq 44.1kHz$       | 0.6          | 1   | ms      |

|                                                                                                                        |                  |                                                                                                                                                              | Volume ramp disabled, $f_S < 44.1kHz$ (Note 4) | 1.1          | 2.3 |         |

|                                                                                                                        |                  |                                                                                                                                                              | Volume ramp enabled, $f_S \geq 44.1kHz$        | 2.3          | 2.7 |         |

|                                                                                                                        |                  |                                                                                                                                                              | Volume ramp enabled, $f_S < 44.1kHz$ (Note 4)  | 2.9          | 4.2 |         |

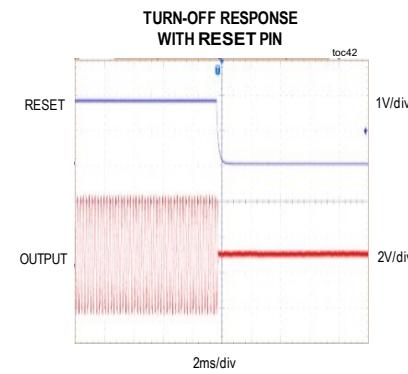

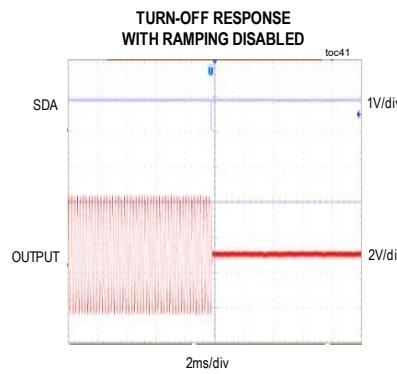

| Turn-Off Time                                                                                                          | $t_{OFF}$        | From full-active state operation to software-shutdown state (power down done status)                                                                         | Volume ramp disabled                           | 70           | 100 | $\mu s$ |

|                                                                                                                        |                  |                                                                                                                                                              | Volume ramp enabled, $f_S \geq 44.1kHz$        | 4.3          | 4.6 | ms      |

|                                                                                                                        |                  |                                                                                                                                                              | Volume ramp enabled, $f_S < 44.1kHz$           | 6.7          | 8   |         |

| Hardware Enable Time                                                                                                   | $t_{HW\_EN}$     | Transition time from the hardware-shutdown state ( $\overline{RESET}$ input set high) to the software-shutdown state ( $I^2C$ ready)                         |                                                | 1.5          |     | ms      |

| Hardware Reset Time                                                                                                    | $t_{HW\_RES}$    | Transition time from software reset (write 1 to the software reset bit) until the device is reset and returns to the software-shutdown state ( $I^2C$ ready) |                                                | 0.4          |     | ms      |

| Hardware Disable Assert Time                                                                                           | $t_{HW\_DIS}$    | Minimum time $\overline{RESET}$ input must be asserted low to ensure the device transitions to the hardware-shutdown state                                   |                                                | 1            |     | $\mu s$ |

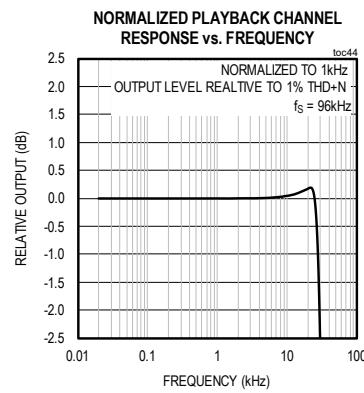

| <b>SPEAKER DIGITAL AUDIO CHANNEL / DAC DIGITAL FILTER CHARACTERISTICS (<math>f_{LRCLK} &lt; 50kHz</math>) (Note 2)</b> |                  |                                                                                                                                                              |                                                |              |     |         |

| Passband Cutoff Frequency                                                                                              | $f_{PLP}$        | Ripple $< \delta_P$                                                                                                                                          | 0.452 x $f_S$                                  |              |     | Hz      |

|                                                                                                                        |                  | Droop $< -3dB$                                                                                                                                               | 0.457 x $f_S$                                  |              |     |         |

| Passband Ripple                                                                                                        | $\delta_P$       | $f_{IN} < f_{PLP}$ , referenced to signal level at 1kHz, digital filter response only                                                                        | -0.1                                           | +0.1         |     | dB      |

| Stopband Cutoff Frequency                                                                                              | $f_{SLP}$        | Attenuation $> \delta_S$                                                                                                                                     |                                                | 0.49 x $f_S$ |     | Hz      |

( $V_{PVDD} = 5V$  (Single-Cell Mode) or  $7.4V$  (Two-Cell Mode),  $V_{DD} = 1.8V$ ,  $V_{GND} = V_{PGND} = 0V$ ,  $C_{PVDD} = 10\mu F + 0.1\mu F$ ,  $C_{VDD} = 1\mu F$ ,  $f_{BCLK} = 3.072MHz$ ,  $f_{LRCLK} = 48kHz$ ,  $Z_{SPK} = \infty$  between OUTP and OUTN, Single-Cell Mode, AC Measurement Bandwidth = 20Hz to 20kHz,  $T_A = T_{MIN}$  to  $T_{MAX}$ , Typical values are at  $T_A = +25^\circ C$ ) (Note 1)

| PARAMETER                                                                                                              | SYMBOL     | CONDITIONS                                                                                                                                   | MIN                                      | TYP               | MAX  | UNITS         |

|------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------|------|---------------|

| Stopband Attenuation                                                                                                   | $\delta_S$ | $f_{IN} > f_{SLP}$                                                                                                                           | 75                                       |                   |      | dB            |

| Group Delay                                                                                                            |            | $f_{IN} = 1kHz$                                                                                                                              |                                          | 5                 |      | samples       |

| <b>SPEAKER DIGITAL AUDIO CHANNEL / DAC DIGITAL FILTER CHARACTERISTICS (<math>f_{LRCLK} \geq 50kHz</math>) (Note 2)</b> |            |                                                                                                                                              |                                          |                   |      |               |

| Passband Cutoff Frequency                                                                                              | $f_{PLP}$  | Ripple $< \delta_P$                                                                                                                          | $0.227 \times f_S$                       |                   |      | Hz            |

|                                                                                                                        |            | Droop $< -3dB$                                                                                                                               | $0.314 \times f_S$                       |                   |      |               |

| Passband Ripple                                                                                                        | $\delta_P$ | $f_{IN} < f_{PLP}$ , referenced to signal level at 1kHz, digital filter response only                                                        | -0.1                                     |                   | +0.1 | dB            |

| Stopband Cutoff Frequency                                                                                              | $f_{SLP}$  | Attenuation $< \delta_S$                                                                                                                     |                                          | $0.49 \times f_S$ |      | Hz            |

| Stopband Attenuation                                                                                                   | $\delta_S$ | $f_{IN} > f_{SLP}$                                                                                                                           | 80                                       |                   |      | dB            |

| Group Delay                                                                                                            |            | $f_{IN} = 1kHz$                                                                                                                              |                                          | 5.5               |      | samples       |

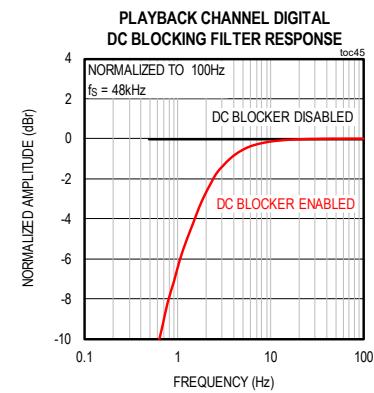

| <b>SPEAKER DIGITAL AUDIO CHANNEL / DC BLOCKING DIGITAL FILTER CHARACTERISTICS (Note 2)</b>                             |            |                                                                                                                                              |                                          |                   |      |               |

| DC Attenuation                                                                                                         |            |                                                                                                                                              | 80                                       |                   |      | dB            |

| DC Blocking Filter -3dB Cutoff Frequency                                                                               | $f_C$      | $f_S = 8kHz, 16kHz, 32kHz, 48kHz$ , and $96kHz$                                                                                              |                                          | 1.872             |      | Hz            |

|                                                                                                                        |            | $f_S = 44.1kHz, 88.2kHz$                                                                                                                     |                                          | 1.72              |      |               |

| <b>SPEAKER CLASS-D AMPLIFIER</b>                                                                                       |            |                                                                                                                                              |                                          |                   |      |               |

| Output Offset Voltage                                                                                                  | $V_{OS}$   | $T_A = +25^\circ C$                                                                                                                          | -3                                       | $\pm 0.3$         | +3   | mV            |

| Click-and-Pop Level                                                                                                    | $K_{CP}$   | Peak voltage, A-weighted, 32 samples per second, digital silence used for input signal, $Z_{SPK} = 8\Omega + 33\mu H$ or $4\Omega + 33\mu H$ | Amp output power down, single-cell mode  | -77               |      | dBV           |

|                                                                                                                        |            |                                                                                                                                              | Amp output power down, two-cell mode     | -71               |      |               |

|                                                                                                                        |            |                                                                                                                                              | Amp output power-up, single-cell mode    | -76               |      |               |

|                                                                                                                        |            |                                                                                                                                              | Amp output power-up, two-cell mode       | -70               |      |               |

| Output Noise                                                                                                           | $e_N$      | A-weighted, 24-bit, or 32-bit data                                                                                                           | Single-cell mode, DAC low-power mode     | 10                |      | $\mu V_{RMS}$ |

|                                                                                                                        |            |                                                                                                                                              | Two-cell mode, DAC high-performance mode | 14.5              |      |               |

| Dynamic Range                                                                                                          | $DR$       | A-weighted, 24-bit or 32-bit data, single-cell mode, DAC low power mode (Note 3)                                                             | $Z_{SPK} = 4\Omega + 33\mu H$            | 110               |      | dB            |

|                                                                                                                        |            |                                                                                                                                              | $Z_{SPK} = 8\Omega + 33\mu H$            | 110.5             |      |               |

|                                                                                                                        |            | A-weighted, 24-bit or 32-bit data, two-cell mode, $V_{PVDD} = 7.4V$ , DAC high-performance mode (Note 3)                                     | $Z_{SPK} = 8\Omega + 33\mu H$            | 111               |      |               |

( $V_{PVDD} = 5V$  (Single-Cell Mode) or  $7.4V$  (Two-Cell Mode),  $V_{DD} = 1.8V$ ,  $V_{GND} = V_{PGND} = 0V$ ,  $C_{PVDD} = 10\mu F + 0.1\mu F$ ,  $C_{VDD} = 1\mu F$ ,  $f_{BCLK} = 3.072MHz$ ,  $f_{LRCLK} = 48kHz$ ,  $Z_{SPK} = \infty$  between OUTP and OUTN, Single-Cell Mode, AC Measurement Bandwidth = 20Hz to 20kHz,  $T_A = T_{MIN}$  to  $T_{MAX}$ , Typical values are at  $T_A = +25^\circ C$ ) (Note 1)

| PARAMETER                         | SYMBOL    | CONDITIONS                                                                                                                           | MIN                                              | TYP  | MAX | UNITS |

|-----------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------|-----|-------|

| Total Harmonic Distortion + Noise | THD+N     | $f_{IN} = 1kHz$ , $T_A = +25^\circ C$ , single-cell mode, $V_{PVDD} = 5V$                                                            | $P_{OUT} = 1W$ , $Z_{SPK} = 4\Omega + 33\mu H$   |      | -87 | dB    |

|                                   |           |                                                                                                                                      | $P_{OUT} = 0.7W$ , $Z_{SPK} = 8\Omega + 33\mu H$ |      | -85 |       |

|                                   |           | $f_{IN} = 1kHz$ , $T_A = +25^\circ C$ , two-cell mode, $V_{PVDD} = 7.4V$ , $P_{OUT} = 1.4W$ , $Z_{SPK} = 8\Omega + 33\mu H$ (Note 4) |                                                  | -83  | -74 |       |

| Full-Scale Output Voltage         | FS        | Single-cell mode, +12dB gain                                                                                                         |                                                  | 12.4 |     | dBV   |

|                                   |           | Two-cell mode, +18dB gain                                                                                                            |                                                  | 18.4 |     |       |

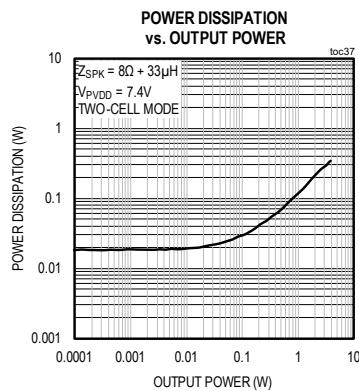

| Efficiency                        | $\eta$    | $f_{IN} = 1kHz$ , $Z_{SPK} = 8\Omega + 33\mu H$ , $V_{PVDD} = 5V$                                                                    | THD+N = 10%                                      | 92   |     | %     |

|                                   |           |                                                                                                                                      | $P_{OUT} = 1W$                                   | 90   |     |       |

|                                   |           |                                                                                                                                      | $P_{OUT} = 0.1W$                                 | 80   |     |       |

|                                   |           |                                                                                                                                      | $P_{OUT} = 0.05W$                                | 72   |     |       |

|                                   |           | $f_{IN} = 1kHz$ , $Z_{SPK} = 4\Omega + 33\mu H$ , $V_{PVDD} = 5V$                                                                    | $P_{OUT} = 1W$                                   | 85.5 |     |       |

|                                   |           |                                                                                                                                      | $P_{OUT} = 0.1W$                                 | 76   |     |       |

|                                   |           |                                                                                                                                      | $P_{OUT} = 0.05W$                                | 69   |     |       |

|                                   |           |                                                                                                                                      |                                                  |      |     |       |

| Output Power                      | $P_{OUT}$ | $f_{IN} = 1kHz$ , THD+N $\leq 1\%$ , $Z_{SPK} = 4\Omega + 33\mu H$                                                                   | $V_{PVDD} = 3.7V$ , single-cell mode             | 1.32 |     | W     |

|                                   |           |                                                                                                                                      | $V_{PVDD} = 5V$ , single-cell mode               | 2.4  |     |       |

|                                   |           |                                                                                                                                      | $V_{PVDD} = 7.4V$ , two-cell mode                | 5.15 |     |       |

|                                   |           |                                                                                                                                      | $V_{PVDD} = 8.4V$ , two-cell mode                | 6.54 |     |       |

|                                   |           | $f_{IN} = 1kHz$ , THD+N $\leq 10\%$ , $Z_{SPK} = 4\Omega + 33\mu H$                                                                  | $V_{PVDD} = 3.7V$ , single-cell mode             | 1.65 |     |       |

|                                   |           |                                                                                                                                      | $V_{PVDD} = 5V$ , single-cell mode               | 3.0  |     |       |

|                                   |           |                                                                                                                                      | $V_{PVDD} = 7.4V$ , two-cell mode                | 6.35 |     |       |

|                                   |           |                                                                                                                                      | $V_{PVDD} = 8.4V$ , two-cell mode                | 8.02 |     |       |

|                                   |           | $f_{IN} = 1kHz$ , THD+N $\leq 1\%$ , $Z_{SPK} = 8\Omega + 33\mu H$                                                                   | $V_{PVDD} = 3.7V$ , single-cell mode             | 0.77 |     |       |

|                                   |           |                                                                                                                                      | $V_{PVDD} = 5V$ , single-cell mode               | 1.4  |     |       |

|                                   |           |                                                                                                                                      | $V_{PVDD} = 7.4V$ , two-cell mode                | 3.05 |     |       |

|                                   |           |                                                                                                                                      | $V_{PVDD} = 8.4V$ , two-cell mode                | 3.87 |     |       |

|                                   |           | $f_{IN} = 1kHz$ , THD+N $\leq 10\%$ , $Z_{SPK} = 8\Omega + 33\mu H$                                                                  | $V_{PVDD} = 3.7V$ , single-cell mode             | 0.95 |     |       |

|                                   |           |                                                                                                                                      | $V_{PVDD} = 5V$ , single-cell mode               | 1.72 |     |       |

|                                   |           |                                                                                                                                      | $V_{PVDD} = 7.4V$ , two-cell mode                | 3.75 |     |       |

( $V_{PVDD} = 5V$  (Single-Cell Mode) or  $7.4V$  (Two-Cell Mode),  $V_{DD} = 1.8V$ ,  $V_{GND} = V_{PGND} = 0V$ ,  $C_{PVDD} = 10\mu F + 0.1\mu F$ ,  $C_{VDD} = 1\mu F$ ,  $f_{BCLK} = 3.072MHz$ ,  $f_{LRCLK} = 48kHz$ ,  $Z_{SPK} = \infty$  between OUTP and OUTN, Single-Cell Mode, AC Measurement Bandwidth = 20Hz to 20kHz,  $T_A = T_{MIN}$  to  $T_{MAX}$ , Typical values are at  $T_A = +25^\circ C$ ) (Note 1)

| PARAMETER                                               | SYMBOL    | CONDITIONS                                                                                                     | MIN   | TYP      | MAX   | UNITS    |

|---------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------|-------|----------|-------|----------|

|                                                         |           | $V_{PVDD} = 8.4V$ ,<br>two-cell mode                                                                           |       | 4.84     |       |          |

| Class-D Switching Frequency                             | $f_{SW}$  |                                                                                                                | 285   | 300      | 315   | kHz      |

| Spread-Spectrum Bandwidth                               | $f_{SSM}$ |                                                                                                                |       | $\pm 14$ |       | kHz      |

| Intermodulation Distortion                              | IMD       | ITU-R, 19kHz/ 20kHz, 1:1,<br>$V_{IN} = -3dBFS$ , $Z_{SPK} = 8\Omega + 33\mu H$                                 |       | -70      |       | dB       |

| Frequency Response                                      |           | Full response from digital audio interface input to the amplifier output                                       | -0.25 |          | +0.25 | dB       |

| Output Stage On-Resistance                              | $R_{ON}$  | PMOS + NMOS (Full H-Bridge),<br>$T_A = +25^\circ C$                                                            |       | 0.38     |       | $\Omega$ |

| Output Current Limit                                    | $I_{LIM}$ |                                                                                                                | 3.5   |          |       | A        |

| Output Current Limit Auto-Restart Time                  |           |                                                                                                                |       | 20       |       | ms       |

| Minimum Load Resistance                                 | $R_L$     | Nominal $4\Omega$ load minus 25%                                                                               |       | 3        |       | $\Omega$ |

| Maximum Device-to-Device Speaker Channel Phase Mismatch |           | Output phase shift between multiple devices from 20Hz to 20kHz across all sample rates and DAI operating modes |       | 1.5      |       | deg      |

| Minimum Load Inductance                                 |           | In series with a $4\Omega$ load                                                                                |       | 0        |       | $\mu H$  |

| Maximum Load Inductance                                 |           | In series with a $4\Omega$ load                                                                                |       | 100      |       | $\mu H$  |

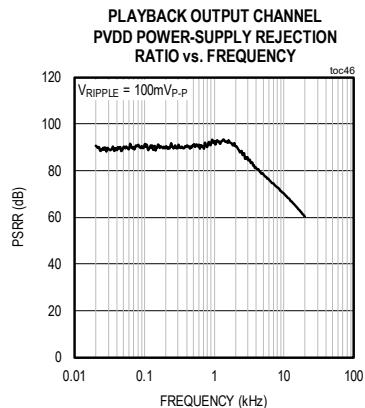

#### SPEAKER CLASS-D AMPLIFIER / POWER-SUPPLY REJECTION

|                                                 |      |                                                                                                                                                  |                      |    |  |    |

|-------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----|--|----|

| PVDD DC Power Supply Rejection Ratio            | PSRR | DC level,<br>$V_{PVDD} = 2.3V$ to $10V$ , $T_A = +25^\circ C$ , digital silence used for input signal, $Z_{SPK} = \infty$                        | 70                   | 85 |  | dB |

| PVDD AC Power Supply Rejection Ratio            | PSRR | $V_{RIPPLE} = 200mV_{PP}$ ,<br>$T_A = +25^\circ C$ , digital silence used for input signal, $Z_{SPK} = 8\Omega + 33\mu H$ or $4\Omega + 33\mu H$ | $f_{RIPPLE} = 217Hz$ | 85 |  | dB |

|                                                 |      |                                                                                                                                                  | $f_{RIPPLE} = 1kHz$  | 85 |  |    |

|                                                 |      |                                                                                                                                                  | $f_{RIPPLE} = 10kHz$ | 70 |  |    |

| V <sub>DD</sub> DC Power Supply Rejection Ratio | PSRR | DC level, $V_{DD} = 1.71V$ to $1.89V$ ,<br>$T_A = +25^\circ C$ , digital silence used for input signal, $Z_{SPK} = \infty$                       | 70                   | 85 |  | dB |

| V <sub>DD</sub> AC Power Supply Rejection Ratio | PSRR | $V_{RIPPLE} = 100mV_{PP}$ ,<br>$T_A = +25^\circ C$ , digital silence used for input signal, $Z_{SPK} = 8\Omega + 33\mu H$ or $4\Omega + 33\mu H$ | $f_{RIPPLE} = 217Hz$ | 90 |  | dB |

|                                                 |      |                                                                                                                                                  | $f_{RIPPLE} = 1kHz$  | 90 |  |    |

|                                                 |      |                                                                                                                                                  | $f_{RIPPLE} = 10kHz$ | 80 |  |    |

#### SPEAKER CLASS-D AMPLIFIER / POWER-SUPPLY INTERMODULATION

|                              |  |  |                                        |     |  |    |

|------------------------------|--|--|----------------------------------------|-----|--|----|

| Power-Supply Intermodulation |  |  | PVDD supply,<br>$f_{RIPPLE} = 217Hz$ , | -80 |  | dB |

|------------------------------|--|--|----------------------------------------|-----|--|----|

( $V_{PVDD} = 5V$  (Single-Cell Mode) or  $7.4V$  (Two-Cell Mode),  $V_{DD} = 1.8V$ ,  $V_{GND} = V_{PGND} = 0V$ ,  $C_{PVDD} = 10\mu F + 0.1\mu F$ ,  $C_{VDD} = 1\mu F$ ,  $f_{BCLK} = 3.072MHz$ ,  $f_{LRCLK} = 48kHz$ ,  $Z_{SPK} = \infty$  between OUTP and OUTN, Single-Cell Mode, AC Measurement Bandwidth = 20Hz to 20kHz,  $T_A = T_{MIN}$  to  $T_{MAX}$ , Typical values are at  $T_A = +25^\circ C$ ) (Note 1)

| PARAMETER                                                                                                      | SYMBOL        | CONDITIONS                                                                                                                   | MIN                       | TYP       | MAX    | UNITS   |

|----------------------------------------------------------------------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------|--------|---------|

|                                                                                                                |               | $T_A = +25^\circ C$ ,<br>$f_{IN} = 1kHz$ ,<br>$P_{OUT} = 400mW$ ,<br>$Z_{SPK} = 8\Omega + 33\mu H$<br>or $4\Omega + 33\mu H$ | $V_{RIPPLE} = 200mV_{PP}$ |           |        |         |

| <b>SPEAKER OUTPUT VOLTAGE FEEDBACK (Note 2)</b>                                                                |               |                                                                                                                              |                           |           |        |         |

| Resolution                                                                                                     |               |                                                                                                                              | 16                        |           |        | Bits    |

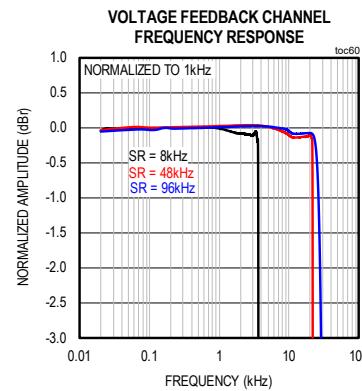

| Sample Rate                                                                                                    | $f_{S\_VFB}$  |                                                                                                                              | 8                         | 96        |        | kHz     |

| Voltage Range                                                                                                  | $V_{SPK}$     | Single-cell mode                                                                                                             |                           | $\pm 5.5$ |        | V       |

|                                                                                                                |               | Two-cell mode                                                                                                                |                           | $\pm 11$  |        |         |

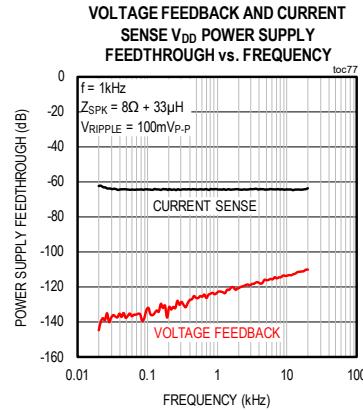

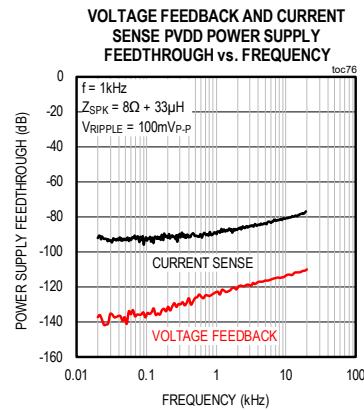

| Power Supply Feedthrough                                                                                       | $PSF$         | No input signal, AC relative to PVDD or $V_{DD}$ , $f_{RIPPLE} = 1kHz$ , $V_{RIPPLE} = 100mV_{PP}$                           |                           | -100      |        | dB      |

| Max Device to Device Voltage Feedback Channel Phase Mismatch                                                   |               | $f_{IN} = 1kHz$                                                                                                              |                           | 0.05      |        | Samples |

| <b>SPEAKER OUTPUT VOLTAGE FEEDBACK / DIGITAL FILTER CHARACTERISTICS (<math>f_S &lt; 50kHz</math>) (Note 2)</b> |               |                                                                                                                              |                           |           |        |         |

| Passband Ripple                                                                                                |               | $f_{IN} < f_{PLP}$ , referenced to the signal level at 1kHz                                                                  | -0.225                    |           | +0.225 | dB      |

| Lowpass Filter Cutoff Frequency                                                                                | $f_{PLP}$     | Ripple $< \delta_P$                                                                                                          | 0.44                      |           |        | Hz      |

|                                                                                                                |               | Droop $< -3dB$                                                                                                               | 0.45                      |           |        |         |

| Lowpass Filter Stopband Frequency                                                                              | $f_{SLP}$     | -40dB limit                                                                                                                  |                           | 0.58      |        | Hz      |

| Lowpass Filter Stopband Attenuation                                                                            |               |                                                                                                                              | 40                        |           |        | dB      |

| Group Delay                                                                                                    |               | $f_{IN} = 1kHz$                                                                                                              |                           | 8         |        | Samples |

| <b>SPEAKER OUTPUT VOLTAGE FEEDBACK / DIGITAL FILTER CHARACTERISTICS (<math>f_S \geq 50kHz</math>) (Note 2)</b> |               |                                                                                                                              |                           |           |        |         |

| Passband Ripple                                                                                                |               | $f_{IN} \leq f_{PLP}$ , referenced to the signal level at 1kHz                                                               | -0.225                    |           | +0.225 | dB      |

| Lowpass Filter Cutoff Frequency                                                                                | $f_{PLP}$     | Ripple $< \delta_P$ , $88.2kHz \leq f_S \leq 96kHz$                                                                          | 0.235                     |           |        | Hz      |

|                                                                                                                |               | Droop $< -3dB$ , $88.2kHz \leq f_S \leq 96kHz$                                                                               | 0.29                      |           |        |         |

| Lowpass Filter Stopband Frequency                                                                              | $f_{SLP}$     | -40dB limit                                                                                                                  |                           | 0.58      |        | Hz      |

| Lowpass Filter Stopband Attenuation                                                                            |               |                                                                                                                              | 40                        |           |        | dB      |

| Group Delay                                                                                                    |               | $f_{IN} = 1kHz$                                                                                                              |                           | 9         |        | Samples |

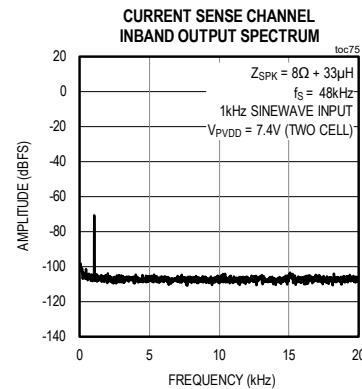

| <b>SPEAKER OUTPUT CURRENT SENSE ADC (Note 2)</b>                                                               |               |                                                                                                                              |                           |           |        |         |

| Resolution                                                                                                     |               |                                                                                                                              | 16                        |           |        | Bits    |

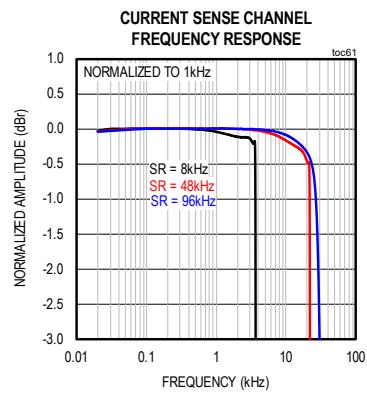

| Sample Rate                                                                                                    | $f_{S\_ISNS}$ |                                                                                                                              | 8                         | 96        |        | kHz     |

| Current Range                                                                                                  | $I_{SPK}$     |                                                                                                                              |                           | $\pm 3$   |        | A       |

( $V_{PVDD} = 5V$  (Single-Cell Mode) or  $7.4V$  (Two-Cell Mode),  $V_{DD} = 1.8V$ ,  $V_{GND} = V_{PGND} = 0V$ ,  $C_{PVDD} = 10\mu F + 0.1\mu F$ ,  $C_{VDD} = 1\mu F$ ,  $f_{BCLK} = 3.072MHz$ ,  $f_{LRCLK} = 48kHz$ ,  $Z_{SPK} = \infty$  between OUTP and OUTN, Single-Cell Mode, AC Measurement Bandwidth = 20Hz to 20kHz,  $T_A = T_{MIN}$  to  $T_{MAX}$ , Typical values are at  $T_A = +25^\circ C$ ) (Note 1)

| PARAMETER                                                                                                  | SYMBOL    | CONDITIONS                                                                                                |                                                            | MIN    | TYP          | MAX | UNITS   |

|------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------|--------------|-----|---------|

| Dynamic Range                                                                                              | DNR       | $f_{IN} = 1kHz$ , unweighted                                                                              |                                                            | 73     |              |     | dB      |

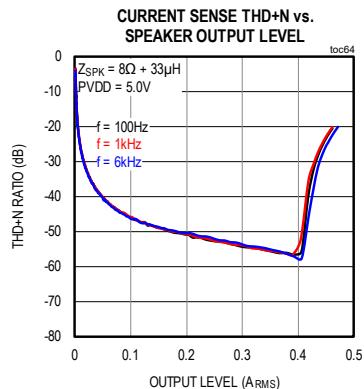

| Total Harmonic Distortion + Noise                                                                          | THD+N     | $f_{IN} = 1kHz$ , $Z_{LOAD} = 4\Omega + 33\mu H$                                                          | Single-cell mode, $V_{PVDD} = 5V$ , $I_{SPK} = 0.6A_{RMS}$ | -59    |              |     | dB      |

|                                                                                                            |           |                                                                                                           | Two-cell mode, $V_{PVDD} = 7.4V$ , $I_{SPK} = 1A_{RMS}$    | -63    |              |     |         |

|                                                                                                            |           | $f_{IN} = 1kHz$ , $Z_{LOAD} = 8\Omega + 33\mu H$                                                          | Single-cell mode, $V_{PVDD} = 5V$ , $I_{SPK} = 0.3A_{RMS}$ | -54    |              |     |         |

|                                                                                                            |           |                                                                                                           | Two-cell mode, $V_{PVDD} = 7.4V$ , $I_{SPK} = 0.5A_{RMS}$  | -59    |              |     |         |

| Differential Mode Gain                                                                                     |           | Open loop current sense channel response, $T_A = +25^\circ C$                                             |                                                            | 0.98   | 1.02         |     |         |

| Differential Mode Gain Variability                                                                         |           | Across supply, $T_A = -40^\circ C$ to $+85^\circ C$ (Note 4)                                              |                                                            | -2.5   | +2.5         | %   |         |

| Maximum Common Mode Gain                                                                                   |           |                                                                                                           |                                                            | -60    |              |     | dB      |

| Highpass Cutoff Frequency                                                                                  |           | -3dB limit, across all sample rates                                                                       |                                                            |        | 2            |     | Hz      |

| DC Offset Current                                                                                          |           | DC blocking filter enabled, $T_A = +25^\circ C$                                                           |                                                            | -0.12  | +0.12        |     | mA      |

|                                                                                                            |           | DC blocking filter disabled, $T_A = +25^\circ C$                                                          | MAX98388, $V_{PVDD} = 3.7V$ , single-cell mode             | -2     | +2           |     |         |

|                                                                                                            |           | DC blocking filter disabled, $T_A = +25^\circ C$                                                          | MAX98389, $V_{PVDD} = 7.4V$ , two-cell mode                | -4     | +4           |     |         |

| Voltage and Current Accuracy Drift Tracking                                                                |           | $T_A = 0^\circ C$ to $+85^\circ C$ , relative to $+25^\circ C$                                            |                                                            | 0.4    |              |     | %       |

| Speaker Amplifier Voltage to Current Sense Crosstalk                                                       |           | MAX98388, $f_{IN} = 1kHz$                                                                                 | Single-cell mode                                           | -80    |              |     | dB      |

|                                                                                                            |           | MAX98389, $f_{IN} = 1kHz$                                                                                 | Two-cell mode                                              | -75    |              |     |         |

| Power Supply Feedthrough                                                                                   | PSF       | No input signal, AC relative to $V_{PVDD}$ or $V_{DD}$ , $f_{RIPPLE} = 1kHz$ , $V_{RIPPLE} = 100mV_{P-P}$ |                                                            | 65     |              |     | dB      |

| Max Current Sense to Voltage Feedback Channel Phase Mismatch                                               |           | $f_{IN} = 1kHz$                                                                                           |                                                            | 0.05   |              |     | Samples |

| Max Device to Device Current Sense Channel Phase Mismatch                                                  |           | $f_{IN} = 1kHz$                                                                                           |                                                            | 0.05   |              |     | Samples |

| <b>SPEAKER OUTPUT CURRENT ADC / DIGITAL FILTER CHARACTERISTICS (<math>f_S &lt; 50</math> kHz) (Note 2)</b> |           |                                                                                                           |                                                            |        |              |     |         |

| Passband Ripple                                                                                            |           | $f_{IN} \leq f_{PLP}$                                                                                     |                                                            | -0.225 | +0.225       |     | dB      |

| Lowpass Filter Cutoff Frequency                                                                            | $f_{PLP}$ | -3dB limit                                                                                                |                                                            | 0.44   | $\times f_S$ |     | Hz      |

( $V_{PVDD} = 5V$  (Single-Cell Mode) or  $7.4V$  (Two-Cell Mode),  $V_{DD} = 1.8V$ ,  $V_{GND} = V_{PGND} = 0V$ ,  $C_{PVDD} = 10\mu F + 0.1\mu F$ ,  $C_{VDD} = 1\mu F$ ,  $f_{BCLK} = 3.072MHz$ ,  $f_{LRCLK} = 48kHz$ ,  $Z_{SPK} = \infty$  between OUTP and OUTN, Single-Cell Mode, AC Measurement Bandwidth = 20Hz to 20kHz,  $T_A = T_{MIN}$  to  $T_{MAX}$ , Typical values are at  $T_A = +25^\circ C$ ) (Note 1)

| PARAMETER                                                                                                 | SYMBOL    | CONDITIONS                                                   | MIN                        | TYP                   | MAX | UNITS   |

|-----------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------|----------------------------|-----------------------|-----|---------|

| Lowpass Filter Stopband Frequency                                                                         | $f_{SLP}$ | -40dB limit                                                  |                            | 0.58<br>$\times f_S$  |     | Hz      |

| Lowpass Filter Stopband Attenuation                                                                       |           |                                                              | 40                         |                       |     | dB      |

| Max Group Delay                                                                                           |           | $f_{IN} = 1kHz$                                              |                            | 8                     |     | Samples |

| <b>SPEAKER OUTPUT CURRENT ADC / DIGITAL FILTER CHARACTERISTICS (<math>f_S \geq 50kHz</math>) (Note 2)</b> |           |                                                              |                            |                       |     |         |

| Passband Ripple                                                                                           |           | $f_{IN} \leq f_{PLP}$                                        | -0.225                     | +0.225                |     | dB      |

| Lowpass Filter Cutoff Frequency                                                                           | $f_{PLP}$ | Droop $< -3dB$ , $88.2kHz \leq f_S \leq 96kHz$               | 0.23<br>$\times f_S$       |                       |     | Hz      |

| Lowpass Filter Stopband Frequency                                                                         | $f_{SLP}$ | -40dB limit                                                  |                            | 0.58<br>$\times f_S$  |     | Hz      |

| Lowpass Filter Stopband Attenuation                                                                       |           |                                                              | 40                         |                       |     | dB      |

| Max Group Delay                                                                                           |           | $f_{IN} = 1kHz$                                              |                            | 9                     |     | Samples |

| <b>BROWNOUT PROTECTION ALC</b>                                                                            |           |                                                              |                            |                       |     |         |

| Brownout Response Time                                                                                    |           | From PVDD below voltage threshold event to audio attenuation | 12                         |                       |     | μs      |

| Brownout Voltage Threshold Range                                                                          |           | PVDD falling, single-cell mode                               | Minimum threshold setting  | 2.5                   |     | V       |

|                                                                                                           |           |                                                              | Maximum threshold setting  | 3.625                 |     |         |