## MAX22216/MAX22217

# Quad Smart Serial-Controlled Solenoid and Motor Driver with Advanced Diagnostic

### General Description

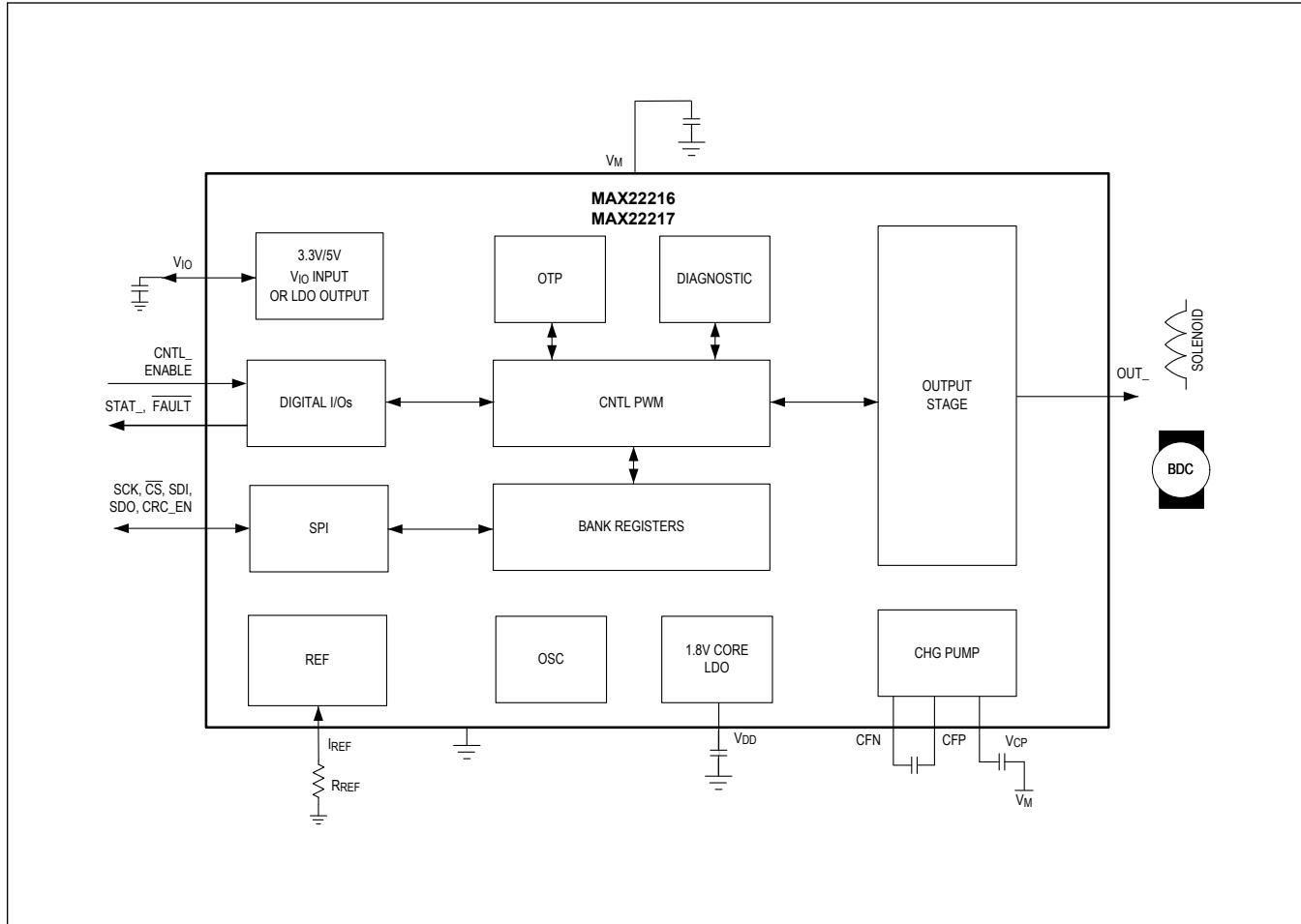

The MAX22216/MAX22217 integrate four programmable 36V half-bridges. It is primarily intended to drive inductive loads such as on-off solenoid valves, DC motors, proportional valves, bi-stable valves, relays, etc. The MAX22216 is capable of up to 3.2A<sub>FS</sub> per half-bridge, whereas the MAX22217 is capable of up to 1A<sub>FS</sub> per half-bridge. The MAX22216/MAX22217 operate from -40°C to +125°C ambient temperature.

The MAX22216/MAX22217 half-bridges support two different use cases. In the first case, configuration settings can be entered through a serial peripheral interface (SPI) and can be changed at any time. Alternatively, settings can be stored in one-time programmable (OTP) registers, which are loaded at power-up. This enables stand-alone operations. Registers are user-programmable. The OTP writing procedure must be executed in a factory under well-controlled temperature and voltage conditions.

High-side/low-side single-ended drive operations and bridge-tied load (BTL) configurations are supported. Channel parallelization is also supported.

Voltage control, current control, and mixed schemes are supported.

In voltage drive regulation mode (VDR mode), the half-bridge output voltage is controlled. Supply variations are internally compensated.

In current drive regulation mode (CDR mode), the half-bridge output current is controlled. The current is internally sensed and fed back to the controller for accurate closed-loop regulation. Proportional and integral gains can be configured to optimize steady-state errors and dynamic performance.

The MAX22216/MAX22217 integrate functions aimed to optimize solenoid and DC motor drive control. These include a two-level sequencer for power saving, drive signal ramp control (RAMP) for noise reduction, a dither function (DITH) to counteract the effects of static friction and hysteresis, a fast demagnetization feature (DC\_H2L) to shorten on-off cycles, and a DC-Motor current limiter for limiting inrush and stall currents.

Advanced diagnostic functions are available to improve system reliability and enable predictive maintenance. These include the detection of plunger movement (DPM), inductance measurement, travel time measurement, open-load detection (OL), and real-time current monitoring through a serial interface.

The MAX22216/MAX22217 feature a full set of protection

circuits, including overcurrent protection (OCP), overtemperature protection (OVT), and undervoltage lockout (UVM). A fault indicator pin is asserted whenever faults are detected.

The MAX22216/MAX22217 are offered in TQFN32 5mm x 5mm packages.

### Applications

- Solenoid On-Off Valves and Relays

- DC Motors

- Proportional Valves

- Bi-Stable Latching Solenoid Valves

- Switching Driver with Real-Time Current Measurement

- Digital Output Interface

- Electromechanical Motor Brake

### Benefits and Features

- Four Serial Controlled 36V Half Bridges

- 1.7A DC ( $T_A = 25^\circ\text{C}$ ) and 3.2A Full-Scale Current Capability (MAX22216)

- 0.55A DC ( $T_A = 25^\circ\text{C}$ ) and 1A Full-Scale Current Capability (MAX22217)

- Low  $R_{ON}$  for High Efficiency

- High Flexibility:

- Independent Channel Setting

- High-Side/Low-Side/Bridge-Tied Load Configuration/Parallel Mode Supported

- Advanced Control Methods

- Voltage/Current Drive Regulation

- Two Levels Sequencer for Power Saving

- DC-Motor Drive with Current Limiter

- Dithering Function

- Ramp up/down Control

- Demagnetization Voltage Control

- Integrated Current Sense

- Diagnostic Functions:

- Reaction and Travel Time Measurement

- Detection of Plunger Movements

- Open-Load Detection

- Inductance Measurement

- Digital Current Sense Monitor

- Full Set of Protections

- Overcurrent Protection

- Thermal Protections

- Undervoltage Lockout

[Ordering Information](#) appears at end of data sheet.

19-101721; Rev 1; 4/24

© 2024 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

One Analog Way, Wilmington, MA 01887 U.S.A. | Tel: 781.329.4700 | © 2024 Analog Devices, Inc. All rights reserved.

**Simplified Block Diagram**

---

**TABLE OF CONTENTS**

---

|                                                              |    |

|--------------------------------------------------------------|----|

| General Description . . . . .                                | 1  |

| Applications . . . . .                                       | 1  |

| Benefits and Features . . . . .                              | 1  |

| Simplified Block Diagram . . . . .                           | 2  |

| Absolute Maximum Ratings . . . . .                           | 8  |

| Package Information . . . . .                                | 8  |

| TQFN 32 - 5mm x 5mm . . . . .                                | 8  |

| Electrical Characteristics . . . . .                         | 8  |

| Pin Configuration . . . . .                                  | 13 |

| MAX22216/MAX22217 . . . . .                                  | 13 |

| Pin Description . . . . .                                    | 13 |

| Functional Diagrams . . . . .                                | 15 |

| Functional Diagram . . . . .                                 | 15 |

| Detailed Description . . . . .                               | 16 |

| OPERATING MODES OVERVIEW . . . . .                           | 17 |

| Single-Ended Operation . . . . .                             | 17 |

| Bridge-Tied Load Operation (Full Bridge) . . . . .           | 19 |

| DC Motor Drive . . . . .                                     | 21 |

| FUNCTIONAL DESCRIPTION . . . . .                             | 22 |

| MAX22216/MAX22217 SPI or OTP Configuration . . . . .         | 22 |

| Enable Logic Input (ENABLE) . . . . .                        | 22 |

| Nap Mode and ACTIVE Bit . . . . .                            | 22 |

| V <sub>IO</sub> Pin Description (V <sub>IO</sub> ) . . . . . | 23 |

| CNTL Pin and CNTL Bits . . . . .                             | 23 |

| Hardware Configuration . . . . .                             | 23 |

| HS or LS Single-Ended Configuration . . . . .                | 25 |

| Chopping Frequency and Timebase Configuration . . . . .      | 25 |

| Slew Rate and Blanking Configuration (SRC) . . . . .         | 25 |

| SEQUENCER SETTINGS . . . . .                                 | 26 |

| Setting the Sequencer Control Mode . . . . .                 | 26 |

| SEQUENCER LEVEL SETTINGS . . . . .                           | 27 |

| Voltage Drive Regulation (VDR) . . . . .                     | 27 |

| CURRENT DRIVE REGULATION (CDR) . . . . .                     | 27 |

| Current Drive Regulation (CDR) . . . . .                     | 27 |

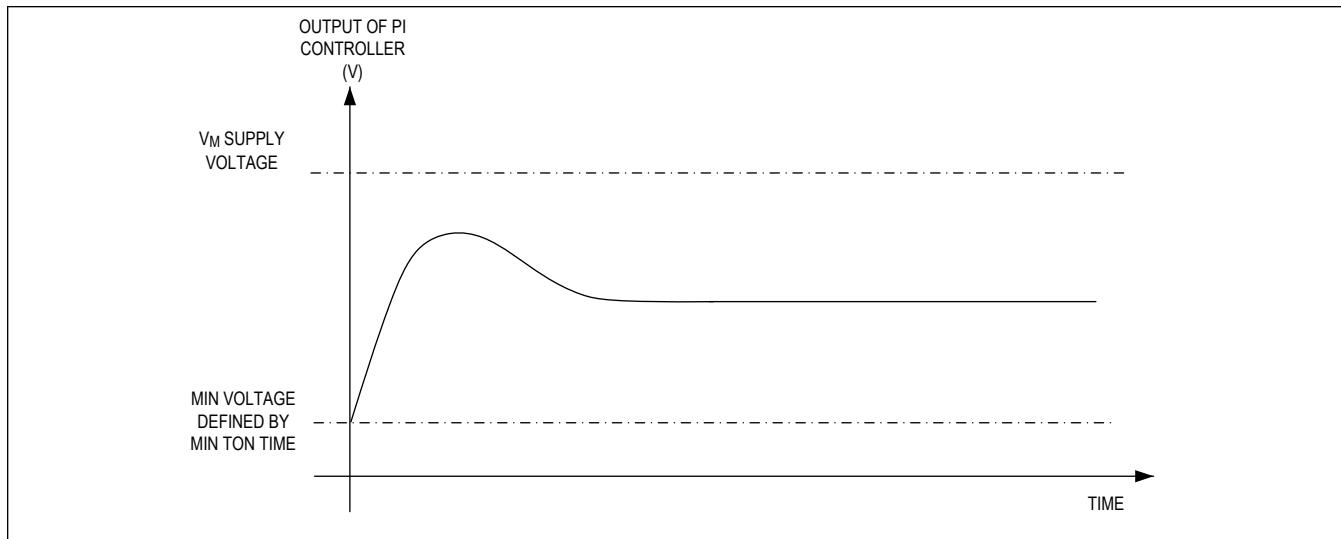

| PI Controller . . . . .                                      | 28 |

| Minimum TON Limitations . . . . .                            | 29 |

| Current Reference . . . . .                                  | 30 |

| Setting the Excitation Time (TIME_L2H) . . . . .             | 30 |

| Setting the Ramp Slopes . . . . .                            | 31 |

**TABLE OF CONTENTS (CONTINUED)**

|                                                                                |    |

|--------------------------------------------------------------------------------|----|

| Enabling the Sine Wave Generator for Dithering or Inductance Measurement ..... | 31 |

| Setting the Sine Wave Generator .....                                          | 32 |

| Brake Current Limiter Function .....                                           | 32 |

| <b>DIAGNOSTIC FUNCTIONS AND STATUS MONITOR</b> .....                           | 33 |

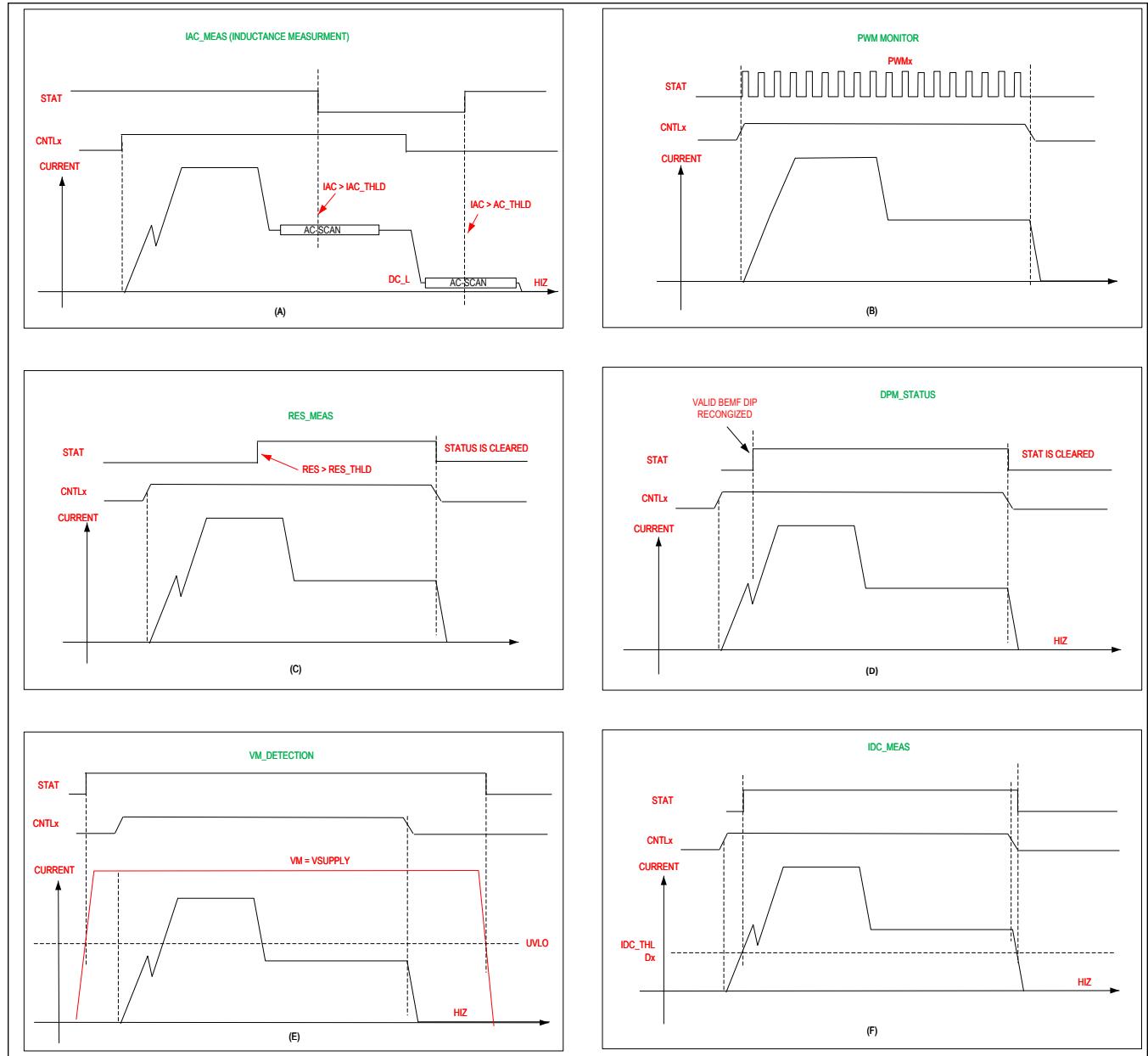

| Digital Current Monitor Function .....                                         | 33 |

| PWM Duty Cycle Monitor Function .....                                          | 34 |

| Digital $V_M$ Supply Voltage Monitor .....                                     | 34 |

| Inductance Measurement Overview .....                                          | 34 |

| Setting the Inductance Measurement .....                                       | 35 |

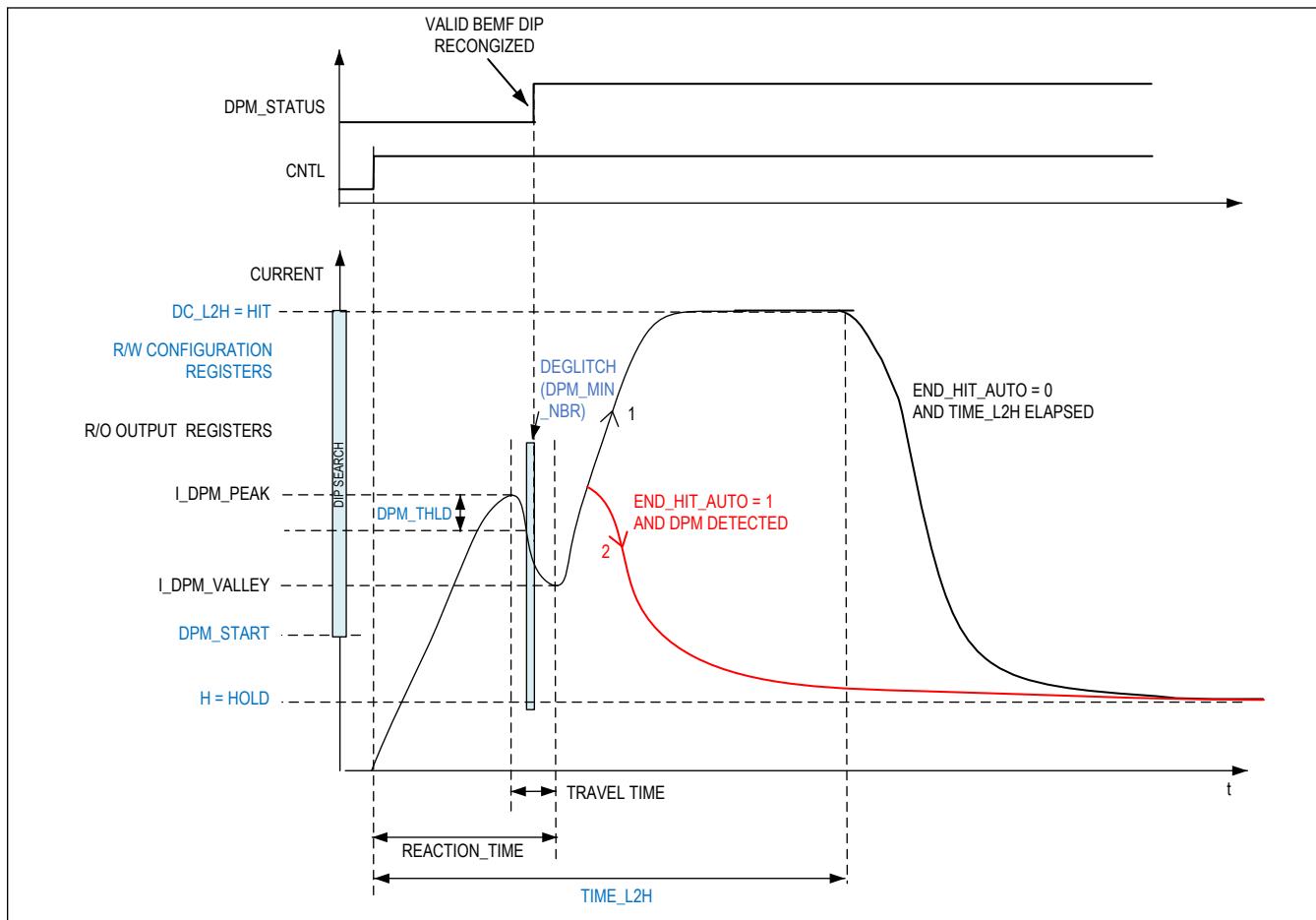

| Detection of Plunger Movement (DPM) - Overview .....                           | 35 |

| Setting the Detection of Plunger Movement .....                                | 37 |

| Resistance Measurement .....                                                   | 38 |

| Setting the Status Monitor .....                                               | 38 |

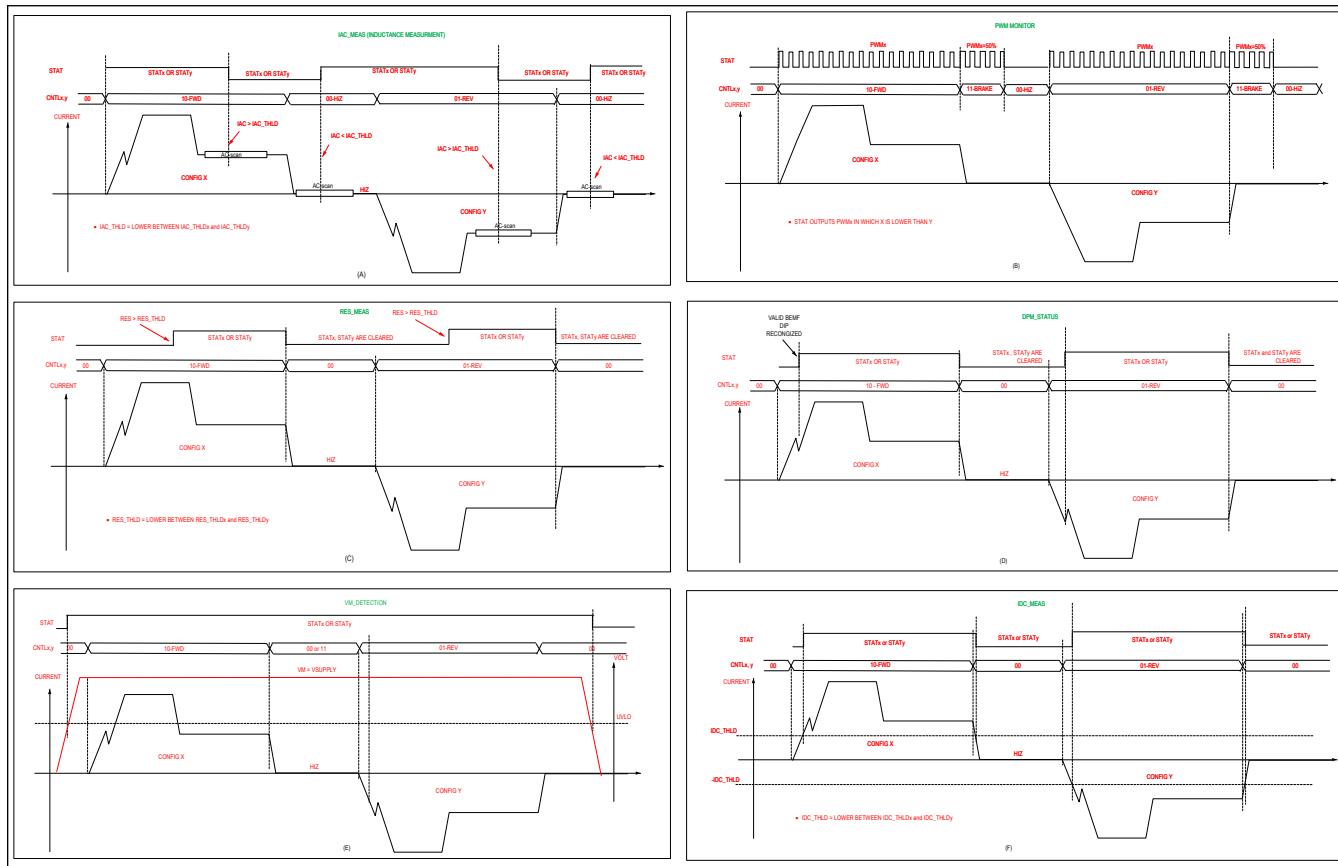

| STAT Monitor - Single-Ended Diagrams .....                                     | 41 |

| STAT Monitor - Differential Diagrams .....                                     | 42 |

| <b>PROTECTIONS AND FAULT INDICATOR</b> .....                                   | 42 |

| Protections and Fault Indicator Pin (FAULT) .....                              | 42 |

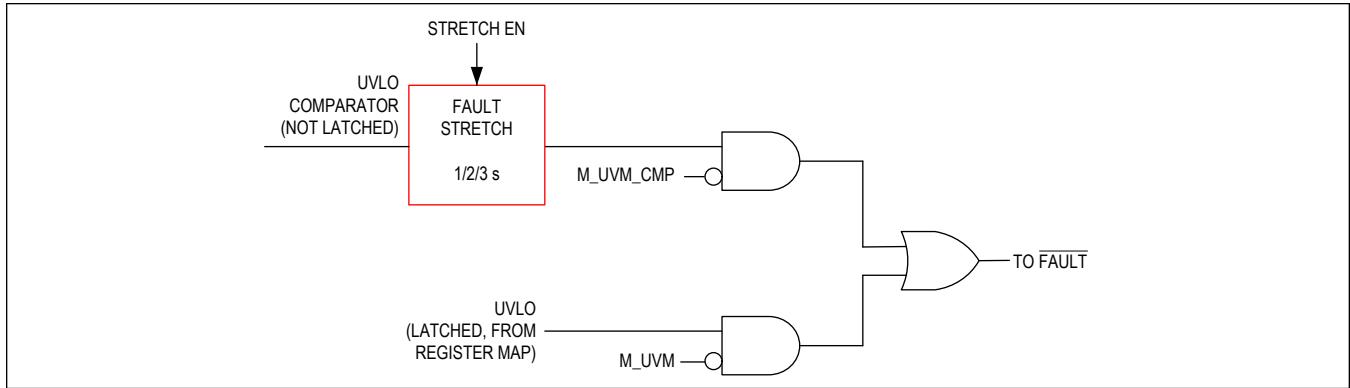

| Undervoltage Lockout (UVM) .....                                               | 43 |

| Overcurrent Protection (OCP) .....                                             | 44 |

| Open-Load Detection During Channel OFF (OL) .....                              | 44 |

| Overtemperature Protection (OVT) .....                                         | 44 |

| "Hit Current not Reached" Flag (HHF) .....                                     | 45 |

| <b>HOW TO CONFIGURE THE MAX22216/MAX22217</b> .....                            | 45 |

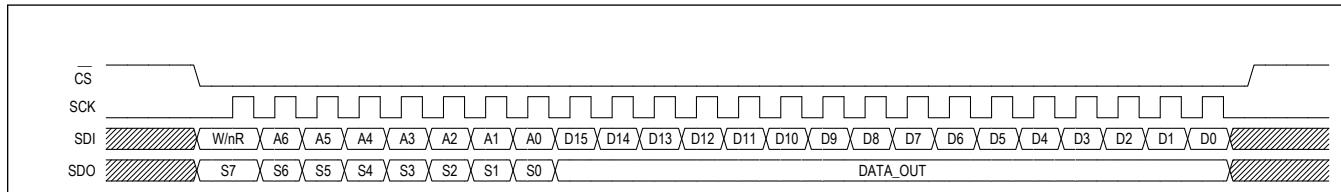

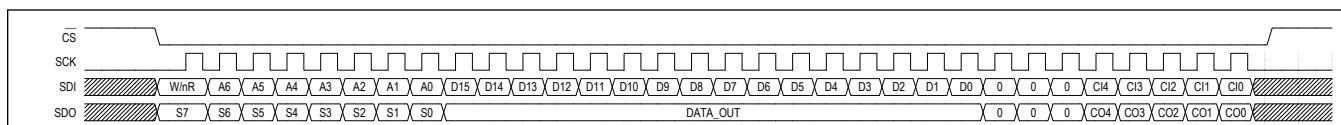

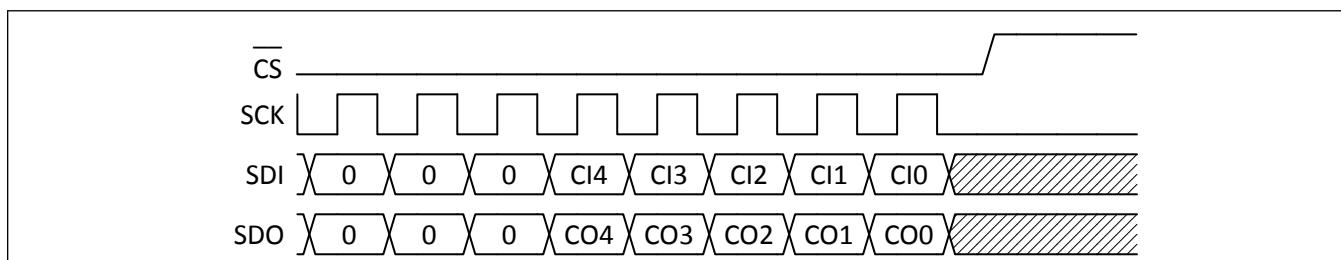

| SPI Description .....                                                          | 45 |

| SPI Data .....                                                                 | 45 |

| CRC Error Detection on the Serial Interface .....                              | 46 |

| One-Time Programmable (OTP) .....                                              | 47 |

| OTP Programming .....                                                          | 47 |

| Wake-Up Time for OTP Download at Power-Up .....                                | 48 |

| <b>Register Map</b> .....                                                      | 49 |

| <b>FUNCTIONAL REGISTERS</b> .....                                              | 49 |

| Register Details .....                                                         | 54 |

| OTP_CONTROLLER .....                                                           | 72 |

| Register Details .....                                                         | 73 |

| Applications Information .....                                                 | 75 |

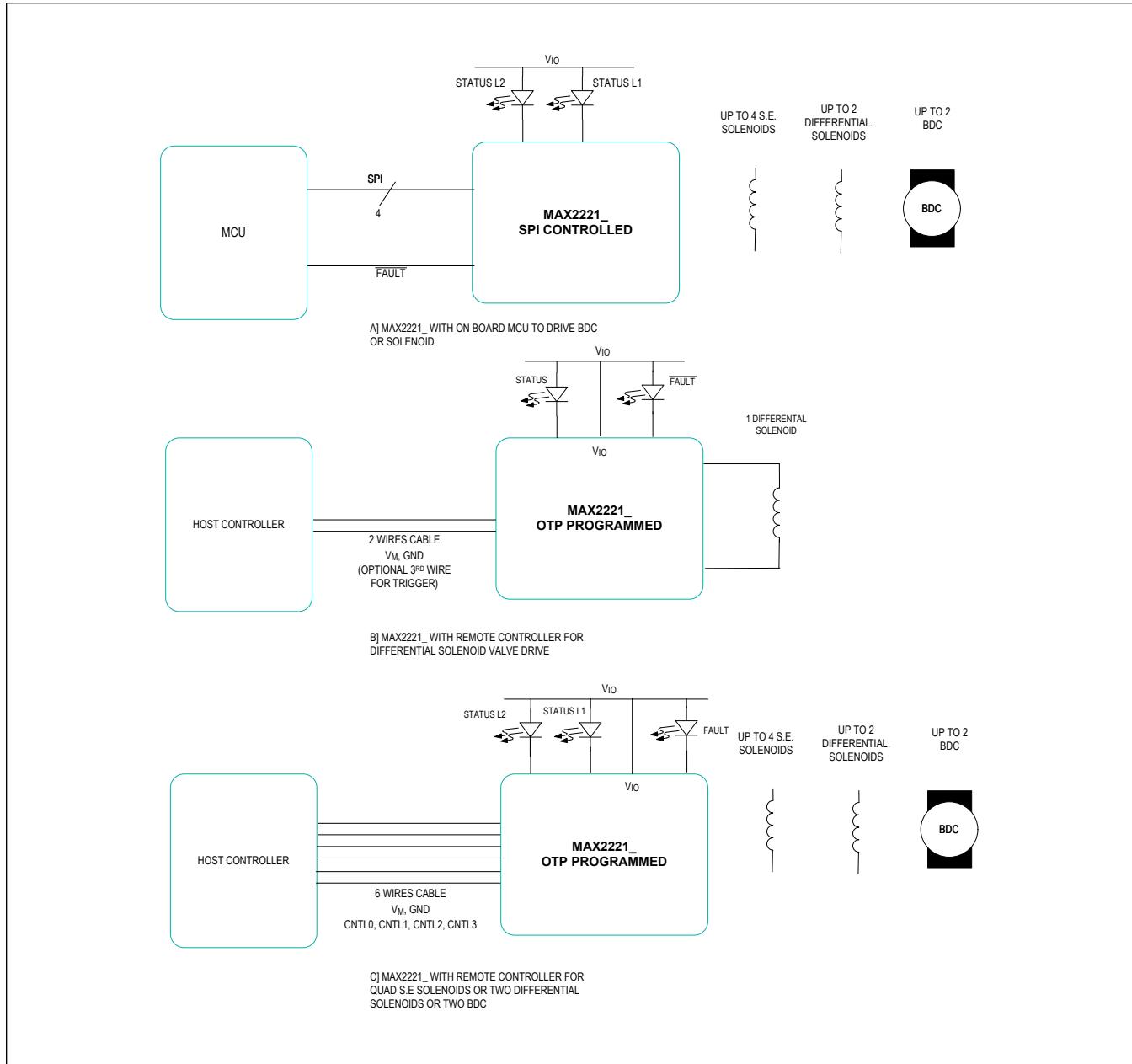

| Examples of Use .....                                                          | 75 |

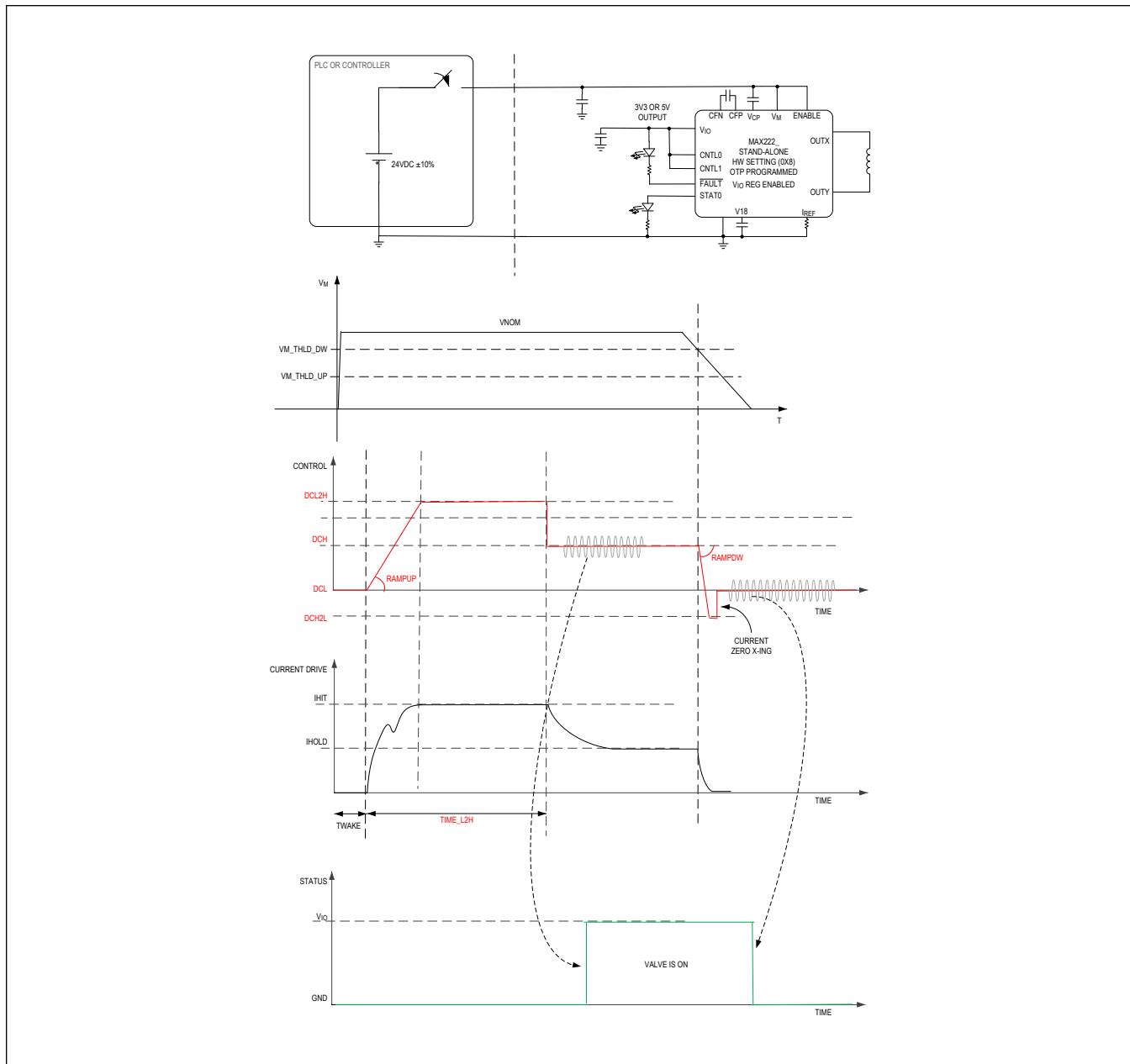

| $V_M$ Switching Stand-Alone .....                                              | 76 |

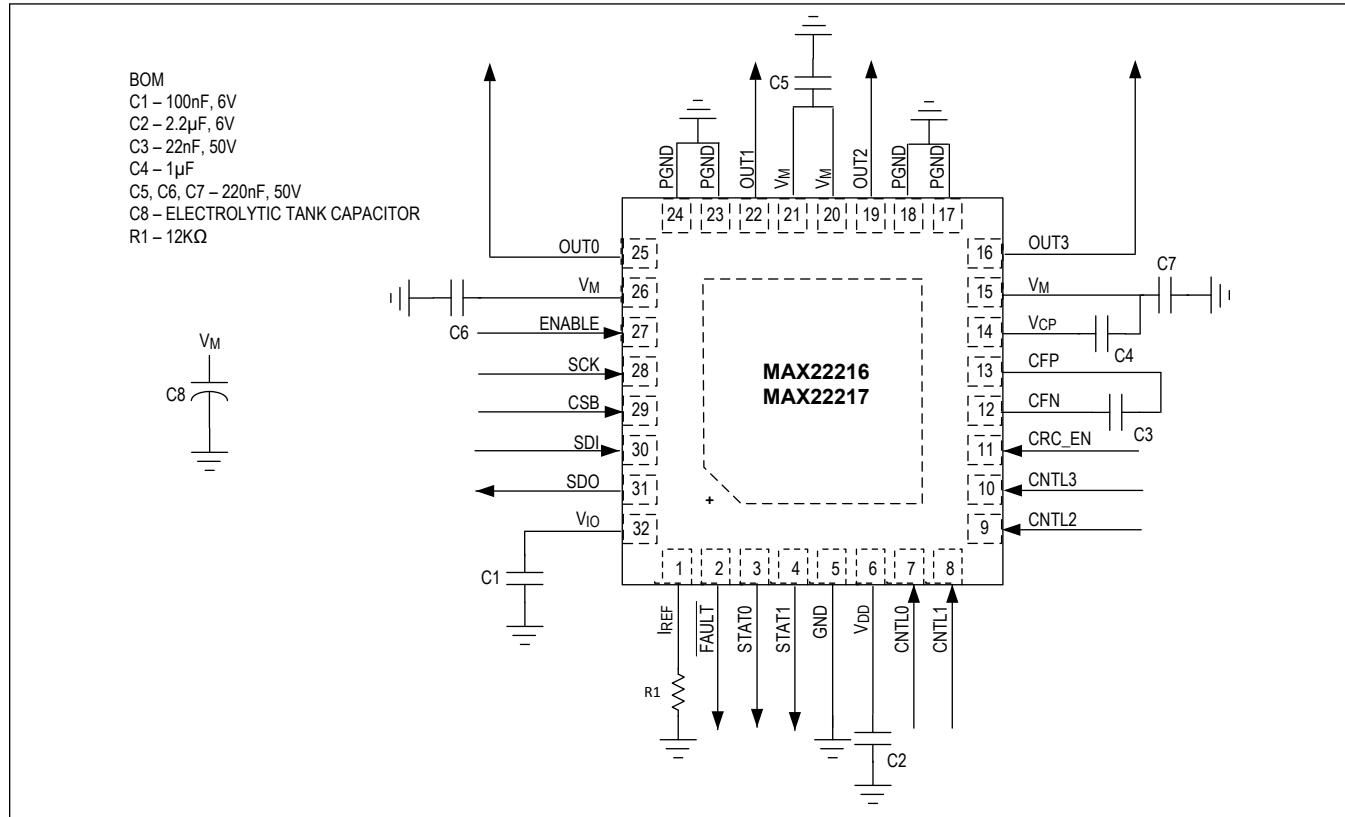

| Typical Application Circuits .....                                             | 79 |

| Typical Application Circuit .....                                              | 79 |

---

**TABLE OF CONTENTS (CONTINUED)**

---

|                            |    |

|----------------------------|----|

| Ordering Information ..... | 79 |

| Revision History .....     | 80 |

---

**LIST OF FIGURES**

---

|                                                          |    |

|----------------------------------------------------------|----|

| Figure 1. Single-Ended Configuration .....               | 18 |

| Figure 2. Bridge-Tied Load Configuration .....           | 19 |

| Figure 3. DC Motor .....                                 | 21 |

| Figure 4. Block Diagram of Current Control Loop .....    | 29 |

| Figure 5. HS Configuration Maximal Voltage Graph .....   | 29 |

| Figure 6. LS Configuration Minimal Voltage Graph .....   | 30 |

| Figure 7. Detection of Plunger Movement .....            | 36 |

| Figure 8. STATUS Output Monitor Pin - Single Ended ..... | 41 |

| Figure 9. STATUS Output Monitor Pin - Differential ..... | 42 |

| Figure 10. Fault Output Schematic .....                  | 44 |

| Figure 11. SPI Datagram without CRC .....                | 45 |

| Figure 12. SPI Datagram with CRC .....                   | 45 |

| Figure 13. CRC byte .....                                | 46 |

| Figure 14. Examples of Use .....                         | 76 |

| Figure 15. Stand-Alone - VM Switching .....              | 78 |

---

**LIST OF TABLES**

---

|                                                                |    |

|----------------------------------------------------------------|----|

| Table 1. Hardware Configuration .....                          | 23 |

| Table 2. Control Table .....                                   | 24 |

| Table 3. Full-Bridge Control .....                             | 24 |

| Table 4. PWM Master Frequency Setting .....                    | 25 |

| Table 5. Individual PWM Frequency .....                        | 25 |

| Table 6. Slew-Rate Control .....                               | 25 |

| Table 7. Blanking Time .....                                   | 26 |

| Table 8. Control Mode Setting .....                            | 26 |

| Table 9. Full Scale and Sense Scale .....                      | 28 |

| Table 10. Dither and Inductance Measurement Table .....        | 32 |

| Table 11. I_MONITOR ADC Max Value - Dec .....                  | 33 |

| Table 12. Inductance Measurement Fault Detection .....         | 35 |

| Table 13. STATUS Monitor Based on Inductance Measurement ..... | 35 |

| Table 14. STAT Logic Output Pin Selection .....                | 39 |

| Table 15. Multifunction Status Pin .....                       | 40 |

| Table 16. Mask Bits .....                                      | 43 |

| Table 17. Stretch Enable .....                                 | 43 |

**Absolute Maximum Ratings**

|                          |                                                          |                                                                                                      |                                             |

|--------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------|

| V <sub>M</sub> to GND    | -0.3V to +42V                                            | SCK to GND                                                                                           | -0.3V to min (6V, V <sub>IO</sub> + 0.3V)V  |

| V <sub>CP</sub> to GND   | V <sub>M</sub> - 0.3V to min (+42V, V <sub>M</sub> + 6V) | SDO to GND                                                                                           | -0.3V to min (6V, V <sub>IO</sub> + 0.3V)V  |

| C <sub>FP</sub> to GND   | V <sub>M</sub> - 0.3V to V <sub>CP</sub> + 0.3V          | V <sub>DD</sub> to GND                                                                               | -0.3V to min (+2.2, V <sub>M</sub> + 0.3)V  |

| C <sub>FN</sub> to GND   | -0.3V to min (+42V, V <sub>M</sub> + 0.3V)               | V <sub>IO</sub> to GND                                                                               | -0.3V to +6V                                |

| CNTL <sub>_</sub> to GND | -0.3V to main (6V, V <sub>IO</sub> + 0.3V)V              | FAULT to GND                                                                                         | -0.3V to +6V                                |

| OUT <sub>_</sub> to GND  | -0.3V to V <sub>M</sub> + 0.3V                           | I <sub>REF</sub> to GND                                                                              | -0.3V to min (+2.2, V <sub>DD</sub> + 0.3)V |

| PGND to GND              | -0.3V to +0.3V                                           | Continuous Power Dissipation (2s2p Board) (T <sub>A</sub> = +70°C, derate<br>34.5mW/°C above +70°C.) | 2758.6mW                                    |

| CRC_EN to GND            | -0.3V to min (6V, V <sub>IO</sub> + 0.3V)V               | Operating Temperature Range                                                                          | -40°C to +125°C                             |

| STAT <sub>_</sub> to GND | -0.3V to V <sub>IO</sub> + 0.3V                          | Junction Temperature                                                                                 | +150°C                                      |

| ENABLE to GND            | -0.3V to V <sub>M</sub> + 0.3V                           | Storage Temperature Range                                                                            | -65°C to 150°C                              |

| CS to GND                | -0.3V to min (6V, V <sub>IO</sub> + 0.3V)V               | Lead Temperature (soldering, 10s)                                                                    | +300°C                                      |

| SDI to GND               | -0.3V to min (6V, V <sub>IO</sub> + 0.3V)V               |                                                                                                      |                                             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Package Information****TQFN 32 - 5mm x 5mm**

|                                                |                           |

|------------------------------------------------|---------------------------|

| Package Code                                   | T3255Y+4C                 |

| Outline Number                                 | <a href="#">21-100214</a> |

| Land Pattern Number                            | <a href="#">90-100082</a> |

| <b>Thermal Resistance, Single-Layer Board:</b> |                           |

| Junction to Ambient (θ <sub>JA</sub> )         | -                         |

| Junction to Case (θ <sub>JC</sub> )            | -                         |

| <b>Thermal Resistance, Four-Layer Board:</b>   |                           |

| Junction to Ambient (θ <sub>JA</sub> )         | 29°C/W                    |

| Junction to Case (θ <sub>JC</sub> )            | 1.7°C/W                   |

For the latest package outline information and land patterns (footprints), go to [www.maximintegrated.com/packages](http://www.maximintegrated.com/packages).

Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to [www.maximintegrated.com/thermal-tutorial](http://www.maximintegrated.com/thermal-tutorial).

**Electrical Characteristics**

(V<sub>M</sub> = 4.5V to 36V, V<sub>IO</sub> = 2.2V to 5.25V, R<sub>REF</sub> = 12kΩ, ENABLE = logic high, Typical values assume T<sub>A</sub> = 25°C and V<sub>M</sub> = 24V, Limits are 100% tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                      | SYMBOL             | CONDITIONS       | MIN | TYP  | MAX | UNITS |

|--------------------------------|--------------------|------------------|-----|------|-----|-------|

| <b>POWER SUPPLY</b>            |                    |                  |     |      |     |       |

| Supply Voltage Range           | V <sub>M</sub>     |                  | 4.5 | 36   | V   |       |

| Logic Input Supply Voltage     | V <sub>IO</sub>    |                  | 2.2 | 5.25 | V   |       |

| Sleep Mode Current consumption | I <sub>SLEEP</sub> | Enable logic low | 4   | 18   | μA  |       |

**Electrical Characteristics (continued)**

( $V_M$  = 4.5V to 36V,  $V_{IO}$  = 2.2V to 5.25V,  $R_{REF}$  = 12k $\Omega$ , ENABLE = logic high, Typical values assume  $T_A$  = 25°C and  $V_M$  = 24V, Limits are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                           | SYMBOL       | CONDITIONS                                         | MIN              | TYP             | MAX   | UNITS      |

|-------------------------------------|--------------|----------------------------------------------------|------------------|-----------------|-------|------------|

| Nap Mode Current Consumption        | $I_{NAP}$    | Enable logic high, Active = 0                      |                  | 210             | 450   | $\mu$ A    |

| Quiescent Current Consumption       | $I_{VM}$     | Enable logic high, Active = 1                      |                  | 7               | 9     | mA         |

| <b>LOGIC LEVEL INPUTS-OUTPUTS</b>   |              |                                                    |                  |                 |       |            |

| Input Voltage Level - High          | $V_{IH}$     |                                                    | 0.7 x $V_{IO}$   |                 |       | V          |

| Input Voltage Level - Low           | $V_{IL}$     |                                                    |                  | 0.3 x $V_{IO}$  |       | V          |

| Input Hysteresis                    | $V_{HYS}$    |                                                    |                  | 0.15 x $V_{IO}$ |       | $mV$       |

| Logic Input Pin Pulldown Resistance | $R_{PD}$     | To GND. Pins CNTL <sub>—</sub> , SCK, SDI, CRC_EN. | 70               | 100             | 130   | k $\Omega$ |

| CS Pin Pullup Resistance            | $R_{PU}$     | To $V_{IO}$                                        | 70               | 100             | 130   | k $\Omega$ |

| Logic-Low Output Voltage            | $V_{OL}$     | $I_{LOAD}$ = 5mA, STAT <sub>—</sub> and FAULT pin  |                  | 0.4             |       | V          |

| Logic-High Output Voltage           | $V_{OH}$     | $I_{LOAD}$ = -5mA                                  | $V_{IO}$ - 0.4   |                 |       | V          |

| Enable Voltage Level High           | $V_{IH(EN)}$ |                                                    | 0.9              |                 |       | V          |

| Enable Voltage Level Low            | $V_{IL(EN)}$ |                                                    |                  | 0.6             |       | V          |

| Enable Pulldown Input Resistance    | $R_{PD(EN)}$ |                                                    | 0.8              | 1.5             |       | $m\Omega$  |

| <b>OUTPUT SPECIFICATIONS</b>        |              |                                                    |                  |                 |       |            |

| Output On-Resistance Low Side       | $R_{ON(LS)}$ | MAX22216                                           | SNSF[1:0] = "00" | 0.17            | 0.330 | $\Omega$   |

|                                     |              |                                                    | SNSF[1:0] = "01" | 0.23            | 0.45  |            |

|                                     |              |                                                    | SNSF[1:0] = "10" | 0.43            | 0.83  |            |

|                                     |              | MAX22217                                           |                  | 0.43            | 0.83  |            |

| Output On-Resistance High Side      | $R_{ON(HS)}$ |                                                    |                  | 0.17            | 0.33  | $\Omega$   |

| Output Leakage                      | $I_{LEAK}$   | Driver OFF                                         |                  | -5              | 5     | $\mu$ A    |

| Dead Time                           | $t_{DEAD}$   |                                                    |                  | 0.1             |       | $\mu$ s    |

| Slew-Rate Control                   | SRC          | SRC[1:0] = "00"                                    |                  | 800             |       | V/ $\mu$ s |

|                                     |              | SRC[1:0] = "01"                                    |                  | 400             |       |            |

|                                     |              | SRC[1:0] = "10"                                    |                  | 200             |       |            |

|                                     |              | SRC[1:0] = "11"                                    |                  | 100             |       |            |

| <b>PROTECTION CIRCUITS</b>          |              |                                                    |                  |                 |       |            |

| Overcurrent Protection Threshold    | OCP          | SNSF[1:0] = "00"                                   | 4                |                 |       | A          |

|                                     | $t_{OCP}$    | SNSF[1:0] = "01"                                   | 2.5              |                 |       |            |

|                                     | OCP          | SNSF[1:0] = "10"                                   | 1.2              |                 |       |            |

**Electrical Characteristics (continued)**

( $V_M$  = 4.5V to 36V,  $V_{IO}$  = 2.2V to 5.25V,  $R_{REF}$  = 12k $\Omega$ , ENABLE = logic high, Typical values assume  $T_A$  = 25°C and  $V_M$  = 24V, Limits are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                                                                             | SYMBOL         | CONDITIONS                                                                                                                                       |                             | MIN         | TYP          | MAX  | UNITS   |

|---------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------|--------------|------|---------|

| Overcurrent Protection Blanking Time                                                  | TOCP           |                                                                                                                                                  |                             | 1.45        | 2.1          | 2.85 | $\mu$ s |

| UVLO Threshold on $V_M$                                                               | UVLO           | Rising                                                                                                                                           |                             | 3.75        | 4            | 4.25 | V       |

|                                                                                       |                | Falling                                                                                                                                          |                             |             | 3.88         | 4.12 |         |

| Thermal Protection Threshold Temperature                                              | $T_{SD}$       |                                                                                                                                                  |                             |             | 165          |      | °C      |

| Thermal Protection Temperature Hysteresis                                             | $T_{SD\_HYST}$ |                                                                                                                                                  |                             |             | 20           |      | °C      |

| Open-Load Detection Current                                                           | $I_{OL\_LS}$   | OL_EN_ = 1                                                                                                                                       | HSnLS = 0, Pulldown current |             | 75           | 135  | $\mu$ A |

|                                                                                       | $I_{OL\_HS}$   |                                                                                                                                                  | HSnLS = 1, Pullup current   | -50         | -22          |      |         |

| Open-Load Detection Voltage                                                           | $V_{OL\_LS}$   | OL_EN_ = 1                                                                                                                                       | HSnLS = 0                   |             | 1.7          | 2.4  | V       |

|                                                                                       | $V_{OL\_HS}$   |                                                                                                                                                  | HSnLS = 1                   | $V_M$ - 2.4 | $V_M$ - 1.75 |      |         |

| Open-Load Detect Deglitch Time                                                        | $t_{OL}$       |                                                                                                                                                  |                             | 189         | 200          | 211  | $\mu$ s |

| <b>LINEAR REGULATORS / <math>V_{DD}</math> REGULATOR</b>                              |                |                                                                                                                                                  |                             |             |              |      |         |

| $V_{DD}$ Regulator Output Voltage                                                     | $V_{VDD}$      | $I_{LOAD}$ = 20mA                                                                                                                                |                             |             | 1.868        |      | V       |

| $V_{DD}$ Current Limit                                                                | $I_{VDD\_LIM}$ |                                                                                                                                                  |                             | 20          |              |      | mA      |

| <b>LINEAR REGULATORS / <math>V_{IO}</math> REGULATOR - (for Stand-Alone USE CASE)</b> |                |                                                                                                                                                  |                             |             |              |      |         |

| $V_{IO}$ Regulator Output Voltage                                                     | $V_{VIO}$      | EN_LDO = 1,<br>$I_{LOAD}$ = 10mA                                                                                                                 | V5nV3 = 1                   | 4.8         | 5            | 5.2  | V       |

|                                                                                       |                |                                                                                                                                                  | V5nV3 = 0                   | 3.15        | 3.3          | 3.4  |         |

| $V_{IO}$ Current Limit                                                                | $I_{VIO\_LIM}$ | Total current. Internal loads account for maximum 10mA                                                                                           |                             | 10          |              |      | mA      |

| <b>CONTROL</b>                                                                        |                |                                                                                                                                                  |                             |             |              |      |         |

| Internal Oscillator Frequency                                                         | FCLK           |                                                                                                                                                  |                             | 23.7        | 25           | 26.3 | MHz     |

| CDR Maximum Full Scale - LS or FB                                                     | IFSMAX         | MAX22216<br>GAIN[1:0] = "00" - LS or FB config.<br>( <a href="#">Note 1</a> )                                                                    | SNSF[1:0] = "00"            | 3.2         |              |      | A       |

|                                                                                       |                |                                                                                                                                                  | SNSF[1:0] = "01"            | 2.1         |              |      |         |

|                                                                                       |                |                                                                                                                                                  | SNSF[1:0] = "10"            | 1           |              |      |         |

| CDR Maximum Full Scale - HS                                                           | IFSMAX         | MAX22216<br>GAIN[1:0] = "00" - HS config. ( <a href="#">Note 1</a> )<br><br>MAX22216<br>GAIN[1:0] = "00" - HS config. ( <a href="#">Note 1</a> ) | SNSF[1:0] = "00"            | 1.5         |              |      | A       |

|                                                                                       |                |                                                                                                                                                  | SNSF[1:0] = "01"            | 1           |              |      |         |

|                                                                                       |                |                                                                                                                                                  | SNSF[1:0] = "10"            | 0.5         |              |      |         |

| CDR Maximum Full Scale - LS or FB                                                     | IFSMAX         | MAX22217 GAIN[1:0] = "00" - LS or FB config. ( <a href="#">Note 1</a> )                                                                          |                             |             | 1            |      | A       |

| CDR Maximum Full Scale - HS                                                           | IFSMAX         | MAX22217 GAIN[1:0] = "00" - HS config. ( <a href="#">Note 1</a> )                                                                                |                             |             | 0.5          |      | A       |

**Electrical Characteristics (continued)**

( $V_M$  = 4.5V to 36V,  $V_{IO}$  = 2.2V to 5.25V,  $R_{REF}$  = 12k $\Omega$ , ENABLE = logic high, Typical values assume  $T_A$  = 25°C and  $V_M$  = 24V, Limits are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                                                           | SYMBOL    | CONDITIONS                                                                                         | MIN                                        | TYP                 | MAX | UNITS      |

|---------------------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------|-----|------------|

| CDR Constant                                                        | $K_{CDR}$ | MAX22216                                                                                           |                                            | 1.017               |     | mA         |

|                                                                     |           | MAX22217                                                                                           |                                            | 0.339               |     |            |

| VDR Constant                                                        | $K_{VDR}$ |                                                                                                    |                                            | 30.518              |     | $\mu$ V    |

| Resistance Measurement Constant                                     | $K_R$     |                                                                                                    |                                            | 8.437               |     | $m\Omega$  |

| REF Pin Resistor Range                                              | $R_{REF}$ | See <a href="#">Note 2</a>                                                                         |                                            | $12k\Omega \pm 5\%$ |     | k $\Omega$ |

| Supply Voltage ( $V_M$ ) Monitoring Constant                        | $K_{VM}$  |                                                                                                    |                                            | 9.73                |     | mV         |

| <b>CONTROL / ACCURACY</b> ( <a href="#">Note 3</a> )                |           |                                                                                                    |                                            |                     |     |            |

| Current Control and Monitor - Accuracy                              | DCDR      | MAX22216,<br>GAIN[1:0] = "00"                                                                      | $I_{OUT} \geq 250mA$ ,<br>SNSF[1:0] = "00" | -5                  | 5   | %          |

|                                                                     |           |                                                                                                    | $I_{OUT} \geq 140mA$ ,<br>SNSF[1:0] = "01" | -5                  | 5   |            |

|                                                                     |           |                                                                                                    | $I_{OUT} \geq 70mA$ ,<br>SNSF = "10"       | -5                  | 5   |            |

|                                                                     |           | MAX22217, GAIN[1:0] = "00"                                                                         | $I_{OUT} \geq 70mA$                        | -5                  | 5   |            |

| <b>FUNCTIONAL TIMINGS</b>                                           |           |                                                                                                    |                                            |                     |     |            |

| Disable Time                                                        | $t_{DIS}$ | Enable falling edge to OUT_tristated                                                               |                                            | 20                  |     | $\mu$ s    |

| Enable Time                                                         | $t_{EN}$  | From enable logic high to normal operation (see <a href="#">Note 4</a> for details)                |                                            | 0.8                 |     | ms         |

| Fixed Wake-Up Time                                                  | $t_{FWU}$ | From active = 1 to normal operation (excluding user OTP download) - ( <a href="#">Note 5</a> )     |                                            | 1.1                 |     | ms         |

| Variable Wake-Up Time                                               | $t_{VWU}$ | Time required to download one user-configurable OTP register (2 bytes). ( <a href="#">Note 5</a> ) |                                            | 2.56                |     | $\mu$ s    |

| <b>SPI SPECIFICATIONS</b>                                           |           |                                                                                                    |                                            |                     |     |            |

| SCK Clock Period                                                    | $t_{CLK}$ | $V_{IO} > 3V$                                                                                      | 100                                        |                     |     | ns         |

|                                                                     |           | $V_{IO} < 3V$                                                                                      | 140                                        |                     |     |            |

| SCK High Time                                                       | $t_{CH}$  |                                                                                                    | 20                                         |                     |     | ns         |

| SCK Low Time                                                        | $t_{CL}$  |                                                                                                    | 20                                         |                     |     | ns         |

| $\overline{CS}$ SCK Valid before or after change of $\overline{CS}$ | $t_{CC}$  |                                                                                                    | 20                                         |                     |     | ns         |

| $\overline{CS}$ Pulse-Width High                                    | $t_{CSH}$ | See also <a href="#">Note 6</a>                                                                    | 20                                         |                     |     | ns         |

| SDI Setup Time before SCK Rising Edge                               | $t_{DS}$  |                                                                                                    | 10                                         |                     |     | ns         |

| SDI Hold Time after SCK Rising Edge                                 | $t_{DH}$  |                                                                                                    | 10                                         |                     |     | ns         |

| SDO Propagation Delay                                               | $t_{DO}$  | $C_{LOAD} = 15pF$                                                                                  | $V_{IO} > 3V$                              | 40                  |     | ns         |

|                                                                     |           |                                                                                                    | $V_{IO} < 3V$                              | 75                  |     |            |

**Note 1:** Recommended "CDR Max full scale" specifies the maximum current at which the device has been characterized and tested. The device can possibly deliver currents higher than IFSMAX, provided that the overcurrent protection and thermal limitations are not exceeded.

**Note 2:** Current control and monitor accuracy is directly proportional to the accuracy of the resistor connected to the I<sub>REF</sub> pin. Use  $\pm 1\%$  tolerance or better resistors whenever accuracy is required. Accuracy data in this data sheet assumes an ideal REF = 12k $\Omega$  resistor.

**Note 3:** Guaranteed by Bench characterization. Not production tested. R<sub>REF</sub> = 12k $\Omega$

**Note 4:** The enable command must be held logic high for longer than 0.8ms to ensure the MAX22216/MAX22217 complete its power-up sequence. Commands shorter than 0.8ms can cause the device to enter in unpredictable status.

**Note 5:** The total wake-up time (t<sub>WU</sub>) is given by the sum of a fixed (T<sub>SWU</sub>) and a variable contribute N x T<sub>YWWU</sub> in which N is the total number of user-programmable OTP registers (2 bytes each) written into the OTP bank. (See the [Wake Up time for OTP download at power up](#) section.)

**Note 6:** A longer T<sub>CSH</sub> is required whenever a fault condition needs to be cleared. We recommend longer than 1 $\mu$ s T<sub>CSH</sub> whenever a fault condition needs to be cleared.

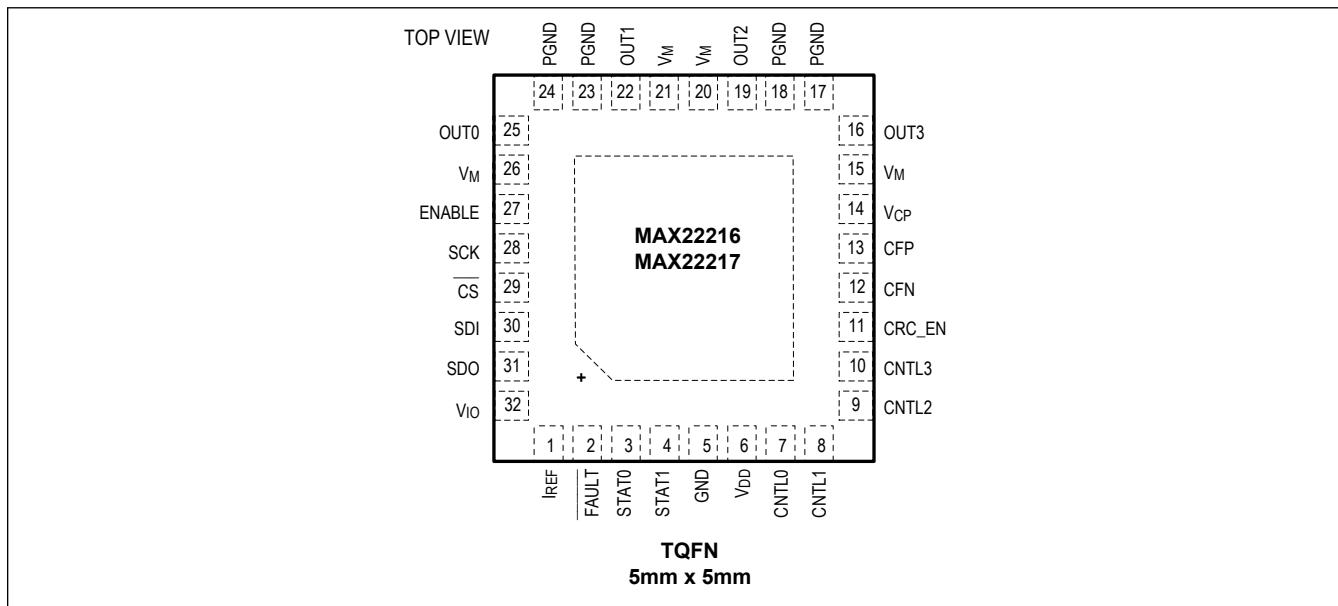

## Pin Configuration

### MAX22216/MAX22217

## Pin Description

| PIN            | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | REF SUPPLY | TYPE  |

|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|

| 15, 20, 21, 26 | VM   | Supply Voltage Input. All VM pins must be shorted on the board. Bypass VM to GND with 0.1µF local ceramic capacitors close to pins 21, 20 and pins 26, 15. Add electrolytic reservoir tank capacitors as required by the application (typically values >10µF).                                                                                                                                                                                                                                                                                                                                                                                                                |            | Power |

| 32             | VIO  | I/O Supply Input Voltage Pin if the Internal Linear Regulator is Disabled (EN_LDO = 0 default condition). For SPI-based applications, connect VIO to the external MCU supply voltage for proper communication between the controller and the MAX22216/MAX22217. Bypass VIO to GND with a 100nF or greater capacitor.<br><br>Voltage regulator output if the internal linear regulator is enabled (EN_LDO = 1). This configuration is used for stand-alone OTP-based applications. The linear regulator output can be configured either at 3.3V or 5V. Connect at least a 0.47µF bypass capacitor to GND to ensure the regulator stability. The maximum external load is 10mA. |            |       |

| 6              | VDD  | 1.8V LDO Regulator Output. Bypass GND with a 2.2µF ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            | Power |

| 12             | CFN  | Charge Pump Capacitor-N Side. Connect a 22nF, VM-rated ceramic capacitor from CFN to CFP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            | Power |

| 13             | CFP  | Charge Pump Capacitor-P Side. Connect a 22nF, VM-rated ceramic capacitor from CFN to CFP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            | Power |

## Pin Description (continued)

| PIN            | NAME             | FUNCTION                                                                                                                                                                                                        | REF SUPPLY      | TYPE              |

|----------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|

| 14             | V <sub>CP</sub>  | Charge Pump Output. Connect a 1 $\mu$ F, 5V, or greater ceramic capacitor to V <sub>M</sub> .                                                                                                                   |                 | Power             |

| 17, 18, 23, 24 | PGND             | Power Ground. All PGND pins must be shorted on the board.                                                                                                                                                       |                 | GND               |

| 5              | GND              | Signal Ground                                                                                                                                                                                                   |                 | GND               |

| 25             | OUT0             | Driver Output Channel 0                                                                                                                                                                                         |                 | Output            |

| 22             | OUT1             | Driver Output Channel 1                                                                                                                                                                                         |                 | Output            |

| 19             | OUT2             | Driver Output Channel 2                                                                                                                                                                                         |                 | Output            |

| 16             | OUT3             | Driver Output Channel 3                                                                                                                                                                                         |                 | Output            |

| 1              | I <sub>REF</sub> | Current Regulation Reference. Connect a 1% accurate 12k $\Omega$ resistor from I <sub>REF</sub> to GND to set the full-scale current for all the channels in CDR Mode.                                          |                 | Analog Input      |

| 29             | CS               | SPI Chip Select—Active Low. Internal pullup current.                                                                                                                                                            | V <sub>IO</sub> | Logic Input       |

| 28             | SCK              | SPI Clock Input. Rising edge clocks data into the part for write operations. Falling edge clocks data out of part for read operations. Internal pulldown to GND.                                                | V <sub>IO</sub> | Logic Input       |

| 30             | SDI              | SPI Data In from Controller. Internal pulldown to GND.                                                                                                                                                          | V <sub>IO</sub> | Logic Input       |

| 31             | SDO              | SPI Data Output.                                                                                                                                                                                                | V <sub>IO</sub> | Logic Output      |

| 7              | CNTL0            | Control Logic Input. Internal pulldown to GND. To avoid spurious triggering by large noise, it is recommended to connect the pin to GND if not used.                                                            | V <sub>IO</sub> | Logic Input       |

| 8              | CNTL1            | Control Logic Input. Internal pulldown to GND. To avoid spurious triggering by large noise, it is recommended to connect the pin to GND if not used.                                                            | V <sub>IO</sub> | Logic Input       |

| 9              | CNTL2            | Control Logic Input. Internal pulldown to GND. To avoid spurious triggering by large noise, it is recommended to connect the pin to GND if not used.                                                            | V <sub>IO</sub> | Logic Input       |

| 10             | CNTL3            | Control Logic Input. Internal pulldown to GND. To avoid spurious triggering by large noise, it is recommended to connect the pin to GND if not used.                                                            | V <sub>IO</sub> | Logic Input       |

| 3              | STAT0            | Status Logic Output.                                                                                                                                                                                            | V <sub>IO</sub> | Logic Output      |

| 4              | STAT1            | Status Logic Output.                                                                                                                                                                                            | V <sub>IO</sub> | Logic Output      |

| 11             | CRC_EN           | Logic Input. Drive CRC_EN logic high to enable cyclic redundancy check on SPI communication. Internal pulldown to GND.                                                                                          | V <sub>IO</sub> | Logic Input       |

| 2              | FAULT            | Pulled Logic Low with a Fault Condition. Open-drain output requires an external pullup resistor.                                                                                                                |                 | Open Drain Output |

| 27             | ENABLE           | Enable Pin. HV logic input pin compatible up to V <sub>M</sub> . Drive ENABLE logic high to enable device; drive ENABLE logic low to enter low-power sleep mode; Internal pulldown resistor.                    |                 | Logic Input       |

| —              | EP               | Exposed Pad. The exposed pad (thermal pad) must be electrically connected to the board GND. For good thermal dissipation, use large ground planes on multiple layers and multiple vias connecting those planes. |                 | GND               |

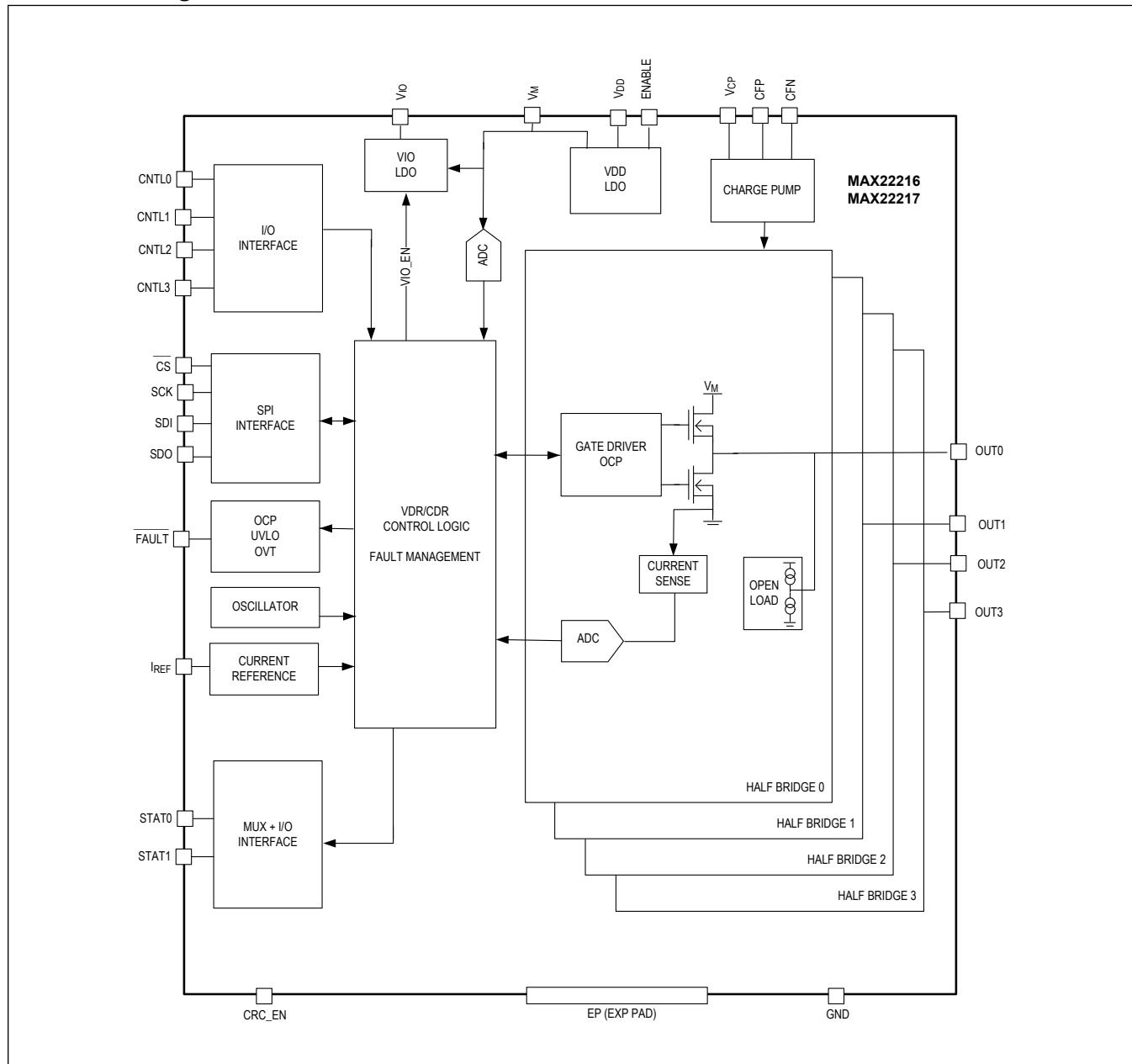

## Functional Diagrams

### Functional Diagram

## Detailed Description

The MAX22216/MAX22217 integrate four programmable 36V Half-Bridges. It is primarily intended to drive inductive loads such as on-off solenoid valves, DC motors, proportional valves, bi-stable valves, relays, etc. The MAX22216 is capable of up to  $3.2A_{FS}$  per half-bridge, whereas the MAX22217 is capable of up to  $1A_{FS}$  per half-bridge. The MAX22216/MAX22217 operate from  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  ambient temperature.

The MAX22216/MAX22217 half-bridges support two different use cases. In the first case, configuration settings can be entered through a serial peripheral interface (SPI) and can be changed any time. Alternatively, settings can be stored into one-time programmable (OTP) registers, which are loaded at power-up. This enables stand-alone operations. Registers are user-programmable. The OTP writing procedure must be executed in a factory under well-controlled temperature and voltage conditions.

Both high-side and low-side single-ended drive operations are supported to accommodate multiple load requirements.

Pairs of half-bridges can also be configured to drive loads in a bridge-tied load (BTL) configuration. Typical examples are proportional solenoid valves, bi-stable valves, or DC motors.

Since settings are completely independent, different types of loads can be driven simultaneously from the same MAX22216/MAX22217 devices. For instance, two single-ended controlled valves and one bi-stable valve in full-bridge configuration can be driven from the same MAX22216/MAX22217.

Channel parallelization is also supported to increase the current capability. For maximum flexibility, two, three, or all four half-bridges can be connected in parallel, resulting in 2X, 3X, and 4X current capability.

Both voltage and current control schemes are supported together with mixed modes.

In voltage mode, two regulation methods are supported and can be configured independently for each drive channel.

- In VDR\_DUTY, the user sets the target duty cycle. In this mode, the actual voltage applied to the load directly depends on the  $V_M$  voltage supply.

- In VDR Mode (VDRnVDRDUTY), the user sets the target voltage to the load. An internal circuitry senses the supply voltage and compensates the output duty cycle to get the desired voltage.

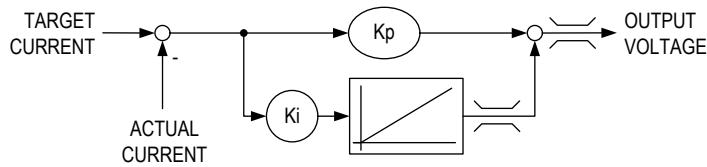

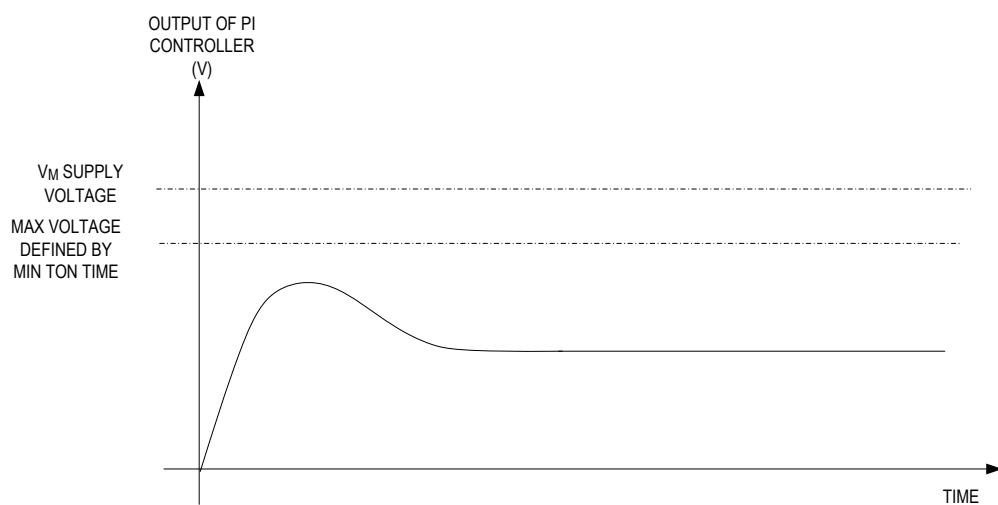

In current mode (CDR mode), the output current is controlled. The current is internally sensed and fed back to the controller for accurate closed-loop regulation. Proportional and Integral gains can be configured to optimize steady-state error and dynamic performances. The reference current in CDR mode is determined by the resistor connected to the  $I_{REF}$  pin. For this reason, an accurate  $12\text{k}\Omega$  resistor must be connected between pin  $I_{REF}$  and GND.

The MAX22216/MAX22217 integrate functions aimed at optimizing solenoid and DC motor drive control, such as:

- Multi-level drive control method (excitation and hold drive with programmable excitation time), resulting in power savings and optimal drive of solenoid valves.

- Programmable voltage/current ramps (RAMP) smooth the activation/deactivation of the valves and hence reduce acoustic noise.

- Programmable dither (DITH) to counteract the effects of stiction and hysteresis by superimposing a small ripple over the DC level.

- A DC motor controller in which the motor is driven in voltage drive mode, the inrush and stall current being limited by an internal limiter circuit.

- A programmable demagnetization voltage (DC\_H2L) to ensure accurate and safe control of the demagnetization current (BTL configuration only).

Advanced diagnostic functions are also available to improve system reliability and enable predictive maintenance. In particular, the device features:

- Detection of plunger movement (DPM) aims to detect the movement of the plunger during the excitation phase and report a fault if the plunger gets stuck.

- An inductance measurement circuitry that can be used to detect the status of ON/OFF solenoid valves.

- Reaction time and travel time measurements for diagnostic and predictive maintenance.

- Open-load detection (OL).

- Real-time current monitoring through serial interface (SPI).

Finally, the MAX22216/MAX22217 feature a full set of protections, including overcurrent protection (OCP),

overtemperature protection (OVT), and undervoltage lockout (UVM). Whenever the fault is detected and if it is not masked, the fault indicator pin is asserted, and fault information is logged into a dedicated register.

The main differences between MAX22216 and MAX22217 are the output current rating and resistance, and channel current measurement. These differences are explained in the [Electrical Characteristics](#), but as a general overview of the current measurement, they have different  $K_{CDR}$  and only the MAX22216 has a sense scaling factor (SNSF) (for MAX22217 you can assume an SNSF of 1 in all formulas related to current measurements).

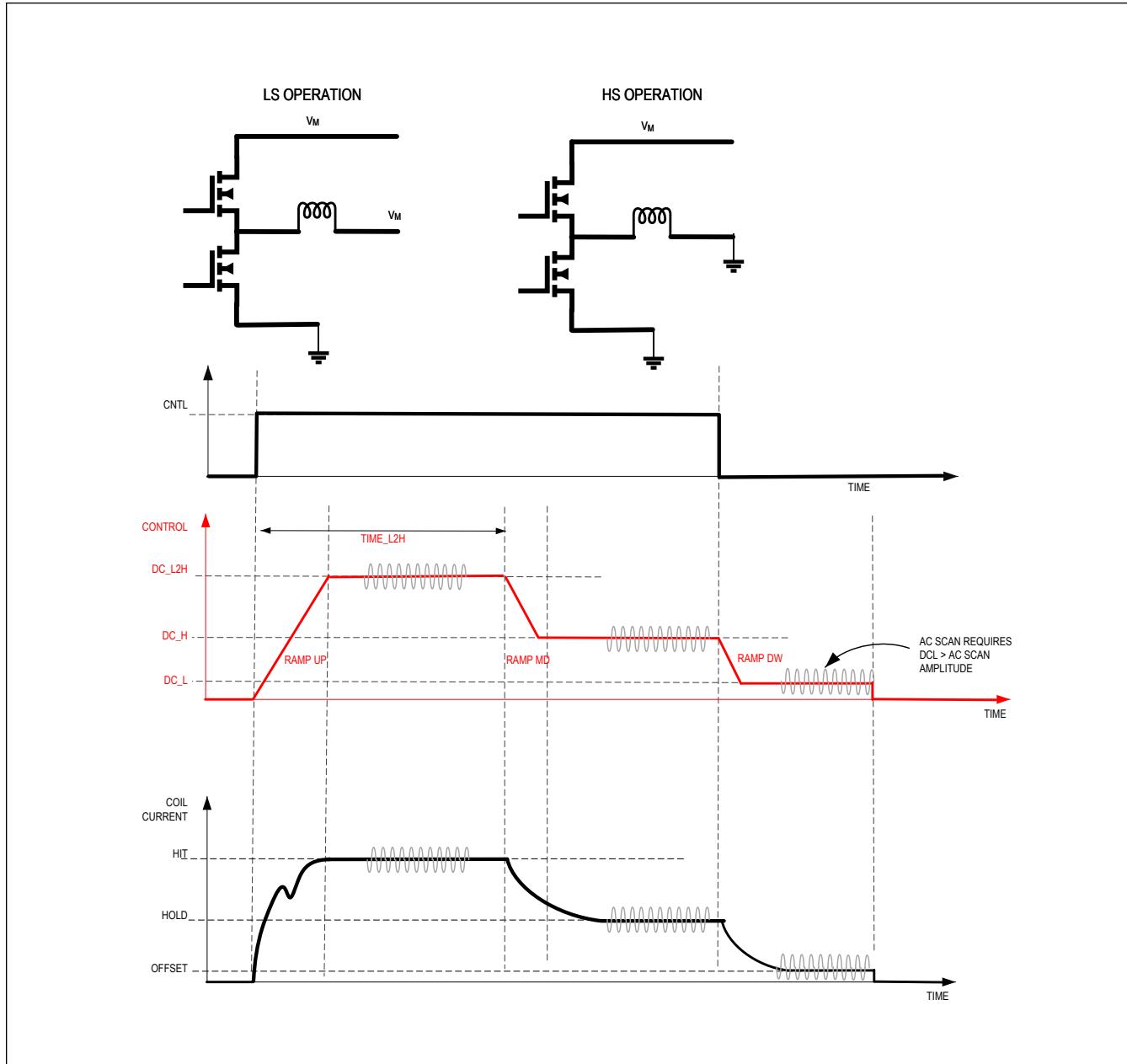

## OPERATING MODES OVERVIEW

### Single-Ended Operation

In this configuration, the load is driven in single-ended mode, with the other terminal connected to the positive rail (low-side drive configuration) or to GND (high-side configuration).

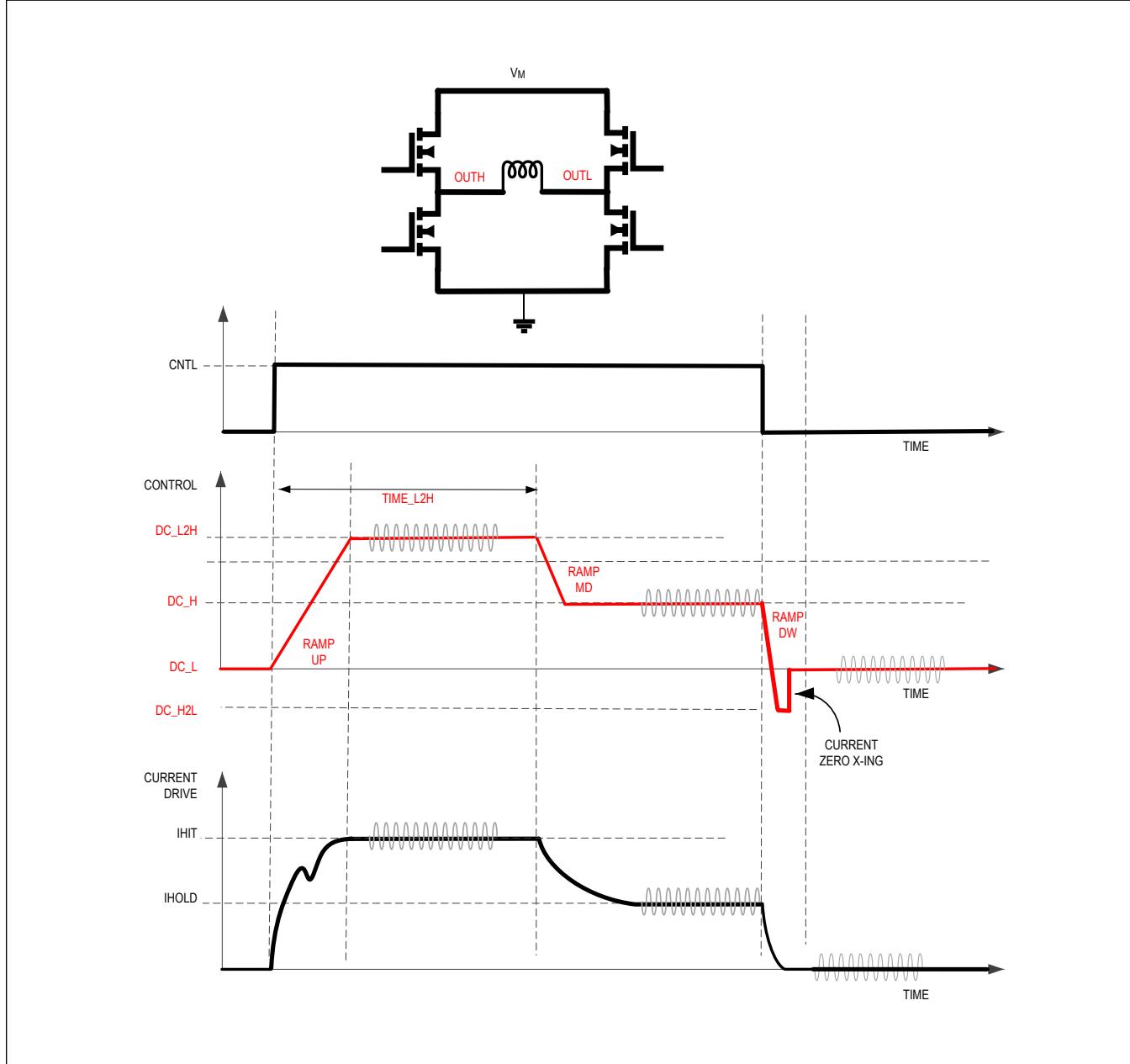

Figure 1. Single-Ended Configuration

[Figure 1](#) shows a typical multilevel drive sequence in single-ended mode. The CNTL signal (namely either the logic input or the corresponding bit in the control register) activates/deactivates the solenoid as shown in [Figure 1](#).

The following parameters are user configurable either with SPI (SPI-based use case) or with OTPs (Stand-alone use case) (see the Register Map section).

#### Low-Side/High-Side Drive Settings

- Excitation High Level: **DC\_L2H[15:0]**

- Hold Level: **DC\_H[15:0]**

- Low Level: **DC\_L[15:0]** Low-level voltage setting is mainly intended for inductance measurement (AC scan)

- Excitation Time: **TIME\_L2H[15:0]**

- Energizing/de-energizing Ramp slope: **RAMP[7:0]**

- AC Scan/Dither Amplitude and Frequency (**U\_AC\_SCAN[14:0]** and **F\_AC\_SCAN[11:0]** global for all the channels)

DC levels settings may refer to voltages, duty cycles, or currents, depending on the desired control strategy. Mixed modes (for instance, DC\_L2H in voltage mode and DC\_H in current mode) are supported too.

### Bridge-Tied Load Operation (Full Bridge)

Figure 2. Bridge-Tied Load Configuration

[Figure 2](#) shows a typical multilevel drive sequence for a bridge-tied load solenoid (Bi-stable valves, proportional valves,

etc.). The CNTL signal (namely the logic input or the corresponding bit in the control register) activates/deactivates the solenoid as shown in [Figure 2](#).

The following parameters are user configurable either with SPI (a SPI-based use case) or with OTPs (a stand-alone use case) (see the Register Map section).

#### Bridge-Tied Load Drive Settings

- Excitation High Level: **DC\_L2H[15:0]**

- Hold Level: **DC\_H[15:0]**

- Demagnetization Voltage: **DC\_H2L[15:0]**. It allows to demagnetize the coil by reverting the drive voltage. To avoid inverting the current, DC\_H2L is automatically de-asserted once the coil current approaches zero. DC\_H2L is global for all the channels.

- Low Level: **DC\_L[15:0]** Low-level voltage (normally set to zero)

- Excitation Time: **TIME\_L2H[15:0]**

- Energizing/de-energizing Ramp Slope: **RAMP[7:0]**

- AC Scan/Dither Amplitude and Frequency: (**U\_AC\_SCAN[14:0]** and **F\_AC\_SCAN[11:0]**) global for all the channels.

With the exception of the demagnetization level (DC\_H2L), which is programmable in voltage mode only, all the DC level settings may refer to voltages, duty cycles, or currents depending on the desired control strategy. Mixed modes (for instance, DC\_L2H in voltage mode and DC\_H in current mode) are supported too.

## DC Motor Drive

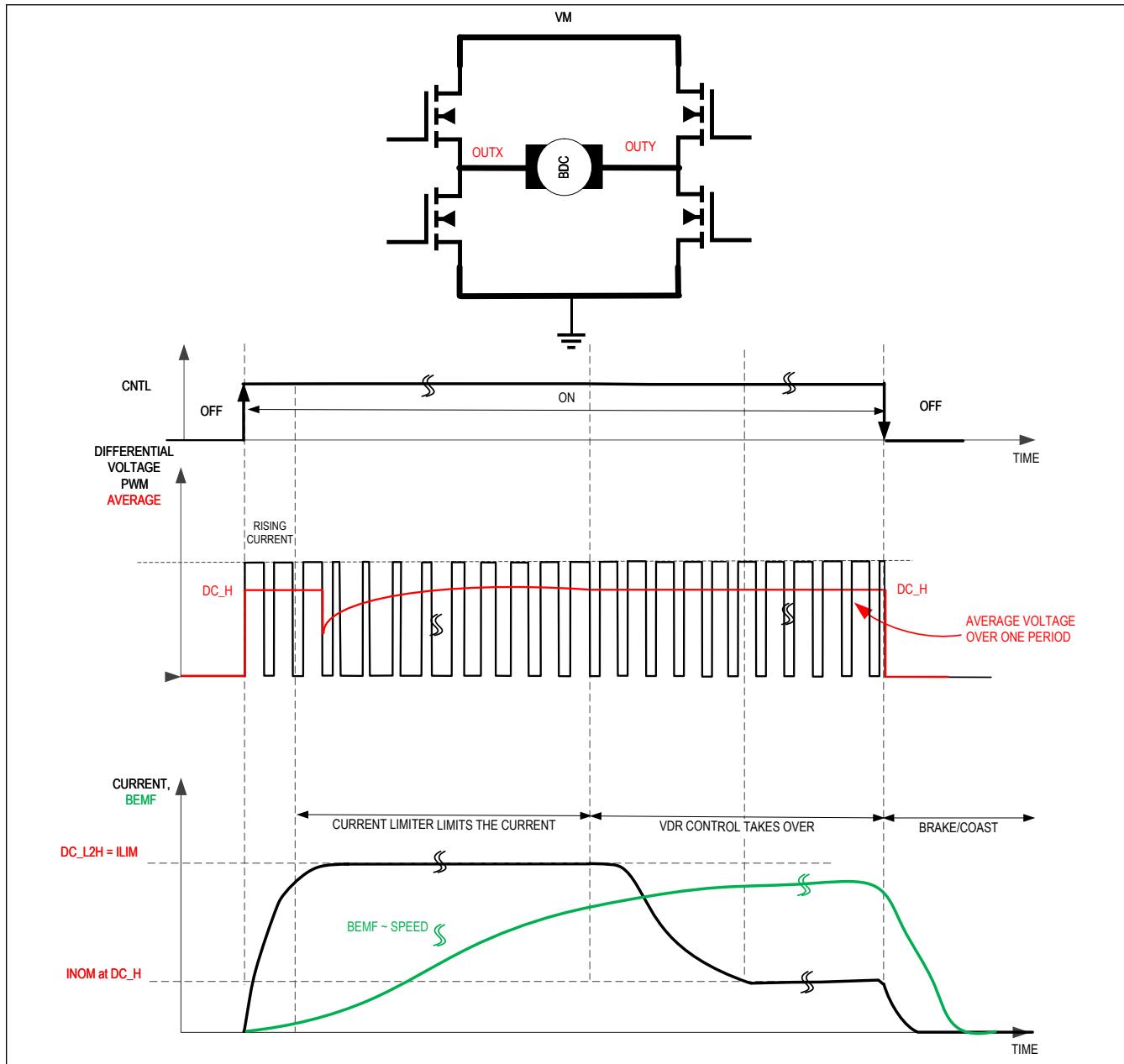

Figure 3. DC Motor

Figure 3 shows the MAX22216/MAX22217 drive signals with reference to a bidirectional DC motor use case (similar drive methods can be implemented for a unidirectional DC motor drive). When the CNTL signal is applied (either from the logic input or via SPI), the controller applies the nominal voltage levels (DC\_H) first. If the inrush current during start-up exceeds the programmable current limiter threshold (DC\_L2H), the current limiter takes over by reducing the PWM output voltage and effectively limiting the inrush current to a safe level. At the nominal speed of the motor, the BEMF limits the current so that the nominal voltage (DC\_H) is automatically applied.

Note that the current limiter is always enabled. In particular, whenever a stall occurs, the limiter limits the stall current to a safe value for the motor and the driver. Once the current exceeds the current limit defined by the DC\_L2H register, the loop reduces the voltage applied to the motor, effectively limiting the current to the desired safe value.

The following parameters are user configurable:

#### Brushed DC Motor Settings

- DC Motor Drive Mode: **CTRL\_MODE[1:0] = 10**

- Current Limiter Threshold: **DC\_L2H[15:0]**

- Drive Voltage Level: **DC\_H[15:0]**

- Brake Current Level: **TIME\_L2H[15:0]**

The MAX22216/MAX22217 feature a current limiter for the motor brake current. This function enables the fastest deceleration of the motor given the overcurrent protection limitations of the device. See the [Brake Current Limiter Function](#) section for further details. Due to the way the output PWM is created, the actual output frequency is double the set F\_PWM. Also, the sine wave generator affects this operating mode only by adding noise at the HiZ state.

DC motor drive can also be used in single-ended mode, but the output will be affected by the CDRs MIN\_T\_ON (LS will have a minimum voltage and HS will have a maximum voltage), and the BRAKE is not functional.

## FUNCTIONAL DESCRIPTION

### MAX22216/MAX22217 SPI or OTP Configuration

As shown in the [OPERATING MODES](#) section, the MAX22216/MAX22217 is a highly configurable device that supports different applications and use cases.

The configuration settings can be input into the MAX22216/MAX22217 in two different ways: through SPI-configuration (Mode 0 or Mode 3) or through OTP-configuration.

In SPI-configuration, volatile registers must be written through a serial peripheral interface (SPI) after power up.

In OTP-configuration, the user writes one-time programmable (OTP) registers whose content is used as the default configuration setting at power-up. OTP writing must be done in a controlled test setup in the factory. When OTP-configuration is used, the MAX22216/MAX22217 can operate in stand-alone mode with minimal control signals from outside.

Further details are available in the [HOW TO CONFIGURE THE MAX22216/MAX22217](#) section.

### Enable Logic Input (ENABLE)

The enable pin is a  $V_M$ -rated logic input pin.

Drive the ENABLE logic low to disable the device. This corresponds to the lowest power consumption for the device.

Drive the ENABLE logic high to enable the device. When enabled, the ENABLE pin must be held high for at least TEN to complete the power-up sequence and prevent the MAX22216/MAX22217 from entering unpredictable statuses.

A pulldown resistor ensures the MAX22216/MAX22217 is disabled if the Enable pin is not actively driven.

In stand-alone operating mode, the ENABLE pin can possibly be externally connected to the positive rail ( $V_M$ ). This way, the solenoid valve can be activated/deactivated by simply powering up/down the device (see the [V\\_M Switching Stand-Alone](#) section).

### Nap Mode and ACTIVE Bit

The ACTIVE bit in the GLOBAL\_CFG register activates/deactivates the MAX22216/MAX22217. When ACTIVE = "0" and ENABLE is logic high, the device is in Nap Mode. Power consumption is minimized (see the [Electrical Characteristics](#) table), the sequencer is disabled, and driver outputs are tri-stated. In SPI-based applications, this corresponds to the default condition at power-up. To enter in normal operation, the ACTIVE bit must be set after the device configuration.

In an OTP-based application, this bit must be programmed high to enable stand-alone operations.

**V<sub>IO</sub> Pin Description (V<sub>IO</sub>)**

The V<sub>IO</sub> voltage is the reference for logic inputs and output signals. The V<sub>IO</sub> pin can be configured by writing two bits in the STATUS\_CFG[15:0] register.

EN\_LDO is the enable bit of the internal regulator.

If EN\_LDO = "0" (default), the V<sub>IO</sub> must be provided from the outside, and V<sub>IO</sub> is a supply voltage input pin.

If EN\_LDO = "1", then an internal linear regulator is turned on and the V<sub>IO</sub> pin becomes an output (settable at 3.3V or 5V).

In SPI-based applications, the V<sub>IO</sub> pin is normally configured as an input and connected to the voltage supply of the external controller to enable communication between the MAX22216/MAX22217 and the controller.

In OTP-based applications (stand-alone mode) in which the SPI is not used and wiring must be minimized, the internal linear regulator can be enabled to supply the internal I/O circuitry. The regulator output voltage can be set either at 3.3V or 5V, depending on the selection of the V5\_nV3 bit. The regulator can only be activated via the OTP programming functionality and is available after a reboot of the part.

**CNTL Pin and CNTL Bits**

As shown in [OPERATING MODES OVERVIEW](#), a change of the status of the CNTL pin or of the CNTL bit in the STATUS register initiates and ends the sequence (with the exception of the V<sub>M</sub> switching stand-alone control, in which the supply voltage itself is used as a command signal; see the [V<sub>M</sub> Switching Stand-Alone](#) section).

The polarity of the CNTL pin can be changed with the CNTL\_POL bit in the GLOBAL\_CFG configuration register, this does not affect the polarity of the CNTL bits. Set CNTL\_POL = "0" for positive polarity (CNTL is active high). Set CNTL\_POL = "1" for negative polarity (CNTL is active low). In the special case of using CNTL\_POL = "1" together with a full-bridge configuration, the CNTL pins will not change polarity, but they will change the control channel. For example, the CNTL0 pin will control CH1 output, and the CNTL1 pin will control CH0. The same applies for CH2 and CH3 pairs. As this setting affects only the CNTL pins, all the other settings are the same.

CNTL bit in the STATUS register and CNTL pins are in or-ing configuration. If either the bit or the input signal is active, then the sequencer is enabled. This also means that once the channel is active using one method, it cannot be turned off using the other control method. If the MAX22216/MAX22217 are controlled via SPI, then the CNTL pins must be set as inactive (it is recommended to connect CNTL logic pins to GND to prevent spurious triggering by noise).

Vice versa, if the MAX22216/MAX22217 are controlled only via logic inputs CNTL, then the CNTL bits must be set as inactive (default state).

**Hardware Configuration**

The MAX22216/MAX22217 provide flexibility. The channel hardware configuration bits CHS[3:0] in the GLOBAL\_CFG register must be set to match the hardware configuration of the half bridge of the MAX22216/MAX22217.

Maximum current can be increased by using a parallel half- or full-bridge configuration. As there is no connection between the channels inside the IC, it has to be done on the PCB. A pair of channels can also be configured in full-bridge mode to drive the load differentially (bridge-tied load). [Table 1](#) summarizes all possible hardware configurations. (HB = Half Bridge, FB = Full Bridge).

**Table 1. Hardware Configuration**

| CHS | SUPPORTED CONFIGURATIONS               | HARDWARE SETTINGS          |

|-----|----------------------------------------|----------------------------|

| 0x0 | 4x Independent half-bridges (HB)       | OUT0, OUT1, OUT2, OUT3     |

| 0x1 | 3x Parallel HBs + 1x Independent HB    | OUT0 = OUT1 = OUT2, OUT3   |

| 0x2 | 2x Parallel HBs + 2x Independent HBs   | OUT0 = OUT1, OUT2, OUT3    |

| 0x3 | 2x Parallel HBs + 2x Parallel HBs      | OUT0 = OUT1, OUT2 = OUT3   |

| 0x4 | 4x Parallel HBs                        | OUT0 = OUT1 = OUT2 = OUT3  |

| 0x5 | 2x Independent Full Bridges (FB)       | OUT0 vs OUT1, OUT2 vs OUT3 |

| 0x6 | 1x Independent FB + 2x Independent HBs | OUT0 vs OUT1, OUT2, OUT3   |

| 0x7 | 1x Independent FB + 2x Parallel HB     | OUT0 vs OUT1, OUT2 = OUT3  |

**Table 1. Hardware Configuration (continued)**

|     |                |                            |

|-----|----------------|----------------------------|

| 0x8 | 1x Parallel FB | OUT0 = OUT1 vs OUT2 = OUT3 |

|-----|----------------|----------------------------|

When channels are parallelized, the MAX22216/MAX22217 uses the configuration settings of the channel with a lower channel index. For instance, for the configuration 0x3 in [Table 1](#), the configuration settings of channel “0” and channel “2” control the parallelized half bridges, whereas the configuration settings of channel “1” and channel “3” are ignored.

[Table 2](#) and [Table 3](#) summarize the active control registers (CFG\_) and the active command signal (CNTL\_) for each Hardware Configuration. The configuration registers store all the parameters that are used by the sequencer (see the [OPERATING MODES](#) section), plus other configuration parameters explained in the following paragraphs. Each CFG is controlled by the specific CNTL channel (CFG\_0 is controlled by CNTL0), and it controls the output based on channel configuration.

The CNTL signals enable (CNTL = 1) or disable (CNTL = 0) the corresponding channels, as shown in [Table 2](#).

The enable/disable signals can be either hardware-based (logic I/Os) or software-based (CNTL bits in the GLOBAL\_CTRL register). HW and SW controls are in OR configuration: if either the logic CNTL input or the corresponding bit in the GLOBAL\_CTRL register are logic high, then the channel is enabled. It follows that in SW-based control, the logic input pins must be grounded (logic low). Vice versa, for HW-based control, the control bits must be set to zero (default at power up).

In full-bridge operation, a center-aligned PWM chopping method is used so that the effective PWM frequency is doubled and ripple is minimized. With this technique, a zero voltage across the load corresponds to a 50% duty cycle applied on each side of the bridge-tied load. Moreover, the control signals (CNTLx, CNTLy) determine the configuration registers, as shown in [Table 3](#).

**Table 2. Control Table**

| OUTPUT SETTINGS |                      | ACTIVE CONFIGURATION REGISTER/CONTROL CHANNEL |                             |             |                             |

|-----------------|----------------------|-----------------------------------------------|-----------------------------|-------------|-----------------------------|

| CHS[3:0]        | OUTPUT CONFIGURATION | CH0 OUTPUT                                    | CH1 OUTPUT                  | CH2 OUTPUT  | CH3 OUTPUT                  |

| 0x0             | 4x Independent HB    | CFG_0/CNTL0                                   | CFG_1/CNTL1                 | CFG_2/CNTL2 | CFG_3/CNTL3                 |

| 0x1             | 3x Parallel HBs      | 1x Independent HB                             | CFG_0/CNTL0                 |             | CFG_3/CNTL3                 |

| 0x2             | 2x Parallel HBs      | 2x Independent HBs                            | CFG_0/CNTL0                 | CFG_2/CNTL2 | CFG_3/CNTL3                 |

| 0x3             | 2x Parallel HBs      | 2x Parallel HBs                               | CFG_0/CNTL0                 |             | CFG_2/CNTL2                 |

| 0x4             | 4x Parallel HBs      |                                               | CFG_0/CNTL0                 |             |                             |