## FEATURES

**Gain: 12 dB typical at 10 GHz to 26 GHz**

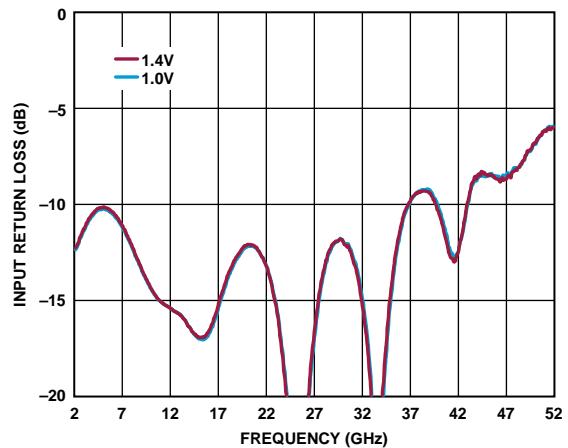

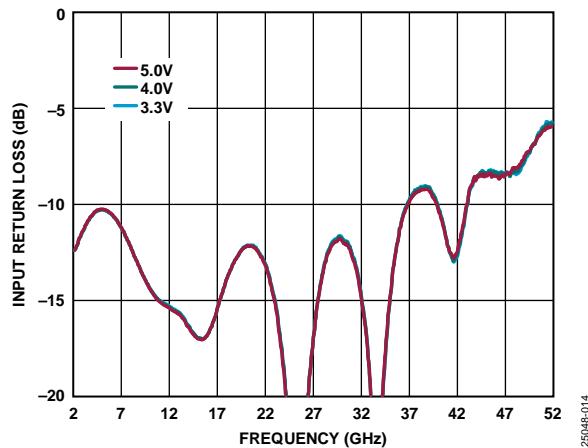

**Input return loss: 14 dB typical at 10 GHz to 26 GHz**

**Output return loss: 16 dB typical at 10 GHz to 40 GHz**

**OP1dB: 17.5 dB typical at 10 GHz to 26 GHz**

$P_{SAT}$ : 21 dBm typical at 10 GHz to 26 GHz

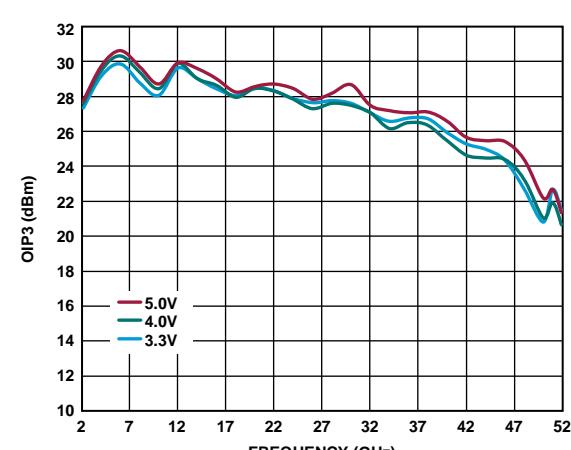

**QIP3: 28.5 dBm typical at 10 GHz to 26 GHz**

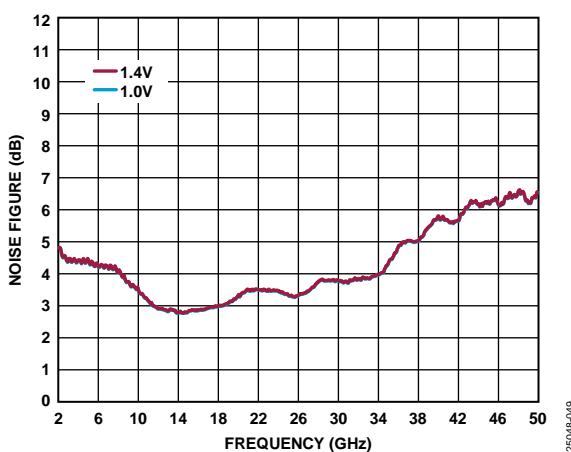

**Noise figure: 3.5 dB typical at 10 GHz**

5 V supply voltage at 85 mA

**5 V supply voltage at 85 mA**

**50 Ω matched input and output**

## APPLICATIONS

## Test instrumentation

## Military and space

## GENERAL DESCRIPTION

The HMC1126ACEZ is a gallium arsenide (GaAs), pseudomorphic high electron mobility transfer (pHEMT), low noise amplifier that operates from 400 MHz to 52 GHz. The HMC1126ACEZ provides 12 dB of typical gain, 28.5 dBm typical output third-order intercept (OIP3), 17.5 dBm typical output power at 1 dB gain compression (OP1dB), and a 3.5 dB typical noise figure at 10 GHz to 26 GHz. The HMC1126ACEZ requires 85 mA from a 5 V supply. All of the typically required

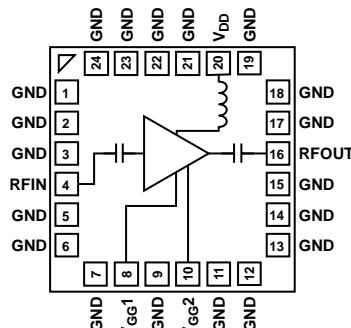

## FUNCTIONAL BLOCK DIAGRAM

Figure 1.

external passive components for operation (ac coupling capacitors and power supply decoupling capacitors) are integrated, which facilitates a small and compact printed circuit board (PCB) footprint.

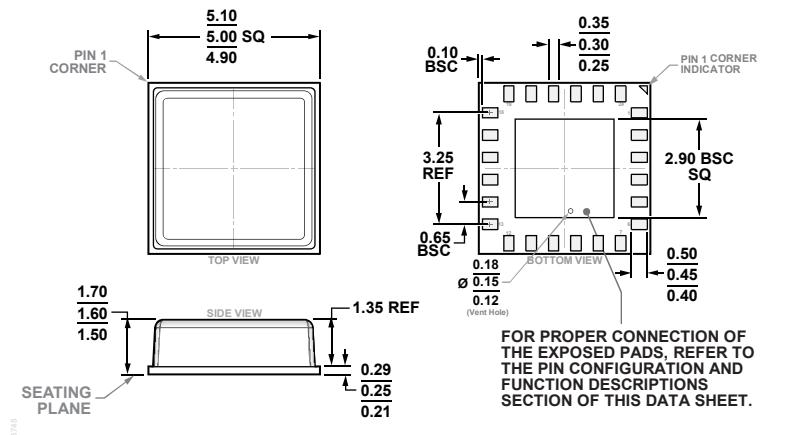

The HMC1126ACEZ is housed in a 5.00 mm × 5.00 mm, 24-terminal chip array small outline no lead cavity (LGA\_CAV) package.

## TABLE OF CONTENTS

|                                             |   |                                                          |    |

|---------------------------------------------|---|----------------------------------------------------------|----|

| Features .....                              | 1 | Pin Configuration and Function Descriptions .....        | 6  |

| Applications .....                          | 1 | Interface Schematics .....                               | 6  |

| Functional Block Diagram .....              | 1 | Typical Performance Characteristics .....                | 7  |

| General Description .....                   | 1 | Theory of Operation .....                                | 15 |

| Revision History .....                      | 2 | Applications Information .....                           | 16 |

| Electrical Specifications .....             | 3 | Power-Up and Power-Down Sequencing .....                 | 16 |

| 400 MHz to 10 GHz Frequency Range .....     | 3 | Biasing the HMC1126ACEZ with the HMC920LP5E .....        | 17 |

| 10 GHz to 26 GHz Frequency Range .....      | 3 | Constant Drain Current Biasing vs. Constant Gate Voltage |    |

| 26 GHz to 40 GHz Frequency Range .....      | 4 | Biasing .....                                            | 19 |

| 40 GHz to 52 GHz Frequency Range .....      | 4 | Outline Dimensions .....                                 | 21 |

| Absolute Maximum Ratings .....              | 5 | Ordering Guide .....                                     | 21 |

| Thermal Resistance .....                    | 5 |                                                          |    |

| Electrostatic Discharge (ESD) Ratings ..... | 5 |                                                          |    |

| ESD Caution .....                           | 5 |                                                          |    |

## REVISION HISTORY

11/2021—Revision 0: Initial Version

## ELECTRICAL SPECIFICATIONS

### 400 MHz TO 10 GHz FREQUENCY RANGE

$T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5 \text{ V}$ ,  $V_{GG2} = 1 \text{ V}$ , and supply current ( $I_{DQ}$ ) = 85 mA, unless otherwise stated. Adjust  $V_{GG1}$  between  $-2 \text{ V}$  and  $0 \text{ V}$  to achieve  $I_{DQ} = 85 \text{ mA}$  typical.

**Table 1.**

| Parameter                            | Min  | Typ   | Max | Unit  | Test Conditions/Comments                                            |

|--------------------------------------|------|-------|-----|-------|---------------------------------------------------------------------|

| FREQUENCY RANGE                      | 0.4  |       | 10  | GHz   |                                                                     |

| GAIN                                 | 10.5 | 12.5  |     | dB    |                                                                     |

| Gain Variation over Temperature      |      | 0.003 |     | dB/°C |                                                                     |

| RETURN LOSS                          |      |       |     |       |                                                                     |

| Input                                |      | 11.5  |     | dB    |                                                                     |

| Output                               |      | 13    |     | dB    |                                                                     |

| OUTPUT                               |      |       |     |       |                                                                     |

| OP1dB                                | 15   | 17.5  |     | dBm   |                                                                     |

| Saturated Output Power ( $P_{SAT}$ ) |      | 20    |     | dBm   |                                                                     |

| OIP3                                 |      | 29    |     | dBm   | Output power ( $P_{OUT}$ ) per tone = 0 dBm with 1 MHz tone spacing |

| Second-Order Intercept (OIP2)        |      | 31    |     | dBm   | $P_{OUT}$ per tone = 0 dBm with 1 MHz tone spacing                  |

| NOISE FIGURE                         |      | 4.0   |     | dB    |                                                                     |

| SUPPLY                               |      |       |     |       |                                                                     |

| $I_{DQ}$                             |      | 85    |     | mA    | Adjust $V_{GG1}$ to achieve $I_{DQ} = 85 \text{ mA}$ typical        |

| $V_{DD}$                             | 3.3  | 5     |     | V     |                                                                     |

### 10 GHz TO 26 GHz FREQUENCY RANGE

$T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5 \text{ V}$ ,  $V_{GG2} = 1 \text{ V}$ , and  $I_{DQ} = 85 \text{ mA}$ , unless otherwise stated. Adjust  $V_{GG1}$  between  $-2 \text{ V}$  and  $0 \text{ V}$  to achieve  $I_{DQ} = 85 \text{ mA}$  typical.

**Table 2.**

| Parameter                       | Min | Typ   | Max | Unit  | Test Conditions/Comments                                     |

|---------------------------------|-----|-------|-----|-------|--------------------------------------------------------------|

| FREQUENCY RANGE                 | 10  |       | 26  | GHz   |                                                              |

| GAIN                            | 10  | 12    |     | dB    |                                                              |

| Gain Variation over Temperature |     | 0.006 |     | dB/°C |                                                              |

| RETURN LOSS                     |     |       |     |       |                                                              |

| Input                           |     | 14    |     | dB    |                                                              |

| Output                          |     | 16    |     | dB    |                                                              |

| OUTPUT                          |     |       |     |       |                                                              |

| OP1dB                           |     | 17.5  |     | dBm   |                                                              |

| $P_{SAT}$                       |     | 21    |     | dBm   |                                                              |

| OIP3                            |     | 28.5  |     | dBm   | $P_{OUT}$ per tone = 0 dBm with 1 MHz tone spacing           |

| OIP2                            |     | 28    |     | dBm   | $P_{OUT}$ per tone = 0 dBm with 1 MHz tone spacing           |

| NOISE FIGURE                    |     | 3.5   |     | dB    |                                                              |

| SUPPLY                          |     |       |     |       |                                                              |

| $I_{DQ}$                        |     | 85    |     | mA    | Adjust $V_{GG1}$ to achieve $I_{DQ} = 85 \text{ mA}$ typical |

| $V_{DD}$                        | 3.3 | 5     |     | V     |                                                              |

**26 GHz TO 40 GHz FREQUENCY RANGE**

$T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5 \text{ V}$ ,  $V_{GG2} = 1 \text{ V}$ , and  $I_{DQ} = 85 \text{ mA}$ , unless otherwise stated. Adjust  $V_{GG1}$  between  $-2 \text{ V}$  and  $0 \text{ V}$  to achieve  $I_{DQ} = 85 \text{ mA}$  typical.

**Table 3.**

| Parameter                       | Min  | Typ  | Max   | Unit        | Test Conditions/Comments                                     |

|---------------------------------|------|------|-------|-------------|--------------------------------------------------------------|

| FREQUENCY RANGE                 | 26   |      | 40    | GHz         |                                                              |

| GAIN                            | 10.5 | 12.5 | 0.007 | dB<br>dB/°C |                                                              |

| Gain Variation over Temperature |      |      |       |             |                                                              |

| RETURN LOSS                     |      |      |       |             |                                                              |

| Input                           |      | 13.5 |       | dB          |                                                              |

| Output                          |      | 16   |       | dB          |                                                              |

| OUTPUT                          |      |      |       |             |                                                              |

| OP1dB                           |      | 16   |       | dBm         |                                                              |

| $P_{SAT}$                       |      | 20   |       | dBm         |                                                              |

| OIP3                            |      | 27   |       | dBm         | $P_{OUT}$ per tone = 0 dBm with 1 MHz tone spacing           |

| NOISE FIGURE                    |      | 4.5  |       | dB          |                                                              |

| SUPPLY                          |      |      |       |             |                                                              |

| $I_{DQ}$                        |      | 85   |       | mA          | Adjust $V_{GG1}$ to achieve $I_{DQ} = 85 \text{ mA}$ typical |

| $V_{DD}$                        | 3.3  | 5    |       | V           |                                                              |

**40 GHz TO 52 GHz FREQUENCY RANGE**

$T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5 \text{ V}$ ,  $V_{GG2} = 1 \text{ V}$ , and  $I_{DQ} = 85 \text{ mA}$ , unless otherwise stated. Adjust  $V_{GG1}$  between  $-2 \text{ V}$  and  $0 \text{ V}$  to achieve  $I_{DQ} = 85 \text{ mA}$  typical.

**Table 4.**

| Parameter                       | Min | Typ  | Max | Unit  | Test Conditions/Comments                                     |

|---------------------------------|-----|------|-----|-------|--------------------------------------------------------------|

| FREQUENCY RANGE                 | 40  |      | 52  | GHz   |                                                              |

| GAIN                            |     | 12   |     | dB    |                                                              |

| Gain Variation over Temperature |     | 0.01 |     | dB/°C |                                                              |

| RETURN LOSS                     |     |      |     |       |                                                              |

| Input                           |     | 7.5  |     | dB    |                                                              |

| Output                          |     | 15   |     | dB    |                                                              |

| OUTPUT                          |     |      |     |       |                                                              |

| OP1dB                           |     | 12.5 |     | dBm   |                                                              |

| $P_{SAT}$                       |     | 17.5 |     | dBm   |                                                              |

| OIP3                            |     | 23.5 |     | dBm   | $P_{OUT}$ per tone = 0 dBm with 1 MHz tone spacing           |

| NOISE FIGURE                    |     | 6    |     | dB    |                                                              |

| SUPPLY                          |     |      |     |       |                                                              |

| $I_{DQ}$                        |     | 85   |     | mA    | Adjust $V_{GG1}$ to achieve $I_{DQ} = 85 \text{ mA}$ typical |

| $V_{DD}$                        | 3.3 | 5    |     | V     |                                                              |

## ABSOLUTE MAXIMUM RATINGS

Table 5.

| Parameter                                                                                                                             | Rating                                        |

|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| $V_{DD}$                                                                                                                              | 6 V                                           |

| Gate Bias Voltage                                                                                                                     |                                               |

| $V_{GG1}$                                                                                                                             | -3 V to 0 V                                   |

| $V_{GG2}$                                                                                                                             |                                               |

| For $V_{DD} = 3.3$ V                                                                                                                  | 0.5 V to 2.5 V                                |

| For $V_{DD} = 4$ V                                                                                                                    | 0.5 V to 3 V                                  |

| For $V_{DD} = 5$ V                                                                                                                    | 1.0 V to 4 V                                  |

| RFIN Power                                                                                                                            | 22 dBm                                        |

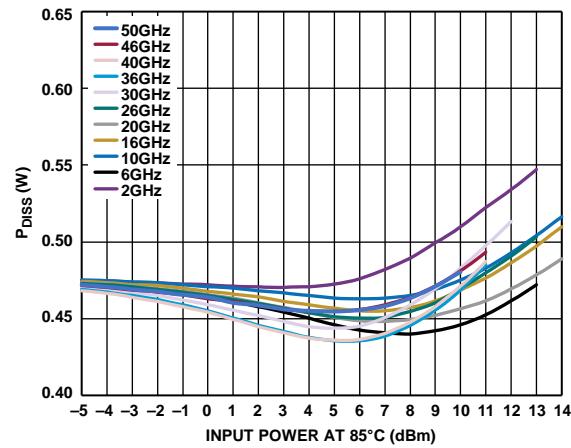

| Continuous Power Dissipation ( $P_{DISS}$ ), $T_A = 85^\circ\text{C}$<br>(Derate 18.4 mW/ $^\circ\text{C}$ Above $85^\circ\text{C}$ ) | 1.66 W                                        |

| Temperature                                                                                                                           |                                               |

| Channel                                                                                                                               | 175 $^\circ\text{C}$                          |

| Peak Reflow (Moisture Sensitivity Level (MSL) 3) <sup>1</sup>                                                                         | 260 $^\circ\text{C}$                          |

| Storage Range                                                                                                                         | -40 $^\circ\text{C}$ to +150 $^\circ\text{C}$ |

| Operating Range                                                                                                                       | -40 $^\circ\text{C}$ to +85 $^\circ\text{C}$  |

| Junction to Maintain 1,000,000 Hours<br>Mean Time to Failure (MTTF)                                                                   | 175                                           |

| Nominal Junction ( $T_A = 85^\circ\text{C}$ , $V_{DD} = 5$ V,<br>$I_{DQ} = 85$ mA)                                                    | 108                                           |

<sup>1</sup> See the Ordering Guide for more information.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL RESISTANCE

Thermal performance is directly linked to system design and operating environment. Careful attention to the PCB thermal design is required.

$\theta_{JC}$  is the channel to case thermal resistance, channel to bottom of die using die attach epoxy.

Table 6. Thermal Resistance

| Package Type         | $\theta_{JC}$ | Unit                      |

|----------------------|---------------|---------------------------|

| CE-24-2 <sup>1</sup> | 54.3          | $^\circ\text{C}/\text{W}$ |

<sup>1</sup>  $\theta_{JC}$  was determined by simulation under the following conditions: the heat transfer is due solely to thermal conduction from the channel, through the ground paddle, to the PCB, and the ground pad is held constant at the operating temperature of 85 $^\circ\text{C}$ .

## ELECTROSTATIC DISCHARGE (ESD) RATINGS

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDDEC JS-001.

Table 7. HMC1126ACEZ, 24-Terminal LGA\_CAV

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | $\pm 250$               | 1A    |

## ESD CAUTION

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

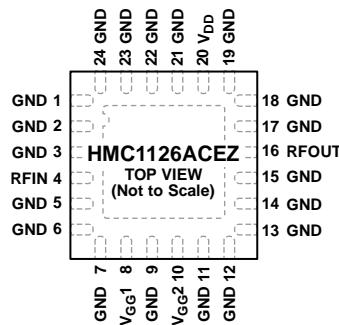

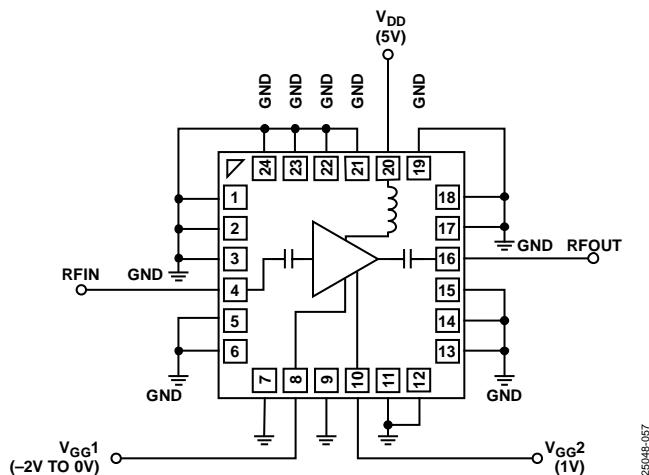

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

NOTES

1. EXPOSED PAD. CONNECT THE EXPOSED PAD TO A GROUND PLANE WITH LOW THERMAL AND ELECTRICAL IMPEDANCE.

25048-002

Figure 2. Pin Configuration

Table 8. Pin Function Descriptions

| Pin No.                                             | Mnemonic         | Description                                                                                                                                                  |

|-----------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3, 5, 6, 7, 9, 11 to 15, 17, 18, 19, 21 to 24 | GND              | Ground. All the ground pins must be connected to a low impedance ground plane. See Figure 7 for the interface schematic.                                     |

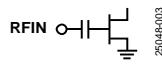

| 4                                                   | RFIN             | RF Input. RFIN is ac-coupled and matched to 50 Ω. See Figure 3 for the interface schematic.                                                                  |

| 8                                                   | V <sub>GG1</sub> | Gate Control 1 for the Amplifier. Adjust V <sub>GG1</sub> to achieve I <sub>DO</sub> = 85 mA. See Figure 6 for the interface schematic.                      |

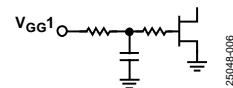

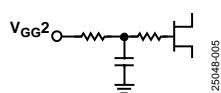

| 10                                                  | V <sub>GG2</sub> | Gate Control 2 for the Amplifier. For nominal operation, apply 1 V to V <sub>GG2</sub> . See Figure 5 for the interface schematic.                           |

| 16                                                  | RFOUT            | RF Output. RFOUT is ac-coupled and matched to 50 Ω. See Figure 4 for the interface schematic.                                                                |

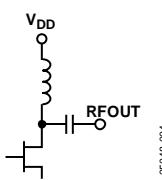

| 20                                                  | V <sub>DD</sub>  | Drain Supply Voltage with Integrated RF Choke. Connect the dc bias to V <sub>DD</sub> to provide I <sub>DO</sub> . See Figure 4 for the interface schematic. |

|                                                     | EPAD             | Exposed Pad. Connect the exposed pad to a ground plane with low thermal and electrical impedance.                                                            |

## INTERFACE SCHEMATICS

Figure 3. RFIN Interface Schematic

Figure 6. V<sub>GG1</sub> Interface SchematicFigure 4. V<sub>DD</sub> and RFOUT Interface Schematic

Figure 7. GND Interface Schematic

Figure 5. V<sub>GG2</sub> Interface Schematic

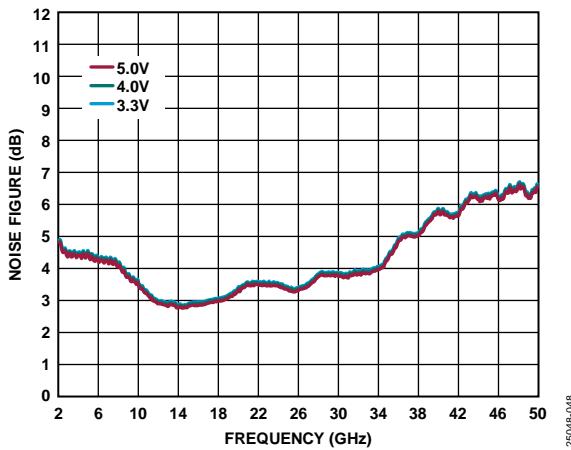

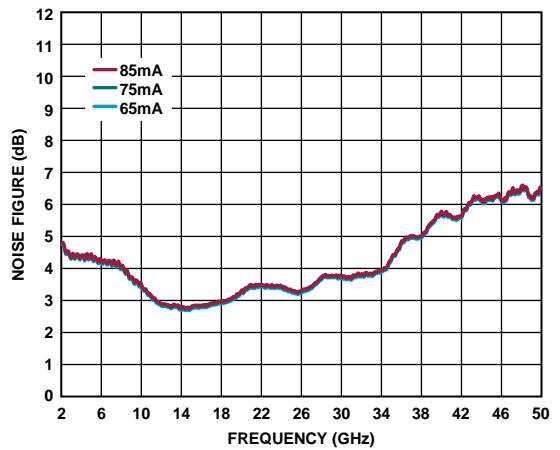

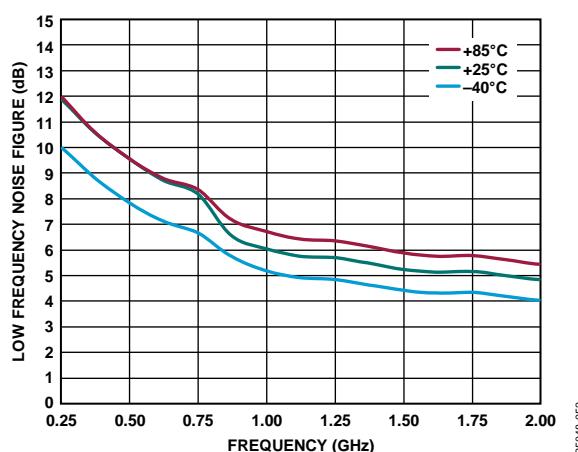

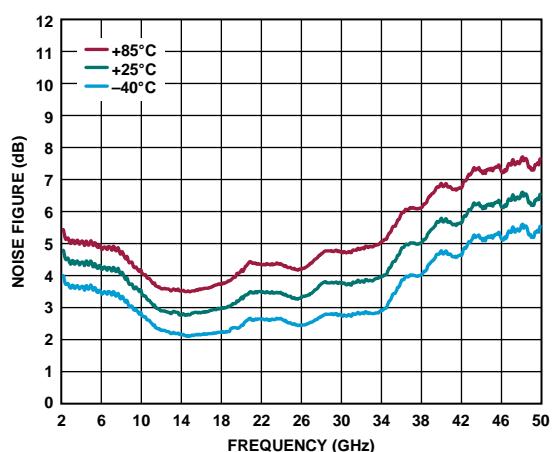

## TYPICAL PERFORMANCE CHARACTERISTICS

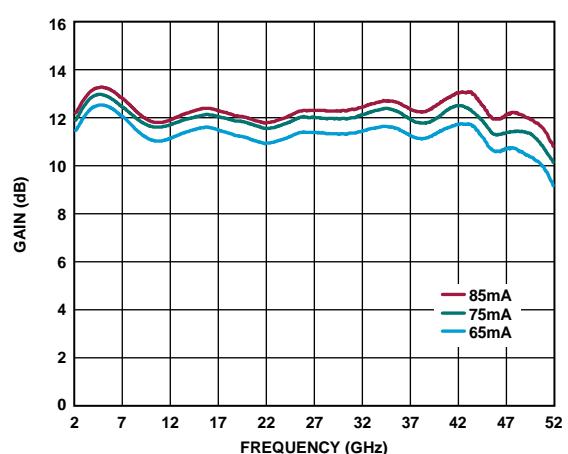

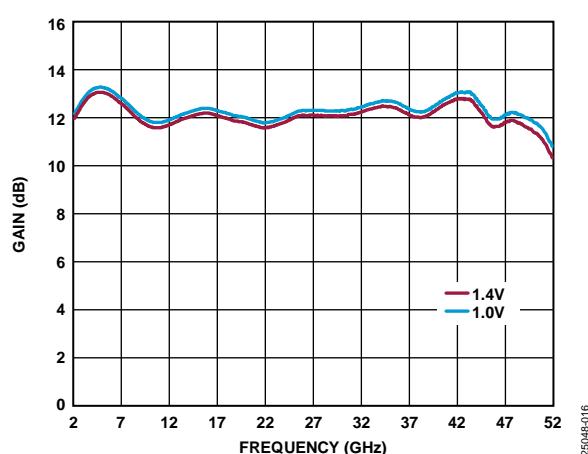

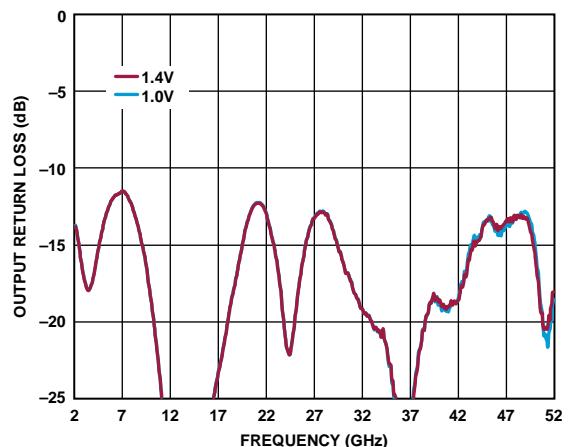

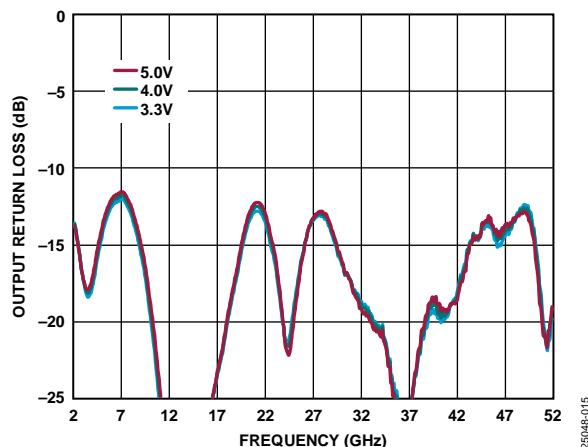

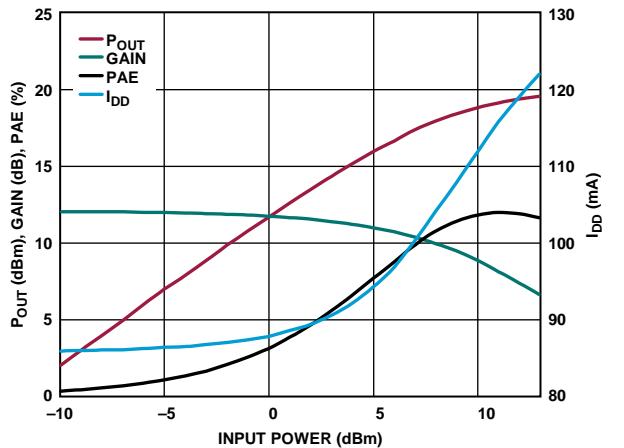

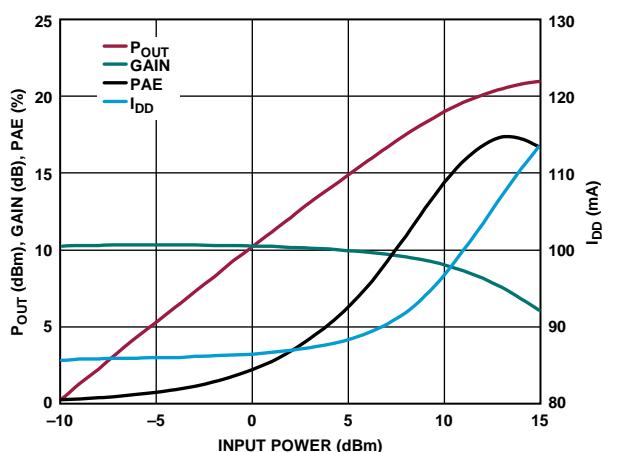

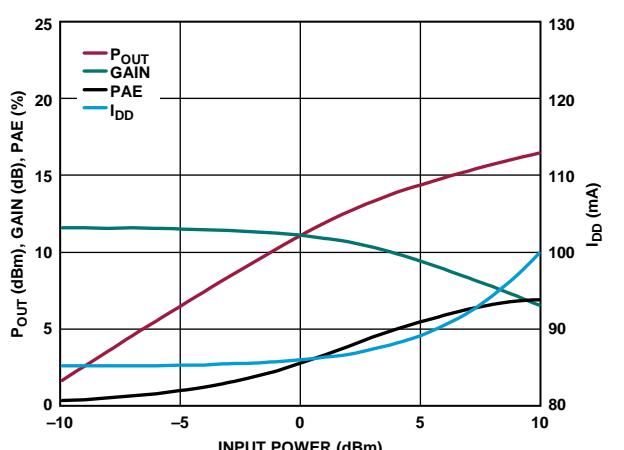

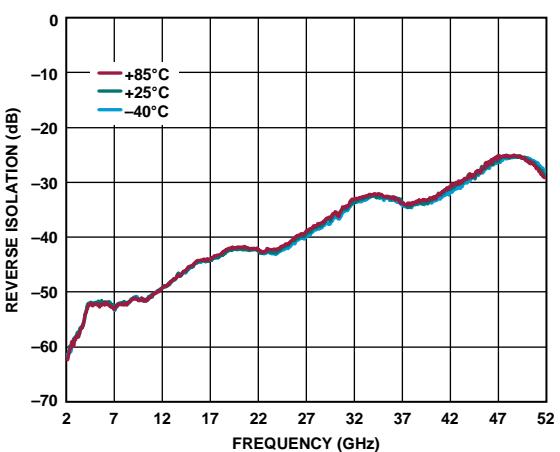

$I_{DQ}$  is the drain current without the RF signal applied, and  $I_{DD}$  is the drain current with the RF signal applied.

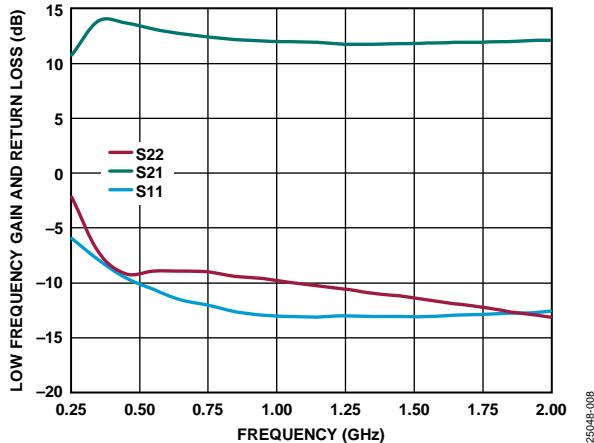

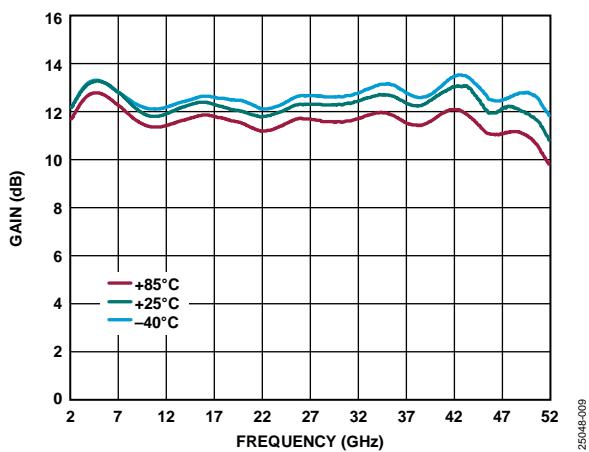

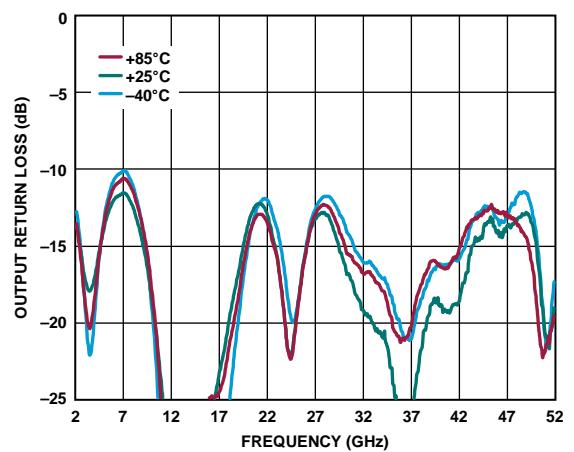

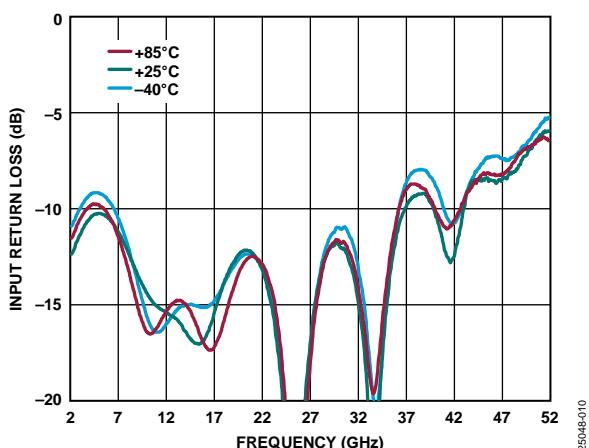

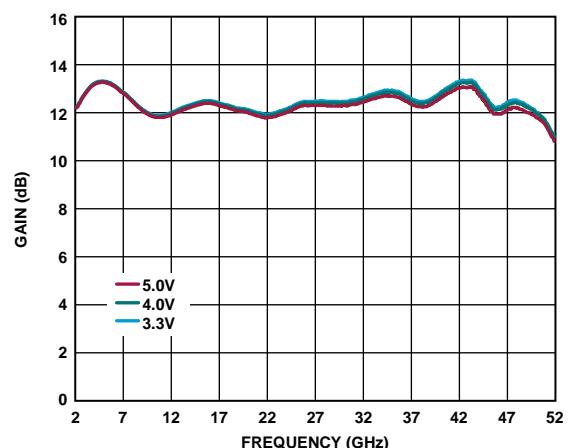

25048-008

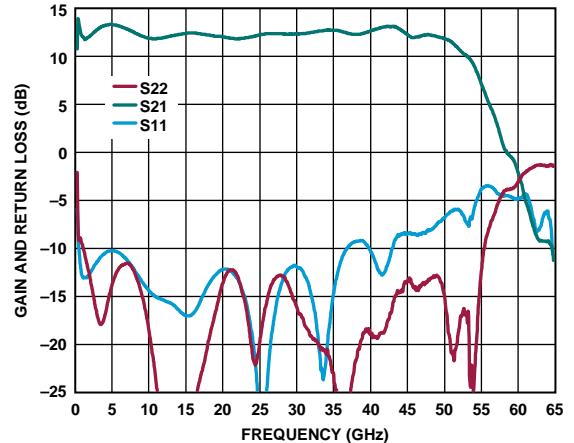

25048-011

25048-009

25048-012

25048-010

25048-013

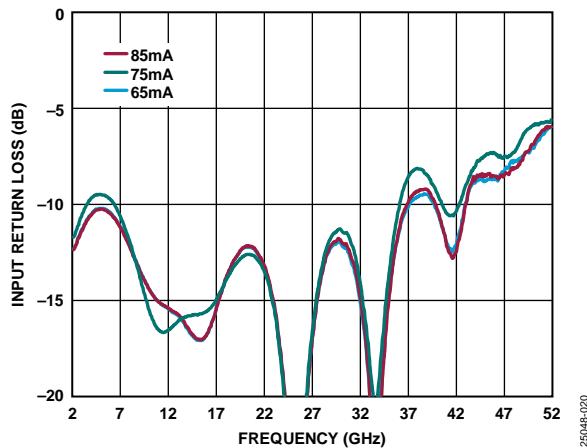

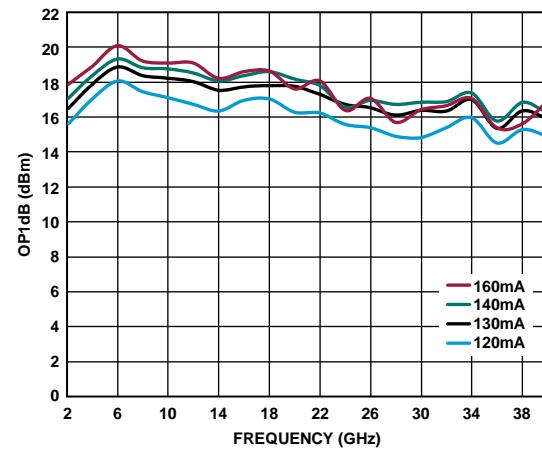

25048-020

Figure 20. Input Return Loss vs. Frequency at Various  $I_{DQ}$  Currents,  $V_{DD} = 5\text{ V}$ ,  $V_{GG2} = 1\text{ V}$

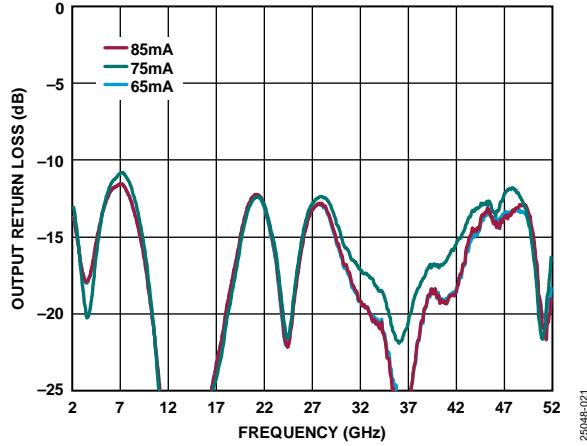

25048-021

Figure 21. Output Return Loss vs. Frequency at Various  $I_{DQ}$  Currents,  $V_{DD} = 5\text{ V}$ ,  $V_{GG2} = 1\text{ V}$

25048-024

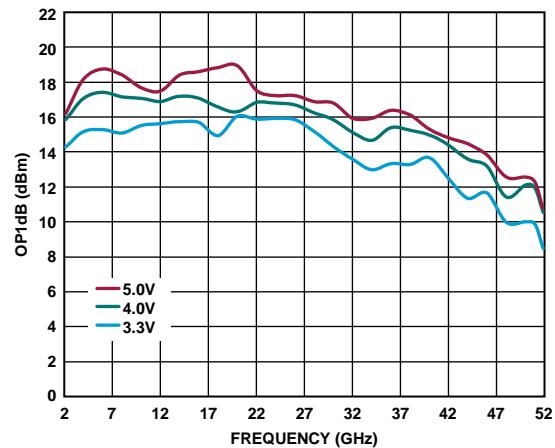

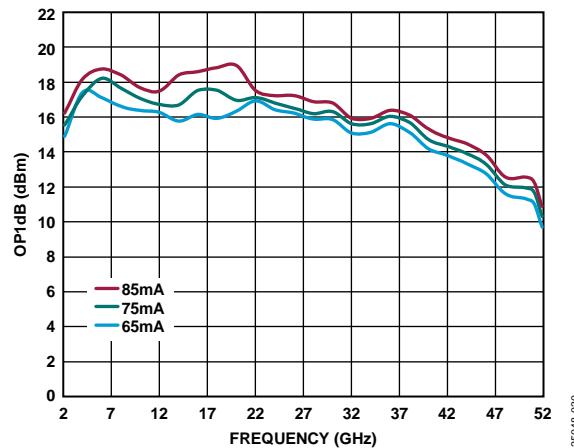

Figure 23. OP1dB vs. Frequency at Various  $V_{DD}$  Voltages,  $I_{DQ} = 85\text{ mA}$ ,  $V_{GG2} = 1\text{ V}$

25048-028

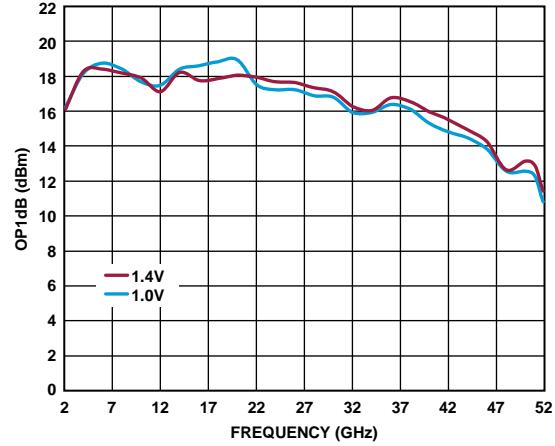

Figure 24. OP1dB vs. Frequency at Various  $V_{GG2}$  Voltages,  $V_{DD} = 5\text{ V}$ ,  $I_{DQ} = 85\text{ mA}$

25048-022

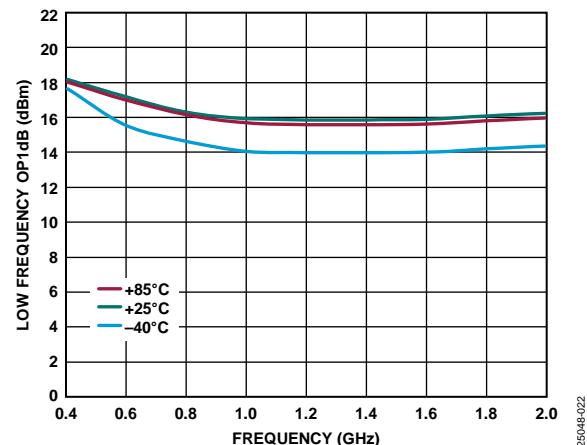

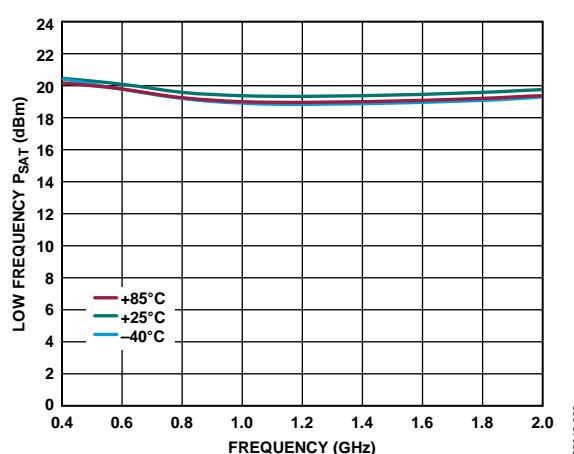

Figure 22. Low Frequency OP1dB vs. Frequency at Various Temperatures,  $V_{DD} = 5\text{ V}$ ,  $I_{DQ} = 85\text{ mA}$ ,  $V_{GG2} = 1\text{ V}$

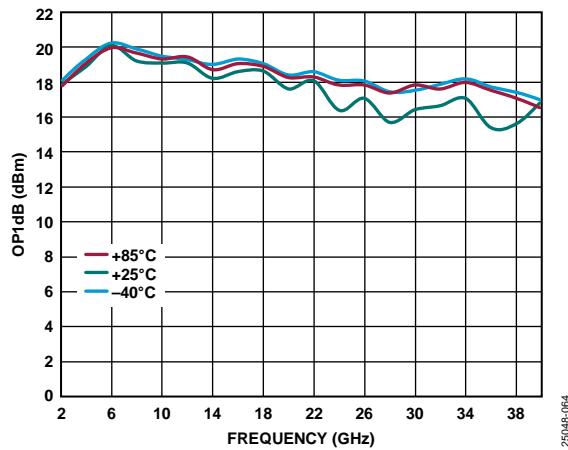

25048-025

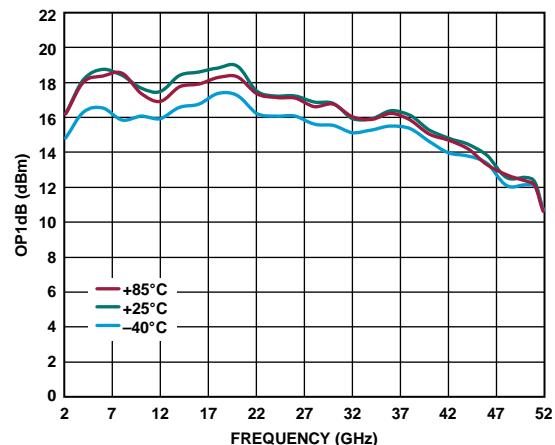

Figure 25. OP1dB vs. Frequency at Various Temperatures,  $V_{DD} = 5\text{ V}$ ,  $I_{DQ} = 85\text{ mA}$ ,  $V_{GG2} = 1\text{ V}$

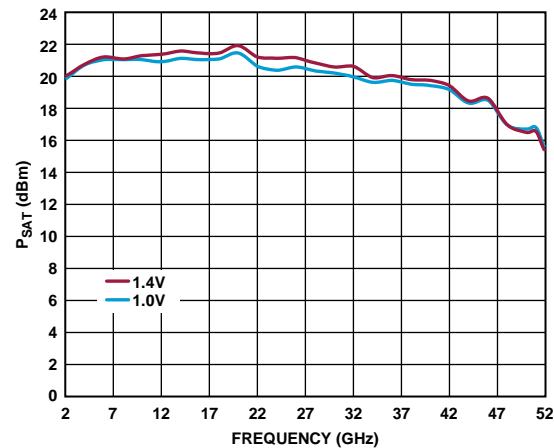

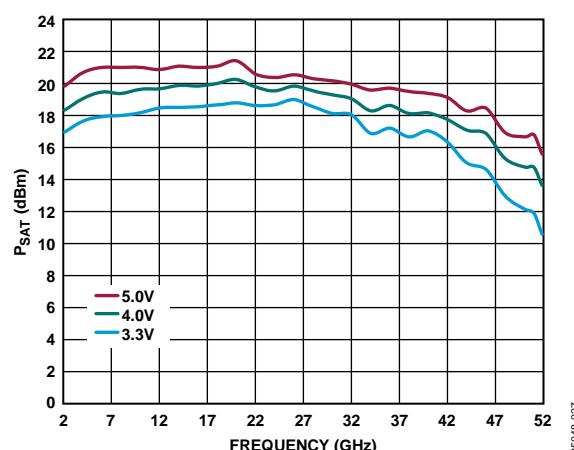

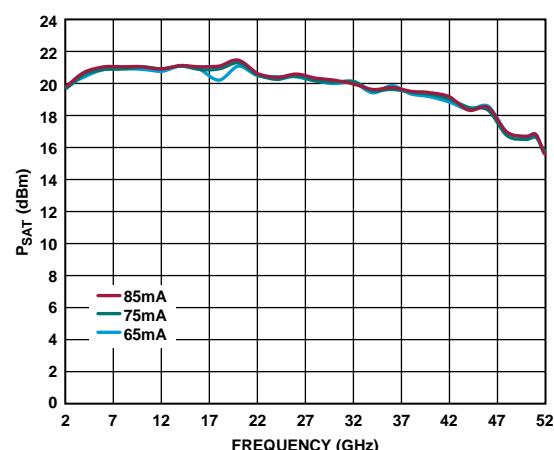

25048-030

25048-029

25048-027

25048-031

25048-023

25048-026

25048-032

25048-033

25048-034

25048-035

25048-036

25048-037

25048-054

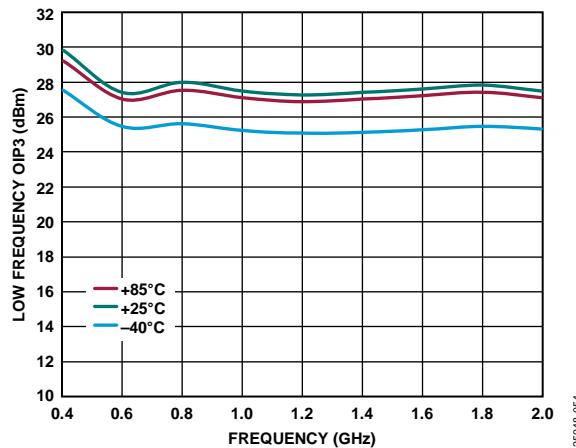

Figure 38. Low Frequency OIP3 vs. Frequency at Various Temperatures,  $V_{DD} = 5 \text{ V}$ ,  $I_{DQ} = 85 \text{ mA}$ ,  $V_{GG2} = 1 \text{ V}$

25048-039

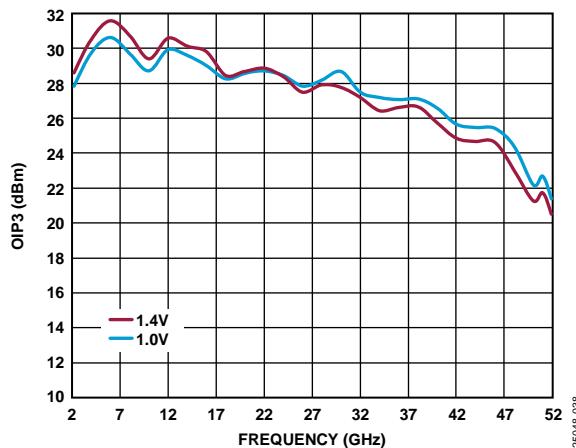

Figure 39. OIP3 vs. Frequency at Various  $V_{GG2}$  Voltages,  $V_{DD} = 5 \text{ V}$ ,  $I_{DQ} = 85 \text{ mA}$

25048-039

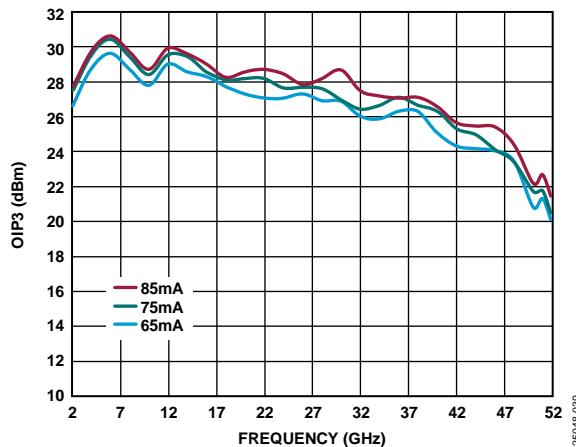

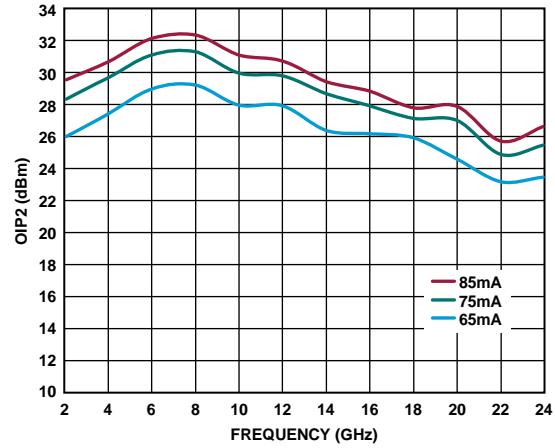

Figure 40. OIP3 vs. Frequency at Various  $I_{DQ}$  Currents,  $V_{DD} = 5 \text{ V}$ ,  $V_{GG2} = 1 \text{ V}$

25048-036

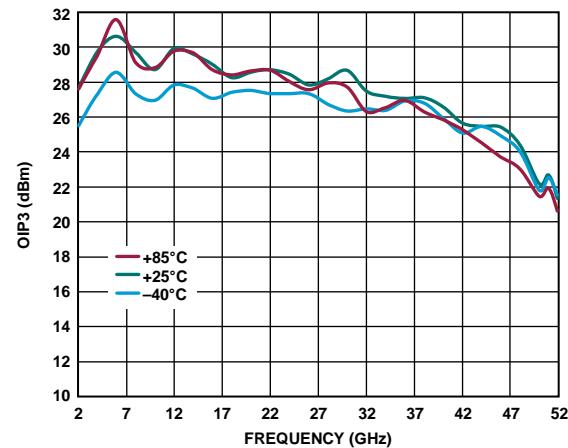

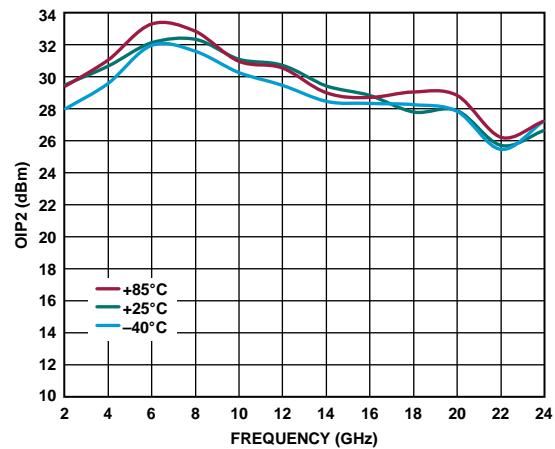

Figure 41. OIP3 vs. Frequency at Various Temperatures,  $V_{DD} = 5 \text{ V}$ ,  $I_{DQ} = 85 \text{ mA}$ ,  $V_{GG2} = 1 \text{ V}$

25048-040

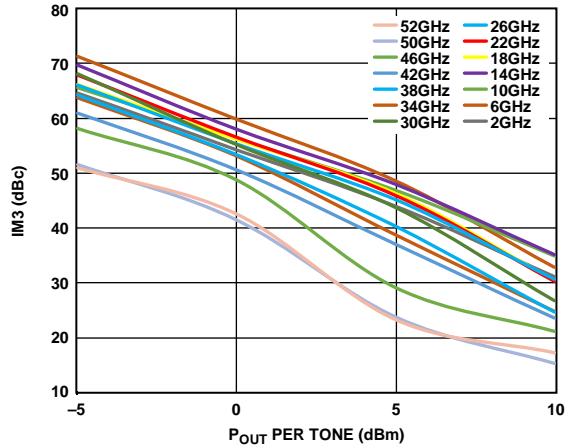

Figure 42. Third-Order Intermodulation (IM3) vs.  $P_{OUT}$  per Tone at Various Frequencies,  $V_{DD} = 3.3 \text{ V}$ ,  $I_{DQ} = 85 \text{ mA}$ ,  $V_{GG2} = 1 \text{ V}$

25048-041

Figure 43. IM3 vs.  $P_{OUT}$  per Tone at Various Frequencies,  $V_{DD} = 4 \text{ V}$ ,  $I_{DQ} = 85 \text{ mA}$ ,  $V_{GG2} = 1 \text{ V}$

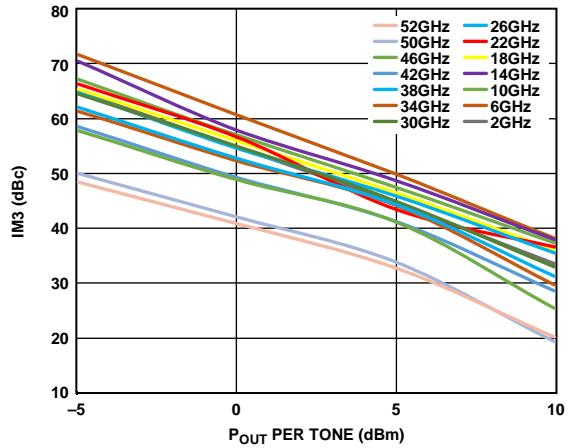

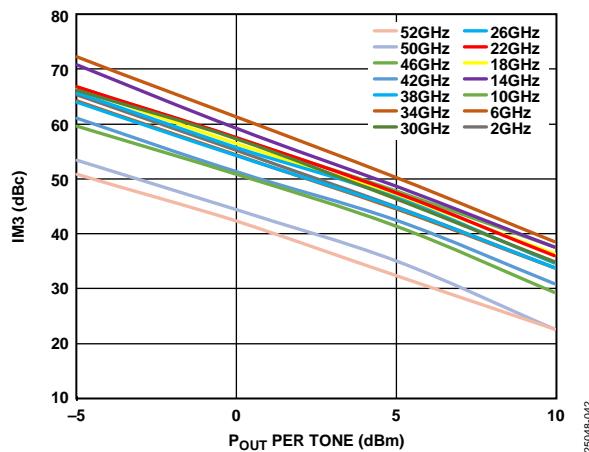

Figure 44. IM3 vs.  $P_{OUT}$  per Tone at Various Frequencies,  $V_{DD} = 5$  V,  $I_{DQ} = 85$  mA,  $V_{GG2} = 1$  V

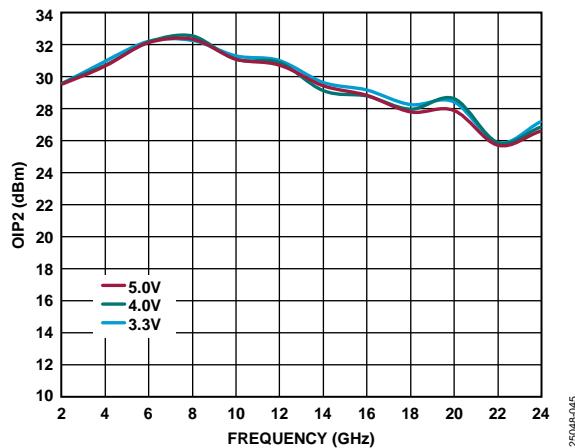

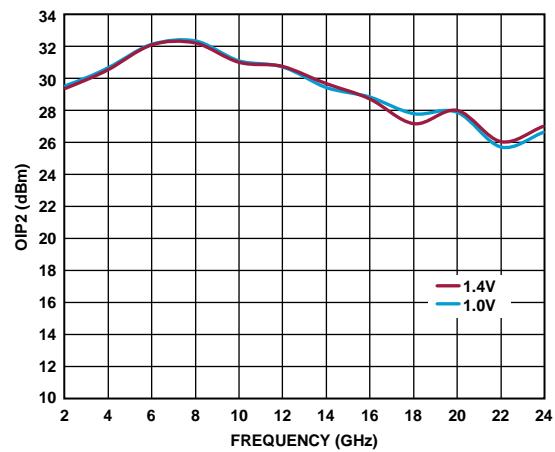

Figure 45. OIP2 vs. Frequency at Various  $V_{DD}$  Voltages,  $I_{DQ} = 85$  mA,  $V_{GG2} = 1$  V

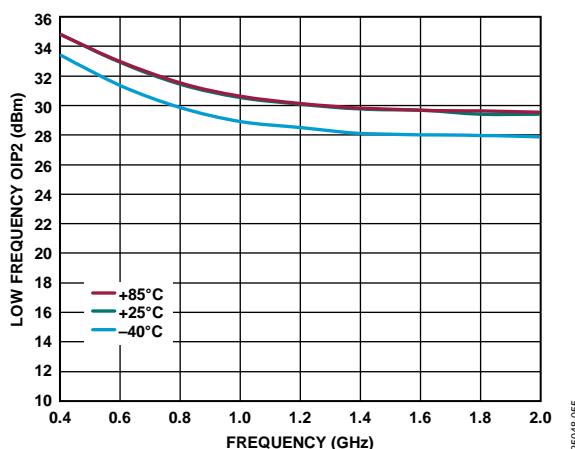

Figure 46. Low Frequency OIP2 vs. Frequency at Various Temperatures,  $V_{DD} = 5$  V,  $I_{DQ} = 85$  mA,  $V_{GG2} = 1$  V

25048-048

25048-050

25048-052

25048-054

25048-049

25048-051

## THEORY OF OPERATION

The HMC1126ACEZ is a GaAs, pHEMT, low noise amplifier.

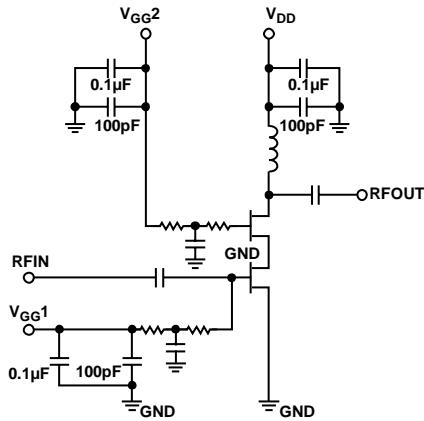

The low noise amplifier uses a fundamental cell of two field effect transistors (FETs), as shown in Figure 56. This fundamental cell is duplicated a number of times, thereby increasing the operational bandwidth.

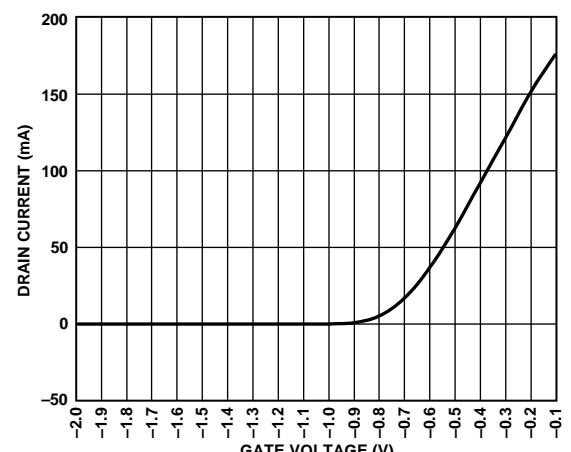

The negative  $V_{GG1}$  sets the supply current, and the voltage on  $V_{GG2}$  ensures that there are approximately equal dc voltages across the top and bottom FETs. The RFIN and RFOUT pins are ac-coupled and matched to  $50\ \Omega$ .  $V_{DD}$  is applied through an integrated choke. The  $0.1\ \mu F$  and  $100\ pF$  decoupling capacitors are integrated. As a result, no external passive components are required for operation.

Figure 56. Simplified Block Diagram

25048-056

## APPLICATIONS INFORMATION

Figure 57 shows the basic connections for operating the HMC1126ACEZ. Because the RFIN and RFOUT pins are internally ac-coupled, no external ac coupling is required. Because  $V_{DD}$ ,  $V_{GG1}$ , and  $V_{GG2}$  are internally decoupled, no external components are required on these pins. Figure 57 shows the configuration used to characterize and qualify the device.

See the [HMC1126-EVALZ](#) user guide for information on using the evaluation board.

### POWER-UP AND POWER-DOWN SEQUENCING

To avoid damaging the device, careful attention must be paid to the power-up and power-down sequencing of the RF input, the gate bias voltages, and the drain bias voltage.

#### Power-Up

The following power-up sequencing is recommended:

1. Connect GND to ground.

2. Set  $V_{GG1}$  to  $-2$  V.

3. Set  $V_{DD}$  to 5 V.

4. Set  $V_{GG2}$  to 1 V.

5. Increase  $V_{GG1}$  to achieve an  $I_{DQ} = 85$  mA.

6. Apply the RF signal.

#### Power-Down

The following power-down sequencing is recommended:

1. Turn off the RF signal.

2. Decrease  $V_{GG1}$  to  $-2$  V to achieve an  $I_{DQ} = 0$  mA.

3. Decrease  $V_{GG2}$  to 0 V.

4. Decrease  $V_{DD}$  to 0 V.

5. Increase  $V_{GG1}$  to 0 V.

Figure 57. Basic Connections

25048-057

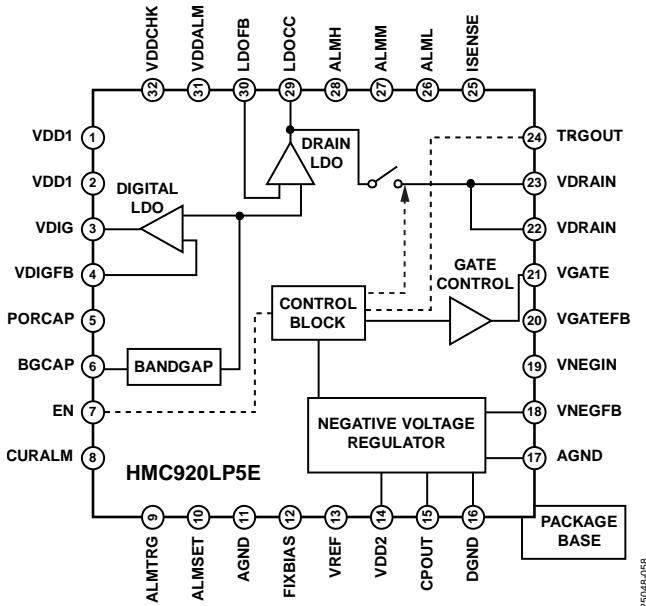

## BIASING THE HMC1126ACEZ WITH THE HMC920LP5E

The HMC920LP5E (see Figure 58) is designed to provide active bias control for enhancement mode and depletion mode amplifiers, such as the HMC1126ACEZ. The HMC920LP5E measures and regulates drain current to compensate for temperature changes and part to part variations.

Figure 58. Functional Diagram of the HMC920LP5E

Additionally, the HMC920LP5E properly sequences gate and drain voltages to ensure safe on and off operation and offers circuit self protection in the event of a short circuit. The active bias controller contains an internal charge pump that generates the negative voltage needed to drive the  $V_{GG1}$  pin on the HMC1126ACEZ. Alternatively, an external negative voltage can be provided.

For more information regarding the use of the HMC920LP5E, refer to the HMC920LP5E data sheet and the [AN-1363 Application Note](#).

### Application Circuit Setup

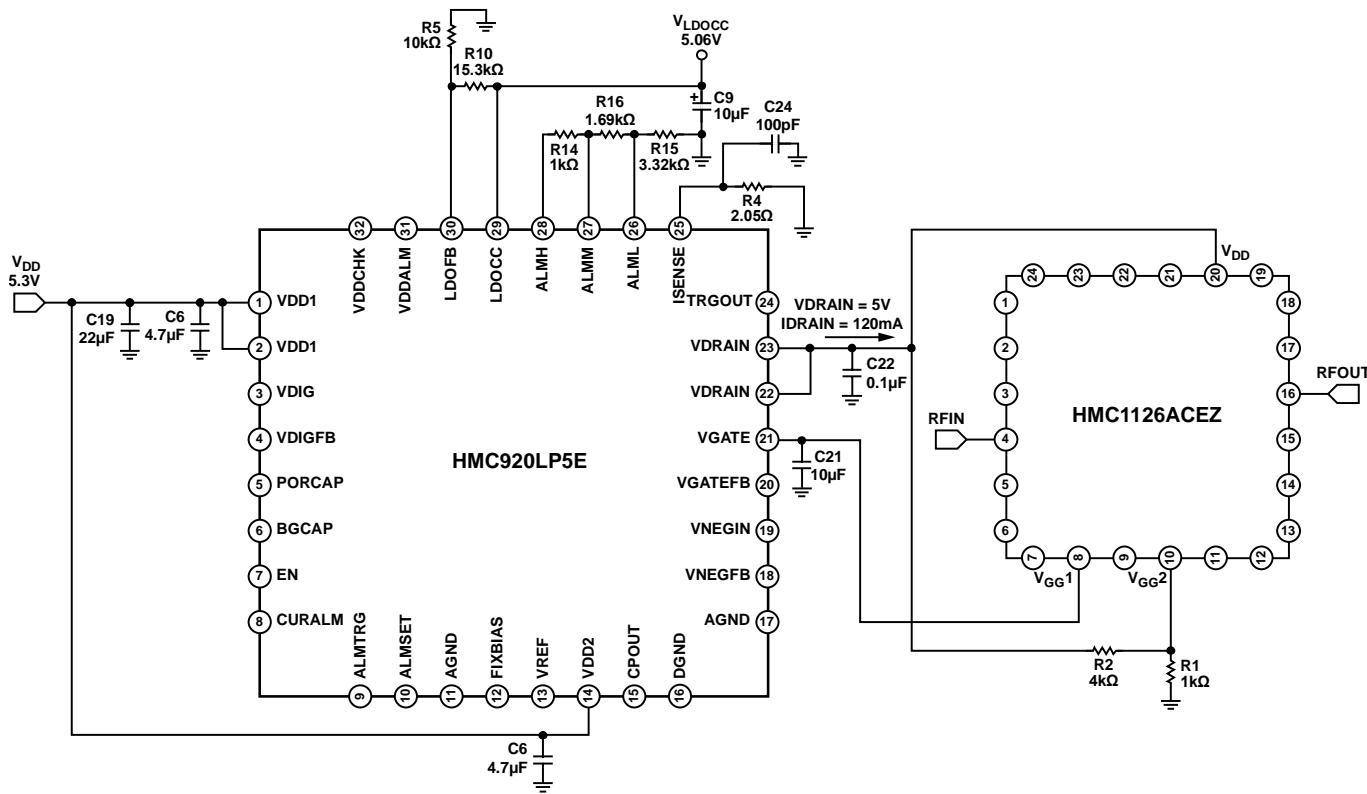

Figure 59 shows the application circuit for bias control of the HMC1126ACEZ using the HMC920LP5E. The current through the HMC920LP5E is measured, and the  $V_{GATE}$  output voltage serves until the setpoint drain current is achieved. The various external components around the HMC920LP5E are set as follows in this section.

The target drain current must first be determined and set. This current must be set based on the maximum drain current required during operation, including when the device is generating the maximum expected output power. In this case, a target drain current of 120 mA was chosen. Set the target value by attaching a 2.05 k $\Omega$  ground referenced resistor to the ISENSE pin (Pin 25) on the HMC920LP5E.

To ensure adequate headroom, the supply voltage for the HMC920LP5E must be set higher than the target drain voltage to the HMC1126ACEZ (5 V). Accordingly, VDD1 and VDD2 on the HMC920LP5E are set to 5.3 V.

The voltage on the LDOCC pin (Pin 29) on the HMC920LP5E drives the VDRAIN pins which in turn drive the  $V_{DD}$  pin of the HMC1126ACEZ. Because the LDOCC output is connected to the VDRAIN output through an internal metal-oxide semiconductor field effect transistor (MOSFET) switch with an on resistance of 0.5  $\Omega$ , the LDOCC voltage ( $V_{LDOCC}$ ) must be set slightly higher than the target drain voltage to the HMC1126ACEZ. To determine the required LDOCC voltage, use the following equation:

$$V_{LDOCC} = V_{DRAIN} + IDRAIN \times 0.5$$

Therefore,  $V_{LDOCC} = 5\text{ V} + (0.12 \times 0.5) = 5.06\text{ V}$ .

To set  $V_{LDOCC}$  to 5.06 V, use the following equation with R5 set to 10 k $\Omega$ :

$$R10 = (R5/2) \times (V_{LDOCC} - 2)$$

Therefore,  $R10 = (10000/2) \times (5.06 - 2) = 15.3\text{ k}\Omega$ .

### Setting $V_{GG1}$ and $V_{GG2}$

The  $V_{GG2}$  fixed bias voltage is set to 1 V using a resistor divider that is derived from VDD1 and VDD2 on the HMC920LP5E. Because the current into the  $V_{GG2}$  pin is low (<1 mA), large resistor values in the k $\Omega$  range can be used to set the  $V_{GG2}$  voltage and save on overall current usage.

The recommended minimum voltage for  $V_{GG1}$  into the HMC1126ACEZ is -2 V, which is also the default value for the VNEGFB pin on the HMC920LP5E. As a result, there is no need to adjust the VNEGFB and VGATE voltages.

Refer to the HMC920LP5E data sheet for the detailed schematic.

Figure 59. Application Circuit Using the HMC920LP5E with the HMC1126ACEZ (Additional Circuitry Omitted for Clarity)

## ***HMC920LP5E Bias Sequence***

When the HMC920LP5E bias control circuit is set up, the HMC1126ACEZ bias can be toggled on and off by applying 3.5 V (high) or 0 V (low) to the EN pin of the HMC920LP5E. If EN is left floating, the pin floats high. When EN is set to 3.5 V,

VGATE initially drops to  $-2\text{ V}$ , and VDRAIN rises to  $5\text{ V}$ . Then, VGATE and  $V_{\text{GG}1}$  increase until IDRAIN equals  $120\text{ mA}$ . The closed control loop then regulates IDRAIN to  $120\text{ mA}$ . When the EN pin goes low, VGATE and  $V_{\text{GG}1}$  drop back to  $-2\text{ V}$  and VDRAIN drops to  $0\text{ V}$ .

## CONSTANT DRAIN CURRENT BIASING vs. CONSTANT GATE VOLTAGE BIASING

### Voltage Biasing

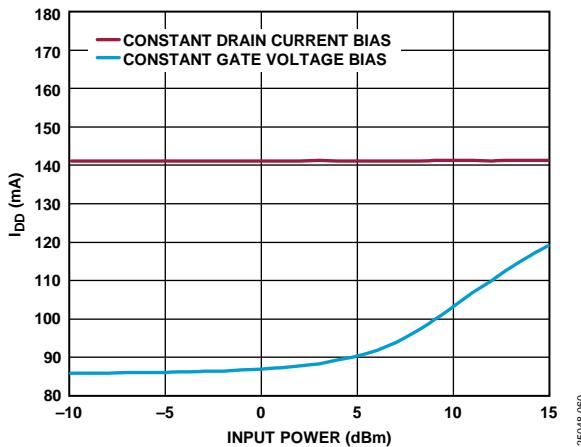

The HMC920LP5E uses closed loop feedback to continuously adjust VGATE to maintain a constant drain current bias over the dc supply variation, temperature, and part to part variations. Constant drain current bias is an ideal method for reducing time in calibration procedures and maintaining consistent performance over time.

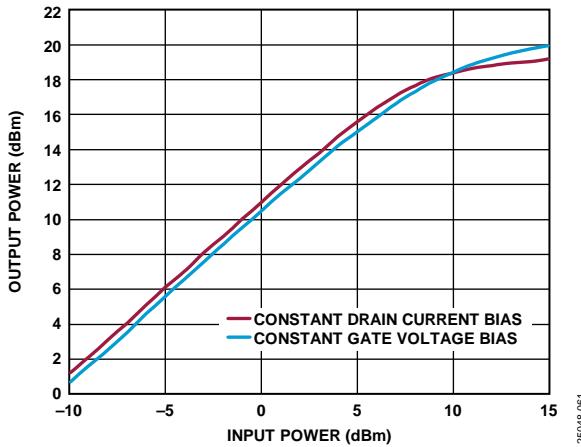

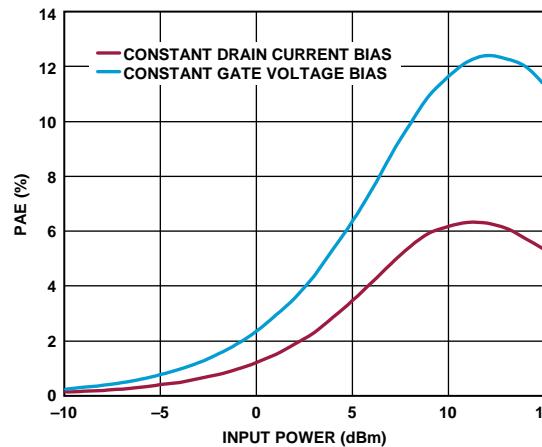

In comparison to a constant gate voltage bias, where the current increases dynamically when the RF power is applied, a constant drain current bias results in constant power consumption.

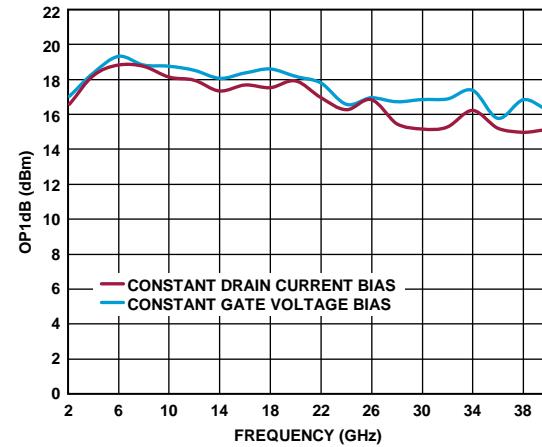

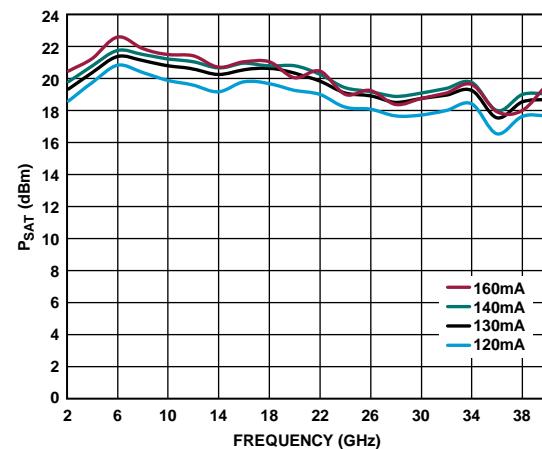

The OP1dB performance for the constant drain current bias can be varied by varying the bias setpoint. By increasing the bias current, OP1dB increases, as shown in Figure 66. The trade-off with a constant drain current is that this higher drain current is present for all RF input and output power levels.

Figure 60.  $I_{DD}$  vs. Input Power,  $V_{DD} = 5$  V, Frequency = 26 GHz, Constant Drain Current Bias ( $I_{DD} = 140$  mA) and Constant Gate Voltage Bias

Figure 61. Output Power vs. Input Power,  $V_{DD} = 5$  V, Frequency = 26 GHz, Constant Drain Current Bias ( $I_{DD} = 140$  mA) and Constant Gate Voltage Bias

The current and temperature limit of  $I_{DD}$  under the constant current operation is usually set by the thermal limitations detailed in the Absolute Maximum Ratings section (see the continuous power dissipation specification in Table 5).

Increasing  $I_{DD}$  does not indefinitely increase OP1dB. Therefore, consider the trade-off between the power dissipation and OP1dB performance when using a constant drain current bias.

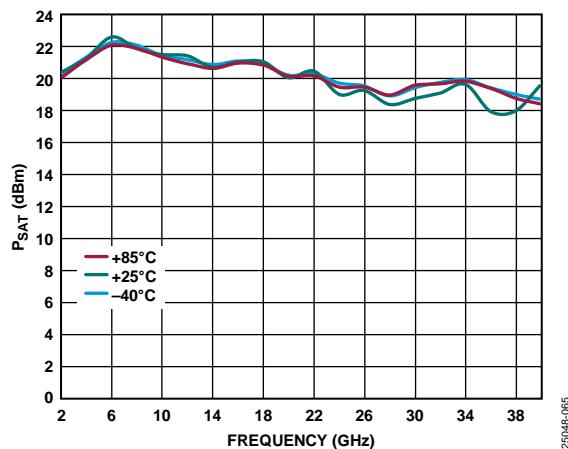

The performance of the constant drain current circuit is summarized in Figure 60 to Figure 67. These figures include comparisons with a constant gate voltage bias. Note that Figure 60 indicates a current consumption of 140 mA, which includes the complete current consumption of the circuit, that is, 120 mA drain current for the HMC1126ACEZ and an additional 20 mA of quiescent current in the HMC920LP5E. Using 140 mA as the current consumption also results in lower PAE compared to a constant gate voltage bias.

Figure 62. PAE vs. Input Power,  $V_{DD} = 5$  V, Frequency = 26 GHz, Constant Drain Current Bias ( $I_{DD} = 140$  mA) and Constant Gate Voltage Bias

Figure 63. OP1dB vs. Frequency,  $V_{DD} = 5$  V, Constant Drain Current Bias ( $I_{DD} = 140$  mA) and Constant Gate Voltage Bias

## OUTLINE DIMENSIONS

Figure 68.24-Terminal Chip Array Small Outline No Lead Cavity [LGA\_CAV]

5.00 mm x 5.00 mm Body and 1.60 mm Package Height

(CE-24-2)

Dimensions shown in millimeters

07-24-2018-A

## ORDERING GUIDE

| Model <sup>1,2</sup> | Temperature Range | MSL Rating <sup>3</sup> | Package Description                                           | Package Option |

|----------------------|-------------------|-------------------------|---------------------------------------------------------------|----------------|

| HMC1126ACEZ          | -40°C to +85°C    | MSL3                    | 24-Terminal Chip Array Small Outline No Lead Cavity [LGA_CAV] | CE-24-2        |

| HMC1126ACEZ-R7       | -40°C to +85°C    | MSL3                    | 24-Terminal Chip Array Small Outline No Lead Cavity [LGA_CAV] | CE-24-2        |

| HMC1126-EVALZ        |                   |                         | Evaluation Board                                              |                |

<sup>1</sup> Z = RoHS Compliant Part.<sup>2</sup> When ordering the evaluation board only, reference the model number, HMC1126-EVALZ.<sup>3</sup> See the Absolute Maximum Ratings section for additional information.

# Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

[Analog Devices Inc.:](#)

[HMC1126ACEZ](#) [HMC1126ACEZ-R7](#)