## Isolated, Sigma-Delta ADCs with SPI

**FEATURES**

- ▶ 2 (ADE9112) or 3 (ADE9113) channel isolated, simultaneously sampling Σ-Δ ADCs, with integrated *isoPower*, isolated dc-to-dc converters

- ▶ 3 (ADE9103) channel nonisolated, simultaneously sampling Σ-Δ ADCs

- ▶ Synchronization of multiple ADE9103/ADE9112/ADE9113 devices

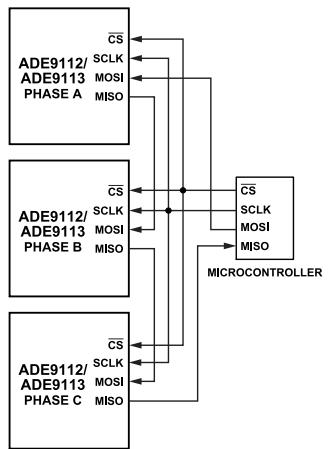

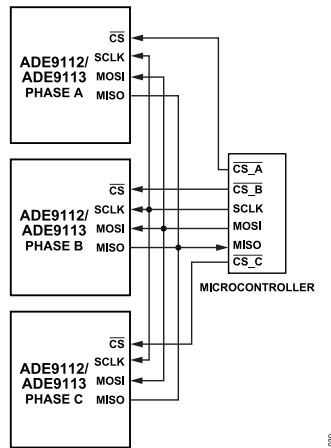

- ▶ 4-wire SPI with bidirectional CRC and daisy-chain functionality

- ▶ Unique SPI readable part ID registers

- ▶ Up to 4 ADE9103/ADE9112/ADE9113 devices clocked from a single crystal or an external clock

- ▶  $\overline{\text{IRQ}}$  hardware pin and registers for fault detection and robustness

- ▶ Sample rate up to 32 kSPS

- ▶ SNR up to 95 dB

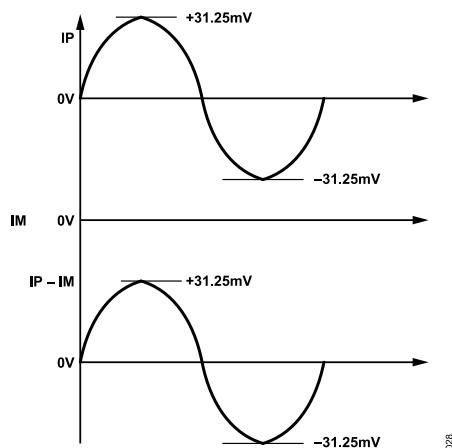

- ▶  $\pm 31.25$  mV peak analog input voltage range for current channel

- ▶  $\pm 500$  mV peak single-ended analog input voltage range for voltage channels

- ▶ Internal voltage reference temperature coefficient:  $<13$  ppm/ $^{\circ}\text{C}$  typical

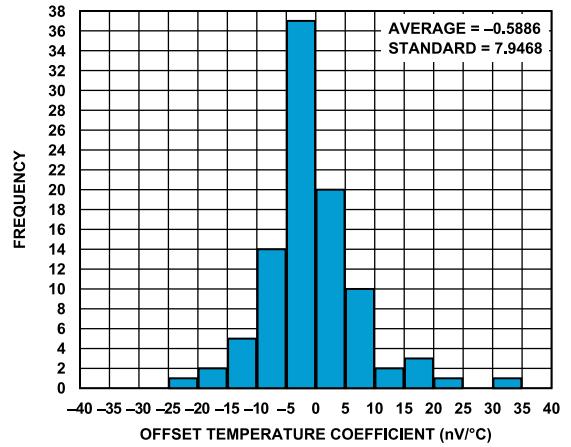

- ▶ ADC offset drift:  $<2$  nV/ $^{\circ}\text{C}$  typical

- ▶ Ideal for both AC and DC measurement systems

- ▶ Single 3.3 V supply for isolated and nonisolated measurements

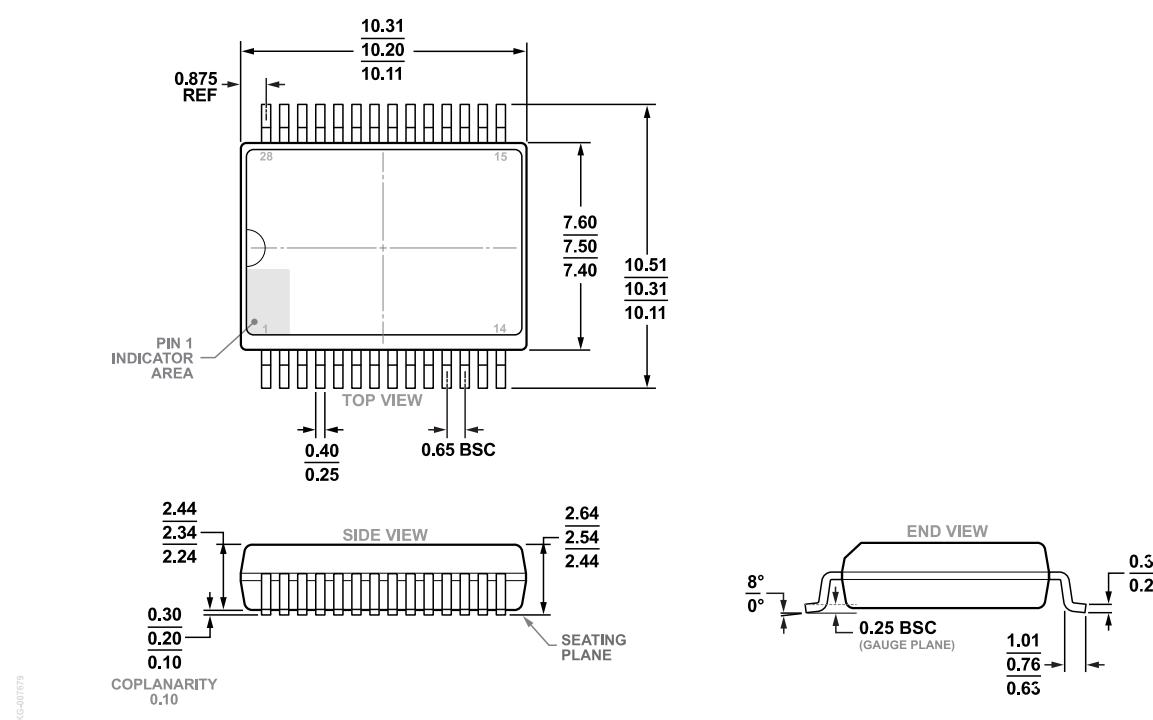

- ▶ **Compact 28-lead, wide-body with finer pitch SOIC package with 8.3 mm creepage**

- ▶ Temperature range:  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$

- ▶ Passes CISPR 32 Class B RF Emissions

- ▶ ADE9112 and ADE9113 **safety and regulatory approvals**

- ▶ IEC 60747-17 certificate of conformity expected

- ▶ 5000 V RMS for 1 minute per UL 1577

- ▶ IEC 61010-1 and IEC 62368-1

**APPLICATIONS**

- ▶ Shunt-based polyphase meters

- ▶ Electric vehicle supply equipment

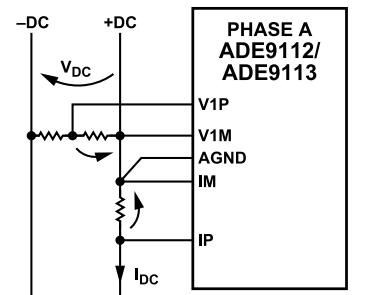

- ▶ DC meters

- ▶ Power quality monitoring

- ▶ Solar inverters

- ▶ Process monitoring

- ▶ Protective devices

- ▶ Isolated sensor interfaces

**GENERAL DESCRIPTION**

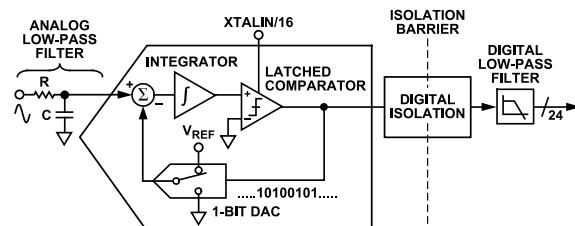

The ADE9103/ADE9112/ADE9113 are precision simultaneously sampling Σ-Δ analog-to-digital converters (ADCs) for both DC and polyphase shunt-based energy metering applications. The ADE9113<sup>1</sup> integrates safety certified signal and power galvanic isolation with three simultaneously sampling fully differential 24-bit Σ-Δ ADC channels. The ADE9112 features two fully differential Σ-Δ ADC channels for isolated applications where only a single voltage channel is required. The ADE9103 is a nonisolated, 3-channel Σ-Δ ADC for use in applications where isolation is not required, such as for neutral measurement. The ADE9103/ADE9112/ADE9113 all include a high-gain, current channel well suited for use with a shunt resistor as the current sensor. Multiple ADE9103/ADE9112/ADE9113 devices can be synchronized to sample simultaneously and provide coherent outputs.

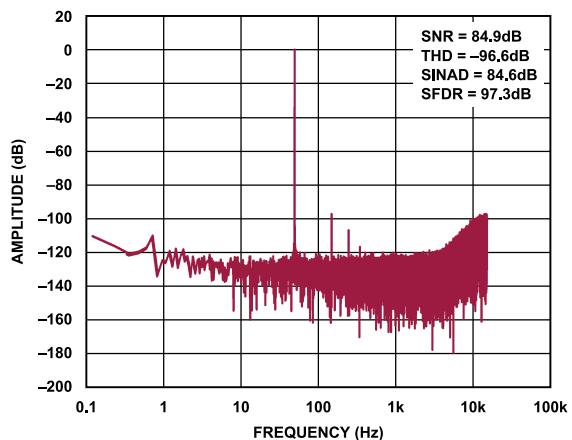

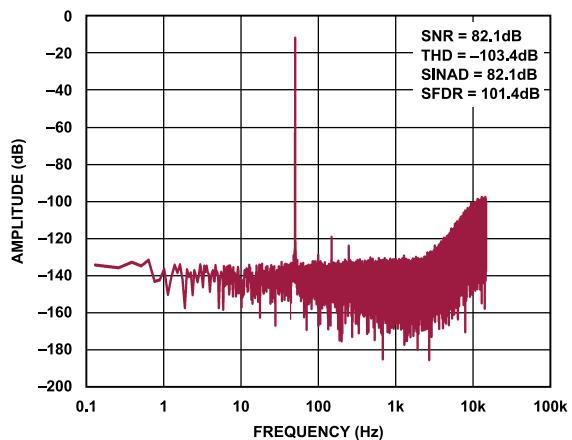

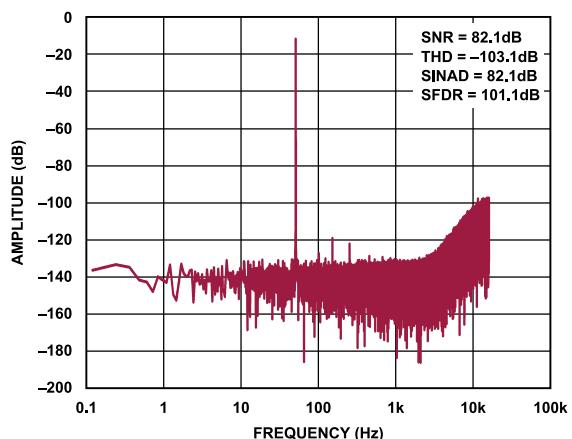

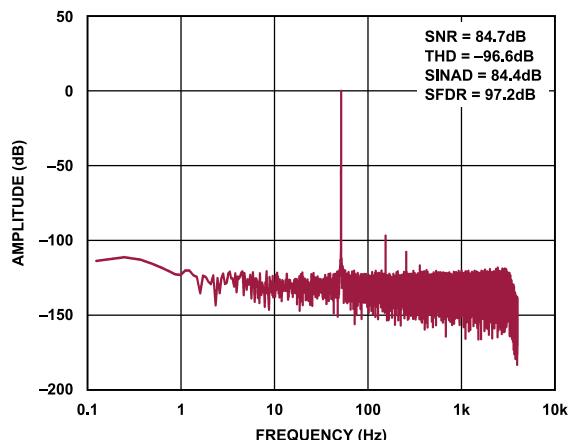

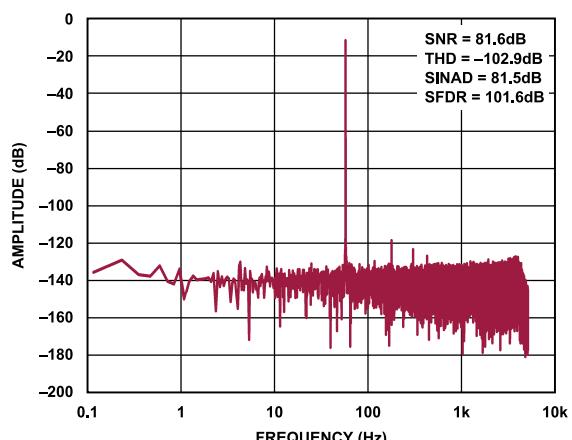

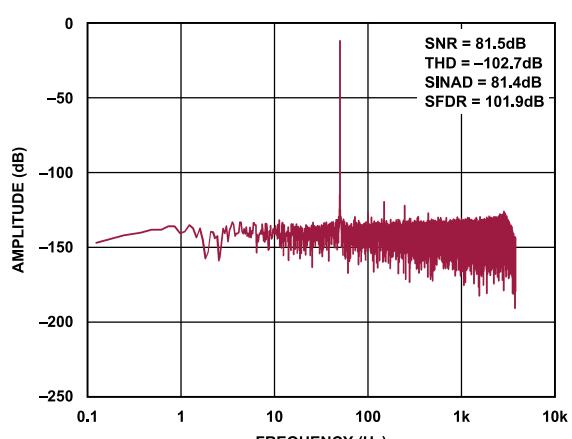

The current channel ADC provides an 86 dBFS signal-to-noise ratio (SNR), at a sample rate of 4 kSPS, over a 1.65 kHz signal bandwidth and a typical gain drift of 13 ppm/ $^{\circ}\text{C}$ , which enables down to Class 0.2 accuracy. The voltage ADCs provide an SNR of 91 dBFS over the same sample rate and bandwidth. The high gain on the current channel (IP and IM) aids the use of lower resistance shunts for reduced losses due to heat. The low offset drift of 2 nV/ $^{\circ}\text{C}$  offers the performance required for DC metering.

The ADE9103/ADE9112/ADE9113 delivers system cost savings and increased robustness. The main ADE9103/ADE9112/ADE9113 can drive clocks of up to three additional ADE9103/ADE9112/ADE9113 with a single crystal. The bidirectional, serial port interface (SPI) supports a daisy-chain capability, allowing access to all registers while reducing the required microcontroller pin count. The **28-lead SOIC\_W\_FPC** allows more compact layouts. Valid data transfers are ensured with bidirectional, cyclic redundancy check (CRC) and  $\overline{\text{IRQ}}$  pin alerts the system of critical faults. The ADE9112 and ADE9113 pass CISPR 32 Class B emissions on a 2-layer printed circuit board (PCB) with the addition of a high voltage capacitor and on a 4-layer PCB with an internal stitching capacitor.

**Table 1. ADE9103/ADE9112/ADE9113 Product Comparison**

| Model   | 24-Bit Current Measurement Channel | 24-Bit Voltage Measurement Channel | Integrated Safety Isolation |

|---------|------------------------------------|------------------------------------|-----------------------------|

| ADE9103 | Yes                                | 2                                  | No                          |

| ADE9112 | Yes                                | 1                                  | Yes                         |

| ADE9113 | Yes                                | 2                                  | Yes                         |

<sup>1</sup> Protected by U.S. Patents 5,952,849; 6,873,065; 7,075,329; 6,262,600; 7,489,526; 7,558,080; 8,892,933; and 11,533,027. Other patents are pending.

## TABLE OF CONTENTS

|                                                   |    |                                             |    |

|---------------------------------------------------|----|---------------------------------------------|----|

| Features.....                                     | 1  | Zero Crossing.....                          | 27 |

| Applications.....                                 | 1  | Interrupts.....                             | 27 |

| General Description.....                          | 1  | Applications Information.....               | 29 |

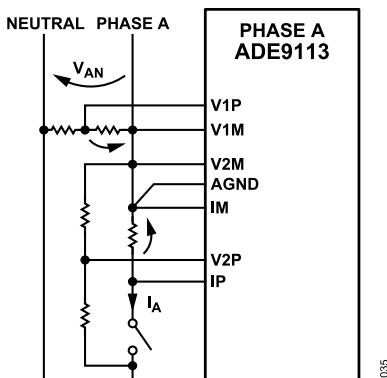

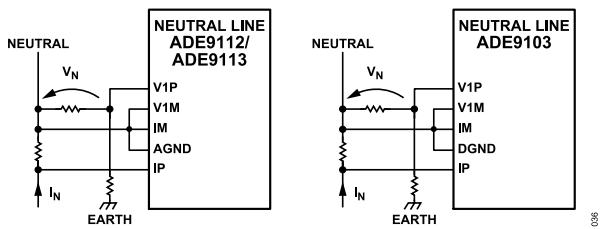

| Typical Applications Circuit.....                 | 4  | Polyphase Energy Meters.....                | 29 |

| Functional Block Diagrams.....                    | 5  | DC Metering .....                           | 30 |

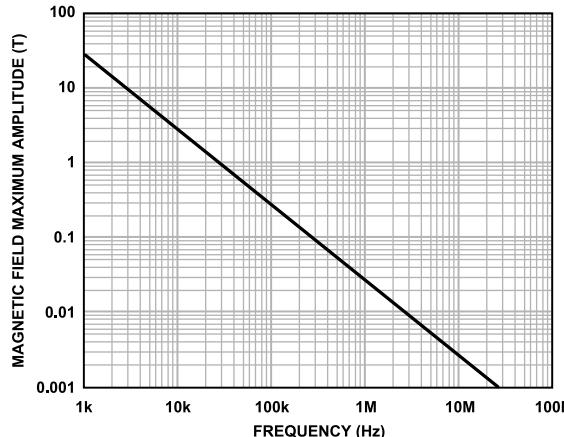

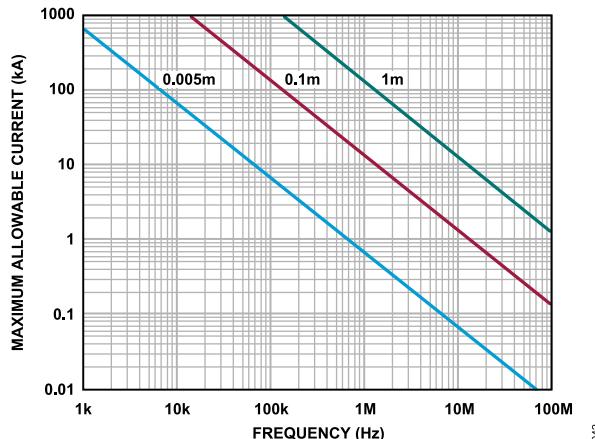

| Specifications.....                               | 6  | Magnetic Field Immunity of Isolation.....   | 31 |

| Timing Characteristics.....                       | 10 | Crystal Oscillator/External Clock.....      | 32 |

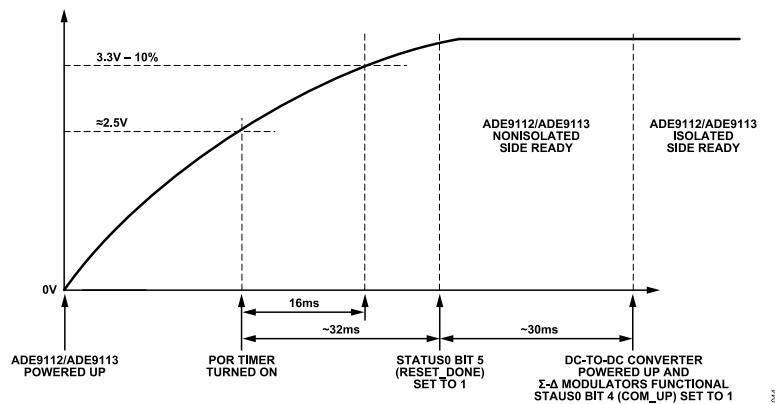

| Insulation Characteristics.....                   | 11 | Power-Up and Initialization Procedures..... | 33 |

| Regulatory Approvals.....                         | 12 | SPI Compatible Communication.....           | 37 |

| Absolute Maximum Ratings.....                     | 13 | Synchronizing Multiple ADE9103/ADE9112/     |    |

| Thermal Resistance.....                           | 13 | ADE9113 Devices.....                        | 42 |

| Electrostatic Discharge (ESD) Ratings.....        | 13 | Power Management.....                       | 44 |

| ESD Caution.....                                  | 13 | DC-to-DC Converter.....                     | 44 |

| Pin Configurations and Function Descriptions..... | 14 | Software Reset.....                         | 45 |

| Typical Performance Characteristics.....          | 18 | Hardware Reset.....                         | 45 |

| Test Circuit.....                                 | 21 | Power-Down Mode.....                        | 45 |

| Terminology.....                                  | 22 | Layout Guidelines.....                      | 46 |

| Theory of Operation.....                          | 24 | ADE9113 Evaluation Board.....               | 46 |

| Analog Inputs.....                                | 24 | Hardware Identifiers.....                   | 46 |

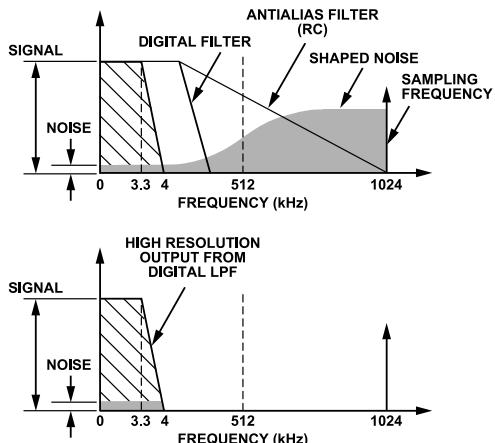

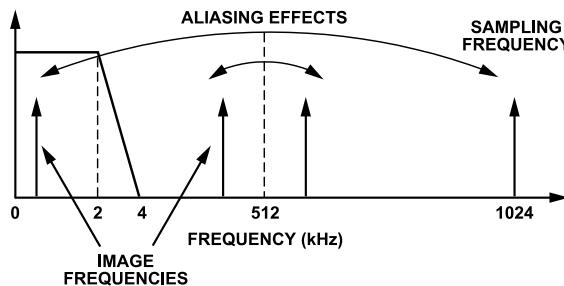

| Analog-to-Digital Conversion.....                 | 24 | Register Summary.....                       | 47 |

| Reference Voltage.....                            | 25 | Register Details.....                       | 49 |

| Protecting the Integrity of Configuration         |    | Outline Dimensions.....                     | 55 |

| Registers.....                                    | 27 | Ordering Guide.....                         | 55 |

| CRC of Configuration Registers.....               | 27 | Evaluation Boards.....                      | 55 |

| Status Registers.....                             | 27 |                                             |    |

## REVISION HISTORY

## 4/2025—Rev. 0 to Rev. A

|                                                                                                                            |    |

|----------------------------------------------------------------------------------------------------------------------------|----|

| Changes to Features Section.....                                                                                           | 1  |

| Added Note 1, Table 1.....                                                                                                 | 6  |

| Changes to Internal Capacitance on XTALIN and XTALOUT to DGND, C <sub>IN1</sub> , C <sub>IN2</sub> Parameter, Table 1..... | 6  |

| Added Note 1, Table 3.....                                                                                                 | 10 |

| Changes to Figure 5 Caption.....                                                                                           | 10 |

| Changes to Table 4 .....                                                                                                   | 11 |

| Changes to Table 5.....                                                                                                    | 12 |

| Changes to Table 6 and Table 7.....                                                                                        | 13 |

| Changes to Table 11.....                                                                                                   | 14 |

| Changes to Table 12.....                                                                                                   | 16 |

| Changes to Figure 27.....                                                                                                  | 21 |

| Changes to ADC Transfer Function Section.....                                                                              | 25 |

| Changes to CRC of Configuration Registers Section.....                                                                     | 27 |

| Added Zero Crossing Section.....                                                                                           | 27 |

| Changes to Interrupts Section.....                                                                                         | 27 |

| Changes to Figure 37.....                                                                                                  | 29 |

| Changed Clock Section to Crystal Oscillator/External Clock Section.....                                                    | 32 |

| Changes to Crystal Oscillator/External Clock Section.....                                                                  | 32 |

| Added Crystal Selection Section.....                                                                                       | 33 |

| Added Load Capacitor Calculation Section.....                                                                              | 33 |

**TABLE OF CONTENTS**

|                                                                                |    |

|--------------------------------------------------------------------------------|----|

| Changed SPI Compatible Section to SPI Compatible Communication Section.....    | 37 |

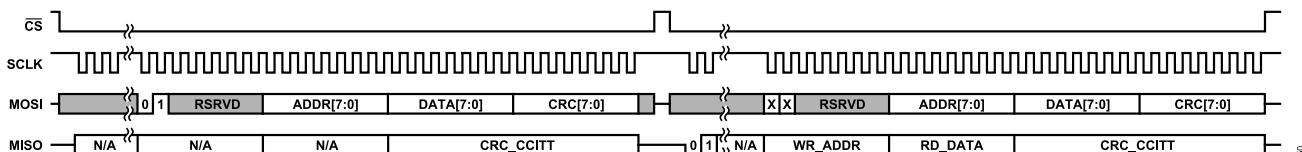

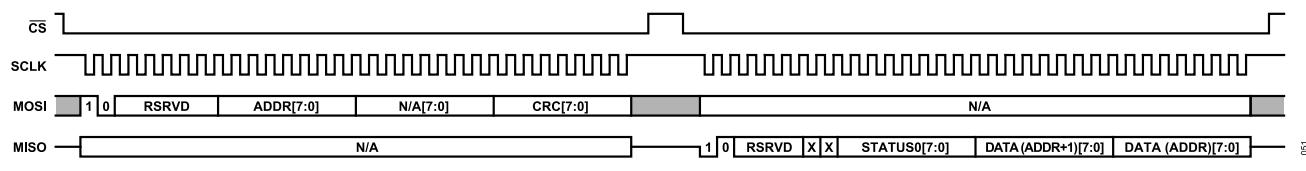

| Changes to SPI Compatible Communication Section.....                           | 37 |

| Changes to Figure 48.....                                                      | 37 |

| Changed SPI Long Operation Section to SPI Long Format Operation Section.....   | 38 |

| Changes to SPI Long Format Operation Section.....                              | 38 |

| Changes to Table 13.....                                                       | 38 |

| Changes to Figure 49 Caption and Figure 50 Caption.....                        | 38 |

| Moved Table 14 and Table 15 .....                                              | 39 |

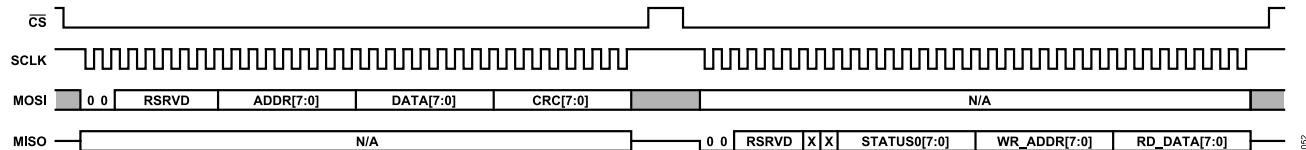

| Changed SPI Short Operation Section to SPI Short Format Operation Section..... | 40 |

| Changes to SPI Short Format Operation Section.....                             | 40 |

| Changes to Figure 51 Caption and Figure 52 Caption.....                        | 40 |

| Changes to CRC of Response Packet Section.....                                 | 42 |

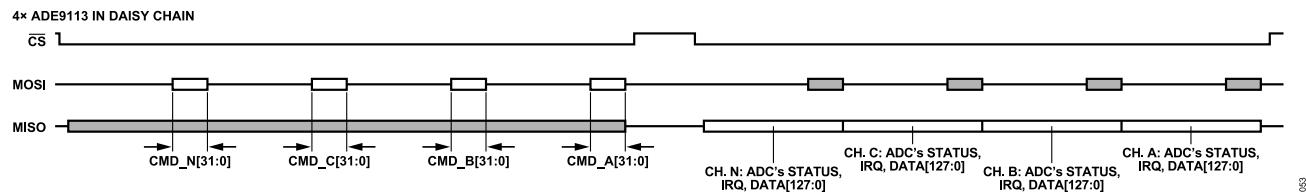

| Changes to Synchronizing Multiple ADE9103/ADE9112/ADE9113 Devices Section..... | 42 |

| Changes to Table 17.....                                                       | 43 |

| Changes to DC-to-DC Converter Section.....                                     | 44 |

| Changes to Table 19.....                                                       | 47 |

| Changes to Table 20.....                                                       | 49 |

**11/2023—Revision 0: Initial Version**

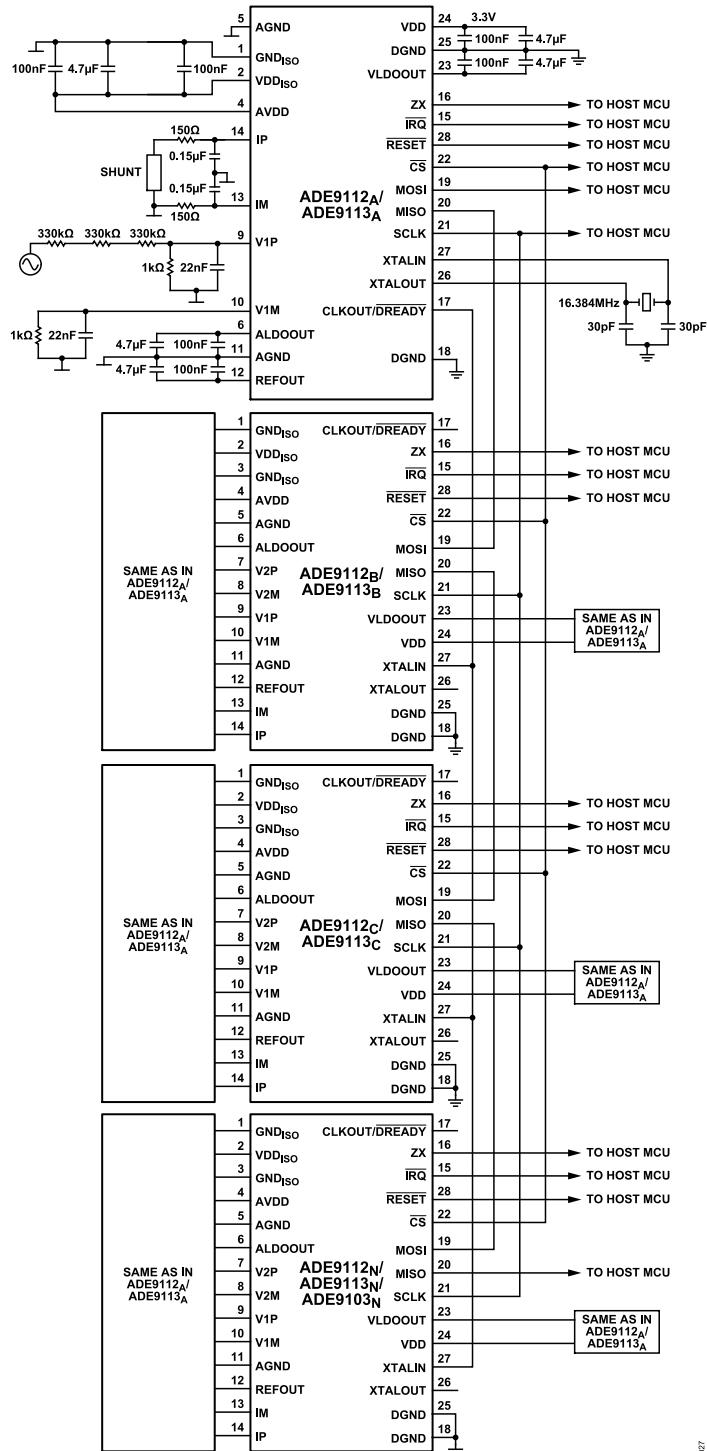

## TYPICAL APPLICATIONS CIRCUIT

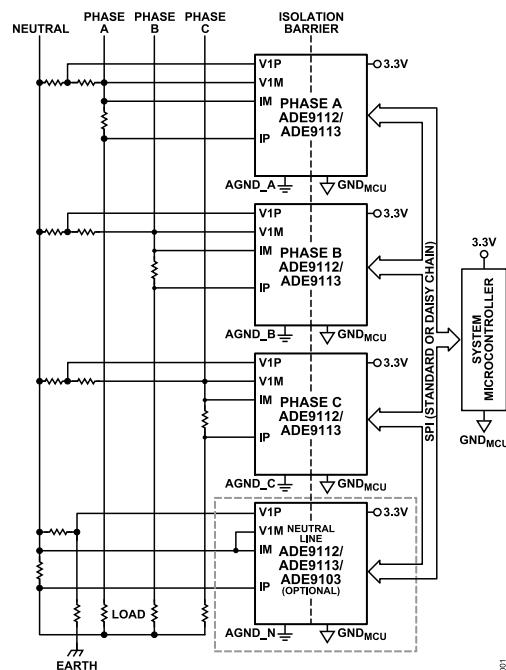

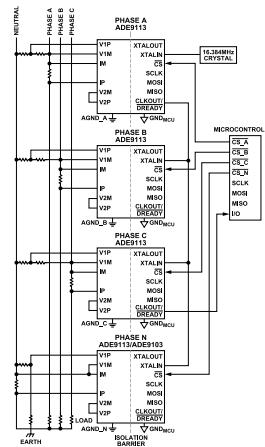

Figure 1. Typical Applications Circuit with isolation between Phase A, Phase B, Phase C and MCU Domains

## FUNCTIONAL BLOCK DIAGRAMS

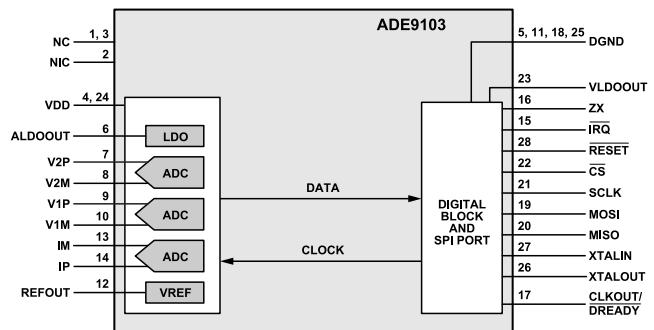

Figure 2. ADE9103 Functional Block Diagram

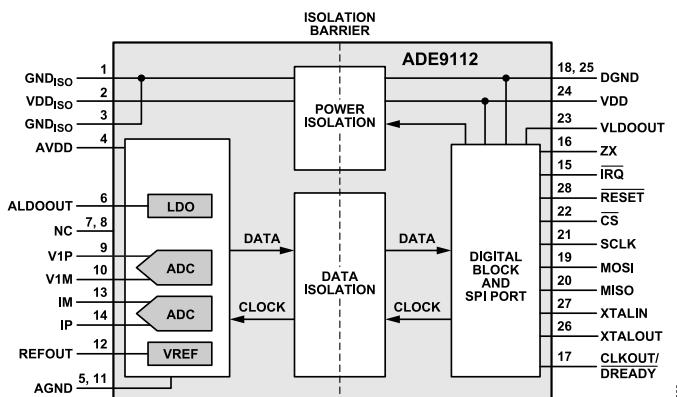

Figure 3. ADE9112 Functional Block Diagram

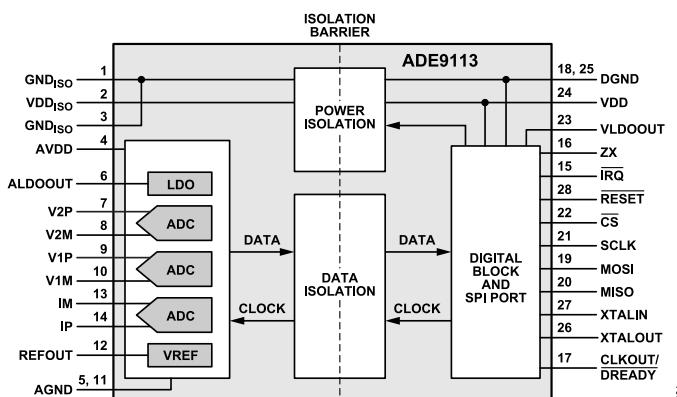

Figure 4. ADE9113 Functional Block Diagram

## SPECIFICATIONS

VDD = 3.3 V ± 10%, AGND = 0 V, DGND = 0 V, on-chip reference, XTALIN = 16.384 MHz, T<sub>MIN</sub> to T<sub>MAX</sub> = -40°C to +125°C, and T<sub>A</sub> = 25°C (typical), unless otherwise noted.

Table 2. Specifications

| Parameter                                                                             | Min     | Typ  | Max     | Unit   | Test Conditions/Comments                                                |

|---------------------------------------------------------------------------------------|---------|------|---------|--------|-------------------------------------------------------------------------|

| POWER SUPPLY                                                                          |         |      |         |        |                                                                         |

| ADE9112/ADE9113                                                                       |         |      |         |        |                                                                         |

| Normal Operation                                                                      | 8       | 13   |         | mA     |                                                                         |

| Hold Reset Operation                                                                  | 9.5     | 12.5 |         | µA     | RESET pin held low                                                      |

| ADE9103                                                                               |         |      |         |        |                                                                         |

| Normal Operation                                                                      | 3.4     | 4.1  |         | mA     |                                                                         |

| Hold Reset Operation                                                                  | 1.0     | 1.3  |         | mA     | RESET pin held low                                                      |

| VDD <sub>ISO</sub> Pin for ADE9112/ADE9113 Only                                       | 2.05    |      |         | V      | Referenced to the GND <sub>ISO</sub> pin                                |

| INTERNAL VOLTAGE REFERENCE                                                            |         |      |         |        |                                                                         |

| Voltage Reference (VREF)                                                              | 1.25    |      |         | V      | REFOUT pin                                                              |

| Temperature Coefficient                                                               |         |      |         |        | T <sub>A</sub> = -40°C to +125°C                                        |

| ADE9112/ADE9113                                                                       | 12      | 23   |         | ppm/°C |                                                                         |

| ADE9103                                                                               | 13      | 28   |         | ppm/°C |                                                                         |

| LOW DROPOUT (LDO) REGULATOR                                                           |         |      |         |        | Generated internally, and external decoupling only                      |

| Analog LDO                                                                            | 1.8     |      |         | V      | ±5%, ALDOOUT pin                                                        |

| Digital LDO                                                                           | 1.8     |      |         | V      | ±5%, VLDOOUT pin                                                        |

| ZERO-CROSSING OUTPUT                                                                  |         |      |         |        |                                                                         |

| Latency                                                                               | 80      |      |         | µs     |                                                                         |

| Jitter                                                                                | 30      |      |         | µs     |                                                                         |

| TEMPERATURE RANGE                                                                     |         |      |         |        |                                                                         |

| Specified Performance                                                                 | -40     |      | +125    | °C     |                                                                         |

| ANALOG INPUTS                                                                         |         |      |         |        |                                                                         |

| Differential Voltage Range                                                            |         |      |         |        |                                                                         |

| IP and IM Pins                                                                        | -31.25  |      | +31.25  | mV     |                                                                         |

| Differential Voltage Range                                                            |         |      |         |        |                                                                         |

| V1P and V1M Pins                                                                      | -1000   |      | +1000   | mV     |                                                                         |

| V2P and V2M Pins                                                                      | -1000   |      | +1000   | mV     |                                                                         |

| Single-Ended Voltage Range <sup>1</sup>                                               |         |      |         |        |                                                                         |

| V1P and V1M Pins                                                                      | -500    |      | +500    | mV     |                                                                         |

| V2P and V2M Pins                                                                      | -500    |      | +500    | mV     |                                                                         |

| Maximum Voltage <sup>1</sup> with Reference to DGND <sup>2</sup> or AGND <sup>3</sup> |         |      |         |        |                                                                         |

| IP and IM Pins                                                                        | -40.625 |      | +40.625 | mV     |                                                                         |

| V1P, V2P, V1M, and V2M Pins                                                           | -600    |      | +600    | mV     |                                                                         |

| Crosstalk <sup>4</sup>                                                                |         |      |         |        | Aggressor channels at full scale. See <a href="#">Crosstalk</a> section |

| V1 and V2 to I                                                                        |         | -125 |         | dB     |                                                                         |

| V1 and I to V2                                                                        |         | -125 |         | dB     |                                                                         |

| V2 and I to V1                                                                        |         | -125 |         | dB     |                                                                         |

| Differential Input Impedance (DC)                                                     |         |      |         |        |                                                                         |

| IP and IM                                                                             | 2700    | 3900 |         | kΩ     |                                                                         |

| V1P, V1M, V2P, and V2M                                                                | 300     | 370  |         | kΩ     |                                                                         |

| ADC Offset                                                                            |         |      |         |        | See <a href="#">ADC Offset</a> section                                  |

| IP and IM                                                                             | 0.3     | ±10  |         | µV     |                                                                         |

| V1P, V1M, V2P, and V2M                                                                | -43     | ±160 |         | µV     |                                                                         |

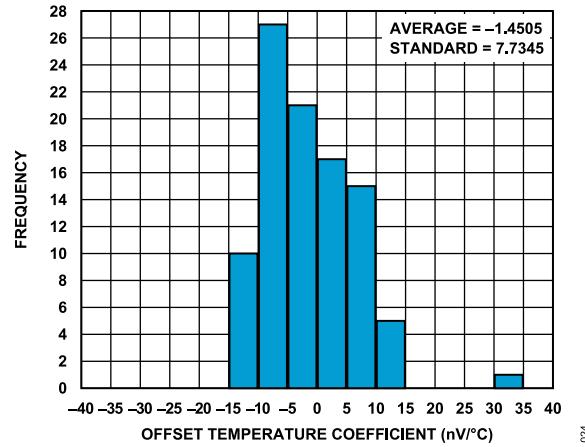

| ADC Offset Drift                                                                      |         |      |         |        | See <a href="#">ADC Offset Drift over Temperature</a> section           |

| IP and IM                                                                             | 2       | 41   |         | nV/°C  |                                                                         |

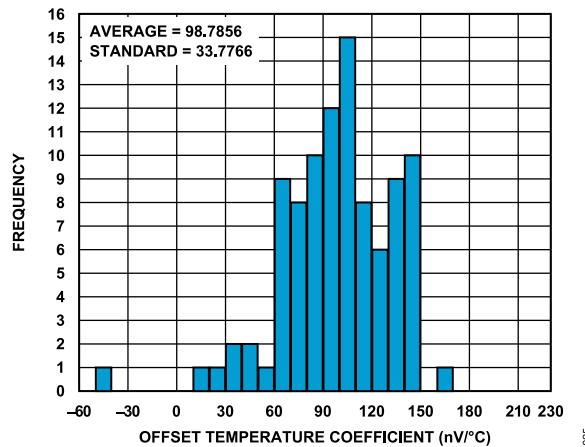

## SPECIFICATIONS

Table 2. Specifications (Continued)

| Parameter                                                        | Min   | Typ  | Max | Unit   | Test Conditions/Comments                                                    |

|------------------------------------------------------------------|-------|------|-----|--------|-----------------------------------------------------------------------------|

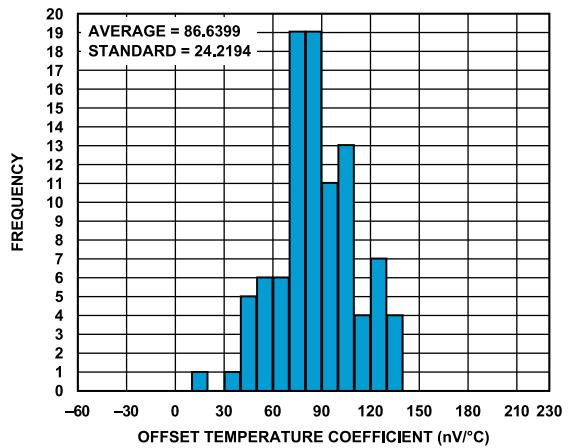

| V1P and V1M                                                      |       |      |     |        |                                                                             |

| ADE9112/ADE9113                                                  | 87    | 212  |     | nV/°C  |                                                                             |

| ADE9103                                                          | 100   | 268  |     | nV/°C  |                                                                             |

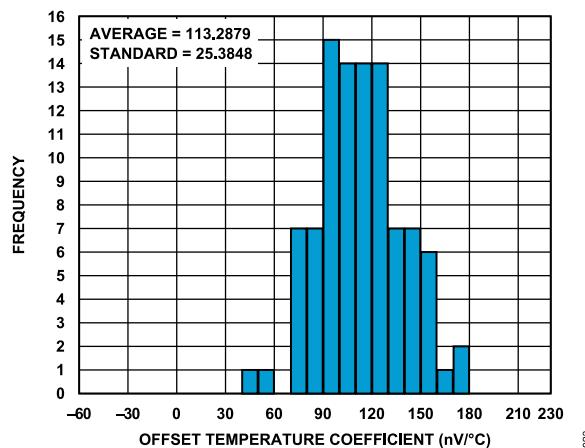

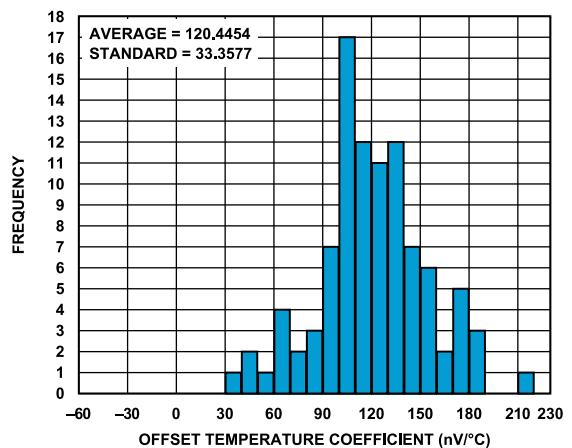

| V2P and V2M                                                      |       |      |     |        |                                                                             |

| ADE9112/ADE9113                                                  | 115   | 245  |     | nV/°C  |                                                                             |

| ADE9103                                                          | 121   | 290  |     | nV/°C  |                                                                             |

| Gain Error                                                       |       |      |     |        |                                                                             |

| All Channels                                                     | ±0.1  | ±0.5 |     | %      | Not including anti-aliasing filter                                          |

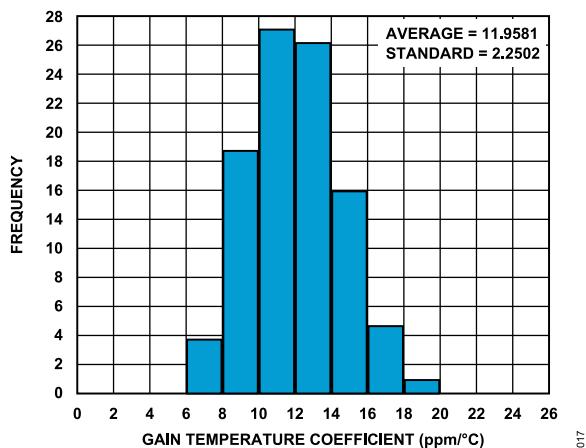

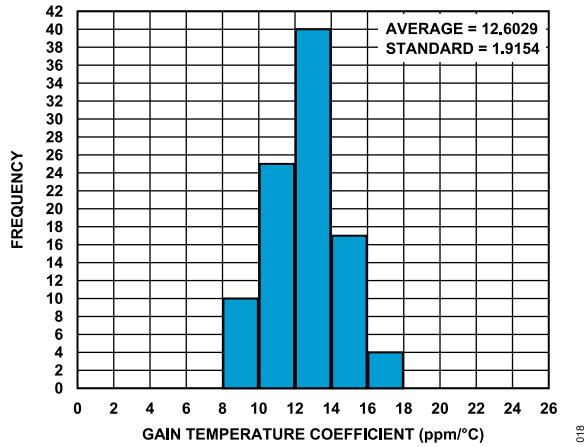

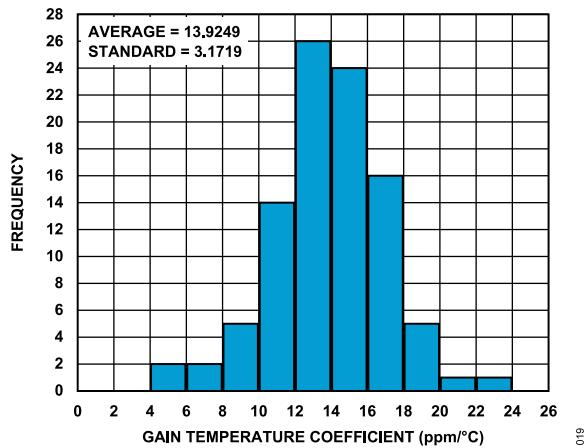

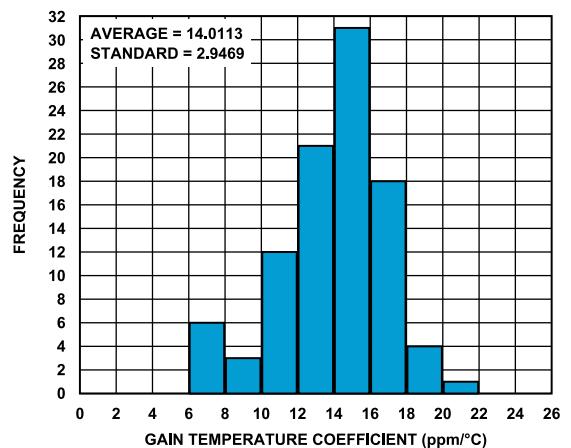

| Gain Drift (Gain Amplifier, ADC, and Internal Voltage Reference) |       |      |     |        | See Gain Drift over Temperature section                                     |

| IP, -40°C to +125°C                                              |       |      |     |        |                                                                             |

| ADE9112/ADE9113                                                  | 12    | 24   |     | ppm/°C |                                                                             |

| ADE9103                                                          | 15    | 31   |     | ppm/°C |                                                                             |

| V1P and V2P, -40°C to +125°C                                     |       |      |     |        |                                                                             |

| ADE9112/ADE9113                                                  | 13    | 24   |     | ppm/°C |                                                                             |

| ADE9103                                                          | 15    | 30   |     | ppm/°C |                                                                             |

| POWER SUPPLY REJECTION (PSR)/COMMON-MODE REJECTION RATIO (CMRR)  |       |      |     |        | See the Power Supply Rejection (PSR) section                                |

| AC PSR                                                           |       |      |     |        | VDD = 3.3 V + 120 mV RMS (100 Hz), IP = V1P = V2P = AGND                    |

| IP and IM                                                        | -120  |      |     | dB     |                                                                             |

| V1P, V1M, V2P, and V2M                                           | -105  |      |     | dB     |                                                                             |

| DC PSR                                                           |       |      |     |        | VDD = 3.3 V ± 330 mV DC, IP = 3.125 mV peak, V1P = V2P = 100 mV peak        |

| IP and IM                                                        | -120  |      |     | dB     |                                                                             |

| V1P, V1M, V2P, and V2M                                           | -105  |      |     | dB     |                                                                             |

| AC CMRR                                                          |       |      |     |        | At 50 Hz and 60 Hz                                                          |

| IP and IM                                                        | -114  |      |     | dB     |                                                                             |

| V1P, V1M, V2P, and V2M                                           | -111  |      |     | dB     |                                                                             |

| Pass-Band Flatness (-0.1 dB)                                     |       |      |     |        |                                                                             |

| 32 kSPS Output                                                   | 1.5   |      |     | kHz    |                                                                             |

|                                                                  | 2.86  |      |     | kHz    | Compensation enabled, LPF_BW = 0                                            |

|                                                                  | 2.43  |      |     | kHz    | Compensation enabled, LPF_BW = 1                                            |

| 8 kSPS Output                                                    | 1.5   |      |     | kHz    |                                                                             |

|                                                                  | 2.87  |      |     | kHz    | Compensation enabled, LPF_BW = 0                                            |

|                                                                  | 2.44  |      |     | kHz    | Compensation enabled, LPF_BW = 1                                            |

| 4 kSPS Output                                                    | 0.77  |      |     | kHz    |                                                                             |

| 2 kSPS Output                                                    | 0.38  |      |     | kHz    |                                                                             |

| 1 kSPS Output                                                    | 0.20  |      |     | kHz    |                                                                             |

| Output Bandwidth (-3 dB) <sup>1</sup>                            |       |      |     |        | DATAPATH_CONFIG = 000 has no LPF and, therefore, bandwidth is not specified |

| 32 kSPS and 8 kSPS                                               | 3.3   |      |     | kHz    | LPF_BW = 0                                                                  |

|                                                                  | 2.7   |      |     | kHz    | LPF_BW = 1                                                                  |

| 4 kSPS                                                           | 1.65  |      |     | kHz    | LPF_BW = 0                                                                  |

|                                                                  | 1.35  |      |     | kHz    | LPF_BW = 1                                                                  |

| 2 kSPS                                                           | 0.825 |      |     | kHz    | LPF_BW = 0                                                                  |

|                                                                  | 0.675 |      |     | kHz    | LPF_BW = 1                                                                  |

| 1 kSPS                                                           | 0.413 |      |     | kHz    | LPF_BW = 0                                                                  |

|                                                                  | 0.338 |      |     | kHz    | LPF_BW = 1                                                                  |

## SPECIFICATIONS

Table 2. Specifications (Continued)

| Parameter                                                                 | Min   | Typ    | Max    | Unit | Test Conditions/Comments                                                                              |

|---------------------------------------------------------------------------|-------|--------|--------|------|-------------------------------------------------------------------------------------------------------|

| CURRENT CHANNEL                                                           |       |        |        |      |                                                                                                       |

| Signal-to-Noise Ratio (SNR)                                               |       |        |        |      | At full-scale input, and see the <a href="#">Signal-to-Noise Ratio (SNR)</a> section                  |

| All 32 kSPS and 8 kSPS Outputs                                            | 83    |        |        | dBFS |                                                                                                       |

| 4 kSPS Output                                                             | 86    |        |        | dBFS |                                                                                                       |

| 2 kSPS Output                                                             | 89    |        |        | dBFS |                                                                                                       |

| 1 kSPS Output                                                             | 91    |        |        | dBFS |                                                                                                       |

| Signal-to-Noise-and-Distortion Ratio (SINAD)                              |       |        |        |      | At full-scale input, and see the <a href="#">Signal-to-Noise-and-Distortion (SINAD) Ratio</a> section |

| All 32 kSPS and 8 kSPS Outputs                                            | 83    |        |        | dBFS |                                                                                                       |

| 4 kSPS Output                                                             | 86    |        |        | dBFS |                                                                                                       |

| 2 kSPS Output                                                             | 89    |        |        | dBFS |                                                                                                       |

| 1 kSPS Output                                                             | 90    |        |        | dBFS |                                                                                                       |

| Total Harmonic Distortion (THD)                                           |       |        |        |      | At full-scale input, and see the <a href="#">Total Harmonic Distortion (THD)</a> section              |

| All Outputs                                                               | -96   |        |        | dBFS |                                                                                                       |

| Spurious-Free Dynamic Range (SFDR)                                        |       |        |        |      | At full-scale input, and see the <a href="#">Spurious-Free Dynamic Range (SFDR)</a> section           |

| All Outputs                                                               | -96   |        |        | dBFS |                                                                                                       |

| VOLTAGE CHANNEL                                                           |       |        |        |      |                                                                                                       |

| Signal-to-Noise Ratio (SNR)                                               |       |        |        |      | At full-scale input, and see the <a href="#">Signal-to-Noise Ratio (SNR)</a> section                  |

| All 32 kSPS and 8 kSPS Outputs                                            | 91    |        |        | dBFS |                                                                                                       |

| 4 kSPS Output                                                             | 93    |        |        | dBFS |                                                                                                       |

| 2 kSPS Output                                                             | 94    |        |        | dBFS |                                                                                                       |

| 1 kSPS Output                                                             | 95    |        |        | dBFS |                                                                                                       |

| Signal-to-Noise-and-Distortion Ratio (SINAD)                              |       |        |        |      | At full-scale input, and see the <a href="#">Signal-to-Noise-and-Distortion (SINAD) Ratio</a> section |

| All 32 kSPS and 8 kSPS Outputs                                            | 88    |        |        | dBFS |                                                                                                       |

| 4 kSPS Output                                                             | 90    |        |        | dBFS |                                                                                                       |

| 2 kSPS Output                                                             | 91    |        |        | dBFS |                                                                                                       |

| 1 kSPS Output                                                             | 91    |        |        | dBFS |                                                                                                       |

| Total Harmonic Distortion (THD)                                           |       |        |        |      | At full-scale input, and see the <a href="#">Total Harmonic Distortion (THD)</a> section              |

| $\pm 0.5 V_{PEAK}$ Differential                                           | -101  |        |        | dBFS |                                                                                                       |

| $\pm 1.0 V_{PEAK}$ Differential                                           | -92   |        |        | dBFS |                                                                                                       |

| Spurious-Free Dynamic Range (SFDR)                                        |       |        |        |      | At full-scale input, and see the <a href="#">Spurious-Free Dynamic Range (SFDR)</a> section           |

| $\pm 0.5 V_{PEAK}$ Differential                                           | 100   |        |        | dBFS |                                                                                                       |

| $\pm 1.0 V_{PEAK}$ Differential                                           | 94    |        |        | dBFS |                                                                                                       |

| XTALIN                                                                    |       |        |        |      |                                                                                                       |

| Input Clock Frequency, XTALIN                                             | 15.84 | 16.384 | 16.547 | MHz  |                                                                                                       |

| XTALIN Duty Cycle                                                         | 45    |        | 55     | %    |                                                                                                       |

| Using XTALOUT to Other Devices                                            | 47.5  |        | 52.5   | %    |                                                                                                       |

| XTALIN Logic Inputs                                                       |       |        |        |      |                                                                                                       |

| Input High Voltage, VINH                                                  | 1.2   |        |        | V    |                                                                                                       |

| Input Low Voltage, VINL                                                   |       |        | 0.5    | V    |                                                                                                       |

| Internal Capacitance on XTALIN and XTALOUT to DGND, $C_{IN1}$ , $C_{IN2}$ |       | 4      |        | pF   |                                                                                                       |

## SPECIFICATIONS

Table 2. Specifications (Continued)

| Parameter                                               | Min | Typ | Max | Unit | Test Conditions/Comments                 |

|---------------------------------------------------------|-----|-----|-----|------|------------------------------------------|

| Internal Feedback Resistance Between XTALIN and XTALOUT |     | 2.7 |     | MΩ   |                                          |

| Transconductance ( $g_m$ )                              | 6   | 10  |     | mA/V |                                          |

| CLKOUT Delay                                            |     |     | 15  | ns   |                                          |

| LOGIC INPUTS—MOSI, SCLK, and $\overline{CS}$            |     |     |     |      |                                          |

| Input High Voltage, $V_{IH}$                            | 2.0 |     |     | V    |                                          |

| Input Low Voltage, $V_{IL}$                             |     | 0.8 |     | V    |                                          |

| Input Current, $I_{IN}$                                 |     | 8.5 |     | μA   |                                          |

| Input Capacitance, $C_{IN}$                             |     | 10  |     | pF   |                                          |

| LOGIC OUTPUTS—CLKOUT/ $\overline{DREADY}$ AND MISO      |     |     |     |      |                                          |

| Output High Voltage, $V_{OH}$                           | 2.4 |     |     | V    | Source current ( $I_{SOURCE}$ ) = 3.5 mA |

| Output Low Voltage, $V_{OL}$                            |     | 0.4 |     | V    | Sink current ( $I_{SINK}$ ) = 3.5 mA     |

<sup>1</sup> Guaranteed by design and not subject to production test.

<sup>2</sup> For the ADE9103 only.

<sup>3</sup> For the ADE9112/ADE9113 only.

<sup>4</sup> V1 refers to V1 voltage channel (V1P and V1M pins), V2 refers to V2 voltage channel (V2P and V2M pins), and I refers to current channel (IP and IM pins).

## SPECIFICATIONS

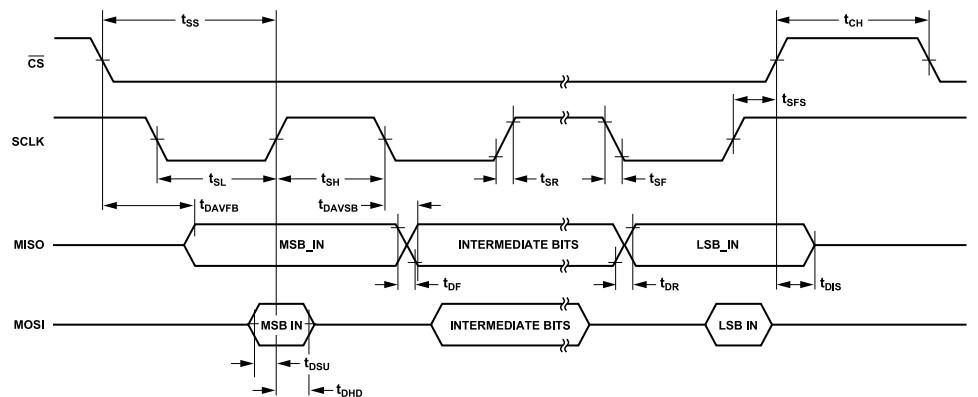

## TIMING CHARACTERISTICS

VDD = 3.3 V  $\pm$  10%, AGND = 0 V, DGND = 0 V, on-chip reference, XTALIN = 16.384 MHz, and T<sub>MIN</sub> to T<sub>MAX</sub> = -40°C to +125°C, unless otherwise noted.

Table 3. SPI Interface Timing Parameters

| Parameter <sup>1</sup>                       | Symbol             | Min    | Max    | Unit |

|----------------------------------------------|--------------------|--------|--------|------|

| CS to SCLK Positive Edge                     | t <sub>SS</sub>    | 10     |        | ns   |

| SCLK Frequency                               | f <sub>SCLK</sub>  | 40     | 20,000 | kHz  |

| SCLK Low Pulse Width                         | t <sub>SL</sub>    | 20     |        | ns   |

| SCLK High Pulse Width                        | t <sub>SH</sub>    | 20     |        | ns   |

| Data Output Valid After CS Edge              | t <sub>DAVFB</sub> |        | 20     | ns   |

| Subsequent Data Output Valid After SCLK Edge | t <sub>DAVSB</sub> |        | 20     | ns   |

| Data Input Setup Time Before SCLK Edge       | t <sub>DSU</sub>   | 10     |        | ns   |

| Data Input Hold Time After SCLK Edge         | t <sub>DHD</sub>   | 10     |        | ns   |

| Data Output Fall Time                        | t <sub>DF</sub>    |        | 10     | ns   |

| Data Output Rise Time                        | t <sub>DR</sub>    |        | 10     | ns   |

| SCLK Rise Time                               | t <sub>SR</sub>    | 5      |        | ns   |

| SCLK Fall Time                               | t <sub>SF</sub>    | 5      |        | ns   |

| MISO Disable After CS Rising Edge            | t <sub>DIS</sub>   | 20     |        | ns   |

| CS High After SCLK Edge                      | t <sub>SFS</sub>   |        | 10     | ns   |

| CS High Time Between SPI Transactions        | t <sub>CH</sub>    |        |        |      |

| Nonisolated (NONISO) Side                    |                    | 400    |        | ns   |

| Isolated (ISO) Side                          |                    | 10,000 |        | ns   |

<sup>1</sup> Specifications guaranteed by design and characterization and not subject to production test.

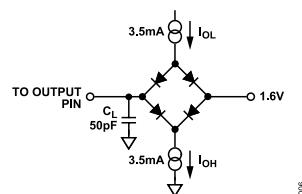

## Timing Diagrams

Figure 5. SPI Timing, CPOL = 1 and CHPA = 1

Figure 6. Load Circuit for Timing Specifications

## SPECIFICATIONS

## INSULATION CHARACTERISTICS

The ADE9112 and ADE9113 are suitable for reinforced electrical insulation only within the safety limit data. Maintenance of the safety data is ensured by the protective circuits.

Table 4. ADE9112 and ADE9113 Isolation Characteristics

| Parameter                                   | Symbol             | Conditions                                                                                                                                                               | Value                          | Unit                     |

|---------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------|

| CLASSIFICATIONS                             |                    |                                                                                                                                                                          |                                |                          |

| Overvoltage Category per IEC 60664-1        |                    | For Rated Mains Voltage $\leq 150 \text{ V}_{\text{RMS}}$<br>For Rated Mains Voltage $\leq 300 \text{ V}_{\text{RMS}}$<br>For Rated Mains Voltage $\leq V_{\text{IOWM}}$ | I to IV<br>I to IV<br>I to III |                          |

| Climatic Classification                     |                    |                                                                                                                                                                          | 40/125/21                      |                          |

| Pollution Degree                            |                    | Per DIN VDE 0110, Table 1                                                                                                                                                | 2                              |                          |

| IEC 60747-17 HIGH VOLTAGE RATINGS           |                    |                                                                                                                                                                          |                                |                          |

| Maximum Working Isolation Voltage           | $V_{\text{IOWM}}$  | Continuous RMS voltage                                                                                                                                                   | 405                            | $\text{V}_{\text{RMS}}$  |

| Maximum Repetitive Isolation Voltage        | $V_{\text{IORM}}$  | Repetitive peak voltage                                                                                                                                                  | 573                            | $\text{V}_{\text{PEAK}}$ |

| Maximum Transient Isolation Voltage         | $V_{\text{IOTM}}$  | Nonrepetitive transient voltages                                                                                                                                         | 7071                           | $\text{V}_{\text{PEAK}}$ |

| Maximum Withstanding Isolation Voltage      | $V_{\text{ISO}}$   | Maximum isolation withstanding AC RMS voltage for one minute                                                                                                             | 5000                           | $\text{V}_{\text{RMS}}$  |

| Maximum Surge Isolation Voltage, Reinforced | $V_{\text{IOSM}}$  | Tested in oil, 1.2 $\mu\text{s}$ /50 $\mu\text{s}$ waveform per IEC 61000-4-5, $V_{\text{TEST}} = 1.3 \times V_{\text{IOSM}} = 10,400 \text{ V}_{\text{PEAK}}$           | 8000                           | $\text{V}_{\text{PEAK}}$ |

| Maximum Impulse Voltage                     | $V_{\text{IMP}}$   | Tested in air, 1.2 $\mu\text{s}$ /50 $\mu\text{s}$ waveform per IEC 61000-4-5                                                                                            | 7071                           | $\text{V}_{\text{PEAK}}$ |

| Input to Output Test Voltage                | $V_{\text{PR}}$    |                                                                                                                                                                          | 1125                           | $\text{V}_{\text{PEAK}}$ |

| Apparent Charge                             | $q_{\text{pd}}$    | Test method B1, $V_{\text{PR}} = 1.875 \times V_{\text{IORM}}$ , $t = 1 \text{ sec}$                                                                                     | 5                              | pC                       |

| PACKAGE CHARACTERISTICS                     |                    |                                                                                                                                                                          |                                |                          |

| External Clearance                          | CLR                | Measured from input terminals to output terminals, shortest distance through air                                                                                         | 8.3                            | mm                       |

| External Creepage                           | CPG                | Measured from input terminals to output terminals, shortest distance along body                                                                                          | 8.3                            | mm                       |

| Internal Clearance                          | DTI                | Distance through thin film insulation                                                                                                                                    | 21.5                           | $\mu\text{m}$            |

| Comparative Tracking Index                  | CTI                |                                                                                                                                                                          | >400                           | V                        |

| Material Group                              |                    |                                                                                                                                                                          | II                             |                          |

| Resistance (Input to Output) <sup>1</sup>   | $R_{\text{IO}}$    | $V_{\text{IO}} = 500 \text{ V}$ , $T_A = 25^\circ\text{C}$                                                                                                               | $10^{12}$                      | $\Omega$                 |

|                                             | $R_{\text{IO\_S}}$ | $V_{\text{IO}} = 500 \text{ V}$ , $T_A = T_S$                                                                                                                            | $10^9$                         | $\Omega$                 |

| Capacitance (Input to Output) <sup>1</sup>  | $C_{\text{IO}}$    | $f_{\text{TEST}} = 1 \text{ MHz}$                                                                                                                                        | 1.3                            | pF                       |

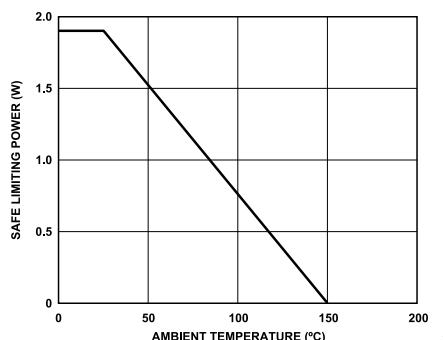

| SAFETY LIMITING VALUES                      |                    |                                                                                                                                                                          |                                |                          |

| Maximum Ambient Safety Temperature          | $T_S$              |                                                                                                                                                                          | 150                            | $^\circ\text{C}$         |

| Maximum Input Power Dissipation             | $P_S$              | Total Power Dissipation at $25^\circ\text{C}$                                                                                                                            | 1.90                           | W                        |

<sup>1</sup> Device is measured as a 2-terminal device.

Figure 7. Thermal Derating Curve, Dependence of Safety Limiting Values, per IEC 60747-17

## SPECIFICATIONS

### REGULATORY APPROVALS

The ADE9112 and ADE9113 are approved by the organizations listed in [Table 5](#). Certifications available on the [Safety and Regulatory Certification for Digital Isolation](#) web page.

Refer to [Table 5](#) for more information about the recommended maximum working voltages for specific cross-isolation waveforms and insulation levels.

**Table 5. ADE9112 and ADE9113 Regulatory Approvals**

| Regulatory Agency | Standard Certification/Approval                                                                                                                                             | File          |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| VDE               | Certified according to DIN EN IEC 60747-17 (VDE 0884-17):2021-10 and EN IEC 60747-17:2020+AC:2021<br>Reinforced insulation, see <a href="#">Table 4</a> for characteristics | (Pending)     |

| UL                | Recognized under the UL1577 Component Recognition Program<br>Single protection, 5000 V RMS isolation voltage                                                                | E214100       |

| TUV Sud           | EN IEC 62368-1:2020/A11:2020<br>Basic insulation at 830 V RMS<br>Reinforced insulation at 415 V RMS                                                                         | B 056232 0034 |

|                   | EN 61010-1:2020/A1:2019<br>Basic insulation at 600 V RMS mains<br>Reinforced insulation at 300 V RMS mains                                                                  | B 056232 0035 |

## ABSOLUTE MAXIMUM RATINGS

$T_A = 25^\circ\text{C}$ , unless otherwise noted.

Table 6. ADE9103 Absolute Maximum Ratings

| Parameter                                                 | Rating                |

|-----------------------------------------------------------|-----------------------|

| VDD to DGND                                               | -0.3 V to +3.7 V      |

| Analog Input Voltage                                      |                       |

| IP and IM to DGND                                         | -1.4 V to +1.4 V      |

| V1P and V1M, to DGND                                      | -2.0 V to +2.0 V      |

| V2P and V2M to DGND                                       | -1 V to +1 V          |

| Digital Input Voltage                                     |                       |

| MOSI, SCLK, CS, <u>RESET</u> , and XTALIN to DGND         | -0.3 V to VDD + 0.3 V |

| Digital Output Voltage                                    |                       |

| <u>IRQ</u> , ZX, CLKOUT, MISO, SCLK, and XTAL-OUT to DGND | -0.3 V to VDD + 0.3 V |

| Temperature                                               |                       |

| Operating                                                 | -40°C to +125°C       |

| Storage Range                                             | -65°C to +150°C       |

| Lead (Soldering, 10 sec) <sup>1</sup>                     | 260°C                 |

| Moisture Sensitivity Level                                | MSL3                  |

<sup>1</sup> Analog Devices recommends that reflow profiles used in soldering RoHS-compliant devices conform to J-STD-020D.1 from JEDEC. Refer to JEDEC for the latest revision of this standard.

Table 7. ADE9112/ADE9113 Absolute Maximum Ratings

| Parameter                                                | Rating                   |

|----------------------------------------------------------|--------------------------|

| VDD to DGND and AVDD to AGND                             | -0.3 V to +3.7 V         |

| Analog Input Voltage                                     |                          |

| IP and IM to AGND                                        | -1.4 V to +1.4 V         |

| V1P and V1M to AGND                                      | -2.0 V to +2.0 V         |

| V2P and V2M to AGND                                      | -1 V to +1 V             |

| Digital Input Voltage                                    |                          |

| MOSI, SCLK, CS, <u>RESET</u> , and XTALIN to DGND        | -0.3 V to VDD + 0.3 V    |

| Digital Output Voltage                                   |                          |

| <u>IRQ</u> , ZX, CLKOUT, MISO, SCLK, and XTALOUT to DGND | -0.3 V to VDD + 0.3 V    |

| Common-Mode Transients <sup>1</sup>                      | -150 kV/μs to +150 kV/μs |

| Temperature                                              |                          |

| Operating Range                                          | -40°C to +125°C          |

| Storage Range                                            | -65°C to +150°C          |

| Lead (Soldering, 10 sec) <sup>2</sup>                    | 260°C                    |

| Moisture Sensitivity Level                               | MSL3                     |

<sup>1</sup> Refers to common-mode transients across the insulation barrier. Common-mode transients exceeding the absolute maximum ratings may cause latch-up or permanent damage.

<sup>2</sup> Analog Devices recommends that reflow profiles used in soldering RoHS-compliant devices conform to J-STD-020D.1 from JEDEC. Refer to JEDEC for the latest revision of this standard.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction-to-ambient thermal resistance measured in a one cubic foot sealed enclosure, and  $\theta_{JC}$  is the junction-to-case thermal resistance.

Table 8. Thermal Resistance

| Package Type | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|--------------|---------------|---------------|------|

| RN-28-1      | 65.69         | 36.19         | °C/W |

## ELECTROSTATIC DISCHARGE (ESD) RATINGS

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

Charged device model (CDM) per ANSI/ESDA/JEDEC JS-002.

## ESD Ratings for ADE9103

Table 9. ADE9103, 28-Lead SOIC\_W\_FP

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | ±4000                   | 3A    |

| CDM       | ±1250                   | C3    |

## ESD Ratings for ADE9112 and ADE9113

Table 10. ADE9112 and ADE9113, 28-Lead SOIC\_W\_FP

| ESD Model <sup>1</sup> | Withstand Threshold (V) | Class |

|------------------------|-------------------------|-------|

| HBM                    | ±4000                   | 3A    |

| CDM                    | ±1250                   | C3    |

<sup>1</sup> With respect to local VDD and AGND, and DGND and GND<sub>ISO</sub> pins.

## ESD CAUTION

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

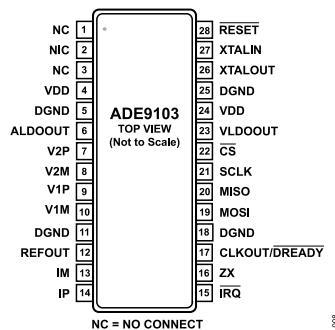

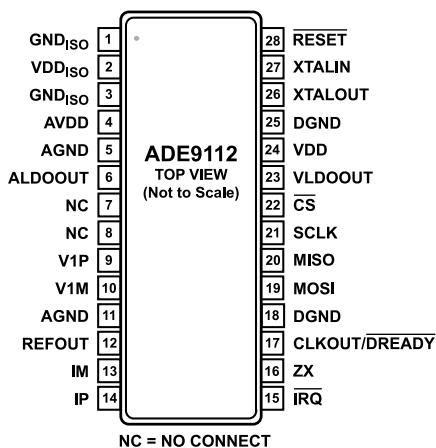

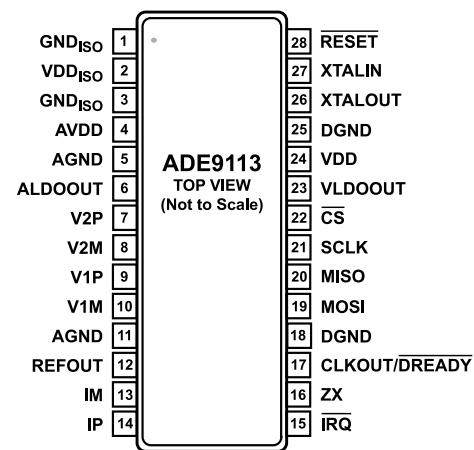

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 8. ADE9103 Pin Configuration

Table 11. ADE9103 Pin Function Descriptions

| Pin No.       | Mnemonic      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3          | NC            | No Connect. Pin 1 and Pin 3 are connected together internally. These NC pins have no internal connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2             | NIC           | Not Connected Internally. The NIC pin has no internal connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4, 24         | VDD           | Primary Supply Voltage. The VDD pins provide the supply voltage for the ADE9103. Maintain the supply voltage at $3.3\text{ V} \pm 10\%$ for the specified operation. Decouple the VDD pins to the closest DGND pin with a $4.7\text{ }\mu\text{F}$ capacitor in parallel with a ceramic $100\text{ nF}$ capacitor.                                                                                                                                                                                                                                                                                                                                                   |

| 5, 11, 18, 25 | DGND          | Ground Reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6             | ALDOOUT       | 1.8 V Output of Analog LDO Regulator. Decouple the ALDOOUT pin with a $4.7\text{ }\mu\text{F}$ capacitor in parallel with a ceramic $100\text{ nF}$ capacitor to DGND, Pin 5. Do not connect the external load circuitry to the ALDOOUT pin.                                                                                                                                                                                                                                                                                                                                                                                                                         |

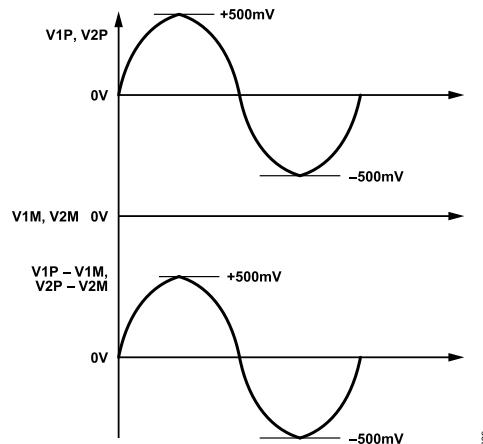

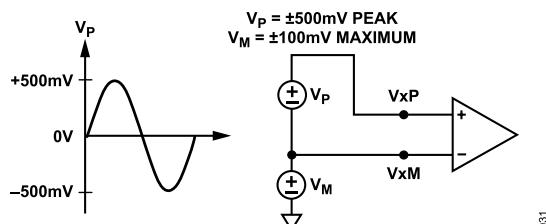

| 7             | V2P           | Positive Analog Input for the V2 Voltage Channel. V2P and V2M are differential voltage inputs with a maximum single-ended signal level of $\pm 500\text{ mV}$ with respect to the VxM pins for specified operation. Use the V2P and V1P pins with the related input circuitry, as shown in Figure 27. If the V2 voltage channel is not used, connect the V2P pin to the V2M pin.                                                                                                                                                                                                                                                                                     |

| 8             | V2M           | Negative Analog Input for the V2 Voltage Channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9             | V1P           | Positive Analog Inputs for the V1 Voltage Channel. The voltage channels are used with the voltage transducers. V1P and V1M are differential voltage inputs with a maximum single-ended signal level of $\pm 500\text{ mV}$ with respect to the VxM pins for specified operation. Use the V1P and V2P pins with the related input circuitry, as shown in Figure 27. If the V1 voltage channel is not used, connect the V1P pin to the V1M pin.                                                                                                                                                                                                                        |

| 10            | V1M           | Negative Analog Input for the V1 Voltage Channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12            | REFOUT        | Voltage Reference Output. The REFOUT pin provides access to the on-chip voltage reference. The on-chip reference has a nominal value of 1.25 V. Decouple the REFOUT pin to DGND, Pin 11, with a $4.7\text{ }\mu\text{F}$ capacitor in parallel with a ceramic $100\text{ nF}$ capacitor. Do not connect external load circuitry to the REFOUT pin.                                                                                                                                                                                                                                                                                                                   |

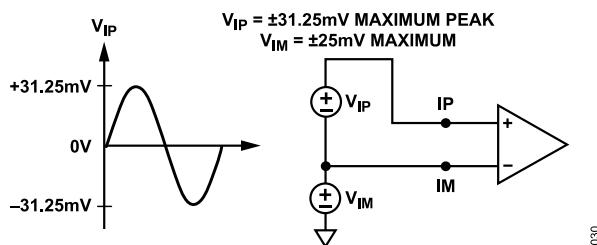

| 13            | IM            | Negative Analog Input for the Current Channel. The current channel is used with shunts. IM and IP are pseudo differential voltage inputs with a maximum differential level of $\pm 31.25\text{ mV}$ . Use the IM and IP pins with the related input circuitry, as shown in Figure 27.                                                                                                                                                                                                                                                                                                                                                                                |

| 14            | IP            | Positive Analog Input for the Current Channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15            | IRQ           | Interrupt Request Output. The IRQ pin is an active low logic open drain output with weak internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 16            | ZX            | Zero-Crossing Output Pin. The ZX pin must float when unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 17            | CLKOUT/DREADY | Clock Output (CLKOUT). When CLKOUT functionality is selected (see the <a href="#">Synchronizing Multiple ADE9103/ADE9112/ADE9113 Devices</a> section for details), the ADE9103 generates a digital signal synchronous to the main clock at the XTALIN pin. Use CLKOUT to provide a clock to other ADE9103/ADE9112/ADE9113 devices. Data Ready, Active Low (DREADY). When DREADY functionality is selected (see the <a href="#">Synchronizing Multiple ADE9103/ADE9112/ADE9113 Devices</a> section for details), the ADE9103 generates an active low signal synchronous to the ADC output frequency. Use this signal to start reading the ADC outputs of the ADE9103. |

| 19            | MOSI          | Data Input for the SPI Port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 20            | MISO          | Data Output for the SPI Port. Attach a $10\text{ k}\Omega$ pull-up resistor to the VDD supply voltage for increased electromagnetic compatibility (EMC) robustness.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 21            | SCLK          | Serial Clock Input for the SPI Port. All serial data transfers are synchronized to this clock (see Table 3 for SPI interface timing parameters and <a href="#">SPI Compatible Communication</a> section for additional SPI port details).                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 22            | CS            | Chip Select for the SPI Port (Active Low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

**PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS****Table 11. ADE9103 Pin Function Descriptions (Continued)**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23      | VLDOOUT  | 1.8 V Output of Digital LDO Regulator. Decouple the VLDOOUT pin with a 4.7 $\mu$ F capacitor in parallel with a ceramic 100 nF capacitor to DGND, Pin 25. Do not connect the external load circuitry to the VLDOOUT pin.                                                                                                                                                                                                                                                                          |

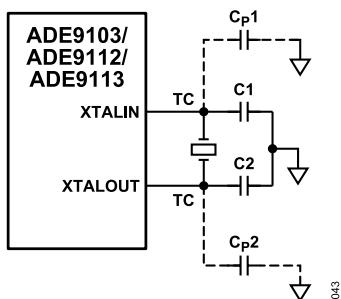

| 26      | XTALOUT  | Crystal Output. A crystal must be chosen based on the transconductance ( $g_m$ ) in <a href="#">Table 2</a> . The crystal is connected across the XTALIN and XTALOUT pins to provide a clock source for the ADE9103. The XTALOUT pin must float when unused.                                                                                                                                                                                                                                      |

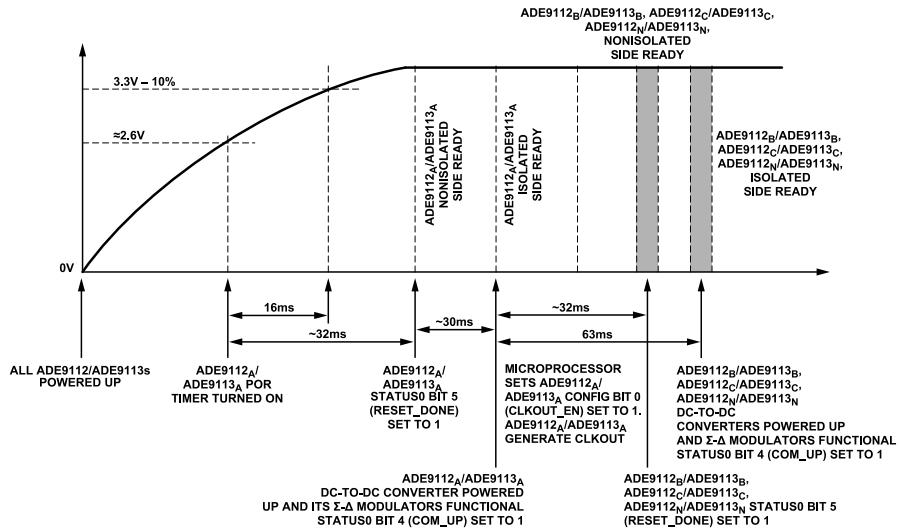

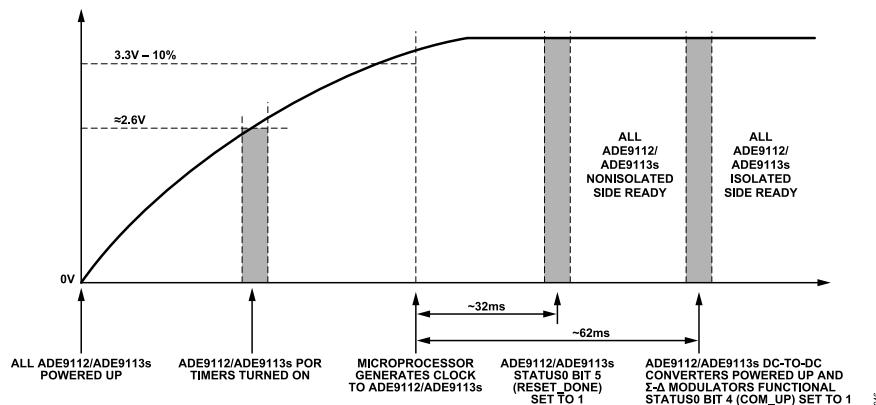

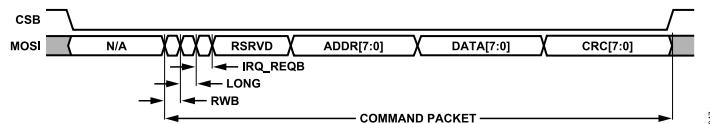

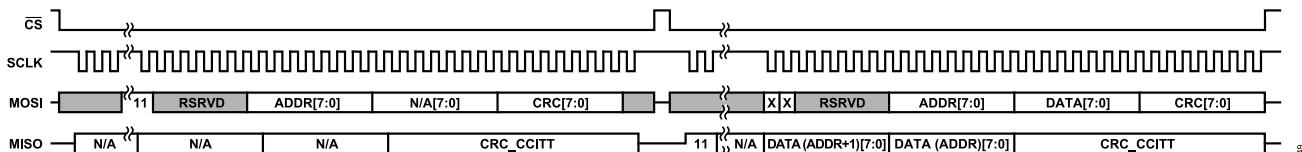

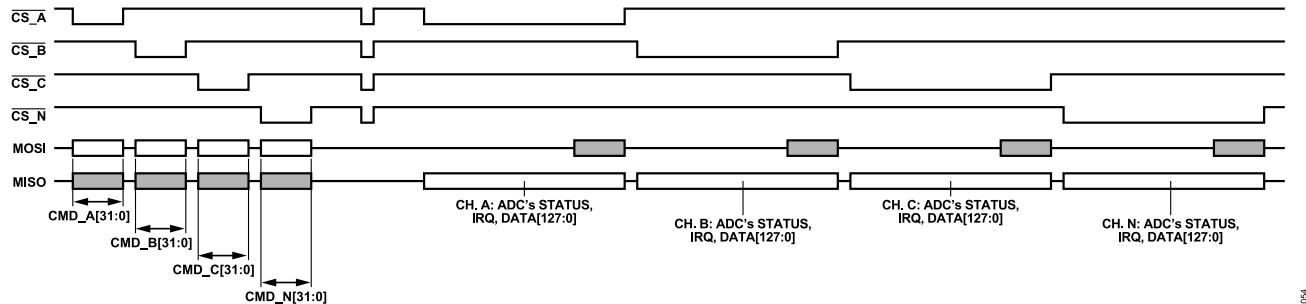

| 27      | XTALIN   | Main Clock Input. An external clock can be provided at this logic input. The CLKOUT signal of another appropriately configured ADE9103/ADE9112/ADE9113 (see the <a href="#">Synchronizing Multiple ADE9103/ADE9112/ADE9113 Devices</a> section for details) can be provided at the XTALIN pin. Alternatively, a crystal can be connected across XTALIN and XTALOUT to provide a clock source for the ADE9103. See the <a href="#">Crystal Oscillator/External Clock</a> section for more details. |