## Contents

|        |                                                                  |    |

|--------|------------------------------------------------------------------|----|

| 1      | Brief Description .....                                          | 2  |

| 2      | Electrical Characteristics .....                                 | 3  |

| 2.1.   | Absolute Maximum Ratings .....                                   | 3  |

| 2.2.   | Operating Conditions .....                                       | 4  |

| 2.3.   | Electrical Parameters .....                                      | 5  |

| 2.3.1. | Supply Current and System Operation Conditions .....             | 5  |

| 2.3.2. | Analog Front-End Characteristics .....                           | 5  |

| 2.3.3. | Temperature Measurement .....                                    | 5  |

| 2.3.4. | Sensor Diagnostics .....                                         | 6  |

| 2.3.5. | A2D Conversion .....                                             | 6  |

| 2.3.6. | DAC and Analog Output (AOUT Pin) .....                           | 6  |

| 2.3.7. | System Response .....                                            | 7  |

| 2.4.   | Interface Characteristics and Nonvolatile Memory .....           | 8  |

| 2.4.1. | I <sup>2</sup> C <sup>TM</sup> Interface .....                   | 8  |

| 2.4.2. | ZACwire <sup>TM</sup> One-Wire Interface (OWI at AOUT pin) ..... | 8  |

| 2.4.3. | Nonvolatile Memory (NVM) .....                                   | 9  |

| 3      | ESD Protection and EMC Specification .....                       | 10 |

| 3.1.   | ESD Protection .....                                             | 10 |

| 3.2.   | Latch-Up Immunity .....                                          | 10 |

| 3.3.   | Electromagnetic Emission .....                                   | 10 |

| 3.4.   | Conducted Susceptibility (DPI) .....                             | 10 |

| 4      | Reliability and RoHS Conformity .....                            | 11 |

| 5      | Glossary .....                                                   | 11 |

| 6      | Document Revision History .....                                  | 12 |

## List of Figures

|            |                              |   |

|------------|------------------------------|---|

| Figure 1.1 | ZSSC4151 Block Diagram ..... | 2 |

|------------|------------------------------|---|

## List of Tables

|           |                                                        |    |

|-----------|--------------------------------------------------------|----|

| Table 2.1 | Absolute Maximum Ratings .....                         | 3  |

| Table 2.2 | Operating Conditions .....                             | 4  |

| Table 2.3 | Electrical Parameters .....                            | 5  |

| Table 2.4 | Interface Characteristics and Nonvolatile Memory ..... | 8  |

| Table 3.1 | Conducted Susceptibility (DPI) Tests .....             | 10 |

## 1 Brief Description

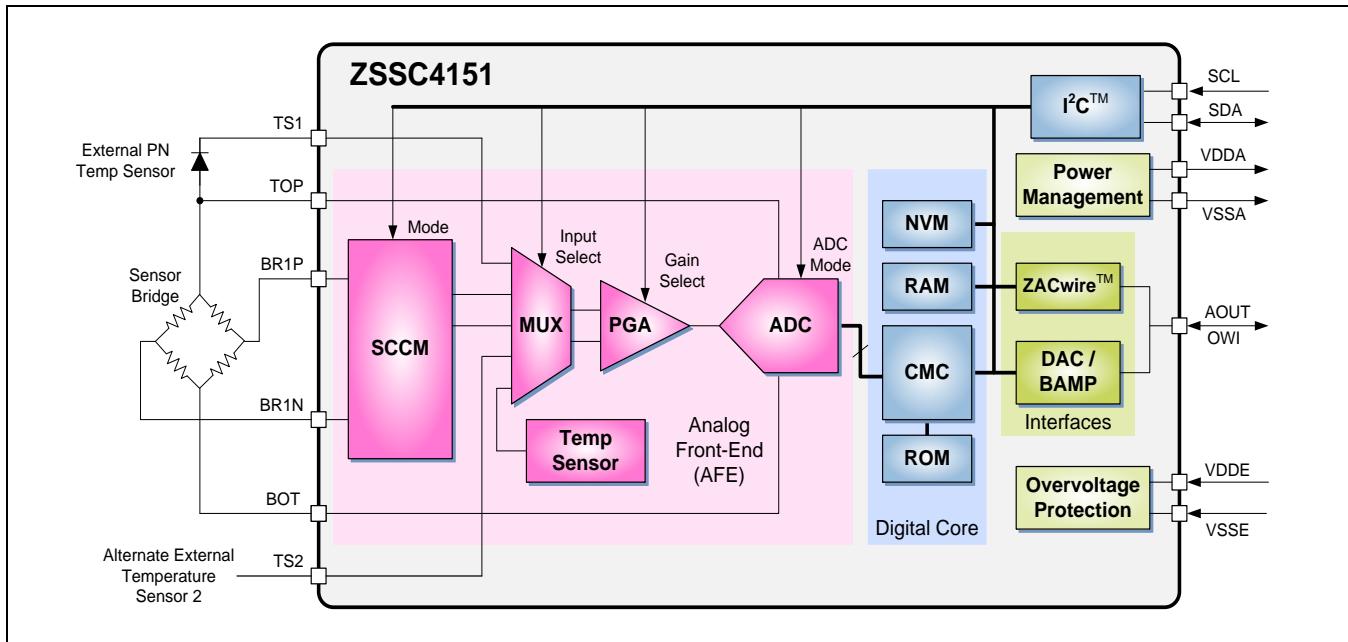

The ZSSC4151 sensor signal conditioner (SSC) is a CMOS integrated circuit for highly accurate amplification and sensor-specific correction of bridge sensor signals. Digital compensation of sensor offset, sensitivity, temperature drift, and non-linearity is accomplished via an internal 16-bit RISC microcontroller running a correction algorithm with calibration coefficients stored in an EEPROM.

The ZSSC4151 is adjustable to nearly all bridge sensor types. Measured values are provided at the analog voltage output and at the digital I<sup>2</sup>C™\* or ZACwire™ interface, also referred to as the One-Wire Interface (OWI). The digital interfaces can be used for a simple PC-controlled calibration procedure in order to program a set of calibration coefficients into an on-chip EEPROM. The specific sensor and the ZSSC4151 can be quickly calibrated together. The ZSSC4151 and the calibration equipment communicate digitally, so the noise sensitivity is greatly reduced. Digital calibration helps keep assembly cost low as no trimming by external devices or lasers is needed.

The ZSSC4151 is optimized for automotive environments by overvoltage and reverse-polarity protection circuitry, excellent electromagnetic compatibility, full automotive temperature range, and multiple diagnostic features.

Figure 1.1 provides a block diagram of the ZSSC4151. Refer to section 5 for definitions of abbreviations.

**Figure 1.1 ZSSC4151 Block Diagram**

\* I<sup>2</sup>C™ is a trademark of NXP.

## 2 Electrical Characteristics

**Important note:** The *absolute maximum ratings* given in section 2.1 are stress ratings only. The ZSSC4151 might not function or be operable above the *recommended operating conditions*. Stresses exceeding the *absolute maximum ratings* might also damage the device. In addition, extended exposure to stresses above the *recommended operating conditions* might affect device reliability. IDT does not recommend designing to the specifications given under “Absolute Maximum Ratings.”

**Important note:** The *operating conditions* given in section 2.2 set the conditions over which IDT specifies device operation. These are the conditions that the application circuit should provide to the device for it to function as intended. Unless otherwise noted, the limits for parameters that appear in the *operating conditions* section are used as test conditions for the limits given in the *electrical characteristics* (section 2.3), *operating conditions*, and *interface characteristics and nonvolatile memory* sections.

### 2.1. Absolute Maximum Ratings

**Table 2.1 Absolute Maximum Ratings**

| No.   | Parameter                 | Symbol            | Conditions | Min  | Max       | Unit |

|-------|---------------------------|-------------------|------------|------|-----------|------|

| 2.1.1 | Supply voltage            | VDDE              |            | -40  | 40        | VDC  |

| 2.1.2 | Voltage at AOUT pin       | V <sub>AOUT</sub> |            | -40  | 40        | VDC  |

| 2.1.3 | Analog supply voltage     | VDDA              |            | -0.3 | 6.5       | VDC  |

| 2.1.4 | Digital supply voltage    | VDD               |            | -0.3 | 1.98      | VDC  |

| 2.1.5 | Voltage at all other pins | V <sub>PIN</sub>  |            | -0.3 | VDDA +0.3 | V    |

| 2.1.6 | Storage temperature       | T <sub>STG</sub>  |            | -55  | 160       | °C   |

## 2.2. Operating Conditions

All voltages in this section are relative to VSSA.

**Table 2.2 Operating Conditions**

Note: See important notes at the end of the table.

| No.   | Parameter                           | Symbol                | Conditions                                           | Min          | Typical | Max  | Unit |

|-------|-------------------------------------|-----------------------|------------------------------------------------------|--------------|---------|------|------|

| 2.2.1 | Supply voltage                      | VDDE                  | To VSSE                                              | 4.5          | 5       | 5.5  | V    |

|       |                                     | VDDA                  | To VSSA<br>VDDE minus drop through protection switch | (VDDE - 0.1) |         | VDDE | V    |

| 2.2.2 | Junction temperature                | T <sub>TQE</sub>      | Extended Temperature Range (TQE)                     | -40          |         | 150  | °C   |

|       |                                     | T <sub>AMB_TQA</sub>  | Advanced-Performance Temperature Range (TQA)         | -40          |         | 125  | °C   |

|       |                                     | T <sub>AMB_TQI</sub>  | Best-Performance Temperature Range (TQI)             | -25          |         | 85   | °C   |

| 2.2.3 | Bridge resistance <sup>1), 2)</sup> | R <sub>BR</sub>       |                                                      | 2            |         | 10   | kΩ   |

|       |                                     | R <sub>BR_10-90</sub> | Output range 10-90%                                  | 1            |         | 15   | kΩ   |

1) No measurement in mass production; parameter is guaranteed by design and/or quality observation.

2) R<sub>BR</sub> greater than the maximum limit results in higher noise.

## 2.3. Electrical Parameters

All parameter values in this section are valid under the operating conditions specified in section 2.2. All voltages referenced to VSSA.

Note: All parameters measured/validated for  $r_{ADC} = 14$ -bit; segmentation of 1<sup>st</sup> and 2<sup>nd</sup> ADC stage = 8/6;  $f_{osc} = 8$ MHz; analog gain = ~100;  $T_{AMB\_TQE}$  (see specification 2.2.2).

**Table 2.3 Electrical Parameters**

Note: See important table notes at the end of the table (page 7).

| No.                                                          | Parameter                                            | Symbol         | Conditions                                                             | Min  | Typ | Max  | Unit           |

|--------------------------------------------------------------|------------------------------------------------------|----------------|------------------------------------------------------------------------|------|-----|------|----------------|

| <b>2.3.1. Supply Current and System Operation Conditions</b> |                                                      |                |                                                                        |      |     |      |                |

| 2.3.1.1                                                      | Supply current <sup>1)</sup>                         | $I_S$          | Oscillator adjusted (typical $f_{osc} = 8$ MHz).                       |      | 5.5 | 7    | mA             |

| 2.3.1.2                                                      | Sensor bridge supply voltage                         | $V_{SENS}$     | $V_{SENS} = V_{TOP} - V_{BOT}$ at $R_{BR} \geq 2k\Omega$               | 0.9  |     | 1    | VDDA           |

| 2.3.1.3                                                      | Oscillator frequency <sup>2)</sup>                   | $f_{osc}$      |                                                                        | 7.2  | 8   | 8.8  | MHz            |

| 2.3.1.4                                                      | Oscillator frequency temperature coefficient         | $T_{Cosc}$     |                                                                        | -200 |     | 200  | ppm/K          |

| <b>2.3.2. Analog Front-End Characteristics</b>               |                                                      |                |                                                                        |      |     |      |                |

| 2.3.2.1                                                      | Input span                                           | $V_{IN\_SPAN}$ | Analog gain = 1 to 200                                                 | 1    |     | 800  | mV/V           |

| 2.3.2.2                                                      | Common mode input range                              | $V_{IN\_CM}$   | Depends on gain adjustment                                             | 0.25 |     | 0.75 | $V_{SENS}$     |

| 2.3.2.3                                                      | External capacitance at input                        | $C_{IN\_EXT}$  | Capacitance at pins BR1P and BR1N to VSSA                              | 0    |     | 12   | nF             |

| 2.3.2.4                                                      | Input leakage current <sup>3)</sup>                  | $I_{IN\_leak}$ |                                                                        | -15  |     | 15   | nA             |

| <b>2.3.3. Temperature Measurement</b>                        |                                                      |                |                                                                        |      |     |      |                |

| 2.3.3.1                                                      | PTAT internal temperature sensitivity                | $ST_{TSI}$     | Raw values, without conditioning calculation<br>Analog gain setting= 6 | 20   |     |      | $LSB_{14} /K$  |

| 2.3.3.2                                                      | External temperature diode channel gain              | $A_{TSE\_D}$   |                                                                        | 10   |     |      | $LSB_{14} /mV$ |

| 2.3.3.3                                                      | External temperature diode bias current              | $I_{TSE\_D}$   |                                                                        | 10   | 20  | 40   | $\mu A$        |

| 2.3.3.4                                                      | External temperature diode input range <sup>3)</sup> | $V_{TSE\_D}$   | Relative to $V_{TOP}$                                                  | -1   |     | -0.2 | V              |

| No.                                            | Parameter                                                    | Symbol            | Conditions                                                                                      | Min  | Typ | Max  | Unit       |

|------------------------------------------------|--------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------|------|-----|------|------------|

| 2.3.3.5                                        | External RTD channel gain                                    | $A_{TSE\_RTD}$    |                                                                                                 | 10   |     |      | LSB /mV    |

| 2.3.3.6                                        | External RTD input range <sup>3)</sup>                       | $V_{TSE\_RTD}$    | Relative to VDDA                                                                                | -2   |     | -0.2 | V          |

| <b>2.3.4. Sensor Diagnostics</b>               |                                                              |                   |                                                                                                 |      |     |      |            |

| 2.3.4.1                                        | Sensor connection loss threshold                             | $R_{SCC\_open}$   |                                                                                                 | 100  |     |      | kΩ         |

| 2.3.4.2                                        | Sensor short threshold to BOT or TOP pin                     | $R_{SCC\_SH\_BT}$ |                                                                                                 |      |     | 50   | Ω          |

| 2.3.4.3                                        | Sensor short threshold between inputs                        | $R_{SCC\_SH\_IN}$ |                                                                                                 |      |     | 150  | Ω          |

| <b>2.3.5. A2D Conversion</b>                   |                                                              |                   |                                                                                                 |      |     |      |            |

| 2.3.5.1                                        | ADC resolution <sup>3)</sup>                                 | $r_{ADC}$         | Selection: 12, 14, 16 or 18 bit                                                                 | 12   |     | 18   | Bit        |

| 2.3.5.2                                        | DNL <sup>3)</sup>                                            | $DNL_{ADC}$       | Best fit; overall AFE; $V_{ADC\_IN}$ according to 2.3.6.4.                                      |      |     | 0.95 | LSB        |

| 2.3.5.3                                        | INL TQA temperature range (specified in 2.2.2) <sup>3)</sup> | $INL_{ADC\_TQA}$  | Best fit                                                                                        |      |     | 4    | LSB        |

| 2.3.5.4                                        | INL TQE temperature range (specified in 2.2.2)               | $INL_{ADC\_TQE}$  | At 14-bit resolution                                                                            |      |     | 8    | LSB        |

| 2.3.5.5                                        | ADC input range                                              | $V_{ADC\_IN}$     |                                                                                                 | 0.1  |     | 0.9  | $V_{SENS}$ |

| <b>2.3.6. DAC and Analog Output (AOUT Pin)</b> |                                                              |                   |                                                                                                 |      |     |      |            |

| 2.3.6.1                                        | DAC resolution                                               | $r_{DAC}$         | Analog output                                                                                   |      | 12  |      | Bit        |

| 2.3.6.2                                        | Output current sink/source                                   | $I_{OUT}$         | $V_{AOUT}: 5\text{-}95\%, R_{LOAD} \geq 5k\Omega$                                               |      |     | 2.5  | mA         |

|                                                |                                                              |                   | $V_{AOUT}: 10\text{-}90\%, R_{LOAD} \geq 1k\Omega$                                              |      |     | 5    | mA         |

| 2.3.6.3                                        | Short-circuit current (AOUT to VSSE or VDDE)                 | $I_{OUT\_max}$    | Short to VSSE or VDDE                                                                           | -25  |     | 25   | mA         |

| 2.3.6.4                                        | Addressable output range                                     | $V_{R\_OUT}$      |                                                                                                 | 0.01 |     | 0.99 | VDDE       |

| 2.3.6.5                                        | Load capacitance                                             | $C_{LOAD}$        | Defined for best EMC performance                                                                | 4    | 10  | 150  | nF         |

| 2.3.6.6                                        | Output slew rate                                             | $SR_{OUT}$        | $C_{LOAD} < 50nF$                                                                               | 0.1  |     |      | V/μs       |

| 2.3.6.7                                        | Clipping levels                                              | LowLim            | Configurable 8-bit value stored in NVM                                                          | 0    |     | 25   | %VDDE      |

|                                                |                                                              | UppLim            | Configurable 8-bit value stored in NVM                                                          | 75   |     | 100  | %VDDE      |

| 2.3.6.8                                        | Clipping adjustment step                                     |                   |                                                                                                 |      |     | 0.1  | %VDDE      |

| 2.3.6.9                                        | Output resistance in Diagnostic Mode                         | $R_{OUT\_DIA}$    | Diagnostic Range:<br>4% to 96%, $R_{LOAD} \geq 5k\Omega$<br>8% to 92%, $R_{LOAD} \geq 1k\Omega$ |      |     | 80   | Ω          |

| No.                           | Parameter                                                                                                                                                              | Symbol                 | Conditions                                                                   | Min   | Typ  | Max  | Unit  |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------|-------|------|------|-------|--|

| 2.3.6.10                      | DNL                                                                                                                                                                    | DNL <sub>OUT</sub>     | r <sub>DAC</sub> =12 bit                                                     | -1.5  |      | 1.5  | LSB   |  |

| 2.3.6.11                      | INL TQA temperature range (specified in 2.2.2) <sup>3)</sup>                                                                                                           | INL <sub>OUT</sub>     | Best fit, r <sub>DAC</sub> =12-Bit                                           | -5    |      | 5    | LSB   |  |

| 2.3.6.12                      | INL TQE temperature range (specified in 2.2.2)                                                                                                                         | INL <sub>OUT</sub>     | Best fit, r <sub>DAC</sub> =12-Bit                                           | -8    |      | 8    | LSB   |  |

| 2.3.6.13                      | Output leakage current at 125°C                                                                                                                                        | I <sub>LEAK_OUT</sub>  | In the event of power or ground loss                                         | -12   |      | 12   | µA    |  |

| 2.3.6.14                      | Output leakage current at 150°C                                                                                                                                        | I <sub>LEAK_OUT</sub>  | In the event of power or ground loss                                         | -20   |      | 20   | µA    |  |

| <b>2.3.7. System Response</b> |                                                                                                                                                                        |                        |                                                                              |       |      |      |       |  |

| 2.3.7.1                       | Startup time <sup>3), 4)</sup><br>(time to first valid output after power-on)                                                                                          | t <sub>STARTUP</sub>   | f <sub>OSC</sub> = 8MHz;<br>ADC: 14-bit and 2 <sup>nd</sup> order conversion |       |      | 5    | ms    |  |

| 2.3.7.2                       | Response time <sup>3), 4) 5)</sup>                                                                                                                                     | t <sub>RESPONSE</sub>  | 100% input step,<br>excluding transmission time                              |       |      | 1.1  | ms    |  |

| 2.3.7.3                       | Bandwidth <sup>3)</sup>                                                                                                                                                |                        | In comparison to analog signal conditioners;<br>66% jump                     |       | 1    |      | kHz   |  |

| 2.3.7.4                       | Analog output noise peak-to-peak <sup>3)</sup>                                                                                                                         | V <sub>NOISE,PP</sub>  | DAC and output buffer only;<br>bandwidth ≤ 10kHz                             |       |      | 10   | mV    |  |

| 2.3.7.5                       | Analog output noise RMS <sup>3)</sup>                                                                                                                                  | V <sub>NOISE,RMS</sub> | DAC and output buffer only;<br>bandwidth ≤ 10kHz                             |       |      | 3    | mV    |  |

| 2.3.7.6                       | Ratiometricity error <sup>3)</sup>                                                                                                                                     | RE <sub>OUT_5</sub>    | Maximum error of<br>VDDE range = 4.5V to 5.5V                                | -1000 |      | 1000 | ppm   |  |

| 2.3.7.7                       | Overall error <sup>6)</sup>                                                                                                                                            | F <sub>ALL</sub>       | TQA temperature range (specified in 2.2.2)                                   |       | 0.35 |      | % FSO |  |

|                               |                                                                                                                                                                        |                        | TQE temperature range (specified in 2.2.2)                                   |       | 0.5  |      |       |  |

| 1)                            | Excluding bridge supply current and excluding output current at AOUT pin.                                                                                              |                        |                                                                              |       |      |      |       |  |

| 2)                            | Oscillator frequency can be trimmed via a setting in nonvolatile memory (NVM).                                                                                         |                        |                                                                              |       |      |      |       |  |

| 3)                            | No measurement in mass production; parameter is guaranteed by design and/or quality observation.                                                                       |                        |                                                                              |       |      |      |       |  |

| 4)                            | No bridge settling included in timing.                                                                                                                                 |                        |                                                                              |       |      |      |       |  |

| 5)                            | Dependent on the configuration. The specified limit is valid only for ADC resolutions ≤15 bits.                                                                        |                        |                                                                              |       |      |      |       |  |

| 6)                            | FSO: full-scale output. No sensor-caused effects included in overall error. ADC input range from 10% to 90% of V <sub>SENS</sub> ; DAC from 5% to 95% of output range. |                        |                                                                              |       |      |      |       |  |

## 2.4. Interface Characteristics and Nonvolatile Memory

**Table 2.4 Interface Characteristics and Nonvolatile Memory**

Note: See important table notes at the end of the table.

| No.                                                                     | Parameter                                                       | Symbol                    | Conditions                                                   | Min   | Typ  | Max   | Unit                   |

|-------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------|--------------------------------------------------------------|-------|------|-------|------------------------|

| <b>2.4.1. I<sup>2</sup>C<sup>TM</sup> Interface</b>                     |                                                                 |                           |                                                              |       |      |       |                        |

| 2.4.1.1                                                                 | I <sup>2</sup> C <sup>TM</sup> voltage level HIGH <sup>1)</sup> | V <sub>I2C_HIGH</sub>     |                                                              | 0.5   |      |       | VDDA                   |

| 2.4.1.2                                                                 | I <sup>2</sup> C <sup>TM</sup> voltage level LOW <sup>1)</sup>  | V <sub>I2C_LOW</sub>      |                                                              |       |      | 0.2   | VDDA                   |

| 2.4.1.3                                                                 | Slave output level LOW <sup>1)</sup>                            | V <sub>I2C_LOW_OUT</sub>  | Open drain, I <sub>OL</sub> < 4mA                            |       |      | 0.1   | VDDA                   |

| 2.4.1.4                                                                 | SDA load capacitance <sup>1)</sup>                              | C <sub>I2C_SDA</sub>      |                                                              |       |      | 400   | pF                     |

| 2.4.1.5                                                                 | SCL clock frequency <sup>1)</sup>                               | f <sub>I2C</sub>          |                                                              |       |      | 400   | kHz                    |

| 2.4.1.6                                                                 | Internal pull-up resistor <sup>1)</sup>                         | R <sub>I2C_PULLUP</sub>   |                                                              | 25    |      | 100   | kΩ                     |

| <b>2.4.2. ZACwire<sup>TM</sup> One-Wire Interface (OWI at AOUT pin)</b> |                                                                 |                           |                                                              |       |      |       |                        |

| 2.4.2.1                                                                 | OWI voltage level HIGH <sup>1)</sup>                            | V <sub>OWI_IN_H</sub>     | Master to slave                                              | 0.75  |      |       | VDDE                   |

| 2.4.2.2                                                                 | OWI voltage level LOW <sup>1)</sup>                             | V <sub>OWI_IN_L</sub>     | Master to slave                                              |       |      | 0.2   | VDDE                   |

| 2.4.2.3                                                                 | Slave output level LOW <sup>1)</sup>                            | V <sub>OWI_OUT_L</sub>    | Open drain, I <sub>OL</sub> ≤ 2mA                            |       |      | 0.1   | VDDE                   |

| 2.4.2.4                                                                 | Start window <sup>1)</sup>                                      | t <sub>OWI_STARTWIN</sub> |                                                              | 100   |      | 300   | ms                     |

| 2.4.2.5                                                                 | Bus free time                                                   | t <sub>OWI_IDLE</sub>     | Between stop and next start                                  | 25    |      |       | μs                     |

| 2.4.2.6                                                                 | Hold time start condition                                       | t <sub>OWI_START</sub>    | Valid minimum f <sub>clk</sub>                               | 25    |      |       | μs                     |

| 2.4.2.7                                                                 | Bit time                                                        | t <sub>OWI_BIT</sub>      | Maximum range                                                | 20    |      | 8000  | μs                     |

|                                                                         |                                                                 |                           | Typical operating range                                      | 40    |      | 4000  | μs                     |

| 2.4.2.8                                                                 | Duty ratio bit '0'                                              | t <sub>OWI_0</sub>        |                                                              | 0.125 | 0.25 | 0.375 | t <sub>OWI_BIT</sub>   |

| 2.4.2.9                                                                 | Duty ratio bit '1'                                              | t <sub>OWI_1</sub>        |                                                              | 0.625 | 0.75 | 0.875 | t <sub>OWI_BIT</sub>   |

| 2.4.2.10                                                                | Hold time stop condition                                        | t <sub>OWI_STOP</sub>     | t <sub>OWI_BIT_L</sub> is the bit time of the last valid bit | 2     |      |       | t <sub>OWI_BIT_L</sub> |

| 2.4.2.11                                                                | Bit period deviation                                            | t <sub>OWI_BIT_DEV</sub>  |                                                              | 0.55  | 1.0  | 1.5   | t <sub>OWI_BIT</sub>   |

| No.                                                                                                 | Parameter                                              | Symbol         | Conditions                                       | Min | Typ | Max | Unit |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------|--------------------------------------------------|-----|-----|-----|------|

| <b>2.4.3. Nonvolatile Memory (NVM)</b>                                                              |                                                        |                |                                                  |     |     |     |      |

| 2.4.3.1                                                                                             | Junction temperature for NVM programming <sup>2)</sup> | $T_{AMB\_NVM}$ |                                                  | -40 |     | 150 | °C   |

| 2.4.3.2                                                                                             | Re-write cycles <sup>1)</sup>                          | $N_{NVM\_TQA}$ | For $T_{TQA}$ (see range in specification 2.2.2) | 100 |     |     |      |

| 2.4.3.3                                                                                             | Re-write cycles at 150°C                               | $N_{NVM\_TQE}$ | For $T_{TQE}$ (see range in specification 2.2.2) | 10  |     |     |      |

| 2.4.3.4                                                                                             | Data retention <sup>1)</sup>                           | $t_{NVM\_RET}$ | Temperature profile:<br>22h bake at 250°C        | 15  |     |     | Year |

| 2.4.3.5                                                                                             | Programming time <sup>1)</sup>                         | $t_{NVM\_WRI}$ | Per written word                                 |     | 2.2 | 5   | ms   |

| 1) No measurement in mass production; parameter is guaranteed by design and/or quality observation. |                                                        |                |                                                  |     |     |     |      |

| 2) Valid for dice. Note: Additional package and temperature range cause restrictions.               |                                                        |                |                                                  |     |     |     |      |

### 3 ESD Protection and EMC Specification

#### 3.1. ESD Protection

All pins have an ESD protection of  $\geq 2000\text{V}$  according to the Human Body Model (HBM, based on MIL883, Method 3015.7). The VDDE, VSSE, and AOUT pins have an additional ESD protection of  $\geq 4000\text{V}$  (HBM).

In addition, Charged Device Model (CDM) tests are processed with protection levels of  $\geq 750\text{V}$  for corner pins and  $\geq 500\text{V}$  for all other pins.

The level of ESD protection has been tested with devices in QFN24 4X4mm packages during the product qualification.

#### 3.2. Latch-Up Immunity

All pins pass  $\pm 100\text{mA}$  latch-up test based on testing that conforms to the standard EIA/JESD 78.

#### 3.3. Electromagnetic Emission

The wired emission of externally connected pins of the device is measured according to the following standard: *IEC 61967\_4:2002 + A1:2006*.

Measurements must be performed with the application circuits described in the *ZSSC4151 Application Description*.

For the off-board pins, the spectral power measured with the  $150\Omega$  method must not exceed the limits according to *IEC 61967\_4k, Annex B.4 code H10kN*. For the VSSE pin, the spectral power measured with the  $1\Omega$  method must not exceed the limits according to *IEC 61967\_4k, Annex B.4 code 15KmO*.

#### 3.4. Conducted Susceptibility (DPI)

The conducted susceptibility of externally connected pins of the device is measured according to the IEC 62132-4 standard, which describes the direct power injection (DPI) test method.

Measurements must be performed with the application circuit described in the *ZSSC4151 Application Description*.

Measurements are performed with an internal reference capacitor and internal temperature sensor. The sensing element is replaced by a resistive divider. Calibration is parameterized so that  $\sim 50\%$  VDDA is output.

Table 3.1 gives the specifications for the DPI tests. RES refers to the coupling impedance.

**Table 3.1 Conducted Susceptibility (DPI) Tests**

| Test                | Frequency Range   | Target (dBm) | Load Pins  | Protocol   | Error Band | Comment                                                  |

|---------------------|-------------------|--------------|------------|------------|------------|----------------------------------------------------------|

| DPI, direct coupled | 1MHz to 300MHz    | 26           | VDDE, AOUT | Analog out | $\pm 1\%$  | LOAD RES = $5\text{k}\Omega$<br>LOAD CAP = $10\text{nF}$ |

| DPI, direct coupled | 300MHz to 1000MHz | 32           | VDDE, AOUT | Analog out | $\pm 1\%$  | LOAD RES = $5\text{k}\Omega$<br>LOAD CAP = $10\text{nF}$ |

## 4 Reliability and RoHS Conformity

The ZSSC4151 is qualified according to the AEC-Q100 standard, operating temperature grade 0. The qualification is extended to 3000h for the High Temperature Operating Life (HTOL) Test for one lot. Two manufacturing lots of extended HTOL qualification data (minimum of 3000h test time) for the ZSSC4151 or other products using identical technology (metallization), the same package supplier, the same package style, and the same die size within a specific tolerance are used to prove the package and bond reliability in the range of 3000h HTOL.

A FIT rate  $\leq 10$  FIT (temperature = 55°C, confidence level = 60%) is guaranteed. A typical FIT rate of TSMC's CV018BCD technology, which is used for the ZSSC4151, is 1 FIT.

The ZSSC4151 complies with the RoHS directive and does not contain hazardous substances.

## 5 Glossary

| Term                           | Description                                                         |

|--------------------------------|---------------------------------------------------------------------|

| ADC                            | Analog-to-Digital Converter                                         |

| AEC                            | Automotive Electronics Council                                      |

| AFE                            | Analog Front-End                                                    |

| BAMP                           | Buffer Amplifier                                                    |

| BR                             | Bridge Sensor                                                       |

| CDM                            | Charged Device Model                                                |

| CM                             | Command Mode                                                        |

| CMC                            | Calibration Microcontroller                                         |

| DAC                            | Digital-to-Analog Converter                                         |

| DNL                            | Differential Nonlinearity                                           |

| DPI                            | Direct Power Injection                                              |

| EMC                            | Electromagnetic Compatibility                                       |

| ESD                            | Electrostatic Discharge                                             |

| FIT                            | Failures in Time                                                    |

| FSO                            | Full Scale Output                                                   |

| HBM                            | Human Body Model                                                    |

| HTOL                           | High Temperature Operating Life                                     |

| I <sup>2</sup> C <sup>TM</sup> | Inter-Integrated Circuit—serial two-wire data bus, trademark of NXP |

| INL                            | Integral Nonlinearity                                               |

| LSB                            | Least Significant Bit                                               |

| MUX                            | Multiplexer                                                         |

| NVM                            | Nonvolatile Memory                                                  |

| Term          | Description                                                           |

|---------------|-----------------------------------------------------------------------|

| OWI           | One-Wire Interface                                                    |

| PGA           | Programmable Gain Amplifier                                           |

| PTAT          | Proportional-to-Absolute Temperature                                  |

| PTC           | Thermistor – Positive Temperature Coefficient Resistor                |

| PWR           | Power Management and Protection Unit                                  |

| QFN           | Quad-Flat No-Leads – IC package                                       |

| RAM           | Random Access Memory                                                  |

| RISC          | Reduced Instruction Set Computing                                     |

| ROM           | Read-Only Memory                                                      |

| RMS           | Root-Mean-Square                                                      |

| RTD           | Resistance Temperature Device                                         |

| SCCM          | Sensor Check and Common Mode Adjustment Unit                          |

| SCL           | Serial Clock                                                          |

| SDA           | Serial Data                                                           |

| SSC           | Sensor Short Check (diagnostic feature) or Sensor Signal Conditioner  |

| TQA, TQE, TQI | Temperature range identifier. See specification 2.2.2 for definition. |

| ZACwire™      | IDT-specific One-Wire Interface                                       |

## 6 Document Revision History

| Revision | Date               | Description                                                                                                                                                                                                                                                                                                                                                              |

|----------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.00     | September 13, 2015 | First release.                                                                                                                                                                                                                                                                                                                                                           |

| 1.01     | November 10, 2015  | Extended leakage current description in section 2.3.6 for specifications 2.3.6.13 and 2.3.6.14<br>Updates for table notes for Table 2.3.<br>Revision of pin names BRP to BR1P and BRN to BR1N.                                                                                                                                                                           |

| 1.02     | April 12, 2016     | Added minimum value for ratiometricity error in Table 2.3.<br>Updated section 4 regarding completion of AEC-Q100 qualification and extension of the minimum test time to 3000h.<br>Updated specification 2.3.7.7 for improved accuracy of $\pm 0.35\%$ of FSO at $-40^\circ\text{C}$ to $125^\circ\text{C}$ and 0.5% FSO at $-40^\circ\text{C}$ to $150^\circ\text{C}$ . |

|          | April 20, 2016     | Changed to IDT branding.                                                                                                                                                                                                                                                                                                                                                 |

**Corporate Headquarters**

6024 Silver Creek Valley Road

San Jose, CA 95138

[www.IDT.com](http://www.IDT.com)

**Sales**

1-800-345-7015 or 408-284-8200

Fax: 408-284-2775

[www.IDT.com/go/sales](http://www.IDT.com/go/sales)

**Tech Support**

[www.IDT.com/go/support](http://www.IDT.com/go/support)

**DISCLAIMER** Integrated Device Technology, Inc. (IDT) reserves the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit [www.IDT.com/go/glossary](http://www.IDT.com/go/glossary). All contents of this document are copyright of Integrated Device Technology, Inc. All rights reserved.

# Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

[IDT \(Integrated Device Technology\):](#)

[ZSSC4151BE2R](#) [ZSSC4151AE2W](#) [ZSSC4151AE2R](#) [ZSSC4151AE2V](#) [ZSSC4151KE2R](#) [ZSSC4151KE2V](#)

[ZSSC4151CE4R](#) [ZSSC4151CE4V](#) [ZSSC4151CE4W](#)