# Current Sense Amplifier, 80 V Common-Mode Voltage, Unidirectional

## Product Preview

### NCS7030, NCS7031, NCV7030, NCV7031

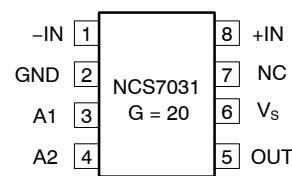

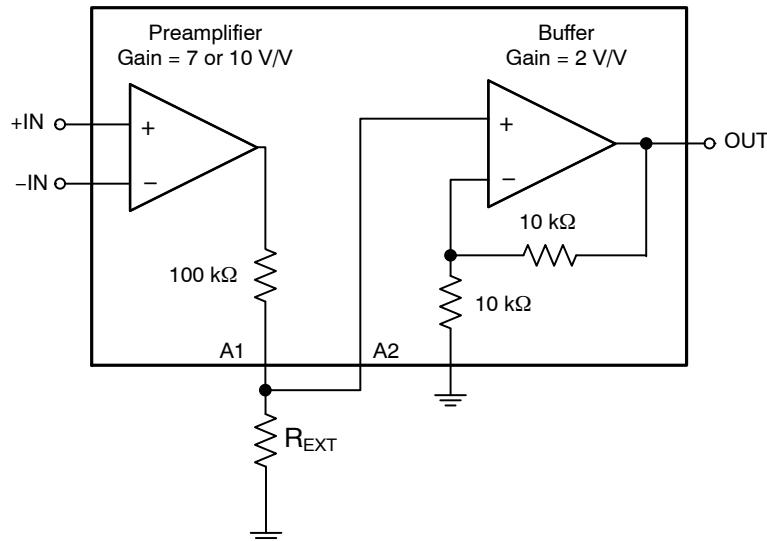

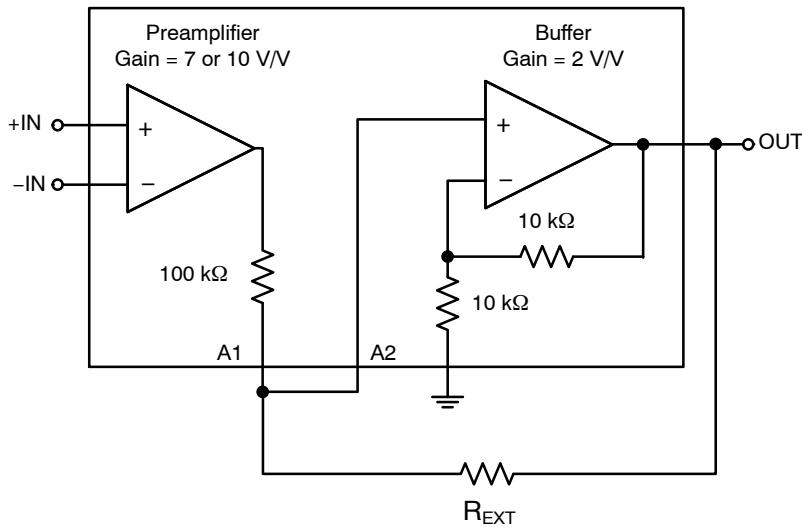

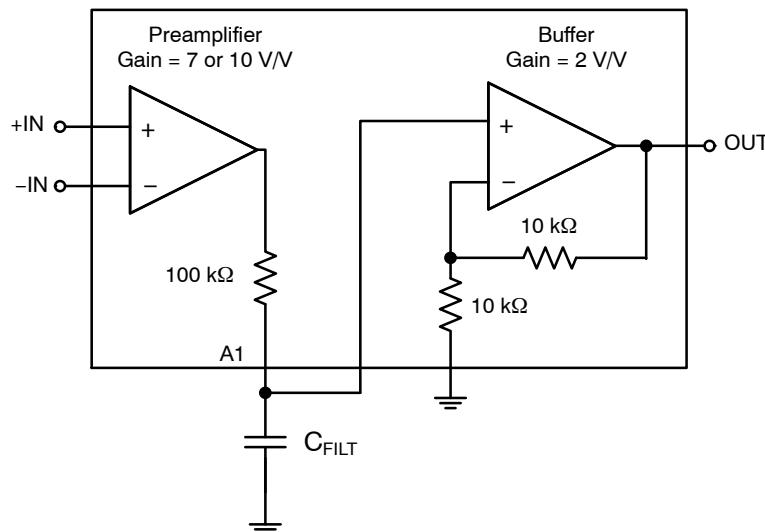

The NCS7030 and NCS7031 are high voltage, current sense amplifiers. They are available with gain options of 14 V/V and 20 V/V, with a maximum  $\pm 0.3\%$  gain error over the entire temperature range. Each part consists of a preamplifier and buffer with access to output and input via A1 and A2 pins for an intermediate filter network or modified gain. The current sense amplifiers offer excellent input common-mode rejection from  $-6\text{ V}$  to  $80\text{ V}$ . They can perform unidirectional current measurements across a sense resistor in a variety of applications. Automotive qualified options are available under NCV prefix. All versions operate over the extended temperature range from  $-40^\circ\text{C}$  to  $150^\circ\text{C}$ .

#### Features

- Bandwidth: 100 kHz

- Input Offset Voltage:  $\pm 300\text{ }\mu\text{V}$  Max Over Temp

- Offset Drift over Temperature:  $\pm 3\text{ }\mu\text{V}/^\circ\text{C}$  max

- Gain Error:  $\pm 0.3\%$  Max Over Temp

- Quiescent Current: 1.5 mA Typ

- Supply Voltage: 3 V to 5.5 V

- Common-Mode Input Voltage Range:  $-6\text{ V}$  to  $80\text{ V}$  Operating,  $-14\text{ V}$  to  $85\text{ V}$  Survival

- CMRR: 85 dB Min

- PSRR: 75 dB Min

- Low-Pass Filter (1-pole or 2-pole)

- This is a Pb-Free Device

#### Typical Applications

- Telecom Equipment

- Power Supply Designs

- Diesel Injection Control

- Automotive

- Motor Control

This document contains information on a product under development. **onsemi** reserves the right to change or discontinue this product without notice.

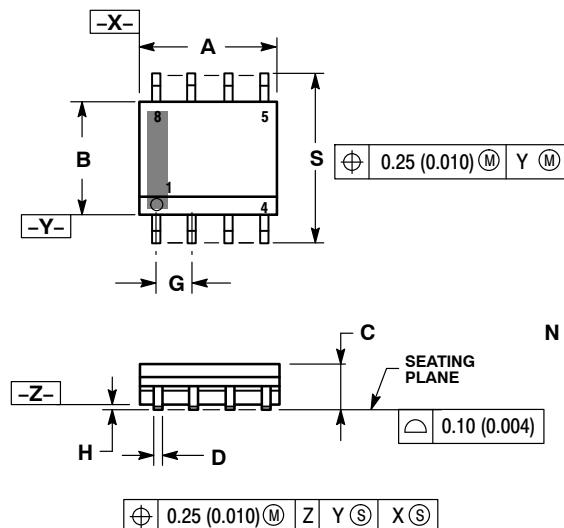

Micro8

CASE 846A-02

SOIC-8 NB

CASE 751-07

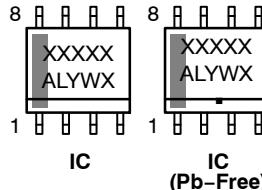

#### MARKING DIAGRAM

XXXXX = Specific Device Code

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

■ = Pb-Free Package

(Note: Microdot may be in either location)

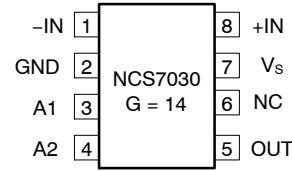

#### PIN CONNECTIONS

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 15 of this data sheet.

# NCS7030, NCS7031, NCV7030, NCV7031

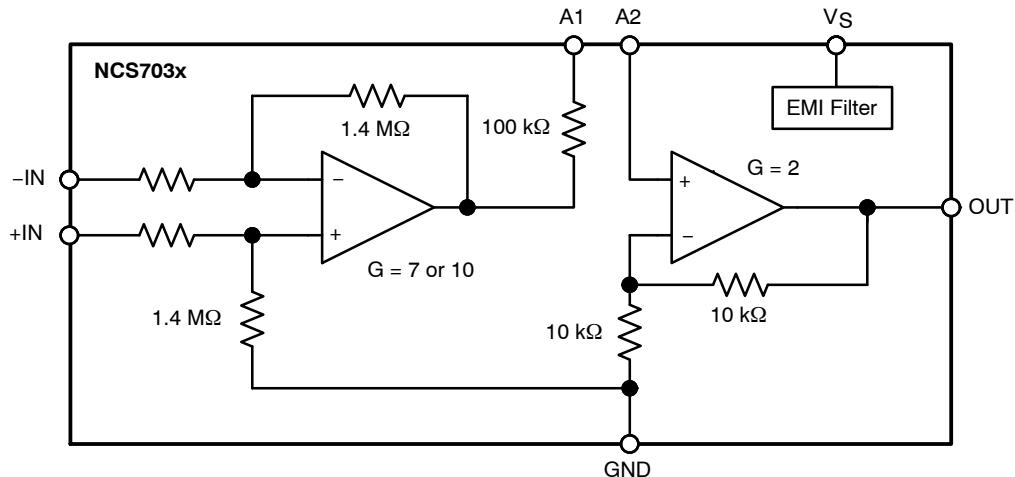

Figure 1. Simplified Block Diagram

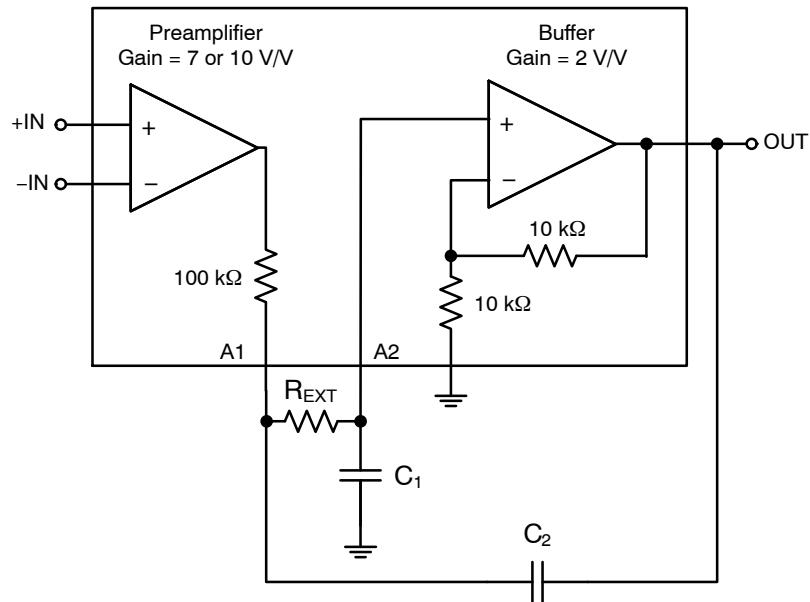

Figure 2. Application Schematic

## PIN FUNCTION DESCRIPTION

| NCS7031 (G = 20) Pinout | NCS7030 (G = 14) Pinout | Pin Name       | Description                                     |

|-------------------------|-------------------------|----------------|-------------------------------------------------|

| 1                       | 1                       | -IN            | Inverting input – connect to sense resistor     |

| 2                       | 2                       | GND            | Device ground                                   |

| 3                       | 3                       | A1             | Pre-amp output connection                       |

| 4                       | 4                       | A2             | Buffer amp input connection                     |

| 5                       | 5                       | OUT            | Device output                                   |

| 6                       | 7                       | V <sub>S</sub> | Power supply connection                         |

| 7                       | 6                       | NC             | No connect                                      |

| 8                       | 8                       | +IN            | Non-inverting input – connect to sense resistor |

# NCS7030, NCS7031, NCV7030, NCV7031

## ABSOLUTE MAXIMUM RATINGS

| Rating                                                                            | Symbol       | Value      | Unit |

|-----------------------------------------------------------------------------------|--------------|------------|------|

| Supply Voltage Range (Note 1)                                                     | $V_S$        | -0.3 to 7  | V    |

| Input Common-Mode Range                                                           | $V_{CM}$     | -14 to 85  | V    |

| Differential Input Voltage                                                        | $V_{ID}$     | $\pm V_S$  | V    |

| Maximum Input Current                                                             | $I_I$        | $\pm 10$   | mA   |

| Maximum Output Current                                                            | $I_O$        | $\pm 50$   | mA   |

| Continuous Total Power Dissipation                                                | $P_D$        | 200        | mW   |

| Maximum Junction Temperature                                                      | $T_{J(max)}$ | 150        | °C   |

| Storage Temperature Range                                                         | $T_{STG}$    | -65 to 150 | °C   |

| ESD Capability (Note 2)                                                           |              |            | V    |

| Human Body Model, Input pins                                                      | HBM          | $\pm 7000$ |      |

| Human Body Model, All other pins                                                  | HBM          | $\pm 4000$ |      |

| Charged Device Model                                                              | CDM          | $\pm 1000$ |      |

| Latch-Up Current (Note 3)                                                         |              | $\pm 100$  | mA   |

| Moisture Sensitivity Level                                                        | MSL          | Level 1    | -    |

| Lead Temperature Soldering<br>Reflow (SMD Styles Only), Pb-Free Versions (Note 4) | $T_{SLD}$    | 260        | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

2. This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per JS-001-2017 (AEC-Q100-002)

ESD Charged Device Model tested per JS-002-2014 (AEC-Q100-011)

3. Latch-up current maximum rating:  $\pm 100$  mA per JEDEC standard JESD78E (AEC-Q100-004).

4. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

## THERMAL CHARACTERISTICS (Note 5)

| Symbol        | Parameter                                    | Package | Value (Note 6) | Unit |

|---------------|----------------------------------------------|---------|----------------|------|

| $\theta_{JA}$ | Thermal Resistance, Junction-to-Air          | Micro8  | 163            | °C/W |

|               |                                              | SOIC-8  | 128            | °C/W |

| $\Psi_{JT}$   | Thermal Characteristic, Junction-to-Case Top | Micro8  | 24.4           | °C/W |

|               |                                              | SOIC-8  | 28.5           | °C/W |

| $\Psi_{JB}$   | Thermal Characteristic, Junction-to- Board   | Micro8  | 137.3          | °C/W |

|               |                                              | SOIC-8  | 103.5          | °C/W |

5. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

6. Values based on copper area of 645 mm<sup>2</sup> (or 1 in<sup>2</sup>) of 1 oz copper thickness and FR4 PCB substrate.

## OPERATING RANGES (Note 7)

| Rating                          | Symbol   | Min | Max          | Unit |

|---------------------------------|----------|-----|--------------|------|

| Supply Voltage                  | $V_S$    | 3   | 5.5          | V    |

| Common-Mode Input Voltage Range | $V_{CM}$ | -6  | 80           | V    |

| Ambient Temperature             | $T_A$    | -40 | 150 (Note 8) | °C   |

7. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

8. Operation up to  $T_A = 150$  °C is permitted, provided the total power dissipation is limited to prevent the junction temperature from exceeding the 150 °C absolute maximum limit.

# NCS7030, NCS7031, NCV7030, NCV7031

**ELECTRICAL CHARACTERISTICS** (At  $V_S = 5$  V,  $T_A = +25^\circ\text{C}$ ,  $V_{CM} = 12$  V,  $R_L \geq 10$  k $\Omega$ , unless otherwise noted. **Boldface** limits apply over the specified temperature range, guaranteed by characterization and/or design.)

| Symbol                         | Parameter                                   | Conditions                                            | Temp (°C)  | Min                    | Typ           | Max         | Unit                           |

|--------------------------------|---------------------------------------------|-------------------------------------------------------|------------|------------------------|---------------|-------------|--------------------------------|

| <b>GAIN</b>                    |                                             |                                                       |            |                        |               |             |                                |

| G                              | Total Gain, Preamplifier and Buffer         | $G = 14$ V/V<br>$G = 20$ V/V                          | 25         | —                      | 14<br>20      | —           | V/V                            |

| $G_e$                          | Gain Error                                  |                                                       | —40 to 125 | —                      | —             | <b>±0.3</b> | %                              |

|                                |                                             |                                                       | —40 to 150 | —                      | —             | <b>±0.5</b> |                                |

| $\Delta G/\Delta T$            | Gain Drift                                  |                                                       | —40 to 125 | —                      | —             | <b>±20</b>  | ppm / °C                       |

| <b>VOLTAGE OFFSET</b> (Note 9) |                                             |                                                       |            |                        |               |             |                                |

| $V_{OS}$                       | Input Offset Voltage                        |                                                       | 25         | —                      | ±100          | <b>±300</b> | $\mu\text{V}$                  |

|                                |                                             |                                                       | —40 to 125 | —                      | —             | <b>±300</b> |                                |

|                                |                                             |                                                       | —40 to 150 | —                      | —             | <b>±400</b> |                                |

| $\Delta V_{OS}/\Delta T$       | Input Offset Voltage Drift over Temperature |                                                       | —40 to 125 | —                      | —             | <b>±3</b>   | $\mu\text{V} / ^\circ\text{C}$ |

| <b>INPUT</b>                   |                                             |                                                       |            |                        |               |             |                                |

| $V_{CM}$                       | Common-Mode Input Voltage Range             |                                                       | —40 to 150 | <b>—6</b>              | —             | <b>80</b>   | V                              |

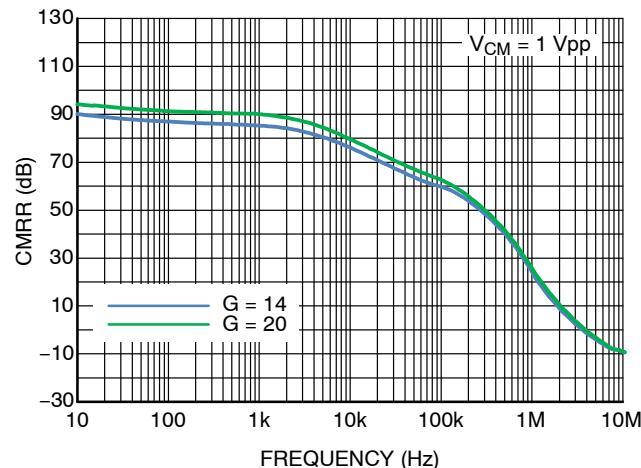

| CMRR                           | Common-Mode Rejection Ratio (Note 9)        | $V_{CM} = —6$ to 80 V                                 | —40 to 150 | <b>85</b>              | 105           | —           | dB                             |

|                                |                                             | $f = 10$ kHz<br>$V_{CM} = 12$ V,<br>1 V <sub>PP</sub> | —40 to 150 | <b>65</b><br><b>70</b> | 75<br>80      | —           |                                |

| <b>PREAMPLIFIER</b>            |                                             |                                                       |            |                        |               |             |                                |

| $G_{PRE}$                      | Gain                                        | $G = 14$ V/V<br>$G = 20$ V/V                          | 25         | —                      | 7<br>10       | —           | V/V                            |

| $G_e$                          | Gain Error                                  |                                                       | —40 to 125 | —                      | —             | <b>±0.3</b> | %                              |

| $V_{OH}$                       | Output Voltage Swing to $V_S$               |                                                       | —40 to 150 | $V_S - 0.05$           | $V_S - 0.002$ | —           | V                              |

| $V_{OL}$                       | Output Voltage Swing to GND                 |                                                       | —40 to 150 | —                      | 1.5           | <b>25</b>   | mV                             |

| $R_{PRE}$                      | Output Resistance                           |                                                       | 25         | 98                     | 100           | 102         | k $\Omega$                     |

|                                |                                             |                                                       | —40 to 150 | <b>94</b>              | —             | <b>106</b>  |                                |

| $I_{IB}$                       | Input Bias Current                          |                                                       | —40 to 125 | —                      | 200           | <b>500</b>  | $\mu\text{A}$                  |

| <b>OUTPUT BUFFER</b>           |                                             |                                                       |            |                        |               |             |                                |

| $G_{OUT}$                      | Gain                                        |                                                       | 25         | —                      | 2             | —           | V/V                            |

| $G_e$                          | Gain Error                                  |                                                       | —40 to 125 | —                      | —             | <b>±0.3</b> | %                              |

| $V_{OH}$                       | Output Voltage Swing to $V_S$               |                                                       | —40 to 150 | $V_S - 0.05$           | $V_S - 0.003$ | —           | V                              |

| $V_{OL}$                       | Output Voltage Swing to GND                 |                                                       | —40 to 150 | —                      | 0.5           | <b>25</b>   | mV                             |

| $I_{IB}$                       | Input Bias Current                          |                                                       | —40 to 125 | —                      | <b>±5</b>     | <b>±20</b>  | nA                             |

| <b>DYNAMIC PERFORMANCE</b>     |                                             |                                                       |            |                        |               |             |                                |

| BW                             | Bandwidth                                   |                                                       | 25         | —                      | 100           | —           | kHz                            |

| SR                             | Slew Rate                                   |                                                       | 25         | —                      | 1             | —           | V / $\mu\text{s}$              |

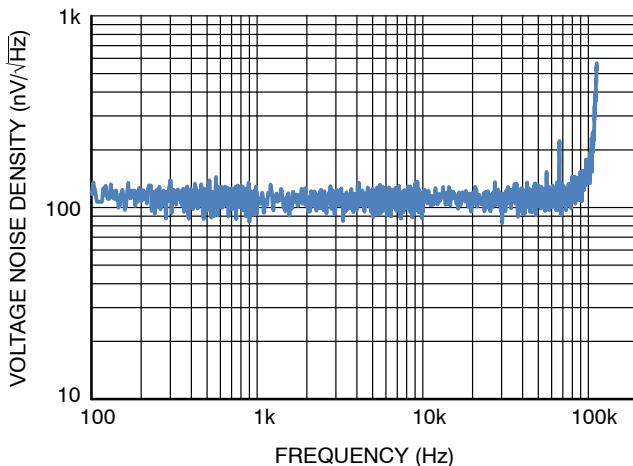

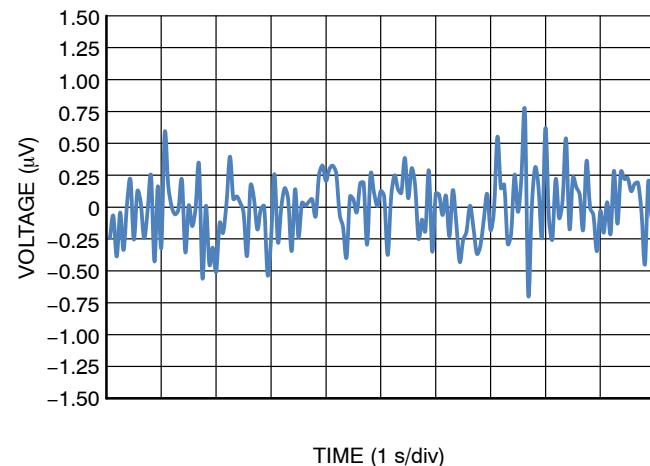

| <b>NOISE</b> (Note 9)          |                                             |                                                       |            |                        |               |             |                                |

| $V_n$                          | Voltage Noise, Peak-to-Peak                 | $f = 0.1$ Hz to 10 Hz                                 | 25         | —                      | 2             | —           | $\mu\text{V}_{\text{p-p}}$     |

| $e_n$                          | Voltage Noise Density                       | $f = 1$ kHz                                           | 25         | —                      | 120           | —           | $\text{nV} / \sqrt{\text{Hz}}$ |

| <b>POWER SUPPLY</b>            |                                             |                                                       |            |                        |               |             |                                |

| $V_S$                          | Operating Voltage Range                     |                                                       | —40 to 150 | <b>3</b>               | —             | <b>5.5</b>  | V                              |

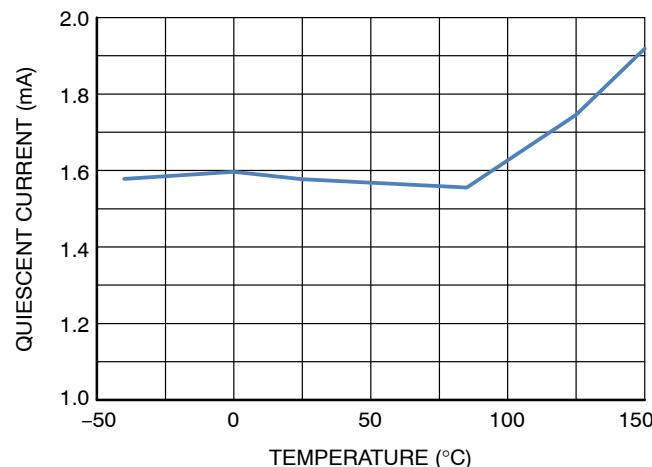

| $I_{DD}$                       | Quiescent Current                           |                                                       | 25         | —                      | 1.5           | 2.4         | mA                             |

|                                |                                             |                                                       | —40 to 125 | —                      | —             | <b>2.7</b>  |                                |

|                                |                                             |                                                       | —40 to 150 | —                      | —             | <b>2.8</b>  |                                |

| PSRR                           | Power Supply Rejection Ratio                |                                                       | —40 to 150 | <b>75</b>              | 90            | —           | dB                             |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

9. Referred to input

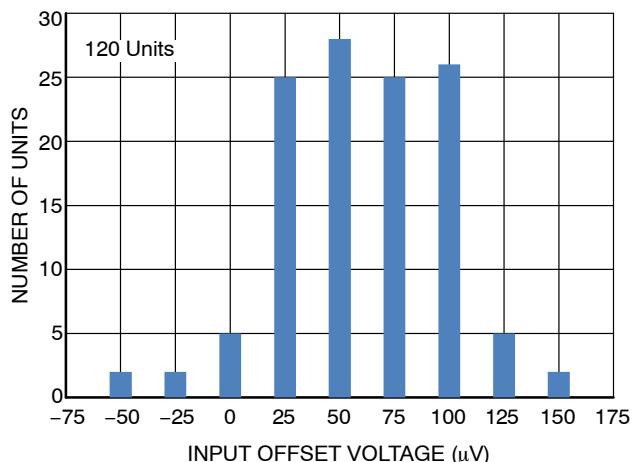

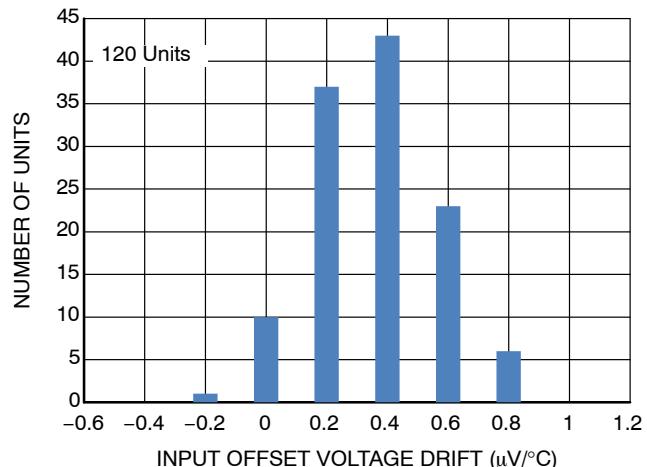

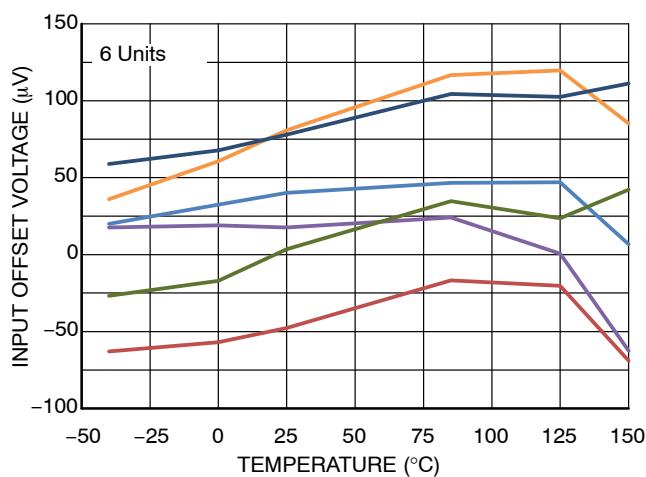

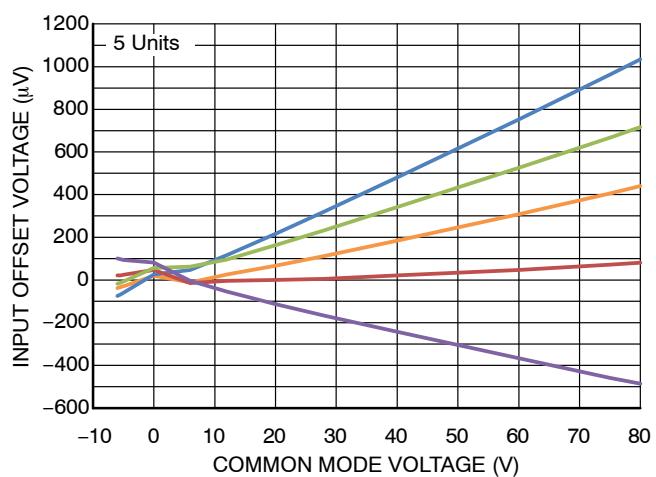

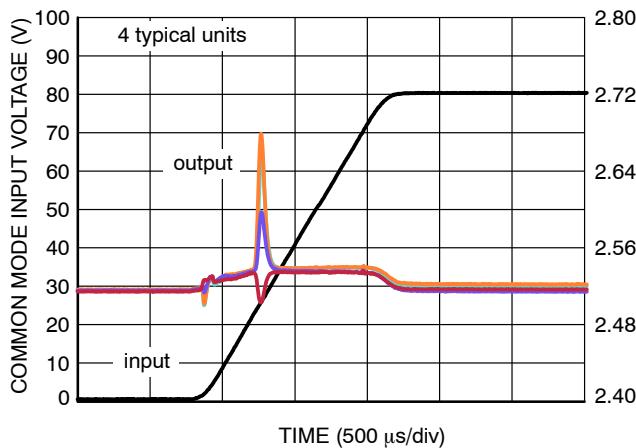

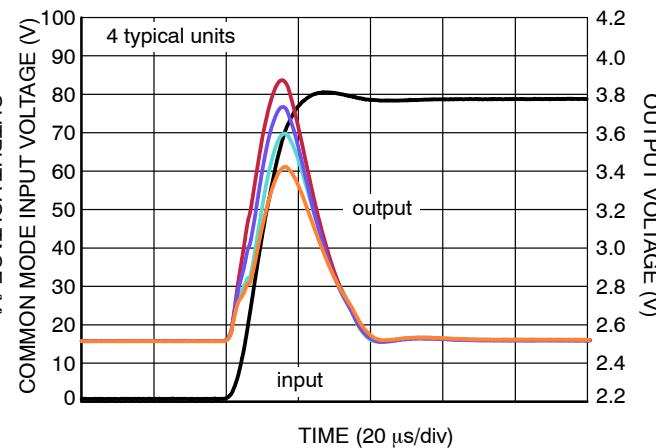

## TYPICAL CHARACTERISTICS

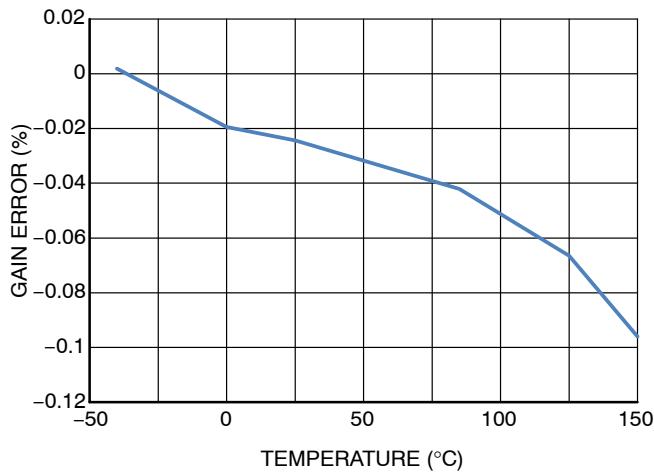

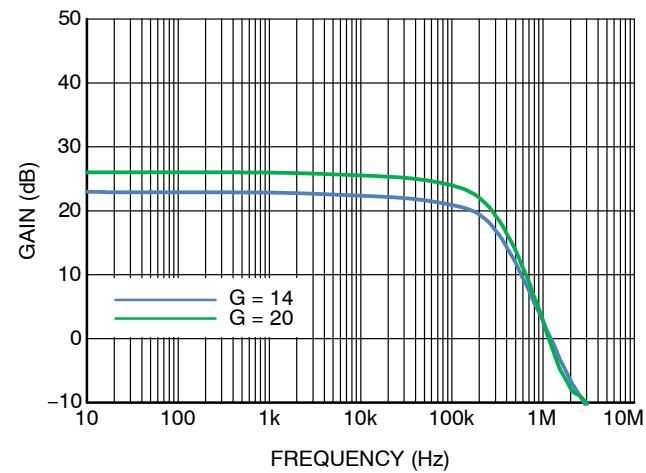

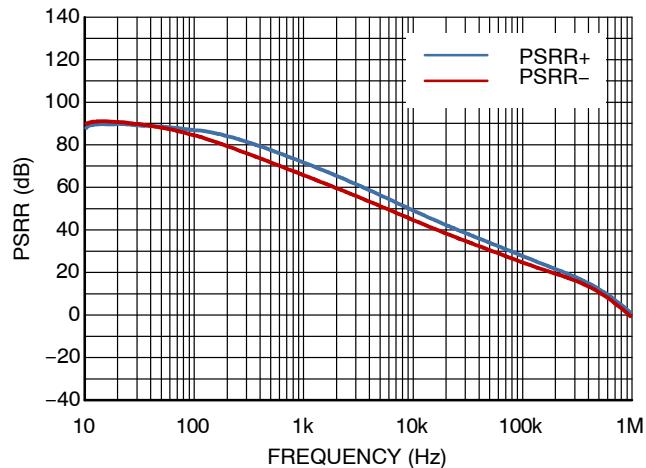

At  $T_A = 25^\circ\text{C}$ ,  $V_S = 5\text{ V}$ ,  $V_{CM} = 12\text{ V}$ ,  $R_L = 10\text{ k}\Omega$ , unless otherwise noted

Figure 3. Input Offset Voltage Distribution

Figure 4. Input Offset Voltage Drift Distribution

Figure 5. Input Offset Voltage vs. Temperature

Figure 6. Input Offset Voltage vs. Common Mode Input Voltage

Figure 7. CMRR vs. Frequency

## TYPICAL CHARACTERISTICS

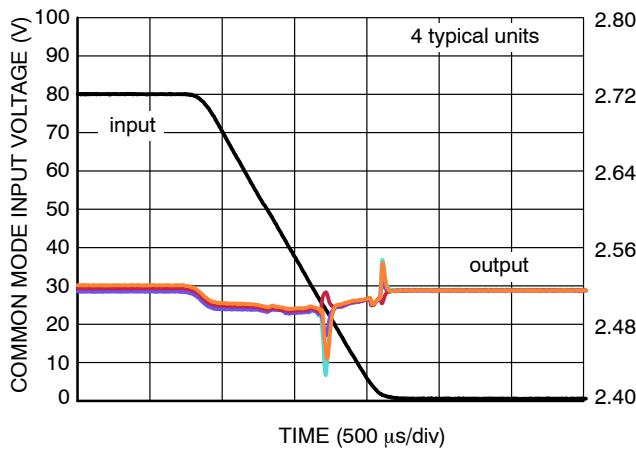

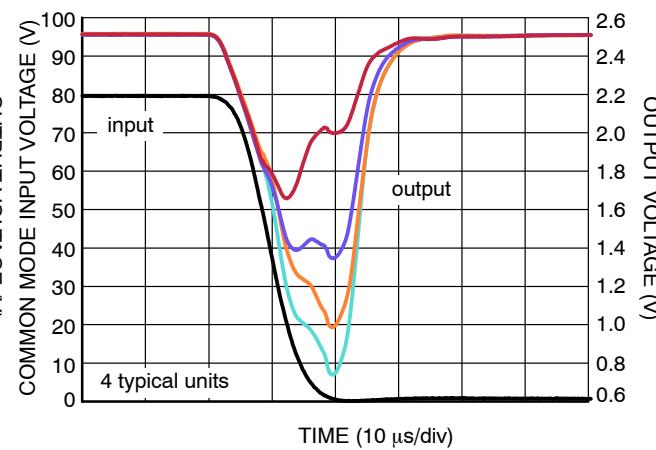

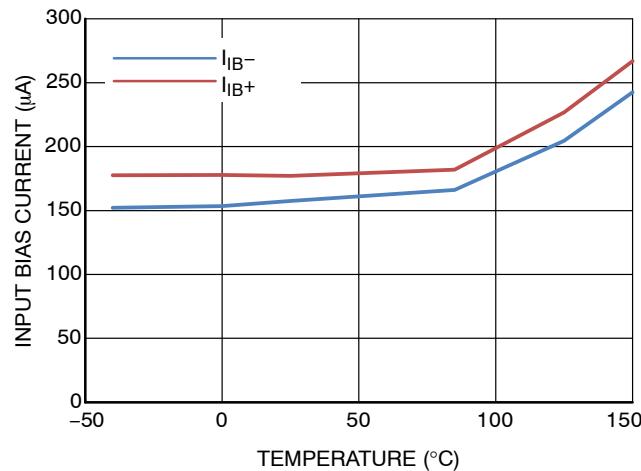

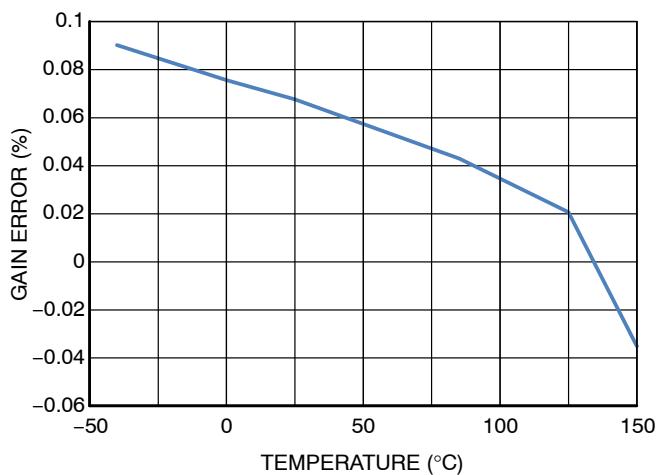

At  $T_A = 25^\circ\text{C}$ ,  $V_S = 5\text{ V}$ ,  $V_{CM} = 12\text{ V}$ ,  $R_L = 10\text{ k}\Omega$ , unless otherwise noted

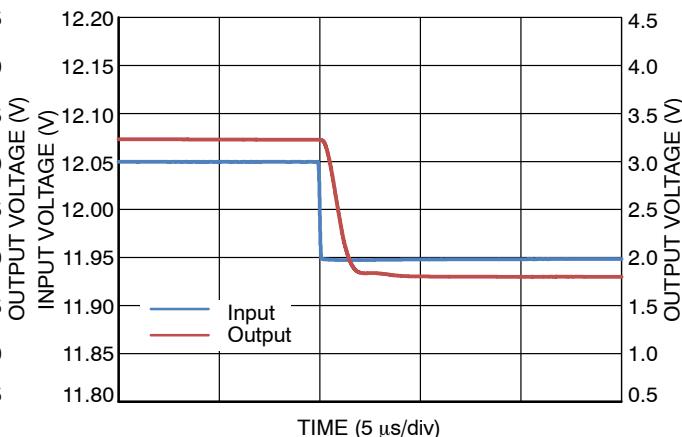

Figure 8. Common Mode Step Response with 1 ms Rising Edge

Figure 9. Common Mode Step Response with 10  $\mu\text{s}$  Rising Edge

Figure 10. Common Mode Step Response with 1 ms Falling Edge

Figure 11. Common Mode Step Response with 10  $\mu\text{s}$  Falling Edge

Figure 12. Preamplifier Input Bias Current vs. Temperature

## TYPICAL CHARACTERISTICS

At  $T_A = 25^\circ\text{C}$ ,  $V_S = 5\text{ V}$ ,  $V_{CM} = 12\text{ V}$ ,  $R_L = 10\text{ k}\Omega$ , unless otherwise noted

Figure 13. Preamplifier Gain Error vs. Temperature

Figure 14. Preamplifier Output Resistance vs. Temperature

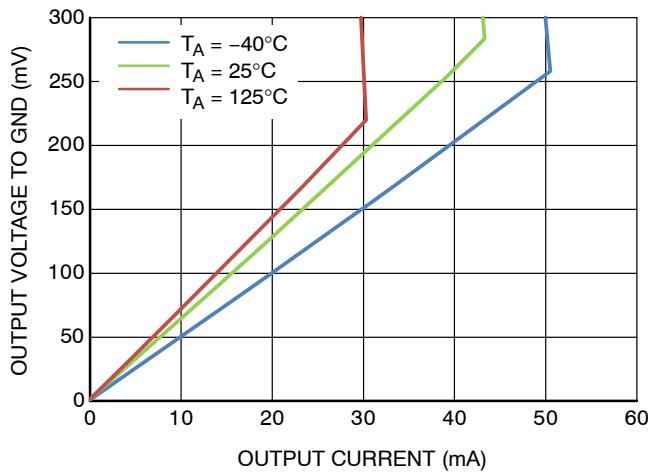

Figure 15. Buffer Output Voltage Swing to GND vs. Output Current

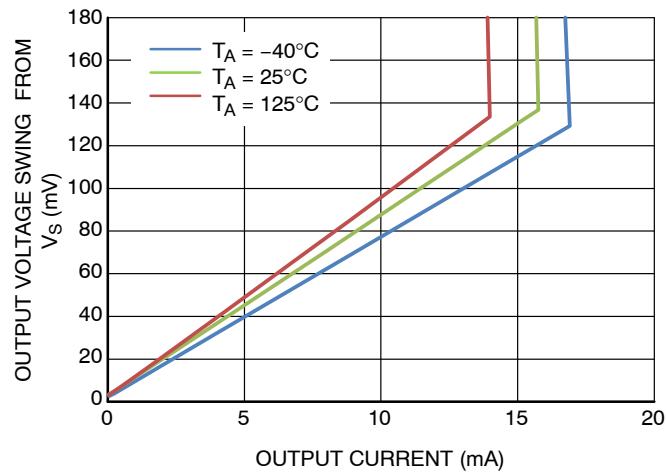

Figure 16. Buffer Output Voltage Swing from Supply Rail vs. Output Current

## TYPICAL CHARACTERISTICS

At  $T_A = 25^\circ\text{C}$ ,  $V_S = 5\text{ V}$ ,  $V_{CM} = 12\text{ V}$ ,  $R_L = 10\text{ k}\Omega$ , unless otherwise noted

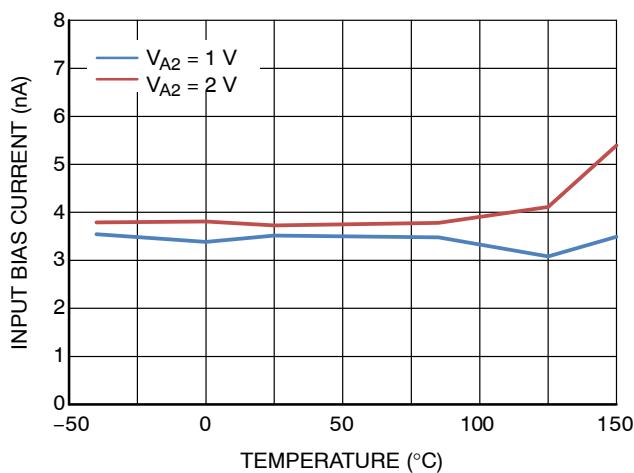

Figure 17. Buffer, Input Bias Current vs. Temperature

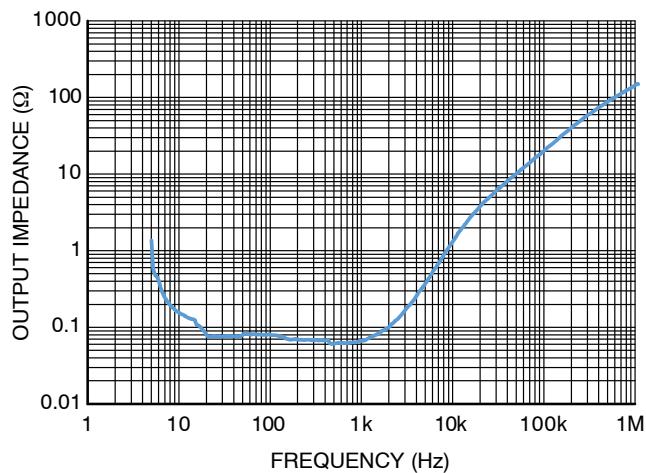

Figure 18. Buffer Output Impedance vs. Frequency

Figure 19. Total Gain Error vs. Temperature

Figure 20. Gain vs. Frequency

Figure 21. PSRR vs. Frequency

# NCS7030, NCS7031, NCV7030, NCV7031

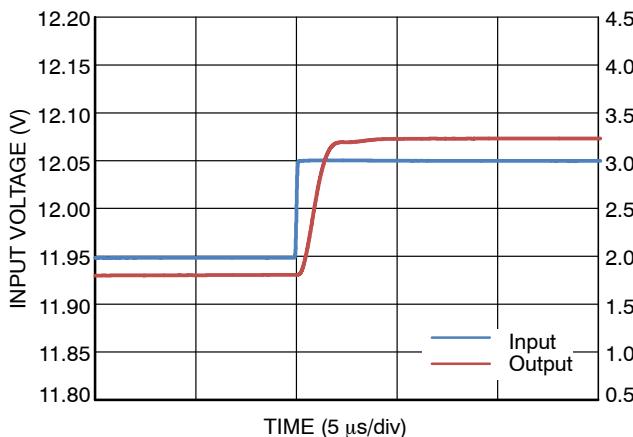

## TYPICAL CHARACTERISTICS

At  $T_A = 25^\circ\text{C}$ ,  $V_S = 5\text{ V}$ ,  $V_{CM} = 12\text{ V}$ ,  $R_L = 10\text{ k}\Omega$ , unless otherwise noted

Figure 22. Transient Response

Figure 23. Transient Response

Figure 24. Voltage Noise Density

Figure 25. Noise, 0.1 Hz to 10 Hz, Referred to Input

Figure 26. Quiescent Current

## APPLICATION INFORMATION

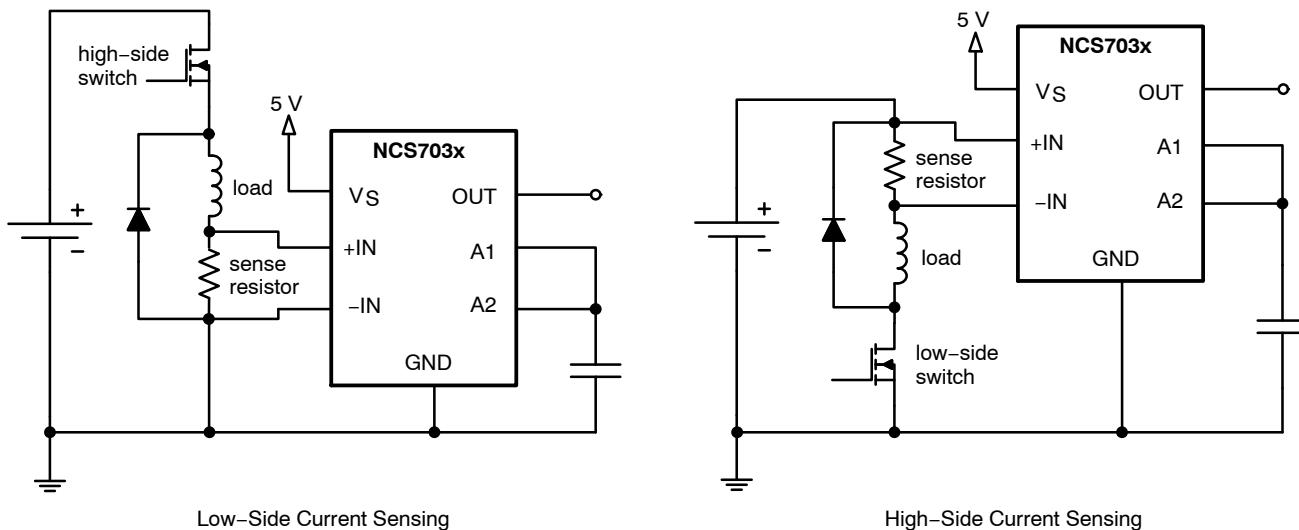

The NCS7030 and NCS7031 are current sense amplifiers featuring a wide common mode voltage up to 80 V independent of the supply voltage. The NCS703x current-sense amplifiers can be configured for both low-side and high-side current sensing.

### Current Sensing Techniques

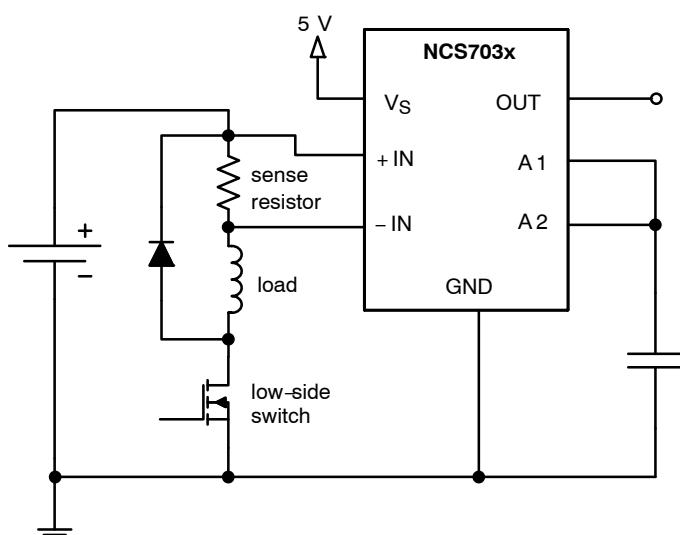

Low-side sensing appears to have the advantage of being straightforward, inexpensive, and can be implemented with

a simple op amp circuit. However, the NCS703x series of devices provides the full differential input necessary to get accurate shunt connections, while also providing a built-in gain network with precision difficult to obtain with external resistors. The NCS703x is shown in a low-side configuration in Figure 27 below.

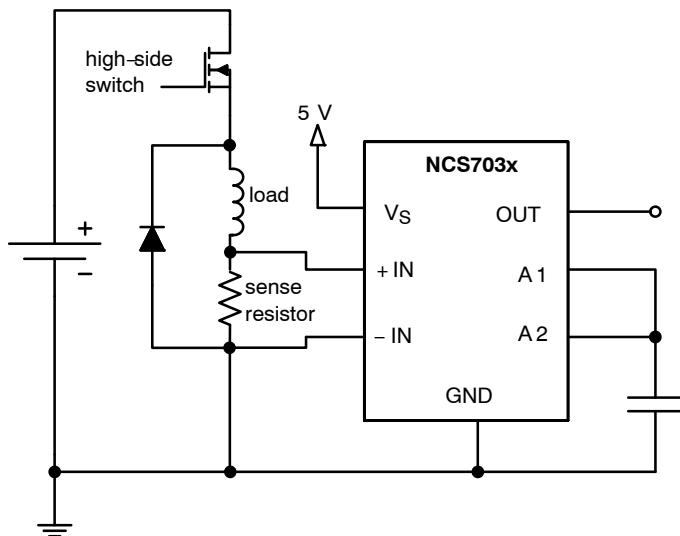

Figure 27. Low-side Current Sensing

While at times the application requires low-side sensing, only high-side sensing can detect a short from the positive supply line to ground. Furthermore, high-side sensing avoids adding resistance to the ground path of the load being

measured. The sections below focus primarily on high-side current sensing. Figure 28 shows the NCS703x configured for high-side current sensing.

Figure 28. High-side Current Sensing

## Unidirectional Operation

In unidirectional current sensing, the measured load current always flows in the same direction. Common applications for unidirectional operation include power supplies and load current monitoring.

NCS703x is internally referenced to ground; therefore, it can only measure current flowing in one direction. The +IN pin of the NCS703x should be connected to the positive side of the sense resistor, while the -IN pin should be connected to the negative side of the sense resistor.

When no current is flowing through the  $R_{SHUNT}$ , the NCS703x output is expected to be within 50 mV of ground. When current is flowing through  $R_{SHUNT}$ , the output will swing positive, up to within 100 mV of the applied supply voltage,  $V_S$ .

$$V_{out} = (V_{+in} - V_{-in}) \times G$$

## Power Supplies

The NCS703x can be connected to the same power supply that it is monitoring current from, or it can be connected to a separate power supply. If it is necessary to detect short circuit current on the load power supply, which may cause the load power supply to sag to near zero volts, a separate power supply must be used on the NCS703x. When using multiple supplies, there are no restrictions on power supply sequencing.

## A1 and A2 Pins

A1 is the preamplifier output and the A2 is the buffer input. These pins can be used to make adjustments to the gain or to create a low-pass filter. The output of the preamplifier integrates a precision resistor of  $100\text{ k}\Omega \pm 2\%$ , which can be utilized for either of these purposes.

The high impedances at the A1 and A2 pins make this connection particularly sensitive, and a careful layout is necessary if the high frequency response is required. Trace lengths should be kept at a minimum and test points should be avoided when possible at these pins. Even a small capacitance of 20 pF from the PCB can lower the  $-3\text{dB}$  signal bandwidth to 80 kHz. This filtering effect is useful for decreasing noise, and is further discussed in the upcoming "Filtering with A1 and A2" section.

## Lowering the Gain with A1 and A2

The gain can be lowered by using the A1 and A2 pins. Connecting A1 to A2 and adding a resistor from this net to GND creates a resistor divider network in combination with the internal  $100\text{ k}\Omega$  resistor, as shown by Figure 29. For example, adding an external  $100\text{ k}\Omega$  resistor, reduces the voltage going into A2 by half, reducing the overall gain by half.

Figure 29. Lowering the Gain Using an External Resistor

The adjusted overall decreased gain,  $G_{ADJ-}$ , becomes a factor of the total nominal gain,  $G$ , and the external resistor,  $REXT$ .

$$G_{ADJ-} = \frac{G \times R_{EXT}}{R_{EXT} + 100\text{ k}\Omega}$$

This equation can be rearranged to calculate the external resistor value for the desired gain value.

$$R_{EXT} = \frac{100\text{ k}\Omega \times G_{ADJ-}}{G - G_{ADJ-}}$$

## Increasing the Gain with A1 and A2

The gain can be increased by adding an external resistor in positive feedback as shown in Figure 30.

$$G_{ADJ+} = \frac{G \times R_{EXT}}{R_{EXT} - 100 \text{ k}\Omega}$$

Figure 30. Increasing the Gain Using an External Resistor in Positive Feedback

## Filtering with A1 and A2

In some applications, the current being measured may be inherently noisy. A low-pass filter can be created by connecting A1 and A2 together and adding a capacitor from

the net to GND as shown in Figure 31. This creates a simple RC filter with the internal 100 kΩ resistor. This single pole filter has a 20 dB/decade attenuation.

Figure 31. Implementing a Single-pole, Low-pass RC Filter

$$f_{FILT} = \frac{1}{2\pi(100 \text{ k}\Omega)C_{FILT}}$$

A two-pole filter with 40 dB/decade attenuation can be created with a Sallen-Key topology as shown in Figure 32.

Figure 32. Implementing a Two-pole, Low-pass Filter using the Sallen-Key Topology

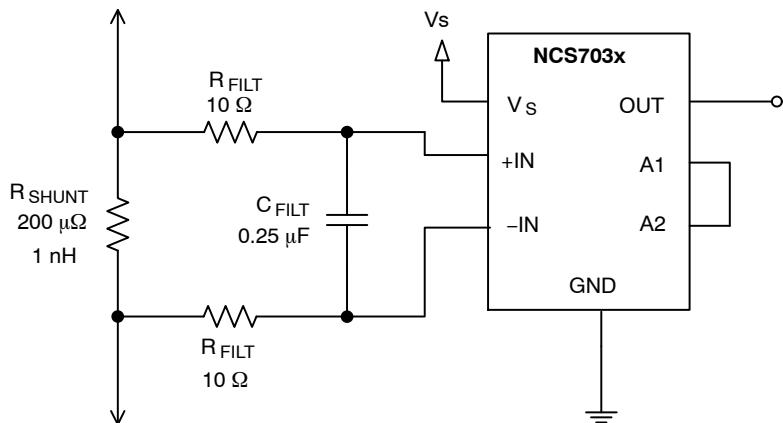

### Input Filtering

Some applications may require filtering at the input of the current sense amplifier. Figure 33 shows the recommended schematic for input filtering.

Figure 33. Input Filtering Compensates for Shunt Inductance on Shunts Less than 1 mΩ, as Well as High Frequency Noise in any Application

Input filtering is complicated by the fact that the added resistance of the filter resistors and the associated resistance mismatch between them can adversely affect gain, CMRR, and Vos. The effect on Vos is partly due to input bias currents as well. As a result, the value of the input resistors should be limited to 10 Ω or less.

As the shunt resistors decrease in value, shunt inductance can significantly affect frequency response. At values below 1 mΩ, the shunt inductance causes a zero in the transfer function that often results in corner frequencies in the low

100's of kHz. This inductance increases the amplitude of high frequency spike transient events on the current sensing line that can overload the front end of any shunt current sensing IC. This problem must be solved by filtering at the input of the amplifier. Note that all current sensing IC's are vulnerable to this problem, regardless of manufacturer claims. Filtering is required at the input of the device to resolve this problem, even if the spike frequencies are above the rated bandwidth of the device.

Ideally, select the capacitor to exactly match the time constant of the shunt resistor and its inductance; alternatively, select the capacitor to provide a pole below that point. Make the input filter time constant equal to or larger than the shunt and its inductance time constant:

$$\frac{L_{SHUNT}}{R_{SHUNT}} \leq 2R_{FILT}C_{FILT}$$

To determine the value of  $C_{FILT}$  based on using 10  $\Omega$  resistors for each  $R_{FILT}$ , the equation simplifies to:

$$C_{FILT} \geq \frac{L_{SHUNT}}{20R_{SHUNT}}$$

If the main purpose is to filter high frequency noise, the capacitor should be increased to a value that provides the desired filtering. As an example, a filtering frequency of 10 kHz would require an 0.8  $\mu\text{F}$  capacitor.

$$f_{FILT} = \frac{1}{2\pi(2R_{FILT})C_{FILT}}$$

### Common Mode Voltage Step Response

Large common mode voltage steps with fast slew rates can invoke transient voltage spikes on the output. Certain applications that operate with large common mode input voltage steps, including solenoid applications, require a thorough evaluation of the output response during such events.

There are a few methods to address this. One way to decrease the transient voltage spike is by decreasing the slew rate of the common mode voltage step. The measurement can also be filtered or averaged; this can be done by adding a low-pass filter using the A1 and A2 pins as described in the previous "Filtering with A1 and A2" section. Finally, there is the option of adding a time delay in the measurement after a common mode voltage step occurs.

The ac response to disturbances in the CMRR voltage is quantified to a certain degree in the CMRR vs. Frequency graph.

### Advantages When Used For Low-Side Current Sensing

The NCS703x series offers many advantages for low-side current sensing. The true differential input is ideal for connection to either Kelvin Sensing shunts or conventional shunts. Additionally, the true differential input rejects the common-mode noise often present even in low-side current sensing. Providing all of this in a tiny package makes it very competitive when compared to discrete op amp solutions.

### Selecting the Shunt Resistor

The desired accuracy of the current measurement determines the precision, shunt size, and the resistor value. The larger the resistor value, the more accurate the measurement possible, but a large resistor value also results in greater power loss.

For the most accurate measurements, use four terminal current sense resistors. It provides two terminals for the current path in the application circuit, and a second pair for the voltage detection path of the sense amplifier. This technique is also known as *Kelvin Sensing*. This insures that the voltage measured by the sense amplifier is the actual voltage across the resistor and does not include the small resistance of a combined connection. When using non-Kelvin shunts, closely follow manufacturers recommendations on how to lay out the sensing traces.

### Shutting Down the NCS703x

While the NCS703x does not provide a shutdown pin, a simple MOSFET, power switch, or logic gate can be used to switch off the power to the NCS703x and eliminate the quiescent current. Note that the shunt input pins will always have a current flow via the input and feedback resistors. The input pins support the rated common mode voltage even when the NCS703x does not have power applied.

# NCS7030, NCS7031, NCV7030, NCV7031

## ORDERING INFORMATION

| Gain | Device            | Marking | Package             | Shipping†          |

|------|-------------------|---------|---------------------|--------------------|

| 14   | NCS7030D2G014R2G  | 7030014 | SOIC-8<br>(Pb-Free) | 2500 / Tape & Reel |

|      | NCS7030DM2G014R2G | 3014    | Micro8<br>(Pb-Free) | 4000 / Tape & Reel |

| 20   | NCS7031D1G020R2G  | 7031020 | SOIC-8<br>(Pb-Free) | 2500 / Tape & Reel |

|      | NCS7031DM1G020R2G | 3120    | Micro8<br>(Pb-Free) | 4000 / Tape & Reel |

## AUTOMOTIVE QUALIFIED

| Gain | Device            | Marking | Package             | Shipping†          |

|------|-------------------|---------|---------------------|--------------------|

| 14   | NCV7030D2G014R2G  | 7030014 | SOIC-8<br>(Pb-Free) | 2500 / Tape & Reel |

|      | NCV7030DM2G014R2G | 3014    | Micro8<br>(Pb-Free) | 4000 / Tape & Reel |

| 20   | NCV7031D1G020R2G  | 7031020 | SOIC-8<br>(Pb-Free) | 2500 / Tape & Reel |

|      | NCV7031DM1G020R2G | 3120    | Micro8<br>(Pb-Free) | 4000 / Tape & Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

SCALE 1:1

SOIC-8 NB

CASE 751-07

ISSUE AK

DATE 16 FEB 2011

## NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

6. 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

| DIM | MILLIMETERS |      | INCHES    |       |

|-----|-------------|------|-----------|-------|

|     | MIN         | MAX  | MIN       | MAX   |

| A   | 4.80        | 5.00 | 0.189     | 0.197 |

| B   | 3.80        | 4.00 | 0.150     | 0.157 |

| C   | 1.35        | 1.75 | 0.053     | 0.069 |

| D   | 0.33        | 0.51 | 0.013     | 0.020 |

| G   | 1.27 BSC    |      | 0.050 BSC |       |

| H   | 0.10        | 0.25 | 0.004     | 0.010 |

| J   | 0.19        | 0.25 | 0.007     | 0.010 |

| K   | 0.40        | 1.27 | 0.016     | 0.050 |

| M   | 0 °         | 8 °  | 0 °       | 8 °   |

| N   | 0.25        | 0.50 | 0.010     | 0.020 |

| S   | 5.80        | 6.20 | 0.228     | 0.244 |

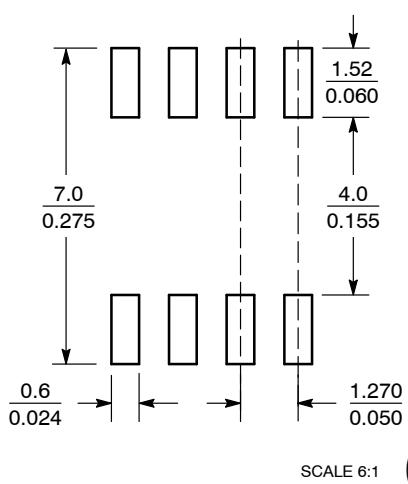

## SOLDERING FOOTPRINT\*

SCALE 6:1 (mm/inches)

GENERIC

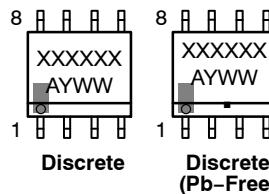

MARKING DIAGRAM\*

XXXXX = Specific Device Code

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

■ = Pb-Free Package

XXXXXX = Specific Device Code

A = Assembly Location

Y = Year

WW = Work Week

■ = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

\*For additional information on our Pb-Free strategy and soldering details, please download the **onsemi** Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

## STYLES ON PAGE 2

|                  |             |                                                                                                                                                                                     |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |

| DESCRIPTION:     | SOIC-8 NB   | PAGE 1 OF 2                                                                                                                                                                         |

**onsemi** and **Onsemi** are trademarks of Semiconductor Components Industries, LLC dba **onsemi** or its subsidiaries in the United States and/or other countries. **onsemi** reserves the right to make changes without further notice to any products herein. **onsemi** makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. **onsemi** does not convey any license under its patent rights nor the rights of others.

**SOIC-8 NB**

**CASE 751-07**

**ISSUE AK**

DATE 16 FEB 2011

|                                                                                                                                                                                            |                                                                                                                                                                                   |                                                                                                                                                                             |                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 1:<br>PIN 1. Emitter<br>2. Collector<br>3. Collector<br>4. Emitter<br>5. Emitter<br>6. Base<br>7. Base<br>8. Emitter                                                                 | STYLE 2:<br>PIN 1. Collector, Die, #1<br>2. Collector, #1<br>3. Collector, #2<br>4. Collector, #2<br>5. Base, #2<br>6. Emitter, #2<br>7. Base, #1<br>8. Emitter, #1               | STYLE 3:<br>PIN 1. Drain, Die #1<br>2. Drain, #1<br>3. Drain, #2<br>4. Drain, #2<br>5. Gate, #2<br>6. Source, #2<br>7. Gate, #1<br>8. Source, #1                            | STYLE 4:<br>PIN 1. Anode<br>2. Anode<br>3. Anode<br>4. Anode<br>5. Anode<br>6. Anode<br>7. Anode<br>8. Common Cathode                                                                           |

| STYLE 5:<br>PIN 1. Drain<br>2. Drain<br>3. Drain<br>4. Drain<br>5. Gate<br>6. Gate<br>7. Source<br>8. Source                                                                               | STYLE 6:<br>PIN 1. Source<br>2. Drain<br>3. Drain<br>4. Source<br>5. Source<br>6. Gate<br>7. Gate<br>8. Source                                                                    | STYLE 7:<br>PIN 1. Input<br>2. External Bypass<br>3. Third Stage Source<br>4. Ground<br>5. Drain<br>6. Gate 3<br>7. Second Stage Vd<br>8. First Stage Vd                    | STYLE 8:<br>PIN 1. Collector, Die #1<br>2. Base, #1<br>3. Base, #2<br>4. Collector, #2<br>5. Collector, #2<br>6. Emitter, #2<br>7. Emitter, #1<br>8. Collector, #1                              |

| STYLE 9:<br>PIN 1. Emitter, Common<br>2. Collector, Die #1<br>3. Collector, Die #2<br>4. Emitter, Common<br>5. Emitter, Common<br>6. Base, Die #2<br>7. Base, Die #1<br>8. Emitter, Common | STYLE 10:<br>PIN 1. Ground<br>2. Bias 1<br>3. Output<br>4. Ground<br>5. Ground<br>6. Bias 2<br>7. Input<br>8. Ground                                                              | STYLE 11:<br>PIN 1. Source 1<br>2. Gate 1<br>3. Source 2<br>4. Gate 2<br>5. Drain 2<br>6. Drain 2<br>7. Drain 1<br>8. Drain 1                                               | STYLE 12:<br>PIN 1. Source<br>2. Source<br>3. Source<br>4. Gate<br>5. Drain<br>6. Drain<br>7. Drain<br>8. Drain                                                                                 |

| STYLE 13:<br>PIN 1. N.C.<br>2. Source<br>3. Source<br>4. Gate<br>5. Drain<br>6. Drain<br>7. Drain<br>8. Drain                                                                              | STYLE 14:<br>PIN 1. N-Source<br>2. N-Gate<br>3. P-Source<br>4. P-Gate<br>5. P-Drain<br>6. P-Drain<br>7. N-Drain<br>8. N-Drain                                                     | STYLE 15:<br>PIN 1. Anode 1<br>2. Anode 1<br>3. Anode 1<br>4. Anode 1<br>5. Cathode, Common<br>6. Cathode, Common<br>7. Cathode, Common<br>8. Cathode, Common               | STYLE 16:<br>PIN 1. Emitter, Die #1<br>2. Base, Die #1<br>3. Emitter, Die #2<br>4. Base, Die #2<br>5. Collector, Die #2<br>6. Collector, Die #2<br>7. Collector, Die #1<br>8. Collector, Die #1 |

| STYLE 17:<br>PIN 1. VCC<br>2. V2OUT<br>3. V1OUT<br>4. TXE<br>5. RXE<br>6. VEE<br>7. GND<br>8. ACC                                                                                          | STYLE 18:<br>PIN 1. Anode<br>2. Anode<br>3. Source<br>4. Gate<br>5. Drain<br>6. Drain<br>7. Cathode<br>8. Cathode                                                                 | STYLE 19:<br>PIN 1. Source 1<br>2. Gate 1<br>3. Source 2<br>4. Gate 2<br>5. Drain 2<br>6. Mirror 2<br>7. Drain 1<br>8. Mirror 1                                             | STYLE 20:<br>PIN 1. Source (N)<br>2. Gate (N)<br>3. Source (P)<br>4. Gate (P)<br>5. Drain<br>6. Drain<br>7. Drain<br>8. Drain                                                                   |

| STYLE 21:<br>PIN 1. Cathode 1<br>2. Cathode 2<br>3. Cathode 3<br>4. Cathode 4<br>5. Cathode 5<br>6. Common Anode<br>7. Common Anode<br>8. Cathode 6                                        | STYLE 22:<br>PIN 1. I/O Line 1<br>2. Common Cathode/VCC<br>3. Common Cathode/VCC<br>4. I/O Line 3<br>5. Common Anode/GND<br>6. I/O Line 4<br>7. I/O Line 5<br>8. Common Anode/GND | STYLE 23:<br>PIN 1. Line 1 IN<br>2. Common Anode/GND<br>3. Common Anode/GND<br>4. Line 2 IN<br>5. Line 2 OUT<br>6. Common Anode/GND<br>7. Common Anode/GND<br>8. Line 1 OUT | STYLE 24:<br>PIN 1. Base<br>2. Emitter<br>3. Collector/Anode<br>4. Collector/Anode<br>5. Cathode<br>6. Cathode<br>7. Collector/Anode<br>8. Collector/Anode                                      |

| STYLE 25:<br>PIN 1. VIN<br>2. N/C<br>3. REXT<br>4. GND<br>5. IOUT<br>6. IOUT<br>7. IOUT<br>8. IOUT                                                                                         | STYLE 26:<br>PIN 1. GND<br>2. dv/dt<br>3. Enable<br>4. ILIMIT<br>5. Source<br>6. Source<br>7. Source<br>8. VCC                                                                    | STYLE 27:<br>PIN 1. ILIMIT<br>2. OVLO<br>3. UVLO<br>4. INPUT+<br>5. SOURCE<br>6. SOURCE<br>7. SOURCE<br>8. DRAIN                                                            | STYLE 28:<br>PIN 1. SW_TO_GND<br>2. DASIC_OFF<br>3. DASIC_SW_DET<br>4. GND<br>5. V_MON<br>6. VBUCK<br>7. VBUCK<br>8. VIN                                                                        |

| STYLE 29:<br>PIN 1. Base, Die #1<br>2. Emitter, #1<br>3. Base, #2<br>4. Emitter, #2<br>5. Collector, #2<br>6. Collector, #2<br>7. Collector, #1<br>8. Collector, #1                        | STYLE 30:<br>PIN 1. DRAIN 1<br>2. DRAIN 1<br>3. GATE 2<br>4. SOURCE 2<br>5. SOURCE 1/DRAIN 2<br>6. SOURCE 1/DRAIN 2<br>7. SOURCE 1/DRAIN 2<br>8. GATE 1                           |                                                                                                                                                                             |                                                                                                                                                                                                 |

|                  |             |                                                                                                                                                                                     |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |

| DESCRIPTION:     | SOIC-8 NB   | PAGE 2 OF 2                                                                                                                                                                         |

**onsemi** and **OnSemi** are trademarks of Semiconductor Components Industries, LLC dba **onsemi** or its subsidiaries in the United States and/or other countries. **onsemi** reserves the right to make changes without further notice to any products herein. **onsemi** makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. **onsemi** does not convey any license under its patent rights nor the rights of others.

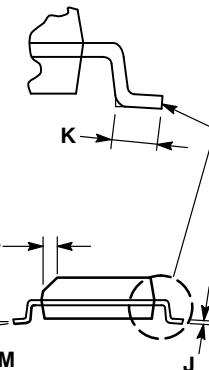

SCALE 2:1

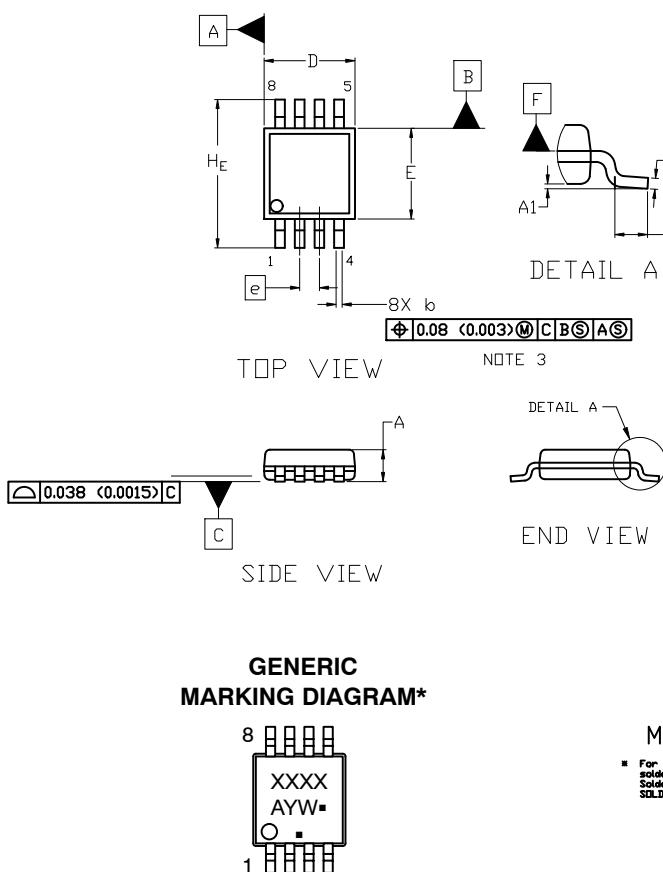

**Micro8**

CASE 846A-02

ISSUE K

DATE 16 JUL 2020

**GENERIC MARKING DIAGRAM\***

XXXX = Specific Device Code

A = Assembly Location

Y = Year

W = Work Week

■ = Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

## NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2009.

2. CONTROLLING DIMENSION: MILLIMETERS

3. DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.10 mm IN EXCESS OF MAXIMUM MATERIAL CONDITION.

4. DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 mm PER SIDE. DIMENSION E DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 mm PER SIDE. DIMENSIONS D AND E ARE DETERMINED AT DATUM F.

5. DATUMS A AND B ARE TO BE DETERMINED AT DATUM F.

6. A1 IS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY.

| DIM            | MILLIMETERS |      |      |

|----------------|-------------|------|------|

|                | MIN.        | NOM. | MAX. |

| A              | ---         | ---  | 1.10 |

| A1             | 0.05        | 0.08 | 0.15 |

| b              | 0.25        | 0.33 | 0.40 |

| c              | 0.13        | 0.18 | 0.23 |

| D              | 2.90        | 3.00 | 3.10 |

| E              | 2.90        | 3.00 | 3.10 |

| e              | 0.65 BSC    |      |      |

| H <sub>E</sub> | 4.75        | 4.90 | 5.05 |

| L              | 0.40        | 0.55 | 0.70 |

For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SODERRM/D.

## STYLE 1:

PIN 1. SOURCE

2. SOURCE

3. SOURCE

4. GATE

5. DRAIN

6. DRAIN

7. DRAIN

8. DRAIN

## STYLE 2:

PIN 1. SOURCE 1

2. GATE 1

3. SOURCE 2

4. GATE 2

5. DRAIN 2

6. DRAIN 2

7. DRAIN 1

8. DRAIN 1

## STYLE 3:

PIN 1. N-SOURCE

2. N-GATE

3. P-SOURCE

4. P-GATE

5. P-DRAIN

6. P-DRAIN

7. N-DRAIN

8. N-DRAIN

|                  |             |                                                                                                                                                                                     |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DOCUMENT NUMBER: | 98ASB14087C | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |

| DESCRIPTION:     | MICRO8      | PAGE 1 OF 1                                                                                                                                                                         |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

**onsemi**, **ONSEMI**, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "**onsemi**" or its affiliates and/or subsidiaries in the United States and/or other countries. **onsemi** owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of **onsemi**'s product/patent coverage may be accessed at [www.onsemi.com/site/pdf/Patent-Marking.pdf](http://www.onsemi.com/site/pdf/Patent-Marking.pdf). **onsemi** reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and **onsemi** makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## ADDITIONAL INFORMATION

### TECHNICAL PUBLICATIONS:

Technical Library: [www.onsemi.com/design/resources/technical-documentation](http://www.onsemi.com/design/resources/technical-documentation)

onsemi Website: [www.onsemi.com](http://www.onsemi.com)

### ONLINE SUPPORT: [www.onsemi.com/support](http://www.onsemi.com/support)

For additional information, please contact your local Sales Representative at

[www.onsemi.com/support/sales](http://www.onsemi.com/support/sales)

# Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

[onsemi](#):

[NCS7031D1G020R2G](#) [NCS7030D2G014R2G](#) [NCS7030DM2G014R2G](#)